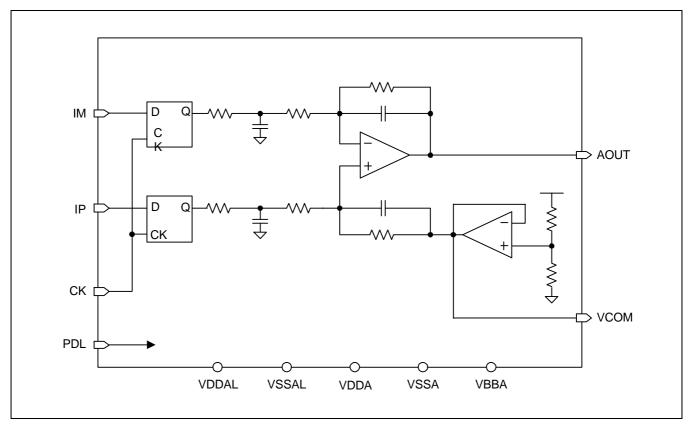

#### **GENERAL DESCRIPTION**

lpf0428x is developed for analog conversion of PWM input and analog low pass filtering function for audio signal processing. The core consists of D-F/F and active R-C analog filter. And it has analog 2.3 volts supply operation.

## **FEATURES**

- Analog 2.3Volt Operation

- 2'nd Order Low Pass Filter

- On chip common level generator

## **APPLICATIONS**

Audio Signal Player

## **FUNCTIONAL BLOCK DIAGRAM**

#### Ver 1.3 (Nov 2001)

This datasheet is a preliminary version. No responsibility is assumed by SEC for its use nor for any infringements of patents or other rights of third parties that may result from its use. The content of this datasheet is subject to change without any notice.

ANALOG LOW PASS FILTER LPF0428X

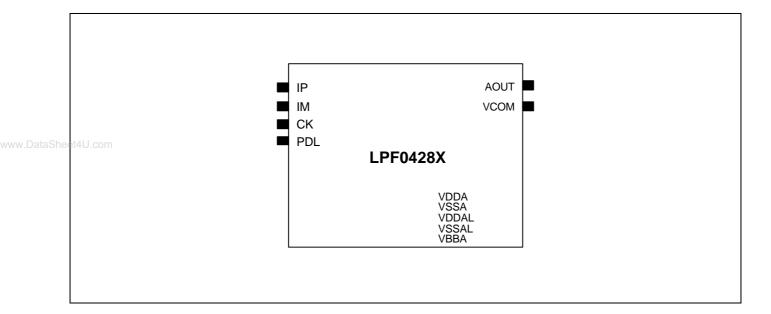

## **CORE PIN DESCRIPTION**

| Pin Name           | I/O Type | I/O Pad   | Pin Description            |

|--------------------|----------|-----------|----------------------------|

| AOUT               | AO       | pmoa_abb  | Analog Output              |

| VCOM               | AO       | pmoa_abb  | Analog Common Level Output |

| IP                 | DI       | pmicc_abb | PWM Positive Input         |

| IM                 | DI       | pmicc_abb | PWM Negative Input         |

| CK<br>Sheet/LL com | DI       | pmicc_abb | Master Clock Input         |

| PDL                | DI       | pmicc_abb | Power Down (Active Low)    |

| VDDA               | AP       | vdd2t_abb | Analog Power               |

| VSSA               | AG       | vss2t_abb | Analog Ground              |

| VDDAL              | AP       | vdd2t_abb | Analog Logic Power         |

| VSSAL              | AG       | vss2t_abb | Analog Logic Ground        |

| VBBA               | AG       | vbb_abb   | Bulk                       |

# I/O Type Abbr.

Al: Analog Input

DI: Digital Input

AO: Analog Output

— DO: Digital Output

AB: Analog Bi-direction

DB: Digital Bi-direction

— AP: Analog Power

AG: Analog Ground

— DP: Digital Power

- DG: Digital Ground

# **CORE CONFIGURATION**

ANALOG LOW PASS FILTER LPF0428X

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristics           | Symbol      | Value                  | Unit |

|---------------------------|-------------|------------------------|------|

| Supply Voltage            | VDDA, VDDAL | 5.0                    | V    |

| Analog Output Voltage     | -           | VSSA-0.15 ~ VDDA+0.15  | V    |

| Digital Input Voltage     | -           | VSSAL+0.5 ~ VDDAL-0.15 | V    |

| Storage Temperature Range | Tstg        | -45 to 125             | °C   |

## NOTES:

- ABSOLUTE MAXIMUM RATING specifies the values beyond which the device may be damaged permanently. Exposure to

ABSOLUTE MAXIMUM RATING conditions for extended periods may affect reliability. Each condition value is applied with

the other values kept within the following operating conditions and function operation under any of these conditions is not

implied.

- 2. All voltages are measured with respect to VSSA unless otherwise specified.

- 3. 100pF capacitor is discharged through a  $1.5K\Omega$  resistor (Human body model)

#### RECOMMENDED OPERATING CONDITIONS

| Characteristics            | Symbol      | Min | Тур | Max | Unit |

|----------------------------|-------------|-----|-----|-----|------|

| Supply Voltage             | VDDA, VDDAL | -   | 2.3 | -   | V    |

| Digital Input High Voltage |             | 1.8 | -   | -   | V    |

| Digital Input Low Voltage  |             | -   | -   | 0.5 | V    |

| Operating Temperature      | Topr        | 0   | -   | 70  | °C   |

**NOTE:** It is strongly recommended that all the supply pins (VDDA, VDDAL) be powered from the same source to avoid power latch-up.

## **AC ELECTRICAL CHARACTERISTICS**

(Measurement Bandwidth is 20Hz~20kHz. Full scale input sine wave 1kHz, CK=16.9344MHz, VDDA=2.3V, VDDAL=2.3V Ta=55°C,Unless otherwise specified.)

| Characteristics              | Symbol | Min | Тур     | Max | Unit | Conditions               |

|------------------------------|--------|-----|---------|-----|------|--------------------------|

| Total Harmonic Distortion    | THD    | -   | TBD     | -   | %    | 0dB 1kHz Sine Wave Input |

| Clock Frequency              | Fck    | -   | 16.9344 | -   | MHz  | -                        |

| Signal to Noise Ratio        | SNR    | -   | TBD     | -   | dB   | 0dB 1kHz Sine Wave Input |

| Offset Voltage               | Vos    | -   | -       | ±20 | mV   | Zero Level Input         |

| Analog Output Maximum Range  | Vmax   | -   | 2.0     | -   | Vpp  | -                        |

| Common Level Voltage         | Vcom   | -   | VDDA/2  | -   | V    | -                        |

| Analog Output Load Resistor  | Rld    | 10  | -       | -   | kΩ   | -                        |

| Analog Output Load Capacitor | Cld    | -   | -       | 10  | pF   | -                        |

| Operating Current            | lopr   | -   | 1.1     | -   | mA   | -                        |

| Power Down Current           | Ipwdn  | -   | 1       | •   | uA   | -                        |

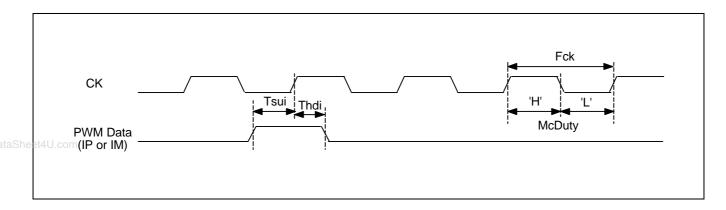

# **TIMING DIAGRAM**

| Parameter          | Symbol | min | typ     | max | Units |

|--------------------|--------|-----|---------|-----|-------|

| Data Setup Time    | Tsui   | -   | 20      | -   | ns    |

| Data Hold Time     | Thdi   | -   | 20      | -   | ns    |

| CK Clock frequency | Fck    | -   | 16.9344 | -   | MHz   |

| CK Duty ratio      | McDuty | -   | 50      | -   | %     |

# **FUNCTION DESCRIPTION**

# Power Down

PDL control the power down function of lpf0428x.

| PDL | Function                                            |

|-----|-----------------------------------------------------|

| L   | Power Down                                          |

|     | Digital inputs (CK, IP, IM) is blocked by nand gate |

| Н   | Normal Operation                                    |

ANALOG LOW PASS FILTER LPF0428X

# **HISTORY CARD**

|           | Version                                                                            | Date     | Modified Items                                                          | Comments |

|-----------|------------------------------------------------------------------------------------|----------|-------------------------------------------------------------------------|----------|

|           | Ver 1.0                                                                            | Aug 2001 | 1. First preliminary version published.                                 |          |

|           | Ver 1.1 Sep 2001 1. Delay Cell Included by customer request. So 6 pins were added. |          |                                                                         |          |

|           |                                                                                    |          | (SA,SB,SC,SD,DLYIM,DLYIP)                                               |          |

|           | Ver 1.2                                                                            | Sep 2001 | 1. The modified items of ver. 1.1 was canceled.                         |          |

| www.Datas | Sheet4U.com                                                                        |          | The PDL_DF pin added. The buffered output of D-F/F (IMQ,IPQ) was added. |          |

|           | Ver 1.3                                                                            | Nov 2001 | 1. Ver 1.2 was canceld.                                                 |          |

|           |                                                                                    |          | 2. Return to ver 1.0                                                    |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |

|           |                                                                                    |          |                                                                         |          |