LP8557, LP85571

SNVSA15B - DECEMBER 2013 - REVISED DECEMBER 2015

# LP8557 High-Efficiency LED Backlight Driver For Tablets

#### 1 Features

- High-Efficiency DC-DC Boost Converter With 28-V Integrated Power MOSFET

- 2.7-V to 5.5-V VDD Range for Supporting Single-Cell Li-Ion Battery Applications

- Six 25-mA High-Precision LED Current Sinks

- Adaptive Boost Voltage and LED Current Sink Headroom Controls for Maximum System Efficiency

- LED String Count Auto-Detect for Maximum Design Flexibility

- Smart Phase Shift PWM Mode for Reduced Audible Noise

- PWM Input Duty Cycle Brightness Control, PWM Output Frequency Selectable Independent of Input Frequency

- Hybrid PWM Plus Current Dimming for Higher LED Drive Optical Efficiency

- Switching Frequency, PWM Output Frequency, and LED Current can be set Through Resistors or I<sup>2</sup>C. Interface

- Programmable Boost SW Slew Rate Control and Spread Spectrum Scheme for Reduced Switching Noise and Improved EMI Performance

- UVLO, TSD, BST\_OVP, BST\_OCP, BST\_UV, LED OPEN\* and LED Short Fault Coverage

- Minimum Number of External Components

# 2 Applications

Tablet LCD Display LED Backlight

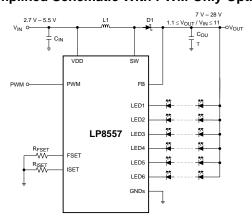

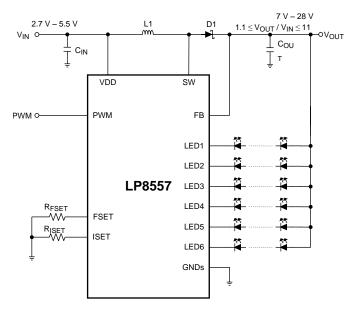

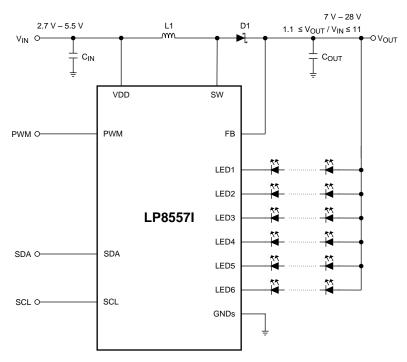

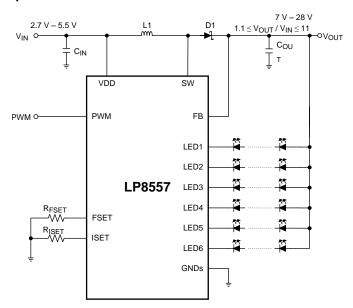

#### **Simplified Schematic With PWM-Only Option**

# 3 Description

The LP8557 and LP8557I are high-efficiency LED drivers each featuring an integrated DC-DC inductive boost converter and six high-precision current sinks. LP8557 is intended for applications that exclusively use a pulse width modulated (PWM) signal for controlling the brightness while LP8557I is intended for applications that can utilize an I<sup>2</sup>C master as well.

The boost converter has adaptive output voltage control. This feature minimizes the power consumption by adjusting the voltage to the lowest sufficient level under all conditions.

The adaptive current sink headroom voltage control scales the headroom voltage with the LED current for optimal system efficiency.

The LED string auto-detect function enables use of the same device in systems with 1 to 6 LED strings for the maximum design flexibility.

Proprietary hybrid PWM plus current mode dimming enables additional system power savings. Phase-shift PWM allows reduced audible noise and smaller boost output capacitors.

Flexible CABC support combines brightness level selections based on the PWM input and I<sup>2</sup>C commands.

#### Device Information<sup>(1)</sup>

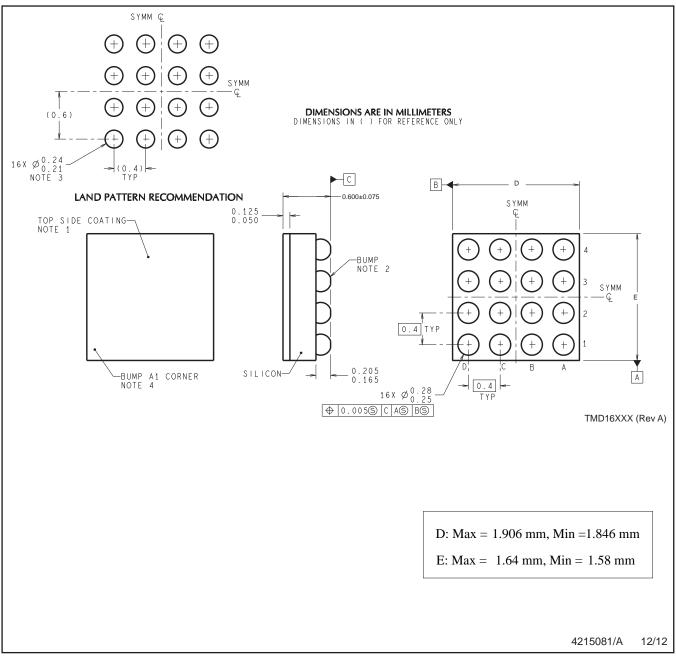

| PART NUMBER | PACKAGE     | BODY SIZE (MAX)    |

|-------------|-------------|--------------------|

| LP8557      | DCDC A (46) | 1.006 mm v 1.64 mm |

| LP8557I     | DSBGA (16)  | 1.906 mm x 1.64 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

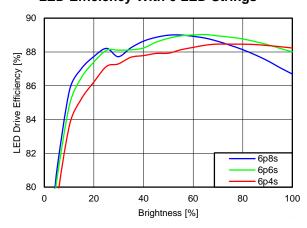

#### **LED Efficiency With 6 LED Strings**

# **Table of Contents**

| 1 | Features 1                                                      |    | 8.2 Functional Block Diagram         | 11 |

|---|-----------------------------------------------------------------|----|--------------------------------------|----|

| 2 | Applications 1                                                  |    | 8.3 Feature Description              | 12 |

| 3 | Description 1                                                   |    | 8.4 Device Functional Modes          | 20 |

| 4 | Revision History                                                |    | 8.5 Programming                      | 20 |

| 5 | Device Comparison Table                                         |    | 8.6 Register Maps                    | 24 |

| 6 | Pin Function and Configurations                                 | 9  | Application and Implementation       | 31 |

| - | _                                                               |    | 9.1 Application Information          | 31 |

| 7 | Specifications                                                  |    | 9.2 Typical Applications             | 34 |

|   | 7.1 Absolute Maximum Ratings                                    | 10 | Power Supply Recommendations         | 38 |

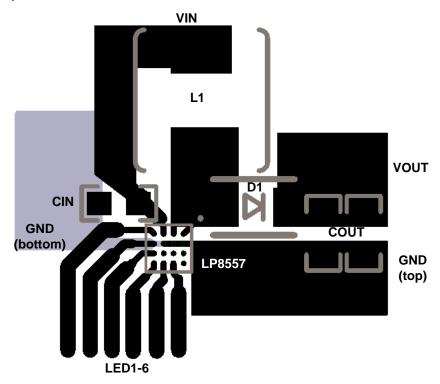

|   | 7.2 ESD Ratings                                                 | 11 | Layout                               |    |

|   | 7.3 Recommended Operating Conditions                            |    | 11.1 Layout Guidelines               |    |

|   | 7.4 Thermal Information                                         |    | 11.2 Layout Example                  |    |

|   | 7.5 Electrical Characteristics                                  | 12 | Device and Documentation Support     |    |

|   | 7.6 Boost Converter Electrical Characteristics                  |    | 12.1 Device Support                  |    |

|   | 7.7 LED Driver Electrical Characteristics (LED1 To LED6 Pins)   |    | 12.2 Related Links                   |    |

|   | 7.8 PWM Interface Characteristics (PWM Pin)                     |    | 12.3 Community Resources             |    |

|   | 7.9 Logic Interface Characteristics (1 WW 1 III)                |    | 12.4 Trademarks                      |    |

|   | (PWM, FSET/SDA, ISET/SCL Pins)                                  |    | 12.5 Electrostatic Discharge Caution |    |

|   | 7.10 I <sup>2</sup> C Serial Bus Timing Parameters (SDA, SCL) 7 |    | 12.6 Glossary                        |    |

|   | 7.11 Typical Characteristics                                    | 13 | Mechanical, Packaging, and Orderable |    |

| 8 | Detailed Description                                            | 13 | Information                          | 43 |

| • | 8.1 Overview                                                    |    |                                      |    |

|   | 0.1 0.000000000000000000000000000000000                         |    |                                      |    |

# 4 Revision History

| Cł | hanges from Revision A (June 2014) to Revision B                  | Page |

|----|-------------------------------------------------------------------|------|

| •  | moved storage temperature range to Abs Max table                  |      |

| •  | Changed Handling Ratings table to ESD Ratings table               | 4    |

| •  | Updated Thermal Information table                                 |      |

| •  | Changed word "safety" to "fault detection"                        | 11   |

| •  | Deleted "to 25% of the brightness range"                          | 16   |

| •  | Changed PGEN register table and descriptions                      | 28   |

| •  | Changed fixed typo "2.4.4 kHz" to "24.4 kHz"                      | 28   |

| •  | Added note to beginning of Application and Implementation section | 31   |

| •  | Added Community Resources section                                 | 43   |

# Changes from Original (December 2013) to Revision A

**Page**

Changed formatting to match new TI datasheet guidelines; added Device Information and Handling Ratings table,

Layout, and Device and Documentation Support sections; reformatted Detailed Description and Application and

Implementation sections, fix typographical errors.

Changed 6 LED strings to 5 LED Strings to correct typo.

# 5 Device Comparison Table

| ORDERABLE DEVICE | DEVICE OPTION                                | PACKAGE TOP<br>MARK | PACKAGE TYPE<br>(DRAWING) | PINS | PACKAGE QTY. |

|------------------|----------------------------------------------|---------------------|---------------------------|------|--------------|

| LP8557AYFQT      | "PWM Only" - Recommended for                 | D40                 |                           |      | 250          |

| LP8557AYFQR      | systems without an I <sup>2</sup> C master   | D40                 | DCDCA (VEO)               | 16   | 3000         |

| LP8557IAYFQT     | "PWM and I <sup>2</sup> C" - Recommended for | D44                 | DSBGA (YFQ)               | 10   | 250          |

| LP8557IAYFQR     | systems with an I <sup>2</sup> C master      |                     |                           |      | 3000         |

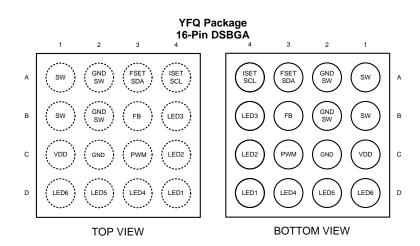

# 6 Pin Function and Configurations

# **Pin Functions**

| P        | IN     | T)(DE (1) | DECODURE                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO.    | TYPE (1)  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FB       | В3     | Α         | Boost feedback pin. The FB and OVP circuitry monitors the voltage on this pin.                                                                                                                                                                                                                                                                                                                                                                   |

| FSET/SDA | А3     | I/O       | Dual function pin. When $I^2C$ is not used (for example, BRTMODE = 00b), this pin can be used to set $f_{SW}$ and/or $f_{PWM}$ by connecting a resistor from this pin to a ground reference. When $I^2C$ is used (for example, BRTMODE = 01, 10 or 11), connect this pin to an SDA line of an $I^2C$ bus. The LP8557 "PWM Only" device option uses this pin as an FSET pin. LP8557I "PWM and $I^2C$ " device option uses this pin as an SDA pin. |

| GND      | C2     | G         | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ISET/SCL | A4     | I         | Dual function pin. When $I^2C$ is not used (for example, BRTMODE = 00b), this pin can be used to set the full-scale LED current by connecting a resistor from the pin to a ground reference. When $I^2C$ is used (for example, BRTMODE =01, 10, or 11), connect this pin to an SCL line of an $I^2C$ bus. The LP8557 "PWM Only" device option uses this pin as an ISET pin. LP8557I "PWM and $I^2C$ " device option uses this pin as an SCL pin. |

| LED1     | D4     | Α         | LED driver – current sink terminal. If unused, this pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

| LED2     | C4     | Α         | LED driver – current sink terminal. If unused, this pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

| LED3     | B4     | Α         | LED driver – current sink terminal. If unused, this pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

| LED4     | D3     | А         | LED driver – current sink terminal. If unused, this pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

| LED5     | D2     | А         | LED driver – current sink terminal. If unused, this pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

| LED6     | D1     | А         | LED driver – current sink terminal. If unused, this pin may be left floating.                                                                                                                                                                                                                                                                                                                                                                    |

| PWM      | C3     | ı         | PWM input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SW       | A1, B1 | Α         | A connection to the drain terminal of the integrated power MOSFET.                                                                                                                                                                                                                                                                                                                                                                               |

| SW_GND   | A2, B2 | G         | A connection to the source terminal of the integrated power MOSFET.                                                                                                                                                                                                                                                                                                                                                                              |

| VDD      | C1     | Р         | Device power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                         |

(1) A: Analog Pin, G: Ground Pin, P: Power Pin, I: Digital Input Pin, I/O: Digital Input/Output Pin

Copyright © 2013–2015, Texas Instruments Incorporated

# 7 Specifications

### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)(2)

|                   |                                            | MIN  | MAX | UNIT |

|-------------------|--------------------------------------------|------|-----|------|

| $V_{DD}$          | Voltage range on VDD pin                   | -0.3 | 6   | V    |

| $V_{IO}$          | Voltage range on digital IO pins           | -0.3 | 6   | V    |

| Vo                | Voltage range on SW, FB, LED1 to LED6 pins | -0.3 | 31  | V    |

| TJ                | Junction temperature                       | -30  | 125 | °C   |

| T <sub>sldr</sub> | Maximum lead temperature (soldering)       |      | 260 | °C   |

| T <sub>stg</sub>  | Storage temperature range                  | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 7.2 ESD Ratings

|                                            |                                                                     |                                                        | VALUE | UNIT |

|--------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|-------|------|

| V                                          | Floatrootatia diaaharaa                                             | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 | \/   |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500                                                   | V     |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted) (1)(2)

| 1 0 1                                |     |     |      |

|--------------------------------------|-----|-----|------|

|                                      | MIN | MAX | UNIT |

| $V_{DD}$                             | 2.7 | 5.5 | V    |

| V (SW, FB, LED1 to LED6)             | 0   | 28  | V    |

| Ambient temperature, T <sub>A</sub>  | -30 | 85  | °C   |

| Junction temperature, T <sub>J</sub> | -30 | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

#### 7.4 Thermal Information

|                      |                                              | LP8557/LP8557I |      |

|----------------------|----------------------------------------------|----------------|------|

|                      | THERMAL METRIC <sup>(1)(2)</sup>             | YFQ (DSBGA)    | UNIT |

|                      |                                              | 16 PINS        |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 75.7           | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 0.5            | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 16.2           | °C/W |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.2            | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 16.2           | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> All voltage values are with respect to the potential at the GND pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> All voltage values are with respect to the potential at the GND pin.

<sup>(2)</sup> Junction-to-ambient thermal resistance is highly application and board-layout dependent. In applications where high maximum power dissipation exists, special care must be paid to thermal dissipation issues in board design.

# 7.5 Electrical Characteristics

Unless otherwise specified: T<sub>A</sub> = 25°C, V<sub>DD</sub> = 3.8 V.

|                       | PARAMETER                              | TEST CONDITIONS               | MIN                       | TYP | MAX                     | UNIT |

|-----------------------|----------------------------------------|-------------------------------|---------------------------|-----|-------------------------|------|

| $V_{DD}$              | Input voltage range                    |                               | 2.7                       |     | 5.5                     | V    |

| $I_{DDQ}$             | Standby current                        |                               |                           |     | 1                       | μΑ   |

| I <sub>DD</sub>       | Operating current                      | No current going through LEDs |                           | 2.2 |                         | mA   |

| $f_{OSC}$             | Internal oscillator frequency accuracy |                               | -4%<br>-7% <sup>(1)</sup> |     | 4%<br>7% <sup>(1)</sup> |      |

| T <sub>TSD</sub>      | Thermal shutdown threshold (2)         |                               |                           | 150 |                         | °C   |

| T <sub>TSD_hyst</sub> | Thermal shutdown hysteresis (2)        |                               |                           | 20  |                         |      |

Limits apply over the full operating ambient temperature range –30°C ≤ T<sub>A</sub> ≤ 85°C.

# 7.6 Boost Converter Electrical Characteristics

Unless otherwise specified:  $T_A = 25$ °C,  $V_{DD} = 3.8 V^{(1)}$ .

|                        | PARAMETER                                | TEST CONDITIONS                                                               | MIN               | TYP                             | MAX               | UNIT |

|------------------------|------------------------------------------|-------------------------------------------------------------------------------|-------------------|---------------------------------|-------------------|------|

| R <sub>DS_ON</sub>     | Switch ON resistance                     | I <sub>SW</sub> = 0.5 A                                                       |                   | 0.2                             |                   | Ω    |

| V <sub>BOOST_MIN</sub> | Minimum output voltage                   |                                                                               | 6 <sup>(2)</sup>  | 7                               | 8 <sup>(2)</sup>  | V    |

| V <sub>BOOST_MAX</sub> | Maximum output voltage                   |                                                                               | 27 <sup>(2)</sup> | 28                              | 29 <sup>(2)</sup> | V    |

| I <sub>SW_CL</sub>     | SW pin current limit                     |                                                                               | 2.1               | 2.4                             | 2.5               | Α    |

| I <sub>LOAD_MAX</sub>  | Maximum continuous load current (3)      | I <sub>SW_LIM</sub> = 2.4 A<br>V <sub>IN</sub> = 3 V, V <sub>OUT</sub> = 24 V |                   | 160                             |                   | mA   |

| $f_{SW}$               | Switching frequency                      |                                                                               |                   | 500<br>1000                     |                   | kHz  |

| V <sub>OVP_TH</sub>    | Overvoltage protection voltage threshold |                                                                               | \                 | / <sub>BOOST_MAX</sub><br>+ 1.6 |                   | V    |

| $V_{UVLO\_TH}$         | UVLO threshold                           |                                                                               |                   | 2.5                             |                   |      |

| V <sub>UVLO_hyst</sub> | UVLO hysteresis                          |                                                                               |                   | 50                              |                   | mV   |

| t <sub>PULSE</sub>     | Switch pulse minimum width (3)           | No load                                                                       |                   | 80                              |                   | ns   |

| t <sub>STARTUP</sub>   | Boost start-up time (3)                  |                                                                               |                   | 1                               |                   | ms   |

<sup>(1)</sup> Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis.

# 7.7 LED Driver Electrical Characteristics (LED1 To LED6 Pins)

Unless otherwise specified:  $T_A = 25$ °C,  $V_{DD} = 3.8 V^{(1)}$ .

|                      | PARAMETER                              | TEST CONDITIONS                           | MIN                       | TYP         | MAX                     | UNIT |

|----------------------|----------------------------------------|-------------------------------------------|---------------------------|-------------|-------------------------|------|

| I <sub>LEAKAGE</sub> | Leakage current                        | Outputs LED1LED6, V <sub>OUT</sub> = 28 V |                           |             | 1                       | μΑ   |

| I <sub>LED_MAX</sub> | Maximum sink current LED16             |                                           |                           | 25          |                         | mA   |

| I <sub>LED_ACC</sub> | LED current accuracy <sup>(2)</sup>    | Output current set to 20 mA               | -3%<br>-4% <sup>(3)</sup> |             | 3%<br>4% <sup>(3)</sup> |      |

| I <sub>MATCH</sub>   | Channel to Channel Matching (2)        | Output current set to 20 mA               |                           | 0.5         |                         |      |

| $f_{LED}$            | LED switching frequency <sup>(4)</sup> | PFREQ = 000b<br>PFREQ = 111b              |                           | 4.9<br>39.1 |                         | kHz  |

| $V_{SAT}$            | Saturation voltage <sup>(5)</sup>      | Output current set to 20 mA               |                           | 200         |                         | mV   |

<sup>(1)</sup> Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis.

truments incorporated Submit Documenta

Product Folder Links: LP8557 LP85571

<sup>(2)</sup> Verified by design and not tested in production.

<sup>(2)</sup> Limits apply over the full operating ambient temperature range  $-30^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ .

<sup>(3)</sup> Verified by design and not tested in production.

<sup>(2)</sup> The LED current accuracy is defined as 100 × (İLED\_AVÉ – ILED\_Target) / ILED\_AVE. The channel-to-channel LED current matching is defined as (ILED\_MAX – ILED\_MIN) / ILED\_AVE.

<sup>(3)</sup> Limits apply over the full operating ambient temperature range –30°C ≤ T<sub>A</sub> ≤ 85°C.

<sup>(4)</sup> Verified by design and not tested in production.

<sup>(5)</sup> Saturation voltage is defined as the voltage when the LED current has dropped 10% from the value measured at 1 V.

# 7.8 PWM Interface Characteristics (PWM Pin)

See (1)

|                      | PARAMETER                                       | TEST CONDITIONS                     | MIN | TYP | MAX   | UNIT |

|----------------------|-------------------------------------------------|-------------------------------------|-----|-----|-------|------|

| $f_{PWM}$            | PWM frequency <sup>(2)</sup>                    |                                     | 75  |     | 25000 | Hz   |

| t <sub>MIN_ON</sub>  | Minimum pulse ON time (2)                       |                                     |     | 1   |       | μs   |

| t <sub>MIN_OFF</sub> | Minimum pulse OFF time (2)                      |                                     |     | 1   |       | μs   |

| t <sub>ON</sub>      | Turnon delay from standby to backlight on (2)   | PWM pin goes from low to switching. |     | 9   |       | ms   |

| t <sub>STBY</sub>    | Turnoff delay from backlight off to standby (2) | PWM pin goes from switching to low. |     | 52  |       | ms   |

|                      |                                                 | f <sub>IN</sub> < 2.4 kHz           |     | 12  |       |      |

|                      |                                                 | $f_{IN}$ < 4.8 kHz                  |     | 11  |       |      |

| $PWM_{RES}$          | PWM input resolution (2)                        | f <sub>IN</sub> < 9.6 kHz           |     | 10  |       | bits |

|                      |                                                 | f <sub>IN</sub> < 19.5 kHz          |     | 9   |       |      |

|                      |                                                 | f <sub>IN</sub> < 25 kHz            |     | 8   |       |      |

<sup>(1)</sup> Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis.

# 7.9 Logic Interface Characteristics (PWM, FSET/SDA, ISET/SCL Pins)

Limits apply over the full operating ambient temperature range  $-30^{\circ}\text{C} \le T_{\text{A}} \le 85^{\circ}\text{C}^{(1)}$ .

|                 | PARAMETER        | TEST CONDITIONS          | MIN  | TYP | MAX | UNIT |

|-----------------|------------------|--------------------------|------|-----|-----|------|

| $V_{IL}$        | Input low level  |                          |      |     | 0.4 | V    |

| $V_{IH}$        | Input high level |                          | 1.44 |     |     | V    |

| I               | Input current    |                          | -1   |     | 1   | μΑ   |

| V <sub>OL</sub> | Output low level | I <sub>SDA</sub> = 3 mA  |      |     | 0.5 | V    |

| Io              | Output leakage   | V <sub>SDA</sub> = 2.8 V |      |     | 1   | μΑ   |

(1) Minimum (Min) and Maximum (Max) limits are specified by design, test, or statistical analysis.

<sup>(2)</sup> Verified by design and not tested in production.

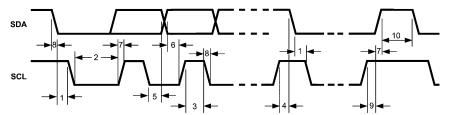

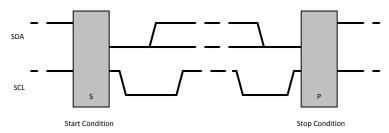

# 7.10 I<sup>2</sup>C Serial Bus Timing Parameters (SDA, SCL)

See<sup>(1)</sup> and Figure 1.

|                   | PARAMETER                                                                          | MIN                    | MAX | UNIT |

|-------------------|------------------------------------------------------------------------------------|------------------------|-----|------|

| $f_{SCL}$         | Clock Frequency                                                                    |                        | 400 | kHz  |

| 1                 | Hold Time (repeated) START Condition                                               | 0.6                    |     | μs   |

| 2                 | Clock Low Time                                                                     | 1.3                    |     | μs   |

| 3                 | Clock High Time                                                                    | 600                    |     | ns   |

| 4                 | Setup Time for a Repeated START Condition                                          | 600                    |     | ns   |

| 5                 | Data Hold Time                                                                     | 50                     |     | ns   |

| 6                 | Data Setup Time                                                                    | 100                    |     | ns   |

| 7                 | Rise Time of SDA and SCL                                                           | 20 + 0.1C <sub>b</sub> | 300 | ns   |

| 8                 | Fall Time of SDA and SCL                                                           | 15 + 0.1C <sub>b</sub> | 300 | ns   |

| 9                 | Set-up Time for STOP condition                                                     | 600                    |     | ns   |

| 10                | Bus Free Time between a STOP and a START Condition                                 | 1.3                    |     | μs   |

| C <sub>b</sub>    | Capacitive Load Parameter for Each Bus Line Load of 1 pF corresponds to 1 ns.      | 10                     | 200 | ns   |

| t <sub>WAIT</sub> | Wait time from V <sub>DD</sub> = 2.7 V to 1 <sup>st</sup> I <sup>2</sup> C command | 150                    |     | μs   |

(1) Verified by design and not tested in production.

Figure 1. I<sup>2</sup>C-Compatible Timing

# 7.11 Typical Characteristics

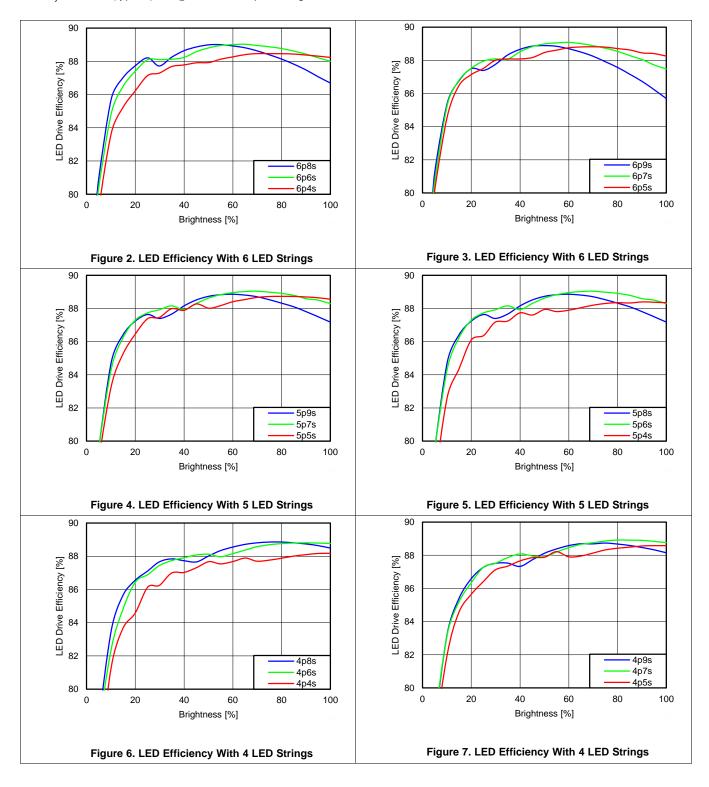

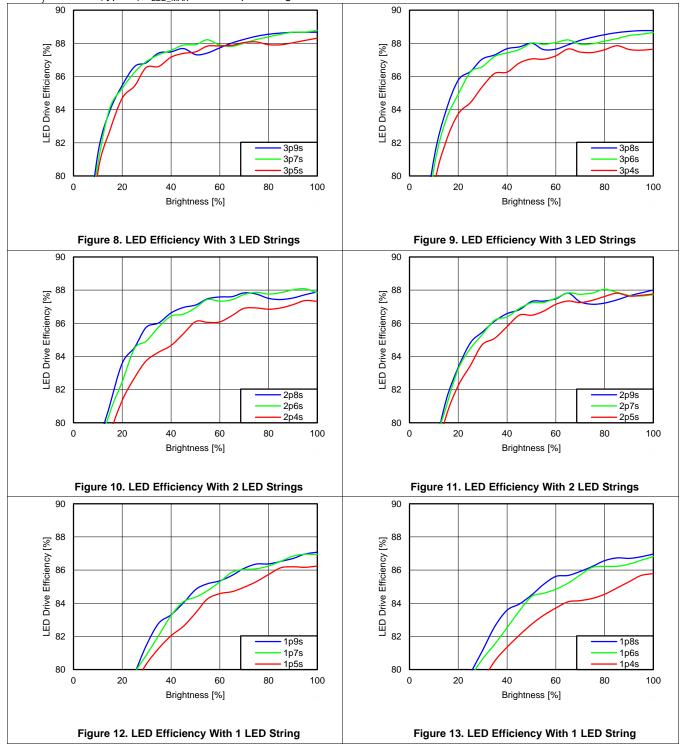

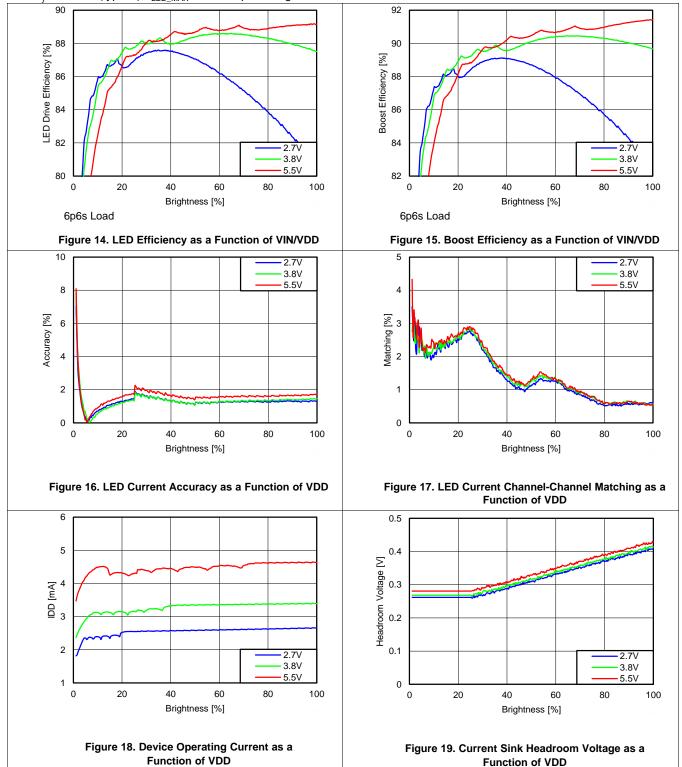

Unless otherwise specified:  $V_{IN} = V_{DD} = 3.8 \text{ V}$ , L = 10  $\mu$ H Cyntec PIME051E, D = Diodes PD3S130L-7,  $C_{OUT} = 2 \times 4.7 \mu$ F, LED  $V_f = 2.85 \text{ V}$  (typical),  $I_{LED\_MAX} = 25 \text{ mA}$  per string.

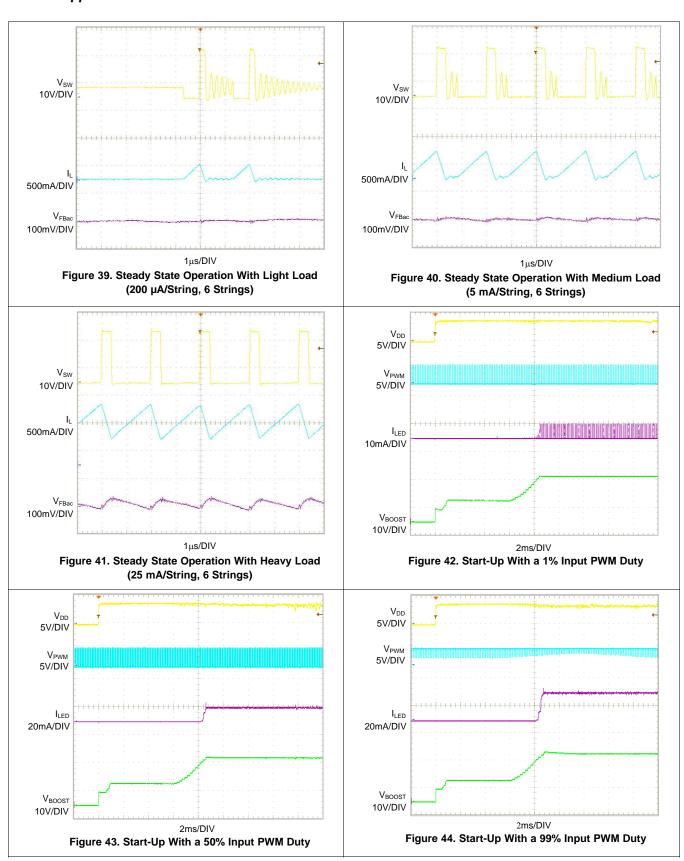

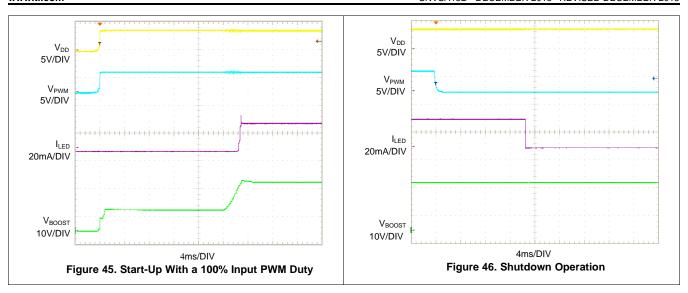

# **Typical Characteristics (continued)**

Unless otherwise specified:  $V_{IN} = V_{DD} = 3.8 \text{ V}$ , L = 10  $\mu$ H Cyntec PIME051E, D = Diodes PD3S130L-7,  $C_{OUT} = 2 \times 4.7 \mu$ F, LED  $V_f = 2.85 \text{ V}$  (typical),  $I_{LED\_MAX} = 25 \text{ mA}$  per string.

# **Typical Characteristics (continued)**

Unless otherwise specified:  $V_{IN} = V_{DD} = 3.8 \text{ V}$ , L = 10  $\mu$ H Cyntec PIME051E, D = Diodes PD3S130L-7,  $C_{OUT} = 2 \times 4.7 \mu$ F, LED  $V_f = 2.85 \text{ V}$  (typical),  $I_{LED\_MAX} = 25 \text{ mA}$  per string.

# 8 Detailed Description

#### 8.1 Overview

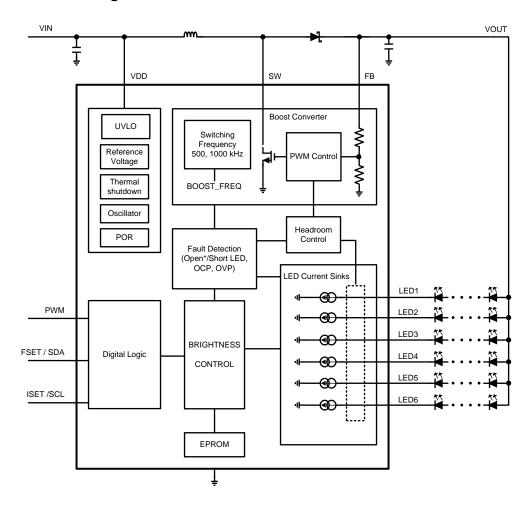

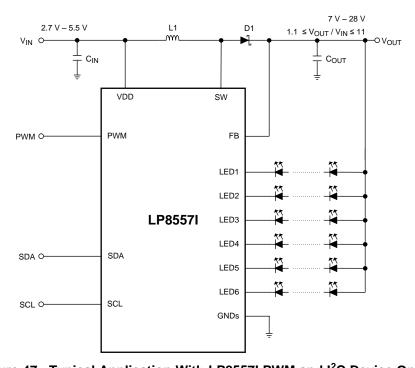

The LP8557 and LP8557I are high-efficiency LED drivers each featuring an integrated DC-DC inductive boost converter and six high-precision current sinks. LP8557 is intended for applications that exclusively use a pulse width modulated (PWM) signal for controlling the brightness while LP8557I is intended for applications that can utilize an I<sup>2</sup>C master as well.

The boost converter has adaptive output voltage control. This feature minimizes the power consumption by adjusting the voltage to the lowest sufficient level under all conditions.

The adaptive current sink headroom voltage control scales the headroom voltage with the LED current for optimal system efficiency.

The LED string auto-detect function enables use of the same device in systems with 1 to 6 LED strings for the maximum design flexibility.

Proprietary hybrid PWM plus current mode dimming enables additional system power savings. Phase shift PWM allows reduced audible noise and smaller boost output capacitors.

Flexible CABC support combines brightness level selections based on the PWM input and I<sup>2</sup>C commands.

The LP8557 and LP8557I feature a full set of features that ensure robust operation of the device and external components. The set consists of input undervoltage lockout, thermal shutdown, overcurrent protection, overvoltage protection, and LED open and short detection.

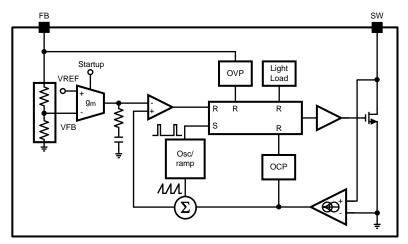

# 8.2 Functional Block Diagram

Copyright © 2013–2015, Texas Instruments Incorporated

#### 8.3 Feature Description

#### 8.3.1 Boost Converter Overview

#### 8.3.1.1 **Operation**

The boost DC-DC converter generates a 7-V to 28-V boost output voltage from a 2.7-V to 5.5-V boost input voltage.

The converter is a magnetic switching PWM mode DC-DC inductive boost converter with a current limit. It uses current programmed mode control, where the inductor current is measured and controlled with the feedback. During start-up, the soft-start function reduces the peak inductor current. Figure 20 shows the boost block diagram.

Figure 20. Boost Circuit Block Diagram

#### 8.3.1.2 Adaptive Boost Output Voltage Control

The boost converter operates in adaptive boost control mode. In this mode, the voltage at the LED pins is monitored by the control loop. It raises the boost voltage when the measured voltage of ANY of the LED strings falls below the voltage threshold of its corresponding LOW comparator. If the headrooms of ALL of the LED strings are above the voltage threshold of their corresponding MID comparator, then the boost voltage is lowered.

Figure 21. Adaptive Headroom Detail

#### 8.3.2 Brightness Control

The brightness can be controlled using an external PWM signal or the Brightness registers accessible via an  $I^2C$  interface or both. Which of these two input sources is selected is set by the BRTMODE bits. The LP8557 operates exclusively in BRTMODE = 00. While the LP8557I, by default, operates in BRTMODE = 11, it can operate in all BRTMODE settings by configuring the bits via the  $I^2C$  interface. How the brightness is controlled in each of the four possible modes is described in the following sections.

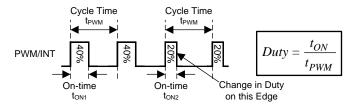

#### 8.3.2.1 PWM Input Duty Measurement

When using PWM input for brightness control the input PWM duty cycle is measured as described in following diagram and the brightness is controlled based on the result. When changing the brightness it must be noted that the measurement cycle is from rising edge to next rising edge and brightness change must be done accordingly (time from rising to rising edge is constant (=cycle time) and falling edge defines the brightness).

Figure 22. PWM Input Duty Cycle Measurement

#### 8.3.2.2 BRTMODE = 00b

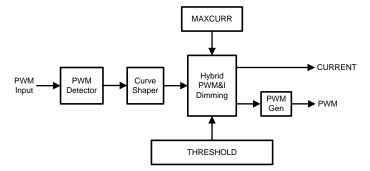

With BRTMODE = 00b, the LED output current is controlled by the PWM input duty cycle. The PWM detector block measures the duty cycle at the PWM pin and uses it to generate a PWM-based brightness code. Before the output is generated, the code goes through the curve shaper block. Then the code goes into the hybrid PWM & I Dimming block which determines the range of the PWM and Current control. The outcome of the hybrid PWM & I dimming block is current and/or up to 6 PWM output signals.

Figure 23. Brightness Data Path for BRTMODE = 00b

Submit Documentation Feedback

Product Folder Links: LP8557 LP85571

Figure 24. Typical Application Circuit for Devices Configured With BRTMODE = 00

#### 8.3.2.3 BRTMODE = 01b

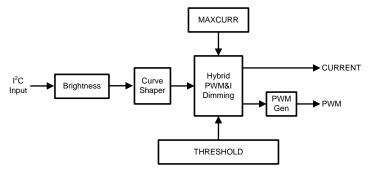

With BRTMODE = 01b, the LED output current is controlled by the BRTHI/BRTLO registers. Before the output is generated the BRTHI/BRTLO registers-based brightness code goes through the Curve Shaper block. Then the code goes into the hybrid PWM & I dimming block which determines the range of the PWM and current control. The outcome of the Hybrid PWM&I Dimming block is Current and/or up to 6 PWM output signals.

Figure 25. Brightness Data Path for BRTMODE = 01b

#### 8.3.2.4 BRTMODE = 10b

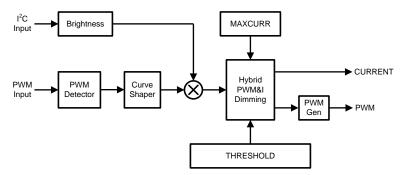

With BRTMODE = 10b, the LED output current is controlled by the PWM input duty cycle and the BRTHI/BRTLO registers. The PWM detector block measures the duty cycle at the PWM pin and uses it to generate PWM-based brightness code. Before the code is multiplied with the BRTHI/BRTLO registers-based brightness code, it goes through the curve shaper block. After the multiplication, the resulting code goes into the hybrid PWM & I dimming block which determines the range of the PWM and Current control. The outcome of the hybrid PWM & I dimming block is current or up to 6 PWM output signals.

Figure 26. Brightness Data Path for BRTMODE = 10b

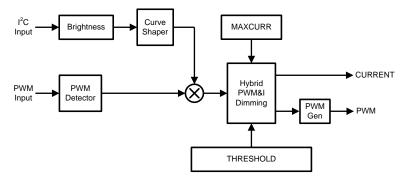

#### 8.3.2.5 BRTMODE = 11b

With BRTMODE = 11b, the LED output current is controlled by the PWM input duty cycle and the BRTHI/BRTLO registers. The PWM detector block measures the duty cycle at the PWM pin and uses it to generate PWM-based brightness code. In this mode, the BRTHI/BRTLO registers-based brightness code goes through the curve shaper block before it is multiplied with the PWM input duty cycle-based brightness code. After the multiplication, the resulting code goes into the hybrid PWM & I dimming block which determines the range of the PWM and Current control. The outcome of the hybrid PWM & I dimming block is current and/or up to 6 PWM output signals.

Figure 27. Brightness Data Path for BRTMODE = 11b

Figure 28. Typical Application Circuit for Devices Configured With BRTMODE = 01, 10, or 11

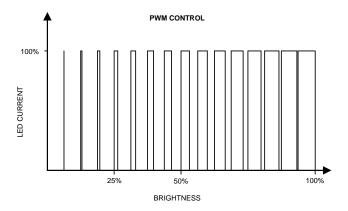

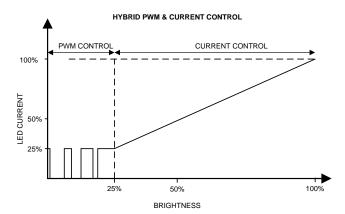

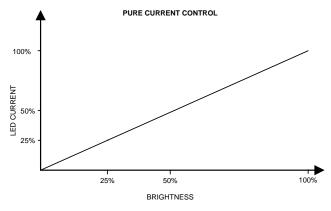

### 8.3.2.6 Hybrid PWM & I Dimming Control

Hybrid PWM & I dimming control combines PWM dimming and LED current-dimming control methods. With this dimming control, better optical efficiency is possible from the LEDs compared to pure PWM control while still achieving smooth and accurate control and low brightness levels. The switch point from current-to-PWM control can be set to get the optimal compromise between good matching of the LEDs brightness/white point at low brightness and good optical efficiency.

Figure 29. Dimming Methods

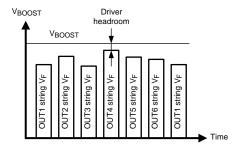

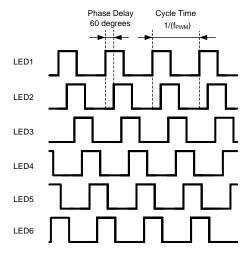

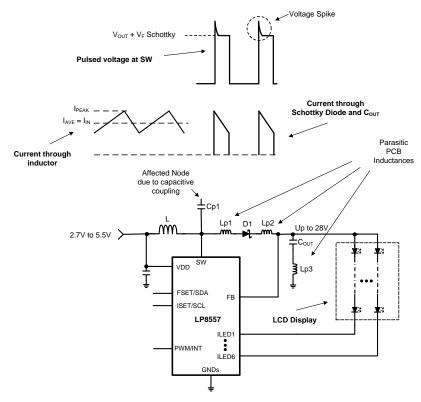

# 8.3.2.7 Phase Shift PWM Scheme

The phase shift PWM (PSPWM) scheme allows delay of the time when each LED current sink is active. When the LED current sinks are not activated simultaneously, the peak load current from the boost output is greatly decreased. This reduces the ripple seen on the boost output and allows smaller output capacitors to be used. Reduced ripple also reduces the output ceramic capacitor audible ringing. The PSPWM scheme also increases the load frequency seen on the boost output by up to six times, therefore transferring the possible audible noise to the frequencies outside the audible range.

The phase difference between each active driver is automatically determined as 360°/number of active drivers.

Figure 30. Phase Shift PWM Dimming Scheme Diagram

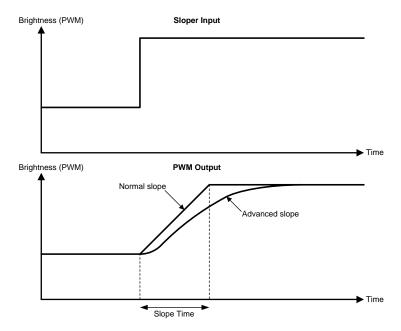

#### 8.3.3 Slope and Advanced Slope

The transition time between two brightness values can be programmed with the STEP bits from 0 to 200 ms. The same slope time is used for sloping up and down. With advanced slope the brightness changes can be made more pleasing to a human eye. It is implemented with a digital smoothing filter. The filter strength is set with SMOOTH bits.

Figure 31. Slope and Advanced Slope

# 8.3.4 LED String Count Auto Detection

The LP8557 and LP8557I can auto-detect the number of the LED strings attached. During the auto-detect routine, the devices automatically remove the unused current sink(s) and adjust the phasing of the remaining current sinks. The LED OPEN\* fault condition is not supported with auto-detect function enabled. On the LP8557I, the user may disable the function by setting CONFIG.AUTO bit to 0 via an I<sup>2</sup>C write.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

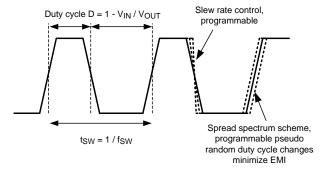

#### 8.3.5 EMI Reduction Schemes

LP8557I features two EMI reduction schemes. By default, the schemes are disabled; however, the schemes can be enabled by I<sup>2</sup>C writes to SSEN and SREN bits in COMMAND register. The schemes are unavailable on the LP8557.

The first scheme, programmable slew rate control, uses a combination of three drivers for boost switch. Enabling all three drivers allows boost switch on/off transition times to be the shortest. On the other hand, enabling just one driver allows boost switch on/off transition times to be the longest. The longer the transition times, the lower the switching noise on the SW terminal. It should also be noted that the shortest transition times bring the best efficiency as the switching losses are the lowest. This scheme can be enabled by setting SREN=1 with an I<sup>2</sup>C write.

The second EMI reduction scheme is the spread spectrum scheme. This scheme deliberately spreads the frequency content of the boost switching waveform, which inherently has a narrow bandwidth, makes the switching waveform's bandwidth wider and ultimately reduces its EMI spectral density. This scheme can be enabled by setting SSEN = 1 with an  $I^2C$  write.

Figure 32. EMI Reduction Schemes

# 8.3.6 Fault Detection

The LP8557 and LP8557I have fault detection for LED SHORT, UVLO, BST\_OVP, BST\_OCP, BST\_UV, and TSD. Additionally, the LP8557I can support LED OPEN\* fault. Faults are recorded in the STATUS register. Each time the STATUS register is read it is automatically cleared.

#### 8.3.6.1 LED Short Detection

Voltages at the individual current sinks are constantly monitored for the LED SHORT fault. This fault may occur when some LEDs in a string are electrically bypassed making that LED string shorter than the other LED strings. The reduced forward voltage causes the current sink attached to that string to have a higher headroom voltage than the other current sinks. When the headroom voltage is higher than the fault comparator threshold (configured with the 0V field in the LEDEN register), that current sink is disabled, and the PWM phasing is automatically adjusted. The fault comparator threshold is at 2 V, typical.

#### 8.3.6.2 LED OPEN\* Detection

When the auto-detect function is disabled, each current sink is also monitored for the LED OPEN\* condition. The condition is set when the headroom voltage on one or more current sinks is below the LOW comparator threshold, and the boost voltage is at the maximum. This fault condition may be caused by one or more OPEN LED strings or by one or more current sinks shorted to GND. The LP8557I immediately shuts down the backlight whenever an LED OPEN\* condition is detected on any enabled LED drivers. The backlight does not turn on again (regardless of the COMMAND.ON bit) until the STATUS register is read.

# 8.3.6.3 Undervoltage Detection

The device continuously monitors the voltage on the VDD pin. When the VDD voltage drops below 2.5 V the backlight is immediately shut down, and the UVLO bit is set in the STATUS register. The backlight automatically starts again when the voltage has increased above 2.5 V + 50 mV hysteresis. Hysteresis is implemented to avoid continuously triggering undervoltage.

Copyright © 2013–2015, Texas Instruments Incorporated

#### 8.3.6.4 Thermal Shutdown

If the internal temperature reaches 150°C, the deviceimmediately shuts down the backlight to protect it from damage. The TSD bit is also set in the STATUS register. The device re-activates the backlight again when the internal temperature drops below 130°C.

#### 8.3.6.5 Boost Overcurrent Protection

The device automatically limits boost current to 2.4 A . When the 2.4-A limit is reached the BST\_OCP bit is set in the STATUS register. It is normal for the device to trigger the boost current limit during the start-up or sudden brightness changes. The STATUS register can be cleared by reading the bit. If the bit is permanently set, it may indicate an issue in the application.

# 8.3.6.6 Boost Overvoltage Protection

The device automatically limits boost voltage to VBOOST\_MAX + 1.6 V. When the limit is reached the BST\_OVP bit is set in the STATUS register. It is normal for the device to trigger the boost OVP limit during the start-up or sudden brightness changes. The status register can be cleared by reading the bit. If the bit is permanently set, it may indicate an issue in the application.

#### 8.3.6.7 Boost Undervoltage Protection

The device can detect when the boost voltage is below VBOOST -2.5 V for longer than 6 ms. When the threshold is reached the BST\_UV bit is set in the STATUS register.

# 8.4 Device Functional Modes

#### 8.4.1 Shutdown Mode

The device is in shutdown mode when the VDD pin is low. Current consumption in this mode from VDD pin is  $< 1 \mu A$ .

#### 8.4.2 Active Mode

In active mode the backlight is enabled either with setting the ON register bit high (LP8557l) or by activating PWM input (LP8557). The power supplying the VDD pin must be present. Brightness is controlled with I<sup>2</sup>C writes to brightness registers or by changing PWM input duty cycle (operation without I<sup>2</sup>C control). Configuration registers are not accessible in Active mode to prevent damage to the device by accidental writes. Current consumption from VDD terminal in this mode is typically 2.2 mA when LEDs are not drawing any current.

# 8.5 Programming

# 8.5.1 I<sup>2</sup>C-Compatible Serial Bus Interface

#### 8.5.1.1 Interface Bus Overview

The I<sup>2</sup>C-compatible synchronous serial interface provides access to the programmable functions and registers on the device. This protocol uses a two-wire interface for bi-directional communications between the devices connected to the bus. The two interface lines are the serial data line (SDA), and the serial clock line (SCL). These lines must be connected to a positive supply, via a pull-up resistor and remain HIGH even when the bus is idle.

The default 7-bit I<sup>2</sup>C address for the LP8557I slave is 2Ch.

20

# **Programming (continued)**

## 8.5.1.2 Start and Stop Conditions

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session (see Figure 33). A START condition is defined as SDA transitioning from HIGH to LOW while SCL is HIGH. A STOP condition is defined as SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered busy after a START condition and free after a STOP condition. During data transmission the I<sup>2</sup>C master can generate repeated START conditions. A START and a repeated START condition are equivalent function-wise. The data on SDA must be stable during the HIGH period of the clock signal (SCL). In other words, the state of SDA can only be changed when SCL is LOW.

Figure 33. Start And Stop Conditions

After the START condition, the  $I^2C$  master sends the 7-bit address followed by an eighth read or write bit (R/W). R/W = 0 indicates a WRITE, and R/W = 1 indicates a READ. The second byte following the chip address selects the register address to which the data is written. The third byte contains the data for the selected register.

#### 8.5.1.3 Data Transactions

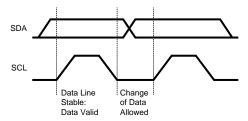

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol permits a single data line to transfer both command/control information and data using the synchronous serial clock.

Figure 34. Bit Transfer

Each data transaction is composed of a START Condition, a number of byte transfers (set by the software) and a STOP Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow. The following sections provide further details of this process.

#### 8.5.1.4 Acknowledge Cycle

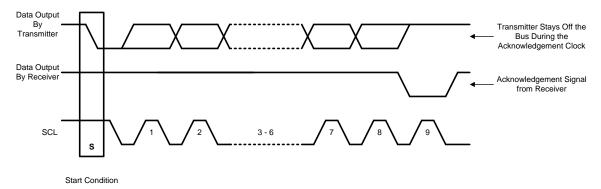

The Acknowledge Cycle consists of two signals: the acknowledge clock pulse the master sends with each byte transferred, and the acknowledge signal sent by the receiving device.

The master generates the acknowledge clock pulse on the ninth clock pulse of the byte transfer. The transmitter releases the SDA line (permits it to go high) to allow the receiver to send the acknowledge signal. The receiver must pull down the SDA line during the acknowledge clock pulse and ensure that SDA remains low during the high period of the clock pulse, thus signaling the correct reception of the last data byte and its readiness to receive the next byte.

# Programming (continued)

Figure 35. Bus Acknowledge Cycle

## 8.5.1.5 Acknowledge After Every Byte Rule

The master generates an acknowledge clock pulse after each byte transfer. The receiver sends an acknowledge signal after every byte received.

There is one exception to the acknowledge after every byte rule. When the master is the receiver, it must indicate to the transmitter an end of data by not-acknowledging (negative acknowledge) the last byte clocked out of the slave. This negative acknowledge still includes the acknowledge clock pulse (generated by the master), but the SDA line is not pulled down.

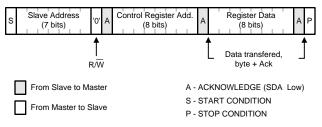

## 8.5.1.6 Control Register Write Cycle

- Master device generates start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master sends data byte to be written to the addressed register.

- Slave sends acknowledge signal.

- If master sends further data bytes the control register address is incremented by one after acknowledge signal.

- Write cycle ends when the master creates stop condition.

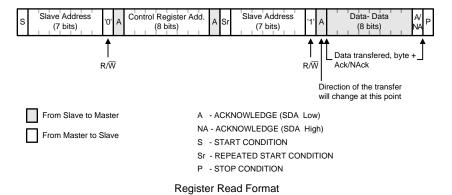

#### 8.5.1.7 Control Register Read Cycle

- Master device generates a start condition.

- Master device sends slave address (7 bits) and the data direction bit (r/w = 0).

- Slave device sends acknowledge signal if the slave address is correct.

- Master sends control register address (8 bits).

- Slave sends acknowledge signal.

- Master device generates repeated start condition.

- Master sends the slave address (7 bits) and the data direction bit (r/w = 1).

- Slave sends acknowledge signal if the slave address is correct.

- Slave sends data byte from addressed register.

- If the master device sends acknowledge signal, the control register address is incremented by one. Slave device sends data byte from addressed register.

- Read cycle ends when the master does not generate acknowledge signal after data byte and generates stop condition.

# **Programming (continued)**

Table 1. Data Read and Write Cycles

|            | ADDRESS MODE                                 |  |  |  |  |

|------------|----------------------------------------------|--|--|--|--|

| Data Read  | <start condition=""></start>                 |  |  |  |  |

|            | <slave address=""><r w="0">[Ack]</r></slave> |  |  |  |  |

|            | <register addr.="">[Ack]</register>          |  |  |  |  |

|            | <repeated condition="" start=""></repeated>  |  |  |  |  |

|            | <slave address=""><r w="1">[Ack]</r></slave> |  |  |  |  |

|            | [Register Data] <ack nack="" or=""></ack>    |  |  |  |  |

|            | additional reads from subsequent             |  |  |  |  |

|            | register address possible                    |  |  |  |  |

|            | <stop condition=""></stop>                   |  |  |  |  |

| Data Write | <start condition=""></start>                 |  |  |  |  |

|            | <slave address=""><r w="0">[Ack]</r></slave> |  |  |  |  |

|            | <register addr.="">[Ack]</register>          |  |  |  |  |

|            | <register data="">[Ack]</register>           |  |  |  |  |

|            | additional writes to subsequent              |  |  |  |  |

|            | register address possible                    |  |  |  |  |

|            | <stop condition=""></stop>                   |  |  |  |  |

Data from master; [] Data from slave

# 8.5.1.8 Register Read and Write Detail

Register Write Format

Figure 36. Register Write Format

Figure 37. Register Read Format

Copyright © 2013–2015, Texas Instruments Incorporated

# 8.6 Register Maps

| Register | Addr | D7        | D6        | D5     | D4       | D3      | D2      | D1      | D0    |

|----------|------|-----------|-----------|--------|----------|---------|---------|---------|-------|

| COMMAND  | 00h  | RESET     |           |        |          |         | SREN    | SSEN    | ON    |

| STATUS   | 01h  | LED_OPEN* | LED_SHORT |        | BST_UV   | BST_OVP | BST_OCP | TSD     | UVLO  |

| BRTLO    | 03h  |           | BRT[3:0]  |        |          |         |         |         |       |

| BRTHI    | 04h  |           |           |        | BRT[11:4 | ]       |         |         |       |

| CONFIG   | 10h  | PWMSB     |           |        |          |         | AUTO    | BRTN    | 1ODE  |

| CURRENT  | 11h  | ISET      |           |        |          |         |         | MAXCURR |       |

| PGEN     | 12h  | PFSET     |           |        |          |         |         | PFREQ   |       |

| BOOST    | 13h  | BCSET     | BISET     |        |          |         |         | BCOMP   | BFREQ |

| LEDEN    | 14h  |           |           | ENABLE |          |         |         |         |       |

| STEP     | 15h  | SMO       | ОТН       |        |          |         | STEP    |         |       |

The register map is useful for LP8557I users intending to re-configure the register reset values. If reconfiguration is necessary, it has to be done every time the power on VDD pin is recycled.

There is a restriction on register writes. The COMMAND, BRTLO, and BRTHI registers can be written at any time; however, the remaining registers only accept writes when the COMMAND.ON bit is low. All registers can be read at any time.

Many registers contain empty bit locations. These blank areas are reserved for future use. When writing to a register any empty fields must not be modified; when reading a register, these empty fields should be ignored.

# 8.6.1 Register Bit Descriptions

#### 8.6.1.1 **COMMAND**

Address: 0x00h

Reset: 0x00h (LP8557I)

| D7    | D6 | D5 | D4 | D3 | D2   | D1   | D0 |

|-------|----|----|----|----|------|------|----|

| RESET |    |    | _  |    | SREN | SSEN | ON |

| Bits | Field    | Туре | Default         | Description                                                                                             |

|------|----------|------|-----------------|---------------------------------------------------------------------------------------------------------|

| 7    | RESET    | R/W  | 0b              | Write 1 to reset the device. This bit is self-clearing and is always 0 when read.                       |

| 6:3  | reserved | R/O  | 0000b           |                                                                                                         |

| 2    | SREN     | R/W  | 0b              | Enable the boost slew rate control. <b>0 = Slew-rate control off (Default)</b> 1 = Slew-rate control on |

| 1    | SSEN     | R/W  | 0b              | Enable the spread-spectrum boost clocking.  0 = Spread-spectrum off (Default)  1 = Spread-spectrum on   |

| 0    | ON       | R/W  | See Description | Turn on the backlight.  0 = backlight off (Default)  1 = backlight on                                   |

The COMMAND.ON bit is used to turn on the backlight.

The COMMAND.SSEN and COMMAND.SREN bits may be updated at any time. It is not necessary for the backlight to be off when changing COMMAND.SSEN or COMMAND.SREN.

# 8.6.1.2 STATUS

Address: 0x01h

Reset: 0x00h

| D7        | D6        | D5 | D4     | D3      | D2      | D1  | D0   |

|-----------|-----------|----|--------|---------|---------|-----|------|

| LED_OPEN* | LED_SHORT | _  | BST_UV | BST_OVP | BST_OCP | TSD | UVLO |

| Bits | Field     | Туре | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-----------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | LED_OPEN* | R/O  | 0b      | An LED_OPEN* condition was detected on one or more strings. The condition is set when the headroom voltage on one or more current sinks is below the LOW comparator threshold, and the boost voltage is at the maximum. This fault condition may be caused by one or more OPEN LED strings or by one or more current sinks shorted to GND. Once set this bit stays set until the STATUS register is read. An LED_OPEN* condition turns off the backlight when CONFIG.AUTO is 0. When CONFIG.AUTO is 1, the condition is never set. |

| 6    | LED_SHORT | R/O  | 0b      | An LED SHORT condition was detected on one or more strings. The condition is set when the headroom voltage on one or more current sinks is above the FAULT comparator threshold and at least one driver has the headroom voltage in regulation (between LOW and MID comparator thresholds). This fault condition may be caused by one or more shorted LEDs on one or more (but not all) strings. Once set this bit stays set until the STATUS register is read.                                                                    |

| 5    | reserved  | R/O  | 0b      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4    | BST_UV    | R/O  | 0b      | A boost output undervoltage condition was detected. The boost voltage is 2.5 V (typical) or more below the target. Once set this bit stays set until the STATUS register is read.                                                                                                                                                                                                                                                                                                                                                  |

| 3    | BST_OVP   | R/O  | 0b      | A boost overvoltage protection condition was detected. The boost voltage is 1.6 V (typical) above the VMAX value. Once set this bit stays set until the STATUS register is read.                                                                                                                                                                                                                                                                                                                                                   |

| 2    | BST_OCP   | R/O  | 0b      | A boost overcurrent protection condition was detected. Once set this bit stays set until the STATUS register is read.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1    | TSD       | R/O  | 0b      | A thermal shutdown condition was detected. Once set, this bit stays set until the STATUS register is read. A thermal shutdown condition turns off the backlight.                                                                                                                                                                                                                                                                                                                                                                   |

| 0    | UVLO      | R/O  | 0b      | An input undervoltage lockout condition was detected. Once set, this bit stays set until the STATUS register is read. An undervoltage lockout condition turns off the backlight.                                                                                                                                                                                                                                                                                                                                                   |

# 8.6.1.3 BRTLO

Address: 0x03h Reset: 0x00h

| D7 | D6  | D5    | D4 | D3 | D2 | D1 | D0 |

|----|-----|-------|----|----|----|----|----|

|    | BRT | T3:01 |    |    |    | _  |    |

| Bits | Field    | Туре | Default | Description                                                                                                                                              |

|------|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4  | BRT[3:0] | R/W  | 0000b   | Least significant bits of the 12-bit wide brightness level. If controlling the brightness with 8-bit resolution, writing to this register is not needed. |

| 6:0  | reserved | R/O  | 0000b   | Reserved.                                                                                                                                                |

#### 8.6.1.4 BRTHI

Address: 0x04h Reset: 0x00h

| D7 | D6 | D5 | D4  | D3     | D2 | D1 | D0 |

|----|----|----|-----|--------|----|----|----|

|    |    |    | BRT | [44.4] |    |    |    |

| Bits | Field     | Туре | Default | Description                                                                                                                                                         |

|------|-----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0  | BRT[11:4] | R/W  |         | Most significant bits of the 12-bit wide brightness level. If controlling the brightness with the 8-bit resolution, writing to this register is all that is needed. |

The brightness level can be updated via one (8 bits) or two (16 bits) register writes. The internal brightness level is 12 bits wide and is only updated when the BRTHI register is written. If the BRTHI register is written without a previous write to the BRTLO register, then the lower order bits of the internal brightness is synthesized from the BRTHI register value.

| BRTLO      | BRTHI      | Brightness | Comments                     |

|------------|------------|------------|------------------------------|

| write 0x95 | write 0xFC | 0xFC9      | BRTLO[3:0] is ignored        |

| write 0x10 | write 0xDC | 0xDC1      | set to an exact 12-bit value |

| no write   | write 0x8C | 0x8C8      | synthesize low order bits    |

| no write   | write 0x0C | 0x0C0      | synthesize low order bits    |

| no write   | write 0x00 | 0x000      | 0% brightness                |

| no write   | write 0xFF | 0xFFF      | 100% brightness              |

#### 8.6.1.5 CONFIG

Address: 0x10h

Reset: 0x07h (LP8557I)

| D7    | D6 | D5 | D4 | D3 | D2   | D1    | D0       |

|-------|----|----|----|----|------|-------|----------|

| PWMSB |    |    | _  |    | AUTO | BRTMC | DDE[1:0] |

| Bits | Field    | Туре | Default | Description                                                                                                                                |

|------|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | PWMSB    | R/W  | 0b      | Enables PWM standby mode  0 = COMMAND.ON alone turns the backlight on/off (Default)  1 = turn off the backlight after 52 ms of PWM pin low |

| 6:3  | reserved | R/O  | 0000b   |                                                                                                                                            |

| 2    | AUTO     | R/W  | 1b      | Automatic LED string configuration0 = enable LED strings using just LEDEN.ENABLE 1 = disable all open LED strings (Default)                |

| 1:0  | BRTMODE  | R/W  | 11b     | Brightness mode 00 = PWM 01 = BRTHI/BRTLO registers 10 = PWM × unshaped BRTHI/BRTLO registers 11 = Unshaped PWM × BRTHI/BRTLO registers    |

The AUTO bit is set, and the LED string configuration is done automatically. The LP8557I allows users to disable the auto-detect function by setting AUTO bit to 0b.

# 8.6.1.6 **CURRENT**

Address: 0x11h

Reset: 0x07h (LP8557I)

| D7   | D6 | D5 | D4 | D3 | D2 | D1           | D0 |

|------|----|----|----|----|----|--------------|----|

| ISET |    |    | _  |    |    | MAXCURR[2:0] |    |

| Bits | Field    | Туре | Default | Description                                                                                                                                                                                  |

|------|----------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | ISET     | R/W  | 0b      | Set full-scale LED current via the ISET pin. <b>0 = Full-scale current is set with MAXCURR bits. (Default)</b> 1 = Full-scale current is set with an external, R <sub>ISET</sub> , resistor. |

| 6:3  | reserved | R/O  | 0000b   |                                                                                                                                                                                              |

| 2:0  | MAXCURR  | R/W  | 111b    | Full-scale current (100% brightness).  000 = 5 mA  001 = 10 mA  010 = 13 mA  011 = 15 mA  100 = 18 mA  101 = 20 mA  110 = 23 mA  111 = 25 mA (Default)                                       |

The ISET bit determines how the maximum LED current is set. On the LP8557I (ISET = 0), the maximum LED current is 25 mA. It may be re-configured via the  $I^2C$  interface by overriding MAXCURR bits. Note that reconfiguration must be done every time the power on VDD pin is recycled.

#### 8.6.1.7 PGEN

Address: 0x12h

Reset: 0x29h (LP8557I)

| D7    | D6 | D5 | D4        | D3 | D2 | D1         | D0 |

|-------|----|----|-----------|----|----|------------|----|

| PFSET | _  |    | THRESHOLD |    |    | PRFEQ[2:0] |    |

| Bits | Field     | Туре | Default | Description                                                                                                                                                                                                                                                                                                                                                                             |

|------|-----------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | PFSET     | R/W  | 0b      | Set PWM output frequency via the FSET pin. <b>0 = PWM output frequency is set with PRFEQ bits. (Default)</b> 1 = PWM output frequency is set with an external, R <sub>FSET</sub> , resistor.                                                                                                                                                                                            |

| 6:3  | reserved  | R/O  | 0101b   |                                                                                                                                                                                                                                                                                                                                                                                         |

| 5:3  | THRESHOLD | R/W  | EPROM   | Adaptive dimming threshold. PWM dimming is used below threshold, and current dimming is used above threshold.  000 = 100% current diming 001 = PWM below 1.5625% (6-bit PWM) 010 = PWM below 3.125% (7-bit PWM) 011 = PWM below 6.25% (8-bit PWM) 100 = PWM below 12.5% (9-bit PWM) 101 = PWM below 25% (10-bit PWM) 110 = PWM below 50% (11-bit PWM) 111 = 100 %PWM below (12-bit PWM) |

| 2:0  | PFREQ     | R/W  | 001b    | PWM output frequency<br>000 = 4.9 kHz<br><b>001 = 9.8 kHz (Default)</b><br>010 = 14.6 kHz<br>011 = 19.5 kHz<br>100 = 24.4 kHz<br>101 = 29.3 kHz<br>110 = 34.2 kHz<br>111 = 39.1 kHz                                                                                                                                                                                                     |

The PFSET bit distinguishes how the PWM dimming frequency is set. On the LP8557I (PFSET = 0), the PWM dimming frequency is 9.8 kHz by default. It may be re-configured via  $I^2C$  interface by overriding PFREQ bits. Note that re-configuration must be done every time the power on VDD pin is recycled.

#### 8.6.1.8 BOOST

Address: 0x13h

Reset: 0x02h (LP8557I)

| D7    | D6    | D5 | D4 | D3 | D2 | D1    | D0    |

|-------|-------|----|----|----|----|-------|-------|

| BFSET | BCSET |    | -  | _  |    | BCOMP | BFREQ |

| Bits | Field    | Туре | Default | Description                                                                                                                                                                                 |

|------|----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | BFSET    | R/W  | 0b      | Set boost frequency via the FSET pin. <b>0 = Boost frequency is set with BFREQ bits. (Default)</b> 1 = boost frequency is set with an external, R <sub>FSET</sub> , resistor.               |

| 6    | BCSET    | R/W  | 0b      | Set boost inductor size via ISET pin. <b>0 = boost inductor and compensation is set with BCOMP bit. (Default)</b> 1 = boost inductor is set with an external, R <sub>ISET</sub> , resistor. |

| 5:2  | reserved | R/O  | 0000b   |                                                                                                                                                                                             |

| 1    | BCOMP    | R/W  | 1b      | Boost compensation options.  0 = Boost compensation option 0  1 = Boost compensation option 1 (Default).                                                                                    |

| 0    | BFREQ    | R/W  | 0b      | Boost frequency.  0 = 500 kHz (Default)  1 = 1 MHz                                                                                                                                          |

The BFSET bit distinguishes how the boost switching frequency is set. If BFSET = 0, the boost switching frequency is set by the BFREQ bit. If BFSET = 1, the switching frequency is set with an external resistor. On the LP8557I (BFSET = 0), the boost switching frequency is 500 kHz by default. It may be re-configured via the  $I^2C$  interface by overriding the BFREQ bit. Please note the re-configuration must be done every time the power on the VDD pin is recycled.

The BCSET bit distinguishes how the boost inductor and compensation is set. If BCSET = 0, the boost inductor and compensation is set by the BCOMP bit. If BCSET = 1, the boost inductor and compensation is set with an external resistor. On the LP8557I (BCSET = 0), the boost compensation is set to option 1 by default. It may be re-configured via I<sup>2</sup>C interface by overriding BCOMP bit. Please note the re-configuration must be done every time the power on the VDD pin is recycled.

Copyright © 2013–2015, Texas Instruments Incorporated

#### 8.6.1.9 LEDEN

Address: 0x14h

Reset: 0xBFh (LP8557I)

| D7 | D6 | D5 | D4 | D3    | D2      | D1 | D0 |

|----|----|----|----|-------|---------|----|----|

|    | -  |    |    | ENABI | LE[6:1] |    |    |

| Bits | Field    | Туре | Default | Description                                                                                                                                                                                |

|------|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

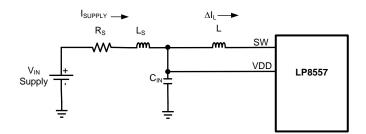

| 7:6  | reserved | R/W  | 10b     |                                                                                                                                                                                            |