### **LP3941A**

# **Cellular Phone Power Management Unit**

### **General Description**

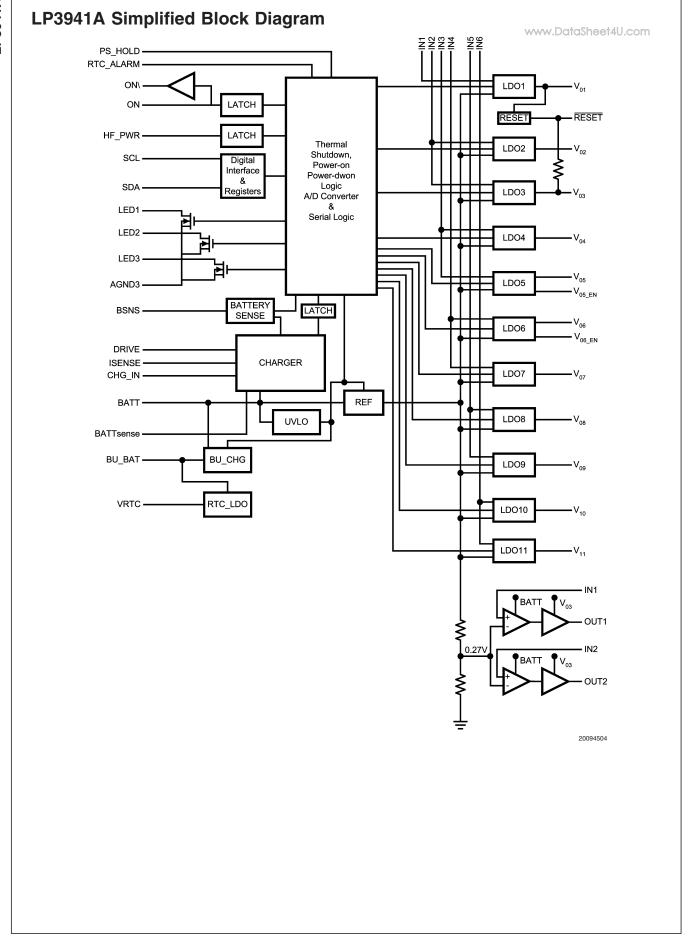

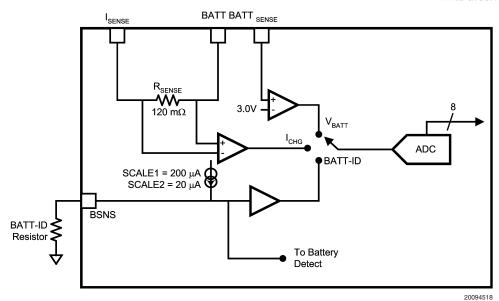

LP3941A is a complete power management IC designed for a cellular phone. It contains 11 low noise low dropout regulators, a linear charger for Li-lon battery, a backup battery charger, real time clock supply regulator, three open drain drivers, two comparators and high speed I<sup>2</sup>C compatible serial interface to program individual regulator output voltages as well as on/off control.

LP3941 is available in a LLP48 package.

#### **Features**

- 11 low dropout, low noise LDOs.

- Dedicated low current LDO for real time clock supply.

- Back-up battery charger

- A constant current / constant voltage battery charger controller with charge status indication via I<sup>2</sup>C compatible interface.

- Three open drain drivers to control a RGB LED

- I<sup>2</sup>C compatible serial interface for maximum flexibility

#### **Applications**

- GSM/EDGE cellular handsets

- Wideband CDMA cellular handsets

#### **Key Specifications**

- 3.0V to 5.5V Input Voltage Range

- 27 µV<sub>RMS</sub> Output noise

- 2% (typical) Output Voltage Accuracy

- 1% Charger Voltage Accuracy

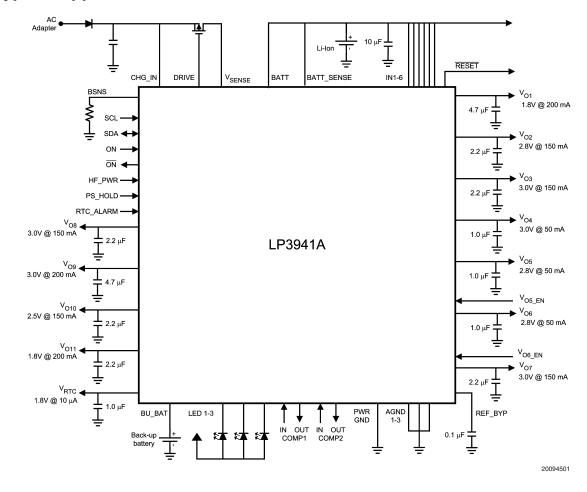

# **Typical Application**

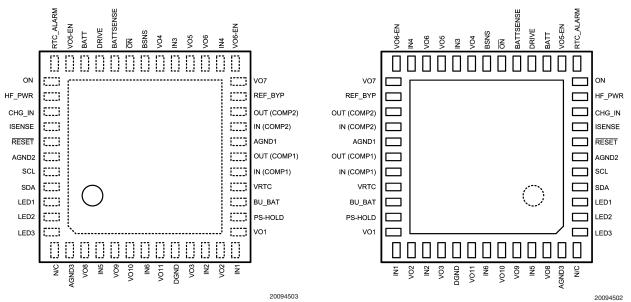

# **Connection Diagrams and Package Mark Information**

www.DataSheet4U.com

48-Pin Leadless Leadframe Package See NS Package Number LQA48B

Note: Circle marks pin 1 position. Pin 1 name is N/C.

**Top View**

**Bottom View**

20094517

**Note:** The actual physical placement of the package marking will vary from part to part. The package markings "UZYY" designate assembly and manufacturing information. "TT" is a NSC internal code for die traceability. Both will vary considerably. "3941LQA" identifies the device.

Package Mark—Top View

### **Ordering Information**

| Order Number | Package Marking | Supplied As               |

|--------------|-----------------|---------------------------|

| LP3941LQ-A   | LP3941LQA       | 250 units, Tape-and-Reel  |

| LP3941LQX-A  | LP3941LQA       | 2500 units, Tape-and-Reel |

Note: \*See LP3941A register table and LDO programming table for information on the default voltages for LP3941A.

| Pin # | Name                  | I/O | Туре | Description www.DataSheet                                                                                                                                                                                                                                                                                                                                                           |

|-------|-----------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | N/C                   | -   | -    | Not used. Connect to ground.                                                                                                                                                                                                                                                                                                                                                        |

| 2     | AGND3                 | G   | G    | Analog ground pin.                                                                                                                                                                                                                                                                                                                                                                  |

| 3     | V <sub>O8</sub>       | 0   | А    | LDO 8 Output                                                                                                                                                                                                                                                                                                                                                                        |

| 4     | IN5                   | I   | Р    | Input power terminal to LDO's. Must be connected to IN1–4 and IN6.                                                                                                                                                                                                                                                                                                                  |

| 5     | V <sub>O9</sub>       | 0   | А    | LDO 9 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 6     | V <sub>O10</sub>      | 0   | А    | LDO 10 output.                                                                                                                                                                                                                                                                                                                                                                      |

| 7     | IN6                   | ı   | Р    | Input power terminal to LDO's. Must be connected to IN1–5.                                                                                                                                                                                                                                                                                                                          |

| 8     | V <sub>O11</sub>      | 0   | А    | LDO 11 output.                                                                                                                                                                                                                                                                                                                                                                      |

| 9     | DGND                  | G   | G    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                         |

| 10    | V <sub>O3</sub>       | 0   | А    | LDO 3 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 11    | IN2                   | I   | Р    | Input power terminal to LDO's. Must be connected to IN1 and IN3-6.                                                                                                                                                                                                                                                                                                                  |

| 12    | V <sub>O2</sub>       | 0   | Α    | LDO 2 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 13    | IN1                   | I   | Р    | Input power terminal to LDO's. Must be connected to IN2–6.                                                                                                                                                                                                                                                                                                                          |

| 14    | V <sub>O1</sub>       | 0   | А    | LDO 1 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 15    | PS-HOLD               | I   | D    | Active low off key initiated by the micro controller.                                                                                                                                                                                                                                                                                                                               |

| 16    | BU_BAT                | I   | А    | Back-up battery connection.                                                                                                                                                                                                                                                                                                                                                         |

| 17    | VRTC                  | 0   | А    | RTC_LDO output.                                                                                                                                                                                                                                                                                                                                                                     |

| 18    | IN (COMP1)            | I   | А    | Non-inverting inout of the comparator 1.                                                                                                                                                                                                                                                                                                                                            |

| 19    | OUT (COMP1)           | 0   | А    | Output of the comparator 1.                                                                                                                                                                                                                                                                                                                                                         |

| 20    | AGND1                 | G   | G    | Analog ground pin.                                                                                                                                                                                                                                                                                                                                                                  |

| 21    | IN (COMP2)            | I   | А    | Non-inverting input of the comparator 2.                                                                                                                                                                                                                                                                                                                                            |

| 22    | OUT (COMP2)           | 0   | А    | Output of the comparator 2.                                                                                                                                                                                                                                                                                                                                                         |

| 23    | REF-BYP               | I   | А    | Reference bypass capacitor.                                                                                                                                                                                                                                                                                                                                                         |

| 24    | V <sub>O7</sub>       | 0   | А    | LDO 7 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 25    | V <sub>O6</sub> -EN   | I   | D    | LDO 6 on/off pin. Internal pull-down resistor of 1 M $\Omega$ .                                                                                                                                                                                                                                                                                                                     |

| 26    | IN4                   | I   | Р    | Input power terminal to LDO's. Must be connected to IN1-3 and IN5-6.                                                                                                                                                                                                                                                                                                                |

| 27    | V <sub>O6</sub>       | 0   | Α    | LDO 6 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 28    | V <sub>O5</sub>       | 0   | А    | LDO 5 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 29    | IN3                   | I   | Р    | Input power terminal to LDO's. Must be connected to IN1-2 and IN4-6.                                                                                                                                                                                                                                                                                                                |

| 30    | V <sub>O4</sub>       | 0   | Α    | LDO 4 output.                                                                                                                                                                                                                                                                                                                                                                       |

| 31    | BSNS                  | I   | Α    | Main battery ID resistor connection.                                                                                                                                                                                                                                                                                                                                                |

| 32    | ŌN                    | 0   | OD   | Inverted open drain output signal of the ON input. Pulled low when ON is pulled high and open drain when ON is pulled low. There is no significant delay between the ON signal going high and $\overline{\text{ON}}$ pin going low. The delay between ON signal going low and $\overline{\text{ON}}$ pin is determined by the pull up currer and capacitance connected to this pin. |

| 33    | BATT <sub>SENSE</sub> | I   | A    | Battery voltage sense pin. Should be connected as close to the battery's + terminal as possible.                                                                                                                                                                                                                                                                                    |

| 34    | Drive                 | 0   | Α    | Gate drive to the external MOSFET.                                                                                                                                                                                                                                                                                                                                                  |

| 35    | BATT                  | 0   | Α    | Battery supply input terminal. Must have 10 µF ceramic capacitor to GND.                                                                                                                                                                                                                                                                                                            |

| 36    | V <sub>O5</sub> -EN   | I   | D    | LDO 5 on/off pin. Internal pull down resistor of 1 M $\Omega$ .                                                                                                                                                                                                                                                                                                                     |

| 37    | RTC_ALARM             | I   | D    | RTC_ALARM input.                                                                                                                                                                                                                                                                                                                                                                    |

| 38    | ON                    | I   | D    | Active high power On/Off key. This pin is pulled to GND by an internal 200 $\mbox{k}\Omega$ resistor.                                                                                                                                                                                                                                                                               |

| 39    | HF_PWR                | I   | D    | Active high Hands Free connection signal. This pin has an internal 200 $\mbox{k}\Omega$ pull down resistor.                                                                                                                                                                                                                                                                         |

| 40    | CHG_IN                | I   | Р    | Charger input from a current limited power source. Must have a 1 µF cerami capacitor to GND.                                                                                                                                                                                                                                                                                        |

| 41    | I <sub>SENSE</sub>    | 0   | Α    | Charge current sense resistor.                                                                                                                                                                                                                                                                                                                                                      |

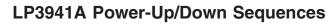

| 42    | RESET                 | 0   | OD   | Reset output. Active low. (See Power Up Timing Diagram.)                                                                                                                                                                                                                                                                                                                            |

#### Pin Description (Continued) Pin # Name I/O Туре Description AGND2 43 G G Analog ground pin. 44 SCL D Serial interface clock input. 45 SDA I/O D Serial interface data input/output. 46 LED1 0 OD LED driver output pin. 47 LED2 0 OD LED driver output pin. 48 LED3 0 OD LED driver output pin.

A: Analog Pin D: Digital Pin G: Ground Pin P: Power Pin I: Input Pin I/O: Input/Output Pin O: Output Pin OD: Open Drain Pin

#### Absolute Maximum Ratings (Notes 1,

2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

CHG-IN -0.3V to +12V

IN1-6, BATT, SDA, SCL, ON, HF-PWR, PS-HOLD, SYS, COMP1\_IN, COMP2\_IN, CHG\_IN, BSNS, VO5-EN,

V<sub>O6</sub>-EN, LED1-3,

RTC\_ALARM, BU\_BAT, V<sub>RTC</sub>,

-0.3V to +6VRESET, BATT<sub>SENSE</sub>.

REFBYP, ON, PS-HOLD,

COMP1 OUT, COMP2 OUT

to GND -0.3V to  $+V_{BAT} + 0.3V$ V<sub>O1</sub> to GND -0.3V to  $+V_{IN1} + 0.3V$

$V_{O2}$ ,  $V_{O3}$  to GND -0.3V to  $+V_{IN2} + 0.3V$  $V_{O4}$ ,  $V_{O5}$  to GND -0.3V to  $+V_{IN3} + 0.3V$  $V_{O6}$ ,  $V_{O7}$  to GND -0.3V to  $+V_{IN4} + 0.3V$

VO8, VO9 to GND -0.3V to  $+V_{IN5} + 0.3V$

$V_{O10}$ ,  $V_{O11}$  to GND -0.3V to  $+V_{IN6} + 0.3V$ GND to GND SLUG

Maximum Continuous Power Dissipation

www.DataShee (P<sub>D MAX</sub>) (Note 3) Junction Temperature (T<sub>J-MAX</sub>) 150°C Storage Temperature Range -65°C to +150°C

Maximum Lead Temperature

(Soldering) (Note 4)

ESD Ratings (Note 5)

All Pins 2 kV HBM 200V MM

#### Operating Ratings (Notes 1, 2)

3.0V to 6.0V  $V_{IN}$  $0V \text{ to } (V_{IN} + 0.3V)$  $V_{EN}$ Junction Temperature (T<sub>1</sub>) Range -40°C to +125°C

Ambient Temperature (T<sub>A</sub>) Range

(Note 6) -40°C to +85°C

#### Thermal Properties (Note 7)

Junction-to-Ambient Thermal

26°C/W Resistance  $(\theta_{JA})$

#### **Electrical Characteristics**

Unless otherwise noted,  $V_{IN}$  = 2.5V to 5.5V,  $C_{IN}$  (IN1-6) = 4.7  $\mu$ F,  $C_{OUT}$  ( $V_{O1}$  and  $V_{O9}$ ) = 4.7  $\mu$ F,  $C_{OUT}$  ( $V_{O2}$ ,  $V_{O3}$ ,  $V_{O7}$ ,  $V_{O8}$ ,  $V_{O9}$ ) = 4.7  $\mu$ F,  $V_{O9}$ ,  $V_{O9}$  $V_{O10}$  and  $V_{O11}$ ) = 2.2  $\mu$ F,  $C_{OUT}$  ( $V_{O4}$  to  $V_{O6}$ ) = 1  $\mu$ F,  $C_{OUT}$  ( $V_{RTC}$ ) = 1  $\mu$ F ceramic,  $C_{BYP}$  = 0.1  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9, 10)

| Symbol              | Parameter                                | Condition                                                                                                                                                             | Min  | Тур       | Max  | Units |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|------|-------|

| I <sub>Q</sub>      | Shutdown Supply Current                  | $V_{\rm BATT}$ = 2.1V, UVLO on, internal logic generator on, $V_{\rm RTC}$ off, all other circuits off.                                                               |      | 14        |      | μА    |

|                     | No Load Supply Current, LDO 1 & 3 & 5 on | $V_{\rm BATT}$ = 3.6V, LDOs $V_{\rm O1}$ , $V_{\rm O3}$ and $V_{\rm O5}$ on, back-up battery charger and $V_{\rm RTC}$ on, charger disconnected, comparator 1 & 2 on. |      | 310       |      | μА    |

|                     | No Load Supply Current                   | V <sub>BATT</sub> = 3.6V, All LDOs on, charger disconnected.                                                                                                          |      | 500       |      | μΑ    |

| BATTERY             | UNDER VOLTAGE LOCKOUT                    |                                                                                                                                                                       |      | •         |      | •     |

| V <sub>UVLO-R</sub> | Under Voltage Lock-Out                   | V <sub>BATT</sub> Rising                                                                                                                                              | 2.91 | 3.1       | 3.32 | V     |

| V <sub>UVLO-F</sub> | Under Voltage Lock-Out                   | V <sub>BATT</sub> Falling                                                                                                                                             | 2.15 | 2.49      | 2.85 | V     |

| V <sub>TH-POR</sub> | Power-On Reset Threshold                 | V <sub>BATT</sub> Falling Edge                                                                                                                                        | 1    | 1.7       | 2.3  | V     |

| THERMAL             | SHUTDOWN                                 |                                                                                                                                                                       |      |           |      |       |

|                     | Threshold<br>Hysteresis                  |                                                                                                                                                                       |      | 160<br>10 |      | °C    |

| OUTPUT (            | CAPACITORS                               |                                                                                                                                                                       |      | '         |      | •     |

| C <sub>OUT</sub>    | Capacitance                              |                                                                                                                                                                       | 1    |           | 20   | μF    |

|                     | ESR                                      |                                                                                                                                                                       | 5    |           | 500  | mΩ    |

| LOGIC AN            | ID CONTROL INPUTS                        |                                                                                                                                                                       |      |           |      |       |

| V <sub>IL</sub>     | Input Low Level                          | PS-HOLD, ON, BSNS, HF-PWR, RTC_ALARM, SDA, SCL, $V_{O5}$ -EN, $V_{O6}$ -EN. $2.5V \le V_{BATT} \le 5.5V$                                                              |      |           | 0.4  | V     |

#### **Electrical Characteristics** (Continued)

Unless otherwise noted,  $V_{IN} = 2.5V$  to 5.5V,  $C_{IN}$  (IN1-6) = 4.7  $\mu$ F,  $C_{OUT}$  ( $V_{O1}$  and  $V_{O9}$ ) = 4.7  $\mu$ F,  $C_{OUT}$  ( $V_{O2}$ ,  $V_{O3}$ ,  $V_{O3}$ ,  $V_{O7}$ ,  $V_{O8}$ ,  $V_{O10}$  and  $V_{O11}$ ) = 2.2  $\mu$ F,  $C_{OUT}$  ( $V_{O4}$  to  $V_{O6}$ ) = 1  $\mu$ F,  $C_{OUT}$  ( $V_{RTC}$ ) = 1  $\mu$ F ceramic,  $C_{BYP}$  = 0.1  $\mu$ F. Typical values and limits appearing in normal type apply for  $T_J$  = 25°C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9, 10)

| Symbol               | Parameter                                                                          | Condition                                                                                                | Min | Тур  | Max | Units |

|----------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| LOGIC AN             | D CONTROL INPUTS                                                                   |                                                                                                          |     |      |     | •     |

| V <sub>IH</sub>      | Input High Level                                                                   | PS-HOLD, ON, BSNS, HF-PWR, RTC_ALARM, SDA, SCL, $V_{O5}$ -EN, $V_{O6}$ -EN. $2.5V \le V_{BATT} \le 5.5V$ | 2.0 |      |     | V     |

| I <sub>IL</sub>      | Logic Input Current                                                                | SDA, SCL<br>0V ≤ V <sub>IN</sub> ≤ 5.5V                                                                  | -5  |      | +5  | μА    |

|                      | PS-HOLD Input Current                                                              | $0V \le V_{IN} \le V_{BATT}$                                                                             | -5  |      | +5  | μA    |

| $R_{IN}$             | ON, HF_PWR Pull-Down Resistance to GND                                             |                                                                                                          |     | 200  |     | kΩ    |

|                      | V <sub>O5</sub> -EN, V <sub>O6</sub> -EN, RTC_ALARM<br>Pull Down Resistance to GND |                                                                                                          |     | 1700 |     | kΩ    |

| LOGIC AN             | D CONTROL OUTPUTS                                                                  |                                                                                                          |     |      |     |       |

| V <sub>OL</sub>      | ON Output Low Level                                                                | I <sub>SINK</sub> = 1 mA                                                                                 |     |      | 0.4 | V     |

| I <sub>LEAKAGE</sub> | ON Open Drain Leakage                                                              | $\overline{V_{ON}} = 4.2V$                                                                               |     |      | 5   | μA    |

| I <sub>O-MAX</sub>   | ON, RESET, OUT (COMP1), OUT (COMP2) Output Maximum Sink/Source Current             |                                                                                                          |     |      | 5   | mA    |

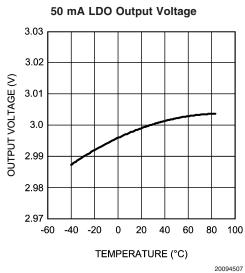

### **V<sub>O1</sub> LDO Electrical Characteristics**

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +85°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                              | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | $1 \text{ mA} \le I_{OUT} \le 200 \text{ mA}, V_{OUT} = 2.2V$<br>$3.0V \le V_{BATT} = V_{IN} \le 5.5V$ | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage Range      | 0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 200 mA<br>Programming Resolution = 100 mV                     | 1.5 | 1.8  | 3.0 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                           |     |      | 200 | mA                |

|                                   | Output Current Limit                   | $V_{OUT} = 0V$                                                                                         |     | 780  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 100 mA                                                                              |     | 70   | 254 | mV                |

| ΔV <sub>OUT</sub>                 | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 100 \text{ mA}$ |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 200 \text{ mA}$                                           |     | 10   |     |                   |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 4.7 $\mu$ F                                       |     | 27   |     | μV <sub>RMS</sub> |

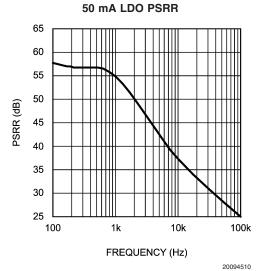

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 4.7 μF                                                                  |     | 60   |     | dB                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 1 mA ≤ I <sub>OUT</sub> ≤ 200 mA                                                                       | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                        | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown ON-signal  | $C_{OUT} = 4.7 \mu F$ , $I_{OUT} = 200 \text{ mA}$ (Note 10)                                           | 80  | 120  | 180 | μs                |

Note: This LDO will be ON after start up by default.

Note:  $(V_{OUT} + 0.25V, 3.0V)_{MAX}$  means greater of the two. That is 3.0V if  $V_{OUT} < 2.75V$ .

Note: The PMU can switch off if battery voltage is below 3.0V due to under voltage lockout designed to protect the battery from excessive discharge at low voltages.

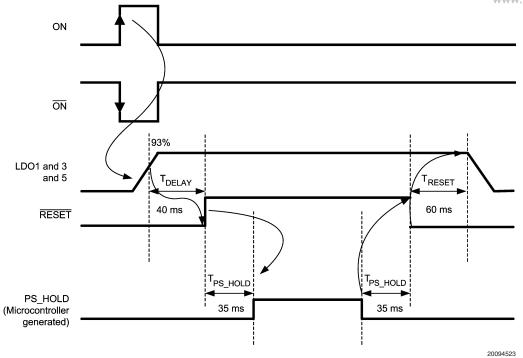

Note: The start-up time (t<sub>START-UP</sub>) is defined as the time between the rising edge of ON-, HF\_PWR-, RTC ALARM- or CHG\_IN- pins going high and activating the power-up sequence of the LP3941A.

$V_{O2}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$  C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125 °C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 200 mA, V <sub>OUT</sub> = 2.2V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | 0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 200 mA<br>Programming Resolution = 100 mV                                                 | 1.5 | 2.8  | 3.0 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                       |     |      | 150 | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                              |     | 540  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 75 mA                                                                                                           |     | 30   | 174 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 75 \text{ mA}$                              |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 150 \text{ mA}$                                                                       |     | 12   | 41  | l                 |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 2.2 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 2.2 μF                                                                                              |     | 57   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                          |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 mA ≤ I <sub>OUT</sub> ≤ 150 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 2.2 \mu F$ , $I_{OUT} = 150 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

$V_{O3}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 150 mA, V <sub>OUT</sub> = 2.7V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | $0$ μA $\leq$ $I_{OUT} \leq$ 150 mA<br>Programming Resolution = 100 mV                                                             | 2.5 | 3.0  | 3.2 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $egin{aligned} \left(V_{OUT} + 0.25V, \ 3.0V ight)_{MAX} \leq V_{BATT} \ V_{BATT} = V_{IN} \leq 5.5V \end{aligned}$                |     |      | 150 | mA                |

|                                   | Output Current Limit                   | $V_{OUT} = 0V$                                                                                                                     |     | 520  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 75 mA                                                                                                           |     | 30   | 156 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 75 \text{ mA}$                              |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V$ , 1 mA $\leq I_{OUT} \leq 150$ mA                                                                                  |     | 12   | 41  |                   |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 2.2 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 2.2 μF                                                                                              |     | 56   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 500 μA                                                                                                          |     | 30   |     | μA                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 mA ≤ I <sub>OUT</sub> ≤ 150 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 2.2 \mu F$ , $I_{OUT} = 150 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

Note: This LDO will be ON after start-up by default. It can be disabled via the register file.

$V_{O4}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$  C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                         | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 50 mA, V <sub>OUT</sub> = 2.2V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | $0 \ \mu A \le I_{OUT} \le 50 \ mA$<br>Programming Resolution = 100 mV                                                            | 1.5 | 3.0  | 3.0 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                      |     |      | 50  | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                             |     | 140  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 25 mA                                                                                                          |     | 7    | 90  | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 25 \text{ mA}$                             |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 50 \text{ mA}$                                                                       |     | 4    | 31  |                   |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 1.0 $\mu$ F                                                                  |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 1.0 μF                                                                                             |     | 56   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                         |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 μA ≤ I <sub>OUT</sub> ≤ 50 mA                                                                                                   | 1   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                   | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 1.0 \mu F$ , $I_{OUT} = 50 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

# **V<sub>O5</sub> LDO Electrical Characteristics**

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125 $^{\circ}C$ . (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                         | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 50 mA, V <sub>OUT</sub> = 2.2V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | 0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 50 mA<br>Programming Resolution = 100 mV                                                 | 2.5 | 2.8  | 3.2 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                      |     |      | 50  | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                             |     | 160  |     | <u> </u>          |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 25 mA                                                                                                          |     | 7    | 90  | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 25 \text{ mA}$                             |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 50 \text{ mA}$                                                                       |     | 4    | 31  |                   |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 1.0 $\mu$ F                                                                  |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 1.0 μF                                                                                             |     | 56   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                         |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 μA ≤ I <sub>OUT</sub> ≤ 50 mA                                                                                                   | 1   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                   | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 1.0 \mu F$ , $I_{OUT} = 50 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

Note: This LDO will be ON after start-up by default.

Note: This LDO has an external active high enable pin,  $V_{05}$ -EN as well as the internal register enable bit. The LDO is on if either of these is "1" (OR-function). The enable bit is "1" by default and can be disabled via the register file.

$V_{O6}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$  C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125 °C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                         | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 50 mA, V <sub>OUT</sub> = 2.7V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | $0 \mu A \le I_{OUT} \le 50 mA$<br>Programming Resolution = 100 mV                                                                | 2.5 | 2.8  | 3.2 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                      |     |      | 50  | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                             |     | 170  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 25 mA                                                                                                          |     | 7    | 90  | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 25 \text{ mA}$                             |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 50 \text{ mA}$                                                                       |     | 4    | 31  |                   |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 1.0 $\mu$ F                                                                  |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 1.0 μF                                                                                             |     | 56   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                         |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 μA ≤ I <sub>OUT</sub> ≤ 50 mA                                                                                                   | 1   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                   | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 1.0 \mu F$ , $I_{OUT} = 50 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

Note: This LDO has an external active high enable pin, V<sub>O6</sub>-EN as well as an internal register enable bit. The LDO is on if either of these is "1" (OR-function). The enable bit is "0" by default and can be enabled via the register file.

# **V<sub>O7</sub> LDO Electrical Characteristics**

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 150 mA, V <sub>OUT</sub> = 2.7V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | $0 \mu A \le I_{OUT} \le 150 mA$<br>Programming Resolution = 100 mV                                                                | 2.5 | 3.0  | 3.2 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                       |     |      | 150 | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                              |     | 500  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 75 mA                                                                                                           |     | 30   | 173 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 75 \text{ mA}$                              |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 150 \text{ mA}$                                                                       |     | 10   | 41  | İ                 |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 2.2 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 2.2 μF                                                                                              |     | 57   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                          |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 μA ≤ I <sub>OUT</sub> ≤ 150 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 2.2 \mu F$ , $I_{OUT} = 150 \text{ mA Note}$                                                                            |     | 60   |     | μs                |

$V_{O8}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$  C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 150 mA, V <sub>OUT</sub> = 2.7V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | $0 \mu A \le I_{OUT} \le 150 mA$<br>Programming Resolution = 100 mV                                                                | 2.5 | 3.0  | 3.2 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                       |     |      | 150 | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                              |     | 510  |     | ]                 |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 75 mA                                                                                                           |     | 30   | 173 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 75 \text{ mA}$                              |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 150 \text{ mA}$                                                                       |     | 12   | 41  |                   |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 2.2 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 2.2 μF                                                                                              |     | 57   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                          |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 μA ≤ I <sub>OUT</sub> ≤ 150 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 2.2 \mu F$ , $I_{OUT} = 150 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

$V_{O9}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

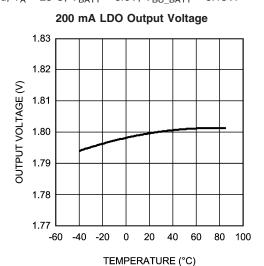

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 200 mA, V <sub>OUT</sub> = 2.2V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | $0 \mu A \le I_{OUT} \le 200 mA$<br>Programming Resolution = 100 mV                                                                | 1.5 | 3.0  | 3.0 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                       |     |      | 200 | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                              |     | 770  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 100 mA                                                                                                          |     | 50   | 288 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 100 \text{ mA}$                             |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V$ , 1 mA $\leq I_{OUT} \leq 200$ mA                                                                                  |     | 15   | 44  |                   |

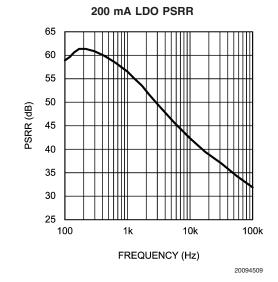

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 4.7 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 4.7 μF                                                                                              |     | 60   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                          |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 1 μA ≤ I <sub>OUT</sub> ≤ 200 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 4.7 \mu F$ , $I_{OUT} = 200 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

$V_{O10}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25^{\circ}C$ . Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125 $^{\circ}C$ . (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

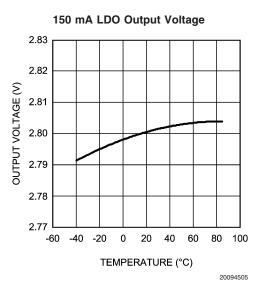

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 150 mA, V <sub>OUT</sub> = 2.2V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -3  | ±1.0 | +3  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | 0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 150 mA<br>Programming Resolution = 100 mV                                                 | 1.5 | 2.5  | 3.0 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                       |     |      | 150 | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                              |     | 610  |     |                   |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 75 mA                                                                                                           |     | 30   | 204 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 75 \text{ mA}$                              |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 150 \text{ mA}$                                                                       |     | 12   | 41  |                   |

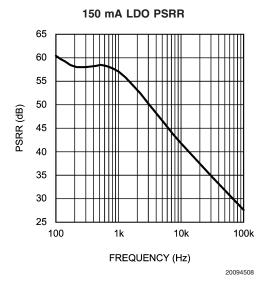

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 2.2 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 2.2 μF                                                                                              |     | 57   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                          |     | 30   |     | μΑ                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 0 μA ≤ I <sub>OUT</sub> ≤ 150 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 2.2 \mu F$ , $I_{OUT} = 150 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

$V_{O11}$  LDO Electrical Characteristics

Unless otherwise noted,  $V_{IN} = V_{BATT} = 3.6V$ . Typical values and limits appearing in normal type apply for  $T_J = 25$ °C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 10)

| Symbol                            | Parameter                              | Condition                                                                                                                          | Min | Тур  | Max | Units             |

|-----------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------------------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | 1 mA $\leq$ I <sub>OUT</sub> $\leq$ 200 mA, V <sub>OUT</sub> = 2.7V<br>3.0V $\leq$ V <sub>BATT</sub> = V <sub>IN</sub> $\leq$ 5.5V | -2  | ±2.0 | +5  | %                 |

| V <sub>OUT</sub><br>Range         | Programmable Output Voltage<br>Range   | 0 $\mu$ A $\leq$ I <sub>OUT</sub> $\leq$ 200 mA<br>Programming Resolution = 100 mV                                                 | 1.8 | 1.8  | 3.3 | V                 |

| I <sub>OUT</sub>                  | Output Current                         | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V$                                                       |     |      | 200 | mA                |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                                                                              |     | 900  |     | İ                 |

| V <sub>IN</sub> -V <sub>OUT</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 100 mA                                                                                                          |     | 50   | 302 | mV                |

| $\Delta V_{OUT}$                  | Line Regulation                        | $(V_{OUT} + 0.25V, 3.0V)_{MAX} \le V_{BATT}$<br>$V_{BATT} = V_{IN} \le 5.5V, I_{OUT} = 100 \text{ mA}$                             |     | 3    |     | mV                |

|                                   | Load Regulation                        | $V_{IN} = 3.6V, 1 \text{ mA} \le I_{OUT} \le 200 \text{ mA}$                                                                       |     | 15   | 44  | 1                 |

| e <sub>N</sub>                    | Output Noise Voltage                   | 10 Hz $\leq$ f $\leq$ 100 kHz,<br>C <sub>OUT</sub> = 4.7 $\mu$ F                                                                   |     | 27   |     | μV <sub>RMS</sub> |

| PSRR                              | Power Supply Ripple<br>Rejection Ratio | f = 217 Hz, C <sub>OUT</sub> = 4.7 μF                                                                                              |     | 60   |     | dB                |

| I <sub>GND</sub>                  | Ground Current                         | I <sub>OUT</sub> = 100 μA                                                                                                          |     | 30   |     | μA                |

| C <sub>OUT</sub>                  | Output Capacitance                     | 1 mA ≤ I <sub>OUT</sub> ≤ 200 mA                                                                                                   | 2   |      | 20  | μF                |

|                                   | Output Capacitor ESR                   |                                                                                                                                    | 5   |      | 500 | mΩ                |

| t <sub>START-UP</sub>             | Start-Up Time from Shutdown            | $C_{OUT} = 4.7 \mu F$ , $I_{OUT} = 200 \text{ mA}$ (Note 10)                                                                       |     | 60   |     | μs                |

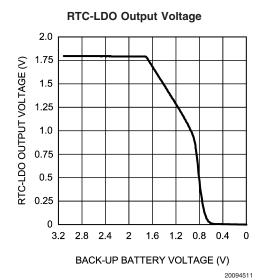

$V_{RTC}$  LDO Electrical Characteristics

Unless otherwise noted, 2.5V <  $V_{BU\_BAT}$  < 3.3V. Typical values and limits appearing in normal type apply for  $T_J = 25$  C. Limits appearing in **boldface** type apply over the entire junction temperature range for operation, -40 to +125°C. (Notes 2, 8, 9)

| Symbol                            | Parameter                              | Condition                                                                 | Min  | Тур  | Max   | Units |

|-----------------------------------|----------------------------------------|---------------------------------------------------------------------------|------|------|-------|-------|

| V <sub>OUT</sub><br>Accuracy      | Output Voltage                         | $I_{OUT} \le 50 \mu A, V_{OUT} = 1.8V$<br>2.15V $\le V_{BU-BAT} \le 3.3V$ | 1.6  | 1.8  | 2.0   | V     |

| IQ                                | Quiescent Current                      | I <sub>OUT</sub> = 6 μA                                                   |      | 2.6  | 6     | μA    |

| I <sub>OUT</sub>                  | Output Current                         | $2.15V \le V_{BU-BAT} \le 3.3V$                                           | 1    | 10   | 50    | μA    |

|                                   | Output Current Limit                   | V <sub>OUT</sub> = 0V                                                     | 1000 | 2000 | 10000 | μΑ    |

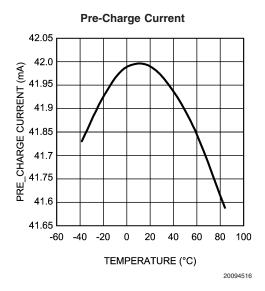

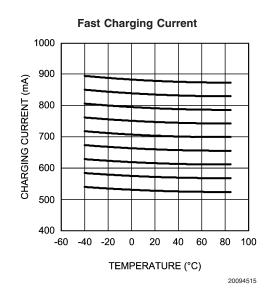

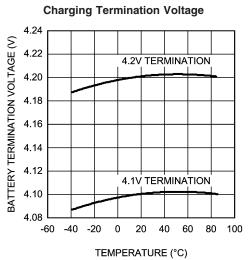

| V <sub>IN</sub> -V <sub>RTC</sub> | Dropout Voltage                        | I <sub>OUT</sub> = 50 mA                                                  |      | 150  | 190   | mV    |