2 μΑ

## **LMV422**

# Dual Rail-to-Rail Output Operational Amplifier with Power Select

## **General Description**

The LMV422 dual rail-to-rail output amplifier offers a power select pin (PS) that allows the user to select one of two power modes depending on the level of performance desired. This is ideal for AC coupled circuits where the circuit needs to be kept active to maintain a quiescent charge on the coupling capacitors with minimum power consumption.

For portable applications, the LMV422 operates in low power mode consuming only 2  $\mu$ A of supply current per channel at a bandwidth of 27 kHz. This allows the user to reduce the power consumption of an amplifier while maintaining an active circuit. For additional bandwidth and output current drive the amplifier can be switched to full power mode with 8 MHz bandwidth while consuming only 400  $\mu$ A per channel.

The LMV422 features a rail-to-rail output voltage swing in addition to an input common mode range that includes ground. The LMV422 is designed for closed loop gains of plus two (or minus one) or greater. The LMV422 is offered in 10-Pin MSOP miniature package to ease the adoption in applications where board area is at a premium.

#### **Features**

| ■ Supply voltage | 2.7V to 5.5V |

|------------------|--------------|

|------------------|--------------|

|      | ,       |      |  |  |

|------|---------|------|--|--|

| — Lo | w power | mode |  |  |

| _    | .11     |      |  |  |

Full power mode 400 μA

Input common mode voltage range −0.3V to 3.8V

■ CMRR 85 dB

■ Output voltage swing Rail-to-Rail

■ Input offset voltage 1 mV

■ Bandwidth

Low power modeFull power mode8 MHz

■ Stable for  $A_V \ge +2$  or  $A_V \le -1$

Supply current per channel

# **Applications**

- AC coupled circuits

- Portable instrumentation

- Smoke detectors

# **Typical Application**

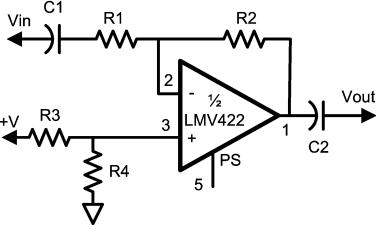

**AC Coupled Application**

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance(Note 2)

Human Body2000VMachine Model200V $V_{IN}$  Differential $\pm 2V$ Supply Voltage (V+ - V-)2.5V to 5.5VStorage Temperature Range $-65^{\circ}$ C to  $+150^{\circ}$ CJunction Temperature (Note 4) $+150^{\circ}$ C

Soldering Information

Infrared or Convection (20 sec) 235 C

Wave Soldering Lead Temp. (10 sec) 260°C

# **Operating Ratings** (Note 1)

Supply Voltage (V $^+$  – V $^-$ ) 2.7V to 5.5V Temperature Range  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$

Package Thermal Resistance  $(\theta_{JA})$

10-Pin MSOP 210°C/W

### **5V Full Power Mode Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ , PS =  $V^-$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                          | Conditions                                                                | Min                 | Тур      | Max               | Units   |

|--------------------|------------------------------------|---------------------------------------------------------------------------|---------------------|----------|-------------------|---------|

|                    |                                    |                                                                           | (Note 6)            | (Note 5) | (Note 6)          |         |

| V <sub>OS</sub>    | Input Offset Voltage               |                                                                           |                     | 1        | 4<br>5.5          | mV      |

| $\Delta V_{OS}$    | Input Offset Voltage Difference    | V <sub>OS</sub> in Full Power Mode –<br>V <sub>OS</sub> in Low Power Mode |                     | 0.1      | 1                 | mV      |

| TC V <sub>os</sub> | Input Offset Average Drift         | (Note 9)                                                                  |                     | 2        |                   | μV/C    |

| I <sub>B</sub>     | Input Bias Current                 |                                                                           |                     | 5        |                   | pA      |

| CMRR               | Common Mode Rejection<br>Ratio     | V <sub>CM</sub> Stepped from 0V to 3.5V                                   | 68<br><b>60</b>     | 85       |                   | dB      |

| PSRR               | Power Supply Rejection Ratio       | V <sup>+</sup> = 2.7V to 5V                                               | 66<br><b>60</b>     | 90       |                   | dB      |

| CMVR               | Input Common Mode Voltage<br>Range | CMRR ≥ 50 dB                                                              | -0.3                |          | 3.8               | V       |

| A <sub>VOL</sub>   | Large Signal Voltage Gain          | $V_O = 0.75V$ to 4.25V $R_L = 1 \text{ M}\Omega$                          | 72<br><b>70</b>     | 100      |                   | -ID     |

|                    |                                    | $V_{O} = 0.75V \text{ to } 4.25V$ $R_{L} = 10 \text{ k}\Omega$            | 75<br><b>70</b>     | 102      |                   | dB      |

| Vo                 | Output Swing High                  | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                               | 4.93<br><b>4.88</b> | 4.97     |                   | V       |

|                    |                                    | $R_L = 1 \text{ M}\Omega \text{ to V}^+/2$                                | 4.94<br><b>4.89</b> | 4.98     |                   | V       |

|                    | Output Swing Low                   | $R_L = 10 \text{ k}\Omega \text{ to V}^+/2$                               |                     | 33       | 180<br><b>230</b> |         |

|                    |                                    | $R_L = 1 \text{ M}\Omega \text{ to V}^+\!/2$                              |                     | 25       | 120<br><b>170</b> | mV      |

| I <sub>sc</sub>    | Output Short Circuit Current       | Sourcing, $V_O = 0V$<br>$V_{ID} = 100 \text{ mV}$                         | 3                   | 5        |                   | mA      |

|                    |                                    | Sinking, $V_O = 5V$<br>$V_{ID} = -100 \text{ mV}$                         | 9                   | 16       |                   | IIIA    |

| I <sub>S</sub>     | Supply Current Per Channel         | PS ≤ 0.5V                                                                 |                     | 400      | 650<br><b>900</b> | μΑ      |

| SR                 | Slew Rate                          | $V_{O} = 3V, A_{V} = +2$                                                  | 1.8                 | 3.8      |                   | V/µs    |

| GBW                | Gain Bandwidth Product             |                                                                           |                     | 8        |                   | MHz     |

| e <sub>n</sub>     | Input-Referred Voltage Noise       | f = 100 kHz<br>f = 1 kHz                                                  |                     | 20<br>25 |                   | nV/ √Hz |

# 5V Full Power Mode Electrical Characteristics (Continued)

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $PS = V^-$ . **Boldface** limits apply at the temperature extremes.

| Symbol           | Parameter                                   | Conditions | Min      | Тур      | Max      | Units   |

|------------------|---------------------------------------------|------------|----------|----------|----------|---------|

|                  |                                             |            | (Note 6) | (Note 5) | (Note 6) |         |

| i <sub>n</sub>   | Input-Referred Current Noise                | f = 1 kHz  |          | 0.006    |          | pA/ √Hz |

| t <sub>LF</sub>  | Time from Low Power Mode to Full Power Mode |            |          | 210      |          | ns      |

| TH <sub>PS</sub> | Full Power Mode Voltage<br>Threshold        |            |          |          | 0.5      | V       |

| I <sub>PS</sub>  | Input Current PS pin(Note 7)                |            |          | -2       |          | μA      |

# **5V Low Power Mode Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for at  $T_J = 25^{\circ}C$ ,  $V^+ = 5V$ ,  $V^- = 0V$ ,  $V_{CM} = V_O = V^+/2$ ,  $PS = V^+$  or Open. **Bold-face** limits apply at the temperature extremes.

| Symbol             | Parameter                                   | Conditions                                                                | Min                 | Тур      | Max               | Units   |

|--------------------|---------------------------------------------|---------------------------------------------------------------------------|---------------------|----------|-------------------|---------|

|                    |                                             |                                                                           | (Note 6)            | (Note 5) | (Note 6)          |         |

| V <sub>OS</sub>    | Input Offset Voltage                        |                                                                           |                     | 1        | 4<br>5.5          | mV      |

| $\Delta V_{OS}$    | Input Offset Voltage Difference             | V <sub>OS</sub> in Full Power Mode –<br>V <sub>OS</sub> in Low Power Mode |                     | 0.1      | 1                 | mV      |

| TC V <sub>os</sub> | Input Offset Average Drift                  | (Note 9)                                                                  |                     | 2        |                   | μV/C    |

| I <sub>B</sub>     | Input Bias Current                          |                                                                           |                     | 5        |                   | рА      |

| CMRR               | Common Mode Rejection<br>Ratio              | V <sub>CM</sub> Stepped from 0V to 3.5V                                   | 60<br><b>55</b>     | 82       |                   | dB      |

| PSRR               | Power Supply Rejection Ratio                | V <sup>+</sup> = 2.7V to 5V                                               | 62<br><b>60</b>     | 90       |                   | dB      |

| CMVR               | Input Common-Mode Voltage<br>Range          | CMRR ≥ 50 dB                                                              | 0                   |          | 3.5               | V       |

| A <sub>VOL</sub>   | Large Signal Voltage Gain                   | $R_L = 1 \text{ M}\Omega$<br>$V_O = 0.75 \text{ to } 4\text{V}$           | 62<br><b>54</b>     | 72       |                   | dB      |

| V <sub>O</sub>     | Output Swing High                           | $R_L = 1 M\Omega$                                                         | 4.94<br><b>4.89</b> | 4.98     |                   | V       |

|                    | Output Swing Low                            | $R_L = 1 M\Omega$                                                         |                     | 150      | 200<br><b>250</b> | mV      |

| I <sub>SC</sub>    | Output Short Circuit Current                | Sourcing, $V_O = 0V$<br>$V_{ID} = 200 \text{ mV}$                         | 40                  | 140      |                   |         |

|                    |                                             | Sinking, $V_O = 5V$<br>$V_{ID} = -200 \text{ mV}$                         | 25                  | 130      |                   | μΑ      |

| I <sub>s</sub>     | Supply Current per channel                  | PS ≥ 4. 5V                                                                |                     | 2        | 3.5<br><b>4.5</b> | μΑ      |

| SR                 | Slew Rate                                   | $V_{O} = 3V, A_{V} = +2$                                                  | 8                   | 14       |                   | V/ms    |

| GBW                | Gain Bandwidth Product                      |                                                                           |                     | 27       |                   | kHz     |

| e <sub>n</sub>     | Input-Referred Voltage Noise                | f = 100 kHz                                                               |                     | 40       |                   | nV/ √Hz |

|                    |                                             | f = 1 kHz                                                                 |                     | 60       |                   |         |

| i <sub>n</sub>     | Input-Referred Current Noise                | f = 1 kHz                                                                 |                     | 0.06     |                   | pA/ √Hz |

| t <sub>FL</sub>    | Time from Full Power Mode to Low Power Mode |                                                                           |                     | 500      |                   | ns      |

| TH <sub>PS</sub>   | Low Power Mode Voltage<br>Threshold         |                                                                           | 4.5                 |          |                   | V       |

| I <sub>PS</sub>    | Input Current PS pin (Note 7)               |                                                                           |                     | 8        |                   | nA      |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics.

Note 2: Human body model, 1.5 k $\Omega$  in series with 100 pF, Machine Model,  $0\Omega$  in series with 200 pF.

Note 3: Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C.

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC board.

Note 5: Typical values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Positive current corresponds to current flowing into the device.

Note 8: Slew rate is the average of the rising and falling slew rates.

Note 9: Offset voltage average drift determined by dividing the change in  $V_{OS}$  at temperature extremes into the total temperature change.

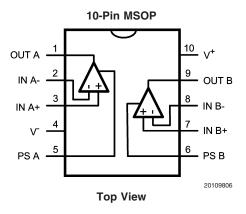

### **Connection Diagram**

# **Ordering Information**

| Package              | Part Number | Package Marking | Transport Media          | NSC Drawing |  |

|----------------------|-------------|-----------------|--------------------------|-------------|--|

| 10-Pin MSOP 3 x 5 mm | LMV422MM    | AJ1A            | 1k Units Tape and Reel   | MUB10A      |  |

|                      | LMV422MMX   | AJIA            | 3.5k Units Tape and Reel | WIUDTUA     |  |

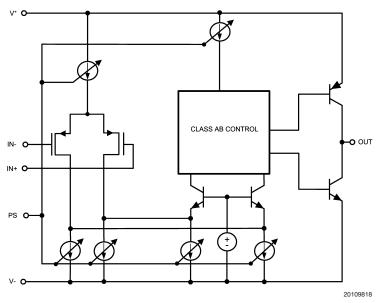

# **Simplified Schematic**

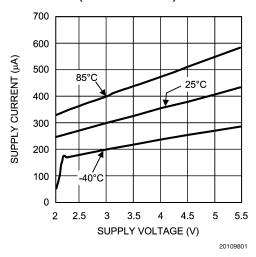

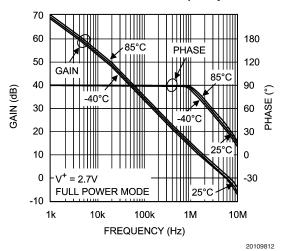

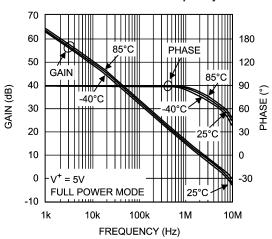

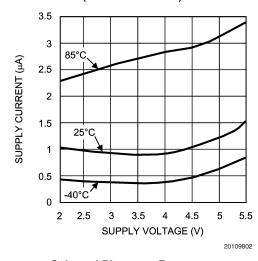

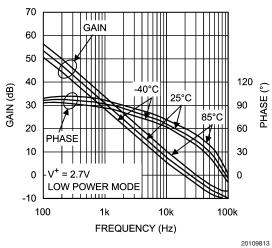

# Typical Performance Characteristics Unless otherwise specified, V+ = 5V, T<sub>A</sub> = 25°C, PS = V+ for

Full Power Mode,  $PS = V^-$  for Low Power Mode.

# Supply Current vs. Supply Voltage per Channel (Full Power Mode)

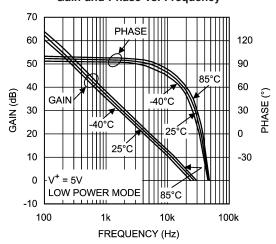

#### Gain and Phase vs. Frequency

#### Gain and Phase vs. Frequency

# Supply Current vs. Supply Voltage per Channel (Low Power Mode)

### Gain and Phase vs. Frequency

# Gain and Phase vs. Frequency

20109815

20109814

# **Typical Performance Characteristics** Unless otherwise specified, V<sup>+</sup> = 5V, T<sub>A</sub> = 25°C, PS = V<sup>+</sup> for Full Power Mode, PS = V<sup>-</sup> for Low Power Mode. (Continued)

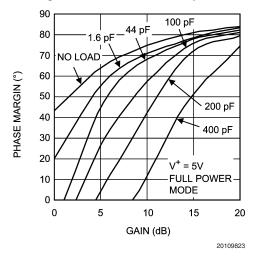

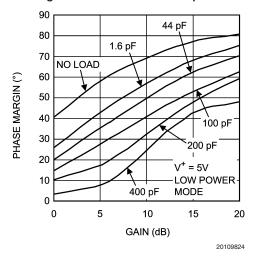

#### Phase Margin vs. Gain for Various Capacitive Load

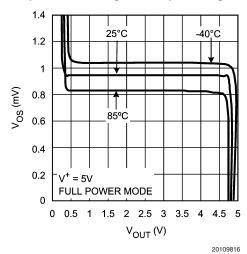

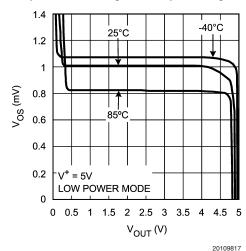

#### Input Offset Voltage vs. Output Voltage

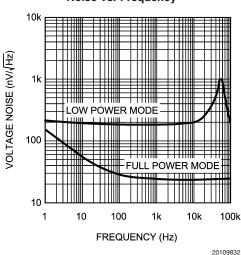

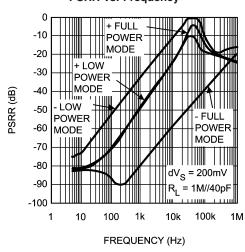

#### Noise vs. Frequency

#### Phase Margin vs. Gain for Various Capacitive Load

#### Input Offset Voltage vs. Output Voltage

#### PSRR vs. Frequency

20109833

# Typical Performance Characteristics Unless otherwise specified, V<sup>+</sup> = 5V, T<sub>A</sub> = 25°C, PS = V<sup>+</sup> for

Full Power Mode,  $PS = V^-$  for Low Power Mode. (Continued)

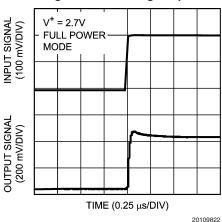

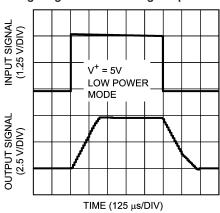

#### **Small Signal Non-Inverting Response**

#### **Small Signal Non-Inverting Response**

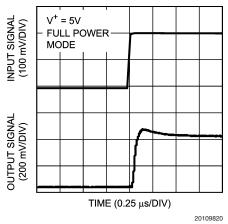

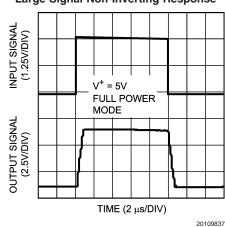

### Large Signal Non-Inverting Response

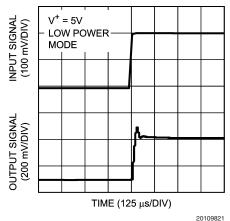

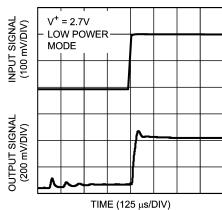

#### **Small Signal Non-Inverting Response**

#### **Small Signal Non-Inverting Response**

#### Large Signal Non-Inverting Response

20109836

# **Application Information**

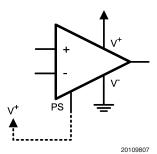

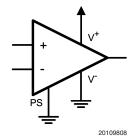

The LMV422 is a dual rail-to-rail output amplifier that can be switched between two active power modes. The power select pin (PS) provides a method to optimize the power consumption, bandwidth and short circuit current. When the PS pin is set to greater than 4.5V (*Figure 1a*) or left open, the LMV422 is in Low Power Mode operating at a bandwidth of

www.DataSheet4U.com

27 kHz and consuming only 2  $\mu$ A of supply current per channel. Setting the PS pin to less than 0.5V, switches the LMV422 to Full Power Mode with a bandwidth of 8 MHz and supply current of 400 uA per channel (*Figure 2b*).. The PS pin should not exceed the supply voltage. The active power modes of the two amplifiers can be set independently.

Figure 1a Low Power Mode

Figure 1b Full Power Mode

#### FIGURE 1.

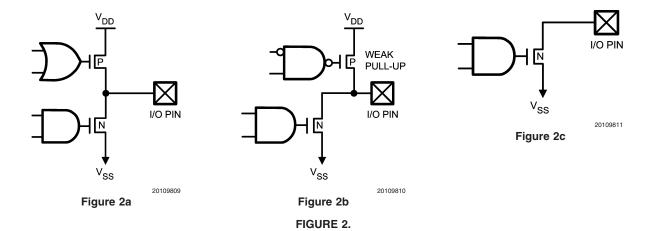

The LMV422 PS pin has an internal pull up and a logic level control gate that makes it easy for the PS pin to be controlled by the output of a logic gate or the output pin of a microcon-

troller. The following figures show the three typical output configurations for logic gates and microcontrollers.

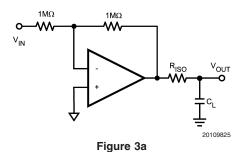

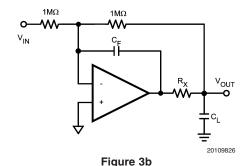

#### **CAPACITIVE LOAD TOLERANCE**

The LMV422 is optimized for maximum bandwidth when operating at a minimum closed loop gain of +2 or -1, therefore, it is not recommended to be configured as a buffer. Like many other op amps, the LMV422 may oscillate when the applied load appears capacitive. The threshold of the oscillation varies both with load and circuit gain (see Phase Margin vs. Gain for various capacitive loads curves). The load capacitance interacts with the amplifier's output resistance to create an additional pole. If this pole frequency is

too low, it will degrade the amplifier's phase margin so that the amplifier is no longer stable.

Figure 3a and 3b show the addition of a small value resistor  $R_{\rm ISO}$  or  $R_{\rm X}$   $(50\Omega$  to  $100\Omega)$  in series with the op amps output. Figure 3b shows the addition of a capacitor  $C_{\rm F}$  (5 pF to 10 pF) between the inverting input and the output pin. This addition capacitor returns the phase margin to a safe value without interfering with lower frequency circuit operation. Note that in all cases, the output will ring heavily when the load capacitance is near the threshold for oscillation.

FIGURE 3.

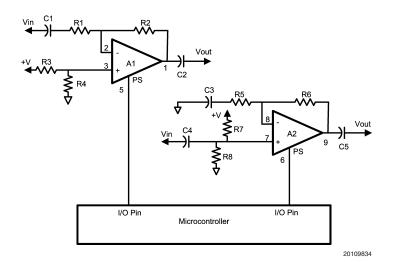

#### **AC COUPLED CIRCUITS**

The two power modes makes the LMV422 ideal for AC coupled circuit where the circuit needs to be kept active to maintain a quiescent charge on the coupling capacitors with minimum power consumption.

Figure 4 shows a schematic of an inverting and non-inverting AC coupled amplifiers using the LMV422 with the PS pins controlled by I/O ports of a microcontroller.

The advantage of the low power active mode for AC coupled amplifiers is the elimination of the time needed to reestablish a quiescent operating point when the amplifier is switched to a full power mode. When amplifiers without a low power active mode are used in low power applications, there are two ways to minimize power consumption. The first is turning off the amplifiers by switching off power to the op amps using a transistor switch. The second is using an amplifier with a shut down pin. Both of these methods have the problem of allowing the coupling capacitors, C1, C2, C3, C4, and C5, to discharge the quiescent DC voltage stored on

them when placed in the shut down state. When the amplifiers are turned on again, the quiescent DC voltages must reestablish themselves. During this time, the amplifier's output is not usable because the output signal is a mixture of the amplified input signal and the charging voltage on the coupling capacitors. The settling time can range from a several milliseconds to several seconds depending on the resistor and capacitor values.

When the LMV422 is placed into the low power mode the power consumption is minimal but the amplifier is active to maintain the quiescent DC voltage on the coupling capacitors and the transition back to the operational high power mode is fast, within few hundred nanoseconds. The active low power mode of the LMV422 separates the two critical aspects of a low power AC amplifier design. The values of the gain resistors, bias resistors, and coupling capacitors can be chosen independently of the turn on and stabilization time.

FIGURE 4.

#### **RESISTIVE LOAD**

The LMV422 has a minimum current drive of 3 mA in full power mode. The minimum resistive load should be 10  $k\Omega$

The current drive in the low power mode is 140 uA, the minimum resistive load should be 100 k $\Omega$ .

# Physical Dimensions inches (millimeters) unless otherwise noted www.DataSheet4U.com .040 [1.02] .193±.006 [4.9±0.15] .118±.004 PIN 1 ID NOTE 2 LAND PATTERN RECOMMENDATION 8X [.0197 [0.5] R.005 TYP [0.13] R.005 TY [0.13] △ .004 [0.1] A .009<sup>+</sup>.004 [0.23<sup>+0</sup>.10] .007±.002 TYP [0.18±0.05] .021 ± .005 [0.53 ± 0.12] SEATING PLANE ⊕ .002 [0.05]M BS CS [.0375 [0.953] CONTROLLING DIMENSION IS INCH VALUES IN [] ARE MILLIMETERS DIMENSIONS IN ( ) FOR REFERENCE ONLY MUB10A (Rev B) 10-Pin MSOP

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

**NS Package Number MUB10A**

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560