# LMF380 Triple One-Third Octave Switched-Capacitor Active Filter

# **General Description**

The LMF380 is a triple, one-third octave filter set designed for use in audio, audiological, and acoustical test and measurement applications. Built using advanced switched-capacitor techniques, the LMF380 contains three filters, each having a bandwidth equal to one-third of an octave in frequency. By combining several LMF380s, each covering a frequency range of one octave, a filter set can be implemented that encompasses the entire audio frequency range while using only a small fraction of the number of components and circuit board area that would be required if a conventional active filter approach were used. The center frequency range is not limited to the audio band, however. Center frequencies as low as 0.125 Hz or as high as 25 kHz are attainable with the LMF380.

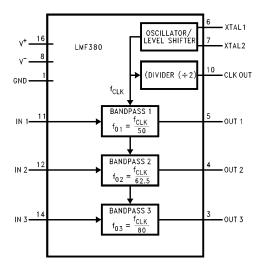

The center frequency of each filter is determined by the clock frequency. The clock signal can be supplied by an external source, or it can be generated by the internal oscillator, using an external crystal and two capacitors. Since the LMF380 has an internal clock frequency divider ( $\div\,2$ ) and an output pin for the half-frequency clock signal, a single clock oscillator for the top-octave LMF380 becomes the master clock for the entire array of filters in a multiple LMF380 application.

Accuracy is enhanced by close matching of the internal components: the ratio of the clock frequency to the center frequency is typically accurate to  $\pm 0.5\%$ , and passband gain and stopband attenuation are guaranteed over the full temperature range.

#### **Features**

- Three bandpass filters with one-third octave center frequency spacing

- Choice of internal or external clock

- No external components other than clock or crystal and two capacitors

# **Key Specifications**

- Passband gain accuracy: Better than 0.7 dB over temperature

- Supply voltage range: ±2V to ±7.5V or +4V to +14V

## **Applications**

- Real-Time Audio Analyzers (ANSI Type E, Class II)

- Acoustical Instrumentation

- Noise Testing

# **Simplified Block Diagram**

## Absolute Maximum Ratings (Notes 1 & 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Dual-In-Line Package (Plastic) 300°C

Surface Mount Package (Note 4)

Vapor Phase (60 seconds) 215°C

Infrared (15 seconds) 220°C

Power Dissipation (Note 5) 500 mW

Maximum Junction Temperature 150°C

Storage Temperature Range -65°C to +150°C

ESD Susceptibility (Note 6) 2000V

# **Operating Ratings** (Note 1)

Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$  LMF380CIN, LMF380CIV, LMF380CIJ  $-40^{\circ}C \le T_A \le +85^{\circ}C$  LMF380CMJ  $-55^{\circ}C \le T_A \le +125^{\circ}C$  Supply Voltage (V<sup>+</sup> – V<sup>-</sup>) 4.0V to 14V Clock Input Frequency 10 Hz to 1.25 MHz

Filter Electrical Characteristics The following specifications apply for  $V^+ = +5V$ ,  $V^- = -5V$ , and  $f_{CLK} = 320$  kHz unless otherwise specified. **Boldface limits apply for T<sub>MIN</sub> to T<sub>MAX</sub>;** all other limits apply for  $T_A = T_J = 25^{\circ}C$ .

| Symbol               | Parameter                                                                              | Conditions                         | Typical (Note 7)  | Limit<br>(Note 8) | Units<br>(Limit)     |

|----------------------|----------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|----------------------|

| f <sub>CLK:f01</sub> | Clock-to-Center-Frequency Ratio, Filter 1                                              |                                    |                   |                   |                      |

| f <sub>CLK:f02</sub> | Clock-to-Center-Frequency Ratio, Filter 2                                              |                                    | 62.5:1            |                   |                      |

| f <sub>CLK:f03</sub> | Clock-to-Center-Frequency Ratio, Filter 3                                              |                                    | 80:1              |                   |                      |

| A <sub>1</sub>       | Gain at f <sub>1</sub> = 3720 Hz (Filter 1),<br>2960 Hz (Filter 2), 2340 Hz (Filter 3) | (Note 9)                           | -32               | -30               | dB (max)             |

| A <sub>2</sub>       | Gain at f <sub>2</sub> = 6080 Hz (Filter 1),<br>4820 Hz (Filter 2), 3820 Hz (Filter 3) | (Note 9)                           | +0.1              | 0.1 ± 0.7         | dB (max)             |

| A <sub>3</sub>       | Gain at f <sub>3</sub> = 6200 Hz (Filter 1),<br>4960 Hz (Filter 2), 3940 Hz (Filter 3) | (Note 9                            | 0.0               | -0.0 ± 0.7        | dB (max)             |

| A <sub>4</sub>       | Gain at f <sub>4</sub> = 6400 Hz (Filter 1),<br>5080 Hz (Filter 2), 4040 Hz (Filter 3) | (Note 9)                           | -0.2              | -0.2 ± 0.7        | dB (max)             |

| A <sub>5</sub>       | Gain at f <sub>5</sub> = 6540 Hz (Filter 1),<br>5180 Hz (Filter 2), 4120 Hz (Filter 3) | (Note 9)                           | -0.1              | -0.1 ± 0.7        | dB (max)             |

| A <sub>6</sub>       | Gain at f <sub>6</sub> = 6720 Hz (Filter 1),<br>5340 Hz (Filter 2), 4240 Hz (Filter 3) | (Note 9)                           | +0.15             | -0.15 ± 0.7       | dB (max)             |

| A <sub>7</sub>       | Gain at f <sub>7</sub> = 8900 Hz (Filter 1),<br>7060 Hz (Filter 2), 5600 Hz (Filter 3) | (Note 9)                           | -22               | -20               | dB (max)             |

| V <sub>OS</sub>      | Output Offset Voltage, Each Filter                                                     |                                    | +50               | + 120<br>-30      | mV (max)<br>mV (min) |

| En                   | Total Output Noise, OUT1<br>Total Output Noise, OUT2<br>Total Output Noise, OUT3       | 0.1 Hz to 20 kHz                   | 240<br>210<br>190 |                   | μVrms                |

| CL                   | Maximum Capacitive Load                                                                |                                    | 200               |                   | pF                   |

|                      | Crosstalk                                                                              | $V_{IN} = 1 \text{ Vrms}, f = f_O$ | -67               |                   | dB                   |

|                      | Clock Feedthrough, Each Filter                                                         | $V^{+} = +5V, V^{-} = -5V$         | 10                |                   | mV <sub>p-p</sub>    |

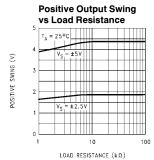

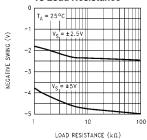

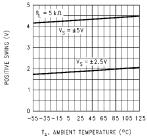

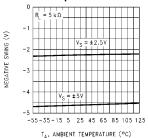

| V <sub>OUT</sub>     | Output Voltage Swing $R_L = 5 \text{ k}\Omega$                                         |                                    | +4.2<br>-4.6      | + 3.8<br>- 4.2    | V (min)<br>V (max)   |

| THD                  | Total Harmonic Distortion                                                              | $V_{IN} = 1 \text{ Vrms}, f = f_O$ | 0.05              |                   | %                    |

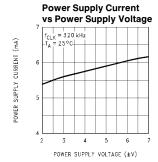

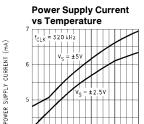

| I <sub>S</sub>       | Supply Current                                                                         |                                    | 6.0               | 9.0               | mA (max)             |

# **Logic Input and Output Electrical Characteristics**

The following specifications for  $V^+ = +5V$  and  $V^- = -5V$  unless otherwise specified. **Boldface limits apply for T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits apply for  $T_A = T_J = +25^{\circ}C$ .

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Parameter                                         |                            | Conditions                                          | Typical<br>(Note 7) | Tested<br>Limit<br>(Note 8)                  | Units<br>(Limit)   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------|-----------------------------------------------------|---------------------|----------------------------------------------|--------------------|

| V <sub>IH</sub><br>V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | XTAL1<br>CMOS Clock<br>Input Voltage              | Logical "1"<br>Logical "0" | $V^{+} = 5V, V^{-} = -5V$                           |                     | +3.0<br>-3.0                                 | V (min)<br>V (max) |

| $V_{IH}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                   | Logical "1"<br>Logical "0" | $V^{+} = 10V, V^{-} = 0V$                           |                     | +8.0<br>+2.0                                 | V (min)<br>V (max) |

| V <sub>IH</sub><br>V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                   | Logical "1"<br>Logical "0" | $V^{+} = 2.5V, V^{-} = -2.5V$                       |                     | + 1.5<br>-1.5                                | V (min)<br>V (max) |

| $egin{array}{c} egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}{c} \egin{array}$ |                                                   | Logical "1"<br>Logical "0" | $V^{+} = 5V, V^{-} = 0V$                            |                     | +4.0<br>+1.0                                 | V (min)<br>V (max) |

| V <sub>OH</sub><br>V <sub>OL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Clock Output Logical "1" Clock Output Logical "0" |                            | $I_{OUT} = -1 \text{ mA}$ $I_{OUT} = +1 \text{ mA}$ |                     | V <sup>+</sup> - 1.0<br>V <sup>-</sup> + 1.0 | V (min)<br>V (max) |

| I <sub>IN</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Input Current XTAL1                               |                            |                                                     |                     | ±20                                          | μΑ (max)           |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional. These ratings do not guarantee specific performance limits, however. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to GND unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supplies  $(V_{IN} < V^- \text{ or } V_{IN} > V^+)$ , the current at that pin should be limited to 5 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of 5 mA to four.

Note 4: See AN450 "Surface Mounting Methods and Their Effect on Product Reliability" or the section titled "Surface Mount" found in any volume of the Linear Data Book Rev. 1 for other methods of soldering surface mount devices.

Note 5: The maximum power dissipation must be derated at elevated temperatures and is a function of  $T_{Jmax}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For guaranteed operation,  $T_{Jmax} = 125^{\circ}C$ . The typical thermal resistance ( $\theta_{JA}$ ) of the LMF380N when board-mounted is 51°C.W.  $\theta_{JA}$  is typically 52°C/W for the LMF380J, and 86°C/W for the LMF380V.

Note 6: Human body model, 100 pF discharged through a 1.5 k $\Omega$  resistor.

Note 7: Typicals are at  $T_{J}=25^{\circ}\text{C}$  and represent the most likely parametric norm.

Note 8: Limits are guaranteed to National's Averge Outgoing Quality Level (AOQL).

Note 9: The nominal test frequencies are:  $f_1 = 0.58 \, f_0$ ,  $f_2 = 0.95 \, f_0$ ,  $f_3 = 0.98 \, f_0$ ,  $f_4 = f_0$ ,  $f_5 = 1.02 \, f_0$ ,  $f_6 = 1.05 \, f_0$ , and  $f_7 = 1.39 \, f_0$ . The actual test frequencies listed in the table may differ slightly from the nominal values.

# Positive Output Swing vs Temperature

-55-35-15 5 25 45 65 85 105 125

$T_A$ , AMBIENT TEMPERATURE (°C)

Negative Output Swing vs Temperature

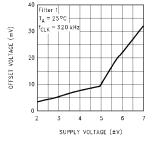

# Offset Voltage vs Supply Voltage

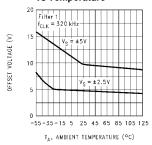

#### Offset Voltage vs Temperature

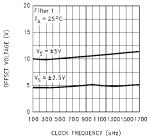

# Offset Voltage vs Clock Frequency

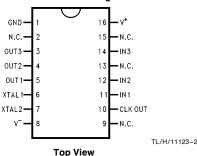

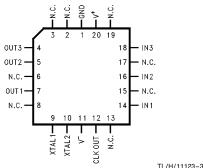

# **Connection Diagrams**

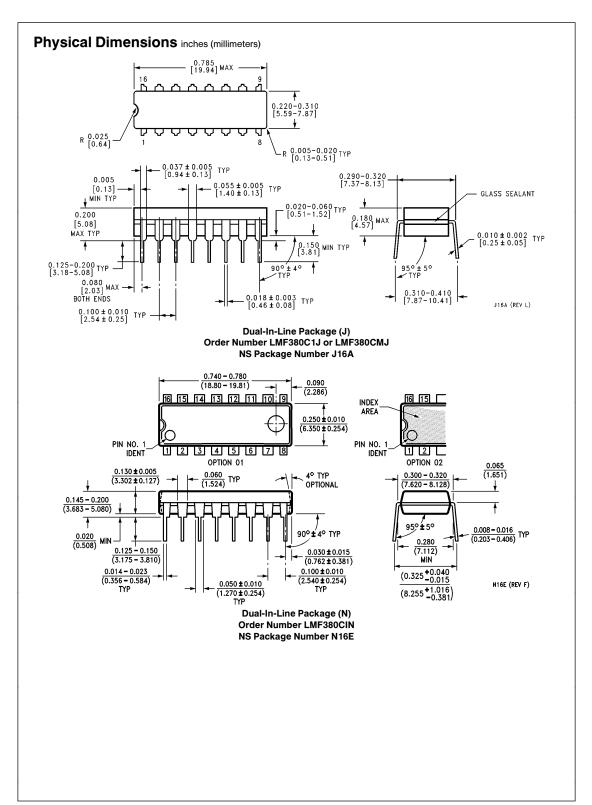

#### **Dual-In-Line Package**

Order Number LMF380CIJ, LMF380CMJ or LMF380CIN See NS Package Number J16A or N16E

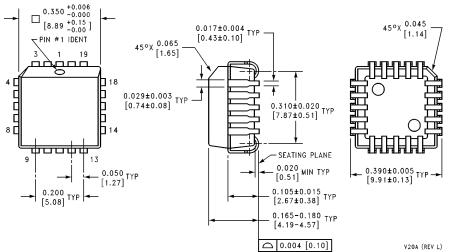

## Plastic Chip Carrier Package

Top View

Order Number LMF380CIV See NS Package Number V20A

#### **Pin Description**

GND

This is the analog ground reference for the LMF380. In split supply applications, GND should be connected to the system ground. When operating the LMF380 from a single positive power supply voltage, pin 1 should be connected to a "clean" reference voltage midway between V+ and V-.

N.C.

These pins are not connected to the internal circuitry.

OUT1, OUT2,

These are the outputs of the filters.

OUT3

XTAL1

This is the crystal oscillator input pin. When using the internal oscillator, the crystal should be tied between XTAL1 and XTAL2. XTAL1 also serves as the input for an external CMOS-level clock.

XTAL2

This is the output of the internal crystal oscillator. When using the internal oscillator, the crystal should be tied between XTAL1 and XTAL2.

٧-

This is the negative power supply pin. It should be bypassed with at least a 0.1  $\mu F$  ceramic capacitor. For best results, a

1.0  $\mu F$  to 10.0  $\mu F$  tantalum capacitor should also be used. For single-supply operation, connect this pin to system ground.

**CLOCK OUT**

This is the clock output pin. It can drive the clock inputs (XTAL1) of additional LMF380s or other components. The clock output frequency is one-half the clock frequency at XTAL1.

INPUT1, INPUT2, INPUT3 V+ These are the signal inputs to the filters.

This is the positive power supply pin. It should be bypassed with at least a 0.1  $\mu\text{F}$  ceramic capacitor. For best results, a 1.0  $\mu\text{F}$  to 10.0  $\mu\text{F}$  tantalum capacitor should also be used.

# **Functional Description**

The LMF380 contains three fourth-order Chebyshev bandpass filters whose center frequencies are spaced one-third of an octave apart, making it ideal for use in "real time" audio spectrum analysis applications. As with other switched-capacitor filters, the center frequencies are proportional to the clock frequency applied to the IC; the center frequencies of the LMF380's three filters are located at  $f_{\rm CLK}/50,\,f_{\rm CLK}/62.5,\,$  and  $f_{\rm CLK}/80.$

The three filters in an LMF380 cover a full octave in frequency, so that by using several LMF380s with clock frequencies separated by a factor of 2n, a complex audio program can be analyzed for frequency content over a range of several octaves. To facilitate this, the CLK OUT pin of the LMF380 supplies an output clock signal whose frequency is one-half that of the incoming clock frequency. Therefore, a single clock source can provide the clock reference for all of the 30 filters (10LMF380s) in a real time analyzer that covers the entire 10-octave audio frequency range. The LMF380 contains an internal clock oscillator that requires an external crystal and two capacitors to operate. Since the clock divider is on-board, only a single crystal is needed for the top-octave filter chip; the remaining devices can derive their clock signals from the master. If desired, an external oscillator can be used instead.

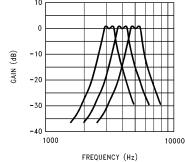

Figure 1 shows the magnitude versus frequency curves for the three filters in the LMF380. Separate input and output pins are provided for the three internal filters. The input pins will normally be connected to a common signal source, but can also be connected to separate input signals when necessary.

FIGURE 1. Response curves for the three filters in the LMF380. The clock frequency is 250 kHz.

# **Applications Information**

## **POWER SUPPLIES**

The LMF380 can operate from a total supply voltage (V $^+$  – V $^-$ ) ranging from 4.0V up to 14V, but the choice of supply voltage can affect circuit performance. The IC depends on MOS switches for its operation. All such switches have inherent "ON" resistances, which can cause small delays in charging internal capacitances. Increasing the supply voltage reduces this "ON" resistance, which improves the accuracy of the filter in high-frequency applications. The maximum practical center frequency improves by roughly 10% to 20% when the supply voltage increases from 5V to 10V.

Dynamic range is also affected by supply voltage. The maximum signal voltage swing capability increases as supply voltage increases, so the dynamic range is greater with higher power supply voltages. It is therefore recommended that the supply voltage be kept near the maximum operating voltage when dynamic range and/or high-frequency performance are important.

As with all switched-capacitor filters, each of the LMF380's power supply pins should be bypassed with a minimum of 0.1  $\mu\text{F}$  located close to the chip. An additional 1  $\mu\text{F}$  to 10  $\mu\text{F}$  tantalum capacitor on each supply pin is recommended for best results.

# Sampled-Data System Considerations

#### **CLOCK CIRCUITRY**

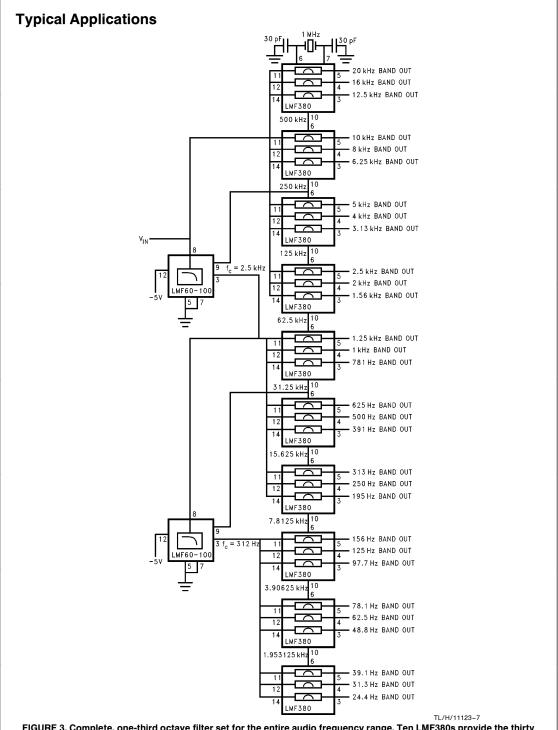

The LMF380's clock input circuitry accepts an external CMOS-level clock signal at XTAL1, or can serve as a self-contained oscillator with the addition of an external 1 MHz crystal and two 30 pF capacitors (see *Figure 3*).

The Clock Output pin provides a clock signal whose frequency is one-half that of the clock signal at XTAL1. This allows multiple LMF380s to operate from a single internal or external clock oscillator.

### **CLOCK FREQUENCY LIMITATIONS**

The performance characteristics of a switched-capacitor filter depend on the switching (clock) frequency. At very low clock frequencies (below 10 Hz), the time between clock cycles is relatively long, and small parasitic leakage currents cause the internal capacitors to discharge sufficiently to affect the filter's offset voltage and gain. This effect becomes more pronounced at elevated operating temperatures.

At higher clock frequencies, performance deviations are due primarily to the reduced time available for the internal operational amplifiers to settle. For this reason, when the filter clock is externally generated, care should be taken to ensure that the clock waveform's duty cycle is as close to 50% as possible, especially at high clock frequencies.

### **OUTPUT STEPS**

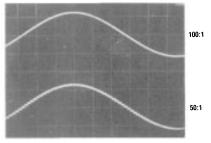

Because the LMF380 uses switched-capacitor techniques, its performance differs in several ways from non-sampled (continuous) circuits. The analog signal at any input is sampled during each filter clock cycle, and since the output voltage can change only once every clock cycle, the result is a discontinuous output signal. The output signal takes the form of a series of voltage "steps", as shown in *Figure 2* for clock-to-center-frequency ratios of 50:1 and 100:1.

TL/H/11123-8

FIGURE 2. Switched-Capacitor Filter Output Waveform.

Note the sampling "steps".

#### **ALIASING**

Another important characteristic of sampled-data systems is their effect on signals at frequencies greater than one-half the sampling frequency, fs. (The LMF380's sampling frequency is the same as the filter clock frequency). If a signal with a frequency greater than one-half the sampling frequency is applied to the input of a sampled-data system, it will be "reflected" to a frequency less than one-half the sampling frequency. Thus, an input signal whose frequency is  $f_S/2 + 10$  Hz will cause the system to respond as though the input frequency was  $f_{\mbox{\scriptsize S}}/2~-~10$  Hz. If this frequency happens to be within the passband of the filter, it will appear at the filter's output, even though it was not present in the input signal. This phenomenon is known as "aliasing". Aliasing can be reduced or eliminated by limiting the input signal spectrum to less than  $f_{\mbox{\scriptsize S}}/2$ . In some cases, it may be necessary to use a bandwidth-limiting filter (often a simple passive RC low-pass) between the signal source and the switched-capacitor filter's input. In the application example shown in Figure 3, two LMF60 6th-order low-pass filters provide anti-aliasing filtering.

#### **OFFSET VOLTAGE**

Switched-capacitor filters often have higher offset voltages than non-sampling filters with similar topologies. This is due to charge injection from the MOS switches into the sampling and integrating capacitors. The LMF380's offset voltage ranges from a minimum of  $-30\,$  mV to a maximum of  $+120\,$  mV.

#### NOISE

Switched-capacitor filters have two kinds of noise at their outputs. There is a random, "thermal" noise component whose amplitude is typically on the order of 210  $\mu V$ . The other kind of noise is digital clock feedthrough. This will have an amplitude in the vicinity of 10 mV peak-to-peak. In some applications, the clock noise frequency is so high compared to the signal frequency that it is unimportant. In other cases, clock noise may have to be removed from the output signal with, for example, a passive low-pass filter at the LMF380's output (see Figure 4).

#### INPUT IMPEDANCE

The LMF380's input pins are connected directly to the internal biquad filter sections. The input impedance is purely capacitive and is approximately 6.2 pF at each input pin, including package parasitics.

FIGURE 3. Complete, one-third octave filter set for the entire audio frequency range. Ten LMF380s provide the thirty bandpass filters required for this function. Power supply connections and bypass capacitors are not shown. Pin numbers are for the dual-in-line package.

## Typical Applications (Continued)

#### THIRD-OCTAVE ANALYZER FILTER SET

The circuit shown in Figure 3 uses the LMF380 to implement a  $1/\!_{2}$ -octave filter set for use in "real time" audio program analyzers. Ten LMF380s provide all of the bandpass filtering for the full audio frequency range. The power supply connections are not shown, but each power supply pin should be bypassed with a 0.1  $\mu\mathrm{F}$  ceramic capacitor in parallel with a 1  $\mu\mathrm{F}$  tantalum capacitor.

The first LMF380, at the top of *Figure 3*, handles the highest octave, with center frequencies of 20 kHz, 16 kHz, and 12.6 kHz. It also contains the 1 MHz master clock oscillator for the entire system. Its Clock Out pin provides a 500 kHz clock for the second LMF380, which supplies 250 kHz to the third LMF380, and so on.

If the audio input signal were applied to all of the LMF380 input pins, aliasing might occur in the lower frequency filters due to audio components near their clock frequencies. For example, the LMF380 at the bottom of *Figure 3* has a clock frequency equal to 1.953125 kHz. An input signal at 1.93 kHz will be aliased down to 23.125 Hz, which is near the band center of the 24.4 Hz bandpass filter and will appear at the output of that filter.

This problem is solved by two LMF60–100 6th order Butterworth low-pass filters serving as anti-aliasing filters, as shown in *Figure 3*. The first LMF60–100 is connected to the input signal. The clock for this LMF60 is 250 kHz and comes from pin 10 of the second LMF380. The cutoff frequency is therefore 2.5 kHz. The output of this first LMF60–100 drives the inputs of the fifth, sixth, and seventh LMF380s. The seventh LMF380 has a 15.625 kHz clock, so aliasing will begin to become a problem around 15.2 kHz. With a sixth-order, 2.5 kHz low-pass filter preceding this circuit, the attenuation at 15.2 kHz is theoretically about 94 dB, which prevents aliasing from occuring at this bandpass filter.

The output of the first LMF60 also drives the input of the second LMF60, which provides anti-aliasing filtering for the three LMF380s that handle the lowest part of the audio frequency spectrum.

Note that no anti-aliasing filtering is provided for the four LMF380s at the top of *Figure 3*. These devices will not encounter aliasing problems for frequencies below about 120 kHz; if higher input frequencies are expected, an additional low-pass filter at  $V_{\rm IN}$  may be required.

#### **DETECTORS**

In a real-time analyzer, the amplitude of the signal at the output of each filter is displayed, usually in "bar-graph" form. The AC signal at the output of each bandpass filter must be converted to a unipolar signal that is appropriate for driving the display circuit.

The detector can take any of several forms. It can respond to the peaks of the input signal, to the average value, or to the rms value. The best type of detector depends on the application. For example, peak detectors are useful when monitoring audio program signals that are likely to overdrive an amplifier. Since the output of the peak detector is propor-

tional to the peak signal voltage, it provides a good indication of the voltage swing. Generally, the output of the peak detector must have a moderately fast (about 1 ms) attack time and a much slower (tens or hundreds of milliseconds) decay time. The actual attack and decay times depend on the expected application. An average detector responds to the average value of the rectified input signal and provides a good solution when measuring random noise. An average detector will normally respond relatively slowly to a rapid change in input amplitude. An rms detector gives an output that is proportional to signal power, and is therefore useful in many instrumentation applications, especially those that involve complex signals.

Peak detectors and average-responding detectors require precision rectifiers to convert the bipolar input signal into a unipolar output. Half-wave rectifiers are relatively inexpensive, but respond to only one polarity of input signal; therefore, they can potentially ignore information. Full-wave rectifiers need more components, but respond to both polarities of input signal. Examples of half- and full-wave peak- and average-responding detectors are shown in Figure 4. The component values shown may need to be adjusted to meet the requirements of a particular application. For example, peak detector attack and decay times may be changed by changing the value of the "hold" capacitor.

The input to each detector should be capacitively-coupled as shown in *Figure 4*. This prevents any errors due to voltage offsets in the preceding circuitry. The cutoff frequency of the resulting high-pass filter should be less than half the center frequency of the band of interest.

Note that a passive low-pass filter is shown at the input to each detector in *Figure 4*. These filters attenuate any clock-frequency signals at the outputs of the third-octave switched-capacitor filters. The typical clock feedthrough at a filter output is 10 mV rms, or 40 dB down from a nominal 1 Vrms signal amplitude. When more than 40 dB dynamic range is needed, a passive low-pass filter with a cutoff frequency about three times the center frequency of the bandpass will attenuate the clock feedthrough by about 24 dB, yielding about 64 dB dynamic range. The component values shown produce a cutoff frequency of 1 kHz; changing the capacitor value will alter the cutoff frequency in inverse proportion to the capacitance.

The offset voltage of the operational amplifier used in the detector will also affect the detector's dynamic range. The LF353 used in the circuits in *Figure 3* is appropriate for systems requiring up to 40 dB dynamic range.

#### **DISPLAYS**

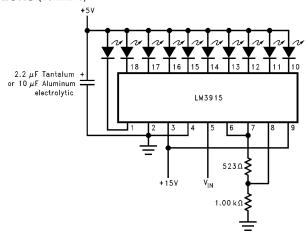

The output of the detector will drive the input of the display circuit. An example of an LED display driver using the LM3915 is shown in *Figure 5*. The LM3915 drives 10 LEDs with 3 dB steps between LEDs; the total display range for an LM3915 is therefore 27 dB. Two LM3915s can be cascaded to yield a total range of 57 dB. See the LM3915 data sheet for more information.

# Typical Applications (Continued) (b) 100 kΩ 100 kΩ $91\,k\Omega$ 1/2 LF353 1/2 LF353 TL/H/11123-9 TL/H/11123-10 (c) 100 kΩ 1% $100\,k\Omega\ 1\%$ C<sub>IN</sub> 0.02 μF 100 kΩ 1/2 LF353 $210\,k\Omega$ $200\,k\Omega$ 1% 1/2 LF353 TL/H/11123-11 (d) 100 kΩ 1% 100 kΩ 1% G<sub>IN</sub> 0.02 μF 1/2 LF353 200 kΩ 1% 210 kΩ $v_{out}$

FIGURE 4. Examples of detectors for audio signals. (a) Half-wave peak detector. (b) Half-wave average detector. (c) Full-wave peak detector. (d) Full-wave average detector. All diodes are 1N914 or 1N4148. Input RC low-pass filters attenuate clock noise from switched-capacitor filters; values shown are for 1 kHz cutoff frequency. C<sub>IN</sub> should be at least 0.27 μF for frequency bands below 50 Hz and 0.1 μF for higher frequencies. Power supplies (not shown) should be bypassed with at least 0.1 μF close to the amplifiers.

1/2 LF353

# Typical Applications (Continued)

TL/H/11123-13

FIGURE 5. LED display using LM3915 bar graph driver. The input voltage range is 2V full-scale, with 3 dB per step.

# Physical Dimensions inches (millimeters) (Continued)

Plastic Chip Carrier Package (V) Order Number LMF380CIV NS Package Number V20A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: onlyeg@etervel.nsc.com

Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408