LM5036 SNVSB14C - APRIL 2018 - REVISED OCTOBER 2021

# LM5036 Half-Bridge PWM Controller with Integrated Auxiliary Bias Supply

#### 1 Features

- High integration controller for small form factor, high-density DC-DC power converters

- Integrated 100-V, 100-mA auxiliary bias supply

- Fully regulated pre-biased start-up

- Enhanced cycle-by-cycle current limiting with pulse matching for low and high primary FETs

- Optimized maximum duty cycle for primary-side **FETs**

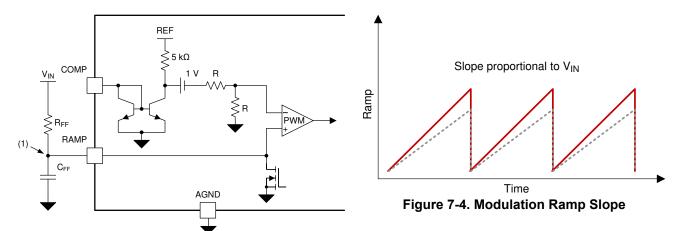

- Voltage-mode control with input voltage feedforward

- 100-V high-voltage start-up regulator

- Configurable latch, OVP operation

- Integrated 100-V, 2-A MOSFET drivers for primary-

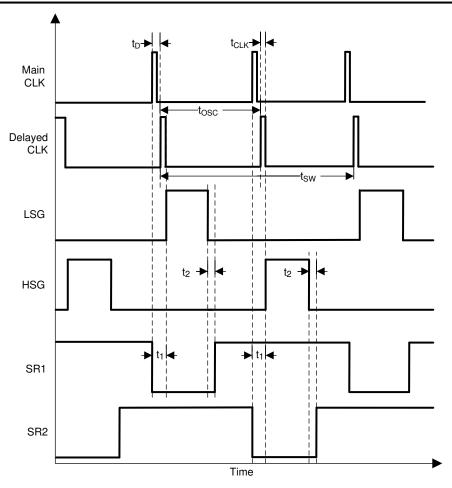

- Programmable dead-time between primary-side and synchronous rectifier (SR) FETs

- Create a custom design using the LM5036 with the Excel Calculator Tool or WEBENCH® Power Designer

# 2 Applications

- Telecom and data communication isolated power

- Industrial power supplies and factory automation

- Test, measurement equipment

# 3 Description

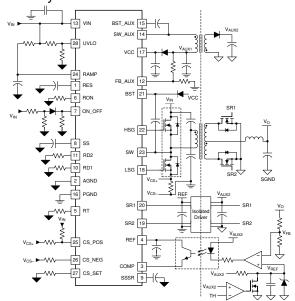

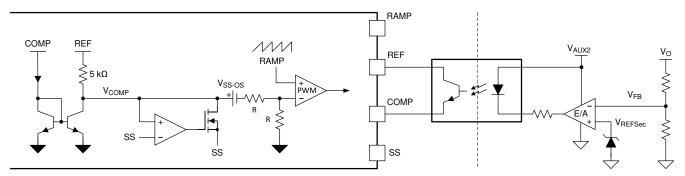

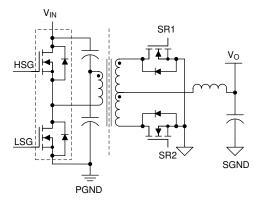

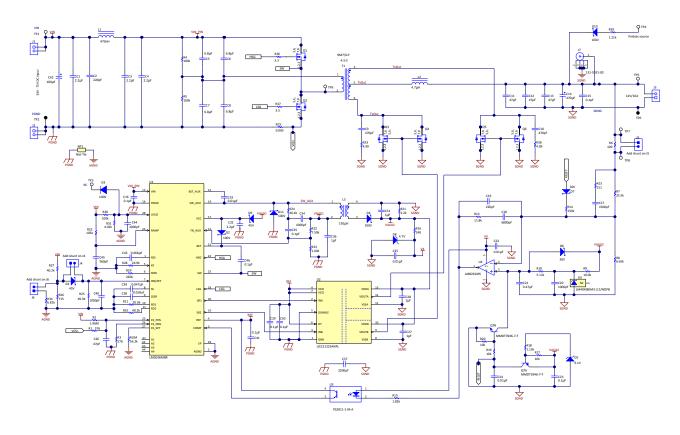

The LM5036 PWM controller, with integrated auxiliary bias supply, offers high power density for industrial isolated power applications. It contains all the features necessary to implement half-bridge power converters, using voltage-mode control, with input voltage feedforward. This controller is intended to operate on the primary side of an isolated converter with DC input voltage up to 100 V. The controller includes features that improve power density and reliability while reducing system cost:

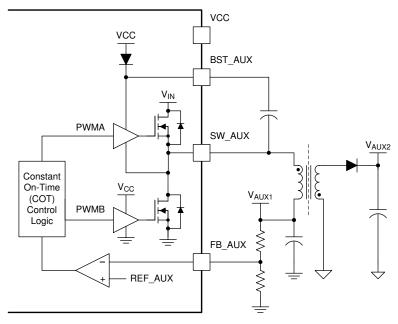

- An integrated fly-buck converter as auxiliary bias supply. Provides bias power for both primary and secondary circuits, with a minimum of external components.

- Fully regulated pre-bias start-up. Eliminates output voltage over-shoot or dips even when starting into a pre-charged output capacitor.

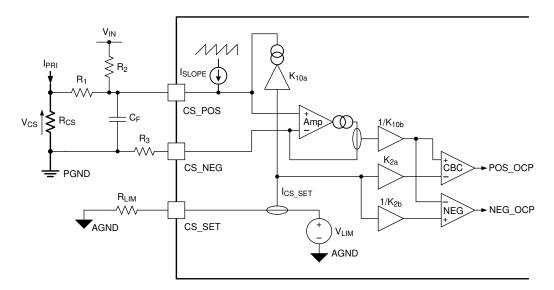

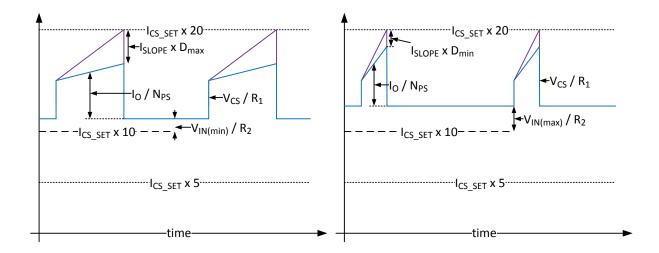

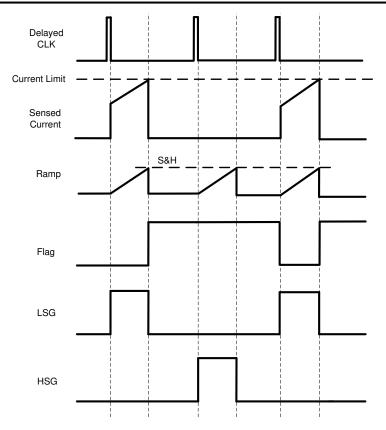

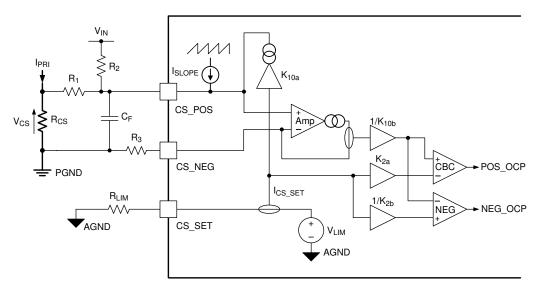

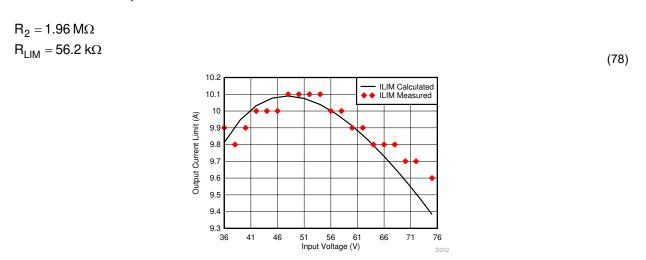

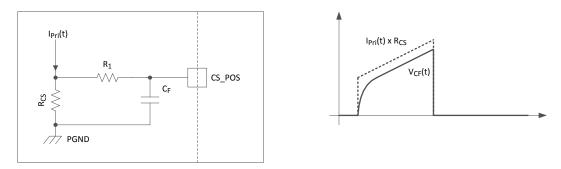

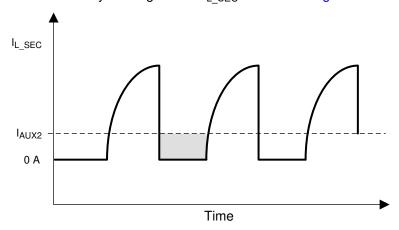

- Enhanced cycle-by-cycle peak current limit with pulse matching. The controller limits both positive and negative current. Pulse matching ensures equal pulse width for low and high side devices, to avoid transformer saturation. Output current limit is approximately constant across the full range of input voltage.

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)   |

|-------------|------------------------|-------------------|

| LM5036      | WQFN (28)              | 5.00 mm × 5.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

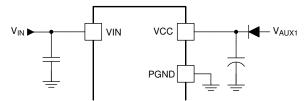

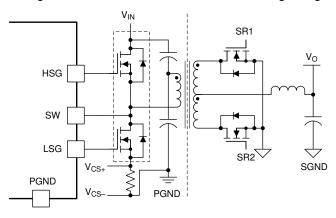

Simplified Application

# **Table of Contents**

| 2 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 0 D = = = 4  =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |

| 3 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 5 Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 6 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 6.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6 10.1 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58                                                      |

| 6.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 6.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 6.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 6.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                         |

| 6.6 Switching Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

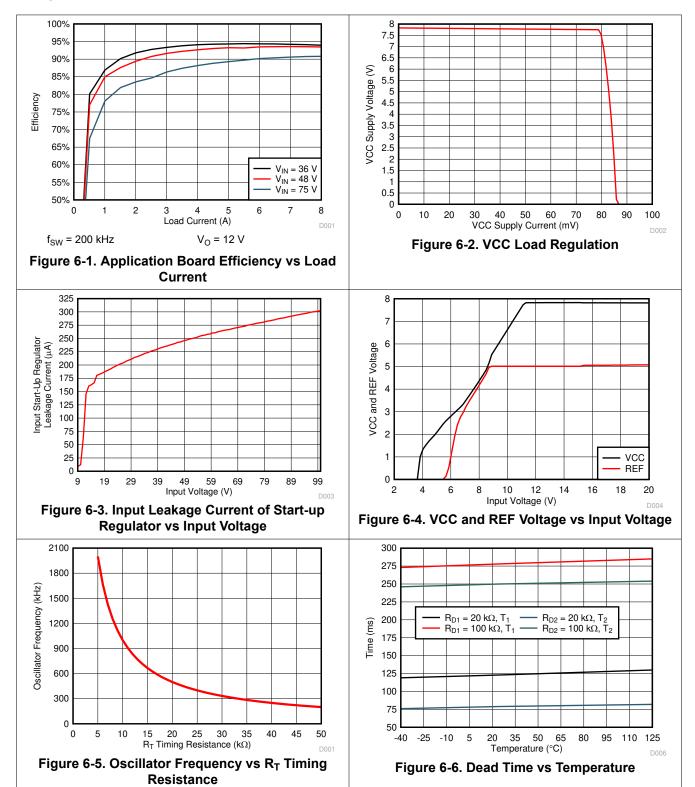

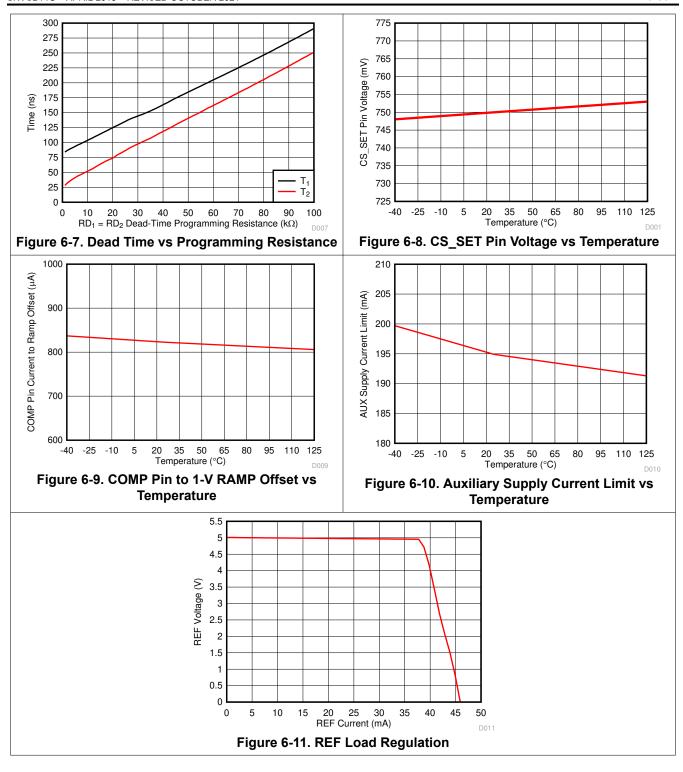

| 6.7 Typical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 7 Detailed Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| 7.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 00                                                      |

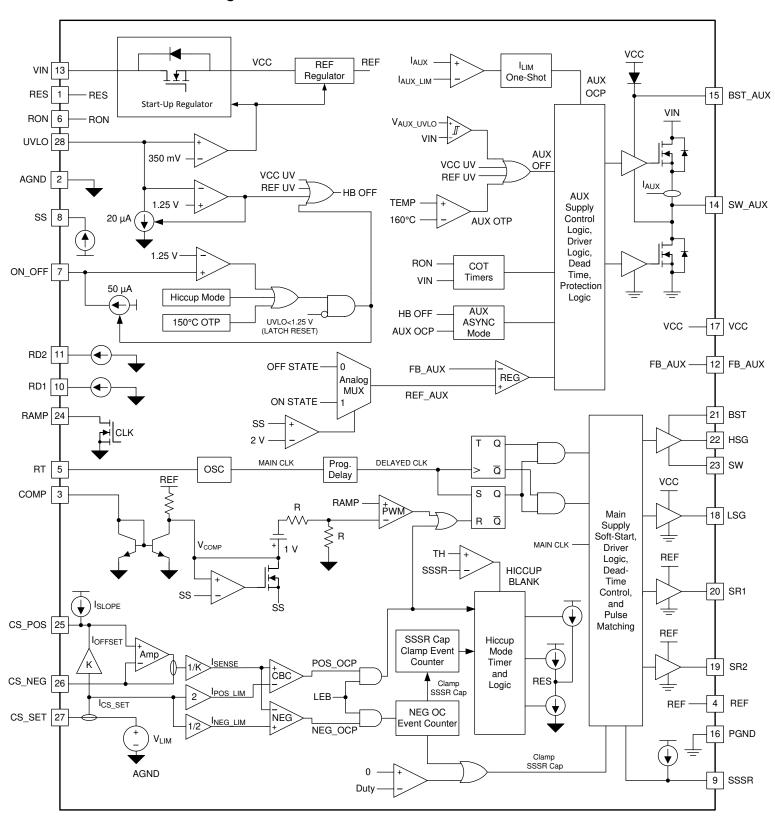

| 7.2 Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61                                                      |

| 7.3 Feature Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15 Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01                                                      |

| <ul> <li>Deleted minimum and maximum peak value Updated typical from 54 µA to 36 µA. Remo</li> <li>Changed typical peak current (I<sub>SO_PRI</sub>) spectors Changed minimum BST_AUX undervoltage</li> <li>Changed typical BST_AUX undervoltage the Changed maximum BST_AUX undervoltage</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | e of current source for slope compensation (I <sub>SLOPE</sub> ) sponded table note (1) from this parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ecifications.<br>7<br>7<br>0 3.5 V7<br>0 V7<br>0 6.5 V7 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                         |

| Changes from Revision A (June 2018) to Re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | evision B (April 2019)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page                                                    |

| <ul> <li>Added minimum recommended values for F</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RD <sub>1</sub> and RD <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>Page</b>                                             |

| <ul><li>Added minimum recommended values for F</li><li>Changed minimum recommended input volt</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>Page</b><br>6                                        |

| <ul> <li>Added minimum recommended values for F</li> <li>Changed minimum recommended input volt</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V<br>DFFSET and I <sub>BiasOffset</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>Page</b> 66                                          |

| <ul> <li>Added minimum recommended values for F</li> <li>Changed minimum recommended input volt</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RD <sub>1</sub> and RD <sub>2</sub><br>tage from 18V to 16V.<br><sub>DFFSET</sub> and I <sub>BiasOffset</sub><br>λ to 54-μΑ<br>at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub>                                                                                                                                                                                                                                                                                                                                                           | Page677                                                 |

| <ul> <li>Added minimum recommended values for F</li> <li>Changed minimum recommended input volt</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> .</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RD <sub>1</sub> and RD <sub>2</sub><br>tage from 18V to 16V.<br><sub>DFFSET</sub> and I <sub>BiasOffset</sub><br>to 54-µA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Page677 testh2,                                         |

| <ul> <li>Added minimum recommended values for F</li> <li>Changed minimum recommended input volt</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> ·</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DFFSET and I <sub>BiasOffset</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page677 ESTh2,77                                        |

| <ul> <li>Added minimum recommended values for F</li> <li>Changed minimum recommended input volt</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> ·</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DFFSET and I <sub>BiasOffset</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page677 ESTh2,77                                        |

| <ul> <li>Added minimum recommended values for F</li> <li>Changed minimum recommended input volt</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> ·</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX</sub> UVLO maximum v</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DFFSET and I <sub>BiasOffset</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page677 EESTh2,77                                       |

| <ul> <li>Added minimum recommended values for F         <ul> <li>Changed minimum recommended input volt</li> </ul> </li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> ·</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RD <sub>1</sub> and RD <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page677 EESTh2777                                       |

| <ul> <li>Added minimum recommended values for F         Changed minimum recommended input volt     </li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>,I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub></li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to Y</li> <li>Added new parameters AUX SUPPLY CUR</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                         | RD <sub>1</sub> and RD <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page677777                                              |

| <ul> <li>Added minimum recommended values for F         Changed minimum recommended input volition     </li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> · Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to S</li> <li>Added new parameters AUX SUPPLY CUR</li> <li>Added new conditions in Switching Charact</li> </ul>                                                                                                                                                                                                                                                                                                                                        | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DEFESET and I <sub>BiasOffset</sub> A to 54-µA.  at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub> M-OS  Value from 16.6V to 16V.  VHC_BLK_TH  RRENT LIMIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , T <sub>AuxSns</sub> teristics for t <sub>ON</sub>                                                                                                                                                                                                                     | Page677777                                              |

| <ul> <li>Added minimum recommended values for F         Changed minimum recommended input volition         Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub>         Changed typical value of I<sub>SLOPE</sub> from 50-µA         Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>,I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub>.</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub>         Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub>         Changed parameter V<sub>AUX_UVLO</sub> maximum v         Changed parameter name HC_BLK_TH to S         Added new parameters AUX SUPPLY CUR         Added new conditions in Switching Charact         Added Reference to the Calculator tool</li> </ul>                                                                                                                                                                                                                                                                                               | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DEFESET and I <sub>BiasOffset</sub> A to 54-µA.  at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub> M-OS Value from 16.6V to 16V.  VHC_BLK_TH  RRENT LIMIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , T <sub>AuxSns</sub> teristics for t <sub>ON</sub>                                                                                                                                                                                                                      | Page677777                                              |

| <ul> <li>Added minimum recommended values for F.</li> <li>Changed minimum recommended input volth</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> .</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to Select the conditions of the conditions.</li> <li>Added Reference to the Calculator tool</li> <li>Changed Positive and negative current limit</li> </ul>                                                                                                                                                                                               | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DFFSET and I <sub>BiasOffset</sub> A to 54-µA.  at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub> M-OS  Value from 16.6V to 16V.  VHC_BLK_TH  RRENT LIMIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , t <sub>AuxSns</sub> teristics for t <sub>ON</sub>                                                                                                                                                                                                                      | Page677777                                              |

| <ul> <li>Added minimum recommended values for FChanged minimum recommended input volton Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub> Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to Standard new parameters AUX SUPPLY CUR</li> <li>Added new conditions in Switching Charact</li> <li>Added Reference to the Calculator tool</li> <li>Changed Positive and negative current limit</li> <li>Added reference to operation from voltages</li> </ul>                                                                                                                                                                                                                  | RD <sub>1</sub> and RD <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page677777                                              |

| <ul> <li>Added minimum recommended values for FChanged minimum recommended input voltoners. Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub>.</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to Y</li> <li>Added new parameters AUX SUPPLY CUR</li> <li>Added new conditions in Switching Charact</li> <li>Added Reference to the Calculator tool</li> <li>Changed Positive and negative current limit</li> <li>Added reference to table of device functions</li> </ul>                                                                                                                                                                                          | RD <sub>1</sub> and RD <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page67777                                               |

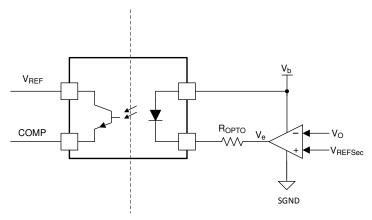

| <ul> <li>Added minimum recommended values for FChanged minimum recommended input volitions.</li> <li>Changed minimum recommended input volitions.</li> <li>Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub>.</li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA.</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub>.</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub>.</li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub>.</li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v.</li> <li>Changed parameter name HC_BLK_TH to added new parameters AUX SUPPLY CUR.</li> <li>Added new conditions in Switching Charact.</li> <li>Added Reference to the Calculator tool</li> <li>Changed Positive and negative current limit.</li> <li>Added reference to operation from voltages.</li> <li>Added reference to table of device functions.</li> <li>Changed Parameter name V<sub>REF</sub> to V<sub>REFSec</sub>.</li> </ul> | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DEFESET and I <sub>BiasOffset</sub> A to 54-μA.  at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub> A-OS  Value from 16.6V to 16V.  V <sub>HC_BLK_TH</sub> RRENT LIMIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , τ <sub>AuxSns</sub> teristics for t <sub>ON</sub> It shown to be affected by LEB signal.  It shows to be affected by LEB signal.  It shows to avoid confusion with primary reference voltage                                                               | Page                                                    |

| <ul> <li>Added minimum recommended values for FChanged minimum recommended input volton Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>, I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub>.</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter V<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to added new parameters AUX SUPPLY CUR</li> <li>Added new conditions in Switching Charact</li> <li>Added Reference to the Calculator tool</li> <li>Changed Positive and negative current limit</li> <li>Added reference to operation from voltages</li> <li>Added reference to table of device functions</li> <li>Changed Parameter name V<sub>REF</sub> to V<sub>REFSec</sub></li> <li>Changed Implied minimum value of t<sub>D</sub> from</li> </ul>                  | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DEFESET and I <sub>BiasOffset</sub> A to 54-μA.  at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub> Value from 16.6V to 16V.  V <sub>HC_BLK_TH</sub> RENT LIMIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , τ <sub>AuxSns</sub> teristics for t <sub>ON</sub> It shown to be affected by LEB signal.  It shows to be affected by LEB signal.  It shows to avoid confusion with primary reference voltage  It o avoid confusion with primary reference voltage  O-ns to 30-ns. | Page                                                    |

| <ul> <li>Added minimum recommended values for FC Changed minimum recommended input volton Added current limit parameters K<sub>CBC1</sub>, V<sub>CSC</sub></li> <li>Changed typical value of I<sub>SLOPE</sub> from 50-µA</li> <li>Added parameter names for some items that V<sub>RESTh3</sub> V<sub>RTReg</sub>, V<sub>RTSync</sub>,I<sub>COSsrEn</sub>, I<sub>AUX(LIM)</sub>.</li> <li>Changed parameter name V<sub>RES</sub> to V<sub>RESTh1</sub></li> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PWM</sub></li> <li>Changed parameter v<sub>AUX_UVLO</sub> maximum v</li> <li>Changed parameter name HC_BLK_TH to S</li> <li>Added new parameters AUX SUPPLY CUR</li> <li>Added new conditions in Switching Charact</li> <li>Added Reference to the Calculator tool</li> <li>Changed Positive and negative current limit</li> <li>Added reference to table of device functions</li> <li>Changed Parameter name V<sub>REF</sub> to V<sub>REFSec</sub></li> <li>Changed Implied minimum value of RD1/RD</li> <li>Added note that minimum value of RD1/RD</li> </ul>                     | RD <sub>1</sub> and RD <sub>2</sub> tage from 18V to 16V.  DEFESET and I <sub>BiasOffset</sub> A to 54-μA.  at had none: I <sub>OVL</sub> , V <sub>SSSecEn</sub> , V <sub>SSREn</sub> , t <sub>CSLSG</sub> , t <sub>CSBLK</sub> , V <sub>R</sub> A-OS  Value from 16.6V to 16V.  V <sub>HC_BLK_TH</sub> RRENT LIMIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , τ <sub>AuxSns</sub> teristics for t <sub>ON</sub> It shown to be affected by LEB signal.  It shows to be affected by LEB signal.  It shows to avoid confusion with primary reference voltage                                                               | Page                                                    |

#### www.ti.com

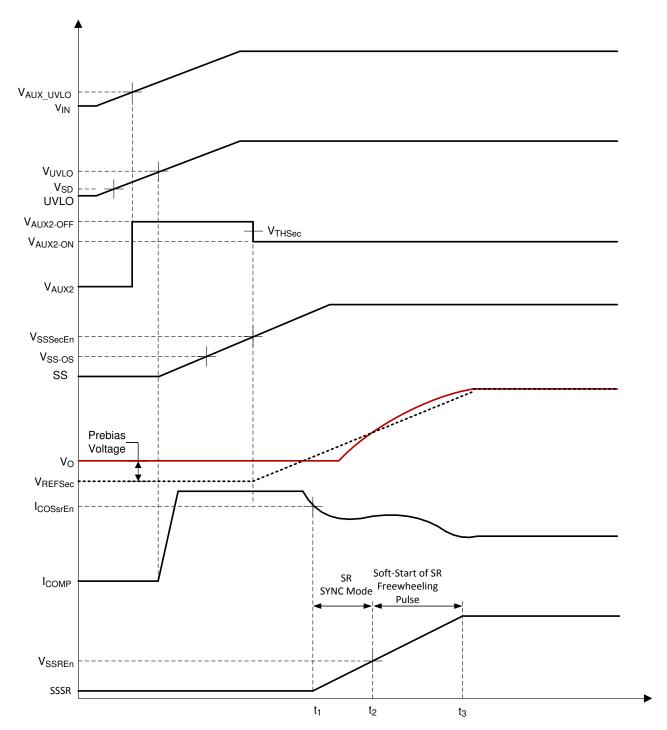

| • | Changed values to parameter names. V <sub>REF</sub> changed to V <sub>REFSec</sub> , TH changed to V <sub>THSec</sub> | <mark>2</mark> 1 |

|---|-----------------------------------------------------------------------------------------------------------------------|------------------|

| • | Changed values to parameter names. I <sub>COMP</sub> is graphed instead of V <sub>COMP</sub>                          | 21               |

| • | Changed V <sub>COMP</sub> to I <sub>COMP</sub>                                                                        |                  |

| • | Changed and expanded Section: 'Enhanced Cycle-by-Cycle Current Limiting with Pulse Matching'                          |                  |

| • | Changed and expanded Section: 'Reverse Current Protection'.                                                           |                  |

| • | Added Section: 'CBC Threshold Accuracy'                                                                               |                  |

| • | Changed values to parameter names.                                                                                    |                  |

| • | Changed Section: 'ON_OFF Pin' to 'Over-Voltage / Latch (ON_OFF Pin)'. Values replaced by parameter                    |                  |

|   | names.                                                                                                                | 33               |

|   | Changed Section: 'Constant On-Time Control' to 'Auxiliary Constant On-Time Control'                                   |                  |

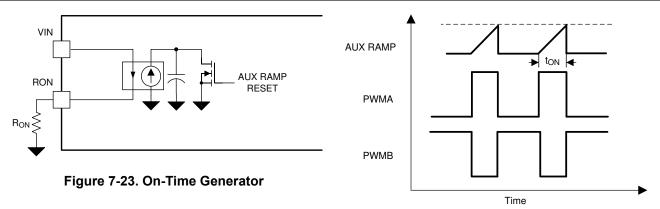

|   | Changed Section: 'On-Time Generator' to 'Auxiliary On-Time Generator'                                                 |                  |

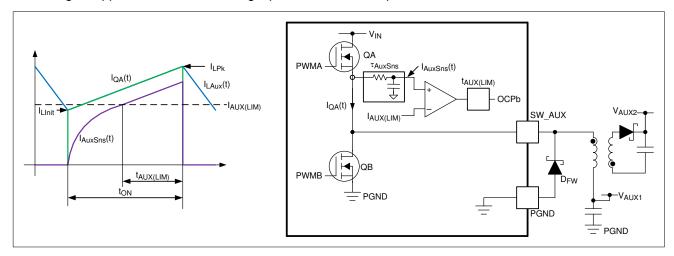

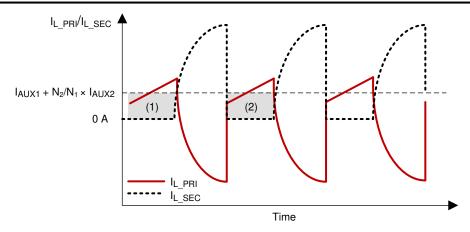

|   | Added method to calculate peak Auxiliary transformer current. External schottky recommended to improve                |                  |

| Ī | Auxiliary efficiency during ASYNCH mode.                                                                              |                  |

|   | Deleted Section: 'Ripple Configuration Types'                                                                         |                  |

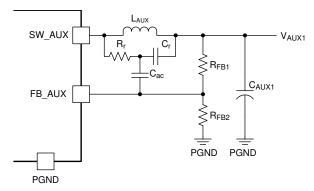

|   | Added Section: 'Auxiliary Ripple Configuration and Control'.                                                          |                  |

|   |                                                                                                                       |                  |

| • | Changed values to parameter names.                                                                                    |                  |

| • | Changed C26 from 330-pF to 47-pF, R29 from 165-kΩ to 220-kΩ. Added D11                                                |                  |

| • | Changed voltage targets for auxiliary output voltage from 12.6 V / 9 V to 11.9 V / 8.5 V.                             |                  |

| • | Added reference to Excel Calculator Tool.                                                                             |                  |

| • | Added restriction on use of TL431 to implement secondary side error amplifier                                         |                  |

| • | Added reference to Power Stage Designer Tool.                                                                         |                  |

| • | Changed values to parameter names. R <sub>UV1</sub> and <sub>RUV2</sub> replace R <sub>1</sub> and R <sub>2</sub>     | 45               |

| • | Changed Section: 'ON_OFF Pin Voltage Divider Selection' to 'Over Voltage / Latch (ON_OFF Pin) Voltage                 |                  |

|   | Divider Selection'.                                                                                                   |                  |

| • | Added new Section: 'Half-Bridge Power Stage Design'                                                                   | 47               |

| • | Changed and expanded Section: 'Current Limit'                                                                         |                  |

| • | Changed calculation of Auxiliary transformer inductance.                                                              | 52               |

| • | Changed calculated value for R <sub>ON</sub> resistor.                                                                |                  |

| • | Changed calculated value of Auxiliary primary output capacitor value.                                                 |                  |

| • | Changed calculation of secondary output capacitor. Now uses ripple peak amplitude not peak-to-peak                    |                  |

|   | amplitude                                                                                                             | 54               |

| • | Changed calculation of Auxiliary Feedback component values.                                                           |                  |

|   | Changed expression for I <sub>COMP</sub> to fix error.                                                                |                  |

|   | Changed layout diagram to include external schottky diode connected between PGND and SW_AUX pins                      |                  |

|   | 58                                                                                                                    | <i>.</i>         |

| _ |                                                                                                                       |                  |

| С |                                                                                                                       | Page             |

| • | Changed marketing status from Advance Information to initial release.                                                 | 1                |

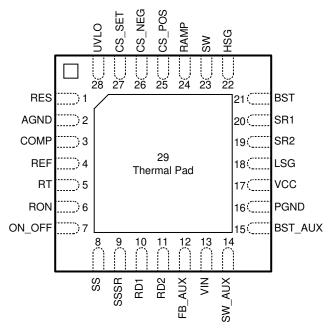

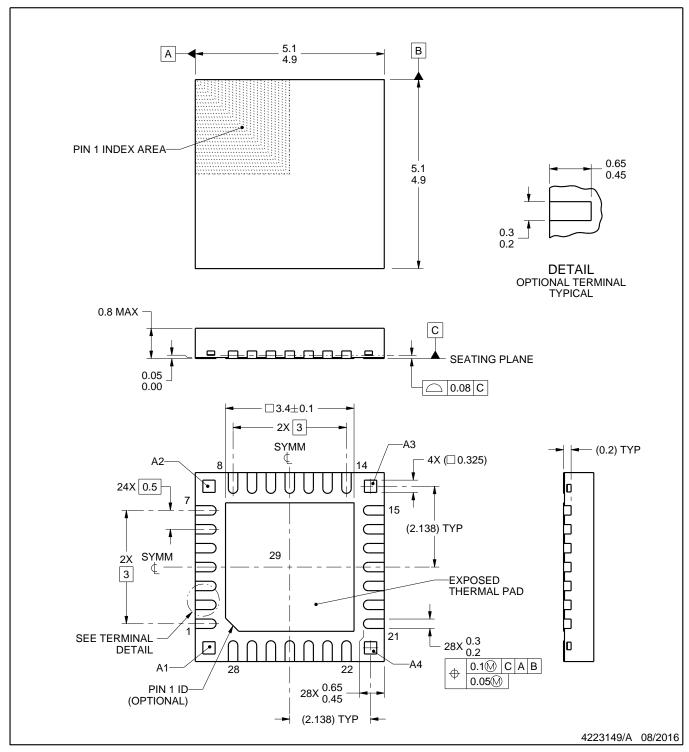

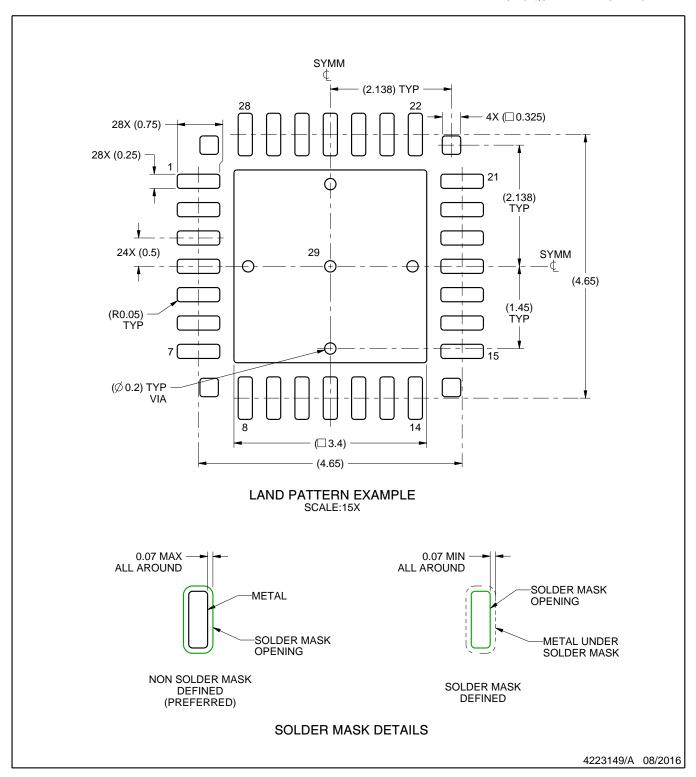

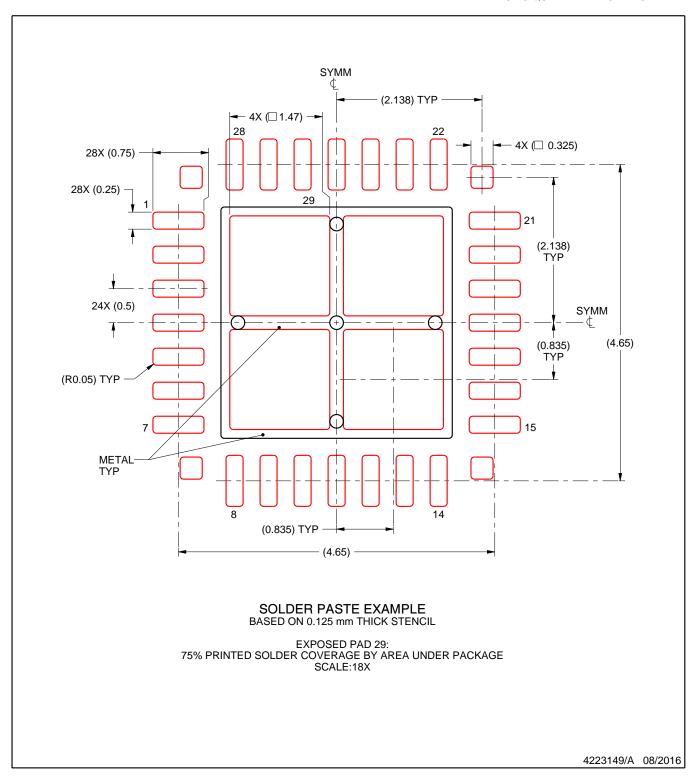

# **5 Pin Configuration and Functions**

Figure 5-1. RJB Package, 28-Pin WQFN (Top View)

Table 5-1. Pin Functions

| PIN     |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                    |

|---------|-----|---------------------|----------------------------------------------------------------|

| NAME    | NO. | ITPE                | DESCRIPTION                                                    |

| AGND    | 2   | G                   | Analog ground                                                  |

| BST     | 21  | I                   | Half-bridge high-side gate drive bootstrap                     |

| BST_AUX | 15  | I                   | Auxiliary supply high-side gate drive bootstrap                |

| COMP    | 3   | I                   | Control current input to half-bridge PWM comparator            |

| CS_NEG  | 26  | I                   | Current sense amplifier negative input terminal                |

| CS_POS  | 25  | I                   | Current sense amplifier positive input terminal                |

| CS_SET  | 27  | I                   | Current limit setting                                          |

| FB_AUX  | 12  | I                   | Auxiliary supply output voltage feedback                       |

| HSG     | 22  | 0                   | Half-bridge high-side MOSFET output driver                     |

| LSG     | 18  | 0                   | Half-bridge low-side MOSFET output driver                      |

| ON_OFF  | 7   | I                   | Configurable for over voltage protection (OVP) or latch mode   |

| PGND    | 16  | G                   | Power ground                                                   |

| RAMP    | 24  | I                   | RAMP signal input to half-bridge PWM comparator                |

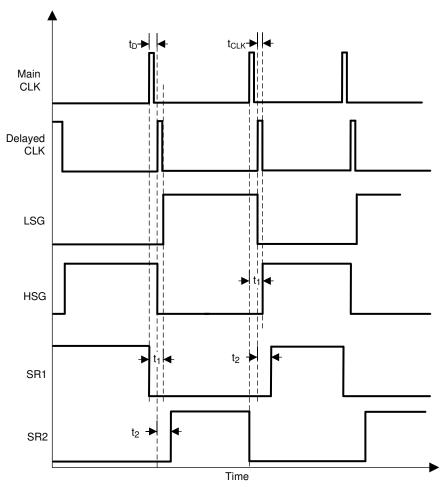

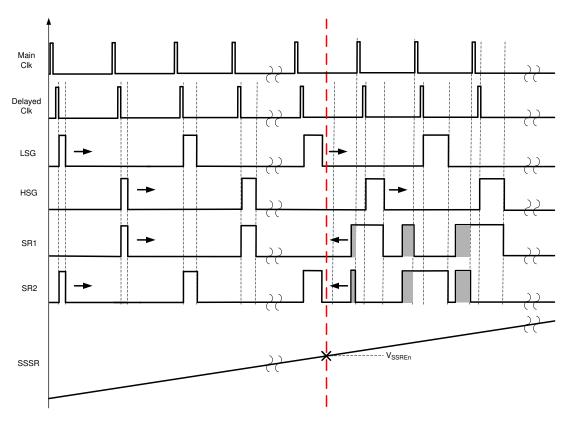

| RD1     | 10  | I                   | Synchronous rectifier trailing-edge delay                      |

| RD2     | 11  | I                   | Synchronous rectifier leading-edge delay                       |

| REF     | 4   | 0                   | 5-V reference regulator output                                 |

| RES     | 1   | I                   | Hiccup mode restart timer                                      |

| RON     | 6   | I                   | Auxiliary supply on-time control                               |

| RT/SYNC | 5   | ı                   | Oscillator frequency control or external clock synchronization |

| SR1     | 20  | 0                   | Synchronous rectifier PWM control output                       |

| SR2     | 19  | 0                   | Synchronous rectifier PWM control output                       |

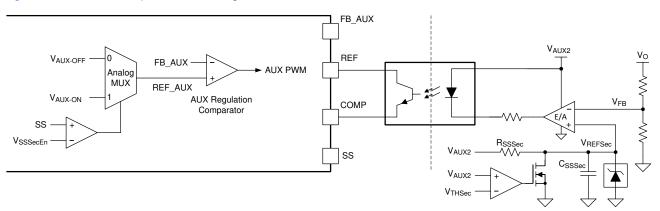

| SS      | 8   | I                   | Soft-start input                                               |

| SSSR    | 9   | I                   | Synchronous rectifier soft-start input                         |

| SW      | 23  | I                   | Half-bridge switch node                                        |

# **Table 5-1. Pin Functions (continued)**

|        |    | TYPE <sup>(1)</sup> | DESCRIPTION                  |  |  |

|--------|----|---------------------|------------------------------|--|--|

|        |    | ITPE                | DESCRIPTION                  |  |  |

| SW_AUX | 14 | I                   | Auxiliary supply switch node |  |  |

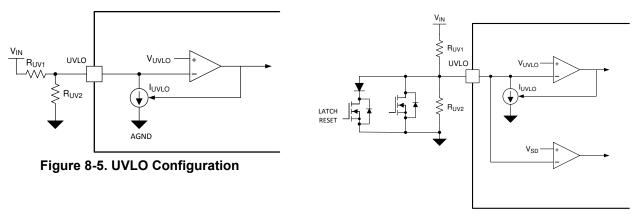

| UVLO   | 28 | I                   | Input undervoltage lockout   |  |  |