LM48823, LM48823TLEVAL

www.ti.com

#### SNAS464E - JUNE 2008 - REVISED OCTOBER 2010

## LM48823

**Boomer**<sup>®</sup> Audio Power Amplifier Series

## Mono, Bridge-Tied Load, Ceramic Speaker Driver with I<sup>2</sup>C Volume Control and Reset

Check for Samples: LM48823, LM48823TLEVAL

### FEATURES

- **Integrated Charge Pump**

- **Bridge-Tied Load Output**

- **High PSRR**

- I<sup>2</sup>C Volume and Mode Control

- **Reset Input**

- **Advanced Click-and-Pop Suppression**

- Low Supply Current

- **Minimum External Components**

- **Micro-Power Shutdown**

- Available in Space-Saving 16-Bump DSBGA Package

## APPLICATIONS

- **Cell Phones**

- Smart Phones

- **Portable Media Devices**

- **Notebook PCs**

### **KEY SPECIFICATIONS**

- Output Voltage at  $V_{DD}$  = 4.2V,  $R_L$  = 2.2 $\mu$ F + 15 $\Omega$ THD+N  $\leq$  1%: 5.4V<sub>RMS</sub> (typ)

- Quiescent Power Supply Current at 4.2V: 3.3mA (typ)

- PSRR at 217Hz: 93dB (typ)

- Shutdown Current: 0.01µA (typ)

### DESCRIPTION

The LM48823 is a single supply, mono, ceramic speaker driver with an integrated charge-pump, designed for portable devices, such as cell phones, where board space is at a premium. The LM48823 charge pump allows the device to deliver 5.4V<sub>RMS</sub> from a single 4.2V supply.

The LM48823 features high power supply rejection ratio (PSRR), 93dB at 217Hz, allowing the device to operate in noisy environments without additional power supply conditioning. Flexible power supply requirements allow operation from 2.0V to 4.5V. The LM48823 features an active low reset input that reverts the device to its default state. Additionally, the LM48823 features a 32-step I<sup>2</sup>C volume control. The low power Shutdown mode reduces supply current consumption to 0.01µA.

The LM48823's superior click and pop suppression eliminates audible transients on power-up/down and during shutdown. The LM48823 is available in an ultra-small 16-bump DSBGA package (2mmx2mm).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

SNAS464E - JUNE 2008-REVISED OCTOBER 2010

www.ti.com

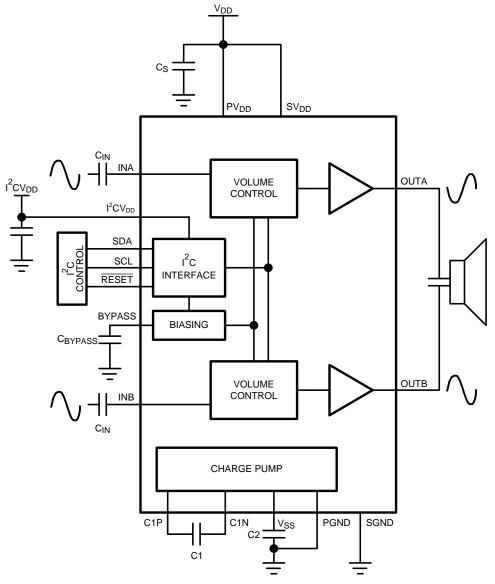

### **Typical Application**

Figure 1. Typical Audio Amplifier Application Circuit

SNAS464E -JUNE 2008-REVISED OCTOBER 2010

#### www.ti.com

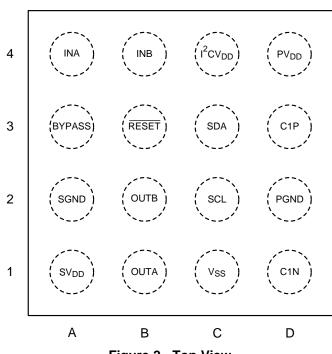

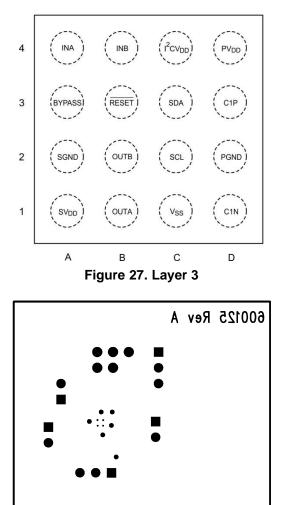

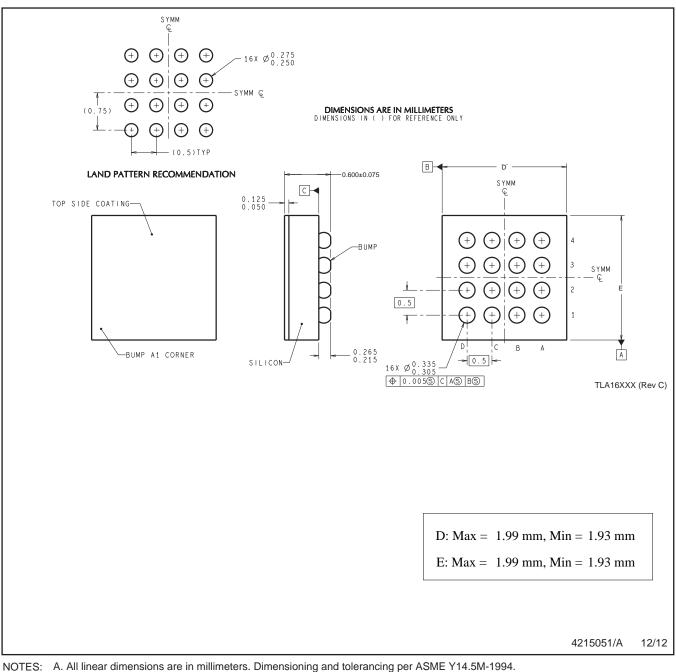

#### **Connection Diagram**

Figure 2. Top View See Package Number YZR 16

#### **Bump Descriptions**

| Pin Designator | Pin Name                        | Pin Function                                                                                                                         |

|----------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| A1             | SV <sub>DD</sub>                | Signal Power Supply                                                                                                                  |

| A2             | SGND                            | Signal Ground                                                                                                                        |

| A3             | BYPASS                          | Amplifier Reference Bypass                                                                                                           |

| A4             | INA                             | Amplifier Inverting input A                                                                                                          |

| B1             | OUTA                            | Amplifier Inverting output A                                                                                                         |

| B2             | OUTB                            | Amplifier Non-Inverting Output B                                                                                                     |

| B3             | RESET                           | Active Low Reset Input. Connect to $V_{\text{DD}}$ for normal operation. Toggle between $V_{\text{DD}}$ and GND to reset the device. |

| B4             | INB                             | Amplifier Non-Inverting Input B                                                                                                      |

| C1             | V <sub>SS</sub>                 | Charge Pump Output                                                                                                                   |

| C2             | SCL                             | I <sup>2</sup> C Serial Clock Input                                                                                                  |

| C3             | SDA                             | I <sup>2</sup> C Serial Data Input                                                                                                   |

| C4             | I <sup>2</sup> CV <sub>DD</sub> | I <sup>2</sup> C Supply Voltage                                                                                                      |

| D1             | C1N                             | Charge Pump Flying Capacitor Negative Terminal                                                                                       |

| D2             | PGND                            | Power Ground                                                                                                                         |

| D3             | C1P                             | Charge Pump Flying Capacitor Positive Terminal                                                                                       |

| D4             | PV <sub>DD</sub>                | Power Supply                                                                                                                         |

## YZR Package 2mm x 2mm x 0.8mm

#### SNAS464E -JUNE 2008-REVISED OCTOBER 2010

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### ABSOLUTE MAXIMUM RATINGS (1) (2)

| Supply Voltage <sup>(1)</sup>      | 5.25V                          |

|------------------------------------|--------------------------------|

| Storage Temperature                | -65°C to +150°C                |

| Input Voltage                      | -0.3V to V <sub>DD</sub> +0.3V |

| Power Dissipation <sup>(3)</sup>   | Internally Limited             |

| ESD Rating <sup>(4)</sup>          | 8kV                            |

| ESD Rating <sup>(5)</sup>          | 250V                           |

| Junction Temperature               | 150°C                          |

| Thermal Resistance                 |                                |

| θ <sub>JA</sub> (typ) - (TLA1611A) | 63.2°C/W                       |

(1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

(3) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation is P<sub>DMAX</sub> = (T<sub>JMAX</sub> - T<sub>A</sub>) / θ<sub>JA</sub> or the number given in *Absolute Maximum Ratings*, whichever is lower.

(4) Human body model, applicable std. JESD22-A114C.

(5) Machine model, applicable std. JESD22-A115-A.

### **OPERATING RATINGS**

| Temperature Range                     |                                                                        |

|---------------------------------------|------------------------------------------------------------------------|

| $T_{MIN} \le T_A \le T_{MAX}$         | $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                              |

| Supply Voltage                        |                                                                        |

| PV <sub>DD</sub> and SV <sub>DD</sub> | $2.0V \le V_{DD} \le 4.5V$                                             |

| I <sup>2</sup> CV <sub>DD</sub>       | $1.8 \text{V} \leq \text{I}^2 \text{CV}_{\text{DD}} \leq 4.5 \text{V}$ |

<sup>(2)</sup> The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

www.ti.com

#### SNAS464E – JUNE 2008 – REVISED OCTOBER 2010

## AUDIO AMPLIFIER ELECTRICAL CHARACTERISTICS $V_{DD} = 4.2V$ <sup>(1) (2)</sup>

The following specifications apply for  $A_V = 6dB$ ,  $R_L = 2.2\mu F + 15\Omega$ ,  $C1 = C2 = 2.2\mu F$ , f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

|                 |                                         |                                                 | LM                 | 48823   | Unite    |                   |

|-----------------|-----------------------------------------|-------------------------------------------------|--------------------|---------|----------|-------------------|

| Symbol          | Parameter                               | Conditions                                      |                    | Typical | Limits   | Units<br>(Limits) |

| I <sub>DD</sub> | Quiescent Power Supply<br>Current       | $V_{IN} = 0V, R_L = \infty$                     | 3.3                | 4.3     | mA (max) |                   |

| I <sub>SD</sub> | Shutdown Current                        | Shutdown Enabled                                |                    | 0.01    | 1        | µA (max)          |

| V <sub>OS</sub> | Differential Output Offset<br>Voltage   | V <sub>IN</sub> = 0V                            |                    | 0.5     | 3        | mV (max)          |

| VIH             | Logic High Input Threshold              | RESET                                           |                    |         | 1.4      | V (min)           |

| V <sub>IL</sub> |                                         | RESET                                           |                    |         | 0.4      | V (max)           |

| ^               | Gain                                    | Minimum Gain Setting                            |                    | -70     |          | dB                |

| A <sub>V</sub>  | Gain                                    | Maximum Gain Setting                            | 24                 |         | dB       |                   |

|                 |                                         | Maximum Cain Satting                            | 9                  | 7       | kΩ (min) |                   |

| Р               | Innut Desistance                        | Maximum Gain Setting                            | 9                  | 11      | kΩ (max) |                   |

| R <sub>IN</sub> | Input Resistance                        | Minimum Gain Setting                            | 80                 | 64      | kΩ (min) |                   |

|                 |                                         | Minimum Gain Setting                            | 80                 | 96      | kΩ (max) |                   |

| V               |                                         | R <sub>1</sub> = 2.2μF+15Ω, THD+N = 1%          | f = 1kHz           | 5.4     |          | V <sub>RMS</sub>  |

| Vo              | Output Voltage                          | $R_L = 2.2\mu r + 15\Omega$ , $1 HD + N = 1\%$  | f = 5kHz           | 3.1     |          | V <sub>RMS</sub>  |

| THD+N           | Total Harmonic Distortion +<br>Noise    | $V_{O} = 4V_{RMS}$                              | $V_{O} = 4V_{RMS}$ |         |          | %                 |

|                 | Power Supply Rejection                  | $V_{RIPPLE} = 200 m V_{P-P}$ Sine, Inputs AC    | f = 217Hz          | 93      | 82       | dB (min)          |

| PSRR Ratio      | GND, $C_{IN} = 1\mu F$ , input referred | f = 1kHz                                        | 93                 |         | dB       |                   |

| SNR             | Signal-to-Noise-Ratio                   | $P_{OUT} = 40$ mW, $R_L = 16\Omega$<br>f = 1kHz |                    | 119     |          | dB                |

| ∈os             | Output Noise                            | AV = 4dB, Input Referred, A-weighted            | Filter             | 5.5     |          | μV                |

| T <sub>WU</sub> | Wake-Up Time                            |                                                 |                    | 200     |          | μs                |

(1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

(2) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

(3) Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the *Recommended Operation Conditions* at the time of product characterization and are not ensured.

(4) Datasheet min/max specification limits are specified by test or statistical analysis.

SNAS464E – JUNE 2008 – REVISED OCTOBER 2010

www.ti.com

## I<sup>2</sup>C INTERFACE CHARACTERISTICS $V_{DD}$ = 3.0V <sup>(1) (2)</sup>

The following specifications apply for  $A_V = 6dB$ ,  $R_L = 2.2\mu F + 15\Omega$ ,  $C1 = C2 = 2.2\mu F$ , f = 1kHz, unless otherwise specified. Limits apply for  $T_A = 25^{\circ}C$ .

| Symbol          | Desembles                  | Conditions | L                      | Units                                 |          |

|-----------------|----------------------------|------------|------------------------|---------------------------------------|----------|

| Symbol          | Parameter                  | Conditions | Typical <sup>(3)</sup> | Limits <sup>(4)</sup>                 | (Limits) |

| t <sub>1</sub>  | SCL period                 |            |                        | 2.5                                   | µs (min) |

| t <sub>2</sub>  | SDA Setup Time             |            |                        | 100                                   | ns (min) |

| t <sub>3</sub>  | SDA Stable Time            |            |                        | 0                                     | ns (min) |

| t <sub>4</sub>  | Start Condition Time       |            |                        | 100                                   | ns (min) |

| t <sub>5</sub>  | Stop Condition Time        |            |                        | 100                                   | ns (min) |

| V <sub>IH</sub> | Logic High Input Threshold |            |                        | 0.7 x I <sup>2</sup> CV <sub>DD</sub> | V (min)  |

| V <sub>IL</sub> | Logic Low Input Threshold  |            |                        | 0.3 x I <sup>2</sup> CV <sub>DD</sub> | V (max)  |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. All voltages are measured with respect to the ground pin, unless otherwise specified.

(2) The Electrical Characteristics tables list ensured specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not ensured.

(3) Typical values represent most likely parametric norms at T<sub>A</sub> = +25°C, and at the *Recommended Operation Conditions* at the time of product characterization and are not ensured.

(4) Datasheet min/max specification limits are specified by test or statistical analysis.

6

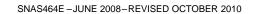

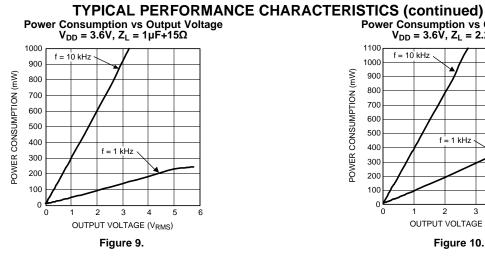

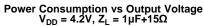

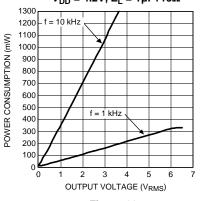

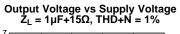

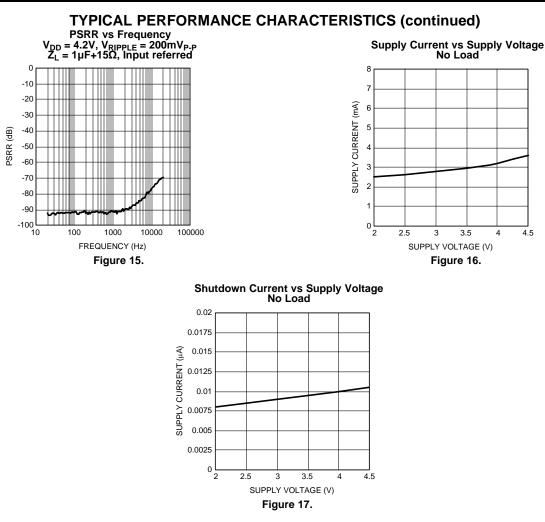

TYPICAL PERFORMANCE CHARACTERISTICS

10

www.ti.com

#### SNAS464E -JUNE 2008-REVISED OCTOBER 2010

Figure 10.

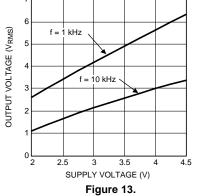

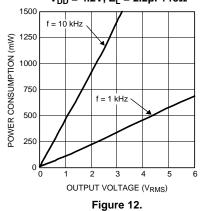

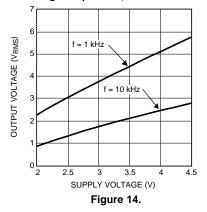

Power Consumption vs Output Voltage  $V_{DD}$  = 4.2V, Z<sub>L</sub> = 2.2µF+15Ω

Output Voltage vs Supply Voltage  $Z_L = 2.2\mu$ F+15 $\Omega$ , THD+N = 1%

8

SNAS464E - JUNE 2008-REVISED OCTOBER 2010

SNAS464E -JUNE 2008-REVISED OCTOBER 2010

www.ti.com

### **APPLICATION INFORMATION**

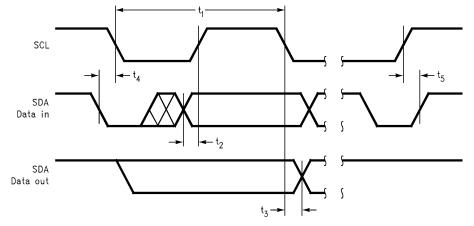

#### I<sup>2</sup>C COMPATIBLE INTERFACE

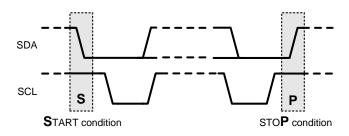

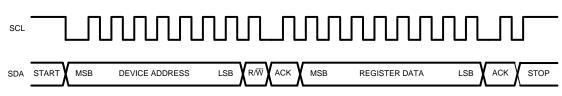

The LM48823 is controlled through an I<sup>2</sup>C compatible serial interface that consists of a serial data line (SDA) and a serial clock (SCL). The clock line is uni-directional. The data line is bi-directional (open drain). The LM48823 and the master can communicate at clock rates up to 400kHz. Figure 18 shows the I<sup>2</sup>C interface timing diagram. Data on the SDA line must be stable during the HIGH period of SCL. The LM48823 is a transmit/receive slave-only device, reliant upon the master to generate the SCL signal. Each transmission sequence is framed by a START condition and a STOP condition (Figure 19). Each data word, device address and data, transmitted over the bus is 8 bits long and is always followed by an acknowledge pulse (Figure 20). The LM48823 device address is 1110110.

### I<sup>2</sup>C BUS FORMAT

The I<sup>2</sup>C bus format is shown in Figure 20. The START signal, the transition of SDA from HIGH to LOW while SCL is HIGH, is generated, alerting all devices on the bus that a device address is being written to the bus.

The 7-bit device address is written to the bus, most significant bit (MSB) first, followed by the R/W bit. R/W = 0 indicates the master is writing to the slave device, R/W = 1 indicates the master wants to read data from the slave device. Set R/W = 0; the LM48823 is a WRITE-ONLY device and will not respond to the R/W = 1. The data is latched in on the rising edge of the clock. Each address bit must be stable while SCL is HIGH. After the last address bit is transmitted, the master device releases SDA, during which time, an acknowledge clock pulse is generated by the slave device. If the LM48823 receives the correct address, the device pulls the SDA line low, generating an acknowledge bit (ACK).

Once the master device registers the ACK bit, the 8-bit register data word is sent. Each data bit should be stable while SCL is HIGH. After the 8-bit register data word is sent, the LM48823 sends another ACK bit. Following the acknowledgement of the register data word, the master issues a STOP bit, allowing SDA to go high while SCL is high.

Figure 18. I<sup>2</sup>C Timing Diagram

Figure 19. Start and Stop Diagram

SNAS464E – JUNE 2008 – REVISED OCTOBER 2010

Figure 20. Example Write Sequence

#### **Table 1. Device Address**

|              | B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 R/W |

|--------------|----|----|----|----|----|----|----|--------|

| Chip Address | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 0      |

**Table 2. Mode Control Registers**

| Register Name | B7   | B6   | B5   | B4   | B3   | B2 | B1       | B0       |

|---------------|------|------|------|------|------|----|----------|----------|

| Mode Control  | VOL4 | VOL3 | VOL2 | VOL1 | VOL0 | 0  | ENABLE_A | ENABLE_B |

#### **GENERAL AMPLIFIER FUNCTION**

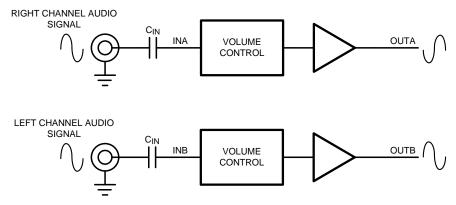

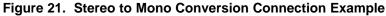

The LM48823 is a ceramic speaker driver that utilizes TI's inverting charge pump technology to deliver over  $15V_{P-P}$  to a  $2.2\mu$ F ceramic speaker while operating from a single 4.2V supply. The LM48823 features a unique input stage that converts two single-ended audio signals into a mono BTL output. This stereo to mono conversion is useful in applications where a stereo audio source is driving a single ceramic speaker, such as a ringer on a cellular phone. Connect INA and INB as shown in Figure 21 for the stereo-to-mono conversion. When the LM48823 is used with a single-ended mono audio source, connect both INA and INB to the audio source as shown in Figure 22.

## LM48823, LM48823TLEVAL

SNAS464E – JUNE 2008 – REVISED OCTOBER 2010

### VOLUME CONTROL

| Volume Step | VOL4 | VOL3 | VOL2 | VOL1 | VOL0 | Gain (dB) |

|-------------|------|------|------|------|------|-----------|

| 1           | 0    | 0    | 0    | 0    | 0    | -70       |

| 2           | 0    | 0    | 0    | 0    | 1    | -56       |

| 3           | 0    | 0    | 0    | 1    | 0    | -46       |

| 4           | 0    | 0    | 0    | 1    | 1    | -38       |

| 5           | 0    | 0    | 1    | 0    | 0    | -32       |

| 6           | 0    | 0    | 1    | 0    | 1    | -28       |

| 7           | 0    | 0    | 1    | 1    | 0    | -24       |

| 8           | 0    | 0    | 1    | 1    | 1    | -21       |

| 9           | 0    | 1    | 0    | 0    | 0    | -18       |

| 10          | 0    | 1    | 0    | 0    | 1    | -15       |

| 11          | 0    | 1    | 0    | 1    | 0    | -12       |

| 12          | 0    | 1    | 0    | 1    | 1    | -10       |

| 13          | 0    | 1    | 1    | 0    | 0    | -8        |

| 14          | 0    | 1    | 1    | 0    | 1    | 6         |

| 15          | 0    | 1    | 1    | 1    | 0    | -4        |

| 16          | 0    | 1    | 1    | 1    | 1    | -2        |

| 17          | 1    | 0    | 0    | 0    | 0    | 0         |

| 18          | 1    | 0    | 0    | 0    | 1    | 2         |

| 19          | 1    | 0    | 0    | 1    | 0    | 4         |

| 20          | 1    | 0    | 0    | 1    | 1    | 6         |

| 21          | 1    | 0    | 1    | 0    | 0    | 8         |

| 22          | 1    | 0    | 1    | 0    | 1    | 10        |

| 23          | 1    | 0    | 1    | 1    | 0    | 12        |

| 24          | 1    | 0    | 1    | 1    | 1    | 14        |

| 25          | 1    | 1    | 0    | 0    | 0    | 16        |

| 26          | 1    | 1    | 0    | 0    | 1    | 18        |

| 27          | 1    | 1    | 0    | 1    | 0    | 19        |

| 28          | 1    | 1    | 0    | 1    | 1    | 20        |

| 29          | 1    | 1    | 1    | 0    | 0    | 21        |

| 30          | 1    | 1    | 1    | 0    | 1    | 22        |

| 31          | 1    | 1    | 1    | 1    | 0    | 23        |

| 32          | 1    | 1    | 1    | 1    | 1    | 24        |

#### **Table 3. Volume Control**

### SHUTDOWN FUNCTION

The LM48823 features a low-power shutdown mode that disables the device, lowering the quiescent current to  $0.01\mu$ A. Set bits B1 (ENABLE\_A) and B2 (ENABLE\_B) to 0 to disable the amplifiers and charge pump. Set both ENABLE\_A and ENABLE\_B to 1 for normal operation. Shutdown mode does not clear the l<sup>2</sup>C register. When reenabled, the device returns to its previous volume setting. To clear the l<sup>2</sup>C register, either remove power from the device, or toggle RESET (see *RESET* section).

### RESET

The LM48823 features an active low reset input. Driving RESET low clears the I<sup>2</sup>C register. Volume control is set to 00000 (-70dB) and both ENABLE\_A and ENABLE\_B are set to 0, disabling the device. While RESET is low, the LM48823 ignores any I<sup>2</sup>C data. After the device is reset, and RESET is driven high, the LM48823 remains in shutdown mode with the volume set to -70dB. Re-enable the device by writing to the I<sup>2</sup>C register.

www.ti.com

SNAS464E - JUNE 2008 - REVISED OCTOBER 2010

www.ti.com

#### **PROPER SELECTION OF EXTERNAL COMPONENTS**

#### Power Supply Bypassing/Filtering

Proper power supply bypassing is critical for low noise performance and high PSRR. Place the supply bypass capacitors as close to the device as possible. Place a  $1\mu$ F ceramic capacitor from V<sub>DD</sub> to GND. Additional bulk capacitance may be added as required.

#### **Bypass Capacitor Selection**

The BYPASS capacitor, C<sub>BYPASS</sub>, improves PSRR, noise rejection and output offset. For best results, use a capacitor of identical value to the input coupling capacitors

#### Charge Pump Capacitor Selection

Use low ESR ceramic capacitors (less than  $100m\Omega$ ) for optimum performance.

#### Charge Pump Flying Capacitor (C1)

The flying capacitor (C1) affects the load regulation and output impedance of the charge pump. A C1 value that is too low results in a loss of current drive, leading to a loss of amplifier headroom. A higher valued C1 improves load regulation and lowers charge pump output impedance to an extent. Above  $2.2\mu$ F, the R<sub>DS(ON)</sub> of the charge pump switches and the ESR of C1 and C2 dominate the output impedance. A lower value capacitor can be used in systems with low maximum output power requirements.

#### Charge Pump Hold Capacitor (C2)

The value and ESR of the hold capacitor (C2) directly affects the ripple on CPV<sub>SS</sub>. Increasing the value of C2 reduces output ripple. Decreasing the ESR of C2 reduces both output ripple and charge pump output impedance. A lower value capacitor can be used in systems with low maximum output power requirements.

#### Input Capacitor Selection

Input capacitors block the DC component of the audio signal, eliminating any conflict between the DC component of the audio source and the bias voltage of the LM48823. The input capacitors create a high-pass filter with the input resistors  $R_{IN}$ . The -3dB point of the high pass filter is found using Equation 1.

$f = 1 / 2\pi R_{IN}C_{IN} \quad (Hz)$

where

• the value of R<sub>IN</sub> is given in the Electrical Characteristics table.

(1)

High pass filtering the audio signal helps protect the speakers. When the LM48823 is using a single-ended source, power supply noise on the ground is seen as an input signal. Setting the high-pass filter point above the power supply noise frequencies, 217Hz in a GSM phone, for example, filters out the noise such that it is not amplified and heard on the output. Capacitors with a tolerance of 10% or better are recommended for impedance matching and improved CMRR and PSRR.

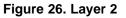

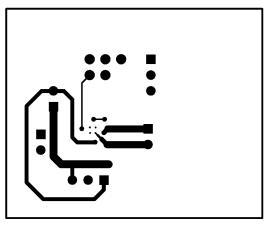

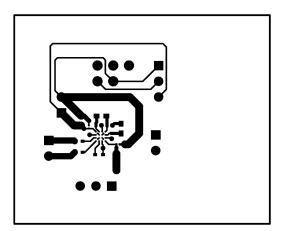

#### PCB LAYOUT GUIDELINES

Minimize trace impedance of the power, ground and all output traces for optimum performance. Voltage loss due to trace resistance between the LM48823 and the load results in decreased output power and efficiency. Trace resistance between the power supply and ground has the same effect as a poorly regulated supply, increased ripple and reduced peak output power. Use wide traces for power supply inputs and amplifier outputs to minimize losses due to trace resistance, as well as route heat away from the device. Proper grounding improves audio performance, minimizes crosstalk between channels and prevents switching noise from interfering with the audio signal. Use of power and ground planes is recommended.

Place all digital components and route digital signal traces as far as possible from analog components and traces. Do not run digital and analog traces in parallel on the same PCB layer. If digital and analog signal lines must cross either over or under each other, ensure that they cross in a perpendicular fashion.

Copyright © 2008–2010, Texas Instruments Incorporated

SNAS464E – JUNE 2008 – REVISED OCTOBER 2010

www.ti.com

## LM48823TL DEMOBOARD BILL OF MATERIALS

| Designator | Quantity | Description                                                                                      |

|------------|----------|--------------------------------------------------------------------------------------------------|

| C1, C2     | 2        | 2.2µF ±10% 10V X5R Ceramic Capacitor (603) Panasonic ECJ-1VB1A225K<br>Murata GRM033R6OJ104KE19D  |

| C3 – C5    | 3        | 1µF ±10% 10V Tantalum Capacitor (402) AVX TACK105M010QTA                                         |

| C6         | 1        | 4.7μF ±10% 6.3V X5R Ceramic Capacitor (603) Panasonic ECJ-1VB0J475K<br>Murata GRM188R6OJ475KE19D |

| C7, C8     | 2        | 0.1µF ±10% 6.3V X5R Ceramic Capacitor (201) Panasonic ECJ-ZEB0J104K<br>Murata GRM188R61A225KE34D |

| JU1 – JU5  | 5        | 2 Pin Header                                                                                     |

| JU6, JU7   | 3        | 2 Pin Header                                                                                     |

| J1         | 1        | 5-Pin I <sup>2</sup> C Header                                                                    |

| LM4823TL   | 1        | LM48823TL (16-Bump DSBGA)                                                                        |

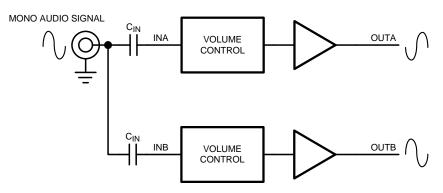

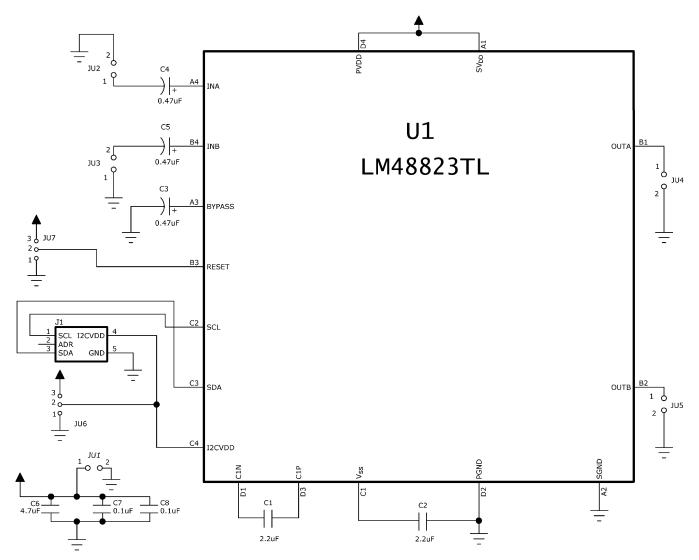

### **DEMO BOARD SCHEMATIC**

www.ti.com

SNAS464E -JUNE 2008-REVISED OCTOBER 2010

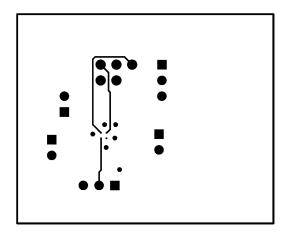

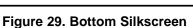

## PC BOARD LAYOUT

Figure 24. Top Silkscreen Layer

Figure 28. Bottom Layer

Figure 25. Top Layer

## LM48823, LM48823TLEVAL

SNAS464E – JUNE 2008 – REVISED OCTOBER 2010

www.ti.com

### **REVISION HISTORY**

| Rev  | Date     | Description                                                   |

|------|----------|---------------------------------------------------------------|

| 1.0  | 06/27/08 | Initial release.                                              |

| 1.01 | 07/15/08 | Edited the Ordering Information table.                        |

| 1.02 | 10/08/10 | Updated some Limits (under Gain) in the Volume Control table. |

24-Sep-2015

## PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|--------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                |              | (4/5)          |         |

| LM48823TL/NOPB   | ACTIVE | DSBGA        | YZR     | 16   | 250     | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM |              | GK6            | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(<sup>6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

24-Sep-2015

## PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

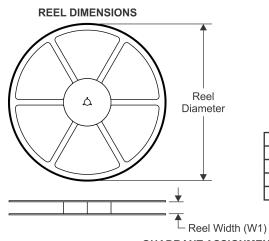

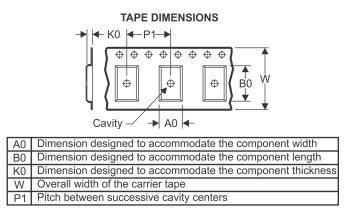

### TAPE AND REEL INFORMATION

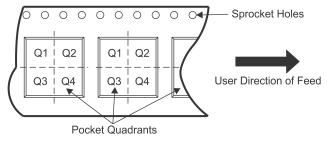

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All | dimensions are nominal |  |

|------|------------------------|--|

|      |                        |  |

| Device         | Package<br>Type | Package<br>Drawing | Pins | SPQ | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|------|-----|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LM48823TL/NOPB | DSBGA           | YZR                | 16   | 250 | 178.0                    | 8.4                      | 2.08       | 2.08       | 0.76       | 4.0        | 8.0       | Q1               |

TEXAS INSTRUMENTS

www.ti.com

## PACKAGE MATERIALS INFORMATION

2-Sep-2015

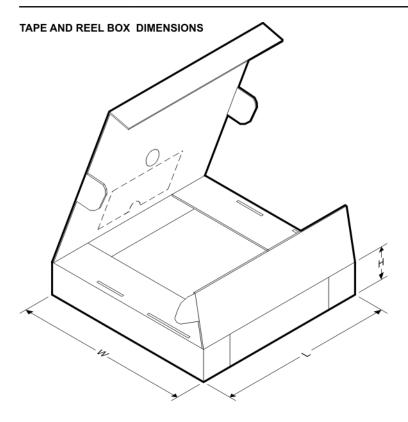

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|-----|-------------|------------|-------------|

| LM48823TL/NOPB | DSBGA        | YZR             | 16   | 250 | 210.0       | 185.0      | 35.0        |

# YZR0016

B. This drawing is subject to change without notice.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2020, Texas Instruments Incorporated