LM3632A

SNVSA63A - APRIL 2015-REVISED SEPTEMBER 2015

# LM3632A Single-Chip Backlight With Bias Power and 1.5-A Flash LED Driver

Technical

Documents

Sample &

Buy

#### Features 1

- Drives up to Two Strings of Typically Eight LEDs in Series

- Integrated Backlight Boost with 29-V Maximum **Output Voltage**

- Two Low-Side Constant-Current LED Drivers with 25-mA Maximum Output Current

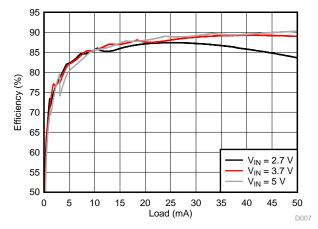

- Backlight Efficiency Up to 90%

- 11-Bit Exponential or Linear Dimming

- External PWM Input for CABC Backlight Operation

- LCD Bias Efficiency > 85%

- Programmable Positive LCD bias, 4-V to 6-V, 50mA Maximum Output Current

- Programmable Negative LCD bias, -4-V to -6-V, 50-mA Maximum Output Current

- 1.5-A Flash LED Boost

- Flash Efficiency > 85%

- 2.7-V to 5-V Input Voltage Range

#### Applications 2

- Smart Phone LCD Backlighting and Bias

- Small Tablet LCD Backlighting and Bias

# 3 Description

Tools &

Software

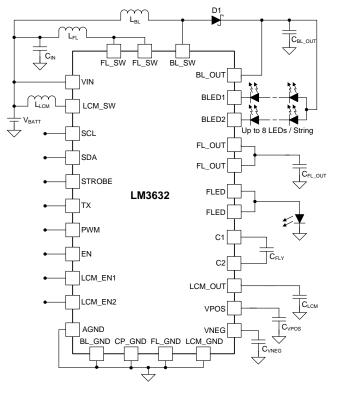

The LM3632A integrates the WLED drivers for both the backlight of the LCD panel and the camera flash along with the bias power for the LCD panel into one device. The device has all the safety features required in LED drivers with up to 90% efficiency and bias positive/negative power rails achieving 1.5% accuracy. Capable of driving up to 16 backlight LEDs, the device is ideal for small- to medium-size displays. A 1.5-A constant-current LED driver powered by a synchronous boost converter can be used for flash applications. The high-side flash current source allows for grounded cathode LED operation.

Support &

Community

20

A high level of integration and programmability allows the LM3632A to address a variety of applications without the need for hardware changes.

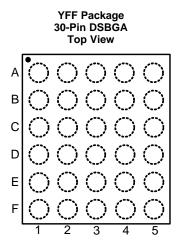

#### Device Information<sup>(1)</sup>

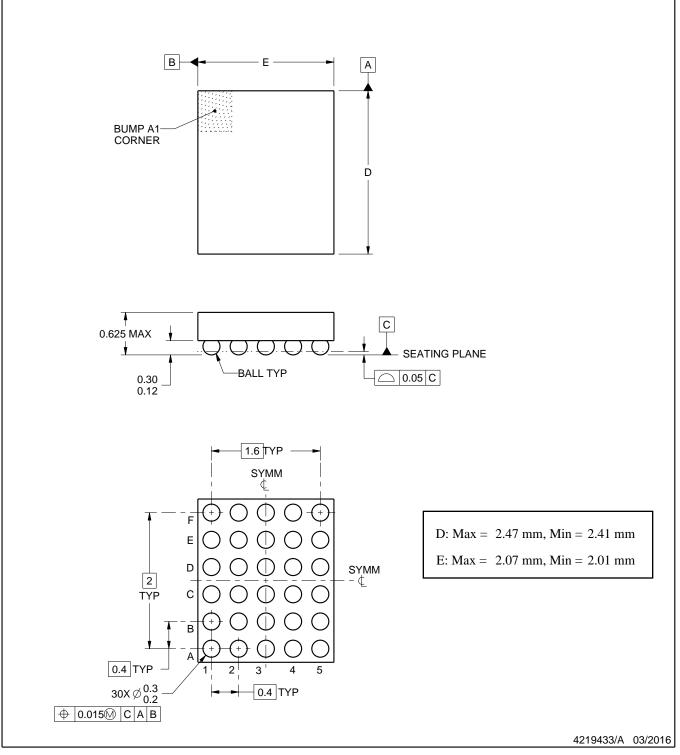

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)   |

|-------------|------------|-------------------|

| LM3632A     | DSBGA (30) | 2.47 mm x 2.07 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

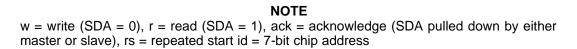

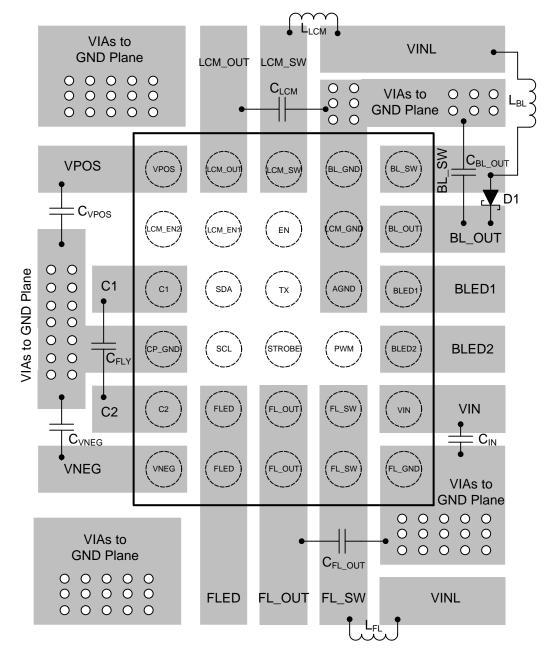

## Simplified Schematic

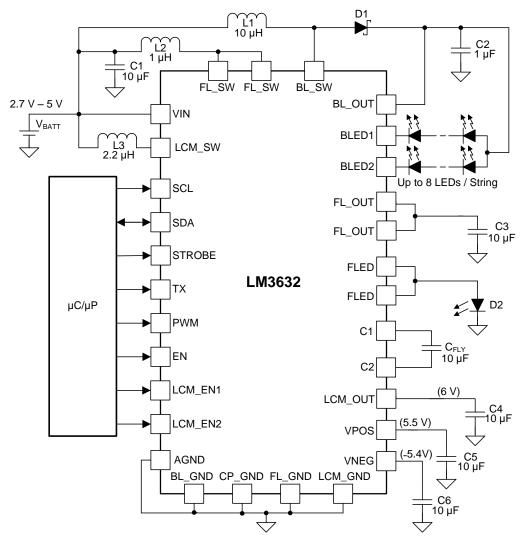

## Backlight Efficiency, 2P7S

2

# **Table of Contents**

| 1 | Feat | tures 1                                         |

|---|------|-------------------------------------------------|

| 2 | Арр  | lications1                                      |

| 3 | Des  | cription1                                       |

| 4 | Rev  | ision History 2                                 |

| 5 | Pin  | Configuration and Functions 3                   |

| 6 | Spe  | cifications 4                                   |

|   | 6.1  | Absolute Maximum Ratings 4                      |

|   | 6.2  | ESD Ratings 4                                   |

|   | 6.3  | Recommended Operating Conditions 4              |

|   | 6.4  | Thermal Information 4                           |

|   | 6.5  | Electrical Characteristics 5                    |

|   | 6.6  | I <sup>2</sup> C Timing Requirements (SDA, SCL) |

|   | 6.7  | Typical Characteristics 9                       |

| 7 | Deta | ailed Description 13                            |

|   | 7.1  | Overview 13                                     |

|   | 7.2  | Functional Block Diagram 14                     |

|   | 7.3  | Features Description 15                         |

|   | 7.4  | Device Functional Modes 27                      |

|   |      |                                                 |

| 7.6       Register Maps       3         8       Application and Implementation       4         8.1       Application Information       4         8.2       Typical Application       4         9       Power Supply Recommendations       5         10       Layout       5         10.1       Layout Guidelines       5         10.2       Layout Example       5         11.1       Device and Documentation Support       5         11.2       Documentation Support       5         11.3       Community Resources       5         11.4       Trademarks       5         11.5       Electrostatic Discharge Caution       5         11.6       Glossary       5         12       Mechanical, Packaging, and Orderable       5 |    | 7.5  | Programming                     | 27 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|---------------------------------|----|

| 8.1       Application Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 7.6  | Register Maps                   | 32 |

| 8.2 Typical Application       4         9 Power Supply Recommendations       5         10 Layout       5         10.1 Layout Guidelines       5         10.2 Layout Example       5         11 Device and Documentation Support       5         11.1 Device Support       5         11.2 Documentation Support       5         11.3 Community Resources       5         11.4 Trademarks       5         11.5 Electrostatic Discharge Caution       5         11.6 Glossary       5         12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                | 8  | Арр  | lication and Implementation     | 40 |

| 9       Power Supply Recommendations       5         10       Layout       5         10.1       Layout Guidelines       5         10.2       Layout Example       5         11       Device and Documentation Support       5         11.1       Device Support       5         11.2       Documentation Support       5         11.3       Community Resources       5         11.4       Trademarks       5         11.5       Electrostatic Discharge Caution       5         11.6       Glossary       5         12       Mechanical, Packaging, and Orderable       5                                                                                                                                                        |    | 8.1  | Application Information         | 40 |

| 10       Layout       5         10.1       Layout Guidelines       5         10.2       Layout Example       5         11       Device and Documentation Support       5         11.1       Device Support       5         11.2       Documentation Support       5         11.3       Community Resources       5         11.4       Trademarks       5         11.5       Electrostatic Discharge Caution       5         11.6       Glossary       5         12       Mechanical, Packaging, and Orderable       5                                                                                                                                                                                                             |    | 8.2  | Typical Application             | 40 |

| 10.1Layout Guidelines510.2Layout Example511Device and Documentation Support511.1Device Support511.2Documentation Support511.3Community Resources511.4Trademarks511.5Electrostatic Discharge Caution511.6Glossary512Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9  | Pow  | er Supply Recommendations       | 54 |

| 10.2       Layout Example       5         11       Device and Documentation Support       5         11.1       Device Support       5         11.2       Documentation Support       5         11.3       Community Resources       5         11.4       Trademarks       5         11.5       Electrostatic Discharge Caution       5         11.6       Glossary       5         12       Mechanical, Packaging, and Orderable       5                                                                                                                                                                                                                                                                                          | 10 | Lay  | out                             | 54 |

| 10.2       Layout Example       5         11       Device and Documentation Support       5         11.1       Device Support       5         11.2       Documentation Support       5         11.3       Community Resources       5         11.4       Trademarks       5         11.5       Electrostatic Discharge Caution       5         11.6       Glossary       5         12       Mechanical, Packaging, and Orderable       5                                                                                                                                                                                                                                                                                          |    | 10.1 | Layout Guidelines               | 54 |

| 11.1Device Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      |                                 |    |

| 11.2Documentation Support511.3Community Resources511.4Trademarks511.5Electrostatic Discharge Caution511.6Glossary512Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11 | Dev  | ice and Documentation Support   | 56 |

| 11.3Community Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 11.1 | Device Support                  | 56 |

| 11.4Trademarks511.5Electrostatic Discharge Caution511.6Glossary512Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 11.2 | Documentation Support           | 56 |

| <ul> <li>11.5 Electrostatic Discharge Caution</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 11.3 | Community Resources             | 56 |

| <ul><li>11.6 Glossary</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 11.4 | Trademarks                      | 56 |

| 12 Mechanical, Packaging, and Orderable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 11.5 | Electrostatic Discharge Caution | 56 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 11.6 | Glossary                        | 56 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12 |      |                                 |    |

| Information5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | Info | rmation                         | 56 |

# 4 Revision History

| Cł | hanges from Original (April 2015) to Revision A                                                                                                                                                                                                  | Page |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added 3 additional graphs for Iq shutdown and standby                                                                                                                                                                                            | 12   |

| •  | Added "It is recommended that V <sub>IN</sub> has risen above 2.7 V before setting EN HIGH and that the EN pin is not forced low while the VNEG output is enabled or before the VNEG output is discharged." to end of <i>EN Input</i> subsection |      |

| •  | Added Community Resources                                                                                                                                                                                                                        | 56   |

#### **EXAS** STRUMENTS

www.ti.com

#### LM3632A SNVSA63A – APRIL 2015–REVISED SEPTEMBER 2015

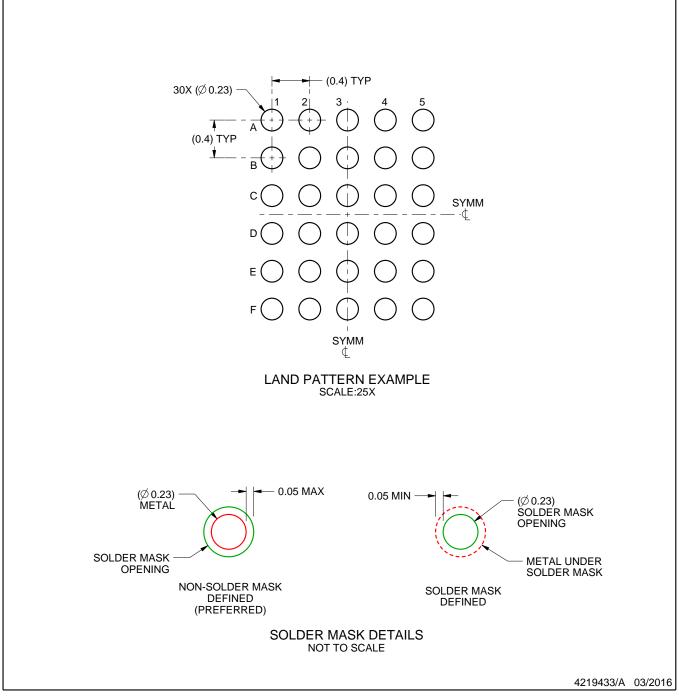

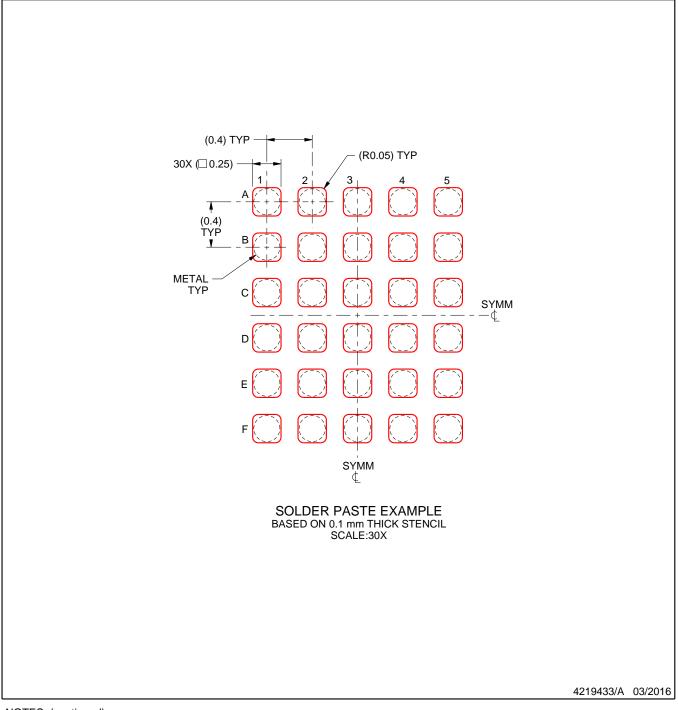

## 5 Pin Configuration and Functions

## **Pin Functions**

| PIN |         | TYPE | DESCRIPTION                                                                                                 |  |  |  |  |

|-----|---------|------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NO. | NAME    | ITPE | DESCRIPTION                                                                                                 |  |  |  |  |

| A1  | VPOS    | 0    | Positive LDO output for LCM bias power                                                                      |  |  |  |  |

| A2  | LCM_OUT | 0    | LCM bias boost output voltage                                                                               |  |  |  |  |

| A3  | LCM_SW  | 0    | LCM bias boost switch connection                                                                            |  |  |  |  |

| A4  | BL_GND  | -    | Backlight boost ground connection                                                                           |  |  |  |  |

| A5  | BL_SW   | 0    | Backlight boost switch connection                                                                           |  |  |  |  |

| B1  | LCM_EN2 | Ι    | Enable for inverting charge pump output; 300-k $\Omega$ internal pulldown resistor between LCM_EN2 and GND. |  |  |  |  |

| B2  | LCM_EN1 | Ι    | Enable for positive LDO output; 300-k $\Omega$ internal pulldown resistor between LCM_EN1 and GND.          |  |  |  |  |

| B3  | EN      | I    | Active high chip enable; 300-k $\Omega$ internal pulldown resistor between EN and GND.                      |  |  |  |  |

| B4  | LCM_GND | -    | LCM bias boost ground connection                                                                            |  |  |  |  |

| B5  | BL_OUT  | 0    | Backlight boost output voltage                                                                              |  |  |  |  |

| C1  | C1      | 0    | rting charge pump flying capacitor positive connection                                                      |  |  |  |  |

| C2  | SDA     | I/O  | erial data connection for I <sup>2</sup> C- compatible interface                                            |  |  |  |  |

| C3  | ТΧ      | I    | ash interrupt input; 300-kΩ internal pulldown resistor between TX and GND.                                  |  |  |  |  |

| C4  | AGND    | -    | nalog ground connection                                                                                     |  |  |  |  |

| C5  | BLED1   | 0    | Input pin to internal LED current sink 1                                                                    |  |  |  |  |

| D1  | CP_GND  | -    | Inverting charge pump ground connection                                                                     |  |  |  |  |

| D2  | SCL     | I    | Serial clock connection for I <sup>2</sup> C- compatible interface                                          |  |  |  |  |

| D3  | STROBE  | I    | Flash enable input; 300-k $\Omega$ internal pulldown resistor between STROBE and GND.                       |  |  |  |  |

| D4  | PWM     | Ι    | PWM input for CABC current control; 300-kΩ internal pulldown resistor between PWM and GND.                  |  |  |  |  |

| D5  | BLED2   | 0    | Input pin to internal LED current sink 2                                                                    |  |  |  |  |

| E1  | C2      | 0    | Inverting charge pump flying capacitor negative connection                                                  |  |  |  |  |

| E2  | FLED    | 0    | High-side current source output for flash LED                                                               |  |  |  |  |

| E3  | FL_OUT  | 0    | Flash boost output voltage                                                                                  |  |  |  |  |

| E4  | FL_SW   | 0    | Flash boost switch connection                                                                               |  |  |  |  |

| E5  | VIN     | I    | Input voltage connection                                                                                    |  |  |  |  |

| F1  | VNEG    | 0    | Inverting charge pump output voltage                                                                        |  |  |  |  |

| F2  | FLED    | 0    | High-side current source output for flash LED                                                               |  |  |  |  |

| F3  | FL_OUT  | 0    | Flash boost output voltage                                                                                  |  |  |  |  |

| F4  | FL_SW   | 0    | Flash boost switch connection                                                                               |  |  |  |  |

| F5  | FL_GND  | -    | Flash boost ground connection                                                                               |  |  |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)

|                                                                                      | MIN  | MAX                | UNIT |

|--------------------------------------------------------------------------------------|------|--------------------|------|

| Voltage on VIN, FL_SW, FL_OUT, FLED, EN, LCM_EN1, LCM_EN2, PWM, STROBE, TX, SCL, SDA | -0.3 | 6                  | V    |

| Voltage on LCM_SW, LCM_OUT, VPOS, C1                                                 | -0.3 | 7                  | V    |

| Voltage on VNEG, C2                                                                  | -7   | 0.3                | V    |

| Voltage on BL_SW, BL_VOUT, BLED1, BLED2                                              | -0.3 | 30                 | V    |

| Continuous power dissipation                                                         |      | Internally limited |      |

| Maximum junction temperature, T <sub>J(MAX)</sub>                                    |      | 150                | ാം   |

| Storage temperature, T <sub>stg</sub>                                                | -45  | 150                |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE                                                | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|------------------------------------------------------|------|

| V                  | Electrostatio discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              |                                                      | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | JEDEC specification JESD22-C101 <sup>(2)</sup> ±1000 |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|                                            | MIN | MAX | UNIT |

|--------------------------------------------|-----|-----|------|

| Input voltage, V <sub>IN</sub>             | 2.7 | 5   | V    |

| Operating ambient temperature, $T_A^{(1)}$ | -40 | 85  | °C   |

(1) In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{A-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125^{\circ}C$ ), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to-ambient thermal resistance of the part/package in the application ( $R_{\theta JA}$ ), as given by the following equation:  $T_{A-MAX} = T_{J-MAX-OP} - (R_{\theta JA} \times P_{D-MAX})$ .

#### 6.4 Thermal Information

|                 |                                              | LM3632A     |      |

|-----------------|----------------------------------------------|-------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                 |                                              | 30 PINS     |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 58.6        |      |

| $R_{\theta JC}$ | Junction-to-case (top) thermal resistance    | 0.2         |      |

| $R_{\theta JB}$ | Junction-to-board thermal resistance         | 8.3         | °C/W |

| $\Psi_{JT}$     | Junction-to-top characterization parameter   | 1.4         |      |

| $\Psi_{JB}$     | Junction-to-board characterization parameter | 8.3         |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

Unless otherwise specified, limits apply over the full operating ambient temperature range (-40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C), V<sub>IN</sub> = 3.7 V, V<sub>VPOS</sub> = 5.5 V, V<sub>VNEG</sub> = -5.4 V, V<sub>LCM\_OUT</sub> = 6 V.

|                        | PARAMETER                                        | TEST CO                                                                                 | NDITION                                                                                                                                                 | MIN  | TYP   | MAX  | UNIT |

|------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| CURRENT CO             | NSUMPTION                                        |                                                                                         |                                                                                                                                                         |      |       |      |      |

| I <sub>SD</sub>        | Shutdown current                                 | EN = 0                                                                                  |                                                                                                                                                         |      | 1     | 4    | μA   |

| l <sub>Q</sub>         | Quiescent current, device not<br>switching       | EN = V <sub>IN</sub> , LCD bias b                                                       | poost disabled                                                                                                                                          |      | 2     | 10   | μA   |

| I <sub>LCD_EN</sub>    |                                                  | LCD bias boost enab                                                                     | oled, no-load                                                                                                                                           |      | 0.5   |      | mA   |

| DEVICE PROT            | ECTION                                           |                                                                                         |                                                                                                                                                         |      |       |      |      |

| TSD                    | Thermal shutdown                                 |                                                                                         |                                                                                                                                                         |      | 140   |      | °C   |

| BACKLIGHT L            | ED CURRENT SINKS                                 |                                                                                         |                                                                                                                                                         |      |       |      |      |

| I <sub>LED_MAX</sub>   | Maximum output current in BLED1/2                | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V}$ , line mode                    | ear or exponential                                                                                                                                      |      | 25    |      | mA   |

| I <sub>LED_MIN</sub>   | Minimum output current in BLED1/2                | $2.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V}, \text{ line mode}$             | ear or exponential                                                                                                                                      |      | 50    |      | μA   |

| I <sub>ACCU</sub>      | LED current accuracy <sup>(1)</sup>              |                                                                                         | $.7 \text{ V} \le \text{V}_{\text{IN}} \le 5 \text{ V}, 50 \mu\text{A} \le \text{I}_{\text{LED}} \le 25 \text{ nA}, \text{ linear or exponential mode}$ |      | 0.1%  | 3%   |      |

| I <sub>MATCH</sub>     | LED1 to LED2 current<br>matching <sup>(1)</sup>  | 2.7 V $\leq$ V <sub>IN</sub> $\leq$ 5 V, 30 mA, linear or expone                        |                                                                                                                                                         | -2%  | 0.1%  | 2%   |      |

| BACKLIGHT B            | BOOST CONVERTER                                  |                                                                                         |                                                                                                                                                         |      |       |      |      |

| V <sub>OVP_BL</sub>    | Backlight boost output<br>overvoltage protection | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V, 29                                                       | V option                                                                                                                                                | 28   | 28.75 | 29.5 | V    |

| Efficiency             | Typical efficiency <sup>(2)</sup>                | I <sub>LED</sub> = 5 mA/string, V<br>(2 x 7 LEDs), (P <sub>OUT</sub> /I                 |                                                                                                                                                         |      |       |      |      |

| V                      | Regulated current sink                           | l <sub>LED</sub> = 25 mA                                                                |                                                                                                                                                         |      | 250   |      | mV   |

| V <sub>HR</sub>        | headroom voltage                                 | $I_{LED} = 5 \text{ mA}$                                                                |                                                                                                                                                         |      | 100   |      | mV   |

| V <sub>HR_MIN</sub>    | Current sink minimum headroom voltage            | I <sub>LED</sub> = 95% of nomina                                                        | al, I <sub>LED</sub> = 5 mA                                                                                                                             |      | 30    |      | mV   |

| R <sub>DSON</sub>      | NMOS switch on resistance                        | I <sub>SW</sub> = 100 mA                                                                |                                                                                                                                                         |      | 0.25  |      | Ω    |

| I <sub>CL</sub>        | NMOS switch current limit                        | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}$                              |                                                                                                                                                         | 900  | 1000  | 1100 | mA   |

| $f_{\sf SW\_BLBOOST}$  | Switching froquency                              | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}$                              | 500-kHz mode                                                                                                                                            | 450  | 500   | 550  | kHz  |

|                        | Switching frequency                              |                                                                                         | 1-MHz mode                                                                                                                                              | 900  | 1000  | 1100 | KIIZ |

| D <sub>MAX</sub>       | Maximum duty cycle                               |                                                                                         |                                                                                                                                                         |      | 94%   |      |      |

| LCM BIAS BO            | OST CONVERTER                                    |                                                                                         |                                                                                                                                                         |      |       |      |      |

| V <sub>OVP_LCM</sub>   | LCM bias boost output<br>overvoltage protection  | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}$                              |                                                                                                                                                         |      | 7     |      | V    |

| fsw_lcmbst             | Switching frequency <sup>(3)</sup>               | 2.7 V ≤ V <sub>IN</sub> ≤ 5 V                                                           |                                                                                                                                                         |      | 2500  |      | kHz  |

|                        | Bias boost output voltage range                  |                                                                                         |                                                                                                                                                         | 4.5  |       | 6.4  | V    |

|                        | Output voltage step size                         |                                                                                         |                                                                                                                                                         |      | 50    |      | mV   |

|                        | Peak-to-peak ripple voltage (3)                  | I <sub>LOAD</sub> = 5 mA & 50 m                                                         | Α, C <sub>BST</sub> = 10 μF                                                                                                                             |      | 50    |      | mVpp |

| V <sub>LCM_OUT</sub>   | LCM_OUT line transient response <sup>(3)</sup>   | V <sub>IN</sub> + 500 mVp-p AC<br>100 mV/μs, 200 Hz,<br>= 5 mA, C <sub>IN</sub> = 10 μF |                                                                                                                                                         | -50  | ±25   | 50   | mV   |

|                        | LCM_OUT load transient response (3)              | Load current step 0 r<br>T <sub>RISE/FALL</sub> = 100 mA/                               |                                                                                                                                                         | -150 |       | 150  | mV   |

| I <sub>CL_LCMBST</sub> | Valley current limit                             |                                                                                         | -                                                                                                                                                       |      | 1000  |      | mA   |

(1) Output Current Accuracy is the difference between the actual value of the output current and programmed value of this current. Matching is the maximum difference from the average. For the constant current sinks on the device (BLED1 and BLED2), the following is determined: the maximum output current (MAX), the minimum output current (MIN), and the average output current of both outputs (AVG). Matching number is calculated: (I<sub>LED1</sub> - I<sub>LED2</sub>)/(I<sub>LED1</sub> + I<sub>LED2</sub>). The typical specification provided is the most likely norm of the matching figure of all parts. Note that some manufacturers have different definitions in use.

(2) Typical value only for information.

(3) Limits set by characterization and/or simulation only.

Copyright © 2015, Texas Instruments Incorporated

## **Electrical Characteristics (continued)**

Unless otherwise specified, limits apply over the full operating ambient temperature range (-40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C), V<sub>IN</sub> = 3.7 V, V<sub>VPOS</sub> = 5.5 V, V<sub>VNEG</sub> = -5.4 V, V<sub>LCM\_OUT</sub> = 6 V.

|                           | PARAMETER                                                           | TEST CON                                                                      | DITION                                                                                                            | MIN   | TYP  | MAX  | UNIT |

|---------------------------|---------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|------|------|------|

| D                         | High-side MOSFET on resistance                                      | $V_{IN} = V_{GS} = 5 V, T_A =$                                                | 25°C                                                                                                              |       | 170  |      |      |

| R <sub>DSON_LCMBST</sub>  | Low-side MOSFET on Resistance                                       | $V_{IN} = V_{GS} = 5 \text{ V},  T_{A} = 25^{\circ}\text{C}$                  |                                                                                                                   |       | 290  |      | mΩ   |

| EFF <sub>LCMBST</sub>     | Efficiency <sup>(2)</sup>                                           | V <sub>LCM_OUT</sub> = 6 V, 5 m/<br>mA                                        | $A < I_{LCMBST} < 100$                                                                                            |       | 92%  |      |      |

| t <sub>ST_LCMBST</sub>    | Start-up time (LCM_OUT), $V_{LCM_OUT} = 10\%$ to 90% <sup>(3)</sup> | $C_{LCM_{BST}} = 10 \ \mu F$                                                  |                                                                                                                   |       |      | 1000 | μs   |

| DISPLAY BIAS              | POSITIVE OUTPUT (VPOS)                                              |                                                                               |                                                                                                                   |       |      |      |      |

|                           | Programmable output voltage range                                   |                                                                               |                                                                                                                   | 4     |      | 6    | V    |

|                           | Output voltage step size                                            |                                                                               |                                                                                                                   |       | 50   |      | mV   |

|                           | Output voltage accuracy                                             | Output voltage = 5.4                                                          | V                                                                                                                 | -1.5% |      | 1.5% |      |

| VPOS                      | VPOS line transient response <sup>(3)</sup>                         | V <sub>IN</sub> + 500 mVp-p AC<br>100 mV/μs, 200 Hz, I<br>= 10 μF             | V <sub>IN</sub> + 500 mVp-p AC square wave, Tr =<br>100 mV/µs, 200 Hz, I <sub>LOAD</sub> = 25 mA, C <sub>IN</sub> |       |      | 50   | mV   |

|                           | VPOS load transient response <sup>(3)</sup>                         | 0 to 50 mA load trans<br>μF                                                   | -50                                                                                                               |       | 50   | mV   |      |

|                           | DC load regulation <sup>(3)</sup>                                   | $0 \text{ mA} \le I_{VPOS} \le 50 \text{ mA}$                                 |                                                                                                                   |       |      | 20   | mV   |

| IMAX_VPOS                 | Maximum output current                                              |                                                                               |                                                                                                                   |       | 50   |      | mA   |

| I <sub>CL_VPOS</sub>      | Output current limit                                                |                                                                               |                                                                                                                   |       | 80   |      | mA   |

| I <sub>RUSH_PK_VPOS</sub> | Peak start-up inrush current <sup>(3)</sup>                         | $V_{LCM\_OUT}$ = 6.3 V, $V_{POS}$ = 5.8 V, $C_{VPOS}$ = 10 $\mu F$            |                                                                                                                   |       |      | 250  | mA   |

| V <sub>DO_VPOS</sub>      | VPOS dropout voltage (4)                                            | $v_{POS} = 50 \text{ mA}, V_{v_{POS}} = 5.5 \text{ V}$                        |                                                                                                                   |       |      | 100  | mV   |

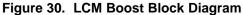

| +                         | Start-up time VPOS, V <sub>VPOS</sub> =                             | $C_{VPOS}$ = 10 $\mu$ F                                                       | 500-µs setting                                                                                                    |       | 500  |      |      |

| t <sub>ST_VPOS</sub>      | 10% to 90% <sup>(3)</sup>                                           |                                                                               | 800-µs setting                                                                                                    |       | 800  |      | μs   |

| R <sub>PD_VPOS</sub>      | Output pull-down resistor<br>(VPOS)                                 | VPOS disabled                                                                 |                                                                                                                   | 30    | 80   | 110  | Ω    |

| DISPLAY BIAS              | NEGATIVE OUTPUT (VNEG)                                              | -                                                                             | ·                                                                                                                 |       |      |      |      |

| V <sub>OVP_VNEG</sub>     | LCM bias negative charge-pump<br>output overvoltage protection      | Below V <sub>VNEG</sub> output v                                              | voltage target                                                                                                    |       | -250 |      | mV   |

| V <sub>SHORT_VNEG</sub>   | LCM bias negative charge-pump<br>output short circuit protection    | VNEG to CP_GND                                                                |                                                                                                                   |       | -750 |      | mV   |

|                           | Programmable output voltage range                                   |                                                                               |                                                                                                                   | -6    |      | -4   | V    |

|                           | Output voltage step size                                            |                                                                               |                                                                                                                   |       | 50   |      | mV   |

|                           | Output accuracy                                                     | Output voltage = -5.4                                                         | ٧                                                                                                                 | -1.5% |      | 1.5% |      |

| V <sub>VNEG</sub>         | Peak-to-peak ripple voltage <sup>(3)</sup>                          | I <sub>LOAD</sub> = 5 mA & 50 m/<br>C <sub>VNEG</sub> = 10 μF                 | Α,                                                                                                                |       | 60   |      | mVpp |

| • VNEG                    | VNEG line transient response <sup>(3)</sup>                         | V <sub>IN</sub> + 500 mVp-p AC<br>mV/µs 200 Hz, 12.5%                         |                                                                                                                   | -50   | ±25  | 50   | mV   |

|                           | VNEG load transient response <sup>(3)</sup>                         | 0 to 50 mA load trans<br>T <sub>RISE/FALL</sub> = 1 $\mu$ s, C <sub>VN</sub>  |                                                                                                                   |       |      | 100  | mV   |

|                           | Efficiency <sup>(2)</sup>                                           | $V_{IN} = 3.7 \text{ V}, V_{LCM_OU}$<br>$V_{VNEG} = -5.4 \text{ V}, I_{VNEG}$ | <sub>T</sub> = 5.8 V,                                                                                             |       | 92%  |      |      |

| I <sub>MAX_VNEG</sub>     | Maximum output current <sup>(3)</sup>                               | $V_{IN} = 3.7 \text{ V}, V_{LCM_OU^-}$<br>$V_{VNEG} = -5.4 \text{ V}$         | <sub>T</sub> = 5.8 V,                                                                                             |       | 50   |      | mA   |

| I <sub>CL_VNEG</sub>      | Output current limit <sup>(3)</sup>                                 |                                                                               |                                                                                                                   |       | 75   |      | mA   |

(4)  $V_{IN_VPOS} - V_{VPOS}$  when  $V_{VPOS}$  has dropped 100 mV below target.

## **Electrical Characteristics (continued)**

Unless otherwise specified, limits apply over the full operating ambient temperature range (-40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C), V<sub>IN</sub> = 3.7 V, V<sub>VPOS</sub> = 5.5 V, V<sub>VNEG</sub> = -5.4 V, V<sub>LCM\_OUT</sub> = 6 V.

|                        | PARAMETER                                                                         | TEST CONDITION                                                                                   | MIN  | TYP | MAX                                   | UNIT |  |

|------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-----|---------------------------------------|------|--|

|                        |                                                                                   | Q1                                                                                               |      | 350 |                                       |      |  |

| R <sub>DSON_VNEG</sub> | Charge FET pump on resistance                                                     | Q2                                                                                               |      | 400 |                                       | mΩ   |  |

|                        |                                                                                   | Q3                                                                                               |      | 400 | 40<br>1.6<br>5.1<br>5<br>3.15<br>2.15 |      |  |

| t <sub>ST_VNEG</sub>   | Start-up time (V <sub>VNEG</sub> ), V <sub>VNEG</sub> = 10% to 90% <sup>(3)</sup> | $V_{VNEG} = -6 V, C_{VNEG} = 10 \mu F$                                                           |      | 1   |                                       | ms   |  |

| R <sub>PU_VNEG</sub>   | Output pullup resistor, VNEG <sup>(3)</sup>                                       | VNEG Disabled, $V_{LCM_OUT} > 4.8 V$                                                             |      | 20  | 40                                    | Ω    |  |

| FLASH DRIVE            | R BOOST                                                                           |                                                                                                  | -    |     | +                                     |      |  |

| I <sub>LED</sub>       | Current source accuracy                                                           | 1.5-A flash, V <sub>FL_OUT</sub> = 4 V                                                           | 1.4  | 1.5 | 1.6                                   | А    |  |

|                        | Output overvoltage protection                                                     | ON threshold                                                                                     | 4.85 | 5   | 5.1                                   |      |  |

| V <sub>OVP</sub>       | trip point                                                                        | OFF threshold                                                                                    | 4.75 | 4.9 | 5                                     | V    |  |

| V <sub>HR</sub>        | Current source regulation voltage                                                 | 1.5-A flash, V <sub>FL_OUT</sub> = 4 V                                                           |      | 275 |                                       | mV   |  |

|                        | Quaitab augurant lingit                                                           |                                                                                                  | 2.45 | 2.8 | 2.15                                  | ٨    |  |

| I <sub>CL</sub>        | Switch current limit                                                              |                                                                                                  | 1.65 | 1.9 |                                       | A    |  |

| R <sub>NMOS</sub>      | NMOS switch on resistance                                                         | I <sub>NMOS</sub> = 1 A                                                                          |      | 80  |                                       | 0    |  |

| R <sub>PMOS</sub>      | PMOS switch on resistance                                                         | I <sub>PMOS</sub> = 1 A                                                                          |      | 100 |                                       | mΩ   |  |

| V <sub>VINM</sub>      | Input voltage monitor trip<br>threshold                                           |                                                                                                  | 2.76 | 2.9 | 3.04                                  | V    |  |

| LOGIC INPUT            | S (PWM, EN, LCM_EN1, LCM_EN2,                                                     | SCL, SDA, TX, STROBE)                                                                            | -    |     |                                       |      |  |

| V <sub>IL</sub>        | Input logic low                                                                   |                                                                                                  | 0    |     | 0.4                                   | V    |  |

| V <sub>IH</sub>        | Input logic high                                                                  |                                                                                                  | 1.2  |     | V <sub>IN</sub>                       | V    |  |

| LOGIC OUTPL            | JTS (SDA)                                                                         |                                                                                                  |      |     |                                       |      |  |

| V <sub>OL</sub>        | Output logic low                                                                  | $2.7 \text{ V} \leq \text{V}_{\text{IN}} \leq 5 \text{ V}, \text{ I}_{\text{OL}} = 3 \text{ mA}$ | 0    |     | 0.4                                   | V    |  |

| PWM INPUT              |                                                                                   |                                                                                                  | -    |     |                                       |      |  |

| fpwm_input             | PWM input frequency <sup>(2)</sup>                                                |                                                                                                  | 100  |     | 20000                                 | Hz   |  |

|                        |                                                                                   | PWM sampling frequency = 1 MHz                                                                   | 6    |     |                                       |      |  |

|                        | Minimum PWM ON/OFF time <sup>(3)</sup>                                            | PWM sampling frequency = 4 MHz                                                                   | 1.5  |     |                                       | μs   |  |

|                        | PWM timeout <sup>(3)</sup>                                                        | PWM sampling frequency = 1 MHz                                                                   |      | 25  |                                       | ~~~  |  |

|                        |                                                                                   | PWM sampling frequency = 4 MHz                                                                   |      | 3   |                                       | ms   |  |

SNVSA63A - APRIL 2015-REVISED SEPTEMBER 2015

www.ti.com

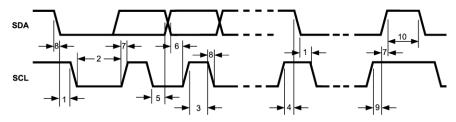

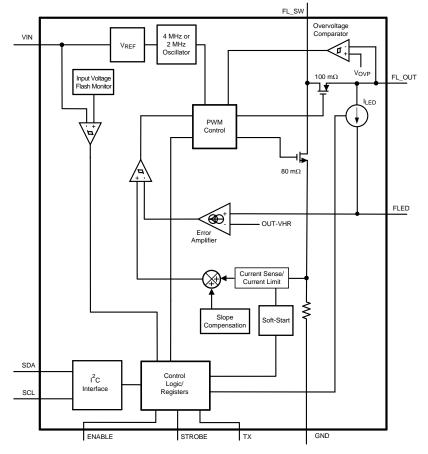

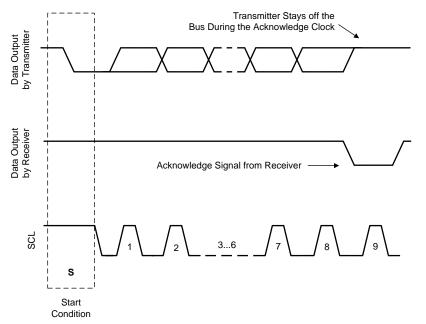

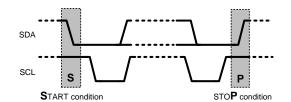

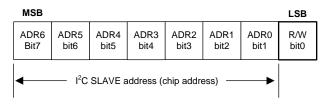

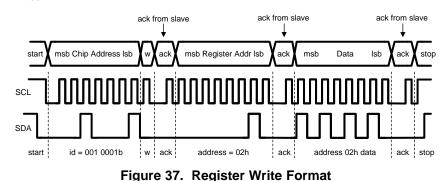

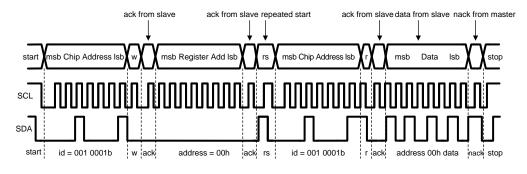

## 6.6 I<sup>2</sup>C Timing Requirements (SDA, SCL) <sup>(1)</sup>

Over operating free-air temperature range (unless otherwise noted)(see Figure 1).

|                  |                                                  | MIN                    | NOM | MAX | UNIT |

|------------------|--------------------------------------------------|------------------------|-----|-----|------|

| f <sub>SCL</sub> | Clock frequency                                  |                        |     | 400 | kHz  |

| 1                | Hold time (repeated) START condition             | 0.6                    |     |     | μs   |

| 2                | Clock low time                                   | 1.3                    |     |     | μs   |

| 3                | Clock high time                                  | 600                    |     |     | ns   |

| 4                | Set-up time for a repeated START condition       | 600                    |     |     | ns   |

| 5                | Data hold time                                   | 50                     |     |     | ns   |

| 6                | Data set-up time                                 | 100                    |     |     | ns   |

| 7                | Rise time of SDA and SCL                         | 20 + 0.1C <sub>b</sub> |     | 300 | ns   |

| 8                | Fall time of SDA and SCL                         | 15 + 0.1C <sub>b</sub> |     | 300 | ns   |

| 9                | Set-Up time between a STOP and a START condition | 1.3                    |     |     | μs   |

| Cb               | Capacitive load for each bus line                | 10                     |     | 200 | pF   |

(1) Limits set by characterization and/or simulation only.

Figure 1. I<sup>2</sup>C Timing Parameters

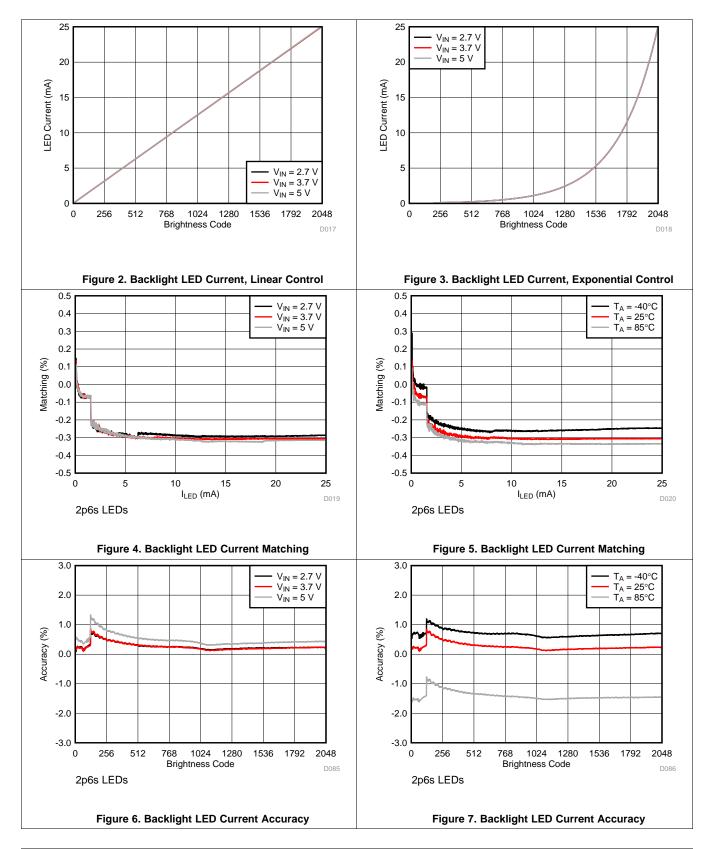

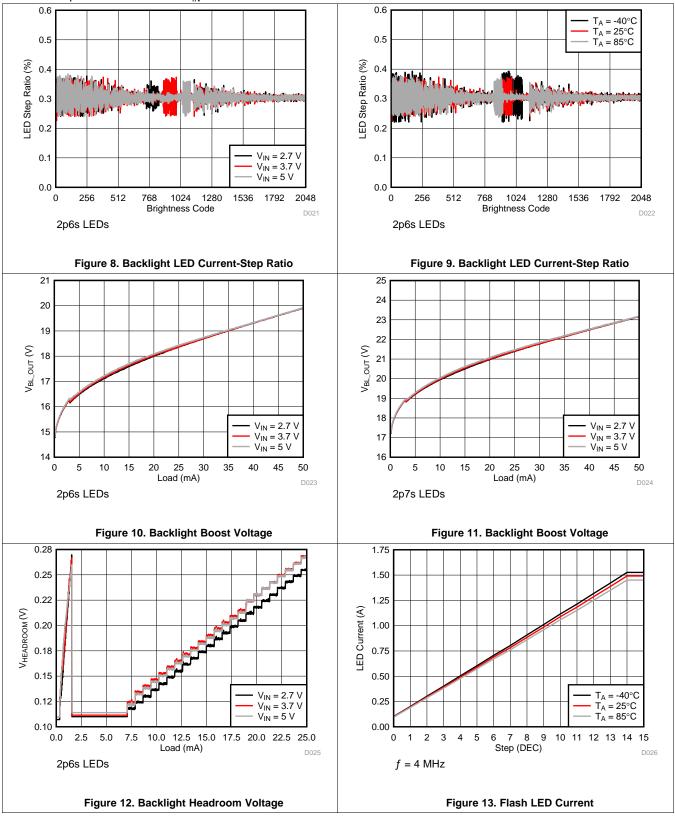

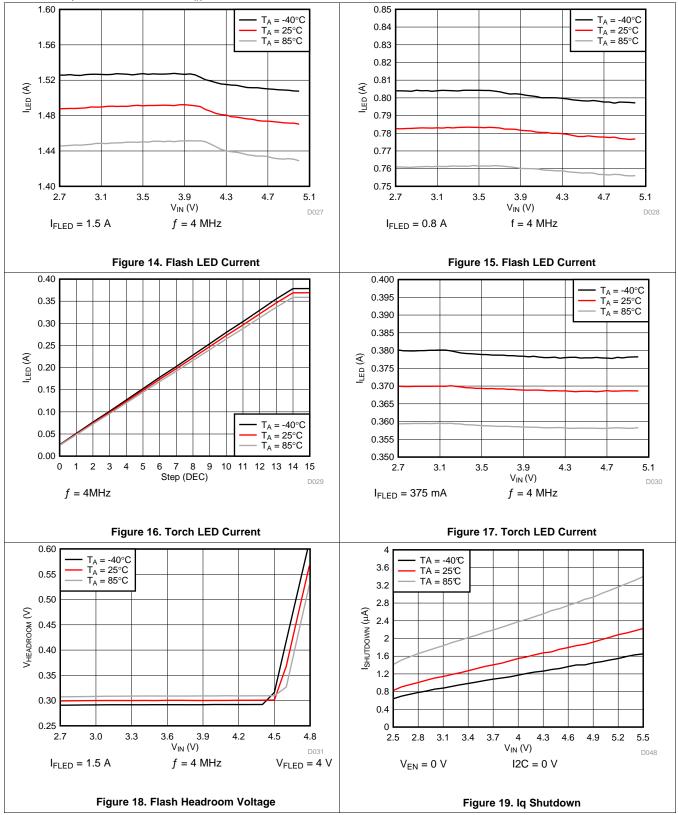

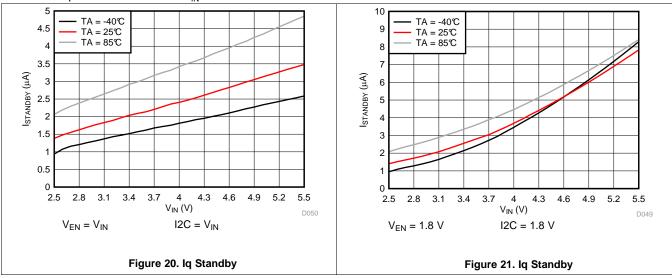

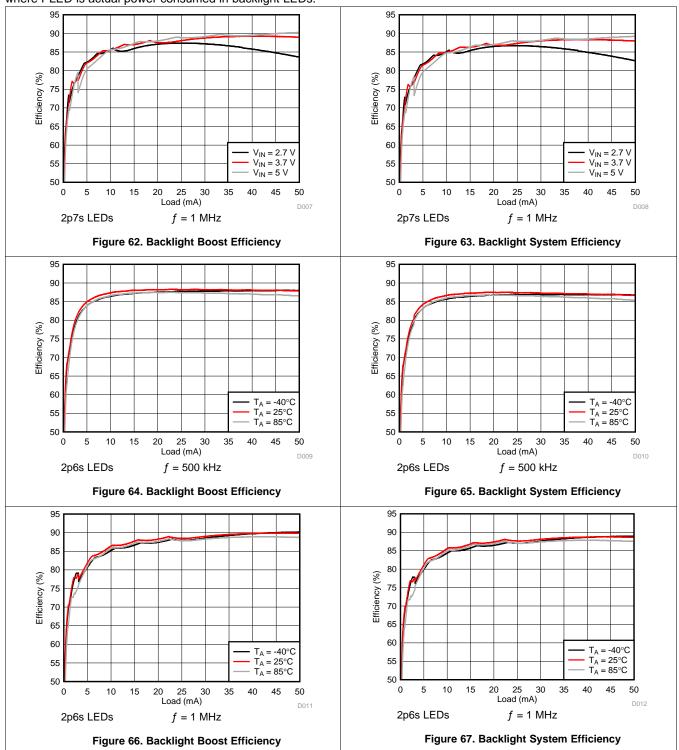

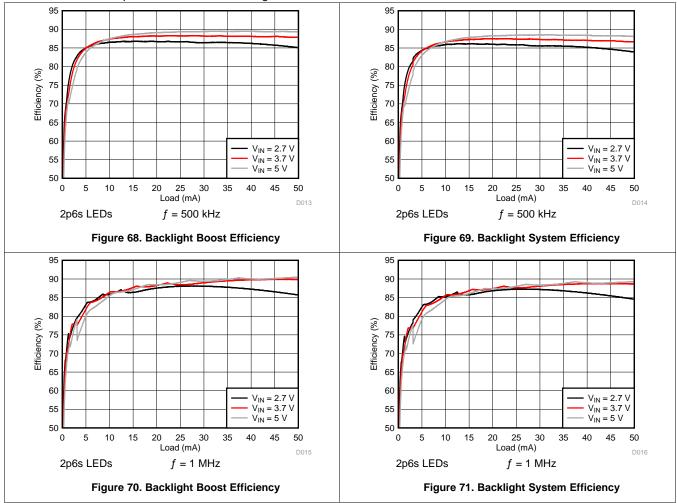

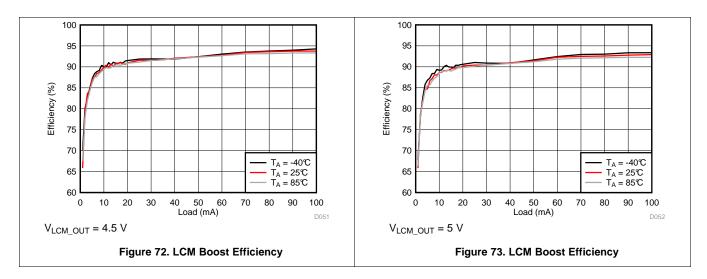

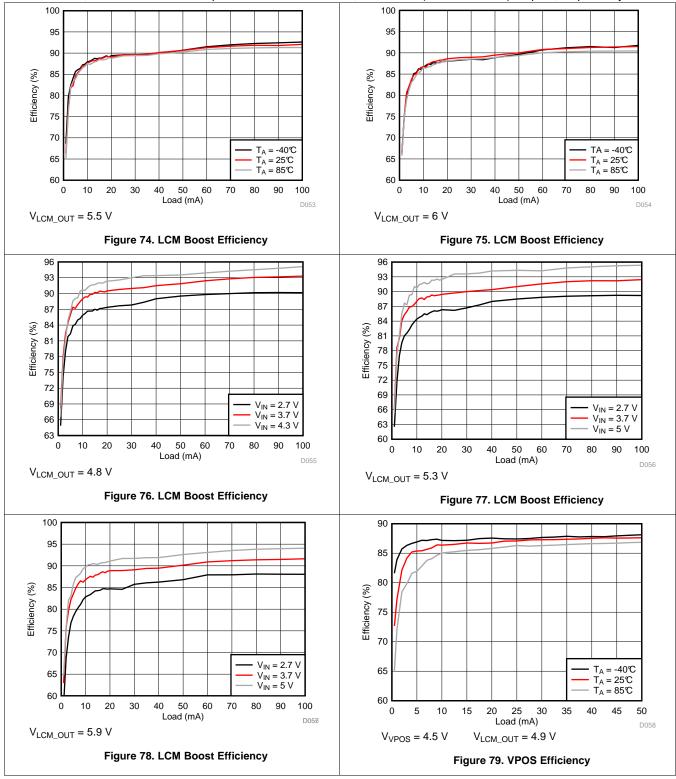

## 6.7 Typical Characteristics

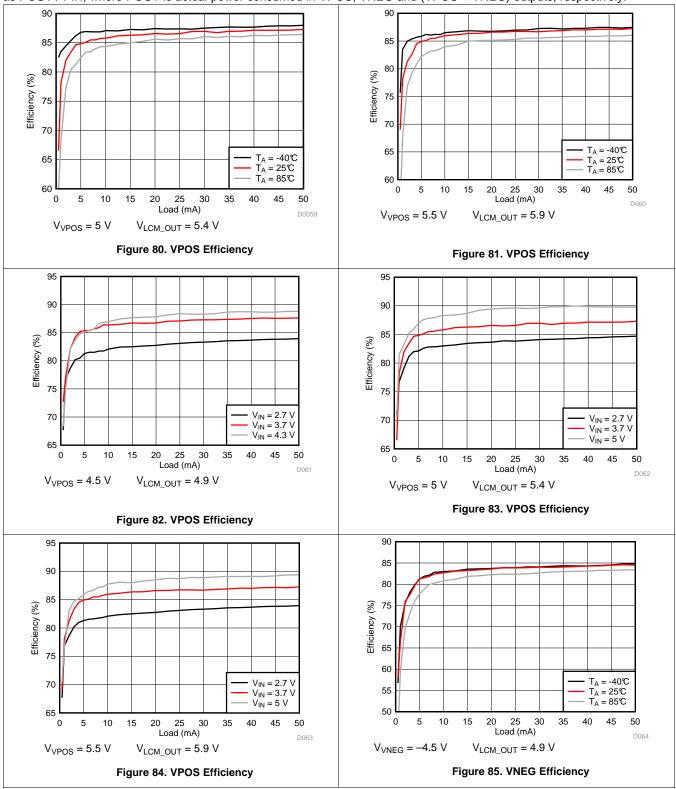

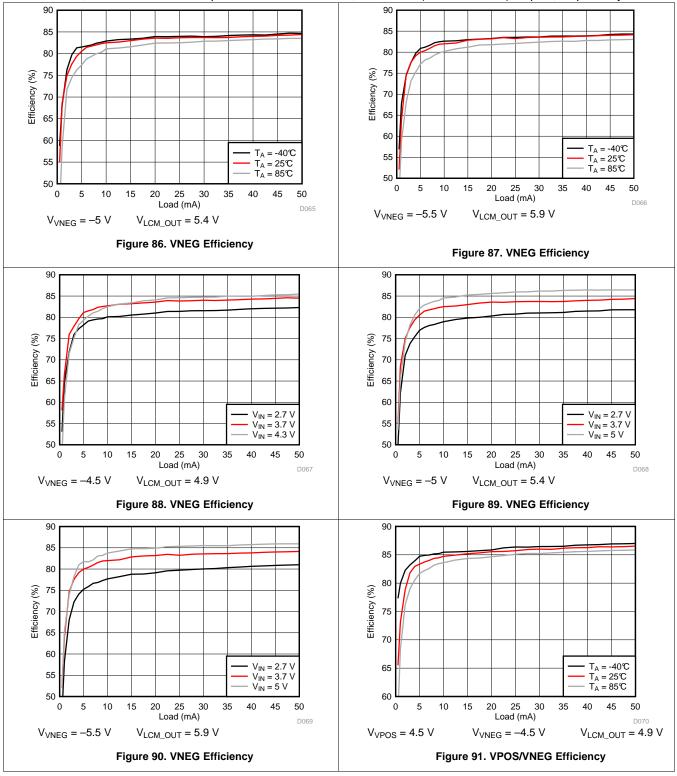

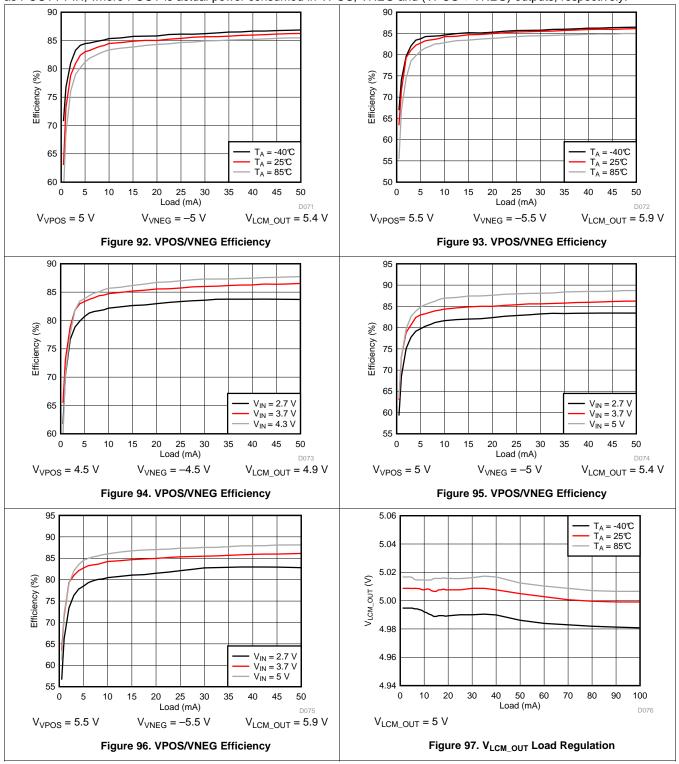

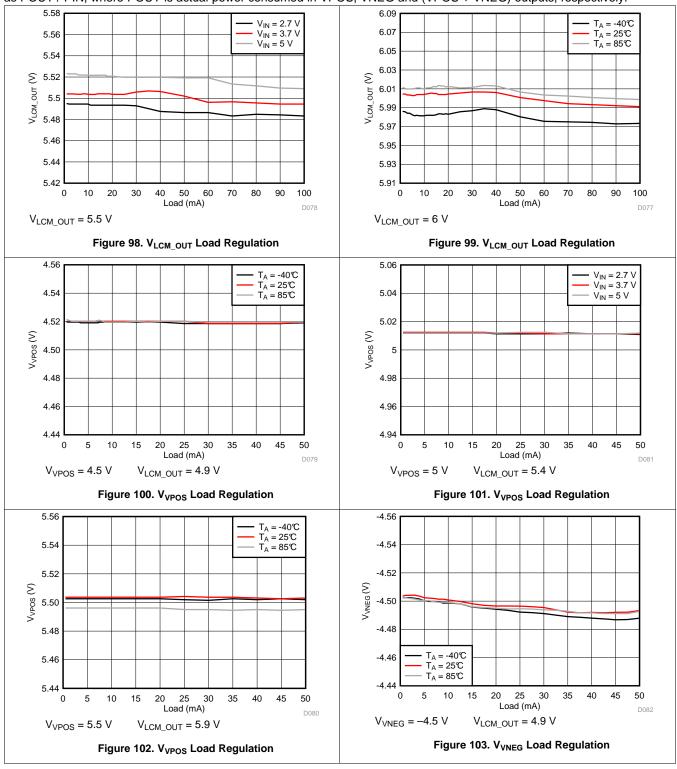

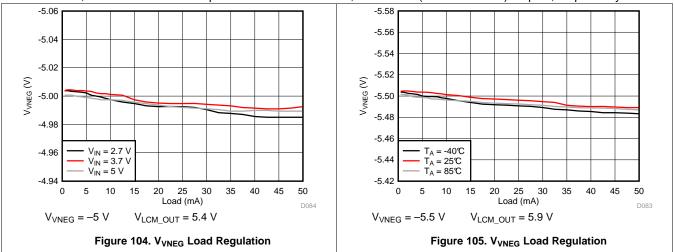

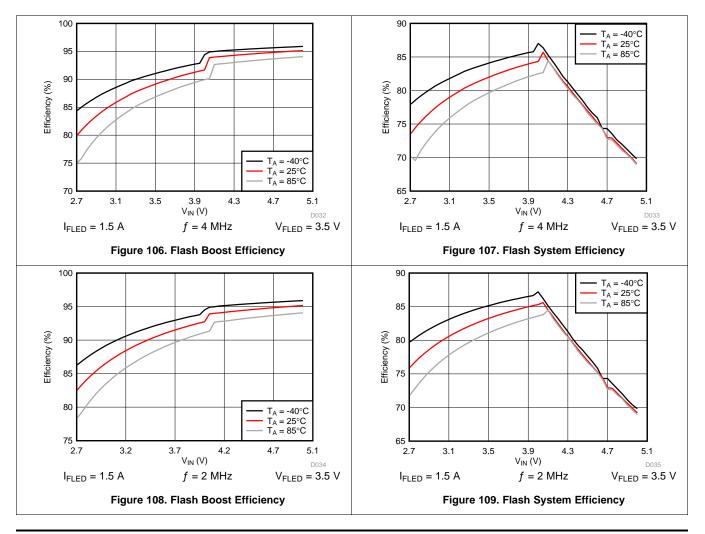

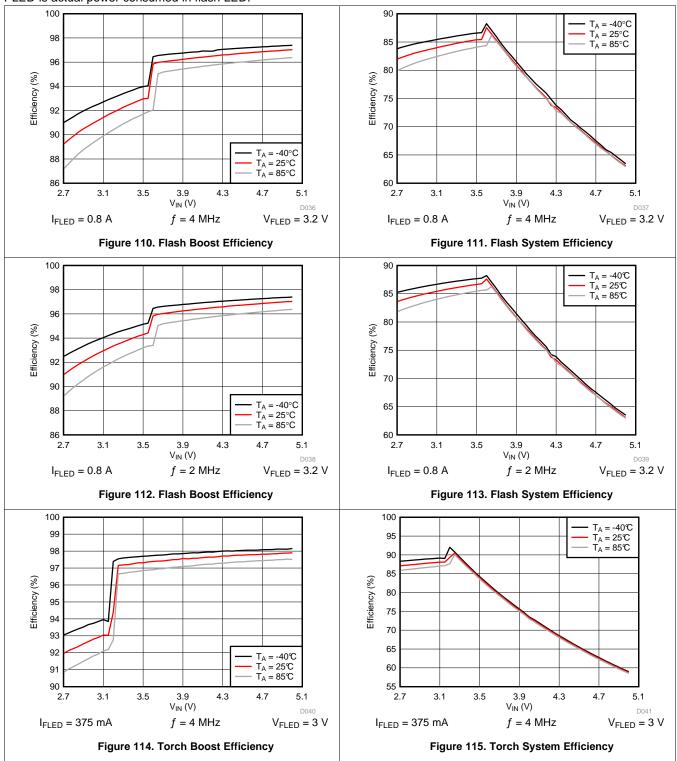

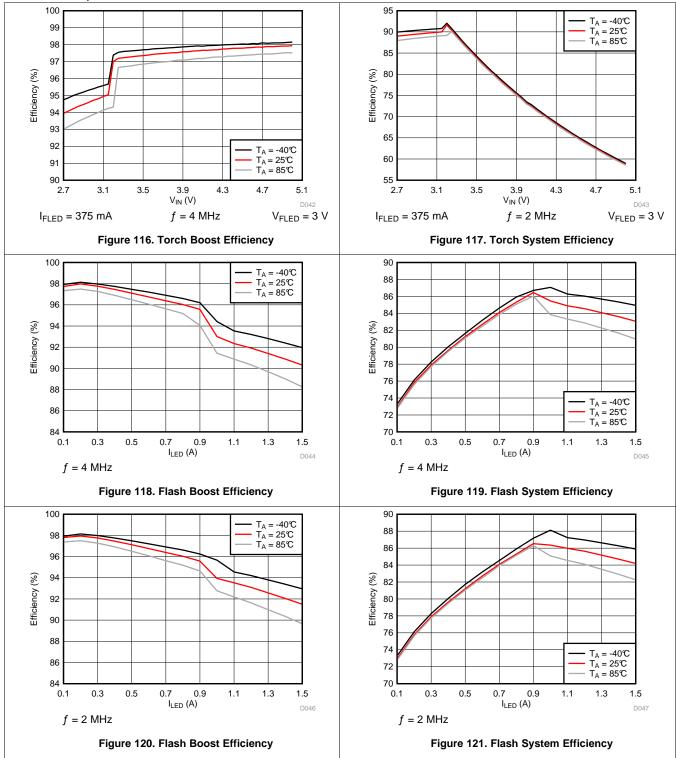

Ambient temperature is 25°C and V<sub>IN</sub> is 3.7 V unless otherwise noted.

## **Typical Characteristics (continued)**

Ambient temperature is 25°C and  $V_{IN}$  is 3.7 V unless otherwise noted.

## **Typical Characteristics (continued)**

Ambient temperature is 25°C and  $V_{IN}$  is 3.7 V unless otherwise noted.

## **Typical Characteristics (continued)**

Ambient temperature is 25°C and  $V_{IN}$  is 3.7 V unless otherwise noted.

## 7 Detailed Description

## 7.1 Overview

The LM3632A is a single-chip complete backlight, LCM power and flash solution. The device operates over the 2.7-V to 5-V input voltage range.

The LM3632A can drive up to two LED strings with up to 8 LEDs each (up to 28 V typical), with a maximum of 25 mA per string. The power for the LED strings comes from a integrated asynchronous backlight boost converter with two selectable switching frequencies to optimize performance or solution area. LED current is regulated by two low-headroom current sinks. Automatic voltage scaling adjusts the output voltage of the backlight boost converter to minimize the LED driver headroom voltage. The 11-bit LED current is set via an I<sup>2</sup>C interface, via a logic level PWM input, or a combination of both.

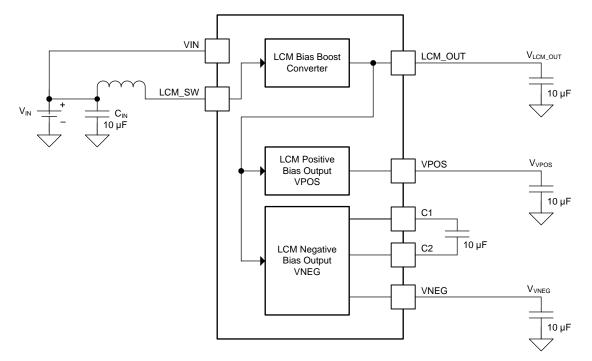

The LCM bias power portion of the LM3632A consists of a synchronous LCM bias boost converter, inverting charge pump, and an integrated LDO. The LCM positive bias voltage  $V_{POS}$  (up to 6 V) is post-regulated from the LCM bias boost converter output voltage. The LCM negative bias voltage  $V_{NEG}$  (down to -6 V) is generated from the LCM bias boost converter output using a regulated inverting charge pump.

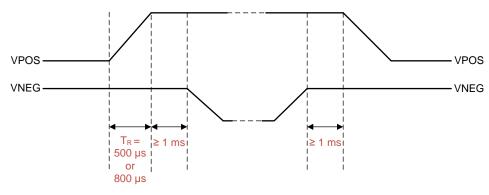

The flash driver consists of a synchronous boost converter and a 1.5-A constant current LED driver. The highside current source allows for grounded cathode LED operation providing flash current up to 1.5 A. An adaptive regulation method ensures the current source remains in regulation and maximizes efficiency.

The LM3632A flexible control interface consists of an EN active low reset input, LCM\_EN1 and LCM\_EN2 inputs for  $V_{POS}$  and  $V_{NEG}$  enable control, PWM input for content adaptive backlight control (CABC), a TX flash interrupt input, and an I<sup>2</sup>C-compatible interface.

Additionally, there are two flag registers with flag and status bits. The user can read back these registers and determine if a fault or warning message has been generated.

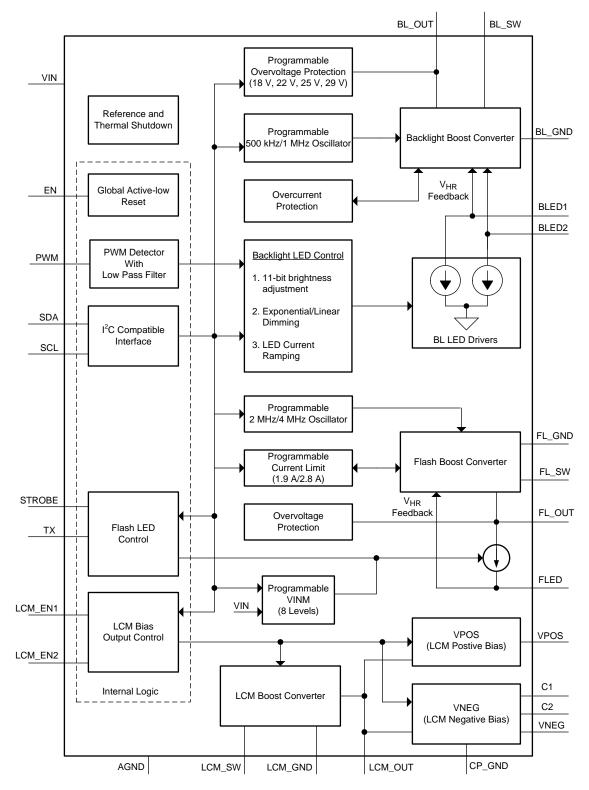

## 7.2 Functional Block Diagram

### 7.3 Features Description

The backlight is enabled if the BL\_EN bit (bit[0] in reg[0x0A]) is set to '1', at least one of the backlight sink outputs is enabled (bit[3] and/or bit[4] in reg[0x0A]), and the brightness value is different than 0. When the brightness value is 0 or the BL\_EN bit is '0', the backlight is disabled.

## 7.3.1.1 Brightness Control

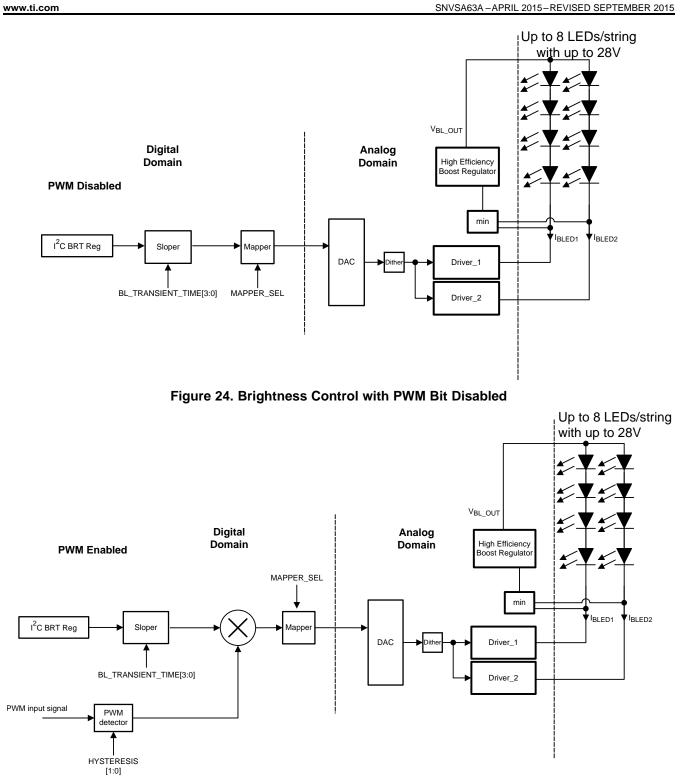

Brightness can be controlled either by the I<sup>2</sup>C brightness register or a combination of the external PWM control and the I<sup>2</sup>C brightness register. The backlight truth table is shown in Table 1.

When controlling brightness through I<sup>2</sup>C, registers 0x04 and 0x05 are used. Registers 0x04 and 0x05 hold the 11-bit brightness data. Register 0x04 contains the 3 LSBs, and register 0x05 contains the 8 MSBs. The LED current transitions to the new level after a write is done to register 0x05.

When controlling brightness through  $l^2C$ , setting the brightness value to '0' shuts down the backlight. When controlling the brightness with PWM input, if PWM input is low for a certain period of time (25 ms typ.), the backlight shuts down. When using the combination of a PWM input and the  $l^2C$  register, either option shuts down the backlight.

| EN PIN | BL_EN<br>0x0A[0] | BLED1_EN<br>0x0A[4] | BLED2_EN<br>0x0A[3] | PWM_EN<br>0x09[6] | ACTION                                                  |

|--------|------------------|---------------------|---------------------|-------------------|---------------------------------------------------------|

| 0      | Х                | Х                   | Х                   | Х                 | Shutdown                                                |

| 1      | 0                | Х                   | Х                   | Х                 | Standby                                                 |

| 1      | 1                | 0                   | 0                   | Х                 | Bias enable                                             |

| 1      | 1                | 1                   | 0                   | 0                 | BLED1 ramp to target current                            |

| 1      | 1                | 0                   | 1                   | 0                 | BLED1 & BLED2 ramp-to-target current                    |

| 1      | 1                | 1                   | 1                   | 0                 | BLED1 & BLED2 ramp-to-target current                    |

| 1      | 1                | 1                   | 0                   | 1                 | BLED1 ramp to (target current × PWM duty cycle)         |

| 1      | 1                | 0                   | 1                   | 1                 | BLED1 & BLED2 ramp to (target current × PWM duty cycle) |

| 1      | 1                | 1                   | 1                   | 1                 | BLED1 & BLED2 ramp to (target current × PWM duty cycle) |

#### Table 1. Backlight Truth Table

#### 7.3.1.1.1 LED Current with PWM Disabled

When LED brightness is controlled from the I<sup>2</sup>C brightness registers, the 11-bit brightness data directly controls the LED current in BLED1 and BLED2. LED mapping can be selected as either linear or exponential. When this mode is selected, setting the PWM input to 0 does not disable the backlight.

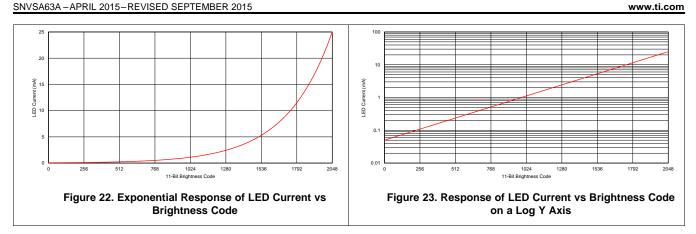

With exponential mapping the 11-bit code-to-current response is approximated by the equation:

$I_{LED} = 50 \ \mu A \times 1.003040572^{I2C \ BRGT \ CODE}$  (for codes > 0)

(1)

Equation 1 is valid for I<sup>2</sup>C brightness codes between 1 and 2047. Code 0 disables the backlight. The Code-to-LED current response realizes a 0.304% change in LED current per LSB of brightness code.

Figure 22 and Figure 23 detail the exponential response of the LED current vs. brightness code. Figure 22 shows the response on a linear Y axis while Figure 23 shows the response on a log Y axis to show the low current levels at the lower codes.

TEXAS INSTRUMENTS

With linear mapping the 11-bit code to current response is approximated by the equation:

I<sub>LED</sub> = 37.8055 μA + 12.1945 μA × I2C BRGT CODE (for codes > 0)

(2)

(3)

(4)

Equation 2 is valid for codes between 1 and 2047. Code 0 disables the backlight.

#### 7.3.1.1.2 LED Current with PWM Enabled

When LED brightness is controlled with the combination of I<sup>2</sup>C register and the PWM duty cycle, the multiplication result of I<sup>2</sup>C register value and PWM duty cycle controls the LED current in BLED1 and BLED2. LED mapping can be selected as either linear or exponential.

With exponential mapping the multiplication result-to-current response is approximated by the equation:

$I_{LED} = 50 \ \mu A \times 1.003040572^{I2C} \ BRGT \ CODE \times PWM \ D/C$

Equation 3 is valid for brightness values other than 0. Brightness value 0 (PWM D/C or I2C BRGT CODE) disables the backlight.

With linear mapping the PWM duty cycle-to-current response is approximated by the equation:

$I_{LED}$  = 37.8055 µA + (12.1945 µA × I2C BRGT CODE × PWM D/C)

Equation 4 is valid for brightness values other than 0. Brightness value 0 (PWM D/C or I2C BRGT CODE) disables the backlight.

LM3632A SNVSA63A – APRIL 2015–REVISED SEPTEMBER 2015

Figure 25. Brightness Control with PWM Bit Enabled

LM3632A SNVSA63A – APRIL 2015–REVISED SEPTEMBER 2015

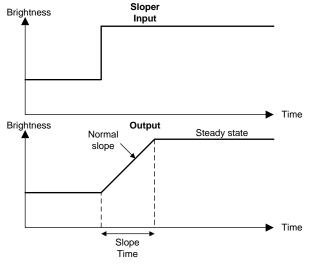

#### 7.3.1.2 Sloper

The sloper smooths the transition from one brightness value to another. Slope time can be adjusted from 0 ms to 8000 ms with BL\_TRANS[3:0] bits (see Table 9 for details). Transient time is used for sloping up and down. Transient time always remains the same regardless of the amount of change in brightness.

Figure 26. Sloper

## 7.3.1.3 Mapper

The mapper block maps the digital word set for the LED driver into current code. The user can select whether the mapping is exponential or linear with the BLED\_MAP bit, register 0x02 bit[4].

Exponential control is tailored to the response of the human eye such that the perceived change in brightness during ramp up or ramp down is linear.

#### 7.3.1.4 PWM Input

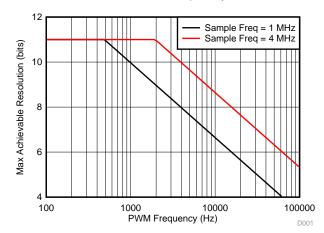

The PWM detector block measures the duty cycle in the PWM pin. The PWM period is measured from the rising edge to the next rising edge. PWM polarity can be changed with bit PWM\_CONFIG, register 0x02 bit[3]. The sample rate for the PWM input can be set to 1 MHz or 4 MHz with bit PWM\_FREQ, register 0x03 bit[2]. The choice of sample rate depends on three factors:

- 1. Required PWM resolution (input duty cycle to brightness code, with 11 bits max)

- 2. PWM input frequency

- 3. Efficiency

The PWM input block timeout is 25 ms for 1-MHz sampling frequency and 3 ms for 4-MHz sampling frequency, measured from the last rising edge. This should be taken into account for 0% and 100% brightness settings (for setting 100% brightness, the high level of PWM input signal should be greater than the PWM input timeout) and for selecting the minimum PWM input signal frequency.

## 7.3.1.5 PWM Minimum On/Off Time

The minimum PWM input signal allowed for low and high pulse width is 6  $\mu$ s for 1-MHz sampling frequency and 1.5  $\mu$ s for 4-MHz sampling frequency. This should be taken into account when selecting the PWM input signal frequency and maximum or minimum duty cycle. For example, if the PWM input signal frequency is 2 kHz (500  $\mu$ s) and the 4-MHz sampling frequency is used, the maximum allowed on-time is: (500 – 1.5)  $\mu$ s = 498.5  $\mu$ s. The maximum duty cycle allowed is 100 × (498.5/500) = 99.7%. By comparison, following similar calculations, with a PWM input signal frequency of 20 kHz the maximum allowed duty cycle is 97%.

## NOTE

If the Minimum Off Time requirement is violated, there may be a range of duty cycle values in which flickering of the LEDs may occur or the LEDs may turn off completely. As the duty cycle increases farther and approaches 100%, the LEDs will turn on at full brightness level. This is due to the algorithm used by the device to detect 100% duty cycle in conjunction with the minimum low pulse width requirement discussed in this section. To avoid LED flickering and/or the LEDs turning off at high PWM duty cycles, the PWM Minimum On/Off Time requirement should be met.

## 7.3.1.6 PWM Resolution and Input Frequency Range

The PWM input resolution depends on the input signal frequency. To achieve the full 11-bit maximum resolution of PWM duty cycle to the LED brightness code, the input PWM duty cycle must be  $\geq$  11 bits, and the PWM sample period (1/f<sub>SAMPLE</sub>) must be smaller than the minimum PWM input pulse width. Figure 27 shows the possible brightness code resolutions based on the input PWM frequency. The minimum recommended PWM frequency is 100 Hz, and maximum recommended PWM frequency is 20 kHz.

Figure 27. PWM Resolution and PWM Input Frequency

## 7.3.1.7 PWM Hysteresis

To prevent jitter in the input PWM signal from feeding through the PWM path and causing oscillations in the LED current, the LM3632A offers 4 programmable PWM hysteresis settings. Hysteresis works by forcing a specific number of 11-bit LSB code transitions to occur in the input duty cycle before the LED current changes. Table 9 describes the hysteresis. Hysteresis only applies during the change in direction of brightness currents. Once the change in direction has taken place, the PWM input must overcome the required LSB(s) of the hysteresis setting before the brightness change takes effect. Once the initial hysteresis has been overcome and the direction in brightness change remains the same, the PWM-to-current response changes with no hysteresis. Hysteresis is selected with the PWM\_HYST bits, register 0x03 bits[1:0]. Changing the hysteresis value is recommended when PWM input frequency increases.

## 7.3.1.8 PWM Timeout

The LM3632A PWM timeout feature turns off the backlight boost output when the PWM input is enabled and there is no PWM pulse detected. The timeout duration depends on the PWM sample rate setting and defines the minimum supported PWM input frequency. Table 2 summarizes the sample rate, timeout, and minimum supported PWM frequency.

| SAMPLE RATE | TIMEOUT | MINIMUM SUPPORTED PWM<br>FREQUENCY |

|-------------|---------|------------------------------------|

| 1 MHz       | 25 msec | 48 Hz                              |

| 4 MHz       | 3 msec  | 400 Hz                             |

Table 2. PWM Timeout and Minimum Supported PWM Frequency vs PWM Sample Rate

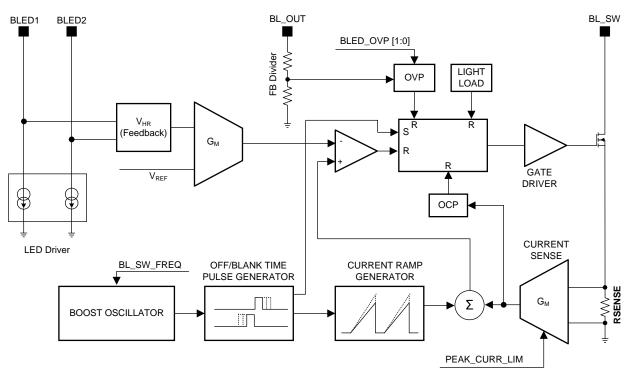

#### 7.3.1.9 Backlight Boost Converter

The high voltage required by the LED strings is generated with an asynchronous backlight boost converter. An adaptive voltage control loop automatically adjusts the output voltage based on the voltage over the LED drivers BLED1 and BLED2.

The LM3632A has two switching frequency modes, 500 kHz and 1 MHz. These are set via the BL\_FREQ Select bit, register 0x03 bit[7]. Operation in low-frequency mode results in better efficiency at lighter load currents due to the decreased switching losses. Operation in high-frequency mode gives better efficiency at higher load currents due to the reduced inductor current ripple and the resulting lower conduction losses in the MOSFETs and inductor.

Figure 28. Backlight Boost Block Diagram

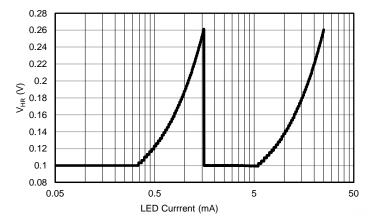

#### 7.3.1.9.1 Headroom Voltage

In order to optimize efficiency, the LED driver-regulated headroom voltage ( $V_{HR}$ ) changes with the programmed LED current. This allows for increased solution efficiency as the dropout voltage of the LED driver changes. Furthermore, in order to ensure that both current sinks remain in regulation when there is a mismatch in string voltages, the minimum headroom voltage between  $V_{BLED1}$  and  $V_{BLED2}$  becomes the regulation point for the boost converter. For example, if the LEDs connected to BLED1 require 25 V at the programmed current, and the LEDs connected to BLED2 require 25.5 V at the programmed current, the voltage at BLED1 is  $V_{HR}$  + 0.5 V, and the voltage at BLED2 is  $V_{HR}$ . In other words, the cathode of the highest voltage LED string becomes the boost output regulation point.

Figure 29. Regulated Headroom vs LED Current

#### 7.3.1.9.2 Backlight Protection and Faults

#### 7.3.1.9.2.1 Overvoltage Protection (OVP) and Open-Load Fault Protection

The LM3632A provides an OVP that monitors the LED boost output voltage ( $V_{BL_OUT}$ ) and protects BL\_OUT and BL\_SW from exceeding safe operating voltages. The OVP threshold can be set to 18 V, 22 V, 25 V or 29 V with register 0x02 bits[7:5]. Once an OVP event has been detected, the BL\_OVP flag is set in the Flags1 register, and the subsequent behavior depends on the state of bit BL\_OVP\_SET in the Enable Register: If BL\_OVP\_SET is set to '0', as soon as  $V_{BL_OUT}$  falls below the backlight OVP threshold, the LM3632A begins switching again. If BL\_OVP\_SET is set to '1' and the device detects three occurrences of  $V_{BL_OUT} > V_{OVP_BL}$  while any of the enabled current sink headroom voltages drops below 40 mV, the BL\_OVP flag is set, the Backlight Enable bit is cleared, and the LM3632A enters standby mode. When the device is shut down due to a BL\_OVP fault the Flags1 register must be read back before the device can be reenabled.

#### 7.3.1.9.2.2 Overcurrent Protection (OCP) and Overcurrent Protection Flag