# LM3477/LM3477A High Efficiency High-Side N-Channel Controller for Switching Regulator

## **General Description**

The LM3477/A is a high-side N-channel MOSFET switching regulator controller. It can be used in topologies requiring a high side MOSFET such as buck, inverting (buck-boost) and zeta regulators. The LM3477/A's internal push pull driver allows compatibility with a wide range of MOSFETs. This, the wide input voltage range, use of discrete power components and adjustable current limit allows the LM3477/A to be optimized for a wide variety of applications.

The LM3477/A uses a high switching frequency of 500kHz to reduce the overall solution size. Current-mode control requires only a single resistor and capacitor for frequency compensation. The current mode architecture also yields superior line and load regulation and cycle-by-cycle current limiting. A 5 $\mu$ A shutdown state can be used for power savings and for power supply sequencing. Other features include internal soft-start and output over voltage protection. The internal soft-start reduces inrush current. Over voltage protection is a safety feature to ensure that the output voltage stays within regulation.

The LM3477A is similar to the LM3477. The primary difference between the two is the point at which the device transitions into hysteretic mode. The hysteretic threshold of the LM3477A is one-third of the LM3477.

#### **Features**

- 500kHz switching frequency

- Adjustable current limit

- 1.5% reference

- Thermal shutdown

- Frequency compensation optimized with a single capacitor and resistor

- Internal softstart

- Current mode operation

- Undervoltage lockout with hysteresis

- 8-lead Mini-SO8 (MSOP-8) package

## **Applications**

- Local Voltage Regulation

- Distributed Power

- Notebook and Palmtop Computers

- Internet Appliances

- Printers and Office Automation

- Battery operated Devices

- Cable Modems

- Battery Chargers

|         | Hysteretic<br>Threshold |

|---------|-------------------------|

| LM3477  | ≈ 36% of                |

|         | programmed current      |

|         | limit                   |

| LM3477A | ≈ 12% of                |

|         | programmed current      |

|         | limit                   |

$<sup>{}^{*}\</sup>mathsf{See}$  Hysteretic Threshold and section for more information.

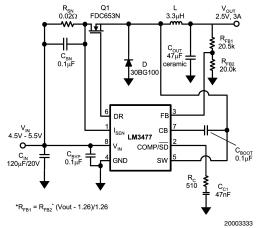

## **Typical Application Circuit**

Typical High Efficiency Step-Down (Buck) Converter

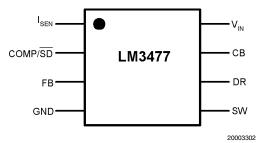

# **Connection Diagram**

8 Lead Mini SO8 Package (MSOP-8 Package)

# **Package Marking and Ordering Information**

| Order Number | Package Type | Package Marking | Supplied As:                |  |

|--------------|--------------|-----------------|-----------------------------|--|

| LM3477MM     | MSOP-8       | S13B            | 1000 units on Tape and Reel |  |

| LM3477MMX    | MSOP-8       | S13B            | 3500 units on Tape and Reel |  |

| LM3477AMM    | MSOP-8       | S13A            | 1000 units on Tape and Reel |  |

| LM3477AMMX   | MSOP-8       | S13A            | 3500 units on Tape and Reel |  |

# **Pin Description**

| Pin Name         | Pin Number | Description                                                                         |

|------------------|------------|-------------------------------------------------------------------------------------|

| I <sub>SEN</sub> | 1          | Current sense input pin. Voltage generated across an external sense resistor is fed |

|                  |            | into this pin.                                                                      |

| COMP/SD          | 2          | Compensation pin. A resistor-capacitor combination connected to this pin provides   |

|                  |            | compensation for the control loop. Pull this pin below 0.65V to shutdown.           |

| FB               | 3          | Feedback pin. The output voltage should be adjusted using a resistor divider to     |

|                  |            | provide 1.270V at this pin.                                                         |

| GND              | 4          | Ground pin.                                                                         |

| SW               | 5          | Switch Node. Source of the external MOSFET is connected to this node.               |

| DR               | 6          | Drive pin. The gate of the external MOSFET should be connected to this pin.         |

| СВ               | 7          | Boot-strap pin. A capacitor must be connected between this pin and SW pin (pin 5)   |

|                  |            | for proper operation. The voltage developed across this capacitor provides the gate |

|                  |            | drive for the external MOSFET.                                                      |

| V <sub>IN</sub>  | 8          | Power Supply Input pin.                                                             |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Input Voltage 36V

Peak Driver Output Current (<10µs) 1.0A

CB Pin Voltage (Note 2) 43V

I<sub>SEN</sub> Pin Voltage 500mV

Power Dissipation Internally Limited

Storage Temperature Range -65°C to +150°C

Junction Temperature +150°C

ESD Susceptibilty (Note 3)

Human Body Model 2kV Machine Model 200V Lead Temperature for MSOP Package

Vapor Phase (60 sec.) 215°C Infared (15 sec.) 220°C

## **Operating Ratings** (Note 1)

Supply Voltage  $2.97V \le V_{IN} \le 35V$

Junction

Temperature Range  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$

## **Electrical Characteristics** (Note 4)

Specifications in Standard type face are for  $T_J = 25^{\circ}C$ , and in **bold type face** apply over the full **Operating Temperature Range**. Unless otherwise specified,  $V_{IN} = 12V$ .

| Symbol                                             | Parameter                            | Conditions                     | Typical         | Limit               | Units     |

|----------------------------------------------------|--------------------------------------|--------------------------------|-----------------|---------------------|-----------|

| $V_{FB}$                                           | Feedback Voltage                     | $V_{COMP} = 1.4V,$             | 1.270           |                     | V         |

|                                                    |                                      | $2.97V \le V_{IN} \le 36V$     |                 | 1.260/ <b>1.252</b> | V(min)    |

|                                                    |                                      |                                |                 | 1.288/ <b>1.290</b> | V(max)    |

| $\Delta V_{LINE}$                                  | Feedback Voltage Line<br>Regulation  | $2.97V \le V_{IN} \le 36V$     | 0.001           |                     | %/V       |

| $\Delta V_{LOAD}$                                  | Output Voltage Load Regulation       |                                | ±0.5            |                     | %/V (max) |

| V <sub>UVLO</sub>                                  | Input Undervoltage Lock-out          |                                | 2.87            |                     | V         |

|                                                    |                                      |                                |                 | 2.97                | V(max)    |

| V <sub>UV(HYS)</sub>                               | Input Undervoltage Lock-out          |                                | 180             |                     | mV        |

| , ,                                                | Hysteresis                           |                                |                 | 130                 | mV (min)  |

|                                                    |                                      |                                |                 | 225                 | mV (max)  |

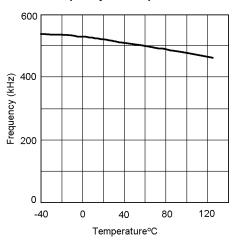

| F <sub>sw</sub>                                    | Switching Frequency                  |                                | 500             |                     | kHz       |

|                                                    |                                      |                                |                 | 435                 | kHz(min)  |

|                                                    |                                      |                                |                 | 575                 | kHz(max)  |

| R <sub>DS1 (ON)</sub>                              | Driver Switch On Resistance (top)    | $I_{DR} = 0.2A, V_{IN} = 5V$   | 7               |                     | Ω         |

| R <sub>DS2 (ON)</sub>                              | Driver Switch On Resistance (bottom) | I <sub>DR</sub> = 0.2A         | 4               |                     | Ω         |

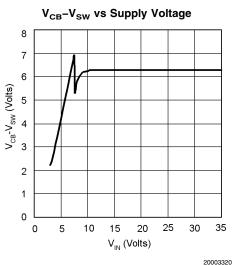

| (V <sub>CB</sub> -V <sub>SW</sub> ) <sub>max</sub> | Maximum Boot Voltage                 | V <sub>IN</sub> < 7.2V         | V <sub>IN</sub> |                     | V         |

|                                                    |                                      | V <sub>IN</sub> ≥ 7.2V         | 7.2             |                     |           |

| D <sub>max</sub>                                   | Maximum Duty Cycle                   |                                | 93              |                     | %         |

| max                                                |                                      |                                |                 | 88                  | %(min)    |

| T <sub>min</sub> (on)                              | Minimum On Time                      |                                | 330             |                     | nsec      |

|                                                    |                                      |                                |                 | 230                 | nsec(min) |

|                                                    |                                      |                                |                 | 495                 | nsec(max) |

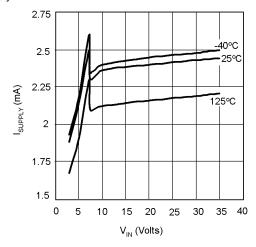

| I <sub>SUPPLY</sub>                                | Supply Current (switching)           | (Note 5)                       | 2.0             |                     | mA        |

|                                                    |                                      |                                |                 | 3.0                 | mA (max)  |

| IQ                                                 | Quiescent Current in Shutdown        | (Note 6), V <sub>IN</sub> = 5V | 5               |                     | μA        |

|                                                    | Mode                                 |                                |                 | 8                   | μA (max)  |

## Electrical Characteristics (Note 4) (Continued)

Specifications in Standard type face are for  $T_J = 25^{\circ}C$ , and in **bold type face** apply over the full **Operating Temperature Range**. Unless otherwise specified,  $V_{IN} = 12V$ .

| Symbol                                                   | Parameter                         | Conditions                                      | Typical | Limit                                 | Units     |

|----------------------------------------------------------|-----------------------------------|-------------------------------------------------|---------|---------------------------------------|-----------|

| V <sub>CL(O)</sub> Current Limit Voltage at 0% Dut Cycle | Current Limit Voltage at 0% Duty  | LM3477                                          | 155     |                                       | mV        |

|                                                          | Cycle                             |                                                 |         | 130/ <b>125</b>                       | mV (min)  |

|                                                          |                                   |                                                 |         | 185/ <b>190</b>                       | mV (max)  |

|                                                          |                                   | LM3477A                                         | 165     |                                       | mV        |

|                                                          |                                   |                                                 |         | 140/ <b>135</b>                       | mV (min)  |

|                                                          |                                   |                                                 |         | 195/ <b>200</b>                       | mV (max)  |

| V <sub>CL(100)</sub>                                     | Current Limit Voltage at 100%     | LM3477                                          | 74      |                                       | mV        |

| CL(100)                                                  | Duty Cycle                        |                                                 |         | 50/ <b>43</b>                         | mV (min)  |

|                                                          |                                   |                                                 |         | 98/ <b>98</b>                         | mV (max)  |

|                                                          |                                   | LM3477A                                         | 65      | 00,00                                 | mV        |

|                                                          |                                   | EWO-1771                                        |         | 41/25                                 | mV (min)  |

|                                                          |                                   |                                                 |         | 89/ <b>98</b>                         | mV (max)  |

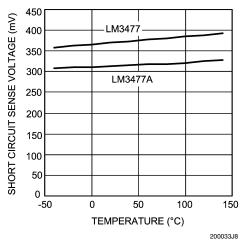

| \ /                                                      | Chart Circuit Comment Limit Comes | \/ 5\/   M0477                                  | 250     | 09/90                                 |           |

| $V_{SC}$                                                 | Short-Circuit Current Limit Sense | V <sub>IN</sub> = 5V, LM3477                    | 350     | 070                                   | mV        |

|                                                          | Voltage                           |                                                 |         | 270                                   | mV (min)  |

|                                                          |                                   |                                                 |         | 420                                   | mV (max)  |

|                                                          |                                   | V <sub>IN</sub> = 5V, LM3477A                   | 310     |                                       | mV        |

|                                                          |                                   |                                                 |         | 260                                   | mV (min)  |

|                                                          |                                   |                                                 |         | 380                                   | mV (max)  |

| V <sub>SL</sub>                                          | Internal Compensation Ramp        | V <sub>IN</sub> = 5V, LM3477                    | 83      |                                       | mV        |

|                                                          | Voltage Height                    | V <sub>IN</sub> = 5V, LM3477A                   | 103     |                                       |           |

| V <sub>OVP</sub>                                         | Output Over-voltage Protection    | $V_{COMP} = 1.4V$                               | 50      |                                       | mV        |

| - 006                                                    | (with respect to feedback         | - COMP                                          |         | 32/ <b>25</b>                         | mV(min)   |

|                                                          | voltage) (Note 7)                 |                                                 |         | 78/ <b>85</b>                         | mV(max)   |

| \/                                                       | Output Over-Voltage Protection    | V <sub>COMP</sub> = 1.4V                        | 60      |                                       | mV        |

| $V_{OVP(HYS)}$                                           | 1 .                               | V <sub>COMP</sub> = 1.4V                        | 60      | 00                                    |           |

|                                                          | Hysteresis(Note 7)                |                                                 |         | 20                                    | mV(min)   |

|                                                          |                                   |                                                 |         | 110                                   | mV(max)   |

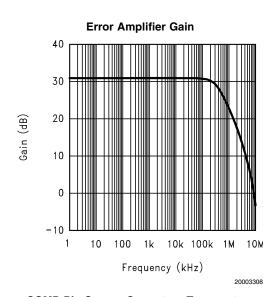

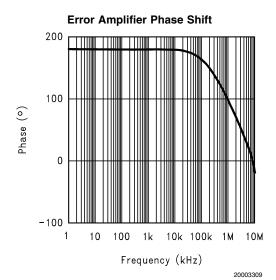

| Gm                                                       | Error Amplifier                   | $V_{COMP} = 1.4V$                               | 750     |                                       | μmho      |

|                                                          | Transconductance                  | $I_{EAO} = 100\mu A$                            |         | 600/ <b>365</b>                       | µmho (min |

|                                                          |                                   | (Source/Sink)                                   |         | 1000/ <b>1265</b>                     | µmho (max |

| $A_{VOL}$                                                | Error Amplifier Voltage Gain      | $V_{COMP} = 1.4V$                               | 38      |                                       | V/V       |

|                                                          |                                   | I <sub>EAO</sub> = 100μA                        |         | 30                                    | V/V (min) |

|                                                          |                                   | (Source/Sink)                                   |         | 42                                    | V/V (max) |

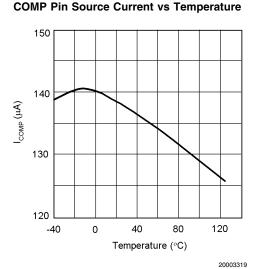

| EAO                                                      | Error Amplifier Output Current    | Source, V <sub>COMP</sub> = 1.4V,               | 100     |                                       | μA        |

| LAO                                                      | (Source/ Sink)                    | V <sub>FB</sub> = 0V                            |         | 75/ <b>50</b>                         | μA (min)  |

|                                                          | ,                                 | LP -                                            |         | 130/ <b>160</b>                       | μA (max)  |

|                                                          |                                   | Sink, V <sub>COMP</sub> = 1.4V, V <sub>FB</sub> | -140    |                                       | μΑ        |

|                                                          |                                   | = 1.4V                                          | 140     | -110/ <b>-95</b>                      | μΑ (min)  |

|                                                          |                                   | _ 1.TV                                          |         | -170/ <b>-95</b><br>-170/ <b>-180</b> | 1 ' ' '   |

|                                                          | Fuser Amendifies October 137 II   | Hanny Live-14                                   | 0.0     | -170/-100                             | μA (max)  |

| $V_{EAO}$                                                | Error Amplifier Output Voltage    | Upper Limit                                     | 2.2     |                                       | V         |

|                                                          | Swing                             | V <sub>FB</sub> = 0V                            |         | 2.0                                   | V(min)    |

|                                                          |                                   | COMP Pin = Floating                             |         | 2.35                                  | V(max)    |

|                                                          |                                   | Lower Limit                                     | 0.75    |                                       | V         |

|                                                          |                                   | V <sub>FB</sub> = 1.4V                          |         | 0.5                                   | V(min)    |

|                                                          |                                   |                                                 |         | 0.95                                  | V(max)    |

| T <sub>ss</sub>                                          | Internal Soft-Start Delay         | V <sub>FB</sub> = 1.2V, V <sub>COMP</sub> =     | 5       |                                       | msec      |

|                                                          |                                   | Floating                                        |         |                                       |           |

| T <sub>r</sub>                                           | Drive Pin Rise Time               | $C_{GS} = 3000 pF, V_{DR} = 0$ to 3V            | 25      |                                       | ns        |

| T <sub>f</sub>                                           | Drive Pin Fall Time               | $C_{GS} = 3000 pF, V_{DR} = 0$ to 3V            | 25      |                                       | ns        |

## Electrical Characteristics (Note 4) (Continued)

Specifications in Standard type face are for  $T_J = 25^{\circ}C$ , and in **bold type face** apply over the full **Operating Temperature Range**. Unless otherwise specified,  $V_{IN} = 12V$ .

| Symbol          | Parameter                   | Conditions           | Typical | Limit | Units   |

|-----------------|-----------------------------|----------------------|---------|-------|---------|

| V <sub>SD</sub> | Shutdown Threshold (Note 8) | Output = High        | 1.15    |       | V       |

|                 |                             |                      |         | 1.35  | V (max) |

|                 |                             | Output = Low         | 0.65    |       | V       |

|                 |                             |                      |         | 0.3   | V (min) |

| I <sub>SD</sub> | Shutdown Pin Current        | $V_{SD} = 5V$        | -1      |       |         |

|                 |                             | V <sub>SD</sub> = 0V | +1      |       | μΑ      |

| TSD             | Thermal Shutdown            |                      | 165     |       | °C      |

| T <sub>SH</sub> | Thermal Shutdown Hysteresis |                      | 10      |       | °C      |

| $\theta_{JA}$   | Thermal Resistance          | MM Package           | 200     |       | °C/W    |

## Electrical Characteristics (Note 4) (Continued)

**Note 1:** Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions under which operation of the device is intended to be functional. For guaranteed specifications and test conditions, see the Electrical Characteristics.

Note 2: The CB pin must not be higher than 8V above the V<sub>SW</sub>.

Note 3: The human body model is a 100 pF capacitor discharged through a  $1.5 k\Omega$  resistor into each pin. The machine model is 200 pF capacitor discharged directly into each pin.

**Note 4:** All limits are guaranteed at room temperature (standard type face) and at **temperature extremes (bold type face)**. All room temperature limits are 100% tested. All limits at **temperature extremes** are guaranteed via correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

Note 5: For this test, the COMP/SD pin must be left floating.

Note 6: For this test, the COMP/SD pin must be pulled low.

Note 7: The over-voltage protection is specified with respect to the feedback voltage. This is because the over-voltage protection tracks the feedback voltage. The over-voltage protection threshold is given by adding the feedback voltage, V<sub>FB</sub> to the over-voltage protection specification.

Note 8: The COMP/SD pin should be pulled to ground to turn the regulator off. The voltage on the COMP/SD pin must be below the limit for Output = Low to keep the regulator off.

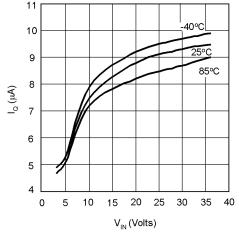

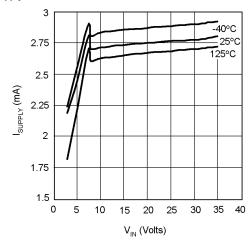

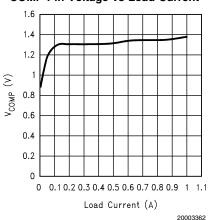

## Typical Performance Characteristics Unless otherwise specified, $V_{IN}$ = 12V, $T_J$ = 25°C.

I<sub>Q</sub> (Shutdown) vs Temperature & Supply Voltage

20003313

$I_{Supply}$  vs Temperature & Supply Voltage (Switching)

20003315

I<sub>Supply</sub> vs Temperature & Supply Voltage (Non-Switching)

20003314

Frequency vs Temperature

20003316

**COMP Pin Voltage vs Load Current**

# Typical Performance Characteristics Unless otherwise specified, $V_{IN}$ = 12V, $T_J$ = 25°C. (Continued)

200033K2

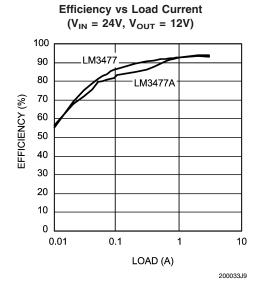

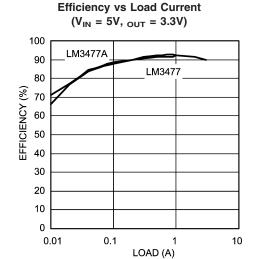

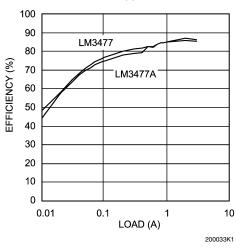

**Efficiency vs Load Current**

# Typical Performance Characteristics Unless otherwise specified, $V_{IN}$ = 12V, $T_J$ = 25°C. (Continued)

#### **Short Circuit vs Temperature**

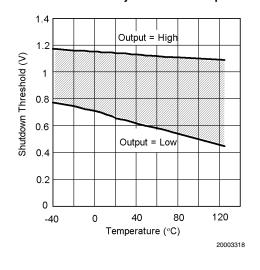

## **Shutdown Threshold Hysteresis vs Temperature**

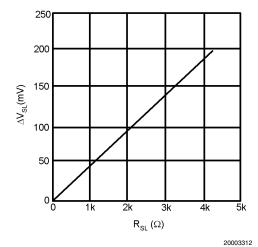

# Slope Compensation Ramp vs Slope Compensation Resistor

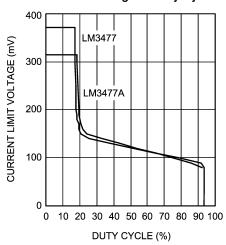

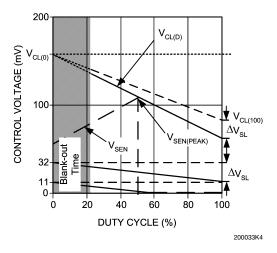

## **Current Sense Voltage vs Duty Cycle**

200033J7

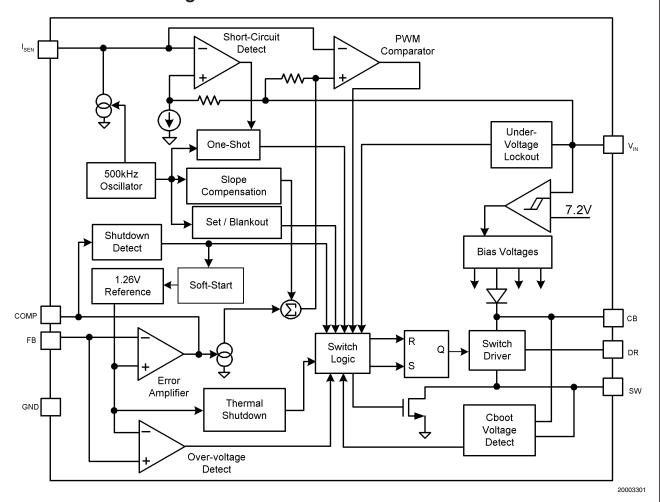

## **Functional Block Diagram**

## **Functional Description**

#### **General Description**

The LM3477/A is a switching regulator controller for topologies incorporating a high side switch. The most common of these topologies is the step-down, or buck, converter. Other topologies such as the inverting (buck-boost) and inverse SEPIC (zeta) converters can be realized. This datasheet will focus on buck converter applications.

The LM3477/A employs current mode control architecture. Among the many benefits of this architecture are superior line and load regulation, cycle-by-cycle current limiting, and simple loop compensation. The LM3477/A features a patented adjustable slope compensation scheme to enable flexible inductor selection. The LM3477/A has a combination of features that allow its use in a wide variety of applications. The input voltage can range from 2.97V to 35V, with the output voltage being positive or negative depending on the topology. The current limit can be scaled to safely drive a wide range of loads. An internal soft-start is provided to limit initial in-rush current. Output over voltage and input under voltage protection ensure safe operation of the LM3477/A.

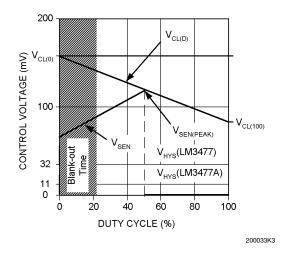

#### **Regions of Operation**

Pulse width modulation (PWM) is the normal mode of operation. In PWM, the output voltage is well regulated and has a ripple frequency equal to the switching frequency (500kHz).

In low load conditions, the part operates in hysteretic mode. In this mode, the output voltage is regulated between a high and low value that results in a higher ripple magnitude and lower ripple frequency than in PWM mode (see *OVER VOLT-AGE PROTECTION* section).

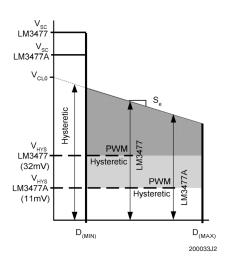

FIGURE 1. Operating Regions of the LM3477/A

## Functional Description (Continued)

The important differences between the LM3477 and the LM3477A are summarized in *Figure 1*. The voltages in *Figure 1* can be referred to the switch current by dividing through by  $R_{SN}$ . The LM3477A has a lower hysteretic threshold voltage  $V_{HYS}$ , and thus will operate in PWM mode for a larger load range than the LM3477. Typically,  $V_{HYS} = 32\text{mV}$  for the LM3477, while  $V_{HYS} = 11\text{mV}$  for the LM3477A. The difference in area between the shaded regions give a graphical representation of this. The lightly shaded region is the extra PWM operating area gained by using the LM3477A. Thus the benefits of operating in PWM mode such as a well regulated output voltage with low noise ripple are extended to a larger load range when the LM3477A is used. While less significant, the other noteworthy difference between the two parts is in the short circuit current limit  $V_{SG}$ .

$\rm V_{SC}$  is a ceiling limit for the peak sense voltage  $\rm V_{SNpk}$  (see the <code>SHORT CIRCUIT CURRENT LIMIT</code> section).  $\rm V_{SC}$  is lower in the LM3477A than in the LM3477 (see the <code>ELECTRICAL CHARACTERISTICS</code> section for limits).

#### **Over Voltage Protection**

The LM3477/A has over voltage protection (OVP) for the output voltage. OVP is sensed at and is in respect to the feedback pin (pin 3). If at anytime the voltage at the feedback pin rises to  $V_{FB} + V_{OVP}$ , OVP is triggered. See *ELECTRICAL CHARACTERISTICS* section for limits on  $V_{FB}$  and  $V_{OVP}$ .

OVP will cause the drive pin to go low, forcing the power MOSFET off. With the MOSFET off, the output voltage will drop. The LM3477/A will begin switching again when the feedback voltage reaches  $V_{\text{FB}}$  +  $(V_{\text{OVP}}$  -  $V_{\text{OVP(HYS)}}$ ). See <code>ELECTRICAL CHARACTERISTICS</code> for limits on  $V_{\text{OVP(HYS)}}$ .

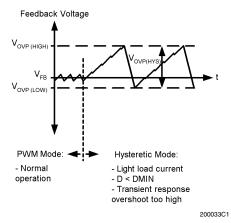

OVP can be triggered by any event that causes the output voltage to rise out of regulation. There are several common circumstances in which this can happen, and it is beneficial for a designer to be aware of these for debugging purposes, since the mode of operation changes from the normal Pulse Width Modulation (PWM) mode to the hysteretic mode. In the hysteretic mode the output voltage is regulated between a high and low value that results in a higher ripple magnitude and lower ripple frequency than in the PWM mode, see Figure 2.

FIGURE 2. The Feedback Voltage is related to the Output Voltage. See different Ripple Components in PWM and Hysteretic Modes

If the load current becomes too low, the LM3477/A will increase the duty cycle, causing the voltage to rise and trigger the OVP. The reasons for this involve the way the LM3477/A regulates the output voltage, using a control waveform at the pulse width modulator. This control waveform has upper and lower bounds.

Another way OVP can be tripped is if the input voltage rises higher than the LM3477/A is able to regulate in pulse width modulation (PWM) mode. The output voltage is related to the input voltage by the duty cycle as:  $V_{\rm OUT} = V_{\rm IN}*D$ . The LM3477/A has a minimum duty cycle of 16.5% (typical), due to the blank-out timing, TMIN. If the input voltage increases such that the duty cycle wants to be less than  $D_{\rm MIN}$ , the duty cycle will hold at  $D_{\rm MIN}$  and the output voltage will increase with the input voltage until it trips OVP.

It is useful to plot the operational boundaries in order to illustrate the point at which the device switches into hysteretic mode. In Figure~1, the limits shown are with respect to the peak voltage across the sense resistor  $R_{\rm SN},~(V_{\rm SNpk});$  they can be referred to the peak inductor current by dividing through by  $R_{\rm SN}.~V_{\rm SNpk}$  is bound to the shaded regions. In normal circumstances  $V_{\rm SNpk}$  is required to be in the shaded region, and the LM3477/A will operate in the PWM mode. If operating conditions are chosen such that  $V_{\rm SNpk}$  would not normally fall in the shaded regions, then the mode of operation is changed so that  $V_{\rm SNpk}$  will be in the shaded region, and the part will operate in the hysteretic mode. What actually happens is that the LM3477/A will not allow  $V_{\rm SNpk}$  to be outside of the shaded regions, so the duty cycle is adjusted.

The output voltage transient response overshoot can also trigger OVP. As discussed in the *OUTPUT CAPACITOR* section, if the capacitance is too low or ESR too high, the output voltage overshoot will rise high enough to trigger OVP. However, as long as there is room for the duty cycle to adjust (the converter is not near  $D_{\text{MIN}}$  or  $D_{\text{MAX}}$ ), the LM3477/A will return to PWM mode after a few cycles of hysteretic mode operation.

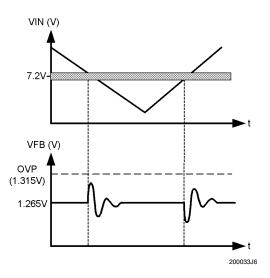

There is one last way that OVP can be triggered. If the unregulated input voltage crosses 7.2V, the output voltage will react as shown in Figure 3. The internal bias of the LM3477/A switches supplies at 7.2V. When this happens, a sudden small change in bias voltage is seen by all the internal blocks of the LM3477/A. The control voltage, VC, shifts because of the bias change, the PWM comparator tries to keep regulation. To the PWM comparator, the scenario is identical to step change in the load current, so the response at the output voltage is the same as would be observed in a step load change. Hence, the output voltage overshoot here can also trigger OVP. The LM3477/A will regulate in hysteretic mode for several cycles, or may not recover and simply stay in hysteretic mode until the load current drops. Note that the output voltage is still regulated in hysteric mode. Predicting whether or not the LM3477/A will come out of hysteretic mode in this scenario is a difficult task, however it is largely a function of the output current and the output capacitance. Triggering hysteretic mode in this way is only possible at higher load currents. The method to avoid this is to increase the output capacitance.

## Functional Description (Continued)

FIGURE 3. The Feedback Voltage Experiences an Oscillation if the Input Voltage Crosses the 7.2V Internal Bias Threshold

#### **Default/Adjustable Slope Compensation**

The LM3477/A uses a current mode control scheme. There are many advantages in a current mode architecture including inherent cycle-by-cycle current limiting and simple compensation of the control loop. However, there are consequences to using current mode control that one must be aware of while selecting circuit components. One of these consequences is the inherent possibility of subharmonic oscillations in the inductor current. This is a form of instability and should be avoided.

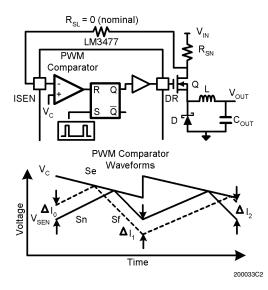

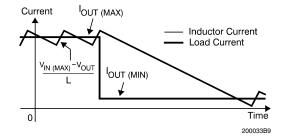

FIGURE 4. The Current Sensing Loop and Corresponding Waveforms

As a brief explanation, consider *Figure 4*. A lot of information is shown here. The top portion shows a schematic of the current sensing loop. The bottom portion shows the pulse width modulation (PWM) comparator waveforms for two

switching cycles. The two solid waveforms shown are the waveforms compared at the internal pulse width modulator, used to generate the MOSFET drive signal. The top waveform with the slope  $S_{\rm e}$  is the internally generated control waveform  $V_C$ . The bottom waveform with slopes  $S_n$  and  $S_f$  is the sensed inductor current waveform V<sub>SEN</sub>. These signals are compared at the PWM comparator. There is a feedback loop involved here. The inductor current is sensed and fed back to the PWM comparator, where it is compared to V<sub>C</sub>. The output of the comparator in combination with the R/S latch determine if the MOSFET is on or off, which effectively controls the amount of current the inductor receives. While  $V_C$  is higher than  $V_{SEN}$ , the PWM comparator outputs a high signal, driving the external power MOSFET on. When MOS-FET is on, the inductor current rises at a constant slope, generating the sensed voltage  $V_{\text{SEN}}.$  When  $V_{\text{SEN}}$  equals  $V_{\text{C}},$ the PWM comparator signals to drive the MOSFET off, and the sensed inductor current decreases with a slope S<sub>f</sub>. The process begins again when R<sub>S</sub> latch is set by an internal

The subharmonic oscillation phenomenon is realized when a load excursion is experienced. The way it is analyzed is to calculate how the inductor current settles after such an excursion. Take for example the case when the inductor current experiences a step increase in its average current, shown as the dotted line in *Figure 4*. In the switching period that the excursion occurs, the inductor current will change by  $\Delta I_0$ . In the following switching period, the inductor current will have a difference  $\Delta I_1$  from its original starting value. The original excursion is being propagated each switching cycle. What is desired is to find out if this propagation is converging or diverging. It is apparent that the difference in the inductor current from one cycle to the next is a function of  $S_n,\,S_f,$  and  $S_e,\,$  as follows:

$$\Delta I_{n} = \frac{S_{f} - S_{e}}{S_{n} + S_{e}} \Delta I_{n-1}$$

Hence, if the quantity  $(S_f - S_e)/(S_n + S_e)$  is greater than 1, the inductor current diverges and subharmonic oscillations result. Notice that as  $S_e$  increases, the factor decreases. Also, when the duty cycle is greater than 50%, as the inductance become less, the factor increases.

The LM3477/A internally generates enough slope compensation  $S_{\rm e}$  to allow for the use of reasonable inductances. The height of the compensation slope ramp  $V_{\rm SL}$  can be found in the <code>ELECTRICAL CHARACTERISTICS</code> section. The LM3477/A incorporates a patented scheme to increase  $S_{\rm e}$  if there is need to use a smaller inductor. With the use of a single resistor  $R_{\rm SL}$ , Se can be increased indefinitely.  $R_{\rm SL}$  increases the compensation slope Se by the amount:

$$\Delta S_{e} = 50 \times 10^{-6} \times f_{S} \times R_{SL} (\frac{V}{\mu s})$$

Therefore,

$$S_e = f_S(V_{SL} + 50 \times 10^{-6} \times R_{SL}) (\frac{V}{\mu s})$$

When excursions of the inductor current are divergent, the current sensing control loop is unstable and produces a subharmonic oscillation in the inductor current. This oscillation is viewed as a resonance in the outer voltage control loop at half the switching frequency. In the inductor section,

## Functional Description (Continued)

calculations for minimum inductance and necessary slope resistance  $R_{\rm SL}$  are carried out based on this resonant peaking.

#### Start-up/Soft-start

The LM3477/A incorporates an internal soft-start during start-up. The soft-start forces the inductor current to rise slowly and smoothly as it increases towards the steady-state current. This technique is used to reduce the input inrush current during soft-start. The soft-start functionality is effective for approximately the first 5ms of start-up.

Note: The LM3477/A will not start-up if the output voltage is being held up externally by more than 200mV.

If the slope resistor  $\rm R_{SL}$  is used, the LM3477/A may need up to 100 mA of pre load to successfully start up.

#### **Short Circuit Protection**

When the voltage across the sense resistor (measured as the  $V_{\rm IN}$  –  $I_{\rm SEN}$  differential voltage) exceeds  $V_{\rm SC}$ , short-circuit current limit gets activated. In the short-circuit protection mode, the external MOSFET is turned off. When the short is removed, the external MOSFET is turned on after five cycles. The short circuit protection voltage  $V_{\rm SC}$  is specified in the <code>ELECTRICAL CHARACTERISTICS</code> section.  $V_{\rm SC}$  is lower in the LM3477A than in the LM3477.

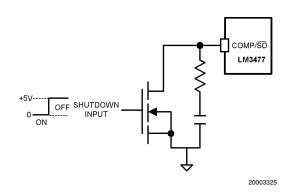

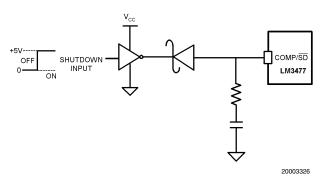

#### Shutdown

The compensation pin (Pin 2) of LM3477/A also functions as a shutdown pin. If a low signal (refer to the *ELECTRICAL CHARACTERISTICS* for definition of low signal) appears on the COMP/ $\overline{SD}$  pin, the LM3477/A stops switching and goes into a low supply current mode. The total supply current of the IC reduces to less than 10µA under these conditions. *Figure 5* shows different implementations of the shutdown function.

FIGURE 5. Implementing Shutdown in LM3477

## **Design Section**

#### General

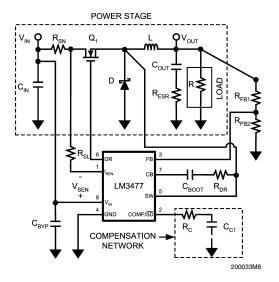

Power supply design involves making tradeoffs. To achieve performance specifications, limitations will be set on component selection. The LM3477/A provides many degrees of flexibility in choosing external components to accommodate various performance/component selection optimizations. For example, the internal slope compensation can be externally increased to allow smaller inductances to be used. The design procedures that follow provide instruction on how to select the external components in a typical LM3477/A buck circuit in continuous conduction mode, as well as aid in the optimization of performance and/or component selection. See *Figure 6* for component reference and typical circuit. The LM3477/A may also be designed to operate in discontinuous conduction mode.

FIGURE 6. LM3477 Buck Converter Reference Schematic

#### **Programming the Output Voltage**

The output voltage can be programmed using a resistor divider between the output and the feedback pins, as shown in *Figure 6*. The resistors are selected such that the voltage at the feedback pin is 1.27V.  $R_{\rm FB1}$  and  $R_{\rm FB2}$  can be selected using the equation:

$$V_{OUT} = 1.27*(1+ R_{FB1}/R_{FB2})$$

#### Calculating the Duty Cycle

In buck converter applications, the duty cycle of the LM3477/A may be calculated as:

$$D = \frac{V_{OUT} + V_{D}}{V_{IN} + V_{D} - V_{Q} - V_{SEN}} \approx \frac{V_{OUT}}{V_{IN}}$$

#### Where

$V_D$  = forward drop of the power diode  $\approx 0.5V$

$V_Q = V_{DS}$  of the MOSFET when it is conducting  $\approx I_{OUT}{}^*R_{DSON}$

$V_{SN}$  = Voltage across the sense resistor =  $I_{OUT}$  x  $R_{SN}$

## **Design Section** (Continued)

This is the fraction of the switching period that the switch is on. The switch is off for the remainder of the period. This fraction is expressed as:

$$D' = 1 - D$$

The LM3477/A has limits for the maximum and minimum duty cycle (see <code>ELECTRICAL CHARACHTERISTICS</code>). The maximum duty cycle of 93% (typical) will limit how low the input voltage may drop while maintaining a regulated output voltage (the dropout voltage). In situations where a very low dropout voltage is required, it is necessary to include  $V_{\rm D},\,V_{\rm Q}$  and  $V_{\rm SN}$  losses in the maximum duty cycle calculation. Voltage drops in the inductor will lower the dropout voltage as well.

The minimum duty cycle of the LM3477/A corresponds to the minimum on time, or blank out time (see *ELECTRICAL CHARACHTERISTICS*).

$$D_{MIN} = T_{MIN} * f_s$$

This will not limit how high the input voltage can rise, however the LM3477/A will operate in hysteretic mode once the operating duty cycle decreases to the minimum duty cycle.

# Programming the Current Limit/Hysteretic Threshold DEFINITIONS:

Current Limit: The current limit is the point at which the LM3477/A begins to limit the peak switch current. The current limit in the LM3477/A varies with duty cycle, which is a function of the  $\rm V_{IN}-\rm V_{OUT}$  differential.

Hysteric Threshold: Hysteretic threshold is the current at which the LM3477/A enters the hysteretic mode of operation (see *OVER VOLTAGE PROTECTION* section). The hysteretic threshold is with respect to the peak switch current.

#### **Setting Current Limit and Hysteretic Threshold**

The adjustable current limit of the LM3477/A is set by the sense resistor  $R_{\rm SN}$ . The voltage across  $R_{\rm SN}$  is compared to an internal control voltage  $V_{\rm C}$ . The onset of current limiting is when  $V_{\rm SEN(peak)}$  equals  $V_{\rm C(max)}$ , or  $V_{\rm CL}$ .  $V_{\rm SEN}$  is defined here as the differential voltage from the  $V_{\rm IN}$  pin to the  $I_{\rm SEN}$  pin.  $V_{\rm CL}$  decreases as the duty cycle increases, as shown in Figure 7. Therefore, it is important to know both  $V_{\rm SEN(peak)}$  and  $V_{\rm CL(min)}$  at the maximum operating duty cycle, or lowest  $V_{\rm IN}$  condition.

FIGURE 7. Current Limit and Hysteretic Threshold vs

Duty Cycle

$$V_{SEN(PEAK)} = R_{SN}(I_{OUT(MAX)} + \frac{V_{OUT}(1-D_{MAX})}{2 \times L \times f_{S}}) (V), R_{SL} = 0$$

$$\approx R_{SN} \times I_{OUT(MAX)} (1 + 0.15) (V)$$

$$\begin{split} &V_{\text{CL(MIN)}} = V_{\text{CL(0)(MIN)}} - D_{\text{(MAX)}} \; (V_{\text{CL(0)(MIN)}} - V_{\text{CL(100)(MIN)}}) \\ &\text{where } D_{\text{MAX}} \; \text{is the duty cycle at the lowest } V_{\text{IN}} \; \text{condition.} \\ &\text{To avoid current limit,} \end{split}$$

$$V_{SEN(peak)} < V_{CL(MIN)}$$

Therefore,

$$\begin{split} R_{SN(MAX)} &= \frac{V_{CL(0)(MIN)} - D_{MAX} \left(V_{CL(0)(MIN)} - V_{CL(100)(MIN)}\right)}{I_{OUT(MAX)} + \frac{V_{OUT}(1 - D_{MAX})}{2 \text{ x L x } f_{S}}} \\ &\approx \frac{V_{CL(0)(MIN)} - D_{MAX} \left(V_{CL(0)(MIN)} - V_{CL(100)(MIN)}\right)}{1.15 \text{ x } I_{OUT(MAX)}} \end{split}$$

## Design Section (Continued)

Example:  $V_{IN(MIN)} = 4.5V$ ,  $V_{OUT} = 2.5V$ ,  $I_{OUT(MAX)} = 3A$

$$R_{SN(MAX)} = \frac{135 - 0.06 (.135 - .025)}{1.15 (3)} = 0.02\Omega$$

The hysteretic threshold is derived in a similar manner, the only difference being that  $V_{\rm SEN(peak)}$  is compared  $V_{\rm C(min)}$  ( $V_{\rm HYS}$ ). Notice that  $V_{\rm HYS}$  does not vary with the duty cycle. The hysteretic threshold is predetermined by the selection of  $R_{\rm SN}$  above. The hysteretic threshold is:

$$I_{HYS} = \frac{V_{HYS}}{R_{SN}} = \frac{0.032}{R_{SN}} \text{ (A), LM3477}$$

$$= \frac{0.011}{R_{SN}} \text{ (A), LM3477A}$$

Continuing with the example above,

$$I_{HYS} = \frac{0.032}{0.02} = 1.6A, LM3477$$

=  $\frac{0.011}{0.02} \approx 0.55A, LM3477A$

If the **peak switch current** decreases below this threshold, the LM3477/A will operate in hysteretic mode (see *OVER VOLTAGE PROTECTION* section). In some designs, it will be desired to use  $R_{\rm SL}$  so that lower valued inductors can be used (see *DEFAULT/ADJUSTABLE SLOPE COMPENSATION* section and Inductor section). Using  $R_{\rm SL}$  will lower the current limit and the hysteretic threshold. See *Figure 8*.  $R_{\rm SL}$  effectively adds an additional slope to the existing slope of the  $V_{\rm C}$  waveform.

FIGURE 8. Current Limit and Hysteretic Threshold vs Duty Cycle with  $\rm R_{SL}$

When R<sub>SL</sub> is used, the following equations apply:

$$\begin{split} R_{SN(MAX)} &= \frac{V_{CL(0)(MIN)} - D_{MAX} \left( V_{CL(0)(MIN)} - (V_{CL(100)(MIN)} - 50 \times 10^{-6} _{x} R_{SL} \right)}{I_{OUT} + \frac{V_{OUT} (1 - D_{MAX})}{2 \times L \times f_{S}}} \\ &\approx \frac{V_{CL(0)(MIN)} - D_{MAX} \left( V_{CL(0)(MIN)} - (V_{CL(100)(MIN)} - 50 \times 10^{-6} _{x} R_{SL} \right)}{1.15 \times I_{OUT}} \end{split}$$

$$I_{HYS} = \frac{MIN (V_{HYS} - 50 \times 10^{-6} \times R_{SL} \times D_{MAX}, 0)}{R_{SN}} (A)$$

where MIN(V<sub>HYS</sub> – 50x10<sup>-6</sup> x R<sub>SL</sub> x D<sub>MAX</sub>, 0) is the smaller of the two values in the parenthesis and V<sub>HYS</sub> is 0.032V and 0.011V for the LM3477 and LM3477A, respectively. R<sub>SL</sub> can be used creatively to intentionally lower the hysteretic threshold, allowing for better performance at lower loads. However, when R<sub>SL</sub> is used, there may be a minimum load requirement (see *START-UP/SOFT-START* section).

#### **Power Inductor Section**

The LM3477/A operates at a high switching frequency of 500kHz, which allows the use of small inductors. This is made apparent in the following set of equations used to calculate the output voltage ripple.

$$\Delta V_{OUT(Pk-Pk)} \approx \Delta i_{L(Pk-Pk)} x R_{ESR} (V)$$

$$\Delta i_{L(Pk-Pk)} = \frac{V_{OUT} (1-D)}{L \times f_{S}} (A)$$

As the switching frequency fs increases, the inductance required for a given output voltage ripple decreases. The equations above for  $\Delta V_{\text{OUT}}$  and  $\Delta i_{\text{L}}$  provide criteria for choosing the inductance. The maximum voltage ripple in steady-state, PWM operation can be controlled by limiting  $\Delta i_1$  which in turn is set by the inductance value. Alternatively, one can simply choose  $\Delta i_L$  as a percentage of the maximum output current. Clearly, the size of the output capacitor ESR, R<sub>ESB</sub>, will have an affect on which criteria is used to choose the inductance. When the ESR is relatively low (less than 100m $\Omega$ ), such as in ceramic, OSCON, and some low ESR tantalum capacitors, it is convenient to choose the inductance based on setting  $\Delta i_1$  to 30% of lout(max). If the ESR is high, then it may be necessary to restrict  $\Delta i_{\text{L}}$  to a lower value so that the output voltage ripple is not too high. Generally speaking, the former suggestion of setting  $\Delta i_L$  to 30% of  $I_{OUT(MAX)}$  is recommended.

The inductance also affects the stability of the converter. The slopes  $S_n$  and  $S_f$  in Figure 4 are functions of the inductance, while the compensation ramp,  $S_e$ , is fixed by default. Therefore if the inductance is too small, the converter may experience sub-harmonic oscillations. The LM3477/A provides sufficient internal slope compensation to allow for inductances chosen according to the  $\Delta i_L=0.3$  x  $I_{OUT}$  guideline in most cases. Still, one should check to make sure the inductance is not too low before continuing the design process. If it is found that the selected inductance is too low, a patented scheme to increase the compensation ramp,  $S_e$ , is provided in the LM3477/A (see <code>DEFAULT/ADJUSTABLE SLOPE COMPENSATION</code> section). In the calculations that follow, if it is found that the chosen inductance is too small,  $R_{\rm SL}$  can be used to increase Se so that the inductance can be used.

In a current mode control architecture, there is an inherent resonance at half the switching frequency (see DEFAULT/ADJUSTABLE SLOPE COMPENSATION sec-

## **Design Section** (Continued)

tion). A convenient indicator of how much resonance exists is quality factor Q. If Q is too high, subharmonic oscillations could occur, if Q is too low, the current mode architecture begins to act like a voltage mode architecture and the necessary compensation becomes more complex. This is discussed in more detail in the COMPENSATION section, but here it is important to calculate Q to be sure the selected inductance will not cause problems to the stability of the converter. The calculations below call for an inductance that results in Q between 0.15 and 2. See the COMPENSATION section if the chosen inductance enforces Q to be out of this range. By default, no extra slope compensation is needed, so  $R_{SL} = 0$ . In general, a Q between 0.5 and 1 is optimal.

$$Q = \frac{1}{\pi (m_c \times D' - 0.5)}$$

Where,

$$D' = 1-D$$

$$D = \frac{V_{OUT} + V_{D}}{V_{IN} + V_{D} - V_{Q} - V_{SEN}} \approx \frac{V_{OUT}}{V_{IN}}$$

$$\begin{split} m_c = 1 + \frac{S_e}{S_n} = 1 + \frac{f_s L R_{SN} (V_{SL} + 50 \times 10^{-6} \times R_{SL})}{V_{IN} \ D' - V_Q - V_{SN}} \\ \approx 1 + \frac{f_s L R_{SN} (V_{SL} + 50 \times 10^{-6} \times R_{SL})}{V_{IN} \ D'} \end{split}$$

$V_Q = V_{DS}$  of the MOSFET when it is conducting  $I_{OUT} * R_{DS(ON)}$ .

$V_{SEN}$  = Voltage across the sense resistor  $\approx I_{OUT} \ x \ R_{SN}$  Back solving for L gives a range for acceptable inductances based on a range for Q:

$$\frac{V_{IN}R_{SN}\left(\frac{1}{\pi Q_{MAX}} + \text{D-0.5}\right)}{f_{S}\left(V_{SL} + 50 \text{ x } 10^{-6} \text{ x } R_{SL}\right)} \leq L \leq \frac{V_{IN}R_{SN}\left(\frac{1}{\pi Q_{MIN}} + \text{D-0.5}\right)}{f_{S}\left(V_{SL} + 50 \text{ x } 10^{-6} \text{ x } R_{SL}\right)}$$

It is recommended that:

Q(max) = 2, and

Q(min) = 0.15

Values for  $V_{SL}$  can be found in the *ELECTRICAL CHARACTERISTICS* section.

Note: Adding slope compensation with  $R_{SL}$  will decrease the current limit. An iterative process may be needed to meet current limit and stability requirements, see *PROGRAM-MING CURRENT LIMIT/HYSTERETIC THRESHOLD* section.

## **Output Capacitor Selection**

A capacitance between  $47\mu F$  -  $100\mu F$  is typically used. Skip to 'Calculations for the Output Capacitance' for minimum capacitance calculations.

#### Type of output capacitors

Different type of capacitors often have different combinations of capacitance, equivalent series resistance (ESR), and voltage ratings. High-capacitance multi-layer ceramic capacitors (MLCCs) have a very low ESR, typically  $12m\Omega$ , but also relatively low capacitance and low voltage ratings. Tantalum capacitors can have fairly low ESR, such as  $18m\Omega$ , and high capacitance (up to 1mF) at higher voltage ratings than MLCCs. Aluminum capacitors offer high capacitance and relatively low ESR and are available in high voltage ratings. OSCON capacitors can achieve ESR values that are even lower than those of MLCCs and with higher capacitance, but the voltage ratings are low. Other tradeoffs in capacitor technology include temperature stability, surge current capability, and capacitance density (physical size vs. capacitance).

#### **Output Capacitor Considerations**

Skip to the 'Calculations for the output capacitor' subsection if a quick design is desired. While it is generally desired to use as little output capacitance as possible to keep costs down, the output capacitor should be chosen with care as it directly affects the ripple component of the output voltage as well as other components in the design. The output voltage ripple is directly proportional to the ESR of the output capacitor (see *POWER INDUCTOR* section). Therefore, designs requiring low output voltage ripple should have an output capacitor with low ESR. Choosing a capacitor with low ESR has the additional benefit of requiring one less component in the compensation network, as discussed in the Compensation section.

In addition to the output voltage ripple, the output capacitor directly affects the output voltage overshoot in a load transient. Two transients are possible: an unloading transient and a loading transient. An unloading transient occurs when the load current transitions to a higher current, and charge is unloaded from the output capacitor. A loading transient is when the load transitions to a lower current, and charge is loaded to the output capacitor. How the output voltage reacts during these transitions is known as the transient response. Both the capacitance and the ESR of the output capacitor will affect the transient response.

FIGURE 9. A Loading Transient

The control loop of the LM3477/A can be made fast enough to saturate the duty cycle when the worst case lode transient occurs. This means the duty cycle jumps to  $D_{\rm MIN}$  or  $D_{\rm MAX}$ , depending on the type of load transient. In a loading transient, as shown in *Figure 9*, the duty cycle drops to  $D_{\rm MIN}$  while the inductor current falls to match the load current. During this time, the regulator is heavily dependent on the output capacitors to handle the load transient. The initial overshoot is caused by the ESR of the output capacitors.

## **Output Capacitor Selection**

(Continued)

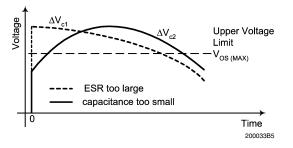

How the output voltage recovers after that initial excursion depends on how fast the inductor current falls and how large the output capacitance is. See *Figure 10*.

FIGURE 10. Output Voltage Overshoot Violation

The ESR and the capacitance of the output capacitor must be carefully chosen so that the output voltage overshoot is within the design's specification V<sub>OS(MAX)</sub>. If the total combined ESR of the output capacitors is not low enough, the initial output voltage excursion will violate the specification, see  $\Delta V_{C1}$ . If the ESR is low enough, but there is not enough output capacitance, the output voltage will travel outside the specification window due to the extra charge being dumped into the capacitor, see  $\Delta V_{C2}$ . The LM3477/A has output over voltage protection (OVP) which could trigger if the transient overshoot is high enough. If this happens, the controller will operate in hysteretic mode (see OVER VOLTAGE PROTEC-TION section) for a few cycles before the output voltage settles to its steady state. If this behavior is not desired, substitute  $V_{\text{OVP}}$  (referred to the output) for  $V_{\text{OS(MAX)}}\left(V_{\text{OVP}}\right.$  is found in the ELECTRICAL CHARACTERISTICS table) to find the minimum capacitance and maximum ESR of the output capacitor.

#### **Calculations for the Output Capacitor**

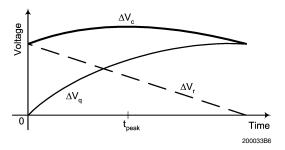

During a loading transient, the delta output voltage  $\Delta V_c$  has two changing components. One is the voltage difference across the ESR  $(\Delta V_r)$ , the other is the voltage difference caused by the gained charge  $(\Delta V_q)$ . This gives:

$$\Delta V_c = \Delta V_r + \Delta V_a$$

The design objective is to keep  $\Delta V_c$  lower than some maximum overshoot (V\_OS(MAX)). V\_OS(MAX) is chosen based on the output load requirements.

Both voltages  $\Delta V_r$  and  $\Delta V_q$  will change with time. For  $\Delta V_r$  the equation is:

$$\Delta V_r = R_{ESR}(\Delta I_{OUT(MAX)} - \frac{V_{OUT} D_{MIN}V_{IN}}{L} t)(V)$$

where,

$R_{ESR}$  = the output capacitor ESR

$\Delta I_{OUT}$  = the difference between the load current change  $I_{OUT(MAX)} - I_{OUT(MIN)}$

$D_{MIN}$  = Minimum duty cycle of device (0.165 typical)

Evaluating this equation at t = 0 gives  $\Delta V_{r(max)}$ . Substituting  $V_{OS(MAX)}$  for  $\Delta V_{r(MAX)}$  and solving for  $R_{ESR}$  gives:

$$R_{ESR(MAX)} = \frac{V_{OS(MAX)}}{\Delta I_{OUT(MAX)}} \Omega$$

The expression for  $\Delta V_{\alpha}$  is:

$$\Delta V_{q} = \frac{\Delta I_{OUT(MAX)}}{C_{OUT}} t - \frac{V_{OUT} - D_{MIN}V_{IN}}{2 \times L \times C_{OUT}} t^{2} (V)$$

From Figure 11 it can be told that  $\Delta V_{C}$  will reach its peak value at some point in time and then decrease. The larger the output capacitance is, the earlier the peak will occur. To find the peak position, let the derivative of  $\Delta V_{C}$  go to zero, and the result is:

$$tpeak = \frac{\Delta I_{OUT(MAX)} \times L}{V_{OUT} - D_{MIN} V_{IN}} - C_{OUT} R_{ESR}$$

FIGURE 11. Output Voltage Overshoot Peak

The intention is to find the capacitance value that will yield, at  $t_{\rm peak},$  a  $\Delta V_C$  that equals  $V_{\rm OS(max)}.$  Substituting tpeak for t and equating  $\Delta V_C$  to  $V_{\rm OS(max)}$  gives the following solution for  $C_{\rm OUT(MIN)}$ :

$$C_{OUT(MIN)} = \frac{L(V_{OS(MAX)}^{-} \sqrt{V_{OS(MAX)}^{2} - (\Delta I_{OUT(MAX)} \times R_{ESR})^{2}})}{(V_{OUT}^{-} D_{MIN} V_{IN}) R_{ESR}^{2}} (F)$$

The chosen output capacitance should not be less than 47µF, even if the solution for  $C_{\text{OUT(MIN)}}$  is less than 47µF. Notice it is already assumed that the total ESR is no greater than  $R_{\text{ESR(MAX)}}$ , otherwise the term under the square root will be a negative number.

#### Power MOSFET Selection

The drive pin of LM3477/A must be connected to the gate of an external MOSFET. In a buck topology, the drain of the external N-Channel MOSFET is connected to the input and the source is connected to the inductor. The  $C_{\rm B}$  pin voltage provides the gate drive needed for an external N-Channel MOSFET. The gate drive voltage depends on the input voltage (see  $TYPICAL\ PERFORMANCE\ CHARACTERISTICS$ ). In most applications, a logic level MOSFET can be used. For very low input voltages, a sub-logic level MOSFET should be used.

The selected MOSFET directly controls the efficiency. The critical parameters for selection of a MOSFET are:

- Minimum threshold voltage, V<sub>TH</sub>(MIN)

- 2. On-resistance, R<sub>DS</sub>(ON)

## Power MOSFET Selection (Continued)

- 3. Total gate charge, Qa

- 4. Reverse transfer capacitance, C<sub>RSS</sub>

- 5. Maximum drain to source voltage,  $V_{DS(MAX)}$

The off-state voltage of the MOSFET is approximately equal to the input voltage.  $V_{\rm DS(MAX)}$  of the MOSFET must be greater than the input voltage. The power losses in the MOSFET can be categorized into conduction losses and ac switching or transition losses.  $R_{\rm DS(ON)}$  is needed to estimate the conduction losses. The conduction loss,  $P_{\rm COND}$ , is the I²R loss across the MOSFET. The maximum conduction loss is given by:

$$P_{COND(MAX)} = I^2 D_{MAX} \left[ 1 + \frac{1}{12} \left( \frac{\Delta i_{(PK-PK)}}{I} \right)^2 \right] R_{DS(ON)}$$

where D<sub>MAX</sub> is the maximum operating duty cycle:

$$D_{\text{max}} \approx \frac{V_{\text{OUT}}}{V_{\text{IN(MIN)}}}$$

The turn-on and turn-off transition times of a MOSFET from the MOSFET specifications require tens of nano-seconds.  $C_{\rm RSS}$  and  $Q_{\rm g}$  are needed from the MOSFET specifications to estimate the large instantaneous power loss that occurs during these transitions.

The average amount of gate current required to turn the MOSFET on can be calculated using the formula:

$$I_G = Q_q.F_S$$

The required gate drive power to turn the MOSFET on is equal to the switching frequency times the energy required to deliver the charge to bring the gate charge voltage to  $V_{\rm DR}$  (see <code>ELECTRICAL CHARACTERISTICS</code> and <code>TYPICAL PERFORMANCE CHARACTERISTICS</code> for the drive voltage specification).

$$P_{Drive} = F_S.Q_g.V_{DR}$$

It is sometimes helpful or necessary to slow down the turn on transition of the FET so that less switching noise appears at the  $I_{\rm SEN}$  pin. This can be done by inserting a drive resistor  $R_{\rm DR}$  in series with the boot-strap capacitor (see  $\it Figure~6$ ). This can help reduce sensing noise that may be preventing designs from operating at or near the LM3477/A's minimum duty cycle limit. Gate drive resistors from 2.2 $\Omega$  to  $51\Omega$  are recommended.

#### **Power Diode Selection**

The output current commutates through the diode when the external MOSFET turns off. The three most important parameters for the diode are the peak current, peak inverse voltage, and average power dissipation. Exceeding these ratings can cause damage to the diode. The average current through the diode is given by:

$$I_{D(AVG)} = I_{OUT} x (1-D)$$

where D is the duty cycle and  $I_{\rm OUT}$  is the output current. The diode must be rated to handle this current.

The off-state voltage across the diode in a buck converter is approximately equal to the input voltage. The peak inverse voltage rating of the diode must be greater than the off-state voltage of the diode. To improve efficiency, a low forward drop schottky diode is recommended.

## Input Capacitor Selection

In a buck converter, the high side switch draws large ripple currents from the input capacitor. The input capacitor must be rated to handle this RMS current.

$$I_{RMS\_CIN} = I_{OUT} \sqrt{\frac{V_{OUT}(V_{IN}-V_{OUT})}{V_{IN}}}$$

The power dissipated in the input capacitor is given by:

$P_{D(CIN)} = I_{RMS\_CIN}^2 R_{ESR\_CIN}$

where  $R_{\rm ESR\_CIN}$  is the ESR of the input capacitor. The input capacitor must be selected to handle the rms current and must be able to dissipate the power.  $P_{\rm D(CIN)}$  must be lower than the rated power dissipation of the selected input capacitor. In many cases, several capacitors have to be paralleled to handle the rms current. In that case, the power dissipated in each capacitor is given by:

$P_{D(CIN)} = (I^2_{RMS\_CIN}R_{ESR\_CIN})/n^2$ , where n is the total number of capacitors paralled at the input.

A 0.1 $\mu$ F or 1 $\mu$ F ceramic bypass capacitor is also recommended on the V<sub>IN</sub> pin (pin 8) of the IC. This capacitor must be connected very close to pin 8.

## Compensation

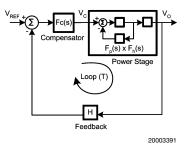

FIGURE 12. Control Block Diagram of a Current Mode Controlled Buck Converter

The LM3477/A is a current mode controller, therefore the control block diagram representation involves 2 feedback loops (see *Figure 12*). The inner feedback loop derives its feedback from the sensed inductor current, while the outer loop monitors the output voltage. This section will not give a rigorous analysis of current mode control, but rather a simplified but accurate method to determine the compensation network. The first part reveals the results of the model, giving expressions for solving for component values in the compensation network.

The compensation network is designed around the power components, or the power stage. An isolated schematic of the error amplifier and the various compensation components is shown in *Figure 13*. The error amplifier in conjunction with the compensation network makes up the compensator block in *Figure 12*. The purpose of the compensator block is to stabilize the control loop and achieve high performance in terms of the transient response, audio susceptibility and output impedance.

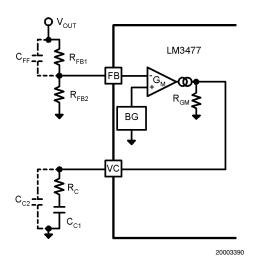

#### FIGURE 13. LM3477 Compensation Components

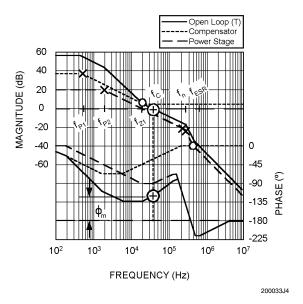

Figure 14 shows a bode plot of a typical current mode buck regulator. It is an estimate of the actual plot using the asymptotic approach. The three plots shown are of the compensator, powerstage, and loop gain, which is the product of the power stage, compensator, and feedback gain. The loop gain determines both static and dynamic performance of the converter. The power stage response is fixed by the selection of the power components, therefore the compensator is designed around the powerstage response to achieve a good loop response. Specifically, the compensator is added to increase low frequency magnitude, extend the 0dB frequency (crossover frequency), and improve the phase characteristic.

FIGURE 14. Typical Open Loop, Compensator, and Power Stage Bode Plots for LM3477 Buck Circuits. Poles, Zeros and Important Measurements are Labeled

There are several different types of compensation that can be used to improve the frequency response of the control loop. To determine which compensation scheme to use, some information about the power stage is needed.

Use  $V_{\text{IN}} = V_{\text{IN(MIN)}}$  and  $R = R_{\text{MIN}} \, (I_{\text{OUT(MAX)}})$  when calculating compensation components.

$$H = feedback gain = \frac{R_{FB2}}{R_{FB1} + R_{FB2}}$$

$$A_{DC} = \frac{R}{R_{SN}} \frac{1}{1 + \frac{R}{f_c L} [mc \times D' - 0.5]}$$

$$m_c = 1 + \frac{S_e}{S_n}$$

$$S_e = f_S(V_{SL} + 50x10^{-6} R_{SL})$$

$$S_n = \frac{V_{IN}D' \times R_{SN}}{L}$$

$$f_{p1} = \frac{1}{2\pi} \left[ \frac{1}{C_{OUT}R} + \frac{1}{f_s LC_{OUT}} (mc \times D' - 0.5) \right] (Hz)$$

$$f_{ESR} = \frac{1}{2\pi C_{OUT} R_{ESR}} (Hz)$$

$$Q = \frac{1}{\pi (m_c \times D' - 0.5)}$$

With the power stage known, a compensator can be designed to achieve improved performance and stability. The LM3477/A will typically require only a single resistor and capacitor for compensation, but depending on the power stage it could require three or four external components.

It is a good idea to check that Q is between 0.15 and 2, if it was not already done when selecting the inductor. If Q is less than 0.15 or greater than 2, skip to the *SAMPLING POLE QUALITY FACTOR* section below before continuing with the compensator design.

First, a target crossover frequency ( $f_{\rm c}$ ) for the loop gain must be selected. The crossover frequency is the bandwidth of the converter. A higher bandwidth generally corresponds to faster response times and lower overshoots to load transients. However, the bandwidth should not be much higher than 1/10 the switching frequency. The LM3477/A operates with a 500kHz switching frequency, so it is recommended to choose a crossover frequency between 10kHz - 50kHz.

The schematic of the LM3477/A compensator is shown in Figure 13. The default design uses  $R_c$  and  $C_{C1}$  to form a lag (type 2) compensator. The  $C_{C2}$  capacitor can be added to form an additional pole that is typically used to cancel out the esr zero of the output capacitor. Finally, if extra phase margin is needed, the Cff capacitor can be added (this does not help at low output voltages, see below).

The strategy taken here for choosing  $\rm R_c$  and  $\rm C_{C1}$  is to set the crossover frequency with  $\rm R_c$ , and set the compensator zero with  $\rm C_{C1}$ . Using the selected target crossover frequency,  $\rm f_C$ , set  $\rm R_C$  to:

$$R_{C} = \frac{f_{C} \times R_{GM}}{A_{DC} \times GM \times R_{GM} \times H \times f_{P1} - f_{C}} \Omega$$

$\rm f_{\rm C} = Crossover$  frequency in Hertz (20kHz - 50kHz is recommended)

$R_{GM} = 50x10^3\Omega$

$GM = 1000x10^{-6} A/V$

The compensator zero,  $f_{Z1}$ , is set with  $C_{C1}$ . When fast transient responses are desired,  $f_{Z1}$  should be placed as high as possible, however it should not be higher than the selected crossover frequency  $f_C$ . The guideline proposed here is to choose  $C_{C1}$  such that  $f_{Z1}$  falls somewhere between the power pole  $f_{P1}$  and ½ decade before the selected crossover frequency fc:

$$\frac{3.16}{2\pi f_{C}R_{C}} \le C_{C1} \le \frac{1}{2\pi f_{p1}R_{C}}$$

In this compensation scheme, the pole created by  $C_{\rm C2}$  is used to cancel out the zero created by the ESR of the output capacitor. In other schemes such as the methods discussed in the *SAMPLING POLE QUALITY FACTOR* subsection, the ESR zero is used. For the typical case, use  $C_{\rm C2}$  if:

$$f_{ESR} < \frac{f_S}{2}$$

$$C_{C2} = \frac{R_{GM} + R_C}{2\pi f_{ESR} R_{GM} R_C} (F)$$

#### **Plotting the Open Loop Response**

The open loop response is expressed as:

$T = A_{DC} \times A_{CM} \times H \times F_{p}(s) \times F_{c}(s)$

Where  $\boldsymbol{A}_{DC}$  and  $\boldsymbol{H}$  are given above and

$A_{CM} = GM \times R_{GM}$

$$F_{P(S)} = \frac{1 + \frac{s}{2\pi f_{ESR}}}{1 + \frac{s}{2\pi f_{p1}}}$$

$$F_h(s) = \frac{1}{s^2 (\frac{1}{\pi f_s})^2 + s(\frac{1}{\pi f_s Q}) + 1}$$

$${\rm F_{C}(s) = \frac{(sC_{\rm C1}R_{\rm C} + 1)}{sC_{\rm C1}R_{\rm GM}\,(R_{\rm GM} + R_{\rm C}) + 1}}\,,\,C_{\rm C2}\,{\rm not\,used}$$

$$F_{c}(s) = \frac{(sC_{c1}R_{c} + 1)}{s^{2}C_{c1}C_{c2}R_{c}R_{c}R_{c} + s(C_{c2}R_{c}R_{c} + C_{c1}(R_{c} + R_{c})) + 1}, C_{c2} \text{ used}$$

One can plot the magnitude and phase of the open loop response to analyze the frequency response.

#### **Example: Compensation Design**

$4.5V \le V_{IN} \le 5.5V$

$V_{OUT} = 2.5V$

$I_{OUT} = 3A (R = 0.83\Omega)$

$R_{SN} = 0.02\Omega$

$L = 3.3 \mu H$

$R_{SI} = 0\Omega$

$C_{OUT} = 100 \mu F$

$R_{ESR} = 0.01\Omega$

First, calculate the power stage parameters using  $V_{\text{IN}(\text{MIN})}$  and  $R_{(\text{MAX})}$ :

H = feedback gain =

$$\frac{1.27}{2.5}$$

= 0.508

$$A_{DC} = \frac{0.83}{0.02} \cdot \frac{1}{1 + \frac{0.83}{(500 \times 10^3)(3.3 \times 10^{-6})} [(5.66)(0.39) - 0.5]} = 22.3$$

$$\begin{split} f_{p1} = \ \frac{1}{2\pi} & \Big( \frac{1}{(100\times 10^{-6})(0.83)} + \frac{1}{(500\times 10^{3})(3.3\times 10^{-6})(100\times 10^{6})} \\ & [(5.66)(0.39) - 0.5] \Big) = 3.58 \text{kHz} \end{split}$$

$$f_{ESR} = \frac{1}{2\pi (100 \times 10^{-6})(0.01)} = 159 \text{kHz}$$

$$Q = \frac{1}{\pi[(5.66)(0.39) - 0.5]} = 0.18$$

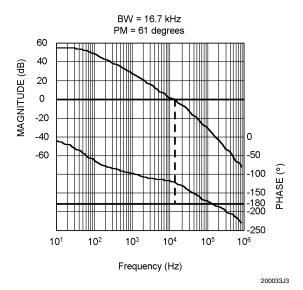

In this example, a crossover frequency of 20kHz is chosen, so:  $f_C = 20000$ .  $R_C$  is now calculated using the power stage information and the target crossover frequency  $f_C$ :

$$R_{\rm C} = \frac{(20 \times 10^3)(50 \times 10^3)}{(22.3)(0.001)(50 \times 10^3)(0.508)(3.58 \times 10^3) - (20 \times 10^3)}$$

$$= 498\Omega$$

This sets the high frequency gain of the compensator such that a crossover frequency of  $f_C$  is obtained. The capacitor  $C_{C1}$  sets the compensator zero,  $f_{Z2}$ . Set  $f_{Z2}$  between the power pole  $f_{P1}$  and the ½ decade before the target crossover frequency  $f_C$ :

$$\frac{3.16}{2\pi(20 \text{ x } 10^3)(507)} \le C_{C1} \le \frac{1}{2\pi(3.58 \text{ x } 10^3)(507)}$$

$$49nF \le C_{C1} \le 88nF$$

Choosing  $C_{C1}=88x10^{-9}\ F$  will set  $f_{Z2}=f_{P1}$ , canceling out the power pole and insuring a -20dB/decade slope in the low frequency magnitude response. In other words, the phase margin below the crossover frequency will always be higher than the phase margin at the crossover frequency.

If better transient response times are desired, a second method is to set  $f_{\rm Z2}$  between  $f_{\rm P1}$  and  $1\!/\!_2$  decade before  $f_{\rm C},$  the target crossover frequency. This trades more low frequency gain for less phase margin, which translates to faster but more oscillatory step responses. We pick  $C_{\rm C1}=49 nF$  (use 47nF).

If the esr zero of the output capacitor  $(f_{\text{ESR}})$  is too low or if more phase margin is required, additional components may be added to increase the flexibility of the compensator.

Use  $C_{C2}$  if  $f_{ESR} < \frac{1}{2} f_S$ , that is if:

$$\frac{1}{2\pi C_{OLIT}R_{ESR}} < 250kHz$$

For this example,  $f_{ESR} = 159 \text{ kHz}$ , so use  $C_{C2}$ .

$$C_{C2} = \frac{50 \times 10^3 + 507}{2\pi (.159 \times 10^3) (50 \times 10^3) (507)} = 2 \text{ nF} \Rightarrow 2.2 \text{ nF}$$

The equations used here for  $R_{\rm C}$ ,  $C_{\rm C1}$ , and  $C_{\rm C2}$  are approximations valid when  $C_{\rm C2}$  <<  $C_{\rm C1}$ . For exact equations, see Plotting Open Loop Response earlier in this section. In some cases, the desired inductance is several times higher than the optimal inductance set by the internal slope compensation. This results in a Q lower than 0.15, in which case additional methods of compensating are presented (see <code>SAMPLING POLE QUALITY FACTOR</code> section).

FIGURE 15. Open Loop Frequency Response for LM3477 Compensation Design Example

#### **Sampling Pole Quality Factor**

In a current mode control architecture, there is an inherent resonace at half the switching frequency. The LM3477/A internally compensates for this by adding a negative slope to the PWM control waveform (see *DEFAULT/ADJUSTABLE SLOPE COMPENSATION* section). The factor in the power

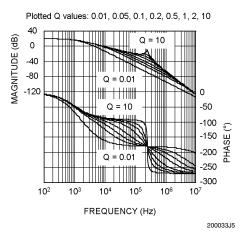

stage equations above, Q, describes how much resonance will be observed. Q is a function of duty cycle and  $m_{\rm c}$ . Figure 16 shows how the power stage bode plot is affected as Q is varied from 0.01 to 10. The resonance is caused by two complex poles at half the switching frequency. If  $m_{\rm c}$  is too low, the resonant peaking could become severe coinciding with subharmonic oscillations in the inductor current. If  $m_{\rm c}$  is too high, the two complex poles split and the converter begins to act like a voltage mode converter and the compensation scheme used above should be changed.

FIGURE 16. The Quality Factor Q of the Two Complex Poles is used to qualify how much resonant peaking is observed in the Power Stage Bode Plot

If Q>2, the sampling poles are imaginary and are approaching the right half of the imaginary plane (the system is becoming unstable). In this case, Q must be decreased by either increasing the inductance, or more preferably, adding more slope compensation through the  $R_{\rm SL}$  resistor (see DEFAULT/ADJUSTABLE SLOPE COMPENSATION section).

If Q<0.15, it means that one of the sampling poles is decreasing in frequency towards the dominant power pole,  $f_{p1}$ . There are three ways to compensate for this. Decrease the crossover frequency, add a phase lead network, or use the output capacitor's ESR to cancel out the low frequency sampling pole.

One option is to decrease the crossover frequency so that the phase margin is not as severely decreased by the sampling pole. Decreasing the crossover frequency to between 1kHz to 10kHz is advisable here. As a result, there will be a decrease in transient response performance.

Another option is the use of the feed-forward capacitor, Cff. This will provide a positive phase shift (lead) which can be used to increase phase margin. However, it is important to note that the effectiveness of Cff decreases with output voltage. This is due to the fact that the frequencies of the zero  $f_{\rm zff}$  and pole  $f_{\rm pff}$  get closer together as the output voltage is reduced.

The frequency of the feed-forward zero and pole are:

$$f_{zff} = \frac{1}{2\pi R_{FB1} C_{ff}} (Hz)$$

$$f_{pff} = \frac{1}{2\pi R_{FB1}C_{ff}} \frac{R_{FB1} + R_{FB2}}{R_{FB2}} = f_{zff} \frac{V_{OUT}}{V_{FB}} (Hz)$$

A third option is to strategically place the ESR zero  $f_{\text{ESR}}$  of the output capacitor to cancel out the sampling pole. In this case, the capacitor  $C_{\text{C2}}$  will not be used to cancel out  $f_{\text{ESR}}$ .  $f_{\text{ESR}}$  should be placed around the crossover frequency  $f_{\text{c}}$ , but this will depend on how low Q is.

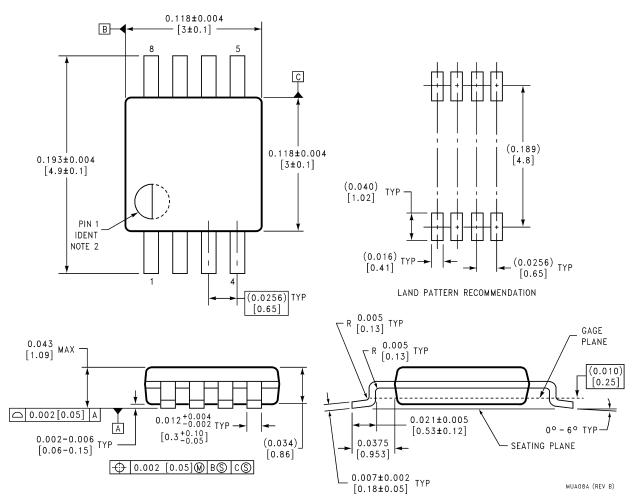

## Physical Dimensions inches (millimeters)

unless otherwise noted

8 Lead Mini SO-8 Package NS Package Number MUA08A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

tional Semiconductor National Semiconductor Europe

pericas Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790 National Semiconductor

Asia Pacific Customer

Response Group

Tel: 65-2544466