## LM1770

# Low-Voltage SOT23 Synchronous Buck Controller With No External Compensation

## **General Description**

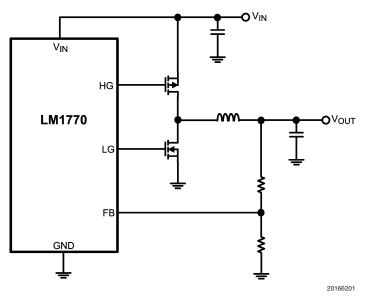

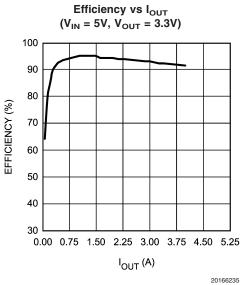

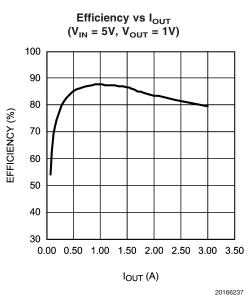

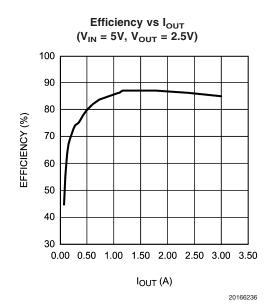

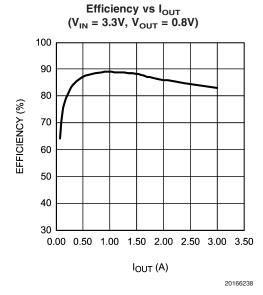

The LM1770 is an efficient synchronous buck switching controller in a tiny SOT23 package. The constant on-time control scheme provides a simple design free of compensation components, allowing minimal component count and board space. It also incorporates a unique input feed-forward to maintain a constant frequency independent of the input voltage. The LM1770 is optimized for a low voltage input range of 2.8V to 5.5V and can provide an adjustable output as low as 0.8V. Driving an external high side PFET and low side NFET it can provide efficiencies as high as 95%.

Three versions of the LM1770 are available depending on the switching frequency desired for the application. Nominal switching frequencies are in the range of 100kHz to 1000kHz.

## **Features**

- Input voltage range of 2.8V to 5.5V

- 0.8V reference voltage

- No compensation required

- Constant frequency across input range

- Low quiescent current of 400µA

- Internal soft-start

- Short circuit protection

- Tiny SOT-23 package

## **Applications**

- Simple To Design, High Efficiency Step Down Switching Regulators

- Set-Top Boxes

- Cable Modems

- Printers

- Digital Video Recorders

- Servers

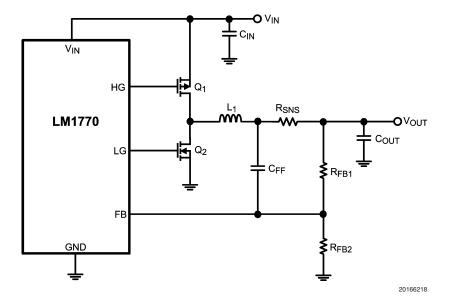

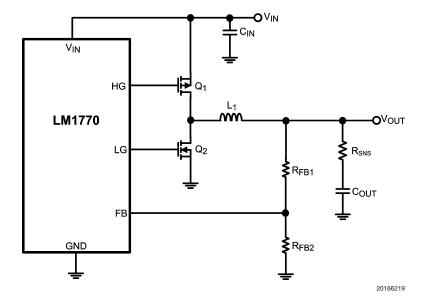

## **Typical Application Circuit**

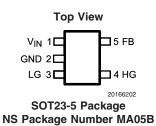

## **Connection Diagram**

## **Ordering Information**

| Order Number | Package Type | NSC Package Drawing | On-time | Supplied As              |

|--------------|--------------|---------------------|---------|--------------------------|

| LM1770SMF    | SOT23-5      | MF05A               | 500ns   | 1000 units Tape and Reel |

| LM1770SMFX   | SOT23-5      | MF05A               | 500ns   | 3000 units Tape and Reel |

| LM1770TMF    | SOT23-5      | MF05A               | 1000ns  | 1000 units Tape and Reel |

| LM1770TMFX   | SOT23-5      | MF05A               | 1000ns  | 3000 units Tape and Reel |

| LM1770UMF    | SOT23-5      | MF05A               | 2000ns  | 1000 units Tape and Reel |

| LM1770UMFX   | SOT23-5      | MF05A               | 2000ns  | 3000 units Tape and Reel |

## **Pin Descriptions**

| Pin # | Name            | Function        |  |

|-------|-----------------|-----------------|--|

| 1     | V <sub>IN</sub> | Input supply    |  |

| 2     | GND             | Ground          |  |

| 3     | LG              | NFET Gate Drive |  |

| 4     | HG              | PFET Gate Drive |  |

| 5     | FB              | Feedback Pin    |  |

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

$V_{IN}$  -0.3V to 6V Storage Temperature Range -65°C to 150°C

Junction Temperature 150°C

Lead Temperature (soldering, 10sec) 260°C

ESD Rating 2.5kV

## **Operating Ratings**

$V_{IN}$  to GND 2.8V to 5.5V Junction Temperature Range (T<sub>J</sub>) -40  $^{\circ}$ C to +125  $^{\circ}$ C

**Electrical Characteristics** Specifications with standard typeface are for  $T_J = 25^{\circ}C$ , and those in **bold face type** apply over the full Junction Temperature Range ( $-40^{\circ}C$  to  $+125^{\circ}C$ ). Minimum and Maximum limits are guaranteed through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J = 25^{\circ}C$  and are provided for reference purposes only. Unless otherwise specified  $V_{IN} = 3.3V$ .

| Symbol                          | Parameter                             | Conditions                     | Min   | Тур  | Max   | Unit |

|---------------------------------|---------------------------------------|--------------------------------|-------|------|-------|------|

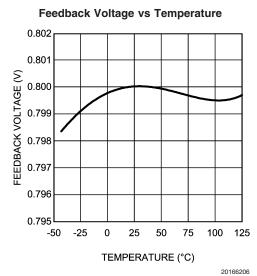

| VFB                             | Feedback pin voltage                  | V <sub>IN</sub> = 3.3V         | 0.782 | 0.80 | 0.818 | V    |

|                                 |                                       | V <sub>IN</sub> = 5.0V         | 0.772 | 0.79 | 0.808 |      |

| $\Delta V_{FB} / \Delta V_{IN}$ | Line Regulation                       | V <sub>IN</sub> = 2.8V to 5.5V |       | -5   |       | mV/V |

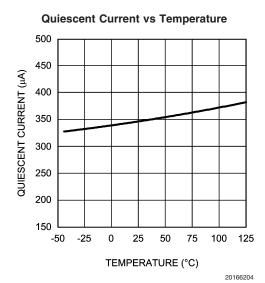

| Ι <sub>Q</sub>                  | Operating Quiescent current           | V <sub>FB</sub> = 0.9V         |       | 400  | 600   | μA   |

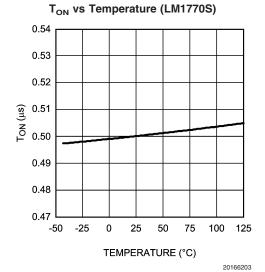

| T <sub>ON</sub>                 | Switch On-Time                        | LM1770S - (500ns)              | 0.4   | 0.5  | 0.6   | μs   |

|                                 |                                       | LM1770T - (1000ns)             | 0.8   | 1.0  | 1.2   |      |

|                                 |                                       | LM1770U - (2000ns)             | 1.6   | 2.0  | 2.4   |      |

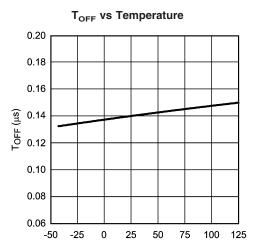

| T <sub>OFF_MIN</sub>            | Minimum Off-Time                      | LM1770S - (500ns)              |       | 150  | 250   | ns   |

|                                 |                                       | LM1770T - (1000ns)             |       | 135  | 225   |      |

|                                 |                                       | LM1770U - (2000ns)             |       | 120  | 220   |      |

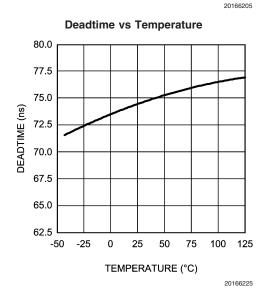

| T <sub>D</sub>                  | Gate Drive Dead-Time                  |                                |       | 70   |       | ns   |

| I <sub>FB</sub>                 | Feedback pin bias current             | V <sub>FB</sub> = 0.9V         |       | 50   |       | nA   |

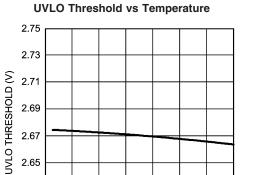

| V <sub>UVLO</sub>               | Under-voltage lock out                | V <sub>IN</sub> Rising Edge    |       | 2.6  | 2.8   | V    |

| V <sub>UVLO_HYS</sub>           | Under-voltage lock out hysteresis     |                                |       | 30   |       | mV   |

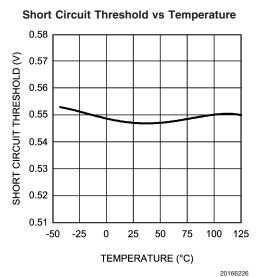

| V <sub>SC_TH</sub>              | Feedback pin Short Circuit Latch      |                                | 0.5   | 0.55 | 0.65  | V    |

|                                 | Threshold                             |                                |       |      |       |      |

| R <sub>DS(ON) 1</sub>           | HG FET driver pull-up On resistance   | I <sub>HG</sub> = 20 mA        |       | 5    |       | Ω    |

| R <sub>DS(ON) 2</sub>           | HG FET driver pull-down On resistance | I <sub>HG</sub> = 20 mA        |       | 9    |       | Ω    |

| R <sub>DS(ON) 3</sub>           | LG FET driver pull-up On resistance   | I <sub>LG</sub> = 20 mA        |       | 9    |       | Ω    |

| R <sub>DS(ON) 4</sub>           | LG FET driver pull-down On resistance | I <sub>LG</sub> = 20 mA        |       | 5    |       | Ω    |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage may occur to the device. Operating Ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications, see Electrical Characteristics.

## **Typical Performance Characteristics**

TEMPERATURE (°C)

## **Typical Performance Characteristics** (Continued)

20166227

100 125

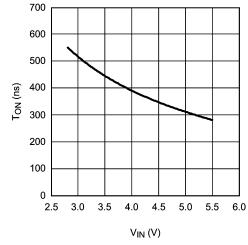

$T_{\rm ON}$  vs  $V_{\rm IN}$  (LM1770S)

20166230

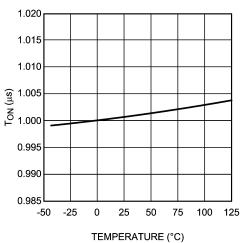

## T<sub>ON</sub> vs Temperature (LM1770T)

25

50 75

TEMPERATURE (°C)

2.63

2.61

-50

-25

0

20166228

20166231

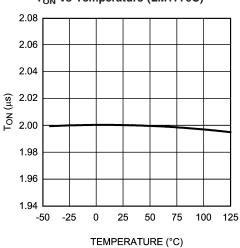

## T<sub>ON</sub> vs Temperature (LM1770U)

20166229

20166232

## Typical Performance Characteristics (Continued)

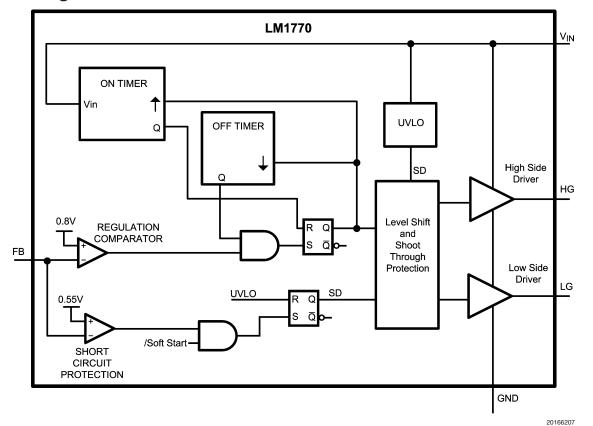

## **Block Diagram**

## **Application Information**

#### THEORY OF APPLICATION

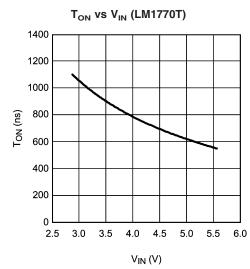

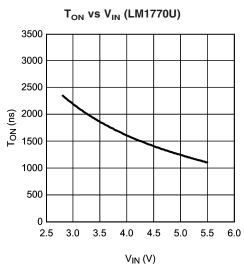

The LM1770 synchronous buck switcher has a control scheme that is referred to as constant on-time control. This topology relies on a fixed switch on-time to regulate the output voltage. This on-time is internally set by EEPROM and is available with three different set-points to allow for different frequency options. The LM1770 automatically adjusts the on-time during operation inversely with the input voltage  $(V_{\text{IN}})$  to maintain a constant frequency. Therefore the switching frequency during continuous conduction mode is independent of the inductor and capacitor size unlike hysteretic switchers.

At the beginning of the cycle the LM1770 turns on the high side PFET for a fixed duration. This on-time is predetermined (internally set by EEPROM and adjusted by  $V_{\rm IN}$ ) and the switch will not turn off until the timer has completed its period. The PFET will then turn off for a minimum predetermined time period. This minimum  $T_{\rm OFF}$  of 150ns is internally set and cannot be adjusted. This is to prevent false triggering from occurring on the comparator due to noise from the SW node transition. After the minimum  $T_{\rm OFF}$  period has expired, the PFET will remain off until the comparator trip-point has been reached. Upon passing this trip-point (set at 0.8V at the feedback pin), the PFET will turn back on and the process will repeat, thus regulating the output.

The NFET control is complementary to the PFET control with the exception of a short dead-time to prevent shoot through from occurring.

#### **DEVICE OPERATION**

#### **Timing Opinion**

Three versions of the LM1770 are available each with a predetermined  $T_{\rm ON}$  set internally by EEPROM. This  $T_{\rm ON}$  setting will determine the switching frequency for the application. Derivation and calculation of the switching frequency's dependence on  $V_{\rm IN}$  and  $T_{\rm ON}$  can be seen in the following section.

In a PWM buck switcher the following equations can be manipulated to obtain the switching frequency. The first equation shows the standard duty-cycle equation given by the volts-seconds balance on the inductor with the following equations defining standard relationships:

$$D = \frac{V_{OUT}}{V_{IN}}$$

$$T_{ON} = D \times T_{P}$$

$$T_P = \frac{1}{f_{SW}}$$

Using this equations and solving for duty-cycle:

$$D = f_{SW} \times T_{ON}$$

Frequency can now be expressed as:

$$F = \frac{V_{OUT}}{V_{IN} x T_{ON}}$$

Or simply written as:

$$f_{SW} = \frac{V_{OUT}}{\alpha}$$

where,

$$\alpha = V_{IN} \times T_{ON}$$

To maintain a set frequency in an application,  $\alpha$  is always held constant by varying  $T_{ON}$  inversely with  $V_{IN}$ . The three versions of the LM1770 are identified by the on times at a  $V_{IN}$  of 3.3V for consistency. For clarification see the table below:

| Product ID | T <sub>ON</sub> @ 3.3V | α <b>(V μs)</b> |

|------------|------------------------|-----------------|

| LM1770S    | 0.5µs                  | 1.65            |

| LM1770T    | 1.0µs                  | 3.3             |

| LM1770U    | 2.0µs                  | 6.6             |

The variation of  $T_{ON}$  versus  $V_{IN}$  can also be expressed graphically. These graphs can be found in the typical curves section of the datasheet.

With  $\alpha$  being a constant regardless of the version of the LM1770 used, equation [6] shows that the only dependent variable remaining is  $V_{OUT}$ . Since  $V_{OUT}$  will be a constant in any application, the frequency will also remain constant. The switching frequency at which the application runs depends upon the  $V_{OUT}$  desired and the LM1770 version chosen. For any  $V_{OUT}$ , three frequency options (LM1770 versions) can be selected. This can be seen in the table below. The recommended frequency range of operation is 100kHz to 1000kHz.

|      | Timing Options |        |        |  |

|------|----------------|--------|--------|--|

| VOUT | 500ns          | 1000ns | 2000ns |  |

| 0.8  | 485            | 242    | 121    |  |

| 1    | 606            | 303    | 152    |  |

| 1.2  | 727            | 364    | 182    |  |

| 1.5  | 909            | 455    | 227    |  |

| 1.8  | 1091           | 545    | 273    |  |

| 2.5  | 1515           | 758    | 379    |  |

| 3.3  | 2000           | 1000   | 500    |  |

Switching Frequency (kHz) of LM1770 based on output voltage and timing

#### SHORT-CIRCUIT PROTECTION

The LM1770 has an internal short circuit comparator that constantly monitors the feedback node (except during soft-start). If the feedback voltage drops below 0.55V (equivalent to the output voltage dropping below 68% of nominal), the comparator will trip causing the part to latch off. The LM1770 will not resume switching until the input voltage is taken below the UVLO threshold and then brought back into its normal operating range. The purpose of this function is to prevent a severe short circuit from causing damage to the application. Due to the fast transient response of the LM1770 a severe short on the output causing the feedback to drop would only occur if the load applied had an effective resistance that approaches the PMOS  $R_{\rm DS(ON)}$ .

#### **SOFT-START**

To limit in-rush current and allow for a controlled startup the LM1770 incorporates an internal soft-start scheme. Every time the input voltage rises through the UVLO threshold the LM1770 goes through an adaptive soft-start that limits the

## **Application Information** (Continued)

on-time and expands the minimum off-time. In addition the part will only activate the PMOS allowing a discontinuous mode of operation enabling a pre-biased startup. The time spent in soft-start will depend on the load applied to the output, but is usually close to a set time that is dependent on the timing option. The approximate soft-start time can be seen below for each timing option.

| Product ID | Timing | T <sub>SS</sub> |

|------------|--------|-----------------|

| LM1770S    | 0.5µs  | 1ms             |

| LM1770T    | 1.0µs  | 1.2ms           |

| LM1770U    | 2.0µs  | 1.8ms           |

It should be noted that as soon as soft-start terminates the short-circuit protection is enabled. This means that if the output voltage does not reach at least 68% of its final value the part will latch off. Therefore, if the input supply is extremely slow rising such that at the end of soft-start the input voltage is still near the UVLO threshold, a timing option should be chosen to ensure that maximum duty-cycle permits the output to meet the minimum condition. As a general recommendation it is advisable to use the 2000ns option (LM1770U) in conditions where the output voltage is 2.5V or greater to avoid false latch offs when there is concern regarding the input supply slew rate.

#### JITTER

The LM1770 utilizes a constant on-time control scheme that relies on the output voltage ripple to provide a consistent switching frequency. Under certain conditions, excessive noise can couple onto the feedback pin causing the switch node to appear to have a slight amount of jitter. This is not indicative of an unstable design. The output voltage will still regulate to the exact same value. Careful component selection and layout should minimize any external influence.

In addition to any external noise that can add to the jitter seen on the switch node, the LM1770 will always have a slight amount of switch jitter. This is because the LM1770 makes a small alteration in the reference voltage every 128 cycles to improve its accuracy and long term performance. This has the effect of causing a change in the switching frequency at that instant. When viewed on an oscilloscope this can be seen as a jitter in the switch node. The change in feedback voltage or output voltage, however, is almost indistinguishable.

## **Design Guide**

The following section walks the designer through the steps necessary to select the external components to build a fully functional power supply. As with any DC-DC converter numerous trade-offs are possible to optimize the design for efficiency, size or performance. These will be taken into account and highlighted throughout this discussion.

The first equation to calculate for any buck converter is duty-cycle. Ignoring conduction losses associated with the FETs and parasitic resistances it can be approximated by:

$$D = \frac{V_{OUT}}{V_{IN}}$$

A more accurate calculation for duty-cycle can be used that takes into account the voltage drops across the FETs. This

equation can be used to determine the slight load dependency on switch frequency if needed. Otherwise the simplified equation works well for component calculation.

$$D = \frac{V_{OUT} + V_{DS\_NMOS}}{V_{IN} + V_{DS\_NMOS} + V_{DS\_PMOS}}$$

#### FREQUENCY SELECTION

The LM1770 is available with three preset timing options that select the on-time and hence determine the switching frequency of the application. Increasing the switching frequency has the effect of reducing the inductor size needed for the application while requiring a slight trade-off in efficiency. The table below shows the same frequency table as shown earlier, with the exception that the recommended timing option for each  $V_{\rm OUT}$  is highlighted. It is not recommended to use a high switching frequency with  $V_{\rm OUT}$  equal to or greater than 2.5V due to the maximum duty-cycle limitations of the device coupled with the internal startup.

|           | Timing Options |        |        |  |

|-----------|----------------|--------|--------|--|

| $V_{OUT}$ | 500ns          | 1000ns | 2000ns |  |

| 0.8       | 485            | 242    | -      |  |

| 1         | 606            | 303    | -      |  |

| 1.2       | 727            | 364    | -      |  |

| 1.5       | 909            | 455    | 227    |  |

| 1.8       | -              | 545    | 273    |  |

| 2.5       | -              | -      | 379    |  |

| 3.3       | -              | -      | 500    |  |

Recommended switching frequency (kHz) based on output voltage and timing option.

### **INDUCTOR SELECTION**

The inductor selection is an iterative process likely requiring several passes before settling on a final value. The reason for this is because it influences the amount of ripple seen at the output, a critical component to ensure general stability of an adaptive on-time circuit. For the first pass at inductor selection the value can be obtained by targeting a maximum peak-to-peak ripple current equal to 30% of the maximum load current. The inductor current ripple  $(\Delta I_{\rm L})$  can be calculated by:

$$\Delta I_{L} = \frac{(V_{IN} - V_{OUT}) \times D}{L \times f_{SW}}$$

Therefore, L can be initially set to the following by applying the 30% rule:

$$L = \frac{(V_{IN} - V_{OUT}) \times D}{0.3 \times f_{SW} \times I_{OUT}}$$

The other features of the inductor that can be selected besides inductance value are saturation current and core material. Because the LM1770 does not have a current limit, it is recommended to have a saturation current higher than the maximum output current to handle any ripple or momentary over-current events. The core material also influences the saturation characteristics as ferrite materials have a hard saturation curve and care should be taken such that they never saturate during normal use. A shielded inductor or low

## Design Guide (Continued)

profile unshielded inductor is recommended to reduce EMI. This also helps prevent any spurious noise from picking up on the feedback node resulting in unexpected tripping of the feedback comparator.

#### **OUTPUT CAPACITOR**

One of the most important components to select with the LM1770 is the output capacitor. This is because its size and ESR have a direct effect on the stability of the loop. A constant on-time control scheme works by sensing the output voltage ripple and switching the FETs appropriately. The output voltage ripple on a buck converter can be approximated by stating that the AC inductor ripple flows entirely into the output capacitor and is created by the ESR of the capacitor. This can be expressed in the following equation:

$$\Delta V_{OUT} = \Delta I_{L} \times R_{ESR}$$

To ensure stability, two constraints need to be met. The first is that there is sufficient ESR to create enough voltage ripple at the feedback pin. The recommendation is to have at least 10mV of ripple seen at the feedback pin. This can be calculated by multiplying the output voltage ripple by the gain seen through the feedback resistors. This gain, H, can be calculated below:

$$H = \frac{V_{FB}}{V_{OUT}} = \frac{0.8V}{V_{OUT}}$$

If the output voltage is fairly high, causing significant attenuation through the feedback resistors, a feed-forward capacitor can be used. This is actually recommended for most circuits as it improves performance. See the feed-forward capacitor section for more details.

The second criteria is to ensure that there is sufficient ripple at the output that is in-phase with the switch. The problem exists that there is actually ripple caused by the capacitor charging and discharging, not only the ESR ripple. Since these are effectively out of phase, problems can exist. To avoid this issue it is recommended that the ratio of the two ripples ( $\beta$ ) is always greater than 5. To calculate the minimum ESR value needed, the following equation can be used.

$$R_{ESR} \ge \frac{\beta x t_P}{8 x C}$$

In general the best capacitors to use are chemistries that have a known and consistent ESR across the entire operating temperature range. Tantalum capacitors or similar chemistries such as Niobium Oxide perform well along with certain families of Aluminum Electrolytics. Small value POSCAPs and SP CAPs also work as they have sufficient ESR. When used in conjunction with a low value inductor it is possible to have an extremely stable design. The only capacitors that require modification to the circuit are ceramic capacitors. Ceramic capacitors cause problems meeting both criteria because they have low ESR and low capacitance. Therefore, if they are to be used, an external ESR resistor (RSNS) should be added. This can be seen below in the following circuit.

This circuit uses an additional resistor in series with the inductor to add ripple at the output. It is placed in this location and used in combination with the feed-forward capacitor ( $C_{\text{FF}}$ ) to provide ripple to the feedback pin, without adding ripple or a DC offset to the output. The benefit of using a ceramic capacitor is still obtained with this technique. Because the addition of the resistor results in power loss, this circuit implementation is only recommended for low currents (2A and below). The power loss and rating of the resistor should be taken into account when selecting this component.

This circuit implementation utilizing the feed-forward capacitor begins to experience limitations when the output voltage is small. Previously the circuit relied on the  $C_{\rm FF}$  for all the ripple at the feedback node by assuming that the resistor divider was negligible. As  $V_{\rm OUT}$  decreases this can not be assumed. The resistor divider contributes a larger amount of ripple which is problematic as it is also out of phase. Therefore the resistor location should be changed to be in series with the output capacitor. This can be viewed as adding an effective ESR to the output capacitor.

## Design Guide (Continued)

#### **FEED-FORWARD CAPACITOR**

The feed-forward capacitor is used across the top feedback resistor to provide a lower impedance path for the high frequency ripple without degrading the DC accuracy. Typically the value for this capacitor should be small enough to prevent load transient errors because of the discharging time, but large enough to prevent attenuation of the ripple voltage. In general a small ceramic capacitor in the range of 1nF to 10nF is sufficient.

If  $C_{\text{FF}}$  is used then it can be assumed that the ripple voltage seen at the feedback pin is the same as the ripple voltage at the output. The attenuation factor H no longer needs to be used. However, in these conditions, it is recommended to have a minimum of 20mV ripple at the feedback pin. The use of a  $C_{\text{FF}}$  capacitor is recommended as it improves the regulation and stability of the design. However, its benefit is diminished as  $V_{\text{OUT}}$  starts approaching  $V_{\text{REF}}$ , therefore it is not needed in this situation.

#### **INPUT CAPACITOR**

The dominating factor that usually sets an input capacitors' size is the current handling ability. This is usually determined by the package size and ESR of the capacitor. If these two criteria are met then there usually should be enough capacitance to prevent impedance interactions with the source. In general it is recommended to use a ceramic capacitor for the input as they provide a low impedance and small footprint. One important note is to use a good dielectric for the ceramic capacitor such as X5R or X7R. These provide better over temperature performance and also minimize the DC voltage derating that occurs on Y5V capacitors. To calculate the input capacitor RMS current, the equation below can be used:

$$I_{CIN\_RMS} = I_{OUT} \sqrt{D \left(1 - D + \frac{\Delta I_L^2}{12 \times I_{OUT}^2}\right)}$$

which can be approximated by,

$$I_{CIN RMS} = I_{OUT} \times \sqrt{D(1 - D)}$$

## **MOSFET Selection**

The two FETs used in the LM1770 requires attention to selection of parameters to ensure optimal performance of the power supply. The high side FET should be a PFET and the low side an NFET. These can be integrated in one package or as two separate packages. The criteria that matter in selection are listed below:

### **VDS VOLTAGE RATING**

The first selection criteria is to select FETs that have sufficient  $V_{\rm DS}$  voltage ratings to handle the maximum voltage seen at the input plus any transient spikes that can occur from parasitic ringing. In general most FETs available for this application will have ratings from 8V to 20V. If a larger voltage rating is used then the performance will most likely be degraded because of higher gate capacitance.

## **RDSON**

The  $R_{\mathrm{DS(ON)}}$  specification is important as it determines several attributes of the FET and the overall power supply. The first is that it sets the maximum current of the FET for a given package. A lower  $R_{\mathrm{DS(ON)}}$  will permit a higher allowable current and reduce conduction losses, however, it will increase the gate capacitance and the switching losses.

#### **GATE DRIVE**

The next step is to ensure that the FETs are capable of switching at the low Vin supplies used by the LM1770. The FET should have the Rdson specified at either 1.8V or 2.5V to ensure that it can switch effectively as soon as the LM1770 starts up.

### **GATE CHARGE**

Because the LM1770 utilizes a fixed dead-time scheme to prevent cross conduction, the FET transitions must occur in this time. The rise and fall time of the FETs gate can be influenced by several factors including the gate capacitance.

## MOSFET Selection (Continued)

Therefore the total gate charge of both FETs should be limited to less than 20nC at 4.5V  $V_{\rm GS}$ . The lower the number the faster the FETs should switch and the better the efficiency.

#### **RISE / FALL TIMES**

A better indication of the actual switching times of the FETs can be found in their electrical characteristics table. The rise and fall time should be specified and selected to be at a minimum. This helps improve efficiency and ensuring that shoot through does not occur.

#### **GATE CHARGE RATIO**

Another consideration in selecting the FETs is to pay attention to the Qgd / Qgs ratio. The reason for this is that proper selection can prevent spurious turn on. If we look at the NFET for example, when the FET is turning off, the gate signal will pull to ground. Conversely the PFET will be turning on, causing the SW node to rise towards  $V_{\rm IN}.$  The gate to drain capacitance of the NFET couples the SW node to the gate and will cause it to rise. If this voltage is excessive, then it could weakly turn on the low side FET causing an efficiency loss. However, this coupling is mitigated by having a large gate to source capacitance of the FET, which helps to hold the gate voltage down. Ideally, a very low Qgd / Qgs would be ideal, but in practice it is common to find the number around 1. As a general rule, the lower the ratio, the better.

If the above selection criteria have been met it is useful to generate a figure of merit to allow comparison between the FETs. One such method is to multiply the  $R_{\rm DS(ON)}$  of the FET by the total gate charge. This allows an easy comparison of the different FETs available. Once again, the lower the product, the better.

#### FEEDBACK RESISTORS

The feedback resistors are used to scale the output voltage to the internal reference value such that the loop can be regulated. The feedback resistors should not be made arbitrarily large as this creates a high impedance node at the feedback pin that is more susceptible to noise. A combined value of  $50 k\Omega$  for the two resistors is adequate. To calculate the resistor values use the equation below. Typically the low side resistor is initially set to a pre-determined value such as  $10 \ k\Omega$ .

$$R_{FB1} = R_{FB2} \left( \frac{V_{FB}}{V_{OUT}} - 1 \right)$$

$V_{\text{FB}}$  is the internal reference voltage that can be found in the electrical characteristics table or approximated by 0.8V.

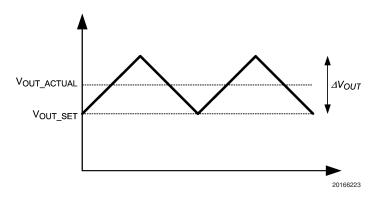

The output voltage value can be set in a precise manner by taking into account the fact that the reference voltage is regulating the bottom of the output ripple as opposed to the average value. This relationship is shown in the figure below.

It can be seen that the average output voltage (VOUT\_ACTUAL) is higher than the output voltage (VOUT\_SET) that was calculated by the earlier equation by exactly half the output voltage ripple. The output voltage that is targeted for regulation may then be appended according to the voltage ripple. This can be seen below:

$$V_{\text{OUT\_ACTUAL}} = V_{\text{OUT\_SET}} + \frac{1}{2} \Delta V_{\text{OUT}} = V_{\text{OUT\_SET}} + \frac{1}{2} \Delta I_{\text{L}} \ x$$

$$R_{\text{ESR}}$$

## **Efficiency Calculations**

One of the most important parameters to calculate during the design stage is the expected efficiency of the system. This can help determine optimal FET selection and can be used to calculate expected temperature rise of the individual components. The individual losses of each component are broken down and the equations are listed below:

#### QUIESCENT CURRENT

The quiescent current consumed by the LM1770 is one of the major sources of loss within the controller. However, from a system standpoint this is usually less than 0.5% of the overall efficiency. Therefore, it could easily be omitted but is shown for completeness:

$$P_{IQ} = V_{IN} \times I_{Q}$$

### **CONDUCTION LOSS**

There are three losses associated with the external FETs. From the DC standpoint there is the I-squared R loss, caused by the on resistance of the FET. This can be modeled for the PMOS by:

$$P_{P\_COND} = D \times R_{DSON\_PMOS} \times I_{OUT}^2$$

and the NMOS by:

$$P_{N\_COND} = (1 - D) \times R_{DSON\_NMOS} \times I_{OUT}^{2}$$

## Efficiency Calculations (Continued)

#### **SWITCHING LOSS**

The next loss is the switching loss that is caused by the need to charge and discharge the gate capacitance of the FETs every cycle. This can be approximated by:

$$P_{P\_SWITCH} = V_{IN} \times Q_{g\_PMOS} \times f_{SW}$$

for the PMOS, and the same approach can be adapted for the NMOS:

$$P_{N \text{ SWITCH}} = V_{IN} \times Q_{q \text{ NMOS}} \times f_{SW}$$

#### TRANSITIONAL LOSS

The last FET power loss is the transitional loss. This is caused by switching the PMOS while it is conducting current. This approach only models the PMOS transition, the NMOS loss is considered negligible because it has minimal drain to source voltage when it switches due to the conduction of the body diode. Therefore the transitional loss of the PMOS can be modeled by:

$$P_{P\_TRANSITIONAL} = 0.5 \text{ x V}_{IN} \text{ x I}_{OUT} \text{ x f}_{SW} \text{ x (t}_r + t_f)$$

$t_r$  and  $t_f$  are the rise and fall times of the FET and can be found in their corresponding datasheet. Typically these numbers are simulated using a  $6\Omega$  drive, which corresponds well to the LM1770. Given this, no adjustment is needed.

#### **DCR LOSS**

The last source of power loss in the system that needs to be calculated is the loss associated with the inductor resistance (DCR) which can be calculated by

$$P_{DCB} = R_{DCB} \times I_{OUT}^2$$

#### **EFFICIENCY**

The efficiency,  $\eta$ , can then be calculated by summing all the power losses and then using the equation below:

$$\eta = \frac{P_{\text{OUT}}}{P_{\text{OUT}} + P_{\text{LOSSES}}}$$

## **Thermals**

By breaking down the individual power loss in each component it makes it easy to determine the temperature rise of each component. Generally the expected temperature rise of the LM1770 is extremely low as it is not in the power path. Therefore the only two items of concern are the PMOS and the NMOS. The power loss in the PMOS is the sum of the conduction loss and transitional loss, while the NMOS only has conduction loss. It is assumed that any loss associated with the body diode conduction during the dead-time is negligible.

For completeness of design it is important to watch out for the temperature rise of the inductor. Assuming the inductor is kept out of saturation the predominant loss will be the DC copper resistance. At higher frequencies, depending on the core material, the core loss could approach or exceed the DCR losses. Consult with the inductor manufacturer for appropriate temp curves based on current.

## Layout

The LM1770, like all switching regulators, requires careful attention to layout to ensure optimal performance. The following steps should be taken to aid in the layout. For more information refer to Application Note AN-1299.

- Ensure that the ground connections of the input capacitor, output capacitor and NMOS are as close as possible. Ideally these should all be grounded together in close proximity on the component side of the board.

- 2. Keep the switch node small to minimize EMI without degrading thermal cooling of the FETs.

- Locate the feedback resistors close to the IC and keep the feedback trace as short as possible. Do not run any feedback traces near the switch node.

- Keep the gate traces short and keep them away from the switch node as much as possible.

- 5. If a small bypass capacitor is used on  $V_{IN}$  (0.1 $\mu$ F) place it as close to the pin, with the ground connection as close to the chip ground as possible.

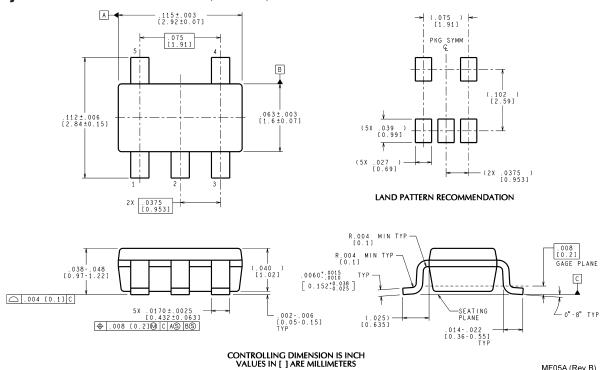

## Physical Dimensions inches (millimeters) unless otherwise noted

SOT23-5 Package **NS Package Number MF05A**

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor manufactures products and uses packing materials that meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no "Banned Substances" as defined in CSP-9-111S2.

Leadfree products are RoHS compliant.

**National Semiconductor Americas Customer** Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

**National Semiconductor Europe Customer Support Center** Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171 Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Support Center Email: ap.support@nsc.com

National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560

MF05A (Rev B)