# **Amplifiers**

# LH0084/LH0084C Digitally-Programmable-Gain Instrumentation Amplifier

# **General Description**

The LH0084/LH0084C is a self-contained, high speed, high accuracy, digitally-programmable-gain instrumentation amplifier. It consists of paired FET-input variable-gain voltage-follower input stages followed by a differential-to-single-ended output stage. The input stage is programmable in accurate gain steps of 1, 2, 5, or 10 controlled by the logic levels of a 2-bit TTL-compatible digital input word. For additional flexibility, the output stage is pin-strappable to fixed gains of 1, 4, or 10 for an overall gain range of 1 to 100.

Applications include increased dynamic range A-to-D converters, test systems, and post multiplexer amplifier for data acquisition systems.

The device exhibits high input impedance, low offset voltage, high CMRR and PSRR, high speed, and excellent gain accuracy and gain non-linearity.

The LH0084 is guaranteed from  $-55^{\circ}$ C to  $+125^{\circ}$ C. The LH0084C is guaranteed from  $-25^{\circ}$ C to  $+85^{\circ}$ C. Both devices are provided in a hermetically sealed 16-lead dual-in-line metal package.

### **Features**

- Excellent gain accuracy and gain non-linearity

- Extremely low gain drift

- 10 ppm/°Cmax

Highinput impedance 10<sup>11</sup>Ω typ

High CMRR and PSRR 70 dB min

- High CMRR and PSRRTTL compatible digital inputs

- High speed, settling to 0.1%

- 4μs max

0.05% max

0.01% typ

# **Simplified Schematic**

# DIGITAL DI 05 SWITCH NETWORK R1 A3 10 VOUT (FORCE) DIGITAL GND 14 SWITCH NETWORK R1 A3 10 VOUT (FORCE) R8 R14 VOUT (SENSE) R10 G1 SIGNAL R15 11 OG10 R11 G10 SIGNAL R15 11 OG10

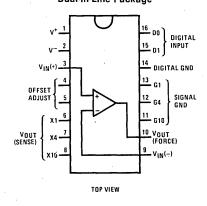

# **Connection Diagram**

### Dual-In-Line Package

Case is electrically isolated

Order Number LH0084D or LH0084CD See NS Package D16D

# **Absolute Maximum Ratings**

Supply Voltage (Note 1)

Analog Input Voltage (Note 2)

Differential Input Voltage (Note 2)

Digital Input Voltage

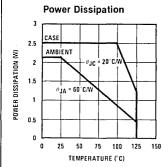

Power Dissipation (See Curve)

± 15V ± 30V - 4V, + 18V 2.5W

± 18V

Output Short Circuit Duration

Operating Temperature Range

LH0084 LH0084C

Storage Temperature Lead Temperature (Soldering, 20 seconds) Continuous

-55°C to +125°C -25°C to +85°C -65°C to +150°C

+ 300 °C

# DC Electrical Characteristics $V_S = \pm 15 V, R_L = 10 \text{ k}\Omega, T_{MIN} \leq T_A \leq T_{MAX} \text{ unless noted}$

| Parameter             |                       | Conditions                   |                        | LH0084 |                  | LH0084C                                          |              |                  | Units       |                                                  |

|-----------------------|-----------------------|------------------------------|------------------------|--------|------------------|--------------------------------------------------|--------------|------------------|-------------|--------------------------------------------------|

|                       |                       |                              |                        | Min    | Тур              | Max                                              | Min          | Тур              | Max         | Units                                            |

| V <sub>IOS</sub>      | Input Offset Voltage  |                              | T <sub>j</sub> = 25,°C |        | 0.3              | 5                                                | [            | 0.3              | 10          | mV                                               |

|                       |                       | ,                            |                        |        |                  | 7                                                |              |                  | 13          | 1                                                |

| ΔV <sub>IOS</sub> /ΔT | Input Offset Voltage  | $R_S = 100\Omega$            |                        |        | 10               |                                                  |              | 10               | -           | μV/°C                                            |

|                       | Change with           |                              | ] ]                    |        | ]                |                                                  | }            | ]                |             | 1                                                |

|                       | Temperature           | $V_{CM} = 0$                 | 1 1                    |        |                  |                                                  |              |                  |             | l                                                |

| V <sub>oos</sub>      | Output Offset Voltage | (Note 3)                     | T <sub>i</sub> = 25°C  |        | 0.6              | 5                                                |              | 0.6              | 10          |                                                  |

|                       |                       |                              |                        |        |                  | 7                                                |              |                  | 13          | m∨                                               |

| ΔV <sub>OOS</sub> /ΔT | Output Offset Voltage |                              | 1                      |        | 20               |                                                  |              | 20               |             | μV/°C                                            |

| 000                   | Change with           |                              |                        |        |                  | i<br>I                                           |              | 1                |             | 1                                                |

|                       | Temperature           | !                            |                        |        |                  |                                                  |              | ł                |             |                                                  |

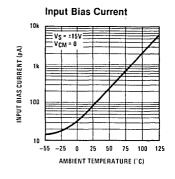

| В                     | Input Bias Current    |                              | T <sub>i</sub> = 25°C  |        | 150              | 500                                              |              | 150              | 500         | pA                                               |

| 5                     | (Note 4)              |                              |                        |        | <del> </del>     | 500                                              | <u> </u>     |                  | 100         | nA                                               |

| los                   | Input Offset Current  |                              | T <sub>i</sub> = 25°C  |        | 50               | 200                                              |              | 50               | 200         | pΑ                                               |

| .03                   |                       |                              |                        |        |                  | 200                                              |              |                  | 50          | nA                                               |

| R <sub>IN</sub>       | Input Resistance      | Differential                 | L                      |        | 10 <sup>11</sup> | <del> </del>                                     | <del> </del> | 10 <sup>11</sup> | <del></del> | <del> </del>                                     |

| ' 'IN                 | input ricolotanice    | Common-Mode                  |                        |        | 1011             |                                                  | ļ            | 1011             |             | Ω                                                |

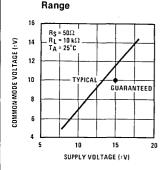

| V <sub>IN</sub>       | Input Voltage Range   |                              |                        | ± 10   |                  |                                                  | ± 10         | 1                |             | V                                                |

| A <sub>V</sub>        | Voltage Gain          | See Table I                  |                        |        | 1                | <del></del>                                      | <del> </del> | 1                |             | <del>                                     </del> |

| <b>~</b> V            | voltage Gain          | See Table I                  |                        |        | 2                |                                                  |              | 2                |             |                                                  |

|                       |                       |                              |                        |        | 5                |                                                  |              | 5                |             |                                                  |

|                       | ,                     |                              |                        |        | 10               | ]                                                | 1            | 10               |             | v/v                                              |

|                       |                       |                              |                        |        | 20               |                                                  | Ì            | 20               |             | '''                                              |

|                       |                       |                              |                        |        | 50               |                                                  | ŀ            | 50               |             |                                                  |

|                       |                       |                              |                        |        | 100              | }                                                |              | 100              |             | 1                                                |

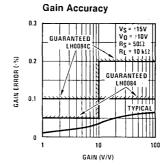

|                       | Gain Error            | A <sub>V</sub> = 1, 2, 5     |                        |        | 0.01             | 0.05                                             | <del> </del> | 0.02             | 0.1         |                                                  |

|                       |                       | $A_V = 10, 20, 50, 100$      | $T_A = 25$ °C          |        | 0.02             | 0.1                                              | <del></del>  | 0.03             | 0.2         | 1                                                |

|                       |                       | A <sub>V</sub> = 1, 2, 5     |                        |        | 0.02             | 0.2                                              | <u> </u>     | 0.02             | 0.2         | 1                                                |

|                       |                       | $A_V = 10, 20, 50, 100$      |                        |        | 0.03             | 0.3                                              |              | 0.03             | 0.3         | %                                                |

|                       | Gain Nonlinearity     |                              | T <sub>A</sub> = 25°C  |        | 0.002            | <u> </u>                                         |              | 0.002            | -           | 1                                                |

|                       | ,                     |                              | -A - 20 0              |        | 0.005            |                                                  |              | 0.005            |             | 1                                                |

| ΔΑ <sub>V</sub> /ΔΤ   | Gain Temperature      |                              | L                      |        | 1                | 10                                               | <del> </del> | 1                | 10          | ppm/°                                            |

| Δ, (γ, <u>Δ</u> , 1   | Coefficient           |                              |                        |        |                  |                                                  | Ì            | ] ' ]            |             | ppiiii                                           |

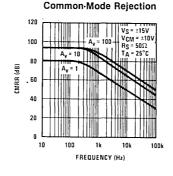

| CMRR                  | Common-Mode           | $V_{IN} = \pm 10V$           | A <sub>V</sub> = 1     | 70     | 80               | <del>                                     </del> | 70           | 80               |             |                                                  |

|                       | Rejection Ratio       | ",                           | A <sub>V</sub> = 10    | 76     | 94               | <b> </b>                                         | 76           | 94               |             | 7                                                |

|                       |                       |                              | A <sub>V</sub> = 100   | 80     | 94               |                                                  | 80           | 94               |             | 1                                                |

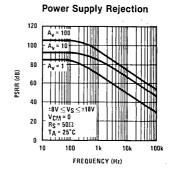

| PSRR                  | Power Supply          | $\pm 8V \le V_S \le \pm 18V$ | A <sub>V</sub> = 1     | 70     | 84               | <u> </u>                                         | 70           | 84               |             | dB                                               |

|                       | Rejection Ratio       |                              | A <sub>V</sub> = 10    | 76     | 92               | <del> </del>                                     | 76           | 92               |             | 1                                                |

|                       |                       |                              | $A_V = 100$            | 80     | 104              | 1                                                | 80           | 104              |             | 1                                                |

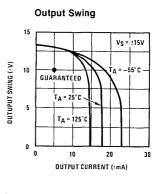

| v <sub>o</sub>        | Output Voltage Swing  | R <sub>L</sub> ≥10 kΩ        |                        | ± 10   | ± 12             | 1                                                | ± 10         | ± 12             |             | V                                                |

| С                     | Output Short-Circuit  |                              | T <sub>A</sub> = 25°C  | ± 5    | ± 18             | ± 40                                             | ±5           | ± 18             | ± 40        | mA                                               |

|                       |                       |                              |                        | ± 2    |                  | ± 40                                             | ± 2          | -                |             |                                                  |

# DC Electrical Characteristics (Continued) $V_S = \pm 15V$ , $R_L = 10 \text{ k}\Omega$ , $T_{MIN} \le T_A \le T_{MAX}$ unless noted

| Parameter          |                                | Conditions             |     | LH0084 | .H0084 |     | LH0084C |      |       |

|--------------------|--------------------------------|------------------------|-----|--------|--------|-----|---------|------|-------|

|                    |                                |                        |     | Тур    | Max    | Min | Тур     | Max  | Units |

| r <sub>O</sub>     | Output Resistance              |                        |     | 0.05   |        |     | 0.05    |      | Ω     |

| VIL                | Digital ''0''<br>Input Voltage |                        |     |        | 0.7    |     |         | 0.7  | V     |

| V <sub>IH</sub>    | Digital "1"<br>Input Voltage   |                        | 2.0 |        |        | 2.0 |         |      |       |

| l <sub>IL</sub>    | Digital "0"<br>Input Current   | V <sub>IN</sub> = 0.4V |     | 1.5    | 40     |     | 1.5     | 40   |       |

| I <sub>IH</sub>    | Digital "1"<br>Input Current   | V <sub>IN</sub> = 2.4V |     | 0.01   |        |     | 0.01    |      | μΑ    |

| V <sub>S</sub>     | Supply Voltage<br>Range        |                        | ± 8 |        | ± 18   | ± 8 |         | ± 18 | V     |

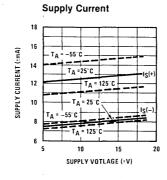

| I <sub>S</sub> (+) | Positive Supply<br>Current     | W 40V                  |     | 12     | 18     |     | 12      | 26   | ^     |

| I <sub>S</sub> (-) | Negative Supply<br>Current     | V <sub>S</sub> ≤ ± 18V |     | 8      | 12     |     | 8       | 14   | mA    |

| P <sub>D</sub>     | Power Dissipation              | V <sub>S</sub> = ± 15V |     | 315    | 450    |     | 315     | 600  | mW    |

# AC Electrical Characteristics $V_S=\pm\,15V, T_A=25\,^{\circ}C,~R_L=10~k\Omega$

|                | Parameter                                 | Condition              | S                                      | Min | Тур  | Max | Units |

|----------------|-------------------------------------------|------------------------|----------------------------------------|-----|------|-----|-------|

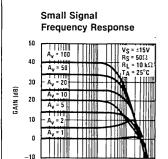

| BW             | Bandwidth (Figure 1)                      | Small Signal,          | $A_V = 1$                              |     | 3250 |     |       |

|                |                                           | - 3 dB                 | $A_V = 10$                             |     | 500  |     |       |

|                |                                           |                        | $A_V = 100$                            |     | 350  |     |       |

|                |                                           | Small Signal,          | A <sub>V</sub> = 1                     |     | 300  |     | kHz   |

|                |                                           | -1%                    | $A_V = 10$                             |     | 75   |     | 1     |

|                |                                           |                        | A <sub>V</sub> = 100                   |     | 55   |     | ]     |

| PBW            | Power Bandwidth                           | V <sub>o</sub> = ± 10V |                                        |     | 200  |     | 1     |

| SR             | Slew Rate                                 |                        |                                        | 10  | 13   | ,   | V/μs  |

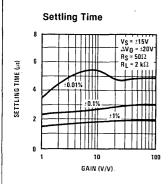

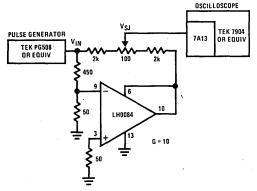

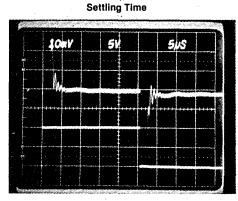

| ts             | Settling Time (Figure 2)                  | $\Delta V_0 = \pm 20V$ | A <sub>V</sub> = 1                     |     | 2.3  | 3.0 |       |

|                | ± 0.1%                                    |                        | $A_V = 10$                             |     | 2.7  | 3.5 | 7     |

|                |                                           |                        | $A_V = 100$                            |     | 3.1  | 4.0 | μS    |

|                | Gain Switching Time                       |                        |                                        |     | 3.5  |     | ,     |

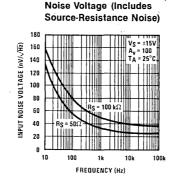

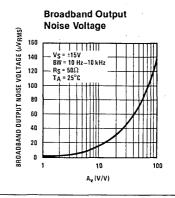

| E <sub>N</sub> | Equivalent Input                          | BW = 0.1 Hz-10 Hz      | BW = 0.1 Hz-10 Hz<br>BW = 10 Hz-10 kHz |     | 7    |     | μVp-p |

|                | Noise Voltage (Figure 3)                  | BW = 10 Hz-10 kHz      |                                        |     | 1.4  |     | μVrms |

| I <sub>N</sub> | Equivalent Input Noise Current (Figure 3) | BW = 10 Hz-10 kHz      |                                        |     | 30   |     | pArms |

$\textbf{Note 1:} \ \, \textbf{Improper supply power-on sequence may damage the device}. See Power Supply Connection section under Applications Information.$

Note 2: For supply voltages less than  $\pm$  15V the maximum input voltage is equal to the supply voltage.

Note 3: Due to limited production test time, these parameters are specified at junction temperature,  $T_J$ . In normal operation the junction temperature rises above the ambient temperature,  $T_A$ , as a result of internal power dissipation,  $P_D$ .  $T_J = T_A + \theta_{JA}P_D$  where  $\theta_{JA}$  is the thermal resistance from junction to ambient.

Note 4: The input bias currents are junction leakage currents which approximately double for every 10 °C increase in the junction temperature.

# **Typical Performance Characteristics**

100

Input Common-Mode

FREQUENCY (Hz)

**Equivalent Input**

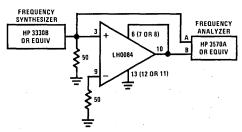

# **AC Test Circuits**

FIGURE 1. Frequency Response Measurement Circuit

FIGURE 2. Settling Time Measurement Circuit

Ay = 10 Input Stage

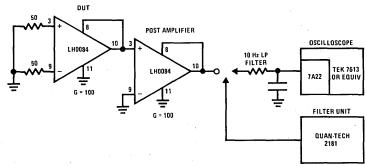

FIGURE 3. Noise Measurement Circuit

### Wideband Noise

$R_S = 50\Omega$  Bandwidth 0.1 Hz to 10 Hz  $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$   $^{\circ}$  Seconds/Division Horizontal

# **Applications Information**

### THEORY OF OPERATION

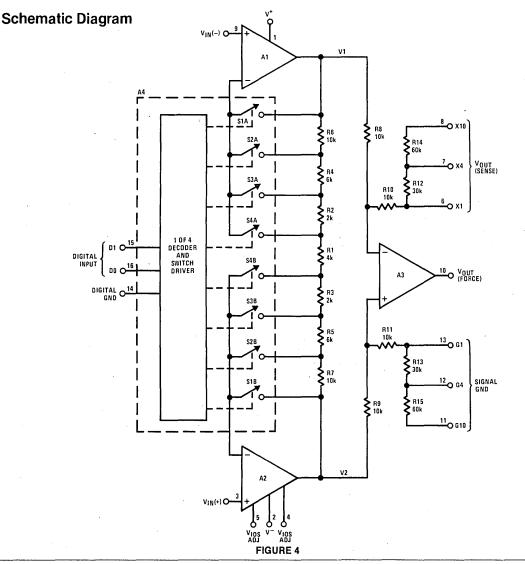

The LH0084 is a digitally-programmable-gain true-instrumentation amplifier composed of a variable-gain voltage-follower input stage (A1 and A2), followed by a differential output stage (A3). The schematic is shown in *Figure 4*.

The input stage contains matched high-speed FET-input op amps (A1 and A2). A high-stability temperature-compensated resistor network (R1 through R7) controls feedback ratios at the inverting inputs of op amps A1 and A2 via FET switches S1A-S4A and S1B-S4B. Since the FET switches are in series with the op amp input impedance their resistance match and temperature drift do not degrade the gain accuracy of the instrumentation amplifier. The FET switches are controlled through a 1-of-4 decoder and switch driver, by the logic levels applied at the digital input terminals D1 and D0 and set the gain of the input stage as shown in Table I.

If, for example, D1 is High ( $\geq$  2.0V) and D0 is Low ( $\leq$  0.7V), FET switch pair S3A and S3B will be closed (and all remaining switches open). The input stage gain,  $A_{V(1)}$ , can then be shown to be:

$$A_{V(1)} = \frac{V2 - V1}{V_{1N}(+) - V_{1N}(-)}$$

$$= 1 + \frac{R4 + R5 + R6 + R7}{R1 + R2 + R3}$$

$$= 1 + \frac{6k + 6k + 10k + 10k}{4k + 2k + 2k}$$

$$= 5$$

(1)

| TABLE | <b>GAIN TRUTH</b> | TARLE AND | CONNECTIO | NTARIF |

|-------|-------------------|-----------|-----------|--------|

|       |                   |           |           |        |

| Digital Inputs   |                  | 1st Stage<br>Gain | Pin Connections | 2nd Stage<br>Gain | Overall<br>Gain       |  |

|------------------|------------------|-------------------|-----------------|-------------------|-----------------------|--|

| D1               | D0               | A <sub>V(1)</sub> |                 | A <sub>V(2)</sub> | A <sub>V</sub>        |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>2<br>5<br>10 | 6-10, 13-GND    | 1                 | 1<br>2<br>5<br>10     |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>2<br>5<br>10 | 7-10, 12-GND    | 4                 | 4<br>8<br>20<br>40    |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 1<br>2<br>5<br>10 | 8-10, 11-GND    | 10                | 10<br>20<br>50<br>100 |  |

The output stage, consisting of op amp A3 and resistors R8 through R15, converts the voltage difference at the output of the input stage, V2 minus V1, to a single-ended output. For increased flexibility of the LH0084, the output stage gain is pin-strappable by selecting R10, R10 + R12, or R10 + R12 + R14 as feedback resistor for A3. The ratios of these resistors to the differential stage input resistor R3 are kept very accurate to maintain the excellent overall gain accuracy of the device. The output stage gain,  $\Lambda_{V(2)}$ , is equal to the feedback resistance divided by the input resistance. Thus with, for example, Pin 7 wired to Pin 10, that gain would be:

$$A_{V(2)} = \frac{V_{OUT}}{V2 - V1}$$

$$= \frac{R10 + R12}{R8}$$

$$= \frac{10k + 30k}{10k}$$

$$= 4$$

(2)

To preserve the high common-mode rejection ratio of the output stage, the ground sense resistor, R11, R11 + R13 or R11 + R13 + R15, must match the feedback resistor used.

The overall gain of the LH0084 is therefore:

$$A_{V} = \frac{V_{OUT}}{V_{IN}(+) - V_{IN}(-)}$$

$$= \frac{V2 - V1}{V_{IN}(+) - V_{IN}(-)} \cdot \frac{V_{OUT}}{V2 - V1}$$

$$= A_{V(1)} \cdot A_{V(2)}$$

(3)

The different gains available are in the range of 1 through 100 and are summarized in Table I.

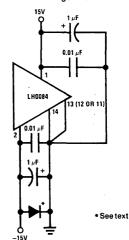

### **POWER SUPPLY CONNECTIONS**

Proper power supply connections are shown in Figure 5. The power supplies should be bypassed to ground as close as possible to device supply pins. For optimum high speed performance V  $^+$  and V  $^-$  should be decoupled with a 0.01  $\mu F$  ceramic disc in parallel with a 1  $\mu F$  electrolytic capacitor.

The two ground pins, analog and digital grounds, should be connected together as close to the device as possible, preferably with a ground plane underneath the device. If this is not possible, the grounds should be connected together locally with back-to-back diodes and hard-wired together off-board. If a ground reference offset is used, it must be low impedance compared to the ground sense resistance to avoid CMRR degradation.

Care must be taken in the supply power-on sequence. The LH0084 may suffer irreversible damage if the V  $^+$  supply is applied prior to the powering on of the V  $^-$  supply. In most applications using dual tracking supplies and with the device supply pins adequately bypassed, this will not present a problem. If this cannot be guaranteed, a germanium or Schottky protection diode should be connected between the digital ground pin and the V  $^-$  pin as shown in Figure 5.

FIGURE 5. Power Supply Connections

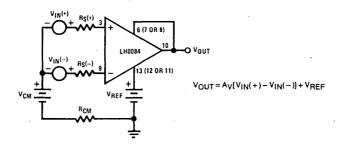

### SIGNAL CONNECTIONS

The input signals should be connected as shown in Figure 6. To minimize errors,  $R_S(+)$ ,  $R_S(-)$  and  $R_{CM}$  should be kept as small as possible.

The output connections are also shown in *Figure 6*. The feedback leads should be kept short as should the ground sense in order to minimize lead resistance and parasitic capacitance.

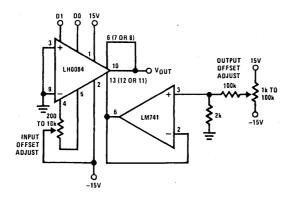

### **OFFSET AND GAIN ADJUSTMENTS**

Special care must be taken when using external offset adjustment. Since the LH0084 is a 2-stage amplifier with each stage contributing offset errors, and the amplifier presumably is used at several different gains, it is important to realize that the offsets of both the 1st and the 2nd stages must be nulled to maintain zero offset referred to output (RTO) at all gain settings.

In general, it is recommended that the input stage offset ( $V_{IOS}$ ) be adjusted with a potentiometer as shown in Figure 7. The output stage offset ( $V_{OOS}$ ) is ideally adjusted at a subsequent gain stage (i.e. sample-and-hold or A-to-D converter), but if this is impractical, it may also be done as shown in Figure 7.

Recommended offset adjust procedure is as follows: Initially set both pots to center positions and short both inputs of the LH0084 to ground.

- a) Set the input stage gain to 1 (pull D1 and D0 low).

Measure the output voltage, V<sub>OUT1</sub>.

- Set the input stage gain to 10 (pull D1 and D0 high). Measure the new output voltage, V<sub>OUT2</sub>.

- c) Calculate the portion of V<sub>OUT2</sub> contributed by the output stage offset per the equation:

$$V_{OOS} = \frac{1}{9} (10 \cdot V_{OUT1} - V_{OUT2})$$

(4)

- d) While maintaining an input stage gain of 10, adjust the input offset voltage (V<sub>IOS</sub>) potentiometer until the output voltage is equal to the voltage calculated in Equation (4).

- e) Change the input back to a gain of 1 and adjust the output offset voltage (V<sub>OOS</sub>) potentiometer until the output voltage is zero.

FIGURE 6. Signal Connections

FIGURE 7. Offset Adjust Circuit

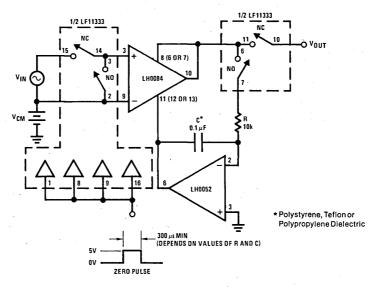

An alternate offset adjust scheme is shown in *Figure 8*. The offset should be rezeroed after each time the gain is changed or when the op amp integrator drift warrants a new zero pulse. An additional advantage of this adjustment technique is that it can also be used to cancel out offset voltage drift and common-mode voltage error contributions.

External gain adjustment is generally discouraged since gain accuracy can be optimized for one gain setting only. If gain adjustment is required, however, it should be done at a subsequent gain stage.

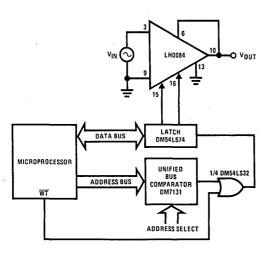

### LOGIC CONNECTIONS

The digital inputs D1 and D0 are referenced to the digital ground. The device interfaces directly to TTL and, with pull-down resistors, to CMOS.

Interfacing with microprocessors will usually require a latch. A circuit using full 6-bit wide address decode and write strobe is shown in *Figure 9*.

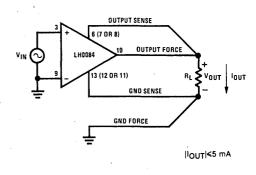

### **REMOTE OUTPUT SENSE**

The feedback resistors of the LH0084 can be connected directly at the load in order to eliminate errors due to lead resistance (*Figure 10*).

FIGURE 8. Auto Zero Circuit

FIGURE 9. Typical Microprocessor Interface

FIGURE 10. Remote Sense Connection

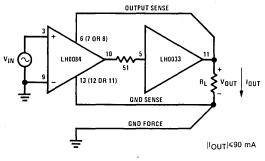

Also a unity gain buffer, such as the LH0033, may be included in the feedback loop for increased current drive capability as shown in *Figure 11*.

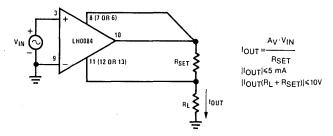

The output sense feature can also be used in other ways such as output offset, *Figure 12*, or current source output, *Figure 13*.

FIGURE 11. Buffered Output Connection

FIGURE 12. Output Offset Connection

FIGURE 13. Output Current Source Connection

# **Applications**

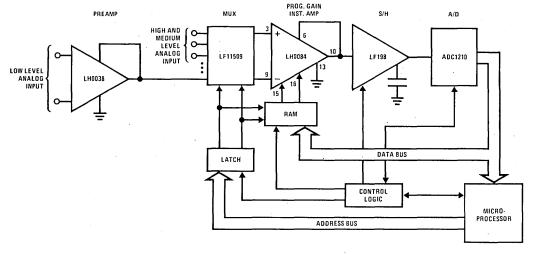

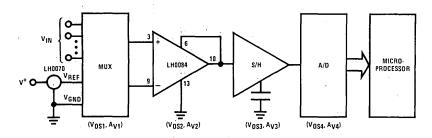

The LH0084 is ideal for application in increased dynamic range A-to-D converters, test systems, process control, and multi-channel data acquisition systems. Figure 14 shows the device used in a typical data acquisition-system.

A software offset and gain error correction scheme is shown in Figure 15. By first selecting a multiplexer input

connected to analog ground, and then selecting a channel connected to a reference of known value, the overall system gain and offset errors can be calculated. For all subsequent readings, offset and gain corrections can be made mathematically by solving a simple first-order equation in software.

FIGURE 14. Typical Data Acquisition System

### Applications (Continued)

FIGURE 15. Software System Offset and Gain Calibration Circuit

### **Definition of Terms**

Input Offset Voltage,  $V_{IOS}$ : The voltage which must be applied to the inputs to force the output of the input stage to 0V.  $V_{IOS}$  can be calculated by measuring  $V_{OS}$  (RTO) at input stage gains of 1 and 10 and using the following equation:

$$V_{IOS} = \frac{1}{9} \left( V_{OS} \middle|_{A_{V} = 10} - V_{OS} \middle|_{A_{V} = 1} \right)$$

where:

$$V_{OS} \Big|_{A_V = 10}$$

= Overall offset (RTO) for  $A_V = 10$

$V_{OS} \Big|_{A_V = 1}$  = Overall offset (RTO) for  $A_V = 1$

Input Offset Current, I<sub>OS</sub>: The difference in the currents into the 2 analog input terminals at 0V.

Input Bias Current, I<sub>B</sub>: The average of the currents into the 2 analog input terminals at OV.

Input Resistance, R<sub>IN</sub>: Common-mode input resistance is the change in input voltage range divided by the change in input bias current with both analog inputs at the same voltage. Differential input resistance is the change in input voltage at one input terminal divided by the change in input current at the other input terminal which is kept still at NV

Input Voltage Range,  $V_{\text{IN}}$ : The voltage range for which the device is operational.

Common-Mode Rejection Ratio, CMRR: The ratio of the input common-mode voltage range to the change in input offset voltage over this range.

Power Supply Rejection Ratio, PSRR: The ratio of the specified change in supply voltage to the change in input offset voltage over this range.

Voltage Gain, A<sub>V</sub>: The ratio of output voltage change to the input voltage change producing it.

Gain Error: The deviation in percent between the ideal voltage gain and the value obtained when the device is configured for that gain.

Gain Non-Linearity: The deviation of the gain from a straight line drawn through the end-points expressed as a percent of full-scale (10V for operation with  $\pm$  15V supply). For testing purposes it is the difference between positive swing gain (0V to 10V) and average gain (- 10V) to 10V) or between negative swing gain (0V to -10V) and average gain.

Output Stage Offset Voltage,  $V_{OOS}$ : The voltage which must be applied to the input of the output stage for the output to be forced to 0V.  $V_{OOS}$  can be calculated by measuring  $V_{OS}$  (RTO) at input stage gains of 1 and 10 and applying the following equation:

$$V_{OOS} = \frac{1}{Q} \left( 10 \cdot V_{OS} \Big|_{A_{V} = 1} - V_{OS} \Big|_{A_{V} = 10} \right)$$

where:

$$V_{OS} \Big|_{A_V = 1}$$

= Overall offset (RTO) for  $A_V = 1$

$V_{OS} \Big|_{A_V = 10}$  = Overall offset (RTO) for  $A_V = 10$

Offset Voltage (Referred to Output),  $V_{OS(RTO)}$ : The output voltage when both inputs are connected to 0V.  $V_{OS}$  is composed of input offset voltage,  $V_{IOS}$ , and output offset voltage,  $V_{OOS}$ , and is a function of amplifier gain. The overall offset voltage is given by:

$$V_{OS(RTO)} = A_{V(2)}(A_{V(1)} V_{IOS} + V_{OOS})$$

where:

V<sub>IOS</sub> = Input offset voltage

V<sub>OOS</sub> = Output stage offset voltage

$A_{V(1)} = Input stage gain$

$A_{V(2)}$  = Output stage gain

### **Definition of Terms** (Continued)

Output Voltage Swing, V<sub>0</sub>: The peak output voltage swing referenced to ground into specified load.

Output Short-Circuit Current, Io: The current supplied by the device with the output connected directly to ground.

Output Resistance, ro: The ratio of change in output voltage to change in output current around zero output.

Supply Voltage Range,  $V_{\rm S}$ : The supply voltage range for which the device is operational.

Supply Current, I<sub>s</sub>: The current required from the supply to operate the device with zero load and with the analog as well as the digital inputs at 0V.

**Power Dissipation, P\_D:** The power dissipated in the device with zero load and with the analog as well as the digital inputs at OV.

Digital "1" Input Voltage, V<sub>IH</sub>: Minimum voltage required at the digital input to guarantee a high logic state.

Digital "0" Input Voltage,  $V_{IL}$ : Maximum voltage required at the digital input to guarantee a low logic state.

**Digital "1" Input Current, I**<sub>IH</sub>: The current into a digital input at specified logic level.

**Digital "0" Input Current, I\_{\rm IL}:** The current into a digital input at specified logic level.

Average Input Offset Voltage Drift,  $\Delta V_{IOS}/\Delta T$ : The ratio of input offset voltage change from 25 °C to either temperature extreme divided by the temperature range.

Average Output Offset Voltage Drift, ΔV<sub>OOS</sub>/ΔT: The ratio of output offset voltage change from 25 °C to either temperature extreme divided by the temperature range.

Average Gain Temperature Coefficient,  $\Delta A_V/\Delta T$ : The ratio of change in gain from 25 °C to either temperature extreme divided by the temperature range.

**Small Signal Bandwidth, BW:** The frequency at which the device gain changes from the low frequency gain by a specified amount.

Power Bandwidth, PBW: Maximum frequency for which the output swing is a large signal sinewave without noticeable distortion.

Slew Rate, SR: The internally limited rate of change in output voltage with a large amplitude step function applied at the input.

Settling Time, t<sub>s</sub>: The time between the initiation of an input step function and the time when the output voltage has settled to within a specified error band of the final output voltage.

Gain Switching Time: The time between the initiation of a gain logic change and the time when the final gain switches are closed. It includes overdrive recovery time, but not settling to final value.

**Equivalent Input Noise Voltage, E<sub>N</sub>:** The rms or peak noise voltage referred to the input (RTI) over a specified frequency band.

Equivalent Input Noise Current,  $I_N$ : The rms or peak noise current referred to the input (RTI) over a specified frequency band.