# **Compact Disc Player DSP**

### Overview

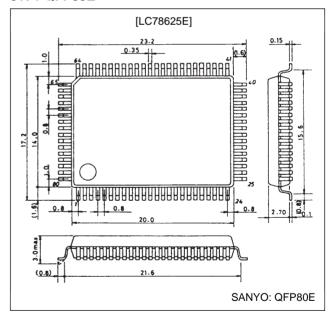

The LC78625E is a CMOS LSI that implements the signal processing and servo control required by compact disc players, laser discs, CD-V, CD-I and related products. The LC78625E provides several types of signal processing, including demodulation of the optical pickup EFM signal, de-interleaving, error detection and correction, and digital filters that can help reduce the cost of CD player units. It also processes a rich set of servo system commands sent from the control microprocessor. It also incorporates an EFM-PLL circuit and a one-bit D/A converter.

This LSI is an improved version of the LC78620E. In addition to supporting low-voltage operation, on/off control of the de-emphasis function and use of the bilingual function have been enabled in certain additional modes.

### **Functions**

- The LC78625E takes an HF signal as input, digitizes (slices) that signal at a precise level, converts that signal to an EFM signal, and generates a PLL clock with an average frequency of 4.3218 MHz by comparing the phases of that signal and an internal VCO.

- A precise reference clock and the necessary internal timings are generated using an external 16.9344 MHz crystal oscillator.

- Disc motor speed control using a frame phase difference signal generated from the playback clock and the reference clock

- Frame synchronization signal detection, protection, and interpolation to assure stable data readout

- EFM signal demodulation and conversion to 8-bit symbol data

- Subcode data separation from the EFM demodulated signal and output of that data to an external microprocessor

- Subcode Q signal output (LSB first) to a microprocessor over the serial interface after performing a CRC error check

- Demodulated EFM signal buffering in internal RAM to handle up to  $\pm 4$  frames of disc rotational jitter

- Demodulated EFM signal reordering in the prescribed order for data unscrambling and de-interleaving

- Error detection, correction, and flag processing (error correction scheme: dual C1 plus dual C2 correction)

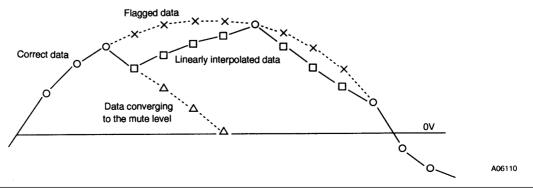

- The LC78625E sets the C2 flags based on the C1 flags and a C2 check, and then performs signal interpolation or muting depending on the C2 flags. The interpolation circuit uses a quadruple interpolation scheme. The output value converges to the muting level when four or more consecutive C2 flags occur.

# **Package Dimensions**

unit: mm

#### 3174-QFP80E

- Support for command input from a control microprocessor: commands include track jump, focus start, disk motor start/stop, muting on/off and track count (8-bit serial input)

- Built-in digital output circuits.

- · Arbitrary track counting to support high-speed data access

- D/A converter outputs with data continuity improved by 8× oversampling digital filters. (These filters function as 4× oversampling filters during double-speed playback.)

- Built-in  $\sum \Delta$  D/A converter implemented by a third-order noise shaper circuit (for PWM output)

- Built-in digital attenuator (8 bits alpha, 239 steps)

- Built-in digital de-emphasis circuit that can be controlled externally in some modes

- · Zero-cross muting

- Support for 2×-speed dubbing

- Support for bilingual applications

- General-purpose I/O ports: 4 pins (when the antishock mode is turned off)

### **Features**

- 5 V single-voltage power supply

- Low-voltage operation: Can be operated at 3.3 V  $\pm 10\%$  (at normal playback speed)

- 80-pin QFP package

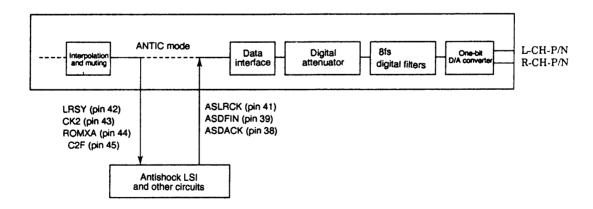

### **Equivalent Circuit Block Diagram**

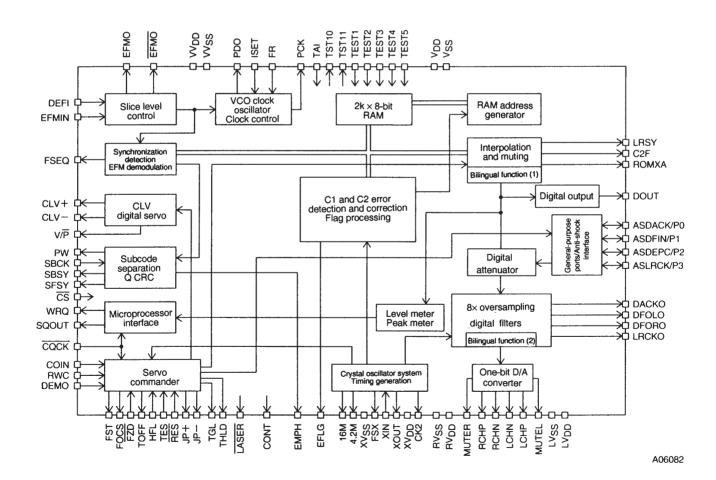

# **Pin Assignment**

# **Specifications**

# Absolute Maximum Ratings at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V

| Parameter                   | Symbol              | Conditions | Ratings                          | Unit |

|-----------------------------|---------------------|------------|----------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max |            | V <sub>SS</sub> – 0.3 to +7.0    | V    |

| Maximum input voltage       | V <sub>IN</sub>     |            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Maximum output voltage      | V <sub>OUT</sub>    |            | $V_{SS} - 0.3$ to $V_{DD} + 0.3$ | V    |

| Allowable power dissipation | Pd max              |            | 300                              | mW   |

| Operating temperature       | Topr                |            | -20 to +75                       | °C   |

| Storage temperature         | Tstg                |            | -40 to +125                      | °C   |

# Allowable Operating Ranges at $Ta = 25^{\circ}C$ , $V_{SS} = 0$ V

| Devembles                    | Cumbal              | Conditions                                                                                                                         |                     | Ratings |                     | V V V |

|------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|---------------------|-------|

| Parameter                    | Symbol Conditions — |                                                                                                                                    | min                 | typ     | max                 | Unit  |

|                              | V <sub>DD</sub> (1) | V <sub>DD</sub> , XV <sub>DD</sub> , LV <sub>DD</sub> , RV <sub>DD</sub> , VV <sub>DD</sub> :<br>At normal playback speed          | 3.0                 |         | 5.5                 | V     |

| Supply voltage               | V <sub>DD</sub> (2) | V <sub>DD</sub> , XV <sub>DD</sub> , LV <sub>DD</sub> , RV <sub>DD</sub> , VV <sub>DD</sub> :<br>At 2× playback speed              | 4.5                 |         | 5.5                 | V     |

| Input high-level voltage     | V <sub>IH</sub> (1) | DEFI, FZD, ASDACK/P0, ASFIN/P1, ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL, TES, SBCK, RWC, CQCK, TAI, TEST1 to TEST5, DEMO, CS          | 0.7 V <sub>DD</sub> |         | $V_{DD}$            | V     |

|                              | V <sub>IH</sub> (2) | EFMIN                                                                                                                              | 0.6 V <sub>DD</sub> |         | $V_{DD}$            | V     |

| Input low-level voltage      | V <sub>IL</sub> (1) | DEFI, FZD, ASDACK/P0, ASFIN/P1,<br>ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL,<br>TES, SBCK, RWC, CQCK, TAI, TEST1 to<br>TEST5, DEMO, CS | 0                   |         | 0.3 V <sub>DD</sub> | V     |

|                              | V <sub>IL</sub> (2) | EFMIN                                                                                                                              | 0                   |         | 0.4 V <sub>DD</sub> | V     |

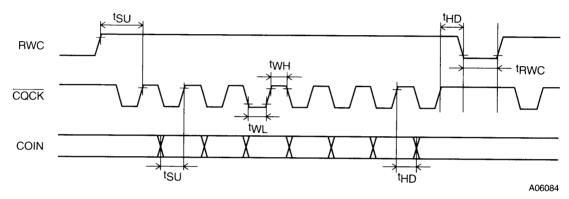

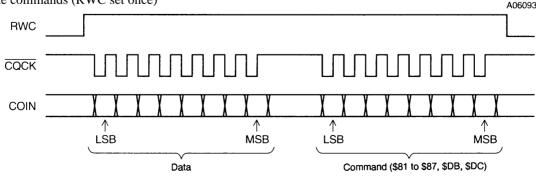

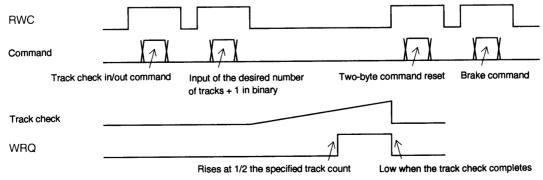

| Data setup time              | t <sub>SU</sub>     | COIN, RWC : Figure 1                                                                                                               | 400                 |         |                     | ns    |

| Data hold time               | t <sub>HD</sub>     | COIN, RWC : Figure 1                                                                                                               | 400                 |         |                     | ns    |

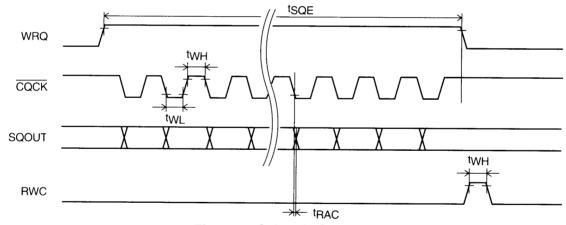

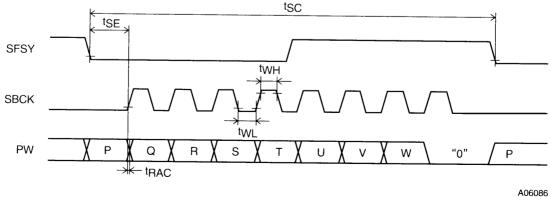

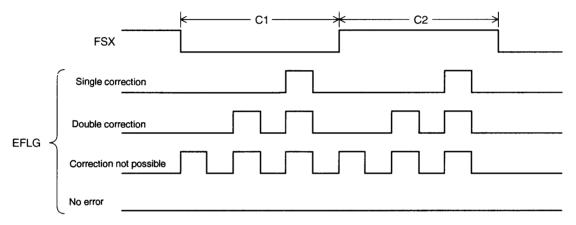

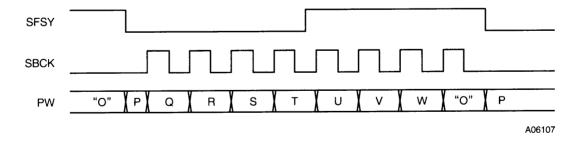

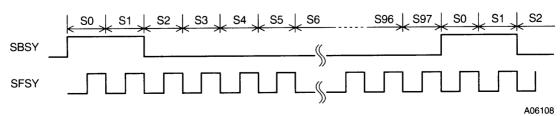

| High-level clock pulse width | t <sub>WH</sub>     | SBCK, CQCK: Figuires 1, 2 and 3                                                                                                    | 400                 |         |                     | ns    |

| Low-level clock pulse width  | t <sub>WL</sub>     | SBCK, CQCK: Figuires 1, 2 and 3                                                                                                    | 400                 |         |                     | ns    |

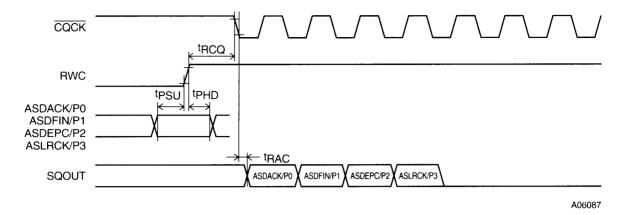

| Data read access time        | t <sub>RAC</sub>    | SQOUT, PW: Figuires 2 and 3                                                                                                        | 0                   | _       | 400                 | ns    |

Continued on next page.

Continued from preceding page.

| Doromotor                    | Cumbal              | Conditions                                                   |         | Ratings |      | Unit |

|------------------------------|---------------------|--------------------------------------------------------------|---------|---------|------|------|

| Parameter                    | Symbol              | Conditions                                                   | min typ |         | max  | Unit |

| Command transfer time        | t <sub>RWC</sub>    | RWC : Figure 1                                               | 1000    |         |      | ns   |

| Subcode Q read enable time   | t <sub>SQE</sub>    | WRQ: Figure 2, with no RWC signal                            |         | 11.2    |      | ms   |

| Subcode read cycle           | t <sub>SC</sub>     | SFSY: Figure 3                                               |         | 136     |      | μs   |

| Subcode read enable time     | t <sub>SE</sub>     | SFSY: Figure 3                                               | 400     |         |      | ns   |

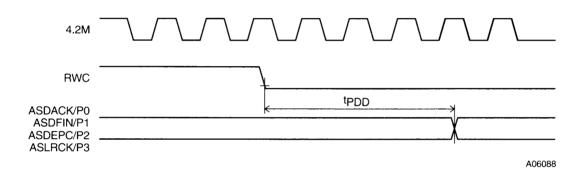

| Port input data setup time   | t <sub>PSU</sub>    | ASDACK/P0, ASFIN/P1, ASDEPC/P2,<br>ASLRCK/P3, RWC : Figure 4 | 400     |         |      | ns   |

| Port input data hold time    | t <sub>PHD</sub>    | ASDACK/P0, ASFIN/P1, ASDEPC/P2,<br>ASLRCK/P3, RWC : Figure 4 | 400     |         |      | ns   |

| Port input clock setup time  |                     | CQCK, RWC : Figure 4                                         | 100     |         |      | ns   |

| Port output data delay time  |                     | ASDACK/P0, ASFIN/P1, ASDEPC/P2,<br>ASLRCK/P3, RWC : Figure 5 |         |         | 1200 | ns   |

|                              | V <sub>IN</sub> (1) | EFMIN                                                        | 1.0     |         |      | Vp-p |

| Input level                  | V <sub>IN</sub> (2) | XIN : Capacitor coupled input                                | 1.0     |         |      | Vp-p |

| Operating frequency range    | f <sub>OP</sub> (1) | EFMIN                                                        |         |         | 10   | MHz  |

| Crystal oscillator frequency | f <sub>X</sub>      | XIN, XOUT : In 16M mode                                      |         | 16.9344 |      | MHz  |

# Electrical Characteristics at $Ta=25^{\circ}C,\,V_{DD}=5~V,\,V_{SS}=0~V$

| Parameter                  | Symbol               | Symbol Conditions                                                                                                                                                                                    |            | Ratings |      |      |  |

|----------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|------|------|--|

| i arameter                 | Gyiriboi             | Conditions                                                                                                                                                                                           | min        | typ     | max  | Unit |  |

| Current drain              | I <sub>DD</sub>      |                                                                                                                                                                                                      |            | 30      | 45   | mA   |  |

| Input high-level current   | I <sub>IH</sub> (1)  | DEFI, EFMIN, FZD, ASDACK/P0, ASFIN/P1, ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL, TES, SBCK, RWC, CQCK: V <sub>IN</sub> = 5 V                                                                             |            |         | 5    | μΑ   |  |

|                            | I <sub>IH</sub> (2)  | TAI, TEST1 to TEST5, DEMO, $\overline{CS}$ :<br>V <sub>IN</sub> = V <sub>DD</sub> = 5.5 V                                                                                                            | 25         |         | 75   | μA   |  |

| Input low-level current    | I <sub>IL</sub>      | DEFI, EFMIN, FZD, ASDACK/P0, ASFIN/P1, ASDEPC/P2, ASLRCK/P3, COIN, RES, HFL, TES, SBCK, RWC, CQCK, TAI, TEST1 to TEST5, DEMO, CS: V <sub>IN</sub> = 0 V                                              | <b>-</b> 5 |         |      | μA   |  |

|                            | V <sub>OH</sub> (1)  | EFMO, EFMO, CLV <sup>+</sup> , CLV <sup>-</sup> , V/P̄, FOCS,<br>PCK, FSEQ, TOFF, TGL, THLD, JP <sup>+</sup> , JP <sup>-</sup> ,<br>EMPH, EFLG, FSX: I <sub>OH</sub> = -1 mA                         | 4          |         |      | V    |  |

| Output high-level voltage  | V <sub>OH</sub> (2)  | MUTEL, MUTER, LRCKO, DFORO, DFOLO, DACKO, TST10, ASDACK/P0, ASFIN/P1, ASDEPC/P2, ASLRCK/P3, LRSY, CK2, ROMXA, C2F, SBSY, PW, SFSY, WRQ, SQOUT, TST11, 16M, 4.2M, CONT:                               | 4          |         |      | V    |  |

|                            | V <sub>OH</sub> (3)  | TASER: I <sub>OH</sub> = -1 mA                                                                                                                                                                       | 4.6        |         |      | V    |  |

|                            | V <sub>OH</sub> (4)  | DOUT : I <sub>OH</sub> = -12 mA                                                                                                                                                                      | 4.5        |         |      | V    |  |

|                            | V <sub>OH</sub> (5)  | LCHP, RCHP, LCHN, RCHN : I <sub>OH</sub> = -1 mA                                                                                                                                                     | 3.0        |         | 4.5  | V    |  |

|                            | V <sub>OL</sub> (1)  | EFMO, EFMO, CLV <sup>+</sup> , CLV <sup>-</sup> , V/P̄, FOCS,<br>PCK, FSEQ, TOFF, TGL, THLD, JP <sup>+</sup> , JP <sup>-</sup> ,<br>EMPH, EFLG, FSX : I <sub>OL</sub> = 1 mA                         |            |         | 1    | V    |  |

| Output low-level voltage   | V <sub>OL</sub> (2)  | MUTEL, MUTER, LRCKO, DFORO, DFOLO, DACKO, TST10, ASDACK/P0, ASFIN/P1, ASDEPC/P2, ASLRCK/P3, LRSY, CK2, ROMXA, C2F, SBSY, PW, SFSY, WRQ, SQOUT, TST11, 16M, 4.2M, CONT, LASER: I <sub>OL</sub> = 2 mA |            |         | 0.4  | ٧    |  |

|                            | V <sub>OL</sub> (3)  | DOUT : I <sub>OL</sub> = 12 mA                                                                                                                                                                       |            |         | 0.5  | V    |  |

|                            | V <sub>OL</sub> (4)  | FST : I <sub>OL</sub> = 5 mA                                                                                                                                                                         |            |         | 0.75 | V    |  |

|                            | V <sub>OL</sub> (5)  | LCHP, RCHP, LCHN, RCHN : I <sub>OL</sub> = 1 mA                                                                                                                                                      | 0.5        |         | 2.0  | V    |  |

| Output off leakage current | I <sub>OFF</sub> (1) | PDO, CLV <sup>+</sup> , CLV <sup>-</sup> , JP <sup>+</sup> , JP <sup>-</sup> , FST : V <sub>OUT</sub> = 5 V                                                                                          |            |         | 5    | μA   |  |

| Output on leakage current  | I <sub>OFF</sub> (2) | PDO, CLV <sup>+</sup> , CLV <sup>-</sup> , JP <sup>+</sup> , JP <sup>-</sup> : V <sub>OUT</sub> = 0 V                                                                                                | <b>–</b> 5 |         |      | μA   |  |

|                            | I <sub>PDOH</sub>    | PDO : RISET = 68 kΩ                                                                                                                                                                                  | 100        | 125     | 150  | μΑ   |  |

| Charge pump output current | I <sub>PDOL</sub>    | PDO : RISET = 68 kΩ                                                                                                                                                                                  | -150       | -125    | -100 | μA   |  |

Note: For guaranteed operation, the VCO oscillator frequency range adjustment resistor FR must be a 1.20 k $\Omega$  ±5.0% tolerance resistor.

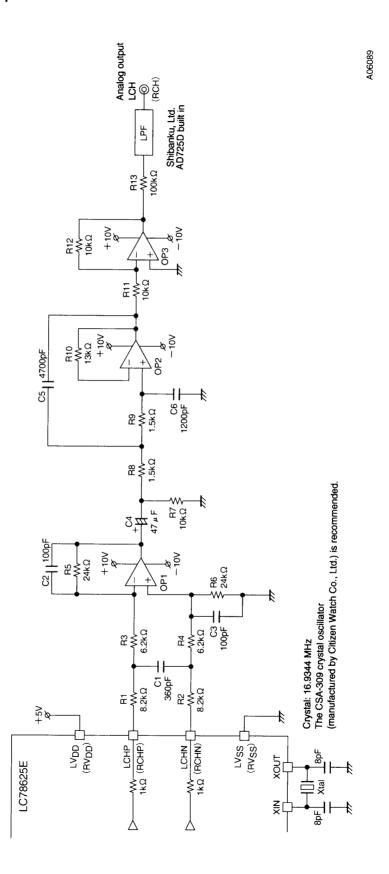

One-Bit D/A Converter Analog Characteristics at Ta = 25  $^{\circ}$ C,  $V_{DD}$  =  $LV_{DD}$  =  $RV_{DD}$  = 5 V,  $V_{SS}$  =  $LV_{SS}$  =  $RV_{SS}$  = 0 V

| Parameter                 | Symbol  | Conditions                                                                                                                  |     | Ratings |        | - Unit |  |

|---------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------|-----|---------|--------|--------|--|

| Farameter                 | Symbol  | Conditions                                                                                                                  | min | typ     | max    |        |  |

| Total harmonic distortion | THD + N | LCHP, RCHP, LCHN, RCHN;<br>1 kHz: 0 dB data input, using the 20 kHz<br>low-pass filter (AD725D built in)                    |     | 0.008   | 0.0010 | %      |  |

| Dynamic range             | DR      | LCHP, RCHP, LCHN, RCHN;<br>1 kHz: –60 dB data input, using the 20 kHz<br>low-pass filter and the A filter (AD725D built in) | 84  | 88      |        | dB     |  |

| Signal-to-noise ratio     | S/N     | LCHP, RCHP, LCHN, RCHN;<br>1 kHz: 0 dB data input, using the 20 kHz<br>low-pass filter and the A filter (AD725D built in)   | 98  | 100     |        | dB     |  |

| Crosstalk                 | СТ      | LCHP, RCHP, LCHN, RCHN;<br>1 kHz: 0 dB data input, using the 20 kHz<br>low-pass filter (AD725D built in)                    | 96  | 98      |        | dB     |  |

Note: Measured with the normal-speed playback mode digital attenuator in the Sanyo one-bit D/A converter block reference circuit.

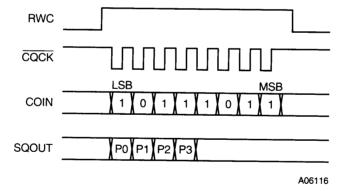

Figure 1 Command Input

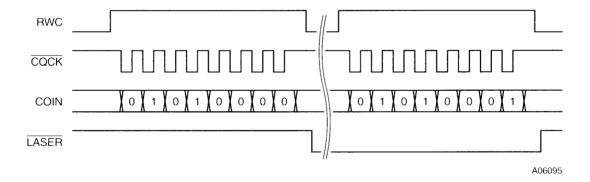

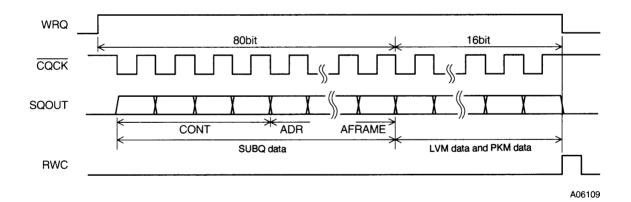

Figure 2 Subcode Q Output

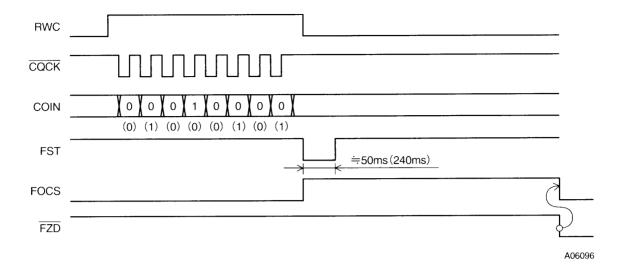

Figure 3 Subcode Output

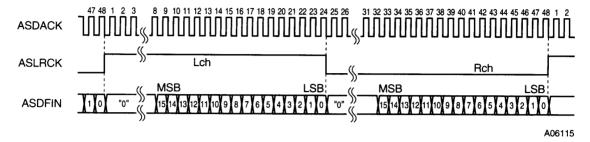

Figure 4 General-Purpose Port Input Timing

Figure 5 General-Purpose Port Output Timing

# One-Bit D/A Converter Output Block Reference Circuit

# **Pin Functions**

| Pin No. | Symbol           | I/O |                                                   | Function                                                                                                                                               |  |  |  |  |

|---------|------------------|-----|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | DEFI             | ı   | Defect detection signal (D                        | EF) input (This pin must be connected to 0 V if unused.)                                                                                               |  |  |  |  |

| 2       | TAI              | Ι   |                                                   | Test input. A pull-down resistor is built in. (This pin must be connected to 0 V in normal operation.)                                                 |  |  |  |  |

| 3       | PDO              | 0   |                                                   | External VCO control phase comparator output                                                                                                           |  |  |  |  |

| 4       | VV <sub>SS</sub> |     |                                                   | Internal VCO ground. (This pin must be connected to 0 V.)                                                                                              |  |  |  |  |

| 5       | ISET             | AI  | PLL pins                                          | PDO output current adjustment resistor connection                                                                                                      |  |  |  |  |

| 6       | VV <sub>DD</sub> |     |                                                   | Internal VCO power supply.                                                                                                                             |  |  |  |  |

| 7       | FR               | AI  |                                                   | VCO frequency range adjustment                                                                                                                         |  |  |  |  |

| 8       | V <sub>SS</sub>  |     | Digital system ground. (Th                        | is pin must be connected to 0 V.)                                                                                                                      |  |  |  |  |

| 9       | EFMO             | 0   |                                                   | EFM signal inverted output                                                                                                                             |  |  |  |  |

| 10      | EFMO             | 0   | Slice level control                               | EFM signal output                                                                                                                                      |  |  |  |  |

| 11      | EFMIN            | ı   |                                                   | EFM signal input                                                                                                                                       |  |  |  |  |

| 12      | TEST2            | ı   | Test input. A pull-down res                       | sistor is built in. This pin must be connected to 0 V in normal operation.                                                                             |  |  |  |  |

| 13      | CLV+             | 0   | · · ·                                             | ut. Acceleration when CLV+ is high, deceleration when CLV- is high.                                                                                    |  |  |  |  |

| 14      | CLV-             | 0   | •                                                 | possible when specified by microprocessor command.                                                                                                     |  |  |  |  |

|         |                  |     | <u> </u>                                          | al automatic switching monitor output. Outputs a high level during rough servo and a low level during                                                  |  |  |  |  |

| 15      | V/P              | 0   | phase control.                                    |                                                                                                                                                        |  |  |  |  |

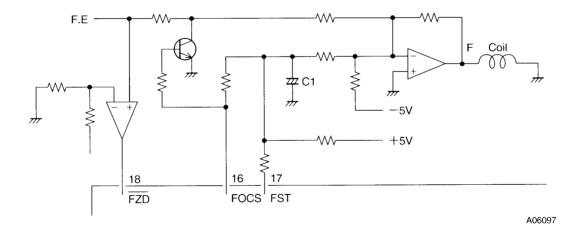

| 16      | FOCS             | 0   | Focus servo on/off output.                        | cus servo on/off output. Focus servo is on when the output is low.                                                                                     |  |  |  |  |

| 17      | FST              | 0   | Focus start pulse output. 1                       | his is an open-drain output.                                                                                                                           |  |  |  |  |

| 18      | FZD              | Ι   | Focus error zero cross sig                        | nal input. (This pin must be connected to 0 V if unused.)                                                                                              |  |  |  |  |

| 19      | HFL              | ı   | Track detection signal inpu                       | ut. This is a Schmitt input.                                                                                                                           |  |  |  |  |

| 20      | TES              | Ι   | Tracking error signal input                       | . This is a Schmitt input.                                                                                                                             |  |  |  |  |

| 21      | PCK              | 0   | EFM data playback clock i                         | monitor. Outputs 4.3218 MHz when the phase is locked.                                                                                                  |  |  |  |  |

| 22      | FSEQ             | 0   | -                                                 | ection output. Outputs a high level when the synchronization signal detected from the EFM signal and inchronization signal agree.                      |  |  |  |  |

| 23      | TOFF             | 0   | Tracking off output                               |                                                                                                                                                        |  |  |  |  |

| 24      | TGL              | 0   |                                                   | utput. Increase the gain when low.                                                                                                                     |  |  |  |  |

| 25      | THLD             | 0   | Tracking hold output                              | apan marada na gam mariam                                                                                                                              |  |  |  |  |

| 26      | TEST3            | Ī   |                                                   | sistor is built in. (This pin must be connected to 0 V.)                                                                                               |  |  |  |  |

| 27      | V <sub>DD</sub>  |     | Digital system power supp                         |                                                                                                                                                        |  |  |  |  |

| 28      | JP+              | 0   | Track jump output. A high                         | level output from JP+ indicates acceleration during an outward jump or deceleration during an inward                                                   |  |  |  |  |

|         | 01               |     | jump.                                             |                                                                                                                                                        |  |  |  |  |

| 29      | JP <sup>-</sup>  | 0   | •                                                 | P- indicates acceleration during an inward jump or deceleration during an outward jump.<br>possible when specified by microprocessor command.          |  |  |  |  |

| 30      | DEMO             | I   | Sound output function input be connected to 0 V.) | sound output function input used for end product adjustment manufacturing steps. A pull-down resistor is built in. (This pin must e connected to 0 V.) |  |  |  |  |

| 31      | TEST4            | ı   | Test input. A pull-down res                       | sistor is built in. (This pin must be connected to 0 V.)                                                                                               |  |  |  |  |

| 32      | EMPH             | 0   | De-emphasis monitor pin.                          | A high level indicates playback of a de-emphasis disk.                                                                                                 |  |  |  |  |

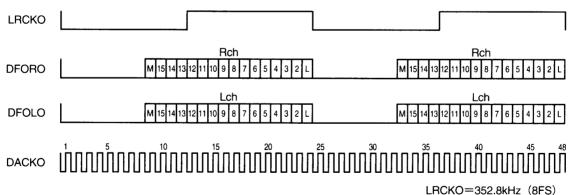

| 33      | LRCKO            | 0   |                                                   | Word clock output                                                                                                                                      |  |  |  |  |

| 34      | DFORO            | 0   |                                                   | Right channel data output                                                                                                                              |  |  |  |  |

| 35      | DFOLO            | 0   | Digital filter outputs                            | Left channel data output                                                                                                                               |  |  |  |  |

| 36      | DACKO            | 0   |                                                   | Bit clock output                                                                                                                                       |  |  |  |  |

| 37      | TST10            | 0   | Test output. Leave open. (                        | Normally outputs a low level.)                                                                                                                         |  |  |  |  |

Continued on next page.

Continued from preceding page.

| Pin No. | Symbol           | I/O |                                                                                                                  | Function                                                                                          |                                                                      |  |  |  |

|---------|------------------|-----|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| 38      | ASDACK/P0        | I/O | When antishock mode is not used,                                                                                 |                                                                                                   | Bit clock input                                                      |  |  |  |

| 39      | ASDFIN/P1        | I/O | these pins are used as general-                                                                                  |                                                                                                   | Left and right channel data input                                    |  |  |  |

| 40      | ASDEPC/P2        | I/O | purpose I/O ports (P0 to P3). They<br>must either be set to input mode and<br>connected to 0 V, or set to output | The antishock inputs in antishock mode.                                                           | Sets the built-in de-emphasis filter on or off. (High: on, low: off) |  |  |  |

| 41      | ASLRCK/P3        | I/O | - · · · · · · · · · · · · · · · · · · ·                                                                          |                                                                                                   | L/R clock input                                                      |  |  |  |

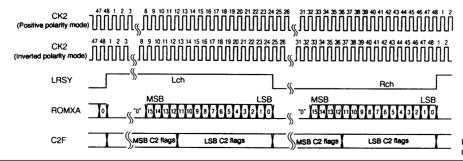

| 42      | LRSY             | 0   |                                                                                                                  | L/R clock output                                                                                  |                                                                      |  |  |  |

| 43      | CK2              | 0   | DOMANA liatitti                                                                                                  | Bit clock output (after reset)                                                                    | Inverted polarity clock output (during CK2CON mode)                  |  |  |  |

| 44      | ROMXA            | 0   | ROMXA application output signals                                                                                 | Interpolation data output (after reset)                                                           | ROM data output (during ROMXA mode)                                  |  |  |  |

| 45      | C2F              | 0   |                                                                                                                  | C2 flag output                                                                                    |                                                                      |  |  |  |

| 46      | MUTEL            | 0   |                                                                                                                  | Left channel mute output                                                                          |                                                                      |  |  |  |

| 47      | $LV_DD$          |     |                                                                                                                  | Left channel power supply                                                                         |                                                                      |  |  |  |

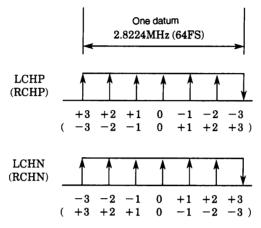

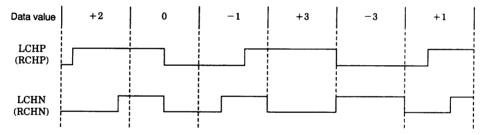

| 48      | LCHP             | 0   |                                                                                                                  | Left channel P output                                                                             |                                                                      |  |  |  |

| 49      | LCHN             | 0   |                                                                                                                  | Left channel N output                                                                             |                                                                      |  |  |  |

| 50      | LV <sub>SS</sub> |     | 0 1:: 5/4                                                                                                        | Left channel ground. Must b                                                                       | e connected to 0 V.                                                  |  |  |  |

| 51      | RV <sub>SS</sub> |     | One-bit D/A converter signals                                                                                    | Right channel ground. Must                                                                        | be connected to 0 V.                                                 |  |  |  |

| 52      | RCHN             | 0   |                                                                                                                  | Right channel N output                                                                            |                                                                      |  |  |  |

| 53      | RCHP             | 0   |                                                                                                                  | Right channel P output                                                                            |                                                                      |  |  |  |

| 54      | RV <sub>DD</sub> |     |                                                                                                                  | Right channel power supply                                                                        |                                                                      |  |  |  |

| 55      | MUTER            | 0   |                                                                                                                  | Right channel mute output                                                                         |                                                                      |  |  |  |

| 56      | DOUT             | 0   | Digital output                                                                                                   | 1                                                                                                 |                                                                      |  |  |  |

| 57      | SBSY             | 0   | Subcode block synchronization signal ou                                                                          | ıtput                                                                                             |                                                                      |  |  |  |

| 58      | EFLG             | 0   | C1, C2, single and double error correction                                                                       | on monitor pin                                                                                    |                                                                      |  |  |  |

| 59      | PW               | 0   | Subcode P, Q, R, S, T, U and W output                                                                            |                                                                                                   |                                                                      |  |  |  |

| 60      | SFSY             | 0   | Subcode frame synchronization signal or                                                                          | utput. This signal falls when th                                                                  | e subcodes are in the standby state.                                 |  |  |  |

| 61      | SBCK             | Т   | Subcode readout clock input. This is a S                                                                         | chmitt input. (This pin must be                                                                   | e connected to 0 V if unused.)                                       |  |  |  |

| 62      | FSX              | 0   | Output for the 7.35 kHz synchronization                                                                          | signal divided from the crystal                                                                   | oscillator                                                           |  |  |  |

| 63      | WRQ              | 0   | Subcode Q output standby output                                                                                  |                                                                                                   |                                                                      |  |  |  |

| 64      | RWC              | Т   | Read/write control input. This is a Schmi                                                                        | tt input.                                                                                         |                                                                      |  |  |  |

| 65      | SQOUT            | 0   | Subcode Q output                                                                                                 |                                                                                                   |                                                                      |  |  |  |

| 66      | COIN             | ı   | Command input from the control micropr                                                                           | ocessor                                                                                           |                                                                      |  |  |  |

| 67      | CQCK             | Ι   | Input for the command input acquisition                                                                          | clock or the SQOUT pin subco                                                                      | ode readout clock input. This is a Schmitt input.                    |  |  |  |

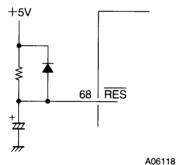

| 68      | RES              | Ι   | Reset input. This pin must be set low brid                                                                       | efly after power is first applied                                                                 |                                                                      |  |  |  |

| 69      | TST11            | 0   | Test output. Leave open. (Normally outp                                                                          | uts a low level.)                                                                                 |                                                                      |  |  |  |

| 70      | LASER            | 0   | Laser on/off output. Controlled by serial                                                                        | data commands from the cont                                                                       | rol microprocessor.                                                  |  |  |  |

| 71      | 16M              | 0   | 16.9344 MHz output                                                                                               |                                                                                                   |                                                                      |  |  |  |

| 72      | 4.2M             | 0   | 4.2336 MHz output                                                                                                |                                                                                                   |                                                                      |  |  |  |

| 73      | CONT             | 0   | Supplementary control output. Controlled                                                                         | d by serial data commands fro                                                                     | m the control microprocessor.                                        |  |  |  |

| 74      | TEST5            | ı   | Test input. A pull-down resistor is built in                                                                     | . (This pin must be connected                                                                     | to 0 V.)                                                             |  |  |  |

| 75      | CS               | Ī   | Chip select input. A pull-down resistor is                                                                       | Chip select input. A pull-down resistor is built in. This pin must be connected to 0 V if unused. |                                                                      |  |  |  |

| 76      | XV <sub>SS</sub> |     | Crystal oscillator ground. Must be conne                                                                         | cted to 0 V.                                                                                      |                                                                      |  |  |  |

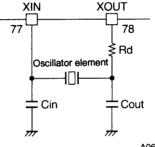

| 77      | XIN              | Ι   | 0                                                                                                                |                                                                                                   |                                                                      |  |  |  |

| 78      | XOUT             | 0   | Connections for a 16.9344 MHz crystal of                                                                         | oscillator                                                                                        |                                                                      |  |  |  |

| 79      | XV <sub>DD</sub> |     | Crystal oscillator power supply                                                                                  |                                                                                                   |                                                                      |  |  |  |

| 80      | TEST1            | Ι   | Test input. A pull-down resistor is built in                                                                     | . (This pin must be connected                                                                     | to 0 V.)                                                             |  |  |  |

Note: All power-supply pins ( $V_{DD}$ ,  $VV_{DD}$ ,  $LV_{DD}$ ,  $RV_{DD}$ , and  $XV_{DD}$ ) must be connected to the same potential.

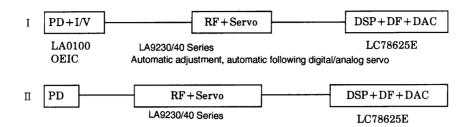

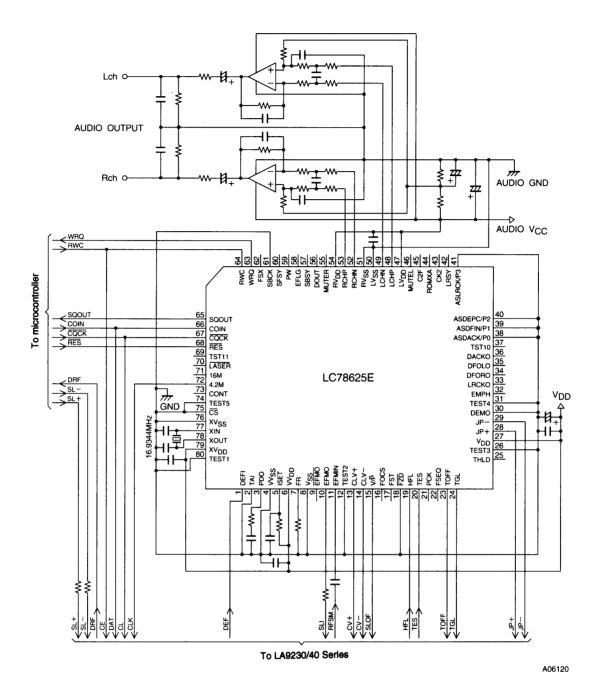

### **CD System Block Diagrams**

### **Pin Applications**

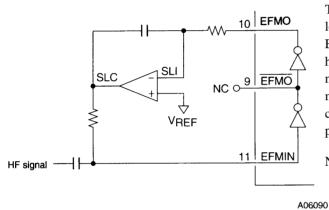

1. HF signal input circuit; Pin 11: EFMIN, pin 10: EFMO, pin 9: EFMO, pin 1: DEFI, pin 13: CLV+

An EFM signal (NRZ) sliced at an optimal level can be acquired by inputting the HF signal to EFMIN.

The LC78625E handles defects as follows. When a high level is input to the DEFI pin (pin 1), the  $\overline{\text{EFMO}}$  (pin 9) and EFMO (pin 10) pins (the slice level control outputs) go to the high-impedance state, and the slice level is held. However, note that this function is only valid in CLV phase control mode, that is, when the  $V/\overline{P}$  pin (pin 15) is low. This function can be used in combination with the LA9230/40 series DEF pin.

Note: If the EFMIN and CLV+ signal lines are too close to each other, unwanted adiation can result in error rate degradation. We recommend laying a ground or V<sub>DD</sub> shield line between these two lines.

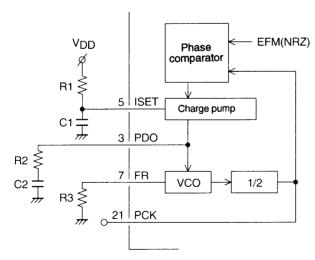

2. PLL clock generation circuit; Pin 3: PDO, pin 5: ISET, pin 7: FR, pin 21: PCK

Since the LC78625E includes a VCO circuit, a PLL circuit can be formed by connecting an external RC circuit. ISET is the charge pump reference current, PDO is the VCO circuit loop filter, and FR is a resistor that determines the VCO frequency range.

(Reference values)

$R1 = 68 \text{ k}\Omega, C1 = 0.1 \mu\text{F}$

$R2 = 680 \text{ k}\Omega$ ,  $C2 = 0.1 \mu\text{F}$

$R3 = 1.2 \text{ k}\Omega$

Note: We recommend using a  $\pm 5.0\%$  tolerance carbon film resistor for R3.

A06091

- 3. VCO monitor; Pin 21: PCK

- PCK is a monitor pin that outputs an average frequency of 4.3218 MHz, which is the VCO frequency divided by two.

- 4. Synchronization detection monitor; Pin 22: FSEQ

Pin 22 goes high when the frame synchronization (a positive polarity synchronization signal) from the EFM signal read in by PCK and the timing generated by the counter (the interpolation synchronization signal) agree. This pin is thus a synchronization detection monitor. (It is held high for a single frame.)

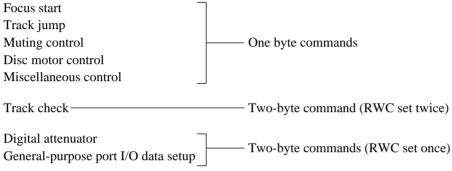

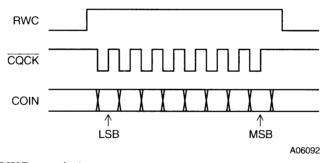

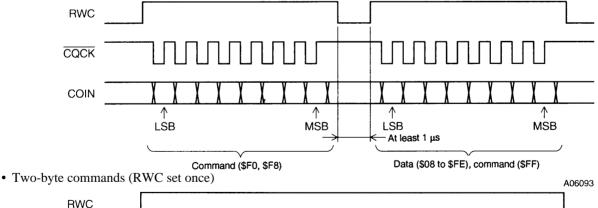

5. Servo command function; Pin 64: RWC, pin 66: COIN, pin 67: CQCK

Commands can be executed by setting RWC high and inputting commands to the COIN pin in synchronization with the  $\overline{CQCK}$  clock. Note that commands are executed on the falling edge of RWC.

· One-byte commands

• Two-byte commands (RWC set twice)

A06094

### · Command noise rejection

| Code | COMMAND                            | RES = L |

|------|------------------------------------|---------|

| \$EF | Command input noise reduction mode |         |

| \$EE | Reset the above mode.              | 0       |

This command reduces the noise on the CQCK clock signal. While this is effective for noise pulses shorter than 500 ns, the  $\overline{\text{CQCK}}$  timings  $t_{\text{WL}}$ ,  $t_{\text{WH}}$ , and  $t_{\text{SU}}$  (see page 5, figures 1 and 2), must be set to be at least 1  $\mu$ s.

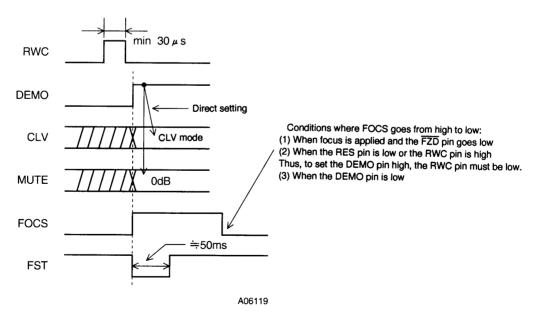

### 6. Focus servo circuit; Pin 16: FOCS, pin 17: FST, pin 18: FZD, pin 70: LASER

| Code | COMMAND        | RES = L |

|------|----------------|---------|

| \$08 | FOCUS START #1 |         |

| \$A2 | FOCUS START #2 |         |

| \$0A | LASER ON       |         |

| \$8A | LASER OFF      | 0       |

| \$FE | NOTHING        |         |

The FOCS, FST, and FZD pins are not required when the LC78625E is used in combination with an LA9230/40 Series LSI. FZD should be connected to 0 V when these pins are not used. The LA9230/40 Series focus start command is identical to the LC78625E FOCUS START #1 command.

#### NOTHING

This command can be used to initialize the LC78625E by inputting FE (hexadecimal: Hexadecimal constants are written with a dollar sign (\$) prefix). Note that \$00 is the reset command for the LA9230/40 Series, and should be used with care since it clears the result of the automatic adjustment process and returns these chips to their initial states.

### · Laser control

The LASER pin can be use as an extended output port.

### · Focus start

When the LC78625E is used in combination with an LA9230/40 Series LSI, the focus start operation is executed completely on the servo side by commands from the control microprocessor. The following section describes this operation when the LC78625E is used in combination with an LA9210M or LA9211M.

When a focus start instruction (either FOCUS START #1 or FOCUS START #2) is input as a servo command, first the charge on capacitor C1 is discharged by FST and the objective lens is lowered. Next, the capacitor is charged by FOCS, and the lens is slowly raised. FZD falls when the lens reaches the focus point. When this signal is received, FOCS is reset and the focus servo turns on. After sending the command, the microprocessor should check the in-focus detection signal (the LA9210 DRF signal) to confirm focus before proceeding to the next part of the program. If focus is not achieved by the time C1 is fully charged, the microprocessor should issue another focus command and iterate the focus servo operation.

Note:\*Values in parentheses are for the FOCUS START #2 command. The only difference is in the FST low period.

- \*An  $\overline{\text{FZD}}$  falling edge will not be accepted during the period that FST is low.

- \*After issuing a focus start command, initialization will be performed if RWC is set high. Therefore, do not issue the next command during focus start until the focus coil drive S curve has completed.

- \*When focus cannot be achieved (i.e., when FZD does not go low) the FOCS signal will remain in the high state and the lens will remain raised, so the microprocessor should initialize the system by issuing a NOTHING command.

- \*When the  $\overline{\text{RES}}$  pin is set low, the  $\overline{\text{LASER}}$  pin is set high directly.

- \*Focus start using the DEMO pin executes a mode #1 focus start.

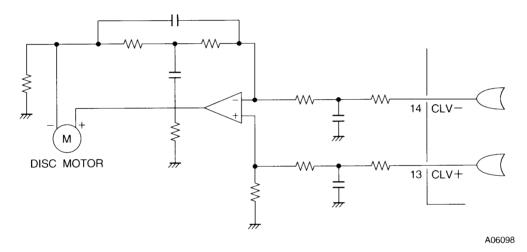

# 7. CLV servo circuit; Pin 13: CLV<sup>+</sup>, pin 14: CLV<sup>-</sup>, pin 15: V/P

| Code | COMMAND                       | RES = L |

|------|-------------------------------|---------|

| \$04 | DISC MOTOR START (accelerate) |         |

| \$05 | DISC MOTOR CLV (CLV)          |         |

| \$06 | DISC MOTOR BRAKE (decelerate) |         |

| \$07 | DISC MOTOR STOP (stop)        | 0       |

The  $CLV^+$  pin provides the signal that accelerates the disk in the forward direction and the  $CLV^-$  pin provides the signal that decelerates the disk. Commands from the control microprocessor select one of the four modes accelerate, decelerate, CLV and stop. The table below lists the  $CLV^+$  and  $CLV^-$  outputs in each of these modes.

| Mode       | CLV+         | CLV-         |

|------------|--------------|--------------|

| Accelerate | Н            | L            |

| Decelerate | L            | Н            |

| CLV        | Pulse output | Pulse output |

| Stop       | L            | L            |

Note: \* CLV servo control commands can set the TOFF pin low only in CLV mode. That pin will be at the high level at all other times. Control of the TOFF pin by microprocessor command is only valid in CLV mode.

• CLV mode the LC78625E detects the disk speed from the HE signal and provides proper linear speed using several

In CLV mode the LC78625E detects the disk speed from the HF signal and provides proper linear speed using several different control schemes by switching the DSP internal modes. The PWM period corresponds to a frequency of 7.35 kHz. The  $V/\overline{P}$  pin outputs a high level during rough servo and a low level during phase control.

| Internal Mode                                   | CLV+ | CLV- | V/P |

|-------------------------------------------------|------|------|-----|

| Rough servo (When determined to be under speed) | Н    | L    | Н   |

| Rough servo (When determined to be over speed)  | L    | Н    | Н   |

| Phase control (PCK locked)                      | PWM  | PWM  | L   |

### · Rough servo gain switching

| Code | COMMAND     | RES = L |

|------|-------------|---------|

| \$A8 | DISC 8 Set  |         |

| \$A9 | DISC 12 Set | 0       |

For 8 cm discs, the rough servo mode CLV control gain can be set about 8.5 dB lower than the gain used for 12 cm discs.

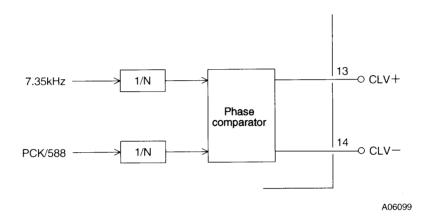

### · Phase control gain switching

| Code | COMMAND                              | RES = L |

|------|--------------------------------------|---------|

| \$B1 | CLV phase comparator divisor: 1/2    |         |

| \$B2 | CLV phase comparator divisor: 1/4    |         |

| \$B3 | CLV phase comparator divisor: 1/8    |         |

| \$B0 | No CLV phase comparator divisor used | 0       |

The phase control gain can be changed by changing the divisor used by the dividers in the stage immediately preceding the phase comparator.

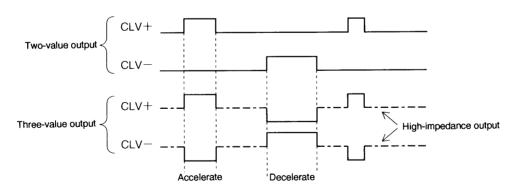

### • CLV three-value output

| Code | COMMAND                                                     | RES = L |

|------|-------------------------------------------------------------|---------|

| \$B4 | CLV three-value output                                      |         |

| \$B5 | CLV two-value output (the scheme used by previous products) | 0       |

The CLV three-value output command allows the CLV to be controlled by a single pin. However, the spindle gain is 6 dB lower when this pin is used, so applications must increase the gain in the servo system.

A06100

### · Internal brake modes

| Code | COMMAND                          | RES = L |

|------|----------------------------------|---------|

| \$C5 | Internal brake on                |         |

| \$C4 | Internal brake off               | 0       |

| \$A3 | Internal brake CONT              |         |

| \$CB | Internal brake continuous mode   |         |

| \$CA | Reset continuous mode            | 0       |

| \$CD | TON mode during internal braking |         |

| \$CC | Reset TON mode                   | 0       |

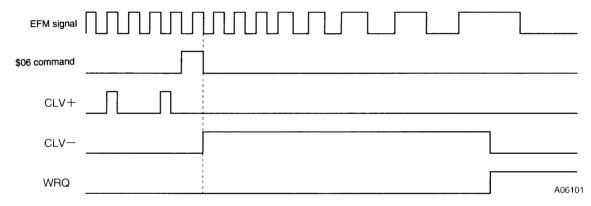

- Issuing the internal brake on command (\$C5) sets the LC78625E to internal brake mode. In this mode, the disc deceleration state can be monitored from the WRQ pin when a brake command (\$06) is executed.

- In this mode the disc deceleration state is determined by counting the EFM signal density in a single frame, and when the EFM signal count falls under four, the CLV<sup>-</sup> pin is dropped to low. At the same time the WRQ signal, which functions as a brake completion monitor, goes high. When the microprocessor detects a high level on the WRQ signal, it should issue a STOP command to fully stop the disc. In internal brake continuous mode, the CLV<sup>-</sup> pin high-level output braking operation continues even after the WRQ brake completion monitor goes high.

- Note that if errors occur in deceleration state determination due to noise in the EFM signal, the problem can be rectified by changing the EFM signal count from four to eight with the internal brake control command (\$A3).

- In internal braking TON mode, the TOFF pin is held low during internal brake operations. We recommend using this feature, since it is effective at preventing incorrect detection at the disc mirror surface.

Note: If focus is lost during the execution of an internal brake command, the pickup must first be refocussed and then the internal brake command must be reissued

Since incorrect deceleration state determination is possible depending on the EFM signal playback state (e.g., disc defects, access in progress), we recommend using these functions in combination with a microprocessor.

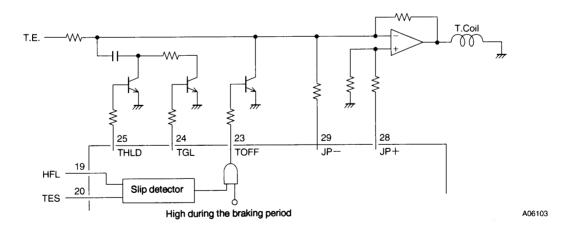

- 8. Track jump circuit; Pin 19: HFL, pin 20: TES, pin 23: TOFF, pin 24: TGL, pin 25: THLD, pin 28: JP<sup>+</sup>, pin 29: JP<sup>-</sup>

- The LC78625E supports the two track count modes listed below.

| Code | COMMAND                                                    | RES = L |

|------|------------------------------------------------------------|---------|

| \$22 | New track count mode (using the TES/HFL combination)       | 0       |

| \$23 | Previous track count mode (directly counts the TES signal) |         |

The earlier track count function uses the TES signal directly as the internal track counter clock.

To reduce counting errors resulting from noise on the rising and falling edges of the TES signal, the new track count function prevents noise induced errors by using the combination of the TES and HFL signals, and implements a more reliable track count function. However, dirt and scratches on the disc can result in HFL signal dropouts that may result in missing track count pulses. Thus care is required when using this function.

### · TJ commands

| Code | COMMAND                            | RES = L |

|------|------------------------------------|---------|

| \$A0 | Previous track jump                | 0       |

| \$A1 | New track jump                     |         |

| \$11 | 1 TRACK JUMP IN #1                 |         |

| \$12 | 1 TRACK JUMP IN #2                 |         |

| \$31 | 1 TRACK JUMP IN #3                 |         |

| \$52 | 1 TRACK JUMP IN #4                 |         |

| \$10 | 2 TRACK JUMP IN                    |         |

| \$13 | 4 TRACK JUMP IN                    |         |

| \$14 | 16 TRACK JUMP IN                   |         |

| \$30 | 32 TRACK JUMP IN                   |         |

| \$15 | 64 TRACK JUMP IN                   |         |

| \$17 | 128 TRACK JUMP IN                  |         |

| \$19 | 1 TRACK JUMP OUT #1                |         |

| \$1A | 1 TRACK JUMP OUT #2                |         |

| \$39 | 1 TRACK JUMP OUT #3                |         |

| \$5A | 1 TRACK JUMP OUT #4                |         |

| \$18 | 2 TRACK JUMP OUT                   |         |

| \$1B | 4 TRACK JUMP OUT                   |         |

| \$1C | 16 TRACK JUMP OUT                  |         |

| \$38 | 32 TRACK JUMP OUT                  |         |

| \$1D | 64 TRACK JUMP OUT                  |         |

| \$1F | 128 TRACK JUMP OUT                 |         |

| \$16 | 256 TRACK CHECK                    |         |

| \$0F | TOFF                               |         |

| \$8F | TON                                | 0       |

| \$8C | TRACK JUMP BRAKE                   |         |

| \$21 | THLD period TOFF output mode       |         |

| \$20 | Reset THLD period TOFF output mode | 0       |

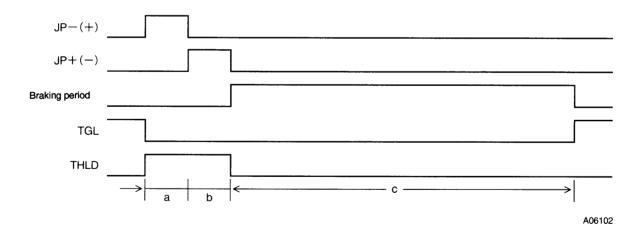

When the LC78625E receives a track jump instruction as a servo command, it first generates accelerating pulses (period a) and next generates deceleration pulses (period b). The passage of the braking period (period c) completes the specified jump. During the braking period, the LC78625E detects the beam slip direction from the TES and HFL inputs. TOFF is used to cut the components in the TE signal that aggravate slip. The jump destination track is captured by increasing the servo gain with TGL. In THLD period TOFF output mode the TOFF signal is held high during the period when THLD is high.

Note: Of the modes related to disc motor control, the TOFF pin only goes low in CLV mode, and will be high during start, stop, and brake operations. Note that the TOFF pin can be turned on and off independently by microprocessor issued commands. However, this function is only valid when disc motor control is in CLV mode.

## · Track jump modes

The table lists the relationships between acceleration pulses, deceleration pulses, and the braking period.

|                          | Pre                      | Previous Track Jump Mode                              |                                         | New Track Jump Mode                                                                                                                |                          |                                         |

|--------------------------|--------------------------|-------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------|

| Item                     | а                        | b                                                     | С                                       | а                                                                                                                                  | b                        | С                                       |

| 1 TRACK JUMP IN (OUT) #1 | 233 µs                   | 233 µs                                                | 60 ms                                   | 233 µs                                                                                                                             | 233 µs                   | 60 ms                                   |

| 1 TRACK JUMP IN (OUT) #2 | 0.5 track jump<br>period | 233 µs                                                | 60 ms                                   | 0.5 track jump<br>period                                                                                                           | 0.5 track jump<br>period | 60 ms                                   |

| 1 TRACK JUMP IN (OUT) #3 | 0.5 track jump<br>period | 233 µs                                                | This period does not exist.             | 0.5 track jump<br>period                                                                                                           | 0.5 track jump<br>period | This period does not exist.             |

| 1 TRACK JUMP IN (OUT) #4 | 0.5 track jump<br>period | 233 µs                                                | 60 ms; TOFF is low during the C period. | 0.5 track jump<br>period                                                                                                           | 0.5 track jump<br>period | 60 ms; TOFF is low during the C period. |

| 2 TRACK JUMP IN (OUT)    |                          | None                                                  |                                         | 1 track jump<br>period                                                                                                             | 1 track jump<br>period   | See note.                               |

| 4 TRACK JUMP IN (OUT)    | 2 track jump<br>period   | 466 μs                                                | 60 ms                                   | 2 track jump<br>period                                                                                                             | 2 track jump<br>period   | 60 ms                                   |

| 16 TRACK JUMP IN (OUT)   | 9 track jump<br>period   | 7 track jump<br>period                                | 60 ms                                   | 9 track jump<br>period                                                                                                             | 9 track jump<br>period   | 60 ms                                   |

| 32 TRACK JUMP IN (OUT)   | 18 track jump period     | 14 track jump<br>period                               | 60 ms                                   | 18 track jump<br>period                                                                                                            | 14 track jump<br>period  | 60 ms                                   |

| 64 TRACK JUMP IN (OUT)   | 36 track jump period     | 28 track jump<br>period                               | 60 ms                                   | 36 track jump period                                                                                                               | 28 track jump<br>period  | 60 ms                                   |

| 128 TRACK JUMP IN (OUT)  | 72 track jump<br>period  | 56 track jump<br>period                               | 60 ms                                   | 72 track jump<br>period                                                                                                            | 56 track jump<br>period  | 60 ms                                   |

| 256 TRACK CHECK          | when 256 tracks          | during the period are passed over. es are not output. | 60 ms                                   | TOFF goes high during the period when 256 tracks are passed over. The a and b pulses are not output. There are no a and b periods. |                          | 60 ms                                   |

| TRACK JUMP BRAKE         | There are no a           | and b periods.                                        | 60 ms                                   |                                                                                                                                    |                          | 60 ms                                   |

Note: \*Applications can select whether or not a braking period (period C) is present. Code \$F6 selects operation without a braking period, and code \$7F selects operation with a 60-ms braking period. The LC78625E defaults to no braking period operation after a reset.

<sup>\*</sup>The 1 TRACK JUMP #3 and 2 TRACK JUMP modes (the earlier modes) do not have a braking period (the C period). Since brake mode must be generated by an external circuit, care is required when using this mode.

When the LC78625E is used in combination with an LA9230/40 Series LSI, since the THLD signal is generated by the LA9230/40, the THLD pin (pin 25) will be unused, and should be left open.

<sup>\*</sup>As indicated in the table, actuator signals are not output during the 256 TRACK CHECK function. This is a mode in which the TES signal is counted in the tracking loop off state. Therefore, feed motor forwarding is required.

<sup>\*</sup>The servo command register is automatically reset after one cycle of the track jump sequence (a, b, c) completes.

<sup>\*</sup> If another track jump command is issued during a track jump operation, the contents of that new command will be executed immediately.

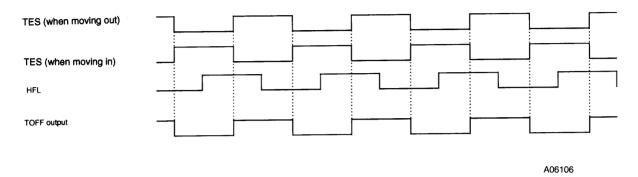

### · Tracking brake

The chart shows the relationships between the TES, HFL, and TOFF signals during the track jump C period. The TOFF signal is extracted from the HFL signal by TES signal edges. When the HFL signal is high, the pickup is over the mirror surface, and when low, the pickup is over data bits. Thus braking is applied based on the TOFF signal being high when the pickup is moving from a mirror region to a data region and being low when the pickup is moving from a data region to a mirror region.

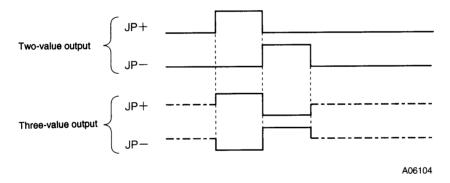

### • JP three-value output

| Code | COMMAND                              | RES = L |

|------|--------------------------------------|---------|

| \$B6 | JP three-value output                |         |

| \$B7 | JP two-value output (earlier scheme) |         |

The JP three value output command allows the track jump operation to be controlled from a single pin. However, the kick gain is 6 dB lower when this pin is used, so applications must increase the gain in the servo system.

### · Track check mode

| Code | COMMAND                | RES = L |

|------|------------------------|---------|

| \$F0 | Track check in         |         |

| \$F8 | Track check out        |         |

| \$FF | Two-byte command reset | 0       |

The LC78625E will count the specified number of tracks when the microprocessor sends an arbitrary binary value in the range 8 to 254 after issuing either a track check in or a track check out command.

A06105

Note: \*When the desired track count has been input in binary, the track check operation is started by the fall of RWC.

- \*During a track check operation the TOFF pin goes high and the tracking loop is turned off. Therefore, feed motor forwarding is required.

- \*When a track check in/out command is issued the function of the WRQ signal switches from the normal mode subcode Q standby monitor function to the track check monitor function. This signal goes high when the track check is half completed, and goes low when the check finishes. The control microprocessor should monitor this signal for a low level to determine when the track check completes.

- \*If a two-byte reset command is not issued, the track check operation will repeat. That is, to skip over 20,000 tracks, issue a track check 201 command once, and then count the WRQ signal 100 times. This will check 20,000 tracks.

- \* After performing a track check operation, use the brake command to have the pickup lock onto the track.

- 9. Error flag output; Pin 58: EFLG, pin 62: FSX

The FSX signal is generated by dividing the crystal oscillator clock, and is a 7.35 kHz frame synchronization signal. The error correction state for each frame is output from EFLG. The playback OK/NG state can be easily determined from the extent of the high level that appears here.

10. Subcode P, Q, and R to W output circuit; Pin 59: PW, pin 57: SBSY, pin 60: SFSY, pin 61: SBCK PW is the subcode signal output pin, and all the codes, P, Q, and R to W can be read out by sending eight clocks to the SBCK pin within 136 µs after the fall of SFSY. The signal that appears on the PW pin changes on the rising edge of SBCK. If a clock is not applied to SBCK, the P code will be output from PW. SFSY is a signal that is output for each subcode frame cycle, and the falling edge of this signal indicates standby for the output of the subcode symbol (P to W). Subcode data P is output on the fall of this signal.

SBSY is a signal output for each subcode block. This signal goes high for the S0 and S1 synchronization signals. The fall of this signal indicates the end of the subcode synchronization signals and the start of the data in the subcode block. (EIAJ format)

# 11. Subcode Q output circuit; Pin 63: WRQ, pin 64: RWC, pin 65: SQOUT, pin 67: $\overline{\text{CQCK}}$ , pin 75: $\overline{\text{CS}}$

| Code | COMMAND      | RES = L |

|------|--------------|---------|

| \$09 | ADDRESS FREE |         |

| \$89 | ADDRESS 1    | 0       |

Subcode Q can be read from the SQOUT pin by applying a clock to the  $\overline{\text{CQCK}}$  pin.

Of the eight bits in the subcode, the Q signal is used for song (track) access and display. WRQ will be high only if the data passed the CRC error check and the subcode Q format internal address is 1 (Note 1). The control microprocessor can read out data from SQOUT in the order shown below by detecting this high level and applying  $\overline{CQCK}$ . When  $\overline{CQCK}$  is applied the DSP disables register update internally. The microprocessor should give update permission by setting RWC high briefly after reading has completed. WRQ will fall to low at this time. Since WRQ falls to low 11.2 ms after going high,  $\overline{CQCK}$  must be applied during the high period. Note that data is read out LSB first.

Note: 1. These conditions will be ignored if an address free command is sent. This is provided to handle CD-ROM applications.

|             | CONT                | ADR           |

|-------------|---------------------|---------------|

|             | TN                  | 0             |

|             | INDEX (             | POINT)*       |

|             | M                   | IN            |

|             | SE                  | EC .          |

|             | FRA                 | ME            |

|             | ZE                  | RO            |

|             | AMIN (PMII          | N)* /PKMIN    |

|             | ASEC (PSEC)* /PKSEC |               |

| _           | AFRAME (PFRA        | ME)* /PKFRAME |

| LVM/PKM     | LVM data            | PKM data      |

| 16-bit data | PKM data            |               |

| _           | -                   |               |

\*: Items in parentheses refer to the read-in area.

Note: Normally, the WRQ pin indicates the subcode Q standby state. However, it is used for a different monitoring purpose in track check mode and during internal braking. (See the items on track counting and internal braking for details.)

The LC78625E becomes active when the  $\overline{\text{CS}}$  pin is low, and subcode Q data is output from the SQOUT pin. When the  $\overline{\text{CS}}$  pin is high, the SQOUT pin goes to the high-impedance state.

### 12. Level meter (LVM) data and peak meter (PKM) data readout

| Code | COMMAND             | RES = L |

|------|---------------------|---------|

| \$2B | PKM Set (LVM Reset) |         |

| \$2C | LVM Set (PKM Reset) | 0       |

| \$2D | PKM mask set        |         |

| \$2E | PKM mask reset      | 0       |

### • Level meter (LVM)

- The LVM set command (\$2C) sets the LC78625E to LVM mode.

- LVM data is a 16-bit word in which the MSB indicates the L/R polarity and the low-order 15 bits are absolute value data. A one in the MSB indicates left channel data and a zero indicates right channel data.

- LVM data is appended after the 80 bits of subcode Q data, and can be read out by applying 96 clock cycles to the CQCK pin. Each time LVM data is read out the left/right channel state is inverted. Data is held independently for both the left and right channels. In particular, the largest value that occurs between readouts for each channel is held.

### • Peak meter (PKM)

- The PKM set command (\$2B) sets the LC78625E to PKM mode.

- PKM data is a 16-bit word in which the MSB is always zero and the low-order 15 bits are absolute value data. This functions detects the maximum value that occurs in the data, whichever channel that value occurs in.

- PKM data is read out in the same manner as LVM data. However, data is not updated as a result of the readout operation.

- The absolute time for PKM mode subcode Q data is computed by holding the absolute time (ATIME) detected after the maximum value occurred and sending that value. (Normal operation uses relative time.)

- It is possible to set the LC78625E to ignore values larger than the already recorded value by issuing the PKM mask set command, even in PKM mode. This function is cleared by issuing a PKM mask reset command. (This is used in PK search in a memory track.)

### 13. Mute control circuit

| Code | COMMAND     | RES = L |

|------|-------------|---------|

| \$01 | MUTE 0 dB   |         |

| \$02 | MUTE −12 dB |         |

| \$03 | MUTE —∞ dB  | 0       |

An attenuation of 12 dB (MUTE -12 dB) or full muting (MUTE  $\infty$  dB) can be applied by issuing the appropriate command from the table. Since zero cross muting is used, there is minimal noise associated with this function. Zero cross is defined for this function as the top seven bits being all ones or all zeros.

### 14. Interpolation circuit

Outputting incorrect audio data that could not be corrected by the error detection and correction circuit would result in loud noises being output. To minimize this noise, the LC78625E replaces the incorrect data with linearly interpolated data based on the correct data on either side of the incorrect data. More precisely, the LC78625E uses this technique if C2 flags occurred up to three times in a row. If C2 flags occurred four or more times in a row, the LC78625E converges the output level to the muting level. However, when correct data is finally output following four or more C2 flag occurrences, the LC78625E replaces the 3 data items between the data output four items previously and the correct data with linearly interpolated data.

### 15. Bilingual function

| Code | COMMAND  | RES = L |

|------|----------|---------|

| \$28 | STO CONT | 0       |

| \$29 | Lch CONT |         |

| \$2A | Rch CONT |         |

- Following a reset or when a stereo command (\$28) has been issued, the left and right channel data is output to the left and right channels respectively.

- When an Lch set command (\$29) is issued, the left and right channels both output the left channel data.

- When an Rch set command (\$2A) is issued, the left and right channels both output the right channel data.

### 16. De-emphasis; Pin 32: EMPH

The pre-emphasis on/off bit in the subcode Q control information is output from the EMPH pin. When this pin is high, the LC78625E internal de-emphasis circuit operates and the digital filters and the D/A converter output de-emphasized data.

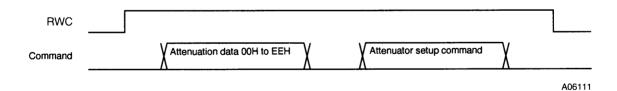

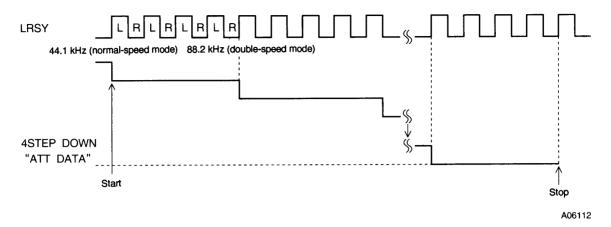

### 17. Digital attenuator

Digital attenuation can be applied to the audio data by setting the RWC pin high and inputting the corresponding twobyte command to the COIN pin in synchronization with the  $\overline{CQCK}$  clock.

| Code | COMMAND         | RES = L      |

|------|-----------------|--------------|

| \$81 | ATT DATA SET    | DATA 00H Set |

| \$82 | ATT 4STEP UP    | (MUTE –∞dB)  |

| \$83 | ATT 4STEP DOWN  |              |

| \$84 | ATT 8STEP UP    |              |

| \$85 | ATT 8STEP DOWN  |              |

| \$86 | ATT 16STEP UP   |              |

| \$87 | ATT 16STEP DOWN |              |

### · Attenuation setup

Since the attenuation level is set to the muted state (a muting of -∞ is specified by an attenuation coefficient of 00H) after the LC78625E is reset, the attenuation coefficient must be directly set to EEH (using the ATT DATA SET command) to output audio signals. Note that the attenuation level can be set to one of 239 values from 00H to EEH. These two-byte commands differ from the two-byte commands used for track counting in that it is only necessary to set RWC once and a two-byte command reset is not required. (See the item on two-byte commands (RWC set once) on page 11.)