LC66PG5XX

EPROM-Mountable Type 4-bit Microcomputer Evaluation Chip for The LC665XX Series Microcomputers

# Overview

The LC66PG5XX is an EPROM-mountable type 4-bit microcomputer for developing and evaluating programs written for the CMOS 4-bit single-chip LC665XX series microcomputers. Either 2764 or 27128 type EPROM can be mounted on the LC66PG5XX. The LC66PG5XX with the EPROM mounted can carry out the same functions as those of the LC665XX series microcomputers. Therefore, you can evaluate programs developed for application products controlled by the LC66PG5XX into the applications before the programs are masked in the ROMs.

## Features

- Either 2764 or 27128 type EPROM can be mounted.

- Shrink type 64-pin configuration compatible with the LC665XX series microcomputers. Note that pull-up resistors need to be externally added.

- Options provided for selecting functions. Options allowing the user to select output signal level for ports 0, 1 and 8 at the initial reset or to specify whether the watchdog timer function is employed by setting external pin levels

- Instruction cycle time 0.92 to 10 microseconds.

- +5V single power source.

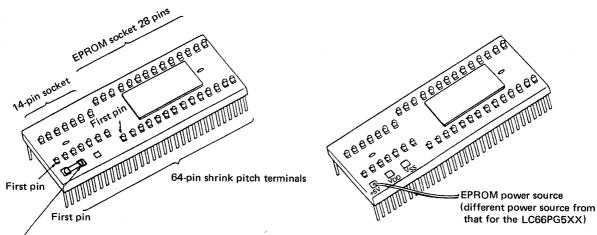

The LC66PG5XX has the 28-pin soket and 14-pin soket on the top face of the package. It also has the shrink type 64-pin terminals on the bottom face of the package. The 28-pin soket is used for mounting the EPROM containing the programs and 14-pin soket for selecting functions by options (input/output options not included). The shrink type 64-pin terminals are compatible with the LC665XX series microcomputers.

#### Pin assignment

| SI0/P20 1   | 0               |                                | 64              | VDD       |

|-------------|-----------------|--------------------------------|-----------------|-----------|

| SO0/P21 2   |                 |                                |                 | P13       |

| SCK0/P22 3  |                 |                                |                 | P12       |

| INT0/P23 4  |                 | 1 14 <b>○ +5∨</b><br>2 13○ +5∨ |                 | P11       |

| INT1/P30 5  |                 | 2 13() +5V<br>3 12() +5V       | 60              | P10       |

| POUT0/P31 6 |                 |                                | 59              | P03       |

| POUT1/P32 7 | RAMCO O         | -                              | 58              | P02       |

| HOLD/P33 8  | 1               | 5 9 <b>O</b> +5V               | 57              | P01       |

| P40 9       | CP1 O           |                                | 56              | P00       |

| P41 10      | CriO            |                                | 55              | PE1/TPB   |

| P42 11      |                 |                                | 54              | PE0/TRA   |

| P43 12      |                 |                                | 53              | PD3/CMP3  |

| P50 13      |                 |                                | 52              | PD2/CMP2  |

| P51 14      |                 |                                | 51              | PD1/CMP1  |

| P52 15      |                 |                                | 50              | PD0/CMP0  |

| P53 16      |                 |                                | 49              | PC3/VREF1 |

| SI1/P60 [17 | <u>г</u>        | ·_/ 1                          | 48              | PC2/VREF0 |

| SO1/P61 18  | +5VO 1          | 28 0 +5                        | 4/              | PC1       |

| SCK1/P62 19 | PM12O 2         | 27 ()+5                        |                 | PC0       |

| PIN1/P63 20 | PM7 0 3         | 26 OPM                         | <sup>3</sup> 45 | PB3       |

| P70 21      | PM6Ó 4          | 25 OPM                         | 44              | PB2       |

| P71 22      | PM50 5<br>PM406 | 24 O PM                        | 43              | PB1       |

| P72 23      | PM30 7          | 23 OPM<br>22 OVS               | 42              | PB0       |

| P73 24      | PM30 7          | 1                              | 41              | PA3       |

| P80 25      | PM10 9          | 21 ÓPM1<br>20 Ó CE             | 40              | PA2       |

| P81 26      | PM0 0 10        | 20 QCE<br>19 QIM7              | . —             | PA1       |

| P82 27      |                 |                                | <u></u>         | PA0       |

| P83 28      |                 |                                | . <u>  »/  </u> | P93/INT5  |

| INT2/P90 29 | IM20 13         |                                | 36              | P92/INT4  |

| TEST 30     | VSS() 14        | 15 OIM3                        | 35              | P91/INT3  |

| VSS 31      | Ĩ               |                                | 34              | RES       |

| OSC1 32     |                 |                                | 33              | OSC2      |

|             |                 |                                | -               |           |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

| Model name   | LC66506A        | LC66508A     | LC66512A     | LC66516A     | LC66PG5XX                      | LC66599                        |

|--------------|-----------------|--------------|--------------|--------------|--------------------------------|--------------------------------|

| ROM capacity | 6KB             | 8KB          | 12KB         | 16KB         | 16K bytes.<br>Externally added | 16K bytes.<br>Externally added |

| RAM capacity | 512×4           | 512×4        | 512×4        | 512×4        | 512×4                          | 512×4                          |

| Package      | DIP64S<br>FLP64 | $\leftarrow$ | $\leftarrow$ | $\leftarrow$ | DIC64S                         | PGA120                         |

| Remarks      | Available       | $\leftarrow$ | $\leftarrow$ | $\leftarrow$ | Piggyback                      | EVA chip                       |

#### Configurations of the LC665XX series microcomputers

#### Notes on use

The LC66PG5XX is a product for developing and evaluating programs for the LC665XX series microcomputers. Keep always in mind the following considerations when using the LC66PG5XX.

- 1. The operating conditions are different from those of the production mask ROM . It is not recommended that the LC66PG5XX is used under the environmental conditions including high temperature and terrible humidity.

- 2. The electric characteristics are not the same as those of the production mask ROM. To evaluate strictly the electric characteristics at the interface with external circuits, use the recommended electric characteristics values of the production mask ROM.

- 3. The discrepancy in internal circuit pattern configuration between the LC66PG5XX and the production mask ROM results in the following differences between them.

•Differrent initial values are set in RAMs at power ON.

•Differrent noise figures (NF) are recorded. That is, the static noise intensity of the LC66PG5XX is different from that of the production mask ROM. Keep it always in mind.

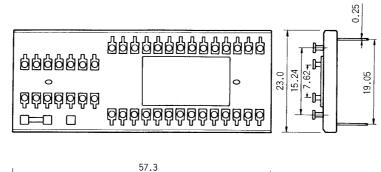

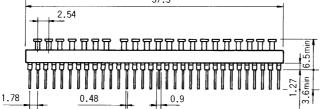

#### **External dimension**

## **Overview of terminal function**

| Terminal<br>name                           | Input/<br>output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | LC66PG5XX output<br>format | Option<br>(production chip)                                                        | At initial<br>reset  |

|--------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------------------|----------------------|

| P00<br>P01<br>P02<br>P03                   | I/O              | Input/output port P00 to P03<br>•Data input and output in 4-bit units or in 1-<br>bit units.<br>•P00 to P03 used for controlling HALT mode.                                                                                                                                                                                                                                                                                                                                                                                        | •Nch OD output             | •Pull-up MOS or Nch OD<br>(open drain) output<br>•Output level at initial<br>reset | H or L<br>(optional) |

| P10<br>P11<br>P12<br>P13                   | I/O              | Input/output port P10 to P13<br>•Data input and output in 4-bit units or in 1-<br>bit units.                                                                                                                                                                                                                                                                                                                                                                                                                                       | •Nch OD output             | Pull-up MOS or Nch OD<br>output     Output level at initial<br>reset               | H or L<br>(optional) |

| P20/SI0<br>P21/SO0<br>P22/SCK0<br>P23/INT0 | I/O              | <ul> <li>Input/output port P20 to P23</li> <li>Data input and output in 4-bit units or in 1-bit units.</li> <li>P20 also used as SI0 terminal for serial input.</li> <li>P21 also used as SO0 for serial output.</li> <li>P22 also used as SCK0 for serial clock signal input/output.</li> <li>P23 also used as INT0 terminal for INT0 interrupt request input. In addition, it is used for timer 0 event count input and pulse width measurement input.</li> </ul>                                                                | •Nch OD output             | •CMOS or Nch OD<br>output                                                          | Η                    |

| P30/INT1<br>P31/POUT0<br>P32/POUT1         | I/O              | <ul> <li>Input/output port P30 to P32</li> <li>Data input and output in 3-bit units or in 1-bit units.</li> <li>P30 also used as INT1 terminal for INT1 interrupt request signal.</li> <li>P31 also used for burst pulse signal output from timer 0.</li> <li>P32 also used for burst pulse signal output from timer 1 and PWM signal output.</li> </ul>                                                                                                                                                                           | •Nch OD output             | •CMOS or Nch OD<br>output                                                          | Η                    |

| P33/HOLD                                   | 1                | <ul> <li>HOLD mode control input.</li> <li>•When HOLD=L, HOLD mode to be set by the HOLD instruction.</li> <li>•During HOLD mode "ON", restart up to the CPU by applying "H"-level signal to the HOLD terminal.</li> <li>•Also used as input port P33 if used together with port P30 to P32.</li> <li>•CPU not to be reset even if "L"-level signal is applied to the RES terminal with the P33/HOLD set to "L". The output level of the P33/HOLD terminal at power ON must not be set "L"on your application products.</li> </ul> | _                          | -                                                                                  | -                    |

| P40<br>P41<br>P42<br>P43                   | I/O              | Input/output port P40 to P43<br>•Data input and output in 4-bit units and 1-bit<br>units.<br>•Also used for data input/output in 8-bit units<br>if jointly used with port P50 to P53.<br>•Used for ROM data output in 8-bit units if<br>jointly used with port P50 to P53.                                                                                                                                                                                                                                                         | •Nch OD output             | •Pull-up MOS or Nch OD<br>output                                                   | н                    |

Continued on next page

#### Continued from preceding page

| Terminal<br>name                             | Input/<br>output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                   | LC66PG5XX output<br>format | Option<br>(production chip)                                        | At initial<br>reset  |

|----------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------|----------------------|

| P50<br>P51<br>P52<br>P53                     | 1/0              | <ul> <li>Input/output port P50 to P53</li> <li>Data input/output in 4-bit units and 1-bit unit.</li> <li>Used for input/output in 8-bit units if jointly used with port P40 to P43.</li> <li>Used for ROM data output in 8-bit units if jointly used with port P40 to P43.</li> </ul>                                                                                                                                                      | •Nch OD output             | •Pull-up MOS or Nch OD<br>output                                   | Н                    |

| P60/SI1<br>P61/SO1<br>P62/SCK1<br>P63/PIN1   | I/O              | Input/output port P60 to P63<br>•Data input/output in 4-bit units and 1-bit<br>units.<br>•P60 terminal also used as terminal SI1 for<br>serial input.<br>•P61 terminal also used as terminal SO1 for<br>serial output.<br>•P62 terminal also used as terminal SCK1<br>for serial clock signal input/output.<br>•P63 terminal also used for event count input<br>to timer 1.                                                                | •Nch OD output             | •CMOS or Nch OD<br>output                                          | Н                    |

| P70<br>P71<br>P72<br>P73                     | 0                | Output port P70 to P73<br>•Data output in 4-bit units and in 1-bit units.<br>•The contents of output latch circuit to be<br>input with input-related instructions.                                                                                                                                                                                                                                                                         | •Nch OD output             | •Pull-up MOS or Nch OD<br>output                                   | Н                    |

| P80<br>P81<br>P82<br>P83                     | 0                | Output port P80 to P83<br>•Data output in 4-bit units and in 1-bit units.<br>•The contents of output latch circuit to be<br>input with input-related instructions.<br>•Pch OD output option available.                                                                                                                                                                                                                                     | •Pch OD output             | •CMOS or Pch OD<br>output<br>•Output level at the initial<br>reset | H or L<br>(optional) |

| P90/INT2<br>P91/INT3<br>P92/INT4<br>P93/INT5 | I/O              | <ul> <li>Input/output port P90 to P93</li> <li>Data input and output in 4-bit units and in 1-bit units.</li> <li>P90 also used as the INT2 terminal for INT2 interrupt request input.</li> <li>P91 also used as the INT3 terminal for INT3 interrupt request input.</li> <li>P92 also used as the INT4 terminal for INT4 interrupt request input.</li> <li>P93 also used as the INT5 terminal for INT5 interrupt request input.</li> </ul> | •Nch OD output             | •CMOS or Nch OD<br>output                                          | Η                    |

| PA0<br>PA1<br>PA2<br>PA3                     | 0                | Output port PA0 to PA3<br>•Data output in 4-bit units and in 1-bit units.<br>•The contents of output latch circuit to be<br>input with input-related instructions.                                                                                                                                                                                                                                                                         | •Nch OD output             | •Pull-up MOS or Nch OD<br>output                                   | Н                    |

| PB0<br>PB1<br>PB2<br>PB3                     | 0                | Output port PB0 to PB3<br>•Data output output in 4-bit units and in 1-bit<br>units.<br>•The contents of output latch circuit to be<br>input with input-related instructions.                                                                                                                                                                                                                                                               | •Nch OD output             | •Pull-up MOS or Nch OD<br>output                                   | Н                    |

Continued on next page

#### Continued from preceding page

| Terminal<br>name                             | Input/<br>output | Function                                                                                                                                                                                                                                                                            | LC66PG5XX output<br>format | Option<br>(production chip)                                                                       | At initial reset |

|----------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------|------------------|

| PC0<br>PC1<br>PC2/VREF0<br>PC3/VREF1         | I/O              | <ul> <li>Input/output port PC0 to PC3</li> <li>Data input and output in 4-bit units and in 1-bit units.</li> <li>PC2 also used as the VREF0 terminal for reference voltage input.</li> <li>PC3 also used as the VREF1 terminal for reference voltage input.</li> </ul>              | •Nch OD output             | •CMOS or Nch OD<br>output                                                                         | н                |

| PD0/CMP0<br>PD1/CMP1<br>PD2/CMP2<br>PD3/CMP3 | 1                | Input port PD0 to PD3<br>•Can be selected as comparator input<br>terminals on programs.<br>PD0 : reference voltage input (VREF0).<br>PD1 to PD3 : reference voltage input<br>(VREF1)<br>•PD0, PD1 (PD2 to PD3) selectable as<br>comparator input ports on programs in this<br>unit. | _                          | _                                                                                                 | Normal input     |

| PE0/TRA<br>PE1/TRB                           | I                | Input port<br>•Selectable as three-state input port on<br>programs.                                                                                                                                                                                                                 | -                          | -                                                                                                 | Normal input     |

| OSC1<br>OSC2                                 | 1<br>0           | Terminals for system clock oscillator<br>externally added.<br>•Leave OSC2 open and close OSC1 for<br>external clock signal input when external<br>clock mode is selected.                                                                                                           | _                          | •Ceramic resonator<br>oscillation, RC (resistor<br>and capacitor) or<br>external clock selection. | _                |

| RES                                          | I                | Terminal for system reset signal input.<br>•CPU to be initialized when P33/HOLD="H"<br>plus "L" level voltage is applied to the RES<br>terminal.                                                                                                                                    | -                          | -                                                                                                 | _                |

| TEST                                         | 1                | Terminal for CPU test signal input.<br>•Always connected to V <sub>SS</sub> during operation.                                                                                                                                                                                       | -                          | -                                                                                                 | _                |

| V <sub>DD</sub><br>V <sub>SS</sub>           | _                | Power source terminal                                                                                                                                                                                                                                                               | -                          | -                                                                                                 | _                |

| Terminal<br>name     | Input/<br>output | Output type   | Function                                                                                                                                                           |

|----------------------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0HL<br>P1HL<br>P8HL | I                | _             | Terminals for signal input to select output level at ports 0, 1 and 8 at the reset. "H" level output to be selected if "H" level signal is input to the terminals. |

| RAMC0<br>RAMC1       | I                | _             | Terminal for signal input to control RAM capacity.                                                                                                                 |

| WDC                  | I                | -             | Terminal for signal input to contorol whether the watchdog timer function is used. The watchdog timer function to be selected if "H" level signal is input.        |

| CP1                  | 0                | Pu MOS output | Terminal for signal output to select clock signal edge for output latch of extended ports.                                                                         |

| IM0 to IM7           | I                | -             | Terminals for instruction input from external circuits.                                                                                                            |

| PM0 to PM13          | 0                | Pu MOS output | Terminals for PC output to external circuits.                                                                                                                      |

| CE                   | 0                | Pu MOS output | Terminal for signal output to contorol the CE terminal of memory externally added.                                                                                 |

#### LC66PG5XX special terminals

Remarks : Pu MOS output ..... Pull-up MOS transistor output.

CMOS output ...... Complementary MOS output. OD output ...... Open drain output.

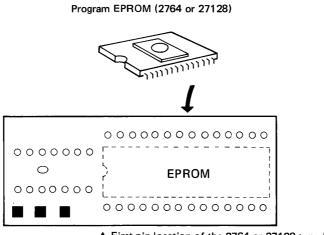

### How to mount and use EPROM on the LC66PG5XX

You write assembled program data into an EPROM and mount it on the LC66PG5XX. To write data into the EPROM, you can use the EPROM writer function of the EVA-800.

#### ▲ First pin location of the 2764 or 27128 type EPROM

#### Power source for EPROM

Normal current drain per EPROM is in the range of 50mA and 100mA. When power capacity of an application product is not sufficient, power can be supplied to the EPROM from external independent power source. That is, the power source which is different from that on the application system can be selected.

At the factory shipment, the +5V pin and  $V_{DD}$  pin are connected on the LC66PG5XX. Therefore, power is supplied to the EPROM from the LC66PG5XX power source terminal (pin64).

Of the power source pads on the package surface, +5V pad is used to supply power to the EPROM.

VDD and +5V supply pad are connected at the time of shipment.

## Note

The LC66PG5XX is a CMOS type IC. This reminds us that latch-up may be caused by input voltage level below the  $V_{SS}$  level or above the  $V_{DD}$  level. The latch-up is specific to this type of IC and destroys IC device structure or adversely affects operating functions. You should be careful about the voltage level range of the LC66PG5XX and EPROM. To start the LC66PG5XX and EPROM operation, first turn on the LC66PG5XX and then the EPROM. To stop the LC66PG5XX and EPROM operation, first turn off the EPROM and then the LC66PG5XX.

# Function selection by options

Select the port 0, port 1 or port 8 output level at the reset, watchdog timer function and internal RAM capacity according to the options and functions of the microcomputer to be evaluated. Set as below pins 1 to 6 of the 14-pin socket on the package surface.

| Function type                             | Pin No.    | Pin name     | Pin s       | etting | Function mode              |

|-------------------------------------------|------------|--------------|-------------|--------|----------------------------|

| Port 0, port 1 and<br>Port 8 output level | 1          | P0HL<br>P1HL | ON          |        | Port output level "H"      |

| at reset                                  | at reset 2 |              | OFF         |        | Port output level "L"      |

| Watah dag timar                           | 6          | WDC          | ON<br>OFF   |        | Operation                  |

| Watchdog timer                            | 0          | WDC          |             |        | Stop                       |

|                                           |            | RAMCO        | Pin setting |        | DAM conseit/               |

|                                           |            |              | RAMC1       | RAMC0  | RAM capacity               |

| Internal RAM                              | 4<br>5     |              | OFF         | OFF    | No setting for the LC665XX |

| capacity                                  | 5          | RAMC1        | OFF         | ON     | series microcomputers      |

|                                           |            |              | ON          | OFF    | 512W                       |

|                                           |            |              | ON          | ON     | 51200                      |

ON: +5V voltage input, OFF : Open.

Pins 14, 13, 12, 11, 10 and 9 of the 14-pin socket are assigned as the +5V terminals. These terminals can be used only for supplying +5V voltage to the pins 1, 2, 3, 4, 5, and 6.

Note that pin 8 is reserved for future use and should be left open.

#### Notes on use

- 1. The port output format for the LC66PG5XX is as follows : The Pch OD format is employed only for port 8. The Nch OD format is employed for the rest. Add resistors to each port according to the port output formats employed for production chips.

- •When optional pull-up resistors are selected for ports P0, P1, P4, P5, P7, PA and PB, add resistors of about  $10k\Omega$  to them and connect the port to the V<sub>DD</sub> terminal.

- •When the optional CMOS output format is selected for port P8, add the resistor of about  $1k\Omega$  to it and connect the port to the V<sub>SS</sub> terminal. Select the resistor in the range of  $0.5k\Omega$  to  $10k\Omega$  according to load balance.

- •When the optional CMOS output format is selected for ports P2, P3 (P33 not included), P6, P9 and PC, add the resistors of about 10 k $\Omega$  to them and connect them to the V<sub>DD</sub> terminal. (add the resistors of more than 1 k $\Omega$  if sink current is used.)

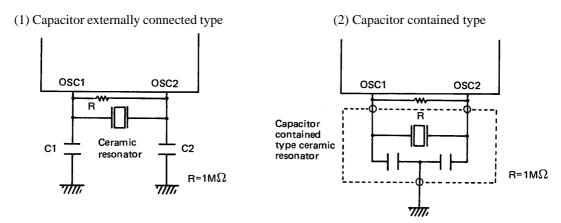

- 2. The LC66PG5XX has no feedback resistors. Add the external feedback resistor of about 1 M $\Omega$  to the LC66PG5XX when the ceramic resonator oscillation is selected. The external capacitance is the same as that of production chips.

- 3. The constants and oscillation characteristics of the RC (resistor and capacitor) oscillation circuit are different from those of production chips. Set them to the oscillation frequency of production chips by making adjustments to volume resistor.

- 4. The operating voltage level of the LC66PG5XX must be within the range of the operating voltage of the EPROM and other ICs.

That is, the level is :  $V_{DD}$ =5Vwith 5% margin.

5. The operating environment temperature is in the range of 10°C to 40°C.

| Parameter                   | Symbol              | Terminal and note                                                      | Condition | Ratings                      | Unit | Note |

|-----------------------------|---------------------|------------------------------------------------------------------------|-----------|------------------------------|------|------|

| Maximum voltage level       | V <sub>DD</sub> max | V <sub>DD</sub>                                                        |           | -0.3 to +7.0                 | V    |      |

| Input voltage               | V <sub>IN</sub> 1   | P2, P3(P33/HOLD not included),<br>P6                                   |           | -0.3 to +15.0                | V    | 1    |

|                             | V <sub>IN</sub> 2   | Other inputs                                                           |           | –0.3 to V <sub>DD</sub> +3.0 | V    | 2    |

| Output voltage              | V <sub>OUT</sub> 1  | P2, P3(P33/HOLD not included),<br>P6, P7 and PA                        |           | -0.3 to +15.0                | V    | 1    |

|                             | V <sub>OUT</sub> 2  | Other outputs                                                          |           | –0.3 to V <sub>DD</sub> +3.0 | V    | 2    |

| Output current per terminal | I <sub>ON</sub> 1   | P0, P1, P2, P3(P33/HOLD not<br>included), P4, P5, P6, P8, P9 and<br>PC |           | 4                            | mA   | 3    |

| output ouriont por torminal | I <sub>ON</sub> 2   | P7, PA, PB                                                             |           | 20                           | mA   | 3    |

|                             | -l <sub>OP</sub> 2  | P8                                                                     |           | 4                            | mA   | 4    |

|                             | ΣI <sub>ON</sub> 1  | P2, P3(P33/HOLD not included),<br>P4, P5, P6, P7 and P8                |           | 75                           | mA   | 3    |

| Total terminal current      | $\Sigma I_{ON}^2$   | P0, P1, P9, PA, PB, PC                                                 |           | 75                           | mA   | 3    |

|                             | $-\Sigma I_{DP}1$   | 8                                                                      |           | 25                           | mA   | 4    |

| Allowable power dissipation | Pd max              | Ta=10 to 40° C                                                         | DIC-64S   | 600                          | mW   |      |

| Operating temperature       | Topr                |                                                                        |           | +10 to +40                   | °C   |      |

| Storage tempurature         | Tstg                |                                                                        |           | +55 to +125                  | °C   |      |

Absolute maximum ratings at  $Ta = 25^{\circ}C$ ,  $V_{SS} = 0V$

Note 1: Applicable only when open drain output format is selected. If the format is not selected, another standard value is used.

Note 2: The self oscillation voltage level can be included in the standard value range as far as oscillation input/output is concerned.

Note 3: Sink current (applicable to P8 only when CMOS output format is selected).

Note 4: Source current (applicable to terminals other than P8 only when pull-up output format or CMOS output format is selected).

# **Recommended operating conditions** at $Ta = 10^{\circ}C$ to $40^{\circ}C$ , $V_{SS} = 0V$ , unless otherwise specified

| Rect                                  | Jinen                            |                                      | perating          | <b>y conditions</b> at                                |                                                                        | odnition |                     |                     | Ratings    | specified            |             |      |

|---------------------------------------|----------------------------------|--------------------------------------|-------------------|-------------------------------------------------------|------------------------------------------------------------------------|----------|---------------------|---------------------|------------|----------------------|-------------|------|

|                                       | Parar                            | neter                                | Symbol            | Terminal                                              |                                                                        | ounnorm  | V <sub>DD</sub> (V) | min                 | typ        | max                  | Unit        | Note |

| Opera<br>voltag                       | ating po<br>Je                   | wer                                  | V <sub>DD</sub>   | V <sub>DD</sub>                                       |                                                                        |          |                     | 4.0                 | 5.0        | 6.0                  | V           |      |

| Memo                                  | ory hold                         | voltage                              | V <sub>DD</sub> H | V <sub>DD</sub>                                       | HOLD mode                                                              |          |                     | 1.8                 |            | 6.0                  | V           |      |

| High-l                                | level inp                        | out voltage                          | V <sub>IH</sub> 1 | P2, P3 (33/HOLD<br>not included),P6                   | Output Nch Tr                                                          | OFF      | 4.0 to 6.0          | 0.75V <sub>DD</sub> |            | +13.5                | V           | 1    |

|                                       |                                  |                                      | V <sub>IH</sub> 2 | P33/HOLD P9,<br>RES, OSC1                             | Output Nch Tr                                                          | OFF      | 4.0 to 6.0          | 0.75V <sub>DD</sub> |            | V <sub>DD</sub>      | V           | 2    |

|                                       |                                  |                                      | V <sub>IH</sub> 3 | P0, P1, P4, P5,<br>PC, PD, PE                         | Output Nch Tr OFF                                                      |          | 4.0 to 6.0          | 0.7V <sub>DD</sub>  |            | V <sub>DD</sub>      | V           | 3    |

|                                       |                                  |                                      | V <sub>IH</sub> 4 | PE                                                    | 3-state input format                                                   |          | 4.0 to 6.0          | 0.8V <sub>DD</sub>  |            | V <sub>DD</sub>      | V           |      |

| Mediu<br>voltag                       | ım-level<br>Je                   | input                                | VIM               | PE                                                    | 3-state input fo                                                       | ormat    | 4.0 to 6.0          | 0.4V <sub>DD</sub>  |            | 0.6V <sub>DD</sub>   | V           |      |

| In-pha<br>range                       | •                                | ut voltage                           | VCMM              | PD, PC2, PC3                                          | Comparator in<br>mode                                                  | put      | 4.0 to 6.0          | 1.0                 |            | V <sub>DD</sub> -1.5 | V           |      |

| Low-level input voltage               |                                  | ut voltage                           | V <sub>IL</sub> 1 | P2, P3 (33/HOLD<br>not included),P6,<br>P9, RES, OSC1 | Output Nch Tr OFF                                                      |          | 4.0 to 6.0          | VSS                 |            | 0.25V <sub>DD</sub>  | V           | 2    |

|                                       |                                  |                                      | V <sub>IL</sub> 2 | P33/HOLD                                              |                                                                        |          | 1.8 to 6.0          | V <sub>SS</sub>     |            | 0.25V <sub>DD</sub>  | V           |      |

|                                       |                                  |                                      | V <sub>IL</sub> 3 | P0, P1, P4, P5,<br>PC, PD, PE, TEST                   | Output Nch Tr                                                          | OFF      | 4.0 to 6.0          | V <sub>SS</sub>     |            | 0.3V <sub>DD</sub>   | V           | 3    |

|                                       |                                  |                                      | V <sub>IL</sub> 4 | PE                                                    | 3-state input format                                                   |          | 4.0 to 6.0          | V <sub>SS</sub>     |            | 0.2V <sub>DD</sub>   | V           |      |

|                                       | -                                | quency<br>ycle time)                 | fop<br>(Tcyc)     |                                                       |                                                                        |          | 4.0 to 6.0          | 0.4<br>(10)         |            | 4.35<br>(0.92)       | MHz<br>(μs) |      |

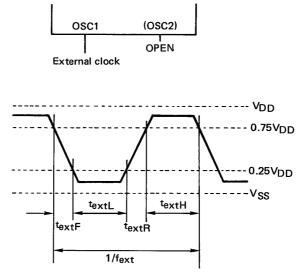

| Externanl clock pulse input condition | Freque                           | ency                                 | fext              | OSC1                                                  | See Figure 1.<br>Input to the OS<br>terminal. OSC2<br>terminal left op | 2        | 4.0 to 6.0          | 0.4                 |            | 4.35                 | MHz         |      |

| ianl clock<br>ion                     | Pulse                            | width                                | textH<br>textL    |                                                       | Same as sbove                                                          | э.       | 4.0 to 6.0          | 7.0                 |            |                      | ns          |      |

| Exterr<br>condit                      | Fall/ris                         | e time                               | textR<br>textF    |                                                       | Same as sbove                                                          | 9.       | 4.0 to 6.0          |                     |            | 30                   | ns          |      |

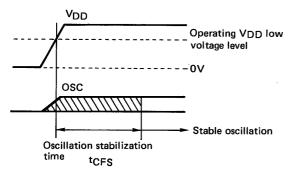

|                                       | Freque                           | ency                                 | fCF               | OSC1, OSC2                                            | See Figure 2.                                                          | 4MHz     | 4.0 to 6.0          |                     | 4.0        |                      | MHz         |      |

| Self osillation conditions            | Ceramic resonator<br>oscillation | Oscillation<br>stabilization<br>time | <sup>f</sup> CFS  |                                                       | See Figure 3.                                                          | 4MHz     | 4.0 to 6.0          |                     |            | 10                   | ms          |      |

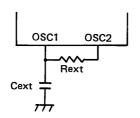

| Self                                  | Extern<br>oscillat<br>consta     | tion                                 | Cext<br>Rext      | OSC1, OSC2                                            | See Flgure 4.                                                          |          | 4.0 to 6.0          |                     | 100<br>2.2 |                      | pF<br>kΩ    |      |

Note 1: Applicable to terminals with open drain output format.  $V_{IH}2$  applied to P33/HOLD terminal.

Note 2: Applicable to terminals with open drain output format.

Note 3:  $V_{IH}^{11}$ ,  $V_{IM}$  and  $V_{IL}$  applied when PE is used for 3-state input operation.

## **Electric characteristics** at $Ta = 10^{\circ}C$ to $40^{\circ}C$ , $V_{SS} = 0$ , unless otherwise specified

|                                                          | Doromot                   | or                | Sumbol                                                                                     | Terminal                                                                | Codnitions                                        | 3           |                     | Ratings            |                     | Linit | Note |

|----------------------------------------------------------|---------------------------|-------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|-------------|---------------------|--------------------|---------------------|-------|------|

|                                                          | Paramet                   | er                | Symbol                                                                                     | Terminal                                                                |                                                   | $V_{DD}(V)$ | min                 | typ                | max                 | Unit  | Note |

| High-                                                    | level input               | current           | I <sub>IH</sub> 1                                                                          | P2, P3 (33/HOLD<br>not included),P6                                     | V <sub>IN</sub> =13.5V<br>Output Nch Tr OFF       | 4.0 to 6.0  |                     |                    | +5.0                | μΑ    | 1    |

|                                                          |                           | I <sub>IH</sub> 2 | P0, P1, P4, P5, P9<br>PC, OSC1, RES,<br>P33/HOLD (PD,<br>PE, PC2 and PC3,<br>not included) | VIN =VDD<br>Output Nch Tr OFF                                           | 4.0 to 6.0                                        |             |                     | +1.0               | μΑ                  | 1     |      |

|                                                          |                           |                   | I <sub>IH</sub> 3                                                                          | PD, PE, PC2, PC3                                                        | VIN <sup>=V</sup> DD<br>Output Nch Tr OFF         | 4.0 to 6.0  |                     |                    | +1.0                | μΑ    | 1    |

| Low-I                                                    | evel input o              | current           | I <sub>IL</sub> 1                                                                          | Input level to<br>terminals other<br>than PD, PE, PC2<br>and PC3        | VIN=VSS<br>Output Nch Tr OFF                      | 4.0 to 6.0  | -1.0                |                    |                     | μA    | 2    |

|                                                          |                           |                   | I <sub>IL</sub> 2                                                                          | PC2, PC3, PD, PE                                                        | VIN <sup>=V</sup> SS<br>Output Nch Tr OFF         | 4.0 to 6.0  | -1.0                |                    |                     | μΑ    | 2    |

| High-                                                    | level outpu               | t voltage         | V <sub>OH</sub> 1                                                                          | P8                                                                      | I <sub>OH</sub> = -1mA                            | 4.0 to 6.0  | V <sub>DD-1.0</sub> |                    |                     | V     |      |

|                                                          |                           |                   |                                                                                            |                                                                         | I <sub>OH</sub> = -0.1mA                          | 4.0 to 6.0  | V <sub>DD-0.5</sub> |                    |                     |       |      |

| Low-I                                                    | evel output               | voltage           | V <sub>OL</sub> 1                                                                          | P0, P1, P2, P3, P4,<br>P5, P6, P9, and PC<br>(P33/HOLD not<br>included) | I <sub>OL</sub> = 1.6mA                           | 4.0 to 6.0  |                     |                    | 0.4                 | V     |      |

|                                                          |                           |                   | V <sub>OL</sub> 2                                                                          | P7, PA, PB                                                              | I <sub>OL</sub> = 10mA                            | 4.0 to 6.0  |                     |                    | 1.5                 | V     |      |

| Outpu                                                    | ut off leak c             | urrent            | I <sub>OFF</sub> 1                                                                         | P2, P3, P6, P7, PA                                                      | V <sub>IN</sub> =13.5V                            | 4.0 to 6.0  |                     |                    | 5.0                 | μΑ    | 6    |

|                                                          |                           |                   | I <sub>OFF</sub> 2                                                                         | (P2, P3, P6, P7, P8<br>and PA not included)                             | V <sub>IN</sub> =V <sub>DD</sub>                  | 4.0 to 6.0  |                     |                    | 1.0                 | μΑ    | 6    |

|                                                          |                           |                   | I <sub>OFF</sub> 3                                                                         | P8                                                                      | V <sub>IN</sub> =V <sub>SS</sub>                  | 4.0 to 6.0  | -1.0                |                    |                     | μΑ    | 7    |

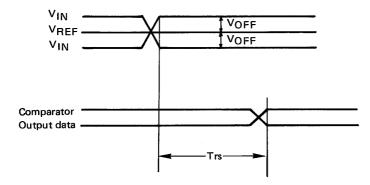

| Comp<br>voltag                                           | parator offs<br>ge        | et                | VOFF                                                                                       | PD                                                                      | V <sub>IN</sub> =1.0V to<br>V <sub>DD</sub> -1.5V | 4.0 to 6.0  |                     | ±50                | ±300                | mV    |      |

|                                                          | Hysteresi                 | s voltage         | V <sub>HYS</sub>                                                                           | P2, P3, RES, P6,<br>P9 and OSC1.                                        |                                                   | 4.0 to 6.0  |                     | 0.1V <sub>DD</sub> |                     | V     |      |

| Schmidt<br>characteristics                               | High-level<br>threshold   |                   | VtH                                                                                        | OSC1 for external clock signal input.                                   |                                                   |             | 0.5V <sub>DD</sub>  |                    | 0.75V <sub>DD</sub> |       |      |

| Schmi<br>charao                                          | Low-level<br>threshold    |                   | VtL                                                                                        |                                                                         |                                                   |             | 0.25V <sub>DD</sub> |                    | 0.5V <sub>DD</sub>  |       |      |

| RC (resistor and<br>capacitor) oscillation<br>frequency) |                           |                   | fRC                                                                                        | OSC1, OSC2                                                              | See Figure 4.<br>Cext=100pF±5%<br>Rext=2.2kΩ±1%   | 4.0 to 6.0  | 2.0                 | 3.0                | 4.0                 | MHz   |      |

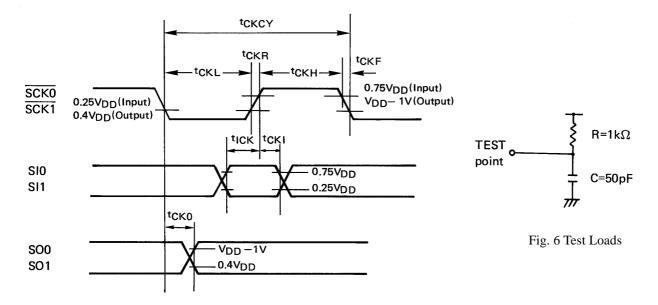

|                                                          | Cycle                     | Input             | <sup>t</sup> CKCY                                                                          | SCK0, SCK1                                                              | See the timing shown                              | 4.0 to 6.0  | 0.92                |                    |                     | μs    |      |

| ×                                                        | time                      | Outnput           |                                                                                            |                                                                         | in Figure 5 and the                               | 4.0 to 6.0  | 2.0                 |                    |                     | Тсус  |      |

| Serial clock                                             | Low-level/<br>high-level/ | Input             | <sup>t</sup> CKL                                                                           |                                                                         | test load in Figure 6.                            | 4.0 to 6.0  | 0.4                 |                    |                     | μs    |      |

| Serial                                                   | pulse width               | Outnput           | <sup>t</sup> СКН                                                                           |                                                                         |                                                   | 4.0 to 6.0  | 1.0                 |                    |                     | Тсус  |      |

| 0)                                                       | Fall/rise                 | Input             | <sup>t</sup> CKR                                                                           |                                                                         |                                                   | 4.0 to 6.0  |                     |                    | 3.0                 | μs    |      |

|                                                          | time                      | Outnput           | <sup>t</sup> CKF                                                                           |                                                                         |                                                   | 4.0 to 6.0  |                     |                    | 0.1                 |       |      |

Continued on next page

#### Continued from preceding page

|                        |                                                                                               |                                        | - ·                              |                     | Codnitions                                                                                                                                                        | ;           |     | Ratings |     |      |      |

|------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------|----------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|---------|-----|------|------|

|                        | Parameter                                                                                     | Symbol                                 | Termin                           | ai                  |                                                                                                                                                                   | $V_{DD}(V)$ | min | typ     | max | Unit | Note |

|                        | Data setup time                                                                               | <sup>t</sup> ICK                       | SI0, SI1                         |                     | See Figure 5 "Serial                                                                                                                                              | 4.0 to 6.0  | 0.3 |         |     | μs   |      |

| Serial input           | Data hold time                                                                                | <sup>t</sup> СКI                       |                                  |                     | input/output timing"<br>Synchronized with the<br>rise ( $\uparrow$ ) of the $\overline{SCK0}$<br>and $\overline{SCK1}$ signals.                                   | 4.0 to 6.0  | 0.3 |         |     | μs   |      |

| Serial output          | Output delay time                                                                             | <sup>t</sup> СКО                       | SO0, SO1                         |                     | See Figure 5 "Serial<br>input/output timing"<br>and Figure 6 "Timing<br>load". Synchronized<br>with the fall ( $\downarrow$ ) of the<br>SCK0 and SCK1<br>signals. | 4.0 to 6.0  |     |         | 0.3 | μs   |      |

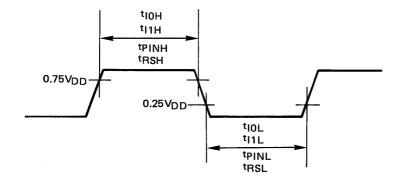

| onditions              | INT0 high-level/<br>low-level/pulse<br>width                                                  | <sup>t</sup> IOH<br><sup>t</sup> IOL   | INTO                             | See<br>Figure<br>7. | <ul> <li>When INT0 interrupt<br/>is accepted.</li> <li>When timer 0 event<br/>counter/pulse width<br/>measure input is<br/>accepted.</li> </ul>                   | 4.0 to 6.0  | 2   |         |     | Тсус |      |

| Pulse input conditions | Interrupt input to<br>terminals other<br>than INT0. High-<br>level/low-level/<br>pulse width. | <sup>ţ</sup> 11Н<br><sup>ţ</sup> 11L   | INT1, INT2<br>INT3, INT4<br>INT5 | -                   | •When each interrupt is accepted.                                                                                                                                 |             | 2   |         |     | Тсус |      |

|                        | PIN1 high-level/<br>low-level/pulse<br>width                                                  | <sup>t</sup> PINH<br><sup>t</sup> PINL | PIN1                             |                     | •When timer 1 event counter input is accepted.                                                                                                                    | -           | 2   |         |     | Тсус |      |

|                        | RES high-level/<br>low-level/pulse<br>width                                                   | <sup>t</sup> RSH<br><sup>t</sup> RSL   | RES                              |                     | •When reset signai is accepted.                                                                                                                                   | -           | 3   |         |     | Тсус |      |

| Com<br>spee            | parator response<br>d                                                                         | T <sub>RS</sub>                        | PD                               | See<br>Figure<br>8. |                                                                                                                                                                   | 4.0 to 6.0  |     |         | 30  | μs   |      |

| Oper<br>drain          | ating mode current                                                                            | IDDop                                  | V <sub>DD</sub>                  | 1                   | 4MHz ceramic resonator oscillation                                                                                                                                | 4.0 to 6.0  |     | 4.5     | 8   | mA   | 8    |

|                        |                                                                                               |                                        |                                  |                     | 4MHz external clock                                                                                                                                               |             |     | 6.5     | 11  |      |      |

|                        |                                                                                               |                                        |                                  |                     | RC oscillation                                                                                                                                                    |             |     | 4.0     | 8   |      |      |

| HALT<br>drain          | mode current                                                                                  | IDDHALT                                | V <sub>DD</sub>                  |                     | 4MHz ceramic resonator oscillation                                                                                                                                | 4.0 to 6.0  |     | 1.0     | 2.5 | mA   | 9    |

|                        |                                                                                               |                                        |                                  |                     | 4MHz external clock                                                                                                                                               | -           |     | 2       | 3.5 |      |      |

|                        |                                                                                               |                                        |                                  |                     | RC oscillation                                                                                                                                                    |             |     | 1.2     | 2.5 |      |      |

| HOLI<br>drain          | D mode current                                                                                | IDDHOLD                                | V <sub>DD</sub>                  |                     |                                                                                                                                                                   | 1.8 to 6.0  |     | 0.01    | 10  | μΑ   | 9    |

Note 1: Open drain output format and output Nch Tr OFF for input/output common ports.

Note 2: Open drain output format and output Nch Tr OFF for input/output common ports.

Note 6: Open drain output format and output Nch Tr OFF.

Note 7: Open drain output format and output Pch Tr OFF.

Note 8: Reset status. EPROM current drain not included.

Note 9: EPROM current drain not included.

Fig. 1 External clock input waveform

Fig. 2 Ceramic resonator oscillation circuit

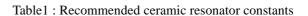

| e                         | 4MHz (Murata)             | C1 | 33pF±10% |  |  |  |  |  |

|---------------------------|---------------------------|----|----------|--|--|--|--|--|

| or<br>y<br>ed type        | CSA4.00MG                 | C2 | 33pF±10% |  |  |  |  |  |

| pacito<br>ernall<br>necte | 4MHz (Kyocera)            | C1 | 33pF±10% |  |  |  |  |  |

| Ca<br>ext<br>cor          | KBR4.0MS                  | C2 | 33pF±10% |  |  |  |  |  |

| acitor<br>ained           | 4MHz CST4.00MG (Murata)   |    |          |  |  |  |  |  |

| Capa<br>conta<br>type     | 4MHz KBR-4.0MES (Kyocera) |    |          |  |  |  |  |  |

Fig. 3 Oscillation stable time

Fig. 4 RC oscillation

Fig. 5 Serial input/output timing

Fig. 7 INT0, INT1, INT2, INT3, INT4, INT5, PIN1, RES input timing

Fig. 8 Comparator response Trs timing

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 2001. Specifications and information herein are subject to change without notice.