## LC6520C, 6522C, LC6520H, 6522H

Single-Chip 4-Bit Microcomputers for Medium/Large-Scale Control-Oriented Applications

The LC6520C/H are single-chip 4-bit microcomputers that contain a 4K-byte ROM, 1K-bit RAM, have 42 pins, and are fabricated using CMOS process technology. Besides 8 input/output common ports of 32 pins and an input port of 4 pins, the LC6520C/H have specific ports that are used to provide the interrupt function, 4-bit/8-bit serial input/output function, and burst pulse output function. All output ports are of the open drain type with a withstand voltage of 15 V and a drive current of 20 mA and have the option of containing a pull-up resistance bitwise.

The LC6520C/H are the same as our LC6500 series in the basic architecture of the CPU and the instruction set, but are made more powerful in the stack level and the cycle time.

The LC6522C/H are the same as the LC6520C/H, except that they contain a 2k-byte ROM, 512-bit RAM.

#### **Features**

- Instruction set with 80 instructions (Common to the LC6500 series)

- ROM/RAM

- : 4096 bytes/1024 bits (LC6520C/H)

- : 2048 bytes/512 bits (LC6522C/H)

- Instruction cycle time:  $6 \mu s$  (C version,  $V_{DD} = 3 \text{ to } 5.5 \text{V}$ )

2.77  $\mu$ s (C version,  $V_{DD} = 4 \text{ to } 5.5 \text{V}$ )

9.92  $\mu$ s (H version, V<sub>DD</sub> = 4.5 to 5.5V)

- Serial input/output interface x 1 (4 bits/8 bits program-selectable)

- I/O ports

Input port:

4 pins

Input/output common ports: 32 pins

Input input/output withstand voltage: 15 V max (all input input/output ports)

Output current:

20 mA max (all output ports)

Pull-up resistance:

Output level during reset:

May be contained bitwise by option. (All output ports)

For ports C, D, output (H or L) during reset may be specified portwise by option.

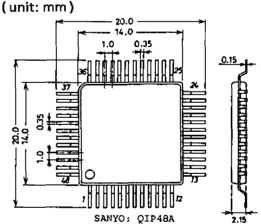

Package Dimensions 3025B-D42SIC (unit: mm)

SANYO: DIP42S

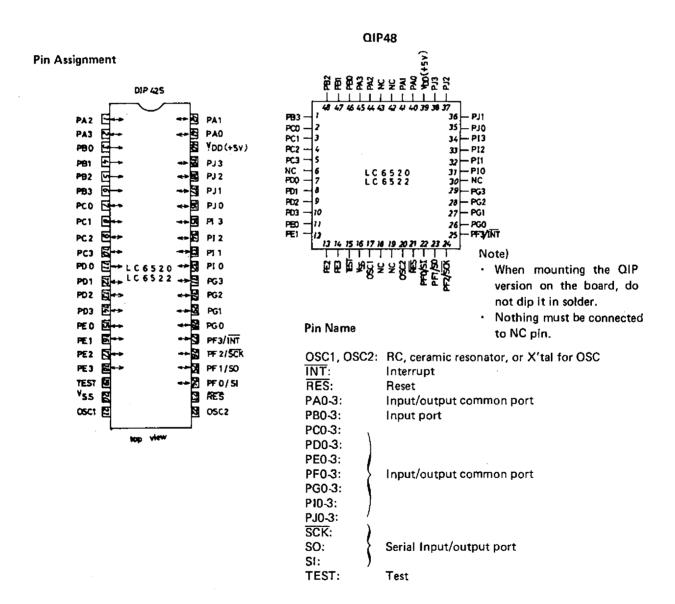

## Package Dimensions 3052A-Q48AIC

- Interrupt function Timer interrupt: 1

- INT pin or serial I/O interrupt: 1

- Stack level: 8 levels (common with interrupt) Timer: 4-bit prescaler + 8-bit programmable timer

- Burst pulse (64 x cycle time, duty 50%) output function

- Oscillator option

Circuit mode: Ceramic mode, RC mode, external clock mode (200 kHz to 4.2 MHz)

(Xtal OSC constants are being checked.)

Predivider option: 1/1, 1/3, 1/4

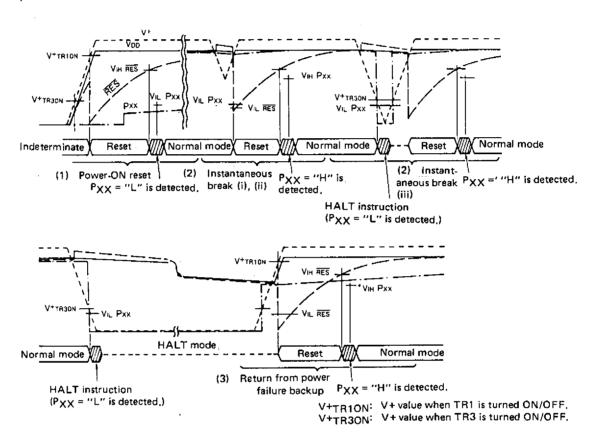

- Standby function: Standby function provided by the HALT instruction

- Supply Voltage: 3 to 5.5 V (C version) 4.5 to 5.5 V (H version) • Package: DIP42 shrink type, QIP48

## Pin Description

| Pin Name                                                                 | Pins | 1/0          | Functions                                                                                                                                                                                                                                                                                                                                                                                                          | Options                                                                                                                                                                                     | <b>During Reset</b>                                                         |

|--------------------------------------------------------------------------|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| V <sub>DD</sub><br>Vss                                                   | 1 1  | ,            | Power supply                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                             |                                                                             |

| OSC1                                                                     | 1    | Input        | <ul> <li>Pin for externally connecting R,</li> <li>C or a ceramic resonator for<br/>system clock generation</li> </ul>                                                                                                                                                                                                                                                                                             | <ul><li>(1) External clock input</li><li>(2) 2-pin RC OSC</li><li>(3) 2-pin ceramic</li></ul>                                                                                               |                                                                             |

| OSC2                                                                     | 1    | Output       | For the external clock mode, the OSC2 pin is open.                                                                                                                                                                                                                                                                                                                                                                 | resonator OSC (4) Predivider option 1. No. predivider 2. 1/3 predivider 3. 1/4 predivider                                                                                                   |                                                                             |

| PAO<br>PA1<br>PA2<br>PA3                                                 | 4    | Input/output | <ul> <li>Input/output common port A0 to 3.</li> <li>4-bit input (IP instruction)</li> <li>4-bit output (OP instruction)</li> <li>Single-bit decision (BP, BNP instructions)</li> <li>Single-bit set/reset (SPB, RPB instructions)</li> <li>Standby is controlled by the PA3 (or PA0 to 3).</li> <li>The PA3 (or PA0 to 3) pin must be free from chattering during the HALT instruction execution cycle.</li> </ul> | (1) Open drain type output (2) With pull-up resistance (1), (2): Specified bit by bit.                                                                                                      | • "H" output<br>(Output Nch<br>transistor<br>OFF)                           |

| PB <sub>0</sub><br>PB <sub>1</sub><br>PB <sub>2</sub><br>PB <sub>3</sub> | 4    | Input        | <ul> <li>Input Port B<sub>0</sub> to 3</li> <li>4-bit input (IP instruction)</li> <li>Single-bit decision (BP, BNP instructions)</li> </ul>                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |                                                                             |

| PC <sub>0</sub><br>PC <sub>1</sub><br>PC <sub>2</sub><br>PC <sub>3</sub> | 4    | Input/output | <ul> <li>Input/output common port Co to 3.         The functions are the same as for the PAo to 3. (Note)         Output ("H" or "L") during reset may be specified by option.     </li> <li>(Note) No standby control function is provided.</li> </ul>                                                                                                                                                            | (1) Open drain type output (2) With pull-up resistance (3) Output during reset: "H" (4) Output during reset: "L"  (1), (2): Specified bit by bit. (3), (4): Specified in a group of 4 bits. | <ul><li>"H" output</li><li>"L" output</li><li>(Option-selectable)</li></ul> |

| PD <sub>0</sub><br>PD <sub>1</sub><br>PD <sub>2</sub><br>PD <sub>3</sub> | 4    | Input/output | <ul> <li>Input/output common port D<sub>0</sub> to<br/>3         The functions, options are the same as for the PC<sub>0</sub> to 3.     </li> </ul>                                                                                                                                                                                                                                                               | Same as for the PC <sub>0</sub> to 3.                                                                                                                                                       | Same as for the PC <sub>0</sub> to 3.                                       |

| PE <sub>0</sub><br>PE <sub>1</sub><br>PE <sub>2</sub><br>PE <sub>3</sub> | 4    | Input/output | <ul> <li>Input/output common port Eq to 3</li> <li>4-bit input (IP instruction)</li> <li>4-bit output (OP instruction)</li> <li>Single-bit decision (BP, BNP instructions)</li> <li>Single-bit set/reset (SPB, RPB instructions)</li> <li>PEq: With burst pulse (64Tcyc) output function</li> </ul>                                                                                                                | (1) Open drain type output (2) With pull-up resistance (1), (2): Specified bit by bit.                                                                                                      | • "H" output<br>(Output Nch<br>transistor<br>OFF)                           |

Continued on next page.

## Continued from preceding page.

| Pin Name                                                                                   | Pins | I/O          | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Options                               | During Reset                                                                     |

|--------------------------------------------------------------------------------------------|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|

| PF <sub>0</sub> /SI<br>PF <sub>1</sub> /SO<br>PF <sub>2</sub> /SCK<br>PF <sub>3</sub> /INT | 4    | Input/output | <ul> <li>Input/output port F0 to 3         The functions, options are the same as for the PE0 to 3. However, no burst pulse output function is provided.     <li>PF0 to 3: Also used for serial interface, INT input. Programselectable.</li> <li>4 bits/8 bits of serial input/output: Program-selectable</li> <li>Serial input port</li> <li>SO: Serial output port</li> <li>SCK: Serial clock input/output</li> <li>INT: Interrupt request input</li> </li></ul> | Same as for the PE <sub>0</sub> to 3. | Same as for the PE <sub>0</sub> to 3. Serial port: Disable Interrupt source: INT |

| PG <sub>0</sub><br>PG <sub>1</sub><br>PG <sub>2</sub><br>PG <sub>3</sub>                   | 4    | Input/output | <ul> <li>Input/output common port Go to<br/>3         The functions, options are the same as for the PEO to 3.     </li> <li>However, no burst pulse output function is provided.</li> </ul>                                                                                                                                                                                                                                                                        | Same as for the PE <sub>0</sub> to 3. | Same as for the PEO to 3.                                                        |

| P10<br>P11<br>P12<br>P13                                                                   | 4    | Input/output | • Input/output common port 10 to 3 The functions, options are the same as for the PG0 to 3.                                                                                                                                                                                                                                                                                                                                                                         | Same as for the PG <sub>0</sub> to 3. | Same as for the PG <sub>0</sub> to 3.                                            |

| PJ2<br>PJ1<br>PJ0                                                                          | 4    | Input/output | Input/output common port J <sub>0</sub> to 3     The functions, options are the same as for the PG <sub>0</sub> to 3.                                                                                                                                                                                                                                                                                                                                               | Same as for the PG <sub>0</sub> to 3. | Same as for the PG <sub>0</sub> to 3.                                            |

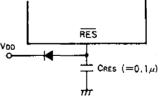

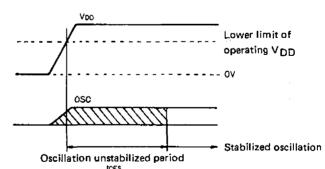

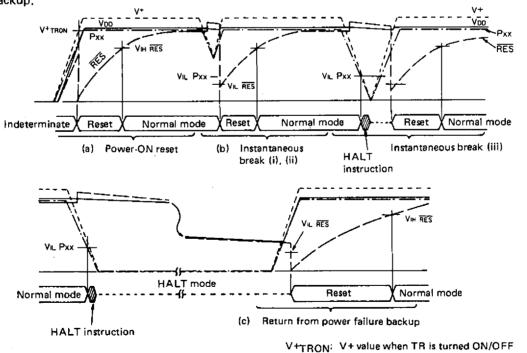

| RES                                                                                        | 1    | Input        | <ul> <li>System reset input</li> <li>For power-up reset, C is connected externally.</li> <li>For reset start, "L" level is applied for 4 clock cycles or more.</li> </ul>                                                                                                                                                                                                                                                                                           |                                       |                                                                                  |

| TEST                                                                                       | 1    | Input        | LSI test pin     Normally connected to VSS                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |                                                                                  |

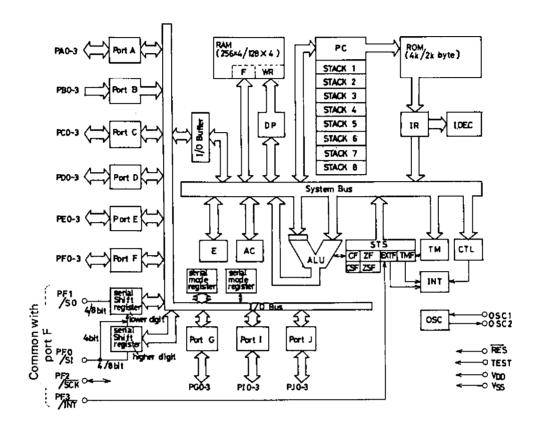

## System Block Diagram

RAM: Data memory F: Flag PC: INT: WR: Working register AC: Accumulator IR: Arithmetic and logic unit ALU: Data pointer DP: E: E register Control register CTL: OSC: Oscillator TM: Timer STS: Status register

ROM: Program memory

PC: Program counter

INT: Interrupt control

IR: Instruction register

I.DEC: Instruction decoder

CF, CSF: Carry flag, carry save flag

ZF, ZSF: Zero flag, zero save flag

EXTF: External interrupt request flag

TMF: Internal interrupt request flag

### **Oscillator Circuit Option**

| <b>Option Name</b>          | Circuit                  | Conditions, etc.    |

|-----------------------------|--------------------------|---------------------|

| 1. External Clock           | 7 0sc,                   | Input: Schmitt type |

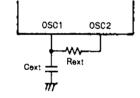

| 2. 2-pin RC OSC             | Cext OSC1  W SOSC2  Rest | Input: Schmitt type |

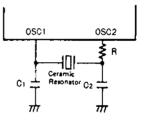

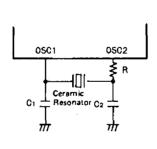

| 3. Ceramic<br>Resonator OSC | Coramic resonator OSC 2  |                     |

## • Predivider Option

| Option Name       | Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Conditions, etc.                                                                                                                                                                                                                                                                                 |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. No predivider  | OSC circuit<br>Timing<br>generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <ul> <li>Applicable to all of 3 OSC options.</li> <li>The OSC frequency, external clock do not exceed 1444 kHz. (LC6520C, LC6522C)</li> <li>The OSC frequency, external clock do not exceed 4330 kHz. (LC6520H, LC6522H)</li> <li>Refer to Table of OSC, Predivider Option (Table 2).</li> </ul> |

| 2. 1/3 predivider | tosc 1/3 tos | <ul> <li>Applicable to only 2 options of external clock, ceramic resonator OSC.</li> <li>The OSC frequency, external clock do not exceed 4330 kHz.</li> <li>Refer to Table of OSC, Predivider Option (Table-2).</li> </ul>                                                                       |

| 3. 1/4 predivider | fosc 1/4 tosc burning to burning  | <ul> <li>Applicable to only 2 options of external clock, ceramic resonator OSC.</li> <li>The OSC frequency, external clock do not exceed 4330 kHz.</li> <li>Refer to table of OSC, Predivider Option (Table 2).</li> </ul>                                                                       |

Options of Ports C, D Output Level during Reset

For input/output common ports C, D, either of the following two output levels may be selected in a group of 4 bits during reset by option.

| Option Name                       | Conditions, etc.            |

|-----------------------------------|-----------------------------|

| 1. Output during reset: "H" level | All of 4 bits of ports C, D |

| 2. Output during reset: "L" level | All of 4 bits of ports C, D |

## Options of Port Output Configuration

For each input/output-common port, either of the following two output configurations may be selected by option (bitwise).

| Option Name                       | Circuit | Conditions, etc. |

|-----------------------------------|---------|------------------|

| Open drain type     output        |         |                  |

| 2. Output with pull-up resistance |         |                  |

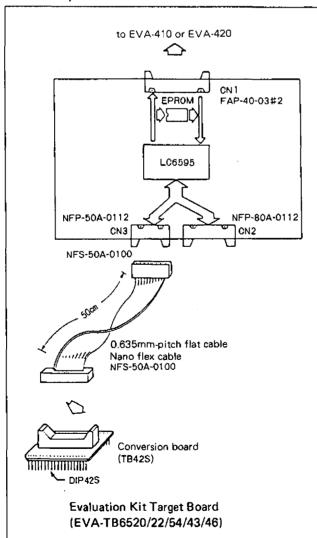

#### **Development Support**

The following are available to support the LC6520, LC6522 program development.

- (1) User's Manual

- "LC6554 Series User's Manual" No. E21B. (Issued in December, 1987)

- (2) Development Tool Manual

For the EVA-410 system, refer to the description of Development Support Tools in "LC6554 Series User's Manual". For the EVA-800 system, refer to "EVA-800-LC6554 Series Development Tool Manual".

- (3) Development Tools

- 1) For program development (EVA-410 system)

- i. MS-DOS host computer system (Note 1)

- ii. MS-DOS base cross assembler (LC65S.EXE)

- iii. Evaluation kit (EVA-410C or EVA-420)

- iv. Evaluation kit target board (EVA-TB6520/22/54/43/46), evaluation chip (LC6595)

- 2) For program evaluation

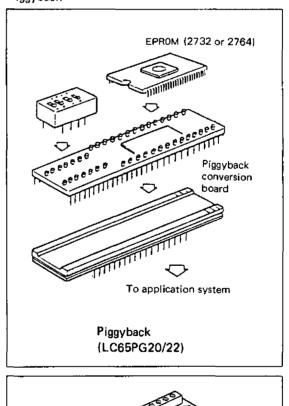

- i. Piggyback (LC65PG20/22), with socket for conversion of number of piggyback pins

Note. For notes on program evaluation, do not fail to refer to "5-3-1. Notes on when evaluating programs for the LC6520/22" in "LC6554 Series User's Manual".

## Appearance of Application Development Tools

EVA-410 System

#### Piggyback

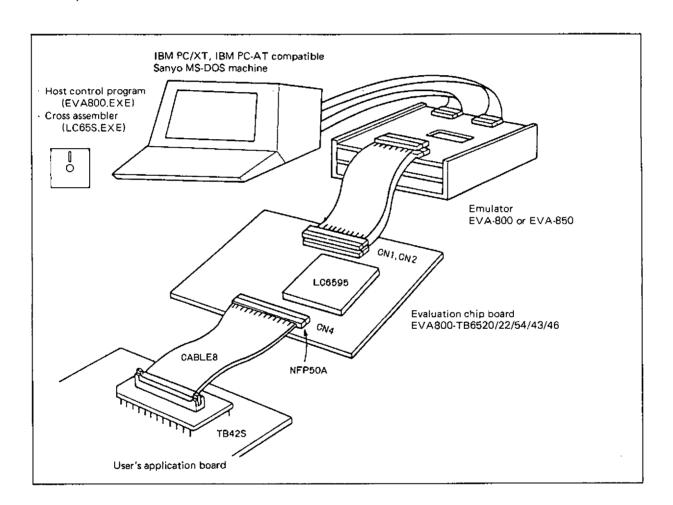

- 3) For program development (EVA-800 system)

- i. IBM PC/XT, IBM PC-AT (Note 1) compatible Sanyo MS-DOS machine

- ii. Cross assembler .....MS-DOS base cross assembler: (LC65S.EXE)

- iii. Host control program: (EVA800.EXE)

- iv. Evaluation chip: LC6595

- v. Emulator : EVA-800 or EVA-850 control board and evaluation chip board (Note 2)

### **Appearance of Development Support System**

## EVA-800 System

(Note 1) IBM PC/XT, IBM PC-AT: Products of IBM Corporation MS-DOS: Trademark of Microsoft Corporation

(Note 2) The EVA-800 is a general term for emulator. A suffix (A, B ...) is added at the end of EVA-800 as the EVA-800 is improved to be a newer version. Do not use the EVA-800 with no suffix added.

## Main Specifications of the LC6520C, 6522C

| Absolute Maximum Ratings/Ta    | = 25°C, V <sub>SS</sub> | s = 0V                                                         |                         | unit                |      |

|--------------------------------|-------------------------|----------------------------------------------------------------|-------------------------|---------------------|------|

| Maximum Supply Voltage         | V <sub>DD</sub> max     |                                                                | -0.3 to +7.0            | V                   |      |

| Output Voltage                 | Vo                      | OSC2 Allowable up to volta                                     | ge generated            | V                   |      |

| Input Voltage                  | V <sub>I</sub> (1)      |                                                                | to V <sub>DD</sub> +0.3 | V                   |      |

|                                | V <sub>1</sub> (2)      |                                                                | to VDD+0.3              | V                   |      |

|                                | V <sub>1</sub> (3)      |                                                                | -0.3 to +15             | v                   |      |

| Input/Output Voltage           | V <sub>10</sub> (1)     |                                                                | -0.3 to +15             | v                   |      |

| input Output Voltage           |                         |                                                                | to V <sub>DD</sub> +0.3 | v                   |      |

| Baals Outsut Course            | V <sub>10</sub> (2)     |                                                                |                         |                     |      |

| Peak Output Current            | IOP                     | Input/output port                                              | -2 to +20               | mA                  |      |

| Average Output Current         | IOA                     | Input/output port:                                             | -2 to +20               | mΑ                  |      |

|                                |                         | Per pin over the period of 100 msec.                           |                         |                     |      |

|                                | $\Sigma$ IOA (1)        | Total current of PA0 to 3, PC0 to 3,                           | 30 to +140              | mA                  |      |

|                                |                         | PDo to 3 and PEo to 3 (Note 2)                                 |                         |                     |      |

|                                | $\Sigma I_{OA}$ (2)     | Total current of PF0 to 3, PG0 to 3,                           | -30 to +140             | mΑ                  |      |

|                                | <b>.</b>                | Plo to 3 and PJo to 3, (Note 2)                                |                         |                     |      |

| Allowable Power Dissipation    | Palmax (1)              | DIP package, $T_a = -30 \text{ to } +70^{\circ}\text{C}$       | 600                     | mW                  |      |

| ,                              |                         | QIP package, $T_a = -30 \text{ to } +70^{\circ}\text{C}$       | 400                     | mW                  |      |

| Operating Temperature          | Topr                    | an puckage, 18                                                 | -30 to +70              | °C                  |      |

|                                | •                       |                                                                | -55 to +125             | °Č                  |      |

| Storage Temperature            | $T_{stg}$               |                                                                | -55 (0 +125             | C                   |      |

| Allowable Operating Conditions | ·/T = 20 +              | o +70°C, V <sub>SS</sub> = 0V, V <sub>DD</sub> = 3.0 to 5.5V   | / min                   | typ max             | unit |

|                                |                         |                                                                |                         | • •                 |      |

| Operating Supply Voltage       | $V_{DD}$                | V <sub>DD</sub>                                                | 3.0                     | 5,5                 | V    |

| Standby Supply Voltage         | V <sub>st</sub>         | V <sub>DD</sub> : RAM, resister hold (Note 3)                  | 1.8                     | 5.5                 | ٧    |

| "H"-Level Input Voltage        | V <sub>IH</sub> (1)     | Port of OD type, PB <sub>0</sub> to 3:<br>Output Nch Tr OFF    | 0.7V <sub>DD</sub>      | +13.5               | V    |

|                                | V <sub>IH</sub> (2)     | Port of PU type: Output Nch Tr OFF                             | 0.7V <sub>DD</sub>      | VDD                 | V    |

|                                | ViH (3)                 | SCK, SI, INT of OD type:                                       | 0.8V <sub>DD</sub>      | +13.5               | V    |

|                                |                         | Output Nch Tr OFF                                              |                         |                     |      |

|                                | V <sub>IH</sub> (4)     | SCK, SI, INT of PU type:                                       | 0.8∨ <sub>DD</sub>      | $V_{DD}$            | V    |

|                                | 1111 ( 17               | Output Nch Tr OFF                                              | on ob                   | 100                 | -    |

|                                | V <sub>IH</sub> (5)     | RES                                                            | 0.8V <sub>DD</sub>      | $V_{DD}$            | V    |

|                                | VIH (6)                 | OSC1: External clock mode                                      | 0.8V <sub>DD</sub>      |                     | v    |

|                                | VIH (0)                 | OSCI, External clock mode                                      | 0.0 V DD                | VDD                 | V    |

|                                |                         |                                                                | min                     | typ max             | unit |

| "I " Lovel Input Voltage       | Mr. (1)                 | PORT: Van a 4 to E EV                                          |                         | • •                 | V    |

| "L"-Level Input Voltage        | V <sub>IL</sub> (1)     | PORT: V <sub>DD</sub> = 4 to 5.5V,                             | $v_{SS}$                | 0.3V <sub>DD</sub>  | V    |

|                                |                         | Output Nch Tr OFF                                              |                         | 0.051/              |      |

|                                | V <sub>IL</sub> (2)     | PORT: Output Nch Tr OFF                                        | Vss                     | 0.25V <sub>DD</sub> | V    |

|                                | V;∟ (3)                 | $\overline{INT}$ , $\overline{SCK}$ , SI: $V_{DD} = 4$ to 5.5V | $v_{SS}$                | 0.25V <sub>DD</sub> | V    |

|                                |                         | Output Nch Tr OFF                                              |                         |                     |      |

|                                | V₁L (4)                 | INT, SCK, SI: Output Nch Tr OFF                                | $v_{SS}$                | 0.2V <sub>DD</sub>  | V    |

|                                | VIL (5)                 | OSC1: $V_{DD} = 4 \text{ to } 5.5V$ ,                          | VSS                     | 0.25V <sub>DD</sub> | V    |

|                                |                         | External clock mode                                            |                         |                     |      |

|                                | V1L (6)                 | OSC1: External clock mode                                      | ٧ss                     | 0.2∨ <sub>DD</sub>  | V    |

|                                | VIL (7)                 | TEST: $V_{DD} = 4 \text{ to } 5.5V$                            | VSS                     | 0.3V <sub>DD</sub>  | V    |

|                                | VIL (8)                 | TEST                                                           | VSS                     | 0.25V <sub>DD</sub> | V    |

|                                | V <sub>1</sub> L (9)    | RES: V <sub>DD</sub> = 4 to 5.5V                               | VSS                     | 0.25V <sub>DD</sub> | v    |

|                                | VIL (10)                | RES                                                            | VSS                     | 0.2V <sub>DD</sub>  | v    |

| Operating Frequency            |                         | 1120                                                           | * 55                    | See Table 2.        | •    |

|                                | fop<br>(Tala)           | $(V_{DD} = 4.0 \text{ to } 5.5 \text{V})$                      | (2.77)                  | (20)                | luch |

| (Cycle Time)                   | (T <sub>cyc</sub> )     | (VDD - 4.0 (0 5.5V)                                            |                         |                     | (μs) |

|                                |                         |                                                                | (6.0)                   | (20)                | (µs) |

|                                |                         |                                                                |                         |                     |      |

| Continued from preceding page  | <b>.</b>             |                                                                            |            |                    |             |            |

|--------------------------------|----------------------|----------------------------------------------------------------------------|------------|--------------------|-------------|------------|

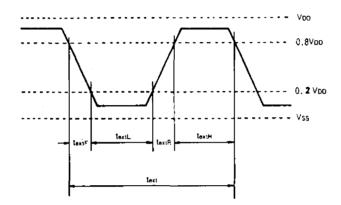

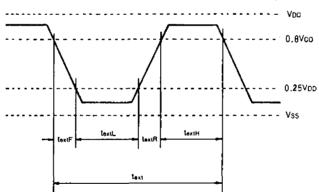

| External Clock Conditions (Wh  | en the extern        | al clock or 2-pin RC OSC option is selected                                | d) min     | typ                | max         | unit       |

| Frequency                      | fext                 | OSC1: Fig. 1                                                               | •          | See Tabl           |             |            |

| Pulse Width                    | [textH               | OSC1: V <sub>DD</sub> = 4 to 5.5V, Fig. 1                                  | 90         |                    |             | ns         |

|                                | textL                | OSC1: Fig. 1                                                               | 180        |                    |             | ns         |

| Rise/Fall Time                 | textR,               | OSC1: $V_{DD} = 4 \text{ to } 5.5 \text{V}$ , Fig. 1                       |            |                    | 30          | ns         |

|                                | textF                | OSC1: Fig. 1                                                               |            |                    | 100         | ns         |

|                                |                      |                                                                            |            |                    |             |            |

| Oscillation Guaranteed Cons    | stants               |                                                                            |            |                    |             | _          |

| 2-Pin RC Oscillation           | C <sub>ext</sub>     | OSC1, OSC2: $V_{DD} = 4 \text{ to } 5.5 \text{V}$ , Fig. 2                 |            | 220±5%             |             | рF         |

|                                | $R_{ext}$            | OSC1, OSC2: $V_{DD} = 4 \text{ to } 5.5 \text{V}$ , Fig. 2                 |            | 6.8±1%             |             | kΩ         |

|                                | C <sub>ext</sub>     | OSC1, OSC2: Fig. 2                                                         | 2          | 270±5%             |             | pF         |

|                                | Rext                 | OSC1, OSC2: Fig. 2                                                         |            | 15±1%              |             | k $\Omega$ |

| Ceramic Resonator Oscillati    | on                   | Fig. 3                                                                     |            | See Tab            | le 1.       |            |

| Electrical Characteristics/T - | 20 to ±70°(          | C, V <sub>SS</sub> = 0V, V <sub>DD</sub> = 3.0 to 5.5V                     | min        | tun                | may         | · unit     |

| "H"-Level Input Current        |                      |                                                                            | mn         | typ                | max<br>+5.0 |            |

| - Level input Current          | I <sub>I</sub> H (1) | Port of open drain type, PB0 to 3:                                         |            |                    | ₹5.0        | μΑ         |

|                                |                      | Output Nch Tr OFF, Including OFF                                           |            |                    |             |            |

|                                |                      | leakage current of Nch Tr,                                                 |            |                    |             |            |

|                                | L (0)                | $V_{1N} = +13.5V$                                                          |            |                    |             |            |

| W. W. L                        | IH (2)               | OSC1: External clock mode, VIN = VDD                                       | 1.0        |                    | +1.0        | μΑ         |

| "L"-Level Input Current        | I <sub>IL</sub> (1)  | Port of open drain type, PB <sub>0</sub> to 3:                             | -1.0       |                    |             | μΑ         |

|                                |                      | Output Nch Tr OFF, VIN = VSS                                               |            |                    |             | _          |

|                                | l∤∟ (2)              | Port with pull-up resistance:                                              | 1.3        | -0.35              |             | mΑ         |

|                                |                      | Output Nch Tr OFF, VIN = VSS                                               |            |                    |             |            |

|                                | Iլ <u>୮</u> (3)      | RES: VIN = VSS                                                             | <b>–45</b> | -10                |             | μΑ         |

|                                | l <sub>IL</sub> (4)  | OSC1: External clock mode,                                                 | -1.0       |                    |             | μΑ         |

|                                |                      | $V_{IN} = V_{SS}$                                                          |            |                    |             |            |

| "H"-Level Output Voltage       | VoH (1)              |                                                                            | J—1.2      |                    |             | V          |

|                                |                      | $V_{DD} = 4 \text{ to } 5.5 \text{V}, I_{OH} = -50 \mu\text{A}$            |            |                    |             |            |

|                                | Vo <sub>H</sub> (2)  |                                                                            | O-0.5      |                    |             | V          |

|                                |                      | $I_{OH} = -10 \mu A$                                                       |            |                    |             |            |

| "L"-Level Output Voltage       | V <sub>OL</sub> (1)  | Port: $V_{DD} = 4$ to 5.5V, $I_{OL} = 10$ mA                               |            |                    | 1.5         | V          |

|                                | V <sub>OL</sub> (2)  | Port: $IOL = 1 \text{ mA}$ , When $IOL$ of                                 |            |                    | 0.5         | V          |

|                                |                      | each port is 1 mA or less.                                                 |            |                    |             |            |

| Hysteresis Voltage             | $v_{Hys}$            | RES, INT, SCK, SI,                                                         | (          | 0.1V <sub>DD</sub> |             | V          |

|                                |                      | OSC1 of Schmitt type (Note 6)                                              |            |                    |             |            |

| Current Dissipation            |                      | Operation mode, Output Nch Tr OFF, Po                                      | rt = Vn    | n                  |             |            |

| 2-Pin RC Oscillation           | IDDOR (1)            | V <sub>DD</sub> : V <sub>DD</sub> = 4 to 5.5V, Fig. 2                      |            | 2                  | 5           | mΑ         |

| 2111110 03011011011            | 1000F (1)            | f <sub>osc</sub> = 750 kHz typ                                             |            | -                  | J           | 107        |

|                                | Innon (2)            | $V_{DD}$ : Fig. 2 $f_{OSC}$ = 350 kHz typ                                  |            | 1.5                | 4.5         | mΑ         |

| Ceramic Resonator              |                      | V <sub>DD</sub> : Fig. 3 V <sub>DD</sub> = 4 to 5.5V, 4MHz,                |            | 5                  | 10          | mΑ         |

| Oscillation                    | יטטטף ייט            | 1/3 predivider                                                             |            |                    | 10          | ши         |

|                                | Innon (4)            | $V_{DD}$ : Fig. 3 $V_{DD} = 4$ to 5.5V, 4MHz,                              |            | 5                  | 10          | mΑ         |

|                                | ייי ייטטטריי         | 1/4 predivider                                                             |            | •                  |             | *****      |

|                                | IDDOR (5)            | V <sub>DD</sub> : Fig. 3 400kHz                                            |            | 1,5                | 4           | mΑ         |

|                                |                      | V <sub>DD</sub> : V <sub>DD</sub> = 4 to 5.5V, Fig. 3 800kHz               |            | 2                  | 5           | mA         |

| External Clock                 |                      | V <sub>DD</sub> : 200 kHz to 667 kHz,                                      |            | 2                  | 5           | mΑ         |

| External Glock                 | ייו אטטטי            | 1/1 predivider                                                             |            | -                  | 3           | W/A        |

|                                |                      | 600 kHz to 2000 kHz, 1/3 predivider                                        |            |                    |             |            |

|                                |                      | 800 kHz to 2667 kHz, 1/4 predivider                                        |            |                    |             |            |

|                                | Innan (0)            |                                                                            |            | 3                  | 10          | ^          |

|                                | 1000P (8)            | V <sub>DD</sub> : V <sub>DD</sub> = 4 to 5.5V,                             |            | J                  | 10          | mA         |

|                                |                      | 200 kHz to 1444 kHz, 1/1 predivider<br>600 kHz to 4330 kHz, 1/3 predivider |            |                    |             |            |

|                                |                      |                                                                            |            |                    |             |            |

| Standby Mode                   | Inna                 | 800 kHz to 4330 kHz, 1/4 predivider                                        |            | 0.05               | 10          |            |

| Standby Mode                   | <sup>1</sup> DDSt    | V <sub>DD</sub> : V <sub>DD</sub> = 5.5V Output Nch Tr OFF,                | •          | 0.05               | 10          | μΑ         |

|                                |                      | $V_{DD}$ : $V_{DD} = 3V$ $V_{DD}$                                          |            | 0.025              | 5           | μΑ         |

| Continued from preceding                                              |                        |                                                                                                              |                    |                                            |                    | ••         |

|-----------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------|--------------------|------------|

| Oscillation Characteristics<br>Ceramic Resonator Os                   |                        |                                                                                                              | min                | typ                                        | max                | unit       |

| Oscillation Frequence                                                 |                        | OSC1, OSC2: Fig. 3 $f_0 = 400 \text{ kHz}$<br>OSC1, OSC2: $V_{DD} = 4 \text{ to } 5.5 \text{V}$ ,            | 392<br>784         | 400<br>800                                 | 408<br>816         | kHz<br>kHz |

|                                                                       |                        | Fig. 3 $f_0$ = 800 kHz<br>OSC1, OSC2: $V_{DD}$ = 4 to 5.5V,<br>Fig. 3 $f_0$ = 3 MHz, 1/3 predivider,         | 2940               | 3000                                       | 3060               | kHz        |

|                                                                       |                        | 1/4 predivider OSC1, OSC2: $V_{DD} = 4$ to 5.5V, Fig. 3 f <sub>O</sub> = 4 MHz, 1/3 predivider,              | 3920               | 4000                                       | 4080               | kHz        |

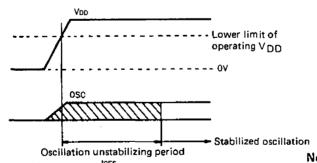

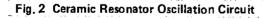

| Oscillation Stabilizin                                                | ig <sup>t</sup> CFS    | 1/4 predivider<br>Fig. 4 f <sub>0</sub> = 400 kHz                                                            |                    |                                            | 10                 | ms         |

| Period                                                                | 3 3, 3                 | $V_{DD} = 4$ to 5.5V, Fig. 4<br>f <sub>0</sub> = 4 MHz, 3 MHz, 800 kHz                                       |                    |                                            | 10                 | ms         |

| 2-Pin RC Oscillation                                                  |                        |                                                                                                              |                    |                                            |                    |            |

| Oscillation Frequenc                                                  |                        | OSC1, OSC2: $V_{DD}$ = 4 to 5.5V, Fig. 2, $C_{ext}$ = 220 pF±5%, $R_{ext}$ = 6.8 k $\Omega$ ±1%              |                    | 750                                        | 1156               | kHz        |

|                                                                       | fMOSC (2)              | OSC1, OSC2: Fig. 2,<br>$C_{ext} = 270 \text{ pF} \pm 5\%$ , $R_{ext} = 15 \text{ k}\Omega \pm 1\%$           | 222                | 350                                        | 609                | kНz        |

| Pull-up Resistance                                                    |                        | · · · · · · · · · · · · · · · · · · ·                                                                        |                    |                                            |                    |            |

| I/O Port Pull-up Resist                                               | F F                    | Port of PU type: $V_{DD} = 5V$                                                                               |                    | 14                                         |                    | k $\Omega$ |

| External Reset Character                                              | istics                 |                                                                                                              |                    | _                                          |                    |            |

| "H"-Level Threshold                                                   | V <sub>t</sub> H       |                                                                                                              | 0.5V <sub>DD</sub> |                                            |                    | V          |

| "L"-Level Threshold                                                   | V <sub>t</sub> L       |                                                                                                              | 0.2∨ <sub>DD</sub> |                                            | ).5∨ <sub>DD</sub> | V          |

| Reset Time                                                            | TRST                   | 6 - 1 MUs. Other than pine to be                                                                             |                    | See Fi                                     | g. 5.              | ٥E         |

| Pin Capacitance                                                       | CP                     | f = 1 MHz, Other than pins to be tested, V <sub>IN</sub> = V <sub>SS</sub>                                   |                    | 10                                         |                    | pF         |

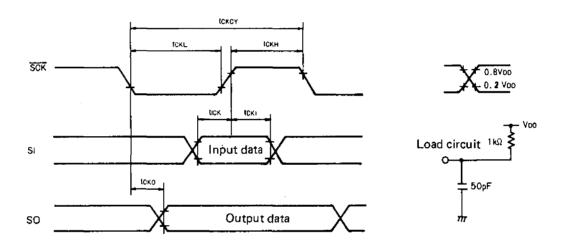

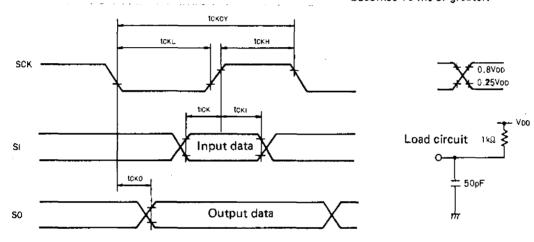

| Serial Clock                                                          |                        |                                                                                                              |                    |                                            |                    |            |

| Input Clock Cycle Ti                                                  |                        | $\overline{SCK}$ : V <sub>DD</sub> = 4 to 5.5V, Fig. 6                                                       | 3.0<br>12.0        |                                            |                    | μs<br>μs   |

| Output Clock Cycle                                                    | Time tCKCY (2)         | SCK (T <sub>C</sub> YC = 4 x System clock period), Fig. 6                                                    | 64                 | x TCYC                                     | :                  | μs         |

| Input Clock                                                           |                        | SCK: V <sub>DD</sub> = 4 to 5.5V, Fig. 6                                                                     | 1.0                |                                            |                    | μs         |

| ("L"-Level Pulse Wid<br>Output Clock                                  | th<br>tCKL (2)         | SCK<br>SCK, Fig. 6                                                                                           | 4,0<br>32          | × TCYC                                     |                    | μs<br>μs   |

| "L"-Level Pulse Wid                                                   |                        |                                                                                                              | 02                 | ^ '\'                                      | 1                  | ~~         |

| (Input Clock<br>("H"-Level Pulse Wid                                  | tcKH (1)               | SCK: V <sub>DD</sub> = 4 to 5.5V, Fig. 6                                                                     | 1.0<br>4.0         |                                            |                    | μs<br>μs   |

| Output Clock                                                          | tCKH (2)               | SCK: Fig. 6                                                                                                  |                    | × TCYC                                     |                    | μs         |

| "H"-Level Pulse Wid<br>Serial Input                                   |                        | -                                                                                                            |                    |                                            |                    |            |

| Data Setup Time                                                       | tICK                   | SI: Specified for 1 of SCK, Fig. 6                                                                           | 0.5                |                                            |                    | μs         |

| Data Hold Time                                                        | tCKI                   | SI: Specified for 1 of SCK, Fig. 6                                                                           | 0.5                |                                            |                    | μs         |

| Serial Output<br>Output Delay Time                                    | tCKO                   | SO: V <sub>DD</sub> = 4 to 5.5V,<br>Specified for ↓ of SCK,                                                  |                    |                                            | 0.5                | μs         |

|                                                                       |                        | Nch OD only: External 1 kohm,                                                                                |                    |                                            |                    |            |

|                                                                       |                        | external 50 pF, Fig. 6<br>SO                                                                                 |                    |                                            | 2.0                | μs         |

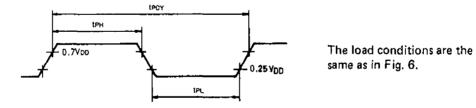

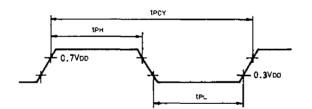

| Pulse Output                                                          |                        |                                                                                                              |                    |                                            |                    |            |

| Period                                                                | tPCY                   | PEO: TCYC = 4 x System clock period, Nch OD only: External 1 kohm,                                           | , 64               | x TCYC                                     | :                  | μs         |

| MIN Lavel Dules Mis                                                   | iale a                 | external 50 pF, Fig. 7                                                                                       | 20                 | T <del>-</del> - 4                         | 00/                |            |

| "H"-Level Pulse Wid                                                   | 1 11                   | PEO:<br>PEO:                                                                                                 |                    | Γ <sub>CYC</sub> ±1<br>Γ <sub>CYC</sub> ∓1 |                    | μs<br>μs   |

|                                                                       | ernally under the osci | llating conditions in Fig. 3, up to the oscillation                                                          | n amplitude (      | generated                                  |                    |            |

| is allowable.  Note 2: Average over the pe Note 3: Operating supply v |                        | held until the standby mode is entered after                                                                 | the execution      | on of the                                  |                    |            |

|                                                                       |                        | rom chattering during the HALT instruction ex                                                                |                    |                                            |                    |            |

| frequency at the ce                                                   |                        | ency. There is a tolerance of approximately 1<br>ominal value presented by the ceramic resonato<br>resonator |                    |                                            |                    |            |

| Note 5: When mounting the                                             | QIP version on the bo  |                                                                                                              | nal clock OS       | C.                                         | :                  |            |

|                                                                       | ••                     | •                                                                                                            |                    |                                            |                    |            |

Fig. 1 External Clock Input Waveform

Fig. 2 2-Pin RC Oscillation Circuit

Fig. 3 Ceramic Resonator Oscillation Circuit

Fig. 4 Oscillation Stabilizing Period

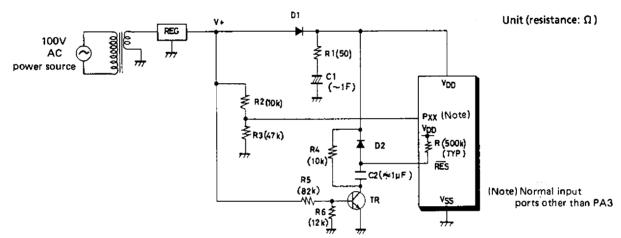

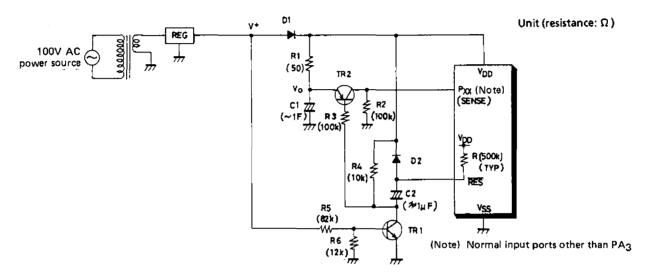

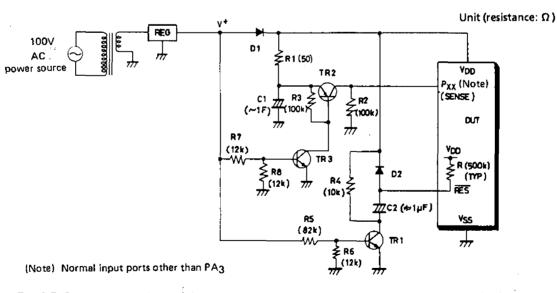

Fig. 5 Reset Circuit

Note 7: When the rise time of the power supply is 0, the reset time becomes 10 ms to 100 ms at  $C_{RES} = 0.1 \,\mu\text{F}$ . If the rise time of the power supply is long, the value of  $C_{RES}$  must be increased so that the reset time becomes 10 ms or greater.

| 4MHz (Murata)  | c 1        | 33pf ± 10% |

|----------------|------------|------------|

| CSA4,00MG      | C2         | 33pf±10%   |

|                | R          | 0Ω         |

| 4MHz (Kyocera) | <b>c</b> 1 | 33PF±10%   |

| KBR4,0MS       | c 2        | 33pf±10%   |

|                | R          | ŋΩ         |

| 3MHz (Murata)  | c 1        | 33pF ± 10% |

| CSA3,00MG      | 0.2        | 33pf±10%   |

|                | Ř          | 0 8        |

| 3MHz (Kyocera) | c 1        | 47pf±10%   |

| KBR3,0MS       | 0.2        | 47pf±10%   |

|                | R          | ΟΩ         |

| 800kHz (Murata)    | c 1 | 220pf±10% |

|--------------------|-----|-----------|

| CSB800D<br>CSB800K | ¢2  | 220pf±10% |

| CSB800K            | Ŕ   | ΟΩ        |

| 800kHz (Kyocera)   | C 1 | 150pf±10% |

| KBR800H            | c2  | 150pf±10% |

|                    | R   | ΟΩ        |

| 400kHz (Murata)    | c 1 | 470pf±10% |

| CSB400P            | C2  | 470pf±10% |

|                    | R   | ΟΩ        |

| 400kHz (Kyocera)   | c 1 | 330pf±10% |

| KBR400B            | c2_ | 330pf±10% |

|                    | R   | ΟΩ        |

Table 1 Constants Guaranteed for Ceramic Resonator Oscillation

Fig. 6 Serial Input/Output Timing

Fig. 7 Pulse Output Timing at Port PE0

| Circuit Configuration                                      | Frequency                                             | Predivider Option<br>(Cycle Time)                                              | V <sub>DD</sub>    | Remarks            |

|------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------|--------------------|--------------------|

| Ceramic Resonator<br>Option                                | 400 kHz                                               | 1/1 (10 μs)                                                                    | 3 to 5.5V          | Unusable with 1/3, |

|                                                            |                                                       | 1/1 (5 μs)                                                                     | 4 to 5.5V          |                    |

|                                                            | 800 kHz                                               | 1/3 (15 μs)                                                                    | 4 to 5.5V          |                    |

|                                                            |                                                       | 1/4 (20 μs)                                                                    | 4 to 5.5V          |                    |

|                                                            | 0.111                                                 | 1/3 (4 μs)                                                                     | 4 to 5.5V          | Unusable with 1/1  |

|                                                            | 3 MHz                                                 | 1/4 (5.33 μs)                                                                  | 4 to 5.5V          | predivider         |

|                                                            | 4 MHz                                                 | 1/3 (3 μs)                                                                     | 4 to 5.5V          | Unusable with 1/1  |

|                                                            |                                                       | 1/4 (4 μs)                                                                     | 4 to 5.5V          | predivider         |

|                                                            | 200 to 667 kHz                                        | 1/1 (20 to 6 μ <sub>s</sub> )                                                  | 3 to 5.5V          |                    |

| External Clock Option                                      | 600 to 2000 kHz                                       | 1/3 (20 to 6 µs)                                                               | 3 to 5.5V          |                    |

| or External Clock                                          | 800 to 2667 kHz                                       | 1/4 (20 to 6 µs)                                                               | 3 to 5.5V          |                    |

| Drive by RC OSC                                            | 200 to 1444 kHz                                       | 1/1 (20 to 2.77 μs)                                                            | 4 to 5.5V          |                    |

| Option                                                     | 600 to 4330 kHz                                       | 1/3 (20 to 2.77 μs)                                                            | 4 to 5.5∨          |                    |

|                                                            | 800 to 4330 kHz                                       | 1/4 (20 to 3.70 μs)                                                            | 4 to 5.5V          |                    |

| External Clock Drive<br>by ceramic resonator<br>OSC Option |                                                       | drive is impossible. When<br>clock option or RC OSC                            |                    | al clock drive,    |

| RC OSC Option                                              | $V_{DD} = 3 \text{ to } 5.5V$ ). If used with other t | ivider, recommended con<br>han recommended consta<br>nge must be the same as f | ants, the predivic | der option,        |

Table 2 Table of Oscillation, Predivider Option (All selectable combinations are shown. Do not use any other combinations than shown above.)

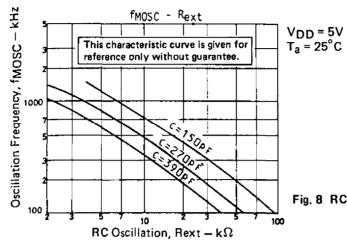

## RC Oscillation Characteristic of the LC6520C, 6522C

Fig. 8 shows the RC oscillation characteristic of the LC6520C, 6522C. For the variation range of RC OSC frequency of the LC6520C, 6522C, the following are guaranteed at the external constants only shown below.

If any other constants than specified above are used, the range of Rext = 4 kohms to 23 kohms, Cext = 150 pF to 400 pF must be observed. (See Fig. 8.)

Note 8: The oscillation frequency at  $V_{DD}$  = 5.0V,  $T_a$  = 25°C must be in the range of 350 kHz to 750 kHz. Note 9: The oscillation frequency at  $V_{DD}$  = 4.0V to 5.5V,  $T_a$  = -30°C to +70°C and  $V_{DD}$  = 3.0V to 5.5V,  $T_a$  = -30°C to +70°C must be within the operation clock frequency range. (See Table 2.)

Fig. 8 RC Oscillation Frequency Data (Typ.)

# Main Specifications of the LC6520H, 6522H

| Absolute Maximum Ratings/Ta                                     |                                          |                                                                                                                      |                           | unit                |      |

|-----------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------|------|

| Maximum Supply Voltage                                          | VDD max                                  |                                                                                                                      | -0.3 to +7.0              | V                   |      |

| Output Voltage                                                  | Vo                                       | OSC2 Allowable up to volt                                                                                            |                           | V                   |      |

| Input Voltage                                                   | V <sub>1</sub> (1)                       |                                                                                                                      | to VDD+0.3                | V                   |      |

|                                                                 | V; (2)                                   |                                                                                                                      | 3 to VDD+0.3              | V                   |      |

|                                                                 | V <sub>1</sub> (3)                       | PB0 to 3                                                                                                             | -0.3 to +15               | V                   |      |

| Input/Output Voltage                                            | V <sub>IO</sub> (1)                      | Port of OD type                                                                                                      | -0.3 to +15               | V                   |      |

|                                                                 | V <sub>IO</sub> (2)                      |                                                                                                                      | 3 to V <sub>DD</sub> +0.3 | V                   |      |

| Peak Output Current                                             | IOP                                      | Input/output port                                                                                                    | -2 to +20                 | mA                  |      |

| Average Output Current                                          | <sup>1</sup> OA                          | Input/output port: Per pin over the period of 100 msec.                                                              | − <b>2</b> to +20         | mA                  |      |

|                                                                 | ΣIOA (1)                                 | Total current of PA <sub>0</sub> to 3, PC <sub>0</sub> to 3, PD <sub>0</sub> to 3, and PE <sub>0</sub> to 3 (Note 2) |                           | mA                  |      |

|                                                                 | ΣIOA (2)                                 | Total current of PF0 to 3, PG0 to 3, and PI0 to 3, PJ0 to 3 (Note 2)                                                 | -30 to +140               | mA                  |      |

| Allowable Power Dissipation                                     |                                          | DIP package, $T_a = -30 \text{ to } +70^{\circ}\text{C}$                                                             | 600                       | mW                  |      |

|                                                                 |                                          | QIP package, $T_a = -30 \text{ to } +70^{\circ}\text{C}$                                                             | 400                       | mΨ                  |      |

| Operating Frequency                                             | $T_{opg}$                                |                                                                                                                      | -30 to +70                | ိုင                 |      |

| Storage Temperature                                             | T <sub>stg</sub>                         |                                                                                                                      | -55 to +125               | °C                  |      |

| Allowable Operating Conditions                                  | /T <sub>a</sub> = -30 to                 | o +70°C, V <sub>SS</sub> = 0V, V <sub>DD</sub> = 4.5 to 5.5                                                          | V min                     | typ max             | unit |

| Operating Supply Voltage                                        | $V_{DD}$                                 | V <sub>DD</sub>                                                                                                      | 4.5                       | 5.5                 | ٧    |

| Standby Supply Voltage                                          | Vst                                      | V <sub>DD</sub> : RAM, resister hold (Note 3)                                                                        | 1.8                       | 5.5                 | V    |

| "H"-Level Input Voltage                                         | VIH (1)                                  | Port of OD type, PB <sub>0</sub> to 3:<br>Output Nch Tr OFF                                                          | 0.7V <sub>DD</sub>        | +13.5               | ٧    |

|                                                                 | V <sub>IH</sub> (2)                      | Port of PU type: Output Nch Tr OFF                                                                                   | 0.7V <sub>DD</sub>        | Vpp                 | V    |

|                                                                 | VIH (3)                                  | SCK, SI, INT: Output Nch Tr OFF                                                                                      | 0.8V <sub>DD</sub>        | +13.5               | V    |

|                                                                 | VIH (4)                                  | SCK, SI, INT: Output Noh Tr OFF                                                                                      | $0.8V_{DD}$               | $V_{DD}$            | V    |

|                                                                 | V <sub>IH</sub> (5)                      | RES                                                                                                                  | 0.8V <sub>DD</sub>        | VDD                 | V    |

|                                                                 | V <sub>1H</sub> (6)                      | OSC1: External clock mode                                                                                            | 0.8V <sub>DD</sub>        | $V_{DD}$            | V    |

| "L"-Level Input Voltage                                         | VIL (1)                                  | Port: Output Nch Tr OFF                                                                                              | VSS                       | 0.3∨ <sub>DD</sub>  | V    |

|                                                                 | V <sub>IL</sub> (2)                      | INT, SCK, SI: Output Nch Tr OFF                                                                                      | $v_{SS}$                  | 0.25V <sub>DD</sub> | V    |

|                                                                 | V <sub>IL</sub> (3)                      | OSC1: External clock mode                                                                                            | VSS                       | 0.25V <sub>DD</sub> | V    |

|                                                                 | VIL (4)                                  | TEST                                                                                                                 | VSS                       | 0.3V <sub>DD</sub>  | V    |

|                                                                 | VIL (5)                                  | RES                                                                                                                  | VSS                       | 0.25V <sub>DD</sub> | V    |