No. 2576B

LB1644

#### Dual Bidirectional Motor Driver

The LB1644 is a dual bidirectional motor driver. Since each channel has a 2input logic circuit and performs bidirectional driving and braking functions, it is capable of direct driving 2pcs. of motor of various types rated at 6 to 24V. The output voltage can be varied by using external zener diodes.

It is especially suited for dual motor drive (reel motor, loading motor, cassette motor in VTR) and for stepping motor drive.

#### **Features**

- . With power transistors for motor drive contained, capable of withstanding dash current of 1A max.

- . Performs braking function at the motor stop mode.

- . Contains elements to absorb motor dash current.

- . Input interfaceable to MOS LSI.

- . Minimum number of external parts required.

- . Wide operating voltage range.

- . Contains thermal shutdown protector.

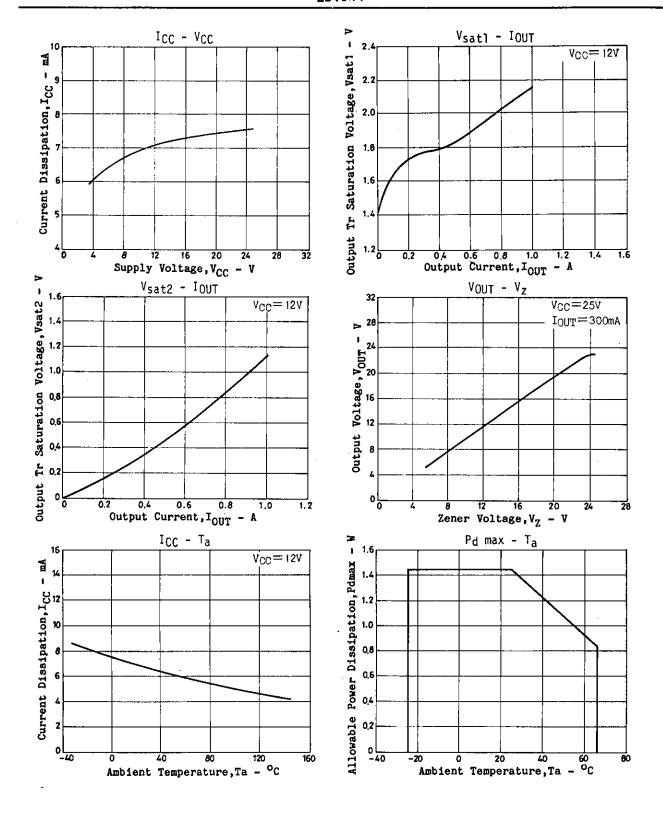

| Absolute Maximum Ratings at              | Ta=25 <sup>O</sup> C      |                                                                                    |         |       | uni    | t    |

|------------------------------------------|---------------------------|------------------------------------------------------------------------------------|---------|-------|--------|------|

| Maximum Supply Voltage                   | $v_{ccmax}$               |                                                                                    |         | 25    | v      |      |

| Input Voltage                            | v <sub>IN</sub>           | •                                                                                  |         | 25    |        |      |

| Output Current                           |                           |                                                                                    |         | ±1    | A      |      |

| Output Current Allowable Power Dissipat: | ion Pdmax                 |                                                                                    |         | 1.44  | . W    |      |

| Operating Temperature                    | $\mathbf{Topr}$           |                                                                                    | -25 to  | +65   | o oc   |      |

| Storage Temperature                      | Tstg                      |                                                                                    | -55 to  | +125  | o oc   |      |

|                                          |                           |                                                                                    |         |       |        |      |

| Allowable Operating Condit:              | ion at Ta=25 <sup>0</sup> | 'C                                                                                 |         |       | uni    | t    |

| Supply Voltage                           | V <sub>CC</sub>           |                                                                                    | •       | to 25 | v      |      |

| Rlectrical Characteristics               | at Ta=25°C, W             | CC=12V,per channel                                                                 | min     | typ   | max    | unit |

| Current Dissipation                      | I <sub>CC1</sub> Pin 1    | Braking mode, R <sub>L</sub> = $\infty$<br>Braking mode, R <sub>L</sub> = $\infty$ |         | 8.0   | 11.5   | mA   |

|                                          | I <sub>CC2</sub> Pin 9    | Braking mode, R <sub>L</sub> =∞                                                    |         | 7.0   | 10.0   | mА   |

| Output Leakage Current                   | IOL                       | Braking mode, $R_L = \infty$                                                       |         | 40    | 120    | μA   |

|                                          | OL                        | per output pin                                                                     |         |       |        | •    |

| Input Threshold Voltage                  | V <sub>th</sub>           | $R_{L}=\infty$                                                                     | 0.9     | 1.05  | 1.20   | V    |

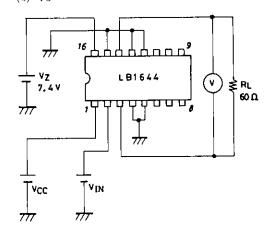

| Output Voltage                           | v <sub>o</sub>            | $R_L = 60 \text{ohms}, V_Z = 7.4 \text{V}$                                         | 6.5     | 7.2   | 7.5    | V    |

|                                          | Ť                         | Con                                                                                | ntinued | on r  | next p | age. |

# Continued from preceding page.

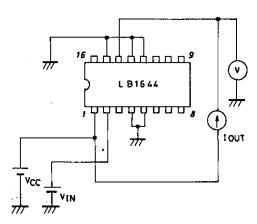

| Output Tr Saturation | V <sub>sat1</sub> I <sub>OUT</sub> =300mA |

|----------------------|-------------------------------------------|

| Voltage (Upper)      | I <sub>OUT</sub> =500mA                   |

| Output Tr Saturation | V <sub>sat2</sub> I <sub>OUT</sub> =300mA |

| Voltage (Lower)      | I <sub>OUT</sub> =500mA                   |

| min | typ | max  | unit |

|-----|-----|------|------|

|     | 1.9 | 2.3  | v    |

|     | 2.0 | 2.4  | V    |

|     | 0.3 | 0.55 | V    |

|     | 0.5 | 0.7  | v    |

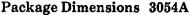

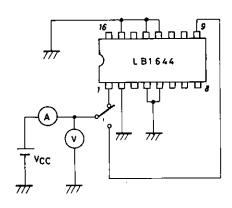

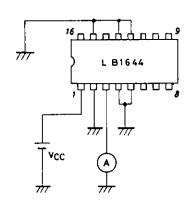

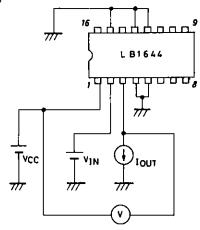

#### Test Circuits (per channel)

(I) ICCI (Ipin)

ICC2 (9pin)

(3) Vth

(5) Vsat1

.(6) Vsat2

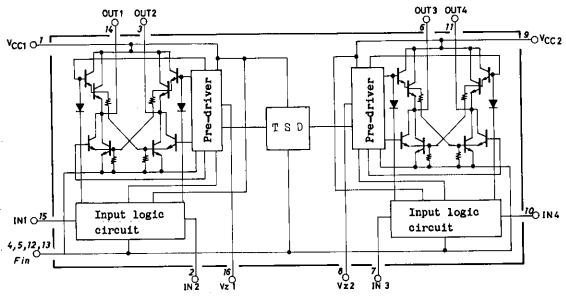

## Equivalent Circuit Block Diagram

Truth Table of Logic Circuit

| - | IN1 | IN2 | OUT1 | OUT2 | IN3 | IN4 | OUT3 | OUT4 |

|---|-----|-----|------|------|-----|-----|------|------|

|   | 0   | 0   | L    | L    | 0   | 0   | L    | L    |

|   | . 1 | 0   | H    | L    | 1   | 0   | H    | L    |

|   | 0   | 1   | L    | H    | 0   | 1   | L    | H    |

|   | 1   | 1   | L    | L    | 1   | 1   | L    | L    |

(Note) A capacitor of 0.01uF or greater must be connected across  $V_{\rm CC}$ 1,2 and GND.

|          | INPUT | NPUT QUTPUT    |       |      | MOD  | MODE |                 |                 |

|----------|-------|----------------|-------|------|------|------|-----------------|-----------------|

| IN1      | IN2,3 | IN4            | OUT 1 | OUT2 | OUT3 | OUT4 | M1              | M2              |

| 0        | 0     | 0              | L     | L    | L    | L    | Braking         | Braking         |

| 1        | 0     | 0              | H     | L    | L    | L    | Forward/reverse | Braking         |

| <u> </u> | 1     | 1              | L     | Н    | L    | L    | Reverse/forward | Braking         |

| 1        | 1     | 0              | L     | L    | H    | L    | Braking         | Forward/reverse |

| <u></u>  | 0     | 1              | L     | L    | L    | H    | Braking         | Reverse/forward |

| 1        | 1     | <del>- i</del> | L     | L    | L    | L    | Braking         | Braking         |

The remaining input states 1,0,1 and 0,1,0 are not inhibited.

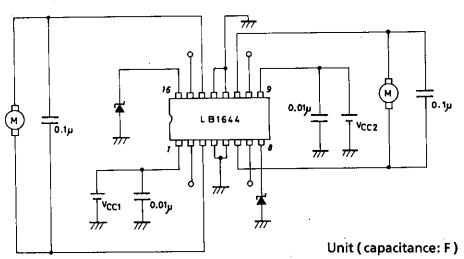

### Sample Application Circuit

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.