## SANYO Semiconductors DATA SHEET

An ON Semiconductor Company

# LB11868V

# Monolithic Digital IC For Fan Motor Variable Speed Single-phase Full-wave Pre-driver

#### Overview

LB11868V is a single-phase bipolar driving motor pre-driver with the variable speed function compatible with external PWM signal. With a few external parts, a highly-efficient and highly-silent variable drive fan motor with low power consumption can be achieved. This product is best suited for driving of the server requiring large air flow and large current and the fan motor of consumer appliances.

#### Features

- Single-phase full-wave driving pre-driver

- Variable speed control possible with external PWM input

- Current limiting circuit incorporated

- Reactive current cut circuit incorporated

- Minimum speed setting pin

- Soft start setting pin

- Start setting pin of on time

- Pch-FET kickback absorption setting pin

- · Lock protection and automatic reset circuits incorporated

- FG (rotational speed detection) output, RD (lock detection) output

- Thermal shutdown circuit incorporated

Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

> SANYO Semiconductor Co., Ltd. http://semicon.sanyo.com/en/network

## **Specifications Absolute Maximum Ratings** at Ta = 25°C

| Parameter                                  | Symbol                     | Conditions                  | Ratings    | Unit |

|--------------------------------------------|----------------------------|-----------------------------|------------|------|

| V <sub>CC</sub> pin maximum supply voltage | V <sub>CC</sub> max        |                             | 18         | V    |

| OUTN pin maximum current                   | I <sub>OUT</sub> N max     |                             | 30         | mA   |

| OUTN pin output withstand voltage          | V <sub>OUT</sub> N max     |                             | 18         | V    |

| OUTP pin maximum Sink current              | I <sub>OUT</sub> P max     |                             | 30         | mA   |

| Maximum inflow current at OUTP pin OFF     | I <sub>OUT</sub> P off max | DUTY8% under                | 10         | mA   |

| OUTP pin output withstand voltage          | V <sub>OUT</sub> P max     | *1                          | 19         | V    |

| VTH/RMI pins withstand voltage             | VVTH/VRMI max              |                             | 7          | V    |

| S-S pin withstand voltage                  | V <sub>S-S</sub> max       |                             | 7          | V    |

| OTS pin withstand voltage                  | V <sub>OTS</sub> max       |                             | 7          | V    |

| KBSET pin withstand voltage                | V <sub>KBSET</sub> max     |                             | 7          | V    |

| FG/RD pin withstand voltage                | V <sub>FG/RD</sub> max     |                             | 19         | V    |

| FG/RD pin maximum Sink current             | I <sub>FG/RD</sub> max     |                             | 10         | mA   |

| REG pin maximum output current             | I <sub>REG</sub> max       |                             | 10         | mA   |

| HB pin maximum output current              | I <sub>HB</sub> max        |                             | 10         | mA   |

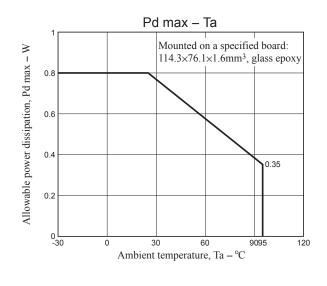

| Allowable power dissipation                | Pd max                     | with specified substrate *2 | 800        | mW   |

| Operating temperature                      | Topr                       | *3                          | -30 to 95  | °C   |

| Storage temperature                        | Tstg                       |                             | -55 to 150 | °C   |

\*1 The direct input from the power supply is improper. There must be resistance between OUTP and the power side power supply.

\*2 Specified substrate: 114.3mm×76.1mm×1.6mm, glass epoxy board.

\*3 Tj max=150°C must not be exceeded.

#### **Recommended Operating Conditions** at $Ta = 25^{\circ}C$

| Parameter                      | Symbol              | Conditions | Ratings    | Unit |

|--------------------------------|---------------------|------------|------------|------|

| V <sub>CC</sub> Supply voltage | V <sub>CC</sub>     |            | 4.0 to 16  | V    |

| VTH/RMI input voltage range    | V <sub>TH/RMI</sub> |            | 0 to 4.0   | V    |

| Hall input voltage range       | VICM                |            | 0.2 to 1.8 | V    |

## Electrical Characteristics at Ta = 25°C, $V_{CC}$ = 12V

| Deservator                    | Symbol              | Conditions                          |      | Unit                 |                      |       |

|-------------------------------|---------------------|-------------------------------------|------|----------------------|----------------------|-------|

| Parameter                     |                     |                                     | min  | typ                  | max                  | Unit  |

| Circuit current               | I <sub>CC</sub> 1   | During drive                        | 7.5  | 9.0                  | 10.5                 | mA    |

|                               | I <sub>CC</sub> 2   | During lock protection              | 6.0  | 7.6                  | 9.0                  | mA    |

| REG voltage                   | V <sub>REG</sub>    | I <sub>REG</sub> = 5mA              | 3.65 | 3.80                 | 3.95                 | V     |

| HB voltage                    | V <sub>HB</sub>     | I <sub>HB</sub> = 5mA               | 1.14 | 1.24                 | 1.34                 | V     |

| Current limiting voltage      | V <sub>LIM</sub>    |                                     | 195  | 215                  | 235                  | mV    |

| CPWM pin "H" level voltage    | V <sub>CPWM</sub> H |                                     | 2.35 | 2.50                 | 2.65                 | V     |

| CPWM pin "L" level voltage    | VCPWML              |                                     | 0.65 | 0.80                 | 0.95                 | V     |

| CPWM pin charge current       | I <sub>CPWM</sub> 1 | V <sub>CPWM</sub> = 0.5V            | 19   | 24                   | 29                   | μA    |

| CPWM pin discharge current    | I <sub>CPWM</sub> 2 | V <sub>CPWM</sub> = 2.8V            | 19.5 | 24.5                 | 29.5                 | μA    |

| CPWM Oscillation frequency    | FPWM                | C = 220PF                           |      | 32                   |                      | kHz   |

| CT pin "H" level voltage      | V <sub>CT</sub> H   |                                     | 2.35 | 2.50                 | 2.65                 | V     |

| CT pin "L" level voltage      | VCTL                |                                     | 0.65 | 0.80                 | 0.95                 | V     |

| CT pin charge current         | I <sub>CT</sub> 1   | V <sub>CT</sub> = 0.5V              | 1.6  | 2.0                  | 2.4                  | μA    |

| CT pin discharge current      | I <sub>CT</sub> 2   | V <sub>CT</sub> = 2.8V              | 0.16 | 0.20                 | 0.24                 | μA    |

| CT pin charge/discharge ratio | R <sub>CT</sub>     | I <sub>CT</sub> 1/I <sub>CT</sub> 2 | 8    | 10                   | 12                   | times |

| S-S pin discharge current     | I <sub>S-S</sub>    | V <sub>S-S</sub> = 1V               | 0.35 | 0.45                 | 0.55                 | μA    |

| OTS pin charge current        | I <sub>OTS</sub> 1  | V <sub>OTS</sub> =0.5V              | 0.65 | 0.85                 | 1.05                 | μA    |

| OTS pin discharge current     | I <sub>OTS</sub> 2  | V <sub>OTS</sub> =0.5V              | 50   | 58                   | 66                   | μA    |

| OTS pin threshold voltage     | V <sub>OTS</sub>    |                                     | 1.2  | 1.3                  | 1.4                  | V     |

| OUTN output H-level voltage   | V <sub>O</sub> NH   | I <sub>O</sub> = 1mA                |      | V <sub>CC</sub> -0.9 | V <sub>CC</sub> -1.0 | V     |

|                               |                     | I <sub>O</sub> = 10mA               |      | V <sub>CC</sub> -1.9 | V <sub>CC</sub> -2.1 | V     |

Continued on next page.

#### Continued from preceding page.

| Parameter                    | Symbol                             | Conditions                                                         |     | Unit |      |      |

|------------------------------|------------------------------------|--------------------------------------------------------------------|-----|------|------|------|

| Parameter                    | Symbol                             | Conditions                                                         | min | typ  | max  | Unit |

| OUTN output L-level voltage  | V <sub>O</sub> NL                  | IO = 10mA                                                          |     | 0.9  | 1.05 | V    |

| OUTP output L-level voltage  | V <sub>O</sub> PL                  | IO = 10mA                                                          |     | 0.4  | 0.55 | V    |

| Hall input sensitivity       | V <sub>HN</sub>                    | IN+, IN- differential voltage<br>(including offset and hysteresis) |     | ±10  | ±20  | mV   |

| FG/RD output L-level voltage | V <sub>FG</sub> L/ <sub>RD</sub> L | I <sub>FG/RD</sub> = 5mA                                           |     | 0.2  | 0.3  | V    |

| FG/RD pin leakage current    | IFG <sup>L/</sup> RD <sup>L</sup>  | V <sub>FG/RD</sub> = 19V                                           |     |      | 10   | μA   |

| VTH/RMI pin bias current     | IVTH/IRMI                          | CPWM = 2V, V <sub>TH/RMI</sub> = 1V                                |     |      | 0.3  | μA   |

## Truth table

## (1) Drive lock CPWM=H VTH, RMI, S-S=L

| IN⁻ | IN <sup>+</sup> | СТ | OUT1P | OUT1N | OUT2P | OUT2N | FG  | RD  | Mode                               |

|-----|-----------------|----|-------|-------|-------|-------|-----|-----|------------------------------------|

| Н   | L               | L  | L     | L     | OFF   | Н     | L   | L   | $OUT1 \rightarrow 2 \text{ drive}$ |

| L   | Н               |    | OFF   | Н     | L     | L     | OFF | L   | $OUT2 \rightarrow 1 \text{ drive}$ |

| Н   | L               |    | OFF   | L     | OFF   | Н     | L   | OFF | Look make the                      |

| L   | Н               | H  | OFF   | Н     | OFF   | L     | OFF | OFF | Lock protection                    |

#### (2) Speed control CT, S-S=L

| VTH, RMI | CPWM | OTS | IN⁻ | IN <sup>+</sup> | OUT1P | OUT1N | OUT2P | OUT2N | Mode                               |                   |

|----------|------|-----|-----|-----------------|-------|-------|-------|-------|------------------------------------|-------------------|

| 1        | н    |     | Н   | L               | L     | L     | OFF   | Н     | $OUT1 \rightarrow 2 \text{ drive}$ |                   |

| L        |      |     | L   | Н               | OFF   | Н     | L     | L     | $OUT2 \rightarrow 1 \text{ drive}$ |                   |

|          | H L  | -   |     | Н               | L     | OFF   | L     | OFF   | Н                                  | Deceneration mode |

| п        |      |     | L   | Н               | OFF   | Н     | OFF   | L     | Regeneration mode                  |                   |

|          |      |     | Н   | L               | OFF   | L     | OFF   | L     |                                    |                   |

| H L      | L    |     | L   | Н               | OFF   | L     | OFF   | L     | Standby mode                       |                   |

For VTH, RMI, and S-S pins, refer to the timing chart.

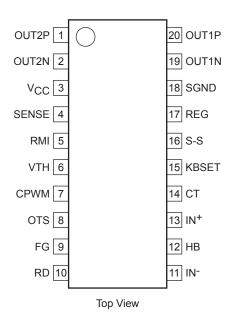

## **Pin Assignment**

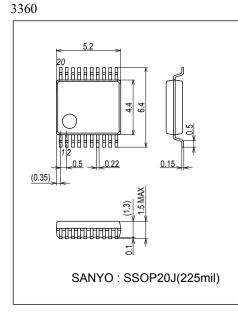

## **Package Dimensions**

unit : mm (typ)

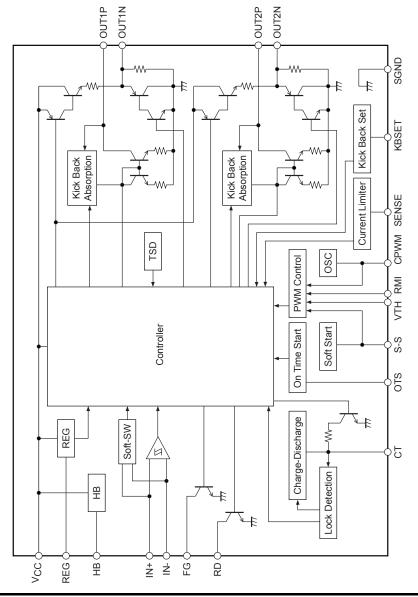

## **Block Diagram**

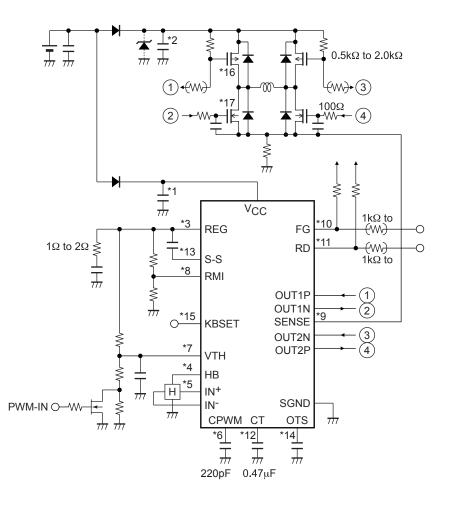

## **Application Circuit Example**

\*1. Power stabilization capacitor

For the power stabilization capacitor on the signal side, use the capacitance of  $1\mu F$  or more. Connect V<sub>CC</sub> and SGND with a thick and shortest pattern.

\*2. Power stabilization capacitor on the power side

For the power stabilization capacitor on the power side, use the capacitance of  $1\mu$ F or more. Connect the power supply on the power side and GND with a thick and shortest pattern. When the IC is used for a fan with a high current level, insert a zener diode between the power supply on the power side and GND.

\*3. REG pin

3.8V constant-voltage output pin. For the REG oscillation prevention and stabilization, use a capacitor with capacitance of 1µF or more. Connect the REG pin and SGND with a thick and shortest pattern.

#### \*4. HB pin

Used for Hall device bias purposes.

\*5. IN+, IN- pins

Hall signal input pin. Wiring should be short to prevent carrying of noise. If noise is carried, insert the capacitor between  $IN^+$  and  $IN^-$  pins. The Hall input circuit functions as a comparator with hysteresis (15mV). This also has a soft switch section with  $\pm 30mV$  (input signal differential voltage). It is also recommended that the Hall input level is minimum 100mV (p-p).

#### \*6. CPWM pin

Pin to connect the capacitor for generation of the PWM basic frequency

The use of CP = 220pF causes oscillation at f = 30kHz (typical), which is the basic frequency of PWM.

As this is used also for the current limiting canceling signal, ON-time start function and Soft start function, be sure to connect the capacitor even when the speed control is not made.

#### \*7. RMI pin

Minimum speed setting pin.

Perform pull-up with REG when this pin is not to be used.

If the IC power supply is likely to be turned OFF first when the pin is used with external power supply, be sure to insert the current limiting resistor to prevent inflow of large current. (The same applies to the VTH pin.)

#### \*8. VTH pin

Speed control pin.

Connect this pin to GND when it is not used (at full speed).

For the control method, refer to the timing chart.

For control with pulse input, insert the current limiting resistor and use the pin with the frequency of 20kHz to 100kHz (20kHz to 50kHz recommended).

#### \*9. SENSE pin

Current limiting detection pin.

When the pin voltage exceeds VLIM, the current is limited and the operation enters the lower regeneration mode. Connect this pin to GND when it is not to be used.

#### \*10. FG pin

Rotational speed detection pin.

Open collector output that can detect rotational speeds by the FG output in response to the phase switching signal. Keep this pin open when it is not to be used.

It is recommended that a current-limiting resistor with a resistance of  $1k\Omega$  or more be inserted in order to protect the pin during unplugging and plugging the connector or when mistakes are made in connection.

#### \*11. RD pin

Lock detection pin

In open collector output, L upon rotation and H when locked (using pull-up resistance). Keep this pin open when it is not to be used.

#### \*12. CT pin

Pin to connect the lock detection capacitor.

The constant-current charge and discharge circuits incorporated cause locking when the pin voltage becomes VCTH and unlocking when it is VCTL.

Connect the pin to GND when it is not to be used (locking not necessary).

#### \*13. S-S pin

Pin to connect the soft-start setting capacitor. Connect the capacitor between REG and S-S pin. This pin enables setting of the soft start time according to the capacity of the capacitor. See the timing char. Connect the pin to GND when it is not to be used.

#### \*14. OTS pin

Pin to connect the ON-time start setting capacitor.

A constant-current charging circuit and a discharging circuit based on the control duty ratio are incorporated, and when the pin voltage exceeds VOTS, the CT pin is discharged and the S-S pin is charged. Connect the pin to GND when it is not to be used (when the lowest speed setting is used).

. . .

#### \*15. KBSET pin

Pch kickback absorption circuit setting pin.

Open: The kickback absorption circuit is activated at a VCC voltage of 7.4V (typ) or above.

Pull-down to GND: Always OFF

Pull-up to REG: Always ON (but when the IC power is OFF, the kickback absorption circuit is OFF)

If the Pch load is to be reduced due to the large fan current, short the KBSET pin to GND, and use a zener diode between the power supply on the power side and GND.

Kickback absorption circuit ON: At OUTPOFF, the OUTP voltage is clamped at VCC + 0.85V (at room temperature and inflow current 5mA (typ)).

Kickback absorption circuit OFF: At OUTPOFF, the OUTP voltage is clamped at 18V or so (at room temperature and inflow current 5mA (typ)) in order to protect the pin.

At OUTPOFF, the maximum inflow current must not be exceeded.

#### \*16. Pch FET

If the Pch kickback absorption circuit is activated and a zener diode between the power supply and GND is not used, the kickback during phase switching is absorbed by Pch.

Since the circuit is activated with a high voltage difference between the drain and source, select a FET with sufficiently high capability.

#### \*17. Nch FET

If the Nch gate voltage fluctuates significantly due to the effects of switching, insert a capacitor between the gate and GND.

Since an Nch diode is used during coil current regeneration, select a FET with sufficiently high capability.

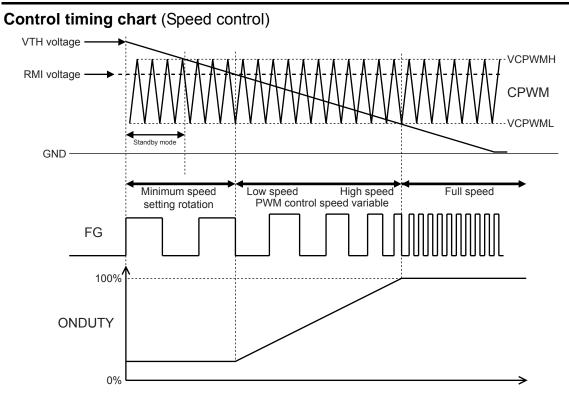

(1) Minimum speed setting (standby) mode

The low-speed fan rotation occurs at the minimum speed set with the RMI pin.

When the minimum speed is not set (RMI pin pulled up to REG), the motor stops.

If the VHT voltage rises when the lowest speed is not set (RMI pin is pulled up to REG), the fan stops running, and if the OTS pin capacitor is used, the standby mode is established.

Details of the standby mode are given in the section "Control timing chart (ON-time start, Lock protection).

(2) Low speed  $\Leftrightarrow$  high speed

PMW control is made by comparing the CPWM oscillation voltage (VCPWML⇔VCPEMH) and VTH voltage. The drive mode is established when the VTH voltage is low.

Both upper and lower output FET are turned ON when the VTH voltage is low.

When the VTH voltage is high, Pch is turned off, and the coil current is regenerated inside the lower FET. Therefore, as the VTH voltage decreases, the output ON-DUTY increases, causing an increase in the coil current and raising the motor rotation speed.

The upper output Pch is turned OFF when the VTH voltage is high, regenerating the coil current in the lower TR. Therefore, as the VTH voltage decreases, the output ON-DUTY increases, causing increase in the coil current, raising the motor rotation speed.

The rotational speed can be monitored using the FG output.

(3) Full speed mode

The full speed mode becomes effective when the VTH voltage is VCPWML or less. (Set VTH = GND when the speed control is not to be made.)

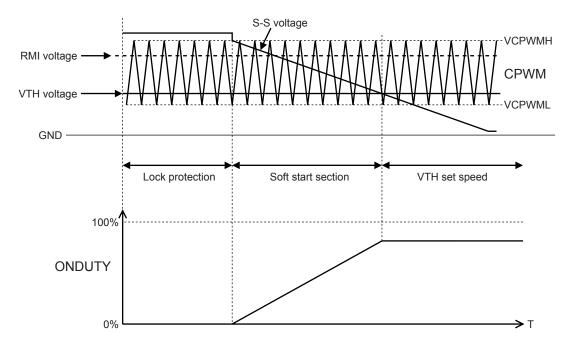

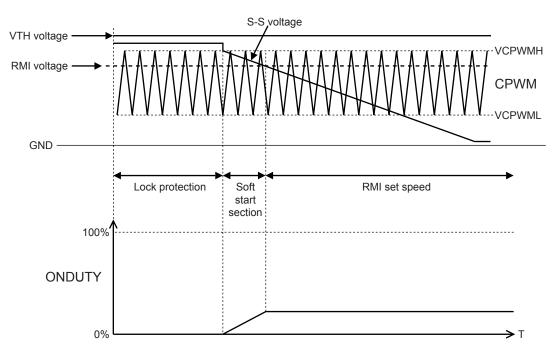

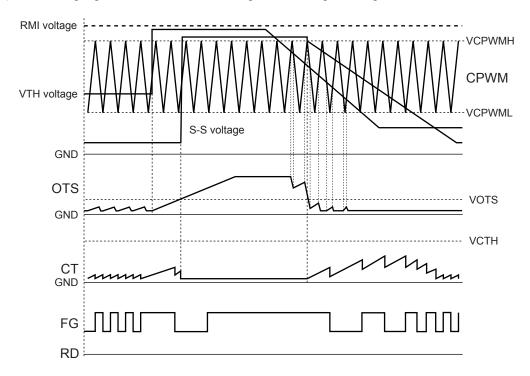

## Control timing chart (Soft start)

(1)At VTH < RMI voltage

(2) At VTH > RMI voltage

Adjust the S-S pin voltage gradient by means of the capacitance of the capacitor between the S-S pin and REG. Recommended capacitor:  $0.1\mu$  to  $1\mu F$

## LB11868V

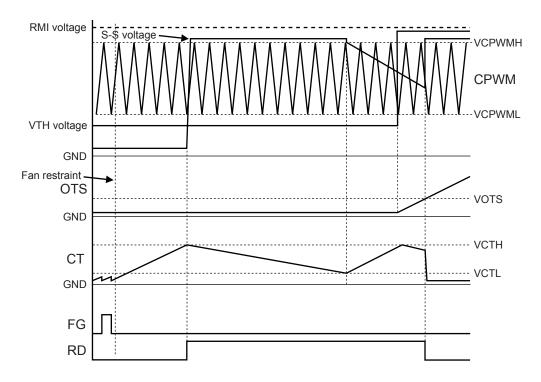

## Control timing chart (ON-time start, Lock protection)

(1) When a stop signal based on the VTH voltage has been input during normal rotation

When the output duty ratio based on the VTH/RMI input drops to below 1% or so, the OTS voltage rises, and when it reaches VOTS, the standby mode is established, the CT pin discharges, and the S-S pin is charged. In the standby mode, if the drive mode has been established again by the VTH/RMI input, the rotation is started immediately with soft start. The CT pin discharges at the same time as the switching of FG. For details on lock protection, refer to (2).

(2) When a stop signal based on the VTH voltage has been input while the fan is constrained

When the fan is constrained, the CT pin voltage rises, and when it reaches VCTH, the lock protection mode is established, and OUTP is set to OFF and RD is set to OFF.

When the lock protection mode is established, the CT pin discharges, and when VCTL is reached, restart (soft start) is initiated. When rotation is started and the FG signal is switched, RD is set to low.

Note: RD is also set to low when the standby mode is established when locked.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of May, 2011 Specifications and information herein are subject to change without notice.