#### **Data Sheet**

## LB1013 High-Voltage Dual Op Amp

### **Features**

- Operates from 5 V to 85 V

- Dual or single power supply operation

- Programmable output currents up to ±80 mA

- 90 V minimum breakdown, complementary bipolar monolithic IC

- Operating temperature of -25 °C to +100 °C

### **Applications**

- Transconductance amplifier for telephone line feed or driver

- Medium power audio amplifiers

- Voltage follower/buffer

- Control system solenoid or relay driver

- Telephone line ringing signal generator

### **Description**

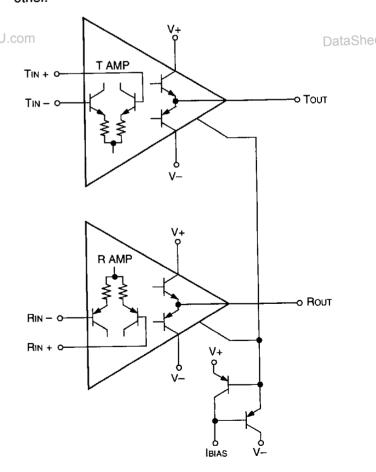

The LB1013AD High-Voltage Dual Op Amp is a monolithic silicon integrated circuit that is fabricated in a junction-isolated, complementary bipolar process that provides PNP transistors with symmetric performance to the NPN. The amplifiers are internally compensated for unity-gain stability and designed for operation in the audio band. A programming pin provides access for setting performance levels, power supply consumption, or logic turn-on/turn-off. Positive power supply pins can be tied together or used to supply input and output stages separately, or to power up one amplifier without the other.

Figure 1. Functional Diagram

www.DataSheet40.com

## **Pin Information**

Figure 2. Pin Diagram

### **Table 1. Positive Supply Pins**

| Pin Symbol Description |         | Description                                                                              |   |

|------------------------|---------|------------------------------------------------------------------------------------------|---|

| 1                      | V+ (RO) | Positive supply to the output stage of R amplifier.                                      |   |

| 3                      |         |                                                                                          |   |

| 9                      |         | Positive supply to T amplifier input stage.                                              |   |

| 10                     | VPos    | Positive supply to both T and R amplifier input stages and to programming pin circuitry. |   |

| 1 <b>7</b>             | Vpos    | Positive supply to R amplifier input stage and to programming pin circuitry.             | D |

### **Table 2. Negative Supply/Ground Pins**

| Pin                       | Symbol | Description                                                                                                                                                                                                                                   |

|---------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 5,<br>6, 13,<br>14, 15 |        | These pins provide redundant electrical continuity to the most negative circuit potential. All of these pins should be connected to ensure satisfactory heat dissipation, although only one pin is required to provide electrical continuity. |

### Table 3. Programming Bias Pin

| Pin | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                        |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  |        | A current source or a suitable value programming resistor (see Figure 7, Note 2) can be connected to this pin. A negative current flow from this pin must be present before the LB1013AD device becomes operational. The peak output current for sinking in the T amplifier and sourcing in the R amplifier is greater than 1000 times IBIAS (see Typical Device Characteristics). |

### **Table 4. Input/Output Pins**

| Pin          | Symbol                  | Description                                                                                                                                                                                                                      |

|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2            | Тоит                    | Output of the T amplifier. Peak current through this pin should not exceed 80 mA, source or sink.                                                                                                                                |

| 7<br>8       | T(IN-)<br>T(IN+)        | These pins are the inverting and noninverting inputs, respectively, for the differential input stage of the T amplifier.                                                                                                         |

| 11<br>12     | R(IN+)<br>R(IN-)        | These pins are the inverting and noninverting inputs, respectively, for the PNP differential input stage of the R amplifier. The LB1013AD uses vertical PNP transistors with ac and dc characteristics well matched to the NPNs. |

| 18<br>ataShe | <b>Rouт</b><br>et4U.com | Output of the R amplifier. Peak output current through this pin must not exceed 80 mA, source or sink.                                                                                                                           |

www.DataSheet4U.com

## Absolute Maximum Ratings (At 25 °C)

Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to Absolute Maximum Ratings for extended periods of time can adversely affect device reliability.

| Parameter                                                 | Symbol | Min        | Max  | Unit |

|-----------------------------------------------------------|--------|------------|------|------|

| Ambient Operating Temperature                             | Ta     | -25        | +100 | °C   |

| Storage Temperature Range                                 | Tstg   | -40        | +125 | °C   |

| Pin Soldering Temperature (t = 15 s max)                  | Ts     | _          | +300 | °C   |

| Voltage (VPos to VNEG)                                    | _      |            | +85  | ٧    |

| Power Dissipation*                                        | Poiss  |            | +2   | W    |

| Differential Input Voltage (See Application Precautions.) | _      | <b>-</b> 5 | +5   | ٧    |

<sup>\*</sup> Care in mounting and environment is required to keep junction operating temperature acceptably low. The package of this device has a thermal resistance (Ojc) of approximately 20 °C/W. The thermal resistance of the wiring board mounting plane to ambient should not exceed 30 °C/W for normal applications. On the printed-circuit board, make the VNEG leads as wide as possible. Also, maximize the amount of printed-circuit board copper in the area of and specifically on the leads connected to this device for the lowest operating temperature. Forced-air circulation or high-thermal conductivity wiring boards may be required.

## Typical Device Characteristics (TA = 25 °C)

Typical values are characteristics of the device and are the results of engineering evaluations. Typical values are for information purposes only and are not part of the testing requirements. Positive current is defined as flowing into the device.

| Characteristic                      | IBIAS = 40 A | IBIAS = 80 μA |

|-------------------------------------|--------------|---------------|

| Slew Rate                           | 2 V/μs       | 4 V/μs        |

| Output Current                      | ±40 mA       | ±80 mA        |

| Power Supply Rejection Ratio (PSRR) | 80 dB        | 80 dB         |

DataShe

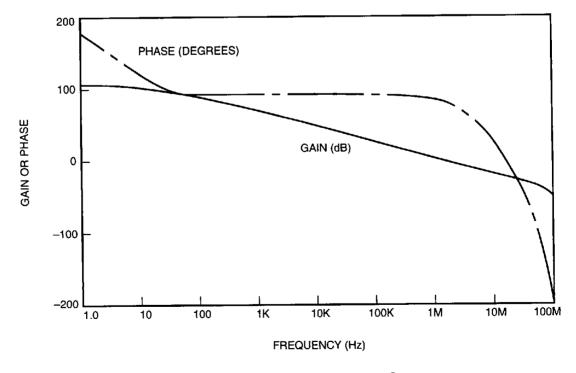

Figure 3. Frequency/Gain Response Curve

DataSheet4U.com Microelectronics

www.DataSheet4U.com

## **Electrical Characteristics**

T = 25 °C, VPos = 25 V; VPos = -25 V, IBIAS connects through a 1.25 M $\Omega$  resistor to V unless otherwise specified. Minimum and maximum values are testing requirements.

| Parameter                    | Test Condition                                     | Min              | Max          | Unit |

|------------------------------|----------------------------------------------------|------------------|--------------|------|

| Open-loop Gain               | f = 100 Hz                                         | 75               | _            | dB   |

|                              | f = 1 kHz                                          | 55               |              | dB   |

| Input Offset Voltage         | <del>-</del>                                       |                  | ±5.0         | mV   |

| Input Bias Current           | Inverting and noninverting pins                    |                  | ±1.0         | μΑ   |

| Input Offset Current         | <u></u>                                            |                  | ±1.0         | μΑ   |

| Common-mode Rejection Ratio  | VPOS = 30 V,                                       | 80               | <del>-</del> | dB   |

|                              | VNEG = -30 V,                                      |                  |              |      |

|                              | VCM = 0 ±20 V                                      |                  |              |      |

| Output Voltage Swing         | $V_{POS} = 38 \text{ V}, V_{NEG} = -38 \text{ V},$ |                  |              |      |

| T Amplifier:                 | noninverting input = Gnd,                          |                  |              |      |

| VHIGH                        | $\Delta V$ (inverting input = ±0.5 V),             | 35.6             | _            | V    |

| VLow                         | IBIAS = 40 $\mu$ A, RL = 1 kΩ                      | -35.4            | —            | V    |

| Output Voltage Swing         | $V_{POS} = 38 \text{ V}, V_{NEG} = -38 \text{ V},$ |                  |              |      |

| R Amplifier:                 | noninverting input = Gnd,                          |                  |              |      |

| VHIGH                        | $\Delta V$ (inverting input = ±0.5 V),             | 35.4             | _            | v    |

| VLow                         | ÍΒΙΑS = 40 $\mu$ A, RL = 1 $k\Omega$               | -35.6            | _            | v    |

| Power Supply Currents        | VPOS = 35 V, VNEG = 35 V                           |                  |              |      |

| (amplifiers activated under  | (See Figure 5.)                                    |                  |              |      |

| no-load conditions)          | IVPos                                              | _                | 1.1          | mA   |

|                              | IVNEG                                              | _                | -1.1         | mA   |

| Power Supply Leakage Current | VPOS = 35 V, VNEG = -35 V                          |                  |              |      |

| (amplifiers off)             | Івіаs = open (See Figure 5.)                       |                  |              | i    |

|                              | IVPOS                                              | _                | ±10          | μА   |

|                              | IVNEG                                              | _                | ±10          | μA   |

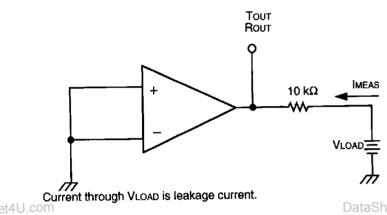

| Output Leakage Current       | VPOS = 35 V, VNEG = -35 V                          |                  |              |      |

| (amplifiers off)             | Івіаs = open (See Figure 4.)                       |                  |              |      |

|                              | VLOAD = 30 V                                       | _                | ±10          | μА   |

|                              | VLOAD = 30 V                                       |                  | ±10          | μΑ   |

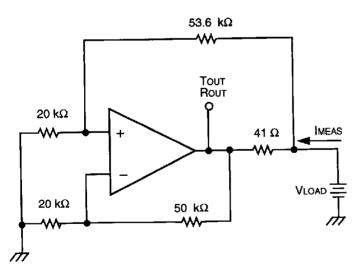

| Τουτ to Veos Fault Current   | VLOAD = 35 V, t = 100 ms                           | 41               | 47           | mA   |

|                              | (See Figure 6.)                                    |                  |              |      |

| Tout to VNEG Fault Current   | VLOAD = -35 V, t = 100 ms                          | -41              | -47          | mA   |

| D + M 5 HO                   | (See Figure 6.)                                    |                  |              |      |

| Rouт to Vpos Fault Current   | VLOAD = 35 V, t = 100 ms                           | 41               | 47           | mA   |

| Rout to VNEG Fault Current   | (See Figure 6.)                                    | <del>     </del> |              |      |

| THOU TO THE FAUIT CUTTERIL   | VLOAD = -35 V, t = 100 ms<br>(See Figure 6.)       | -41              | 47           | mA   |

|                              | (See Figure 6.)                                    | <u> </u>         |              |      |

DataShe

www.DataSheet4U.com

## **Simplified Test Circuits**

Figure 4. Output Leakage Current

Figure 5. Power-Supply Current

Figure 6. Fault Current

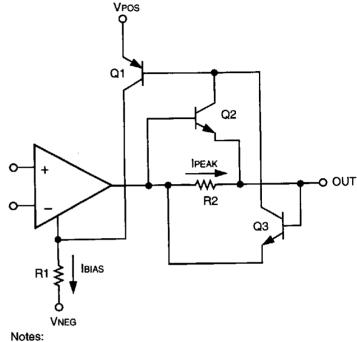

### **Short-Circuit Protection**

The outputs of the LB1013AD device can be protected from short circuits by using the external circuitry shown in Figure 6.

1. Q1, Q2, Q3; V(BR)CEO > 90 V.

DataSheet4U.com

2. R1 =

$$\frac{V_{POS}(Pin17) - V_{NEG} - 1.2 \ V}{I_{BIAS}}$$

$$3.R2 = \frac{0.6 \text{ V}}{\text{IPEAK}}.$$

Figure 7. External Circuitry

DataShe

www.DataSheet4U.com DataSheet4U.com

## **Applications**

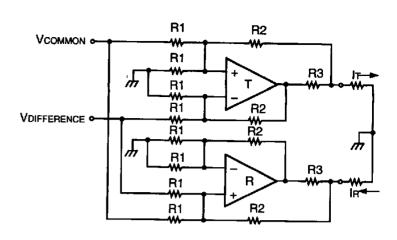

The simplified schematic outlined in Figure 8 illustrates an application as a transconductance amplifier for a telephone line drive. Other applications include highvoltage/power-voltage followers and audio amplifiers and circuits where high-voltage, high-power op amp capabilities are required. The equations relating to the circuit outlined in Figure 8 are as follows:

For R1 & R2 >> R3

$$IT = \frac{VC - VD}{R1} \times \frac{R2}{R3}$$

$$IR = -\frac{VC - VD}{R1} \times \frac{R2}{R3}$$

et4U.com

Figure 8. Simplified Line-Feed Operation (power-supply connection not shown)

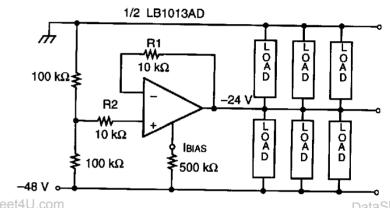

Figure 9. Typical Voltage Follower

DataSheet4U.com DataShe

+48 - 80 V 1 ΜΩ LB1013AD Т O TIP 1 ΜΩ 220 kΩ ≥ R RING 220 kΩ 1 ΜΩ 0.047 µF CYCLE CONTROL

Figure 10. Dual Op Amp Solid-State Differential Signal Generator

www.DataSheet4U.com

DataSheet4U.com

#### **Data Book**

### Applications (continued)

Certain precautions are necessary to prevent this device from latching and from going into an oscillationclipping mode.

### **Latching Prevention**

If the differential input voltage exceeds 5.0 V (breaking down the input transistor) and the power-supply voltage exceeds 30 V, the output of the T amplifier can latch to the positive-supply rail and the R amplifier can latch to the negative power-supply rail. This latching can occur in an op amp that is connected in the unity-gain configuration when a voltmeter or load is connected to the output. In this case, the capacitance of the voltmeter or ground can cause a temporary overload of the input, causing the latch to occur. The following practices are recommended for the prevention of latching modes:

- 1. The power supply voltages should be removed or reduced below 30 V before connections are either made or removed from the LB1013AD device.

- 2. It is a good practice to place a resistor (R1, Figure 9) between the resistor of equal value (R2, Figure 9) and any external connections. The value of these heet4U.com resistors should be between 1 k $\Omega$  and 10 k $\Omega$ .

- 3. Differential input voltage should not exceed ±5.0 V.

### Clipping

The T amplifier of the LB1013AD device has an NPN input stage, and the R amplifier has a PNP input stage. Thus, the common-mode input voltage range of the two amplifiers is different with the T amplifier being more positive and the R amplifier being more negative. If the outputs of the T and R amplifiers are allowed to come within 3.4 V of the negative and positive supply voltages, respectively, the outputs will begin clipping. The clipped portion of the waveform exhibits an oscillation.

LB1013 High-Voltage Dual Op Amp

Oscillation will not occur in circuits where the commonmode input voltage of the T amplifier is closer to the positive supply voltage; the common-mode input voltage of the R amplifier is closer to the negative supply voltage, and the signal only causes clipping in one polarity. In this case, clipping starts when the output voltage comes within 2 V of the supply rail.

## LB1013 High-Voltage Dual Op Amp

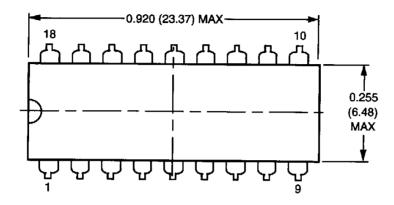

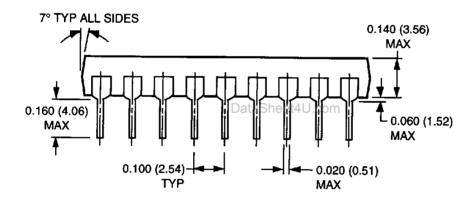

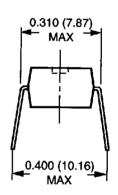

## **Outline Drawings**

Dimensions are in inches and (millimeters).

## 18-Pin, Plastic DIP

DataShe

5-2644

DataSheet4U.com

et4U.com

www.DataSheet4U.com

# **Packaging and Ordering Information**

Throughout this section the following abbreviations are used:

DIP — Dual in-line package; SOG — Small-outline gull wing; SOJ — Small-outline J-lead; SONB — Small-outline narrow body; PLCC — Plastic leaded chip carrier.

| Device Code                  | Package Type                 | Temperature              |  |

|------------------------------|------------------------------|--------------------------|--|

| ATTL7551AP                   | 44-Pin PLCC                  | -40 °C to +85 °C         |  |

| ATTL7551AF                   | 24-Pin DIP                   | –40 °C to +85 °C         |  |

| ATTL7554AP                   | 44-Pin PLCC                  | -40 °C to +85 °C         |  |

| ATTL7556AAU                  | 20 71 71 00                  |                          |  |

| ATTL7557AAU                  | 32-Pin PLCC                  | <del>-40 C10 +03 G</del> |  |

| ATTL7561AP                   |                              | -40 °C to +85 °C         |  |

| ATTL7564AP                   | 44-Pin PLCC                  | -40 C 10 +65 C           |  |

| ATTL7581AC/BC                | 16-Pin DIP                   | -40 °C to +85 °C         |  |

| ATTL7581AAE/BAE              | 16-Pin Plastic SOG           | -40 °C to +85 °C         |  |

| ATTL7582AE/BE                | 16-Pin Plastic DIP           | –40 °C to +85 °C         |  |

| ATTL7582AAE/BAE              | 16-Pin Plastic SOG           | -40 °C to +85 °C         |  |

| ATTL7583AF/BF                | 24-Pin Plastic DIP (600 mil) | -40 °C to +85 °C         |  |

| ATTL7583ACG/BCG              | 24-Pin Plastic DIP (300 mil) | -40 °C to +85 °C         |  |

| ATTL7583AAJ/BAJ              | 28-Pin Plastic SOG           | -40 °C to +85 °C         |  |

| ATTL/583AAJ/BAJ              | 14-Pin                       | -40 °C to +85 °C         |  |

| ATTL7591AB                   | 8-Pin, DIP                   | -40 °C to +85 °C         |  |

| ATTL7591AS                   | 8-Pin, SONB                  | -40 °C to +85 °C         |  |

| LB1011AB                     | 8-Pin, DIP                   | –20 °C to +70 °C         |  |

| nm                           | DataS 8 Pin UDIP             | -25 °C to +85 °C         |  |

| LB1013AD                     | 8-Pin, DIP                   | -40 °C to +65 °C         |  |

| LB1060AB<br>LB1201AB         | 8-Pin, DIP                   | -40 °C to +85 °C         |  |

| LB1201AS                     | 8-Pin, SONB                  | -40 °C to +85 °C         |  |

| LB1208AAJ                    | 28-pin SOG                   | -40 °C to +85 °C         |  |

| LB1276AP                     | 44-Pin PLCC                  | -40 °C to +85 °C         |  |

|                              | 24-Pin DIP                   | -40 °C to +85 °C         |  |

| LB1276AF                     | 24-Pin DIP                   | -40 °C to +85 °C         |  |

| LB1356AF                     | 20-Pin Plastic DIP           | -40 °C to +85 °C         |  |

| LH1263AR                     | 8-pin Plastic DIP            | -40 °C to +85 °C         |  |

| LH1571AB                     | 8-pin SOG                    | -40 °C to +85 °C         |  |

| LH1571AAC<br>T - 7503 EL     | 20-Pin, SOJ                  | -40 °C to +85 °C         |  |

|                              | 20-Pin, SOJ                  | 0 °C to 70 °C            |  |

| T - 7503 1EC                 | 28-Pin, DIP                  | -40 °C to +85 °C         |  |

| T - 7504 PL<br>T - 7504 ML   | 28-Pin, PLCC                 | -40 °C to +85 °C         |  |

|                              | 28-Pin, DIP                  | -40 °C to +85 °C         |  |

| T - 5504 PL                  | 28-Pin, PLCC                 | -40 °C to +85 °C         |  |

| T - 5504 ML                  | 20-Pin, SOJ                  | -40 °C to +85 °C         |  |

| T - 7513B EE                 | 20-Pin, DIP                  | -40 °C to +85 °C         |  |

| T - 7513B PE                 | 16-Pin, DIP                  | -40 °C to +85 °C         |  |

| T - 7517A EE                 | 16-Pin, SOJ                  | -40 °C to +85 °C         |  |

| T - 7517A PE                 | 28-Pin, PLCC                 | 0 °C to 85 °C            |  |

| T - 7548 ME2<br>T - 7570 ML2 | 28-Pin, PLCC                 | -40 °C to +85 °C         |  |

www.DataSheet4U.com DataSheet4U.com