# SANYO Semiconductors DATA SHEET

## LA72700V — Monolithic Linear IC US MTS (Multi Channel Television Sound) Decoder

#### Overview

LA72700V is a US MTS (Multi Channel Television Sound) decoder.

#### Features

- With SIF circuit, STEREO channel separation is alignment-free.

- Built-in filters are adjustment free.

- SAP output level is selectable 2 levels.

- Included control function for STEREO and SAP detection sensitivity.

#### **Functions**

- SIF FM-Demodulator.

- STEREO decoder.

- ALC function is included.

- dbx Noise Reduction system.

- SAP demodulator.

- STEREO detection.

- SAP detection.

## **Specifications**

**Maximum Ratings** at  $Ta = 25^{\circ}C$

| Parameter                    | Symbol              | Conditions | Ratings     | Unit |

|------------------------------|---------------------|------------|-------------|------|

| Maximum power supply voltage | V <sub>CC</sub> max |            | 9.6         | V    |

| Allowable power dissipation  | Pd max              | Ta≤70°C *  | 810         | mW   |

| Operating temperature        | Topr                |            | -10 to +70  | °C   |

| Storage temperature          | Tstg                |            | -55 to +150 | °C   |

\* ON board (114.3  $\times$  76.1  $\times$  1.6 mm Glass Epoxy resin board)

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

#### **Operating Conditions** at $Ta = 25^{\circ}C$

| Parameter                     | Symbol             | Conditions | Ratings    | Unit |

|-------------------------------|--------------------|------------|------------|------|

| Recommended operating voltage | V <sub>CC</sub>    |            | 9.0        | V    |

| Operating voltage range       | V <sub>CC</sub> op |            | 8.5 to 9.5 | V    |

## Electrical Characteristics at $Ta=25^{\circ}C,\ V_{CC}=9.0V$

| Parameter                            | Symbol | Conditions                                                                                                                                          |         | Ratings |       | Unit |

|--------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|------|

| Falameter                            | Symbol | Conditions                                                                                                                                          | min     | typ     | max   | Unit |

| Current dissipation                  | ICC    | No signal Inflow current at pin 31<br>* Default condition                                                                                           | 50      | 60      | 70    | mA   |

| SIF input level<br>(Reference)       | VILIM  | fc = 4.5MHz<br>Deviation<br>MONO (300Hz, Mod = 100%, Pre-emphasis ON) $\rightarrow$<br>±25kHz                                                       | (80)    | (90)    | (100) | dBμV |

| Base band input level<br>(Reference) | VILIMB | 100% Modulation   MONO(L+R): 530mVp-p (300Hz, Pre-emphasis ON)   SUB(L-R): 380mVp-p (300Hz, dbx-NR ON), Pilot: 1   SAP: 300mVp-p (300Hz, dbx-NR ON) | 10mVp-p |         |       |      |

| MONO output level                    | VOMON  | Input: fm = 1kHz, 100% Mod, MONORAL<br>Measure OUT (L), OUT (R)                                                                                     | -7.0    | -6.0    | -5.0  | dBV  |

| MONO distortion                      | THDMON | Input: fm = 1kHz, 100% Mod, MONORAL<br>Measure OUT (L), OUT (R)                                                                                     |         | 0.15    | 0.6   | %    |

| MONO frequency characteristics       | FCM1   | Input: fm = 8kHz, 30% Mod, MONORAL<br>Measure OUT(L), OUT(R),<br>Ratio from fm = 1kHz level.                                                        | -2      | 0       | 2     | dB   |

| MONO S/N ratio                       | SNM    | S = VOMON, N = 0% Mod<br>Measure OUT (L), OUT (R)<br>With 15kHz LPF, JIS-A                                                                          | 55      | 65      |       | dB   |

| STEREO output level                  | VOST   | Input: fm = 1kHz, 100% Mod, STEREO<br>Measure OUT (L), OUT(R)                                                                                       | -7.0    | -6.0    | -5.0  | dBV  |

| STEREO distortion                    | THDS   | Input: fm = 1kHz, 100% Mod, STEREO<br>Measure OUT (L), OUT (R)                                                                                      |         | 1.0     | 2.5   | %    |

| STEREO frequency<br>characteristics  | FCS1   | fm = 8kHz 30% Mod, STEREO<br>Measure OUT (L), OUT (R),<br>Ratio from fm = 1kHz level.                                                               | -3      | 0       | 3     | dB   |

| STEREO S/N ratio                     | SNS    | S = VOST, N = 0% Mod<br>Measure OUT (L), OUT (R)<br>With 15kHz LPF, JIS-A                                                                           | 50      | 60      |       | dB   |

| STEREO separation 1                  | STSE1  | f = 300Hz (R/L), 30% Mod<br>Measure ratio OUT (L) with OUT (R)                                                                                      | 20      | 25      |       | dB   |

| STEREO separation 2                  | STSE2  | f = 3kHz (R/L), 30% Mod<br>Measure ratio OUT (L) with OUT (R)                                                                                       | 20      | 25      |       | dB   |

| STEREO Detection level-1             | VINSD1 | Except Stereo Detection → Stereo Detection<br>Measure PILOT level, at STERO det.                                                                    | 52      | 57      | 62    | %    |

| STEREO Detection level-2             | VINSD2 | Except Stereo Detection → Stereo Detection<br>* Insert Resistor pin 14 to GND (ex. 51kΩ)<br>Measure PILOT level, at STERO det.                      | 62      | 67      | 72    | %    |

|                                      |        |                                                                               |      | Ratings |      |      |

|--------------------------------------|--------|-------------------------------------------------------------------------------|------|---------|------|------|

| Parameter                            | Symbol | Conditions                                                                    | min  | typ     | max  | Unit |

| STEREO detection hysteresis          | HYST   | Input Mod. Difference at Stereo /Except Stereo Det.<br>* at default condition | 10   | 15      | 25   | %    |

| SAP output level-1                   | VOSA   | Fm = 1kHz, 100% Mod, SAP<br>Measure OUT (L), OUT<br>* at bit6 = 0             | -7.5 | -6.5    | -5.5 | dBV  |

| SAP output level-2                   | VOSA2  | Fm = 1kHz, 100% Mod, SAP<br>Measure OUT (L), OUT<br>* at bit6 = 1             | -5.5 | -4.5    | -3.5 | dBV  |

| SAP distortion                       | THDSA  | Fm = 1kHz, 100% Mod, SAP<br>Measure OUT (L), OUT                              |      | 1.5     | 3.5  | %    |

| SAP S/N ratio                        | SNSA   | S = VOSA, N = 0% Mod,<br>Measure OUT (L), OUT (R)<br>With 15kHz LPF, JIS-A    | 55   | 65      |      | dB   |

| SAP detection level-1                | VINSA1 | Measure SAP carrier level,<br>when SAP det<br>* Default condition             | 13   | 18      | 23   | %    |

| SAP detection level-2<br>(Reference) | VINSA2 | Measure SAP carrier level,<br>when SAP det<br>* pin15 to GND (ex 33kΩ)        | (5)  | (10)    | (15) | %    |

| SAP detection level-3<br>(Reference) | VINSA3 | Measure SAP carrier level,<br>when SAP det<br>* pin15 to GND (ex 8.2kΩ)       | (20) | (25)    | (30) | %    |

| SAP detection hysteresis             | HYSA   | Input Mod. Difference at SAP/Except SAP Det.<br>* at default condition        | 2    | 5       | 10   | %    |

| MODE output MONO                     | MODMO  | Input = MONO: f = 1kHz, 0% Mod<br>Measure pin32                               | 0.7  | 1       | 1.3  | V    |

| MODE output SAP                      | MODSA  | Input = SAP: Carrier<br>Measure pin32                                         | 1.7  | 2       | 2.3  | V    |

| MODE output STEREO                   | MODST  | Input = STEREO: Pilot<br>Measure pin32                                        | 2.7  | 3       | 3.3  | V    |

| MODE output ST + SAP                 | MODSS  | Input = STEREO: Pilot,<br>SAP: Carrier<br>Measure pin32                       | 3.5  | 3.8     | 4.2  | V    |

| Distortion                           | THDALC | MONO 1kHz Mod 100%<br>* ALC on Measure OUT (L), OUT (R)                       |      | 0.3     | 0.5  | %    |

\* Normally measurement condition is Input = SIF mode (-90dB $\mu$ V), ALC = OFF

\* " Reference " Items are reference levels, their specs are no-guarantee.

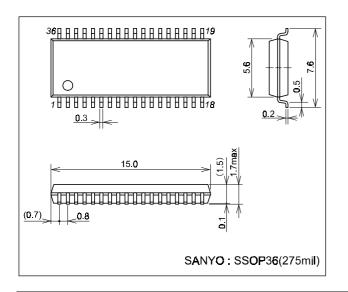

## **Package Dimensions**

unit : mm 3247B

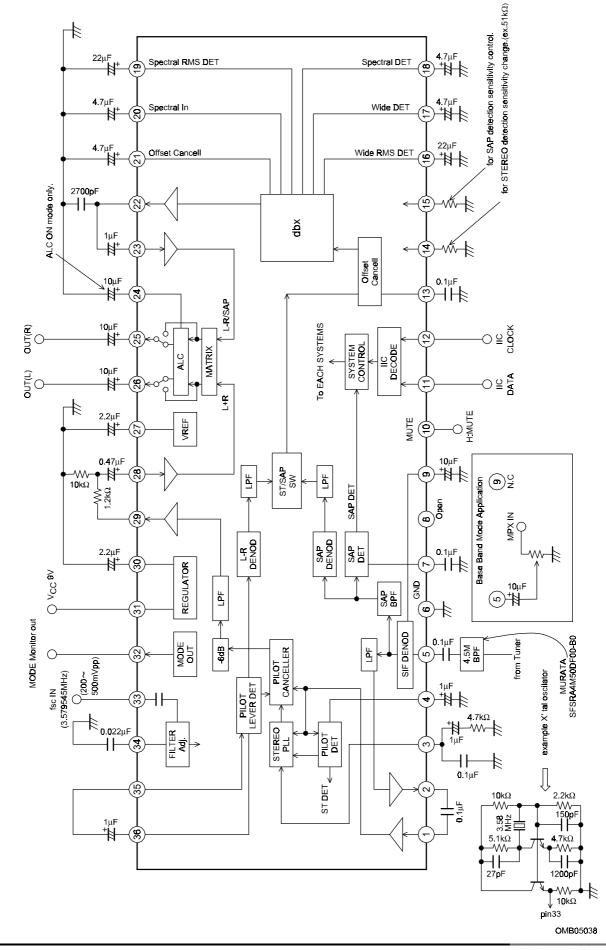

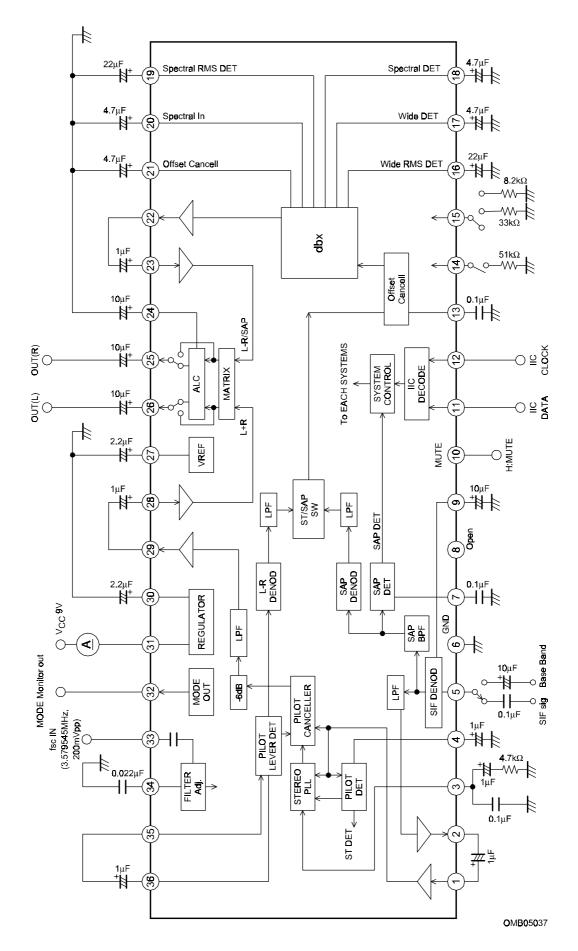

#### **Block Diagram and Application Circuit Example**

www.DataSheet4U.com No.A0015-4/16

#### 00p-1 (Normally use : group-1 only )

|   | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | Condition            |

|---|----|----|----|----|----|----|----|----|----------------------|

| r |    |    |    |    |    |    | 0  | 0  | Stereo               |

|   |    |    |    |    |    |    | 0  | 1  | SAP                  |

|   |    |    |    |    |    |    | 1  | 0  | Both                 |

|   |    |    |    |    |    |    | 1  | 1  | Prohibit             |

|   |    |    |    |    |    | 0  |    |    | Normal (Auto det)    |

|   |    |    |    |    |    | 1  |    |    | Forced Mono          |

| r |    |    |    |    | 0  |    |    |    | Normal (MUTE off)    |

|   |    |    |    |    | 1  |    |    |    | MUTE                 |

| , |    |    |    | 0  |    |    |    |    | ALC off (Through)    |

|   |    |    |    | 1  |    |    |    |    | ALC on               |

|   |    |    | 0  |    |    |    |    |    | SAP LEVEL-1          |

|   |    |    | 1  |    |    |    |    |    | SAP LEVEL-2          |

| , |    | 0  |    |    |    |    |    |    | SIF mode             |

|   |    | 1  |    |    |    |    |    |    | Base Band mode       |

| , | 0  |    |    |    |    |    |    |    | Fix                  |

|   | 1  |    |    |    |    |    |    |    | Prohibit (TEST MODE) |

\*: Initial condition

#### Read out data

| D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | Condition  |

|----|----|----|----|----|----|----|----|------------|

|    |    | 0  | 0  | 0  | 0  | 0  | 0  | Fixed      |

|    | 0  |    |    |    |    |    |    | Normal     |

|    | 1  |    |    |    |    |    |    | SAP det    |

| 0  |    |    |    |    |    |    |    | Normal     |

| 1  |    |    |    |    |    |    |    | Stereo det |

#### **Test mode condition**

When STOP condition transform at Grp-1 data-end, controlled NORMAL mode. Grp-2(Only test condition: Normally, this data is no-need)

| D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | Condition/Monitor position |

|----|----|----|----|----|----|----|----|----------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Normal (Usually, Fixed)    |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | TEST-1 SIF output          |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | TEST-2 SAP BPF             |

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | TEST-3 SAP VCO             |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | TEST-4 ST VCO              |

| 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | TEST-5 ADJ VCO             |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | TEST-6 dbx input           |

| 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | TEST-7 L-R Demod output    |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | TEST-8 Pilot cancel        |

| 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | TEST-9 dbx 2.19k LPF       |

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | TEST-10 dbx 408 LPF        |

| 0  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | TEST-11 dbx DET 10k LPF    |

| 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | TEST-12 dbx SPEC 7.6k LPF  |

| 0  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | TEST-13 dbx SPEC output    |

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | TEST-14 (No operation)     |

| 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | TEST-15 (No operation)     |

#### **Pin Functions**

|     | unctions     |                         |                                              |                       |

|-----|--------------|-------------------------|----------------------------------------------|-----------------------|

|     |              | DC voltage              |                                              |                       |

| No. | Pin function | AC level                | Input/output form                            | Reference             |

| 1   | PC_DC_IN     | DC: 3.8V<br>AC: 2.4Vp-p | Vcc<br>Vcc                                   | AC coupling (Input)   |

| 2   | PC_DCOUT     | DC: 3.8V<br>AC: 2.4Vp-p | 500Ω<br>1kΩ<br>1kΩ<br>1kΩ<br>0MP05005        | AC coupling (Output)  |

| 3   | PCSTFILT     | DC: 3.8V                |                                              | Stereo VCO PLL filter |

| 4   | PCPLDET      | DC: 3.8V                |                                              | Pilot level detect    |

| 5   | PISIF        | DC: 3.7V                | 5<br>500Ω<br>55KΩ<br>500Ω<br>1kΩ<br>0MP05008 | Signal input          |

www.DataSheet4U.com

| Continued | I from preceding pag | ge.        |                                      |                          |

|-----------|----------------------|------------|--------------------------------------|--------------------------|

| No.       | Pin function         | DC voltage | Input/output form                    | Reference                |

|           |                      | AC level   |                                      |                          |

| 6         | GND                  |            |                                      | CAD corrier lowel detect |

|           | CSAPDET              | DC: 2.8V   |                                      | SAP carrier level detect |

| 8         | NC                   |            |                                      | No connect               |

| 9         | PC FIL               | DC: 2.9V   |                                      | SIF offset cancel        |

| 10        | MUTE                 | DC: 0V     |                                      | MUTE = 5V                |

| 11        | SDA                  | 5V         |                                      | Serial data input        |

| 12        | SCL                  | 5V         | (12)<br>1kΩ<br>1kΩ<br>1m<br>0MP05013 | Serial clock input       |

| Continued | from preceding pag | je.        |                                          |                                                                  |

|-----------|--------------------|------------|------------------------------------------|------------------------------------------------------------------|

| No.       | Pin function       | DC voltage | Input/output form                        | Reference                                                        |

|           |                    | AC level   |                                          |                                                                  |

| 13        | PC DBXIN           | DC: 2.5V   | 450kΩ<br>450kΩ<br>13<br>200Ω<br>0MP05014 | Offset cancel filter                                             |

| 14        | PSTSENS            | DC: 3.1V   |                                          | Stereo det sensitivity change                                    |

|           |                    |            |                                          | OPEN = default<br>Insert resistor(30k or over) = Low sensitivity |

| 15        | PSAPSENS           | DC: 3.1V   |                                          | SAP detect sensitivity control<br>OPEN = default                 |

|           |                    |            |                                          | controlled by insert resistor<br>* see electrical reference      |

| 16        | PCTNWID            | DC: 4.0V   |                                          | dbx RMS detect(wide band)                                        |

| 17        | PCDETWID           | DC: 3.8V   | 5kΩ<br>17<br>0MP05018                    | dbx wide detect                                                  |

| Continued | 1 from preceding pag | ge                       |                                                                      |                                    |

|-----------|----------------------|--------------------------|----------------------------------------------------------------------|------------------------------------|

| No.       | Pin function         | DC voltage               | Input/output form                                                    | Reference                          |

|           |                      | AC level                 |                                                                      |                                    |

| 18        | PCTIMSPE             | DC: 3.8V                 | 18 → ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                             | dbx spectral detect                |

| 19        | PCDETSPE             | DC: 3.8V                 | · -•-                                                                | dbx RMS detect (Spectral band)     |

|           |                      |                          |                                                                      |                                    |

| 20        | PCSPECIN             | DC: 3.8V                 | 20)<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ<br>σ | dbx main signal V/I convert filter |

| 21        | PCDOSPE              | DC: 3.8V<br>AC: 220mVp-p |                                                                      | Offset cancel filter               |

|           |                      |                          | 7777 OMP05022                                                        |                                    |

| 22        | PCDBXOUT             | DC: 3.8V<br>AC: 220mVp-p |                                                                      | AC coupling (Output)               |

| 23        | PCDBX_IN             |                          | 500Ω<br>1kΩ<br>1kΩ<br>1kΩ<br>1kΩ<br>0MP05023                         | AC coupling (Input)                |

| Continued | l from preceding pag | e.           |                                                                                                                            |                                                                  |

|-----------|----------------------|--------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| No.       | Pin function         | DC voltage   | Input/output form                                                                                                          | Reference                                                        |

| INO.      | Pin function         | AC level     | inputoulput form                                                                                                           | Reference                                                        |

| 24        | PCALCFIL             | DC: 0.6V     | 2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>150Ω<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2kΩ<br>2k | ALC filter<br>* When ALC function no-use, this terminal is open. |

| 25        | PORCH                | DC: 3.8V     | OMPU5U24                                                                                                                   | Line out R                                                       |

| 25        | FURCH                | AC: 1.4mVp-p | 200Ω<br>200Ω<br>25<br>OMP05025                                                                                             |                                                                  |

| 26        | POLCH                | DC: 3.8V     |                                                                                                                            | Line out L                                                       |

|           |                      | AC: 1.4mVp-p | 200Ω<br>200Ω<br>26<br>OMP05026                                                                                             |                                                                  |

| 27        | PCREG                | DC: 3.8V     |                                                                                                                            | Reference Voltage                                                |

|           |                      |              |                                                                                                                            |                                                                  |

| Continued | l from preceding pag | e.                                       |                                                                     |                                                                             |

|-----------|----------------------|------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------|

| No.       | Pin function         | DC voltage                               | Input/output form                                                   | Reference                                                                   |

|           |                      | AC level                                 |                                                                     |                                                                             |

| 28        | PMAIN_IN             | DC: 3.5V<br>AC: 220mVp-p                 | Vcc                                                                 | AC coupling (Input)                                                         |

| 29        | PMAINOUT             | DC: 3.8V                                 |                                                                     | AC coupling (Output)                                                        |

|           |                      | AC: 220mVp-p                             | СМР05028                                                            |                                                                             |

| 30        | PCREG76              | DC: 1.2V                                 |                                                                     | Regulator                                                                   |

| 31        | VCC                  |                                          |                                                                     |                                                                             |

| 32        | POLED                | DC*<br>* See Mode<br>table               | 32<br>500Ω<br>5КΩ<br>5КΩ<br>5КΩ<br>0МР05030                         | Mode out<br>MONO = 0.9V<br>SAP = 2.0V<br>STEREO = 3.0V<br>STEREO+SAP = 3.8V |

| 33        | PICLKFSC             | DC: 0V<br>AC*<br>* 200mVp-p<br>Recommend | 33<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- | Fsc input<br>3.579545MHz, 200mVp-p                                          |

| Continued | 1 from preceding pag | ge.                        |                   |                                 |  |  |

|-----------|----------------------|----------------------------|-------------------|---------------------------------|--|--|

| No.       | Pin function         | DC voltage                 | Input/output form | Peference                       |  |  |

|           |                      | AC level Input/output form |                   | Reference                       |  |  |

| 34        | PCDJFIL              | DC: 2.5V                   |                   | Filter adjustment signal detect |  |  |

| 35        | PCPLC                | DC: 6.3V                   |                   | Pilot canceller reference-1     |  |  |

| 36        | PCPLC2               | DC: 6.3V                   |                   | Pilot canceller reference-2     |  |  |

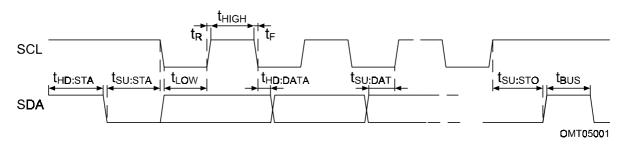

## Serial Control (I<sup>2</sup>C)

## (1) Data Transfer Manual

This LSI adopts control method ( $I^2C$  -BUS) with serial data, and controlled by two terminals which called SCL (serial clock) and SDA (serial data). At first, set up <sup>\*1</sup> the condition of starting data transfer, and after that, input 8 bit data to SDA terminal with synchronized SCL terminal clock. The order of transferring is first, MSB (the Most Scale of Bit), and save the order. The 9th bit takes ACK (Acknowledge) period, during SCL terminal takes 'H', this LSI pull down the SDA terminal. After transferred the necessary data, two terminals lead to set up and of <sup>\*2</sup> data transfer stop condition, thus the transfer comes to close.

\*1 Defined by SCL rise down SDA during 'H' period.

\*2 Defined by SCL rise up SDA during 'H' period.

#### (2) Transfer Data Format

After transfer start condition, transfers slave address (1000000\*) to SDA terminal, control data, then, stop condition (See figure 1).

Slave address is made up of 7bits, <sup>\*3</sup> <u>8th bit</u> shows the direction of transferring data, if it is "L", takes write mode (As this LSI side, this is input operation mode), and in case of 'H', reading mode (As this LSI side, this is output operation mode).

Data works with all of bit, transfer the stop condition before stop 8bit transfer, and to stop transfer, it will be canceled the transfer dates.

\*3 It is called R/W bit.

#### Fig.1 DATA STRUCTURE " WRITE " mode

|  | START Condition | Slave Address | R/W<br>L | ACK | Control data | ACK | STOP condition |

|--|-----------------|---------------|----------|-----|--------------|-----|----------------|

|--|-----------------|---------------|----------|-----|--------------|-----|----------------|

#### Fig.2 DATA STRUCTURE " READ " mode

| START condition Slave Address HW | ACK | Internal Data* | ACK | STOP condition |

|----------------------------------|-----|----------------|-----|----------------|

|----------------------------------|-----|----------------|-----|----------------|

\* Output 5bits data as follows;

bit8 is result of STERO DET (H: STEREO) bit7 is result of SAP DET (H: SAP) bit6 to bit1 are fixed to "L"

### (3) Initialize

This LSI is initialized for circuit protection. Initial condition is "0 (all bits)".

| Parameter                                                                        | Symbol               | Min  | Max | Unit |

|----------------------------------------------------------------------------------|----------------------|------|-----|------|

| LOW level input voltage                                                          | VIL                  | -0.5 | 1.5 | V    |

| HIGH level input voltage                                                         | ∨I <sub>IH</sub>     | 3.0  | 5.5 | V    |

| LOW level output current                                                         | I <sub>OL</sub>      |      | 3.0 | mA   |

| SCL clock frequency                                                              | <sup>f</sup> SCL     | 0    | 100 | kHz  |

| Set-up time for a repeated START condition                                       | <sup>t</sup> SU: STA | 4.7  |     | μs   |

| Hold time START condition. After this period, the first clock pulse is generated | <sup>t</sup> HD: STA | 4.0  |     | μs   |

| LOW period of the SCL clock                                                      | <sup>t</sup> LOW     | 4.7  |     | μs   |

| Rise time of both SDA and SDL signals                                            | <sup>t</sup> R       | 0    | 1.0 | μs   |

| HIGH period of the SCL clock                                                     | <sup>t</sup> HIGH    | 4.0  |     | μs   |

| Fall time of both SDA and SDL signals                                            | <sup>t</sup> F       | 0    | 1.0 | μs   |

| Data hold time                                                                   | <sup>t</sup> HD: DAT | 0    |     | μs   |

| Data set-up time                                                                 | <sup>t</sup> SU: DAT | 250  |     | ns   |

| Set-up time for STOP condition                                                   | <sup>t</sup> SU: STO | 4.0  |     | μs   |

| BUS free time between a STOP and START condition                                 | <sup>t</sup> BUF     | 4.7  |     | μs   |

## **Timing Chart**

#### **Measurement Circuit**

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, of otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of October, 2005. Specifications and information herein are subject to change without notice.