# L8C201/202/203/204

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

#### **FEATURES**

- ☐ First-In/First-Out (FIFO) using **Dual-Port Memory**

- ☐ Advanced CMOS Technology

- ☐ High Speed to 10 ns Access Time

- ☐ Asynchronous and Simultaneous Read and Write

- ☐ Fully Expandable by both Word Depth and/or Bit Width

- ☐ Empty and Full Warning Flags

- ☐ Half-Full Flag Capability

- ☐ Auto Retransmit Capability

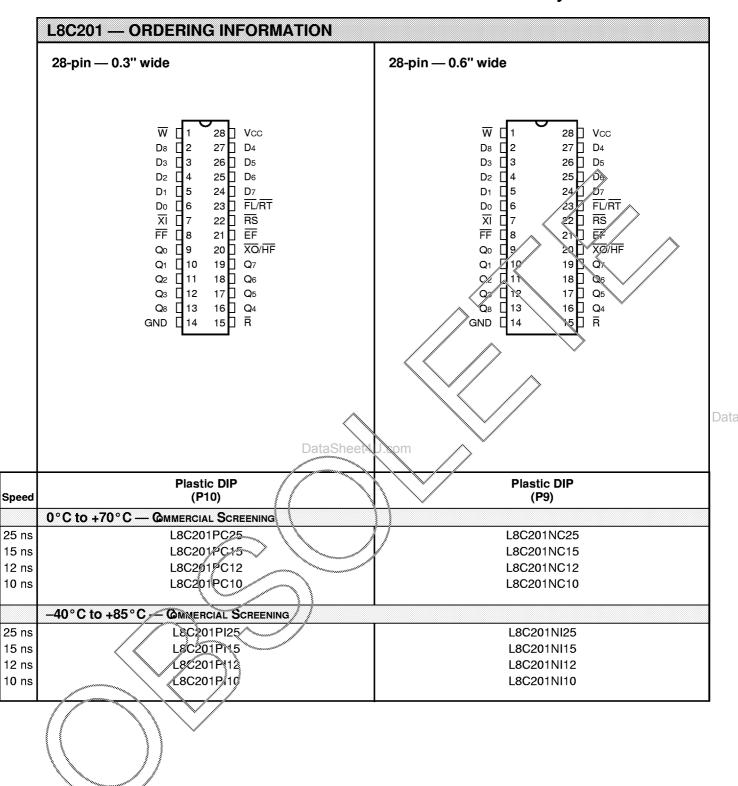

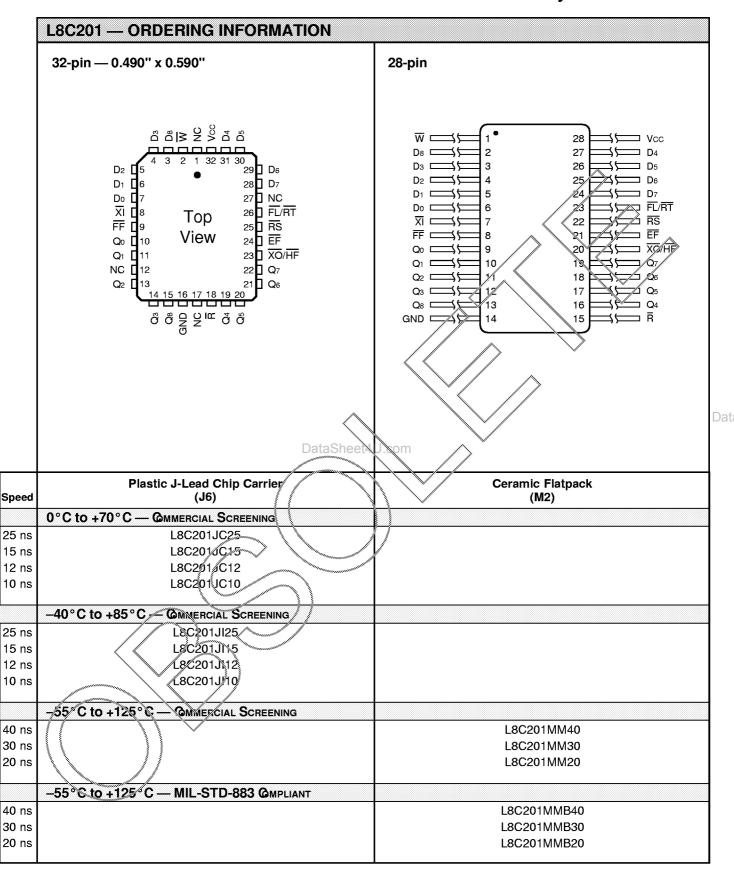

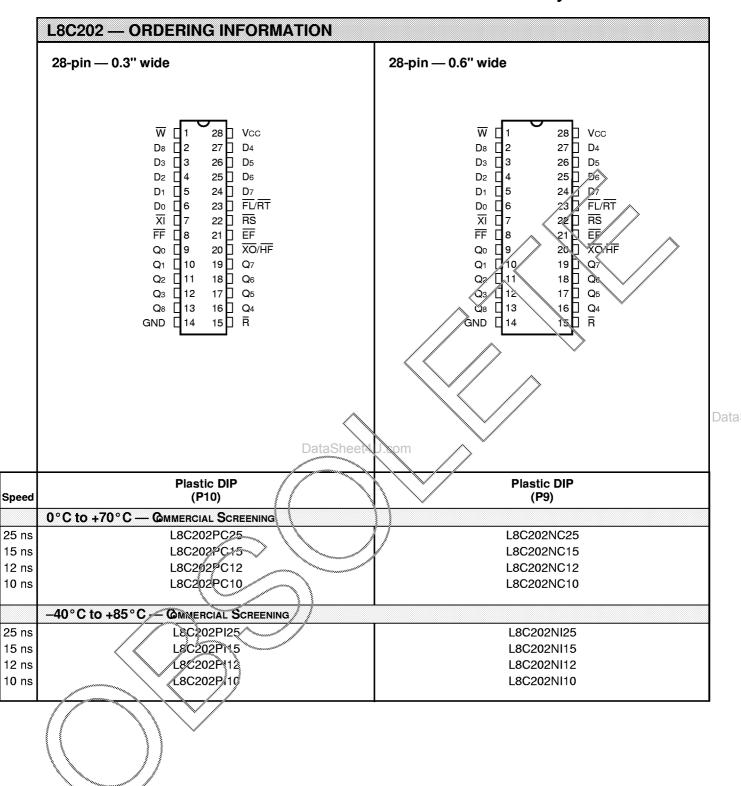

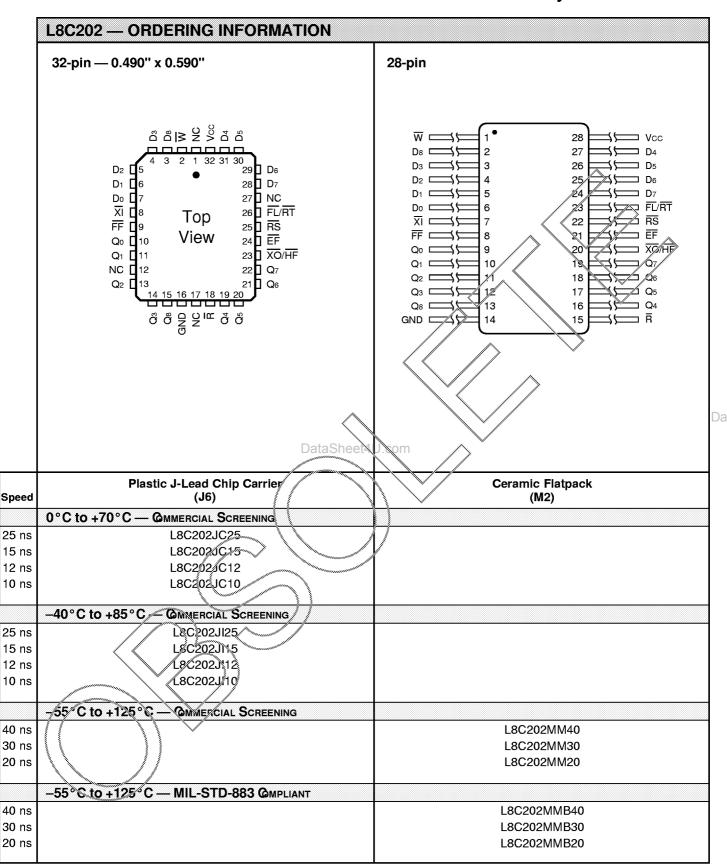

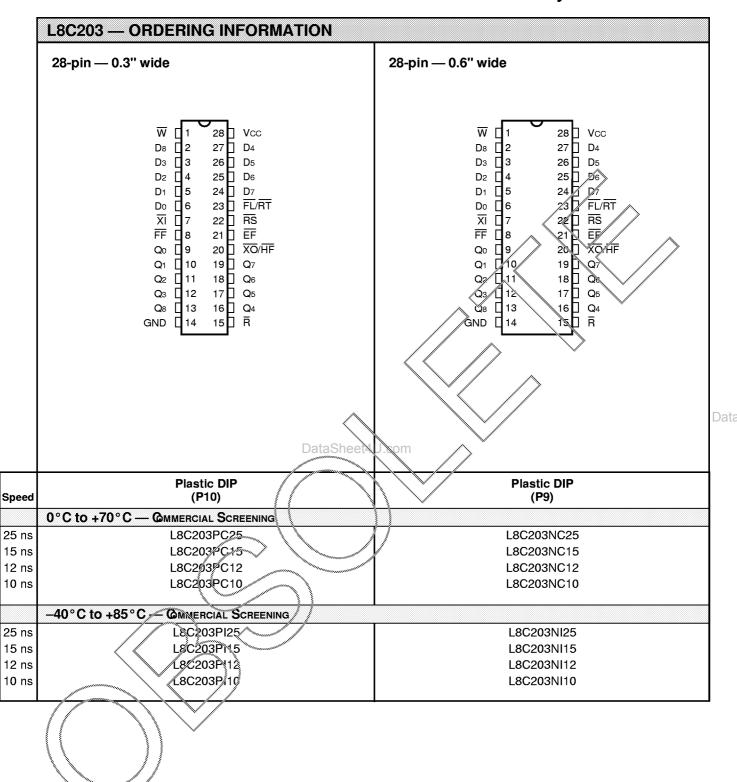

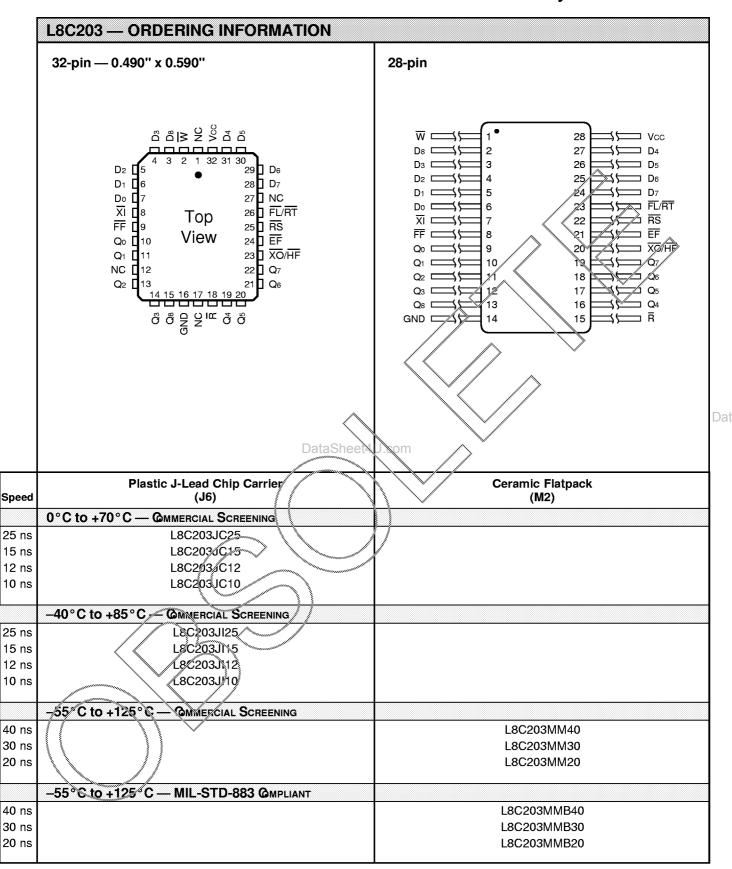

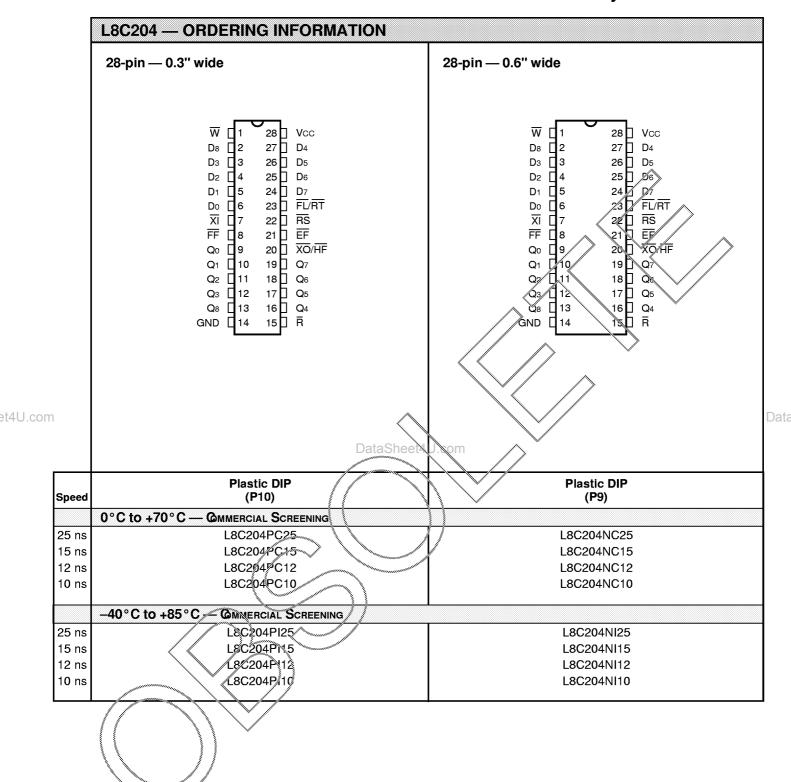

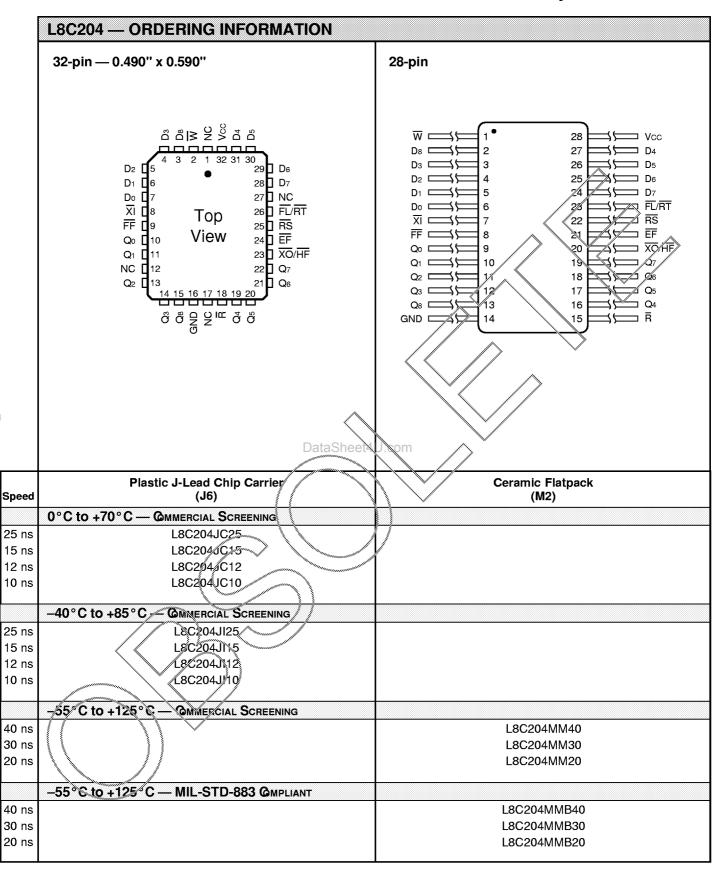

- ☐ Package Styles Available:

- 28-pin Plastic DIP

- 32-pin Plastic LCC

- 28-pin Ceramic Flatpack

#### DESCRIPTION

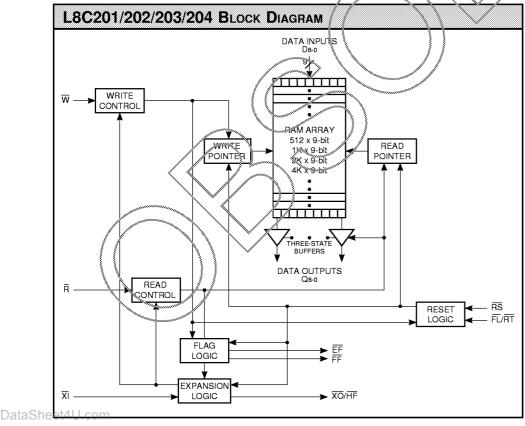

The L8C201, L8C202, L8C203, and L8C204 are dual-port First-In/First-Out (FIFO) memories. The FIFO memory products are organized as:

L8C201 — 512 x 9-bit

L8C202 — 1024 x 9-bit

L8C203 — 2048 x 9-bit

L8C204 — 4096 x 9-bit

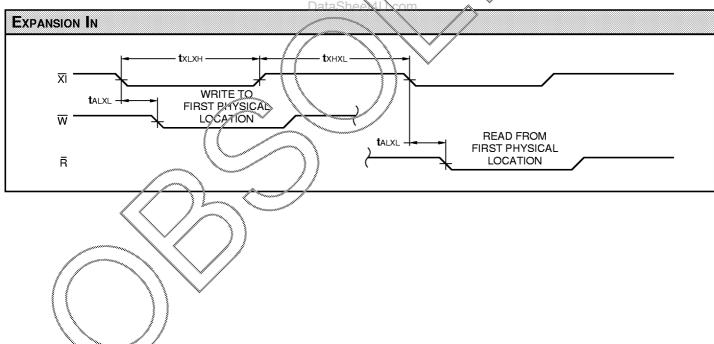

Each device utilizes a special algorithm that loads and empties data on a firstin/first-out basis. Full and Empty flags are provided to prevent data overflow and underflow. Three additional pins are also provided to allow for unlimited expansion in both word size and depth. Depth Expansion does not regultin a flow-through penalty. Multiple devices are connected with the data and control signals in parallel. The active device is determined by the Expansion In  $(\overline{XI})$ and Expansion Out (XO) signals which are daisy chained from device to device.

1

The read and write operations are internally sequential through the use of ring pointers. No address information is required to load and unload data. The write operation occurs when the Write (Ѿ) signal is LOW. Read occurs/when Read/(R) goes LOW. The nine data outputs go to the high impedance state when R is HIÇA, Retransmit (RT) capability allows for reset of the read pointer when Rk is pulsed LOW, allowing for retransivission of data from the beginning. Read Enable ( $\overline{R}$ ) and Write Enable (W) must both be HIGH during a retransmit cycle, and then  $ar{\mathbb{R}}$ is used to access the data. A Half-Full (HF) output flag is available in the single device and width expansion ൂര് ്യൂes. In the depth expansion configuration, this pin provides the Expansion Out ( $\overline{XO}$ ) information which is used to tell the next FIFO that it will be activated.

These FIFOs are designed to have the fastest data access possible. Even in lower cycle time applications, faster access time can eliminate timing bottlenecks as well as leave enough margin to allow the use of the devices without external bus drivers.

The FIFOs are designed for those applications requiring asychronous and simultaneous read/writes in multiprocessing and rate buffer applications.

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

#### SIGNAL DEFINITIONS

#### Inputs

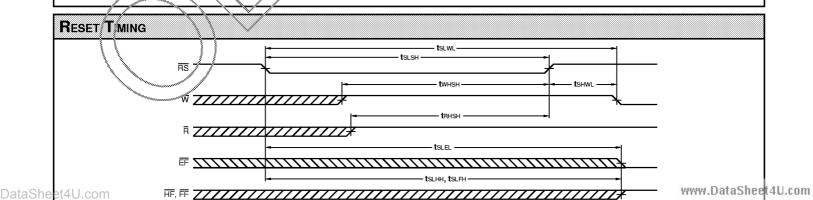

$\overline{RS}$  — Reset

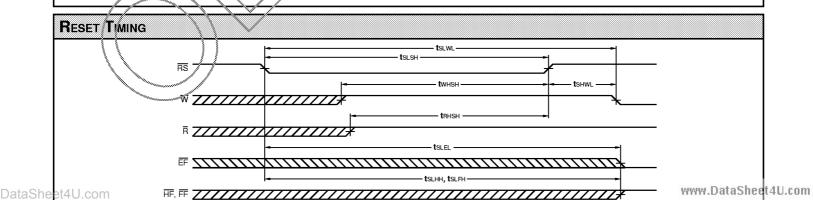

Reset is accomplished whenever the Reset ( $\overline{RS}$ ) input is taken to a LOW state. During reset, both internal read and write pointers are set to the first location. A reset is required after power-up before a write operation can take place. Both the Read Enable ( $\overline{R}$ ) and Write Enable ( $\overline{W}$ ) inputs must be in the HIGH state during the window shown (i.e., tWHSH before the rising edge of  $\overline{RS}$ ) and should not change until tSHWL after the rising edge of  $\overline{RS}$ . Hall-Full Flag ( $\overline{HF}$ ) will be reset to high after Reset ( $\overline{RS}$ ).

#### $\overline{W}$ — Write Enable

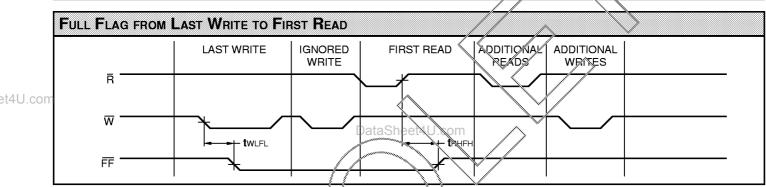

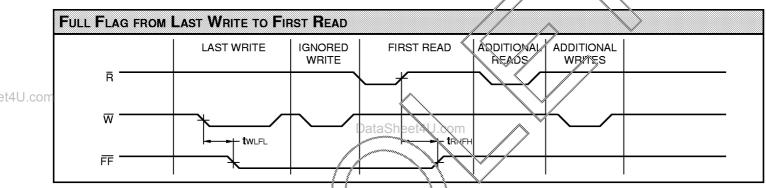

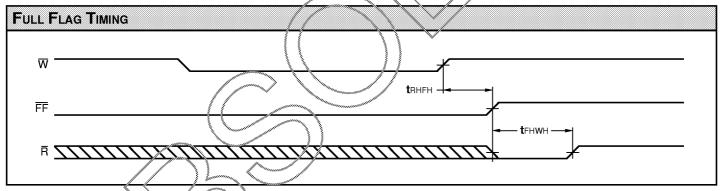

A write cycle is initiated on the falling edge of this input if the Full Flag (FF) et4U.comis not set. Data setup and hold time must be adhered to with respect to the rising edge of the Write Enable (W). Data is stored in the RAM array sequentially and independently of any on-going read operation.

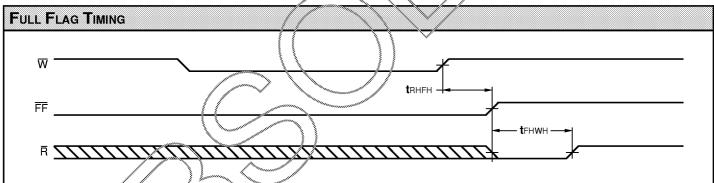

To prevent data overflow, the Full Flag ( $\overline{FF}$ ) will go LOW, inhibiting further write operations. Upon the completion of a valid read operation the Full Flag ( $\overline{FF}$ ) will go HIGH after tRHFH, allowing a valid write to begin. When the FIFO is full, the internal write pointer is blocked from  $\overline{W}$ , so external changes in  $\overline{W}$  will not affect the FIFO when it is full.

#### R — Read Enable

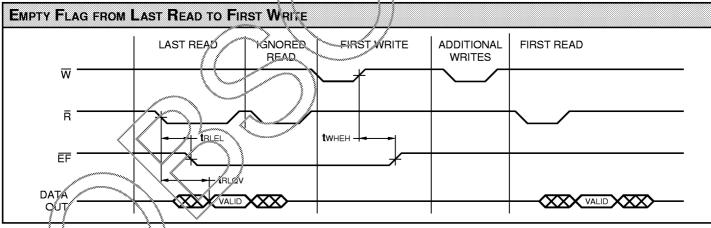

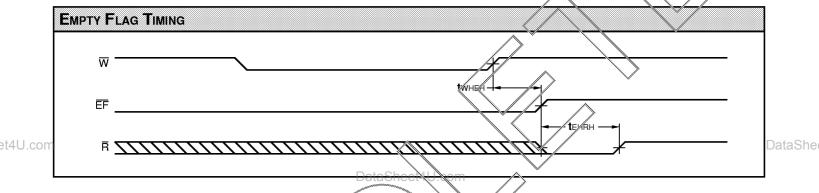

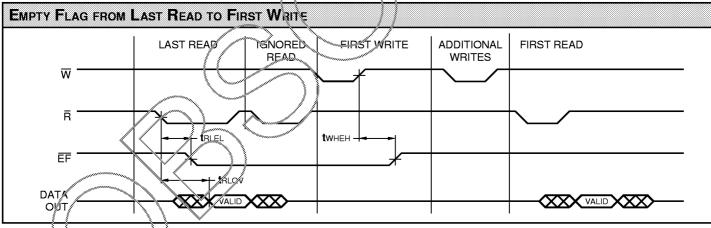

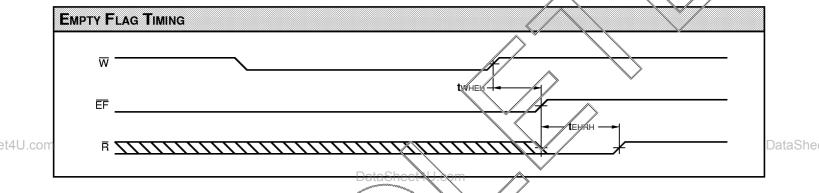

A read cycle is initiated on the falling edge of the Read Enable (\$\overline{R}\$) provided the Empty Flag (\$\overline{EF}\$) is not set. The data is accessed on a First-In/First-Out basis, independent of any ongoing write operation. After Read Enable (\$\overline{R}\$) goes HIGH, the Data Outputs (D8-0) will return to a high impedance condition until the next read operation. When all the data has been read from the FIFO, the Empty Flag (\$\overline{EF}\$) will go LOW, allowing the

"final" read cycle but inhibiting further read operations with the data outputs remaining in a high impedance state. Once a valid write operating has been accomplished, the Empty Flag ( $\overline{EF}$ ) will go HIGH after tWHEH and a valid read can then begin. When the FIFO is empty, the internal read pointer is blocked from  $\overline{R}$  so external changes in  $\overline{R}$  will not affect the FIFO.

#### $\overline{FL}/\overline{RT}$ — First Load/Retransmit

This is a dual-purpose input. In the Depth Expansion Mode, this pin is grounded to indicate that it is the first loaded (see Operating Modes). In the Single Device Mode, this pin acts as the retransmit input. The Single Device Mode is initiated by grounding the Expansion In  $(\overline{XI})$ .

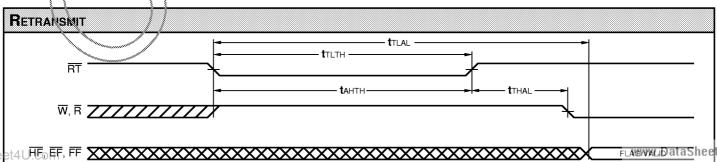

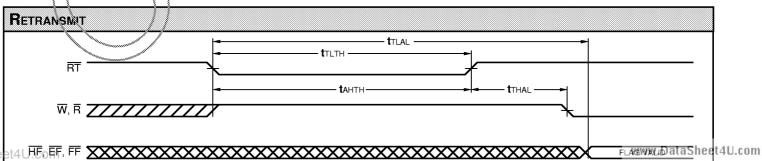

The FIFOs can be made to retransmit data when the Retransmit Enable control (RT) input is pulsed LOW. A retransmit operation will set the internal read pointer to the first location and will not affect the write pointer, Read Enable  $(\overline{\mathbb{R}})$  and Write Enable  $(\overline{\mathbb{W}})$ must be in the HIGH state during retransmit. This feature is useful when iess than the full memory has been written between resets Retransmit will affect the Half-Full-Flag (HF), depending on the relative locations of the read and write pointers. The retransmit feature is not compatible with the Depth Expansion Mode.

#### XI — Expansion In

This input is a dual-purpose pin. Expansion In  $(\overline{XI})$  is grounded to indicate an operation in the single device mode. Expansion In  $(\overline{XI})$  is connected to Expansion Out  $(\overline{XO})$  of the previous device in the Depth Expansion or Daisy Chain Mode.

#### D8-0 — Data Input

Data input signals for 9-bit wide data. Data has setup and hold time requirements with respect to the rising edge of  $\overline{W}$ .

2

#### Outputs

FF — Full Flag

The Full Flag ( $\overline{FF}$ ) will go LOW, inhibiting further write operations, indicating that the device is full. If the read pointer is not moved after Reset ( $\overline{RS}$ ), the Full Flag ( $\overline{FF}$ ) will go LOW after 512 writes for the L8C201, 1024 writes for the L8C203, and 4096 writes for the L8C204.

### EF — Empty Flag

The Empty Flag (ET) will go LOW, inhibiting further read operations, when the read pointer is equal to the write pointer, indicating that the device is empty.

💯 /XO/HF 🗻 Expansion Out/Half-Full Flag

This is a dual-purpose output. In the Single Device Mode, when Expansion DataShe In (XI) is grounded, this output acts as an indication of a half-full memory.

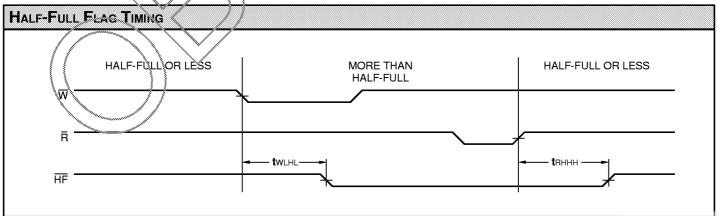

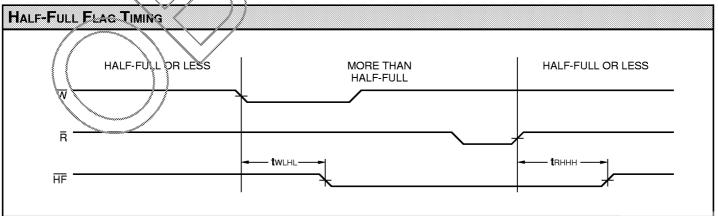

After half of the memory is filled and at the falling edge of the next write operation, the Half-Full Flag (HF) will be set to LOW and will remain set until the difference between the write pointer and read pointer is less than or equal to one-half of the total memory of the device. The Half-Full Flag (HF) is then deasserted by the rising edge of the read operation.

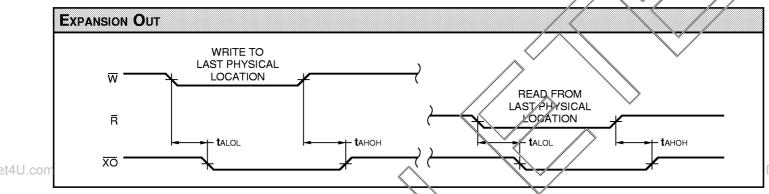

In the Depth Expansion Mode, Expansion In  $(\overline{XI})$  is connected to Expansion Out  $(\overline{XO})$  of the previous device. This output acts as a signal to the next device in the daisy chain by providing a pulse to the next device when the previous device reaches the last location of memory.

#### *Q8-0* — *Data Output*

Data outputs for 9-bit wide data. This data is in a high impedance condition whenever Read Enable  $(\overline{R})$  is in a HIGH state or the device is empty.

www.DataSheet4U.com

FIFO Products

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

#### **OPERATING MODES**

Single Device Mode

A single FIFO may be used when the application requirements are for the number of words in a single device. The FIFOs are in a Single Device Configuration when the Expansion In  $(\overline{XI})$  control input is grounded. In this mode the Half-Full Flag  $(\overline{HF})$ , which is an active-low output, is the active function of the combination pin  $\overline{XO}/\overline{HF}$ .

#### Width Expansion Mode

et4U.coi

Word width may be increased simply by connecting the corresponding input control signals of multiple devices. Status flags (EF, FF, and HF) can be detected from any one device. Any word width can be attained by adding additional FIFOs. Flag detection is accomplished by monitoring the FF, EF, and HF signals on either (any) device used in the width expansion configuration. Do not connect any output signals together.

#### Depth Expansion (Daisy Chain) Mode

The FIFOs can easily be adapted to applications where the requirements are for greater than the number of words in a single device. Any depth can be attained by adding additional FIFOs. The FIFOs operates in the Depth Expansion configuration when the following conditions are mel:

- 1. The first device must be designated by grounding the First Load (FL) control input.

- 2. All other devices must have \( \overline{\pi} \) in the HIGH state.

- 3. The Expansion Out (NO) pin of each device must be tied to the Expansion In (NI) pin of the next device with the last device connecting back to the first.

4. External logic is needed to generate a composite Full Flag (FF) and Empty Flag (EF). This requires the ORing of all EFs and ORing of all FFs (i.e., all must be set to generate the correct composite FF or EF).

5. The Retransmit (RT) function and Half-Full Flag (HF) are not available in the Depth Expansion Mode.

#### Bidirectional Mode

Applications which require data buffering between two systems (each system capable of read and write operations) can be achieved by pairing FIFOs. Care must be taken to assure that the appropriate flag is monitored by each system (i.e.,  $\overline{FF}$  is monitored on the device when  $\overline{W}$  is used:  $\overline{EF}$  is monitored on the device when  $\overline{R}$  is used). Both Depth Expansion and Width Expansion may be used in this mode.

DataSheet4U.com

3

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

| MAXIMUM RATINGS Above which useful life may be impaired (Notes 1 | , 2)             |

|------------------------------------------------------------------|------------------|

| Storage temperature                                              | 65°C to +150°C   |

| Operating ambient temperature                                    | –55°Cto +125°C   |

| Vcc supply voltage with respect to ground                        | 0.5 V to +7.0 V  |

| Input signal with respect to ground                              | –0.5 V to +7.0 V |

| Signal applied to high impedance output                          | –3.0 V to +7.0 V |

| Output current into low outputs                                  | 25 mA            |

| ·                                                                | A                |

#### OPERATING CONDITIONS To meet specified electrical and switching characteristics

Mode

Active Operation, Commercial

Active Operation, Industrial

Active Operation, Military

Temperature Range (Ambient) 0°C to +70°C -40°C to +85°C

-55°C to +125°C

Supply Voltage

4.5 ò **v**cc ≥ 5.5 √ 4.5 ò **v**cc ≤ 5.5 √

4.5 **V≤V**cc ≤ 5.5 V

ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 5)

|              |                           |                                          | L8C20 | 1/202/2 | 203/204             | 1    |

|--------------|---------------------------|------------------------------------------|-------|---------|---------------------|------|

| Symbol       | Parameter                 | Test Condition                           | Min   | Тур     | Max                 | Unit |

| <b>V</b> OH  | Output High Voltage       | VCC = 4.5 V, IOH = -2.0 MA               | 2.4   |         |                     | V    |

| <b>V</b> OL  | Output Low Voltage        | Vcc = 4.5 V, lor=8.0 mA                  |       |         | 0.4                 | V    |

| <b>V</b> iH  | Input High Voltage        |                                          | 2.0   |         | <b>V</b> cc<br>+0.3 | V    |

| <b>V</b> IL  | Input Low Voltage         | (Note 3)                                 | -0.5  |         | 0.8                 | V    |

| lix          | Input Leakage Current     | Ground ≤ Vin ≤ Vcc                       |       |         | ±1                  | μА   |

| loz          | Output Leakage Current    | Ř ≥ Víh, GND ≤ Vout ≤ Vcc                |       |         | ±10                 | μА   |

| ICC2         | Vcc Current, T/L mactive  | All Inputs = VIH MIN (Note 6)            |       |         | 15                  | mA   |

| ICC3         | Vcc Current, CMOS Stapeby | All Inputs = VCC (Note 12)               |       |         | 5                   | mA   |

| CIN          | Input Capacitance         | Ambient Temp = 25°C, <b>V</b> cc = 4.5 V |       |         | 5                   | pF   |

| <b>C</b> OUT | Output Capacitance        | Test Frequency = 1 MHz (Note 9)          |       |         | 7                   | pF   |

|        |                     |                |    | L8C | 201/202 | 2/203/2 | 04- |     |     |      |

|--------|---------------------|----------------|----|-----|---------|---------|-----|-----|-----|------|

| Symbol | Parameter           | Test Condition | 40 | 30  | 25      | 20      | 15  | 12  | 10  | Unit |

| ICC1   | Vcc Current, Active | (Note 5)       | 90 | 95  | 100     | 110     | 120 | 150 | 180 | mA   |

DataSheet4U.com www.DataSheet4U.com

FIFO Products

et4U.com

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Commercial and Industrial Operating Range

|               |                                                         |          |     |     | L8C2 | 201/20 | 2/203 | /204– |     |     |

|---------------|---------------------------------------------------------|----------|-----|-----|------|--------|-------|-------|-----|-----|

|               |                                                         |          | 2   | 5   | 1    | 5      | 1     | 2     | 10  | 0   |

| Symbol        | Parameter                                               |          | Min | Max | Min  | Max    | Min   | Max   | Min | Max |

| <b>t</b> rlrl | Read Cycle Time (MHz)                                   |          | 35  |     | 25   |        | 20    |       | 15  |     |

| <b>t</b> RLQV | Read Low to Output Valid (Access Time)                  |          |     | 25  |      | 15     |       | 12    |     | 10  |

| <b>t</b> rhrl | Read High to Read Low (Notes 8, 9)                      |          | 10  |     | 10   |        | 8/    |       | 5   |     |

| <b>t</b> rlrh | Read Low to End of Read Cycle (Notes 8, 9)              |          | 25  |     | 15   |        | 12    |       | 10  |     |

| <b>t</b> rhqv | Read High to Output Valid                               |          | 5   |     | 5 *  |        | 5 //  |       | 5   |     |

| <b>t</b> rhqz | Read High to Output High Z (Note 14)                    |          |     | 20  |      | 15     |       | 15    |     | 15  |

| twlwl         | Write Cycle Time (Note 9)                               |          | 35  |     | 25   | 1      | 20    |       | 15  |     |

| <b>t</b> wLWH | Write Low to Write High (Notes 8, 9)                    |          | 25  |     | 15   |        | 12    |       | 10  |     |

| <b>t</b> whwL | Write High to End of Write Cycle (Notes 8, 9)           |          | 10  |     | ßį   |        | 8     |       | 5   |     |

| <b>t</b> DVWH | Data Valid to Write High (Notes 8, 9)                   |          | //5 |     | 10   |        | 8     |       | 8   |     |

| <b>tw</b> HDX | Write High to Data Change (Notes 8, 9)                  |          | 0   |     | 0    | 1      | 0     |       | 0   |     |

| <b>t</b> slsh | Reset Cycle Time (Notes 9, 10)                          |          | 25/ |     | 15   |        | 12    |       | 10  |     |

| <b>t</b> slwl | Reset Low to Write Low (Notes 9, 10)                    |          | 35  |     | 25   |        | 20    |       | 15  |     |

| <b>t</b> whsh | Write High to Reset High (Notes 9, 10)                  |          | 25  |     | 15   |        | 12    |       | 10  |     |

| <b>t</b> rhsh | Read High to Reset High (Notes 9, 10)                   |          | 25  |     | 15   |        | 12    |       | 10  |     |

| <b>t</b> shwl | Reset High to Write Low (Notes 9, 10)  DataSheet AU Tom |          | 12  |     | 10   |        | 8     |       | 5   |     |

| <b>t</b> SLEL | Reset Low to Empty Flag Low                             |          |     | 25  |      | 15     |       | 12    |     | 10  |

| <b>t</b> slhh | Reset Low to Half-Full Flag High                        |          |     | 25  |      | 15     |       | 12    |     | 10  |

| <b>t</b> SLFH | Reset Low to Full Flag High                             | <b>\</b> |     | 25  |      | 15     |       | 12    |     | 10  |

ASYNCHRONOUS READ AND WRITE OPERATION

R

Q8-0

D8-0

D8-0

DATA-IN VALID

DATA-IN VALID

DATA-IN VALID

DATA-IN VALID

FIFO Products

03/04/99-LDS.8C201/2/3/4-H

DataShe

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Commercial and Industrial Operating Range

| Full/E        | MPTY FLAG AND RETRANSMIT TIMING (ns)                       |       |     |      |       |       |                |     |          |

|---------------|------------------------------------------------------------|-------|-----|------|-------|-------|----------------|-----|----------|

|               |                                                            |       |     | L8C2 | 01/20 | 2/203 | /204           |     |          |

|               |                                                            | 25 15 |     |      | 12    |       | 10             | D   |          |

| Symbol        | Parameter                                                  | Min   | Max | Min  | Max   | Min   | Max            | Min | Max      |

| <b>t</b> rlqv | Read Low to Output Valid (Access Time)                     |       | 25  |      | 15    |       | 12             |     | 10       |

| <b>t</b> RLEL | Read Low to Empty Flag Low                                 |       | 25  |      | 15    |       | 12             |     | 10       |

| <b>t</b> RHFH | Read High to Full Flag High                                |       | 25  |      | 15    |       | 12             |     | 10       |

| twheh         | Write High to Empty Flag High                              |       | 25  |      | 15    |       | 12             |     | 10       |

| twlfl         | Write Low to Full Flag Low                                 |       | 25  | . *  | 15    |       | 1/2            |     | 10       |

| <b>t</b> TLAL | Retransmit Cycle Time                                      | 35    |     | 25   |       | 20/   | and the second | 15) | <b>.</b> |

| <b>t</b> TLTH | Retransmit Low to End of Retransmit Cycle (Notes 8, 9, 10) | 25    |     | 15   | *     | 12    | . //           | 16  |          |

| <b>t</b> ahth | Read/Write High to Retransmit High (Notes 8, 9, 10)        | 25    |     | 75   |       | 12    |                | 10  |          |

| <b>t</b> THAL | Retransmit High to Read/Write Low (Note 9)                 | 10    |     | 18   |       | 8     | W.             | 5   |          |

= FIFO Products

03/04/99-LDS.8C201/2/3/4-H

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Commercial and Industrial Operating Range

| FULL/F                 | ALF-FULL/EMPTY FLAG TIMING (ns)                 |     |     |      |        |             |       |     |     |

|------------------------|-------------------------------------------------|-----|-----|------|--------|-------------|-------|-----|-----|

|                        |                                                 |     |     | L8C2 | 201/20 | 2/203       | /204– |     |     |

|                        |                                                 |     | :5  | 1    | 5      | 12          |       | 1   | 0   |

| Symbol                 | Parameter                                       | Min | Max | Min  | Max    | Min         | Max   | Min | Max |

| <b>t</b> RHFH          | Read High to Full Flag High                     |     | 25  |      | 15     |             | 12    |     | 10  |

| <b>t</b> ehrh          | Read Pulse Width After Empty Flag High          | 25  |     | 15   |        | 12          |       | 10  |     |

| <b>t</b> rhhh          | Read High to Half-Full Flag High                |     | 25  |      | 15     |             | 12    |     | 10  |

| <b>t</b> wheh          | Write High to Empty Flag High                   |     | 25  |      | 15     |             | 12    |     | 10  |

| twlhl                  | Write Low to Half-Full Flag Low                 |     | 25  | . 4  | 15     |             | 1/2   |     | 10  |

| <b>t</b> FH <b>W</b> H | Write Pulse Width After Full Flag High (Note 9) | 25  |     | 15>  |        | <b>1</b> 2/ |       | 10  |     |

DataSheet4U.com www.DataSheet4U.com

03/04/99-LDS.8C201/2/3/4-H

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Commercial and Industrial Operating Range

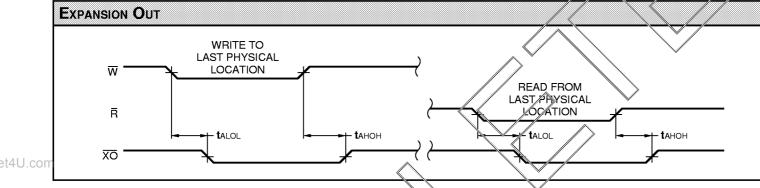

| EXPAN         | sion Timing (ns)                                    |                     |     |     |       |     |     |     |     |  |  |  |

|---------------|-----------------------------------------------------|---------------------|-----|-----|-------|-----|-----|-----|-----|--|--|--|

|               |                                                     | L8C201/202/203/204- |     |     |       |     |     |     |     |  |  |  |

|               |                                                     | 2                   | 25  |     | 5     | 12  |     | 1   | 0   |  |  |  |

| Symbol        | Parameter                                           | Min                 | Max | Min | Max   | Min | Max | Min | Max |  |  |  |

| <b>t</b> ALOL | Read/Write to Expansion Out Low (Note 11)           |                     | 25  |     | 15    |     | 12  |     | 12  |  |  |  |

| <b>t</b> ahoh | Read/Write to Expansion Out High (Note 11)          |                     | 25  |     | 15    |     | 12  |     | 12  |  |  |  |

| <b>t</b> xlxh | Expansion In Pulse Width (Notes 9, 11)              | 25                  |     | 15  | , and | 12  |     | 10  |     |  |  |  |

| <b>t</b> xhxl | Expansion In High to Expansion In Low (Notes 9, 11) | 10                  |     | 10  |       | 10  |     | 10  |     |  |  |  |

| <b>t</b> alxl | Read/Write Low to Expansion In Low (Notes 9, 11)    | 15                  |     | 12  |       | 8 / |     | 8   |     |  |  |  |

DataSheet4U.com www.DataSheet4U.com

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Military Operating Range

|                        | HRONOUS AND RESET TIMING (ns)                         |      | L8C2             | 01/20 | 2/203/   | 204– |     |

|------------------------|-------------------------------------------------------|------|------------------|-------|----------|------|-----|

|                        |                                                       | 4    |                  |       | <u> </u> | 20   |     |

| Symbol                 | Parameter                                             | Min  | Max              | Min   | Max      | Min  | Max |

| <b>t</b> rlrl          | Read Cycle Time (MHz)                                 | 50   |                  | 40    |          | 30   |     |

| <b>t</b> rlqv          | Read Low to Output Valid (Access Time)                |      | 40               |       | 30       |      | 20  |

| <b>t</b> rhrl          | Read High to Read Low (Notes 8, 9)                    | 10   |                  | 19    |          | 10   |     |

| <b>t</b> rlrh          | Read Low to End of Read Cycle (Notes 8, 9)            | 40   |                  | 30    |          | 20   |     |

| <b>t</b> rhqv          | Read High to Output Valid                             | 5    |                  | 5 /   |          | 5    |     |

| <b>t</b> rhqz          | Read High to Output High Z (Note 14)                  |      | 25               |       | 20       |      | 15  |

| twLwL                  | Write Cycle Time (Note 9)                             | 50   | , and the second | 40    |          | 30   |     |

| twLwH                  | Write Low to Write High (Notes 8, 9)                  | 40   |                  | 30    | Y        | 20   |     |

| twhwl                  | Write High to End of Write Cycle (Notes 8, 9)         | 12   |                  | 10    |          | 10   |     |

| <b>t</b> DV <b>W</b> H | Data Valid to Write High (Notes 8, 9)                 | 20   |                  | 18    |          | 12   |     |

| <b>t</b> whdx          | Write High to Data Change (Notes 8, 9)                | 0    |                  | 0     |          | 0    |     |

| <b>t</b> slsh          | Reset Cycle Time (Notes 9, 10)                        | 40   |                  | 30    |          | 20   |     |

| tslwl                  | Reset Low to Write Low (Notes 9, 10)                  | /50> |                  | 40    |          | 30   |     |

| <b>tw</b> HSH          | Write High to Reset High (Notes 9, 10)                | 40   |                  | 30    |          | 20   |     |

| <b>t</b> rhsh          | Read High to Reset High (Notes 9, 10)                 | 40   |                  | 30    |          | 20   |     |

| tshwl                  | Reset High to Write Low (Notes 9, 10) DataSheet U. om | 10   |                  | 10    |          | 10   |     |

| <b>t</b> SLEL          | Reset Low to Empty Flag Low                           |      | 50               |       | 40       |      | 30  |

| tslhh                  | Reset Low to Half-Full Flag High                      |      | 50               |       | 40       |      | 30  |

| tslfh                  | Reset Low to Full Flag High                           |      | 50               |       | 40       |      | 30  |

ASYNCHRONOUS READ AND WRITE OPERATION

RHOV

DATA-OUT VALID

DATA-IN VALID

DATA-IN VALID

DATA-IN VALID

FIFO Products

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Military Operating Range

| FULL/E        | MPTY FLAG AND RETRANSMIT TIMING (ns)                       |             |      |        |     |     |     |

|---------------|------------------------------------------------------------|-------------|------|--------|-----|-----|-----|

|               |                                                            |             | L8C2 | 01/202 |     |     |     |

|               |                                                            | 4           | 0    | 3      | 0   | 20  | 0   |

| Symbol        | Parameter                                                  | Min         | Max  | Min    | Max | Min | Max |

| <b>t</b> RLQV | Read Low to Output Valid (Access Time)                     |             | 40   |        | 30  |     | 20  |

| <b>t</b> RLEL | Read Low to Empty Flag Low                                 |             | 30   |        | 30  |     | 20  |

| <b>t</b> RHFH | Read High to Full Flag High                                |             | 35   |        | 30  |     | 20  |

| <b>t</b> wheh | Write High to Empty Flag High                              |             | 35   |        | 30  |     | 20  |

| twlFL         | Write Low to Full Flag Low                                 |             | 35   |        | 30  |     | 20  |

| <b>t</b> TLAL | Retransmit Cycle Time                                      | <i>x</i> 6> |      | \\\ \\ |     | 36  | >   |

| <b>t</b> TLTH | Retransmit Low to End of Retransmit Cycle (Notes 8, 9, 10) | 40          |      | 30     |     | 20  |     |

| <b>t</b> ahth | Read/Write High to Retransmit High (Notes 8, 9, 10)        | 40          |      | 30     |     | 20  |     |

| <b>t</b> THAL | Retransmit High to Read/Write Low (Note 9)                 | 10          |      | 10     |     | 10  |     |

FIFO Products

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Military Operating Range

| Full/h        | ALF-FULL/EMPTY FLAG TIMING (ns)                 |     |            |        |        |      |                  |

|---------------|-------------------------------------------------|-----|------------|--------|--------|------|------------------|

|               |                                                 |     | L8C2       | 01/202 | 2/203/ | 204– |                  |

|               |                                                 | 4   | 0          | 3      | 0      | 2    | 0                |

| Symbol        | Parameter                                       | Min | Max        | Min    | Max    | Min  | Max              |

| <b>t</b> rhfh | Read High to Full Flag High                     |     | 35         |        | 30     |      | 20               |

| <b>t</b> ehrh | Read Pulse Width After Empty Flag High          | 40  |            | 30     |        | 20   |                  |

| <b>t</b> rhhh | Read High to Half-Full Flag High                |     | 50         |        | 40     |      | 30               |

| <b>tw</b> HEH | Write High to Empty Flag High                   |     | 35         |        | 30     |      | 20               |

| twlhl         | Write Low to Half-Full Flag Low                 |     | <b>(50</b> |        | 49     |      | 30               |

| <b>t</b> FHWH | Write Pulse Width After Full Flag High (Note 9) | 40> |            | 86/    |        | 25   | $\triangleright$ |

DataSheet4U.com www.DataSheet4U.com

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

### SWITCHING CHARACTERISTICS Over Military Operating Range

| Expan:        | sion Timing (ns)                                    |         |                     |        |       |  |  |  |  |  |  |  |

|---------------|-----------------------------------------------------|---------|---------------------|--------|-------|--|--|--|--|--|--|--|

|               |                                                     | L8C     | L8C201/202/203/204- |        |       |  |  |  |  |  |  |  |

|               |                                                     | 40      | 30                  |        | 20    |  |  |  |  |  |  |  |

| Symbol        | Parameter                                           | Min Max | Min N               | lax Mi | n Max |  |  |  |  |  |  |  |

| <b>t</b> alol | Read/Write to Expansion Out Low (Note 11)           | 40      |                     | 30     | 20    |  |  |  |  |  |  |  |

| <b>t</b> ahoh | Read/Write to Expansion Out High (Note 11)          | 40      |                     | 30     | 20    |  |  |  |  |  |  |  |

| <b>t</b> xlxh | Expansion In Pulse Width (Notes 9, 11)              | 40      | /30>                | 20     | )     |  |  |  |  |  |  |  |

| <b>t</b> xhxl | Expansion In High to Expansion In Low (Notes 9, 11) | 10      | 10                  | _ 10   | )     |  |  |  |  |  |  |  |

| <b>t</b> alxl | Read/Write Low to Expansion In Low (Notes 9, 11)    | 10 🗸 🔾  | 10                  | 1(     | )     |  |  |  |  |  |  |  |

www.DataSheet4U.com

DataSheet4U.com

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

| TABLE 1. RESET | AND   | RETRA | NSMIT  | (Single Device Configuration | /Width Expansion Mode) |    |      |    |

|----------------|-------|-------|--------|------------------------------|------------------------|----|------|----|

|                |       | NPUT  | 3///   | INTERNA                      | L STATUS               | 0  | UTPU | ГS |

| MODE           | RS    | RT    | χί     | Read Pointer                 | Write Pointer          | EF | FF   | HF |

| Reset          | 0     | Х     | 9      | Location Zero                | Location Zero          | 0  | 1    | 1  |

| Retransmit     | 1,/// | 0     | o Time | Location Zero                | Unchanged              | X  | Х    | X  |

| Read/Write     | 1/1/  | 1     | ٥      | Increment                    | Increment              | Х  | Х    | Х  |

| TABLE 2 RESET AND FIRST LOAD TRUTH TABLE (DEPTH EXPANSION/COMPOUND EXPANSION MODE) |        |     |     |                        |                        |         |    |

|------------------------------------------------------------------------------------|--------|-----|-----|------------------------|------------------------|---------|----|

| IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII                                               | INPUTS |     | 3// | INTERNAL STATUS        |                        | OUTPUTS |    |

| MODE                                                                               | R\$    | RT  | ΧĪ  | Read Pointer           | Write Pointer          | EF      | FF |

| Reset Rirst Device                                                                 | 9/     | 0   | (1) | Location Zero          | Location Zero          | 0       | 1  |

| Reset All Others                                                                   | 9/     | 1   | (1) | Location Zero Disabled | Location Zero Disabled | 0       | 1  |

| Read/Write                                                                         | 1      | (2) | (1) | ×                      | X                      | X       | X  |

<sup>(1)</sup> See Figure 1 (Depth Expansion Block Diagram)

www.DataSheet4U.com

DataSheet4U.com

<sup>(2)</sup> Unchanged

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

#### NOTES

- 1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability of the tested device.

- 2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

- 3. This product provides hard clamping of transient undershoot. Input levels below ground will be clamped beginning at –0.6 V. A current in excess of 100 mA is required to reach –2 V. The device can withstand indefinite operation with inputs as low as –3 V subject only to power dissipation and bond wire fusing constraints.

- 4. "Typical" supply current values are not shown but may be approximated. At a VCC of +5.0 V, an ambient temperature of +25°C and with nominal manufacturing parameters, the operating supply currents will be approximately 3/4 or less of the maximum values shown.

- 5. Tested with outputs open and data inputs changing at the specified read and write cycle rate. The device is neither full or empty for the test.

- 6. Tested with outputs open in the worst static input control signal combination (fee., W, R, XI, FL, and RS).

- 7. These parameters are guaranteed but not 100% tested.

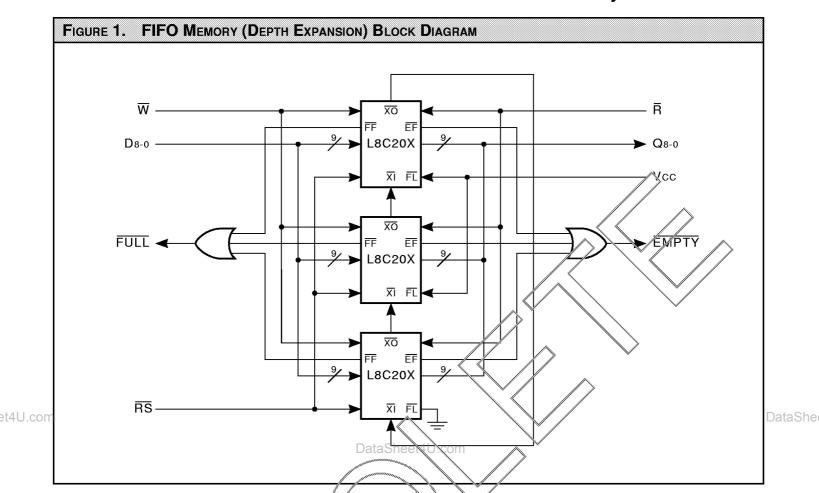

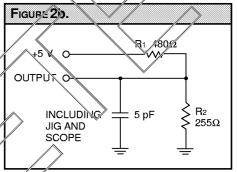

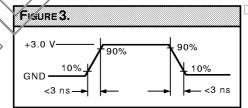

- 8. Test conditions assume input transition times of 5 ns or less, reference levels of 1.5 V output loading for specified 10 and 101 plus 30 pF (Fig. 2a), and input pulse levels of 0 to 3.0 V (Fig. 3).

- 9. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. For example, tRLRH is specified as a minimum since the external system must supply at least that much time to meet the worst-case require-

ments of all parts. Responses from the internal circuitry are specified from the point of view of the device. Access time, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

- 10. When cascading devices, the reset pulse width must be increased to equal tslsh + tslhh.

- 11. It is not recommended that Logic Devices and other vendor parts be cascaded together. The parts are designed to be pinfor-pin compatible but temperature and voltage compensation may vary from vendor to vendor. Logic Devices can only guarantee the cascading of Logic Devices parts to other Logic Devices parts.

- 12. Tested with output open and  $\overline{RS} = \overline{FL}$ =  $\overline{XI} = \overline{R} = \overline{W} = \mathbf{V}CC$ .

- 13. At any given temperature and voltage condition, output disable time is less than output enable time for any given device.

- 14. Transition is measured ±200 mV from steady state voltage with specified loading in Fig. 2b. This parameter is sampled and not 100% tested.

- 15. This product is a very high speed device and care must be taken during testing in order to realize valid test information. Inadequate attention to setups and procedures can cause a good part to be rejected as faulty. Long high-inductance leads that cause supply bounce must be avoided by bringing the VCC and ground planes directly up to the contactor fingers. A 0.04 µF high frequency capacitor is also required between VCC and ground. To avoid signal reflections, proper terminations must be used.

14

et4U.com

DataSheet4U.com

DEVICES INCORPORATED

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com www.DataSheet4U.com

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com

et4U.com

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com

= FIFO Products

www.DataSheet4U.com

et4U.com

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com

et4U.com

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com

www.DataSheet4U.com

et4U.com

# 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com

et4U.com

www.DataSheet4U.com

03/04/99-LDS.8C201/2/3/4-H

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com www.DataSheet4U.com

### 512/1K/2K/4K x 9-bit Asynchronous FIFO

DataSheet4U.com

et4U.com