# **CLOCK OSCILLATORS**

## TTL / HCMOS, TRISTATE

Combine state-of-the-art, thick film hybrid technology with precision quartz oscillators to achieve unsurpassed qualities of small size, cost, high reliability and frequency accuracy.

The crystal clock oscillator is composed of a crystal resonator and an oscillator circuit which is made by the hybrid IC technique. So, the oscillator itself is the perfect stable oscillator. This technique and process are entirely IC's one, so you can expect high reliability on it.

**Standard Specifications**

| item                         | TTL & HCMOS                                                                                                                    |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| model                        | KXO-210                                                                                                                        |

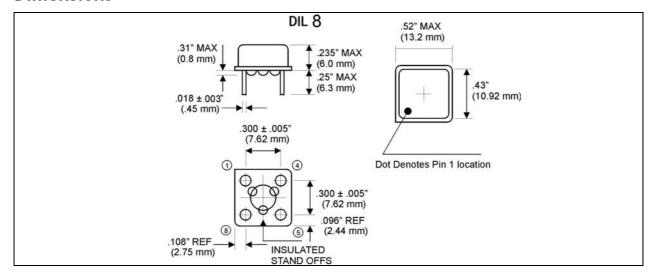

| package                      | DIL 8                                                                                                                          |

| frequency range              | 0,5 ~ 100 MHz *                                                                                                                |

| frequency stability          | standard ± 100 ppm<br>available ± 25 ppm ~ ± 100 ppm                                                                           |

| storage<br>temperature range | -55°C ~ +125°C                                                                                                                 |

| operating temperature range  | standard $-20^{\circ}\text{C} \sim +70^{\circ}\text{C}$<br>available $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$ (=KXO-215) |

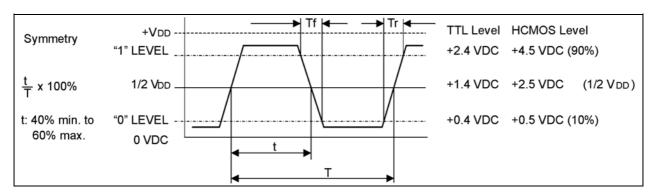

| symmetry                     | standard 60/40% (+1/ $_2$ V $_{DD}$ ) available 55/45%                                                                         |

| rise and fall time max.      | 10 ns 0.5 ~ 25 MHz<br>6 ns 25.1 ~ 70 MHz<br>4 ns 70.1 ~ 100 MHz                                                                |

| "O" level (max.)             | +0.5V (10%V <sub>DD</sub> )                                                                                                    |

| "1" level (min.)             | + 4.5V (90%V <sub>DD</sub> )                                                                                                   |

| input voltage                | +5.0VDC ± 10%                                                                                                                  |

| input current max.           | 20mA 0.5 ~ 20MHz<br>40mA 20.1 ~ 70MHz<br>60mA 70.1 ~100MHz                                                                     |

| output load                  | 1 - 8 TTL or<br>CL = 50pF (TYP)                                                                                                |

| logic family                 | TTL & HCMOS<br>compatible                                                                                                      |

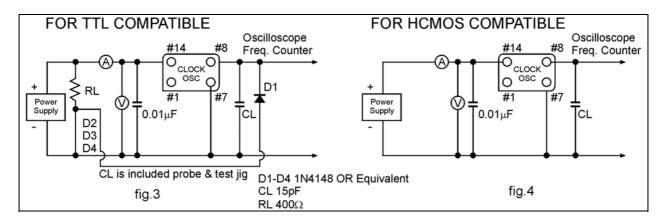

| test circuit                 | fig. 3, 4                                                                                                                      |

| pin connection               | # 1 (#1): N/C<br># 7 (#4): CASE GND<br># 8 (#5): OUTPUT<br>#14 (#8): +V <sub>DD</sub>                                          |

| lead-free                    | started from date code May, 2005                                                                                               |

| packing unit                 | 40 pcs.                                                                                                                        |

|                              | -                                                                                                                              |

<sup>\* &</sup>gt; 100,0 MHz on request

www.DataSheet4U.com

#### **Dimensions**

#### **Test Circuit**

### **Output Wave Shape**