# 2Mx32 Synchronous MASKROM FEATURES

- JEDEC standard 3.3V power supply

- LVTTL compatible with multiplexed address

- Address: Row address: RA0 ~ RA12

Column address: CA0 ~ CA7 (x32): CA0 ~ CA8 (x16)

- Switchable organization 4,194,304 x 16(word mode) / 2,097,152 x 32(double word mode)

- All inputs are sampled at the rising edge of the system clock

- Read Performance at memory point of view

@33MHz

4-1-1-1 (RAS Latency=1, CAS Latency=3)

@50MHz

666MHz

666MHz

7-1-1-1 (RAS Latency=1, CAS Latency=4)

@83MHz

7-1-1-1 (RAS Latency=2, CAS Latency=5)

@100MHz

7-1-1-1 (RAS Latency=2, CAS Latency=5)

- tsac : 6ns

- · MRS cycle with address key programs

- -. RAS Latency(1 & 2)-. CAS Latency(3 ~ 6)

- -. Burst Length: 4, 8

- -. Burst Type : Sequential & Interleaved

- DQM for data-out masking

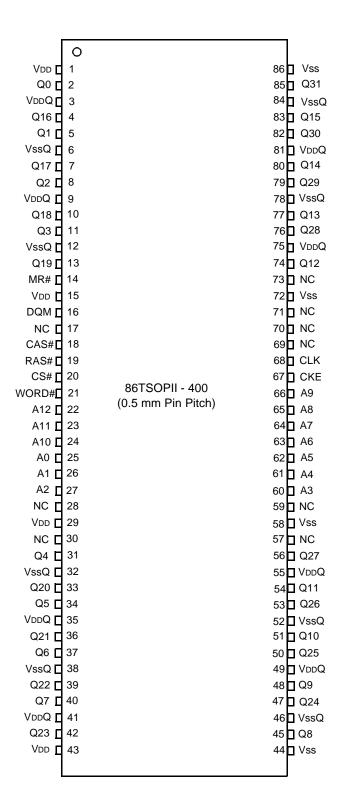

- Package:86TSOP2 400

#### **GENERAL DESCRIPTION**

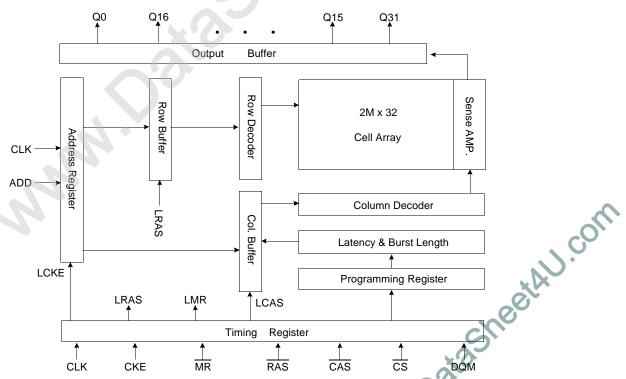

The KM23SV64205T is a synchronous high bandwidth mask programmable ROM fabricated with SAMSUNG's high performance CMOS process technology and is organized either as 4,194,304 x16bit(word mode) or as 2,097,152 x32bit(double word mode) depending on polarity of WORD pin.(see pin function description). Synchronous design allows precise cycle control, with the use of system clock, I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

#### ORDERING INFORMATION

| Part NO.        | MAX Freq. | Interface | Package |  |  |  |

|-----------------|-----------|-----------|---------|--|--|--|

| KM23SV64205T-10 | 100MHz    |           |         |  |  |  |

| KM23SV64205T-12 | 83MHz     |           |         |  |  |  |

| KM23SV64205T-15 | 66MHz     | LVTTL     | 86TSOP2 |  |  |  |

| KM23SV64205T-20 | 50MHz     |           |         |  |  |  |

| KM23SV64205T-30 | 33MHz     |           |         |  |  |  |

## **FUNCTIONAL BLOCK DIAGRAM**

Samsung Electronics reserves the right to change products or specification without notice.

# PIN CONFIGURATION (TOP VIEW)

# PIN FUNCTION DESCRIPTION

| PIN           | NAME                         | INPUT FUNCTION                                                                                                                                                                          |

|---------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK           | System Clock                 | Active on the rising edge to sample all inputs.                                                                                                                                         |

| <del>CS</del> | Chip Select                  | Disables or enables device operation by masking or enabling all inputs except CLK and CKE.                                                                                              |

| CKE           | Clock Enable                 | Masks system clock to freeze operation from the next clock cycle. CKE should be enabled at least one cycle prior to new command. Disables input buffers for power down in standby mode. |

| A0 ~ A12      | Address                      | Row / Column addresses are multiplexed on the same pins. Row address: RA0 ~ RA12, Column address: CA0 ~ CA7 (x32): CA0 ~ CA8 (x16)                                                      |

| RAS           | Row Address Strobe           | Latches row addresses on the rising edge of the CLK with RAS low.  Enables row access                                                                                                   |

| CAS           | Column Address Strobe        | Latches column addresses on the rising edge of the CLK with CAS low. Enables column access.                                                                                             |

| MR            | Mode Register Set            | Enables mode register set with MR low. (Simultaneously CS,RAS and CAS are low)                                                                                                          |

| Q0 ~ Q31      | Data Output                  |                                                                                                                                                                                         |

| VDD/VSS       | Power Supply/Ground          | Power and ground for the input buffers and the core logic.                                                                                                                              |

| VDDQ/VSSQ     | Data Output Power/<br>Ground | Power and ground for the output buffers.                                                                                                                                                |

| WORD          | x32/x16 Mode Selection       | Double word mode/word mode, depending on polarity of WORD pin.  Should be set before CAS enabling.                                                                                      |

| DQM           | Data-out Masking             | It works similar to OE during read operation.                                                                                                                                           |

| N.C           | No Connection                | This pin is recommended to be left No Connection on the device.                                                                                                                         |

Note1. VDD and VDDQ is same voltage.

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Symbol    | Min  | Max           | Unit |

|------------------------------------|-----------|------|---------------|------|

| Voltage on VDD Relative to Vss     | VDD, VDDQ | -0.5 | 4.6           | V    |

| Voltage on Any Pin Relative to Vss | VIN, VOUT | -0.5 | VDD + 0.5≤4.6 | V    |

| Operating Temperature              | TA        | 0    | 70            | °C   |

| Storage Temperature                | Тѕтс      | -55  | 125           | °C   |

| Short circuit current              | los       | -    | 50            | mA   |

| Power Dissipation                  | PD        | -    | 1             | W    |

Note: Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to recommended operating condition.

#### DC OPERATING CONDITIONS

Recommended operating conditions(Voltage referenced to Vss, Ta=0 to 70°C)

| Parameter              | Symbol    | Min | Тур | Max | Unit |

|------------------------|-----------|-----|-----|-----|------|

| Supply Voltage         | Vdd, VddQ | 3.0 | 3.3 | 3.6 | V    |

| Supply Voltage(Ground) | Vss,VssQ  | 0   | 0   | 0   | V    |

# **DC CHARACTERISTICS**

| Parameter                              | Symbol | Min  | Max       | Unit | Test Condition                              |

|----------------------------------------|--------|------|-----------|------|---------------------------------------------|

| Standby Current ( Note3)               | Іссзр  | -    | 150       | uA   | CKE≤Vı∟(Max), tcc=Min                       |

| Standby Current (Notes)                | ICC3PS | -    | 150       | uA   | CKE=0, tcc=Min                              |

| Active Standby Current                 | Іссзи  | -    | 50        | mA   | CS≥VIH(Min), tcc=Min, All Outputs Open      |

| Burst Mode Operating Current           | ICC4   | -    | 100       | mA   | tcc=Min, All Outputs Open                   |

| Input Leakage Current                  | lıL    | -10  | 10        | uA   | 0V≤VIN≤VDD + 0.3V<br>Pins not under test=0V |

| Output Leakage Current (Dout Disabled) | loL    | -10  | 10        | uA   | (0V≤Voυτ≤Vɒɒ Max)<br>Q# in High-Z           |

| Input High Voltage, All Inputs         | ViH    | 2.0  | VDD + 0.3 | V    | (Note1)                                     |

| Input Low Voltage, All Inputs          | VIL    | -0.3 | 0.8       | V    | (Note2)                                     |

| Output High Voltage Level (Logic 1)    | Voн    | 2.4  | -         | V    | IOH=-2mA                                    |

| Output Low Voltage Level (Logic 0)     | Vol    | -    | 0.4       | V    | IoL=2mA                                     |

- Note : 1. ViH(Max)=4.6V for pulse width≤10ns acceptable, pulse width measured at 50% of pulse amplitude.

- 2. VIL(Min)=-1.5V for pulse width≤10ns acceptable, pulse width measured at 50% of pulse amplitude.

- 3. The condition is the same as Self Refresh Mode of SDRAM, that is, in this case  $\overline{\text{CS}, \text{RAS}}, \overline{\text{CAS}}$  have to be set to Low,  $\overline{\text{MR}}$  has to be set to High.

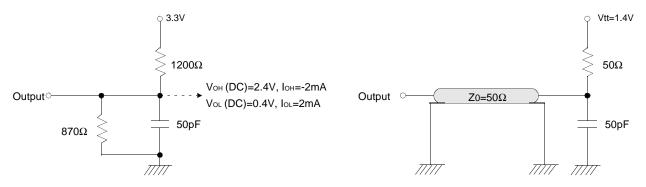

# AC OPERATING TEST CONDITIONS(TA = 0 to 70°C, VDD = 3.3V±0.3V, unless otherwise noted.)

| Parameter                                       | Value             |  |  |  |  |

|-------------------------------------------------|-------------------|--|--|--|--|

| Timing Reference Levels of Input/Output Signals | 1.4V              |  |  |  |  |

| Input Signal Levels                             | VIH/VIL=2.4V/0.4V |  |  |  |  |

| Transition Time (Rise & Fall) of Input Signals  | tr/tf=1ns/1ns     |  |  |  |  |

| Output Load                                     | LVTTL             |  |  |  |  |

Note: If CLK transition time is longer than 1ns, timing parameters should be compensated. Add [(tr+tf)/2-1]ns for transition time longer than 1ns. Transition time is measured between VIL(Max) and VIH(Min).

(Fig. 1) DC Output Load Circuit

(Fig. 2) AC Output Load Circuit

#### **OPERATING AC PARAMETERS**

(AC operating conditions unless otherwise noted)

| Parameter                            | Symbol | up to 1 | 00MHz | up to | 83MHz | up to | 66MHz | up to | 50 Mhz | Unit  | Notes |

|--------------------------------------|--------|---------|-------|-------|-------|-------|-------|-------|--------|-------|-------|

| i arameter                           | Symbol | Min     | Max   | Min   | Max   | Min   | Max   | Min   | Max    | Oille | Notes |

| CLK Cycle Time                       | tcc    | 10      |       | 12    |       | 15    | -     | 20    | -      | ns    |       |

| CLK to Valid Output Delay            | tsac   | -       | 6     | -     | 6     | -     | 6     | -     | 6      | ns    |       |

| Data Output Hold Time                | tон    | 2       | -     | 2     | -     | 2     | -     | 2     | -      | ns    |       |

| CLK High Pulse Width                 | tch    | 3       | -     | 3.5   | -     | 4     | -     | 6.5   | -      | ns    |       |

| CLK Low Pulse Width                  | tcl    | 3       | -     | 3.5   | -     | 4     | -     | 6.5   | -      | ns    |       |

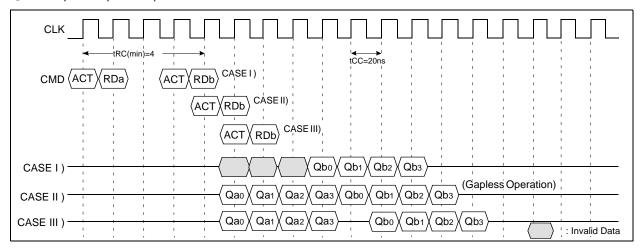

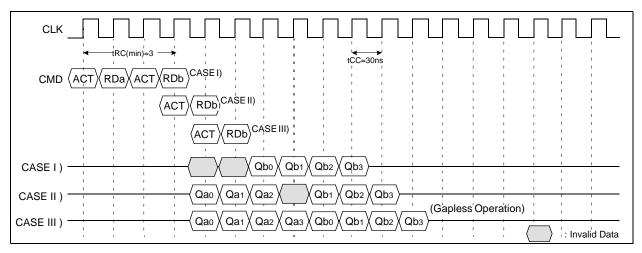

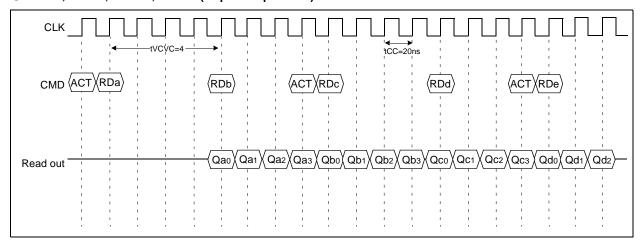

| Row-active to Row-active             | trc    | 10      | -     | 10    | -     | 8     | -     | 8     | -      | clks  | 1     |

| Input Setup Time                     | tss    | 2       | -     | 3     | -     | 4     | -     | 4     | -      | ns    |       |

| Input Hold Time                      | tsH    | 1       | -     | 1     | -     | 2     | -     | 2     | -      | ns    |       |

| CLK to Output in Low-Z               | tslz   | 0       | -     | 0     | -     | 0     | -     | 0     | -      | ns    |       |

| CLK to Output in High-Z              | tshz   | -       | 7     | -     | 8     | -     | 10    | -     | 15     | ns    |       |

| Transition Time                      | tτ     | 0.1     | 10    | 0.1   | 10    | 0.1   | 10    | 0.1   | 10     | ns    |       |

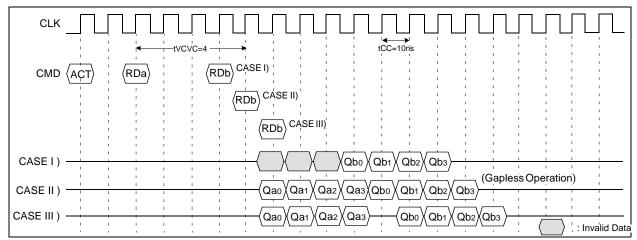

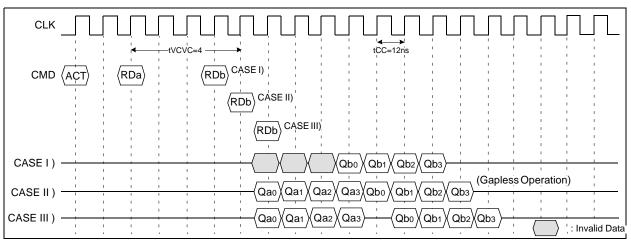

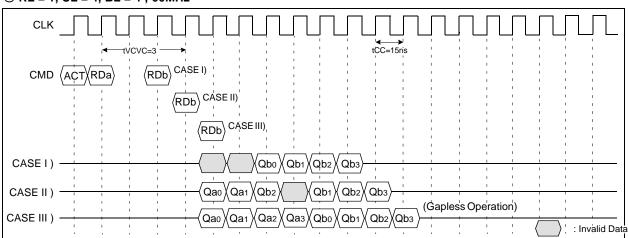

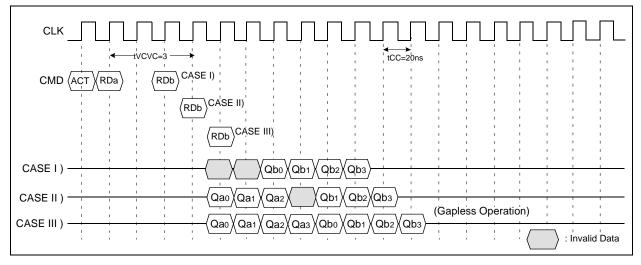

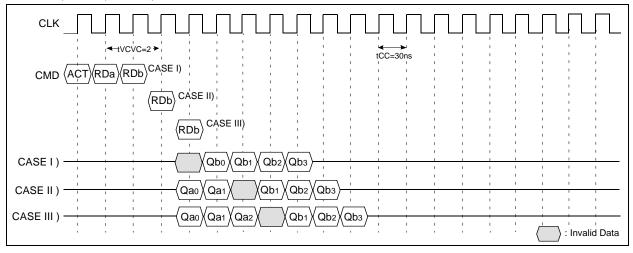

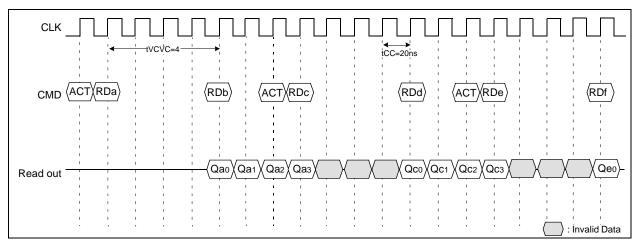

| Valid CAS Enable to Valid CAS Enable | tvcvc  | 8       | -     | 8     | -     | 7     | -     | 7     | -      | clks  | 2     |

#### Note:

- 1. These trc values are for BL=8. For BL=4, trc=6 clks for up to 100MHz, trc=6 clks for up to 83MHz, trc=4 clks for up to 66MHz, trc=4 clks for up to 50MHz, and trc=3 clks for up to 33MHz.

- RAS latency increase means, a simultaneous trc increase in the same number of cycles.

- ( If RAS latency is 3 clks, tRc is 12 clks for BL=8.) Refer to attached technical note for gapless operation.

- 2. These tvcvc values are for BL=8. For BL=4, tvcvc=4clks for up to 100MHz, tvcvc=4clks for up to 83MHz, tvcvc=3clks for up to 66MHz, tvcvc=3clks for up to 66MHz, tvcvc=3clks for up to 50MHz, and tvcvc=2clks for up to 33MHz.

- Refer to attached technical note for gapless operation.

#### **CAPACITANCE**(TA=25°C, f=1MHz)

| Parameter          | Symbol | Min | Max | Unit |

|--------------------|--------|-----|-----|------|

| Input Capacitance  | CIN    | -   | 5   | pF   |

| Output Capacitance | Соит   | -   | 7   | pF   |

#### **FUNCTION TRUTH TABLE**

|                                 | Command                    |       | CKEn-1 | CKEn | cs | RAS | CAS | MR | DQM | Add. | WORD | Notes |

|---------------------------------|----------------------------|-------|--------|------|----|-----|-----|----|-----|------|------|-------|

| Register                        | Mode Register Set          |       | Н      | Х    | L  | L   | L   | L  | Х   | Code | Х    | 1     |

| Row Active<br>Row Access& Latch | Row Access & Latch         |       | Н      | Х    | L  | L   | Н   | Н  | х   | RA   | Х    |       |

| Read                            | Column Access & La         | Н     | Х      | L    | Н  | L   | Н   | Х  | CA  | Х    |      |       |

| Burst Stop                      | (Burst Stop on Synch.DRAM) |       | Н      | Х    | L  | Н   | Н   | L  | Х   | Х    | Х    |       |

| Burst Stop                      | (Precharge on Synch.Df     | Н     | Х      | L    | L  | Н   | L   | Х  | Х   | Х    |      |       |

| Power Down &                    | Two Standby Mode           | Entry | Н      | L    | Х  | Х   | Х   | Х  | Х   | Х    | Х    | 2     |

| Clock Suspend                   |                            | Exit  | L      | Н    | Х  | Х   | Х   | Х  | Х   | Х    | Х    |       |

| DQM                             |                            |       | Н      |      |    | Х   |     |    | V   | ,    | X    | 3     |

| Illegal                         | (Write on Synch.DRAM)      |       | Н      | Х    | L  | Н   | L   | L  | Х   | CA   | Х    |       |

| Illegal                         | (Refresh on Synch.DRA      | M)    | Н      | Х    | L  | L   | L   | Н  | Х   | Х    | Х    |       |

| No Operation Comma              | and                        |       | Н      | Х    | Н  | Х   | Х   | Х  | Х   | Х    | Х    | 4     |

| No Operation Command            |                            | Н     | Х      | L    | Н  | Η   | Η   | Х  | Х   | Х    | 7    |       |

| Organization Control            | Organization Control       |       |        | Х    | L  | Н   | L   | Н  | Х   | CA   | Н    | 5     |

| Organization Control            |                            |       | Н      | ^    | L  | 11  | L   |    |     | 5    | L    | 3     |

(V=Valid, X=Don't Care, H=Logic High, L=Logic Low)

Abbreviations (RA: Row Address, CA: Column Address, NOP: No Operation Command, DWM: Double Word Mode, WM: Word Mode)

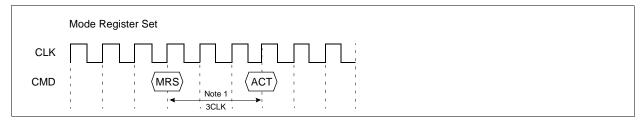

- 1. Ao ~ As: Program keys (@MRS). After power up, mode register set, can be set before issuing other input command. After the mode register set command is completed, no new commands can be issued for 3 CLK Cycles, and  $\overline{\text{CS}}$  or  $\overline{\text{MR}}$  state must be defined "H" within 3 CLK cycles. Refer to the

- 2. In the case CKE is low, two standby modes are possible. Those are stand-by mode in power-down.

Power Down: CKE="L" (at all the parts except the range of Row Active, Read & Data out)

Clock Suspend: CKE="L" (at the range of Row Active, Read & Data Out)

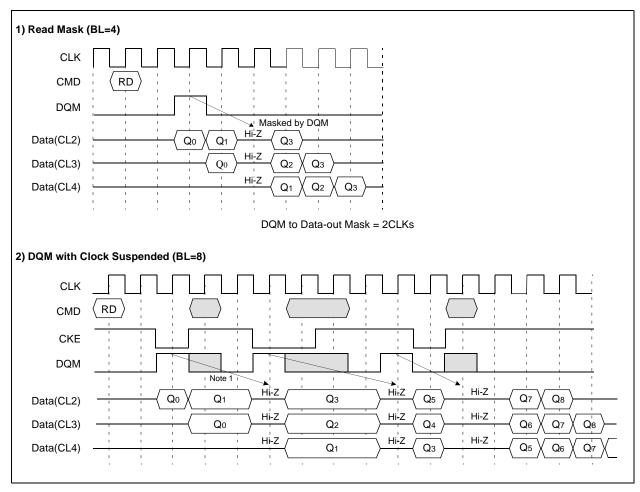

3. DQM sampled at rising edge of a CLK makes a Hi-Z state the data-out state, delayed by 2CLK cycles.

4. Precharge command on Synch.DRAM can be used for Burst Stop operation during burst read operation only.

5. Mode selection control is decided simultaneously with column access start, and according to the polarity of WORD pin, "H" state is DWM, "L" state is WM.

## MODE REGISTER FIELD TABLE TO PROGRAM MODES

## **Register Programmed with MRS**

| Address  | A6          | <b>A</b> 5 | <b>A</b> 4  | А3 | A2         | A1 A0   |        |  |

|----------|-------------|------------|-------------|----|------------|---------|--------|--|

| Function | RAS Latency |            | CAS Latency |    | Burst Type | Burst I | _ength |  |

| RAS | S Latency |    | C  | CAS Laten | су       | Вι | urst Type  |    | Burst Le | ngth     |

|-----|-----------|----|----|-----------|----------|----|------------|----|----------|----------|

| A6  | Length    | A5 | A4 | Аз        | Length   | A2 | Туре       | A1 | A0       | Length   |

| 0   | 1         | 0  | 0  | 0         | Reserved | 0  | Sequential | 0  | 0        | Reserved |

| 1   | 2         | 0  | 0  | 1         | Reserved | 1  | Interleave | 0  | 1        | 4        |

|     |           | 0  | 1  | 0         | 3        |    |            | 1  | 0        | 8        |

|     |           | 0  | 1  | 1         | 4        |    |            | 1  | 1        | Reserved |

|     |           | 1  | 0  | 0         | 5        |    |            |    |          |          |

|     |           | 1  | 0  | 1         | 6        |    |            |    |          |          |

|     |           | 1  | 1  | 0         | Reserved |    |            |    |          |          |

|     |           | 1  | 1  | 1         | Reserved |    |            |    |          |          |

#### Notes:

# **ADDRESSING MAP**

# (1) WORD = "H" : x32 Organization

| Function       | A <sub>0</sub>  | <b>A</b> 1      | A <sub>2</sub>  | Аз  | A4              | <b>A</b> 5      | A <sub>6</sub>  | A7                  | A8  | <b>A</b> 9 | A10              | A11  | A12              |

|----------------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|---------------------|-----|------------|------------------|------|------------------|

| Row Address    | RA <sub>0</sub> | RA <sub>1</sub> | RA <sub>2</sub> | RАз | RA4             | RA <sub>5</sub> | RA6             | RA7                 | RA8 | RA9        | RA <sub>10</sub> | RA11 | RA <sub>12</sub> |

| Column Address | CA <sub>0</sub> | CA <sub>1</sub> | CA <sub>2</sub> | САз | CA <sub>4</sub> | CA <sub>5</sub> | CA <sub>6</sub> | CA7 <sup>Note</sup> | Χ   | Χ          | Χ                | Χ    | Χ                |

Note: Column Address MSB (at x32 organization)

(X=Don't Care)

# (2) WORD="L" : x16 Organization

| Function       | A <sub>0</sub>  | A1              | A2              | Аз  | A4              | <b>A</b> 5      | A <sub>6</sub>  | A7              | A8                  | <b>A</b> 9 | A10              | A11  | A12              |

|----------------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|-----------------|-----------------|---------------------|------------|------------------|------|------------------|

| Row Address    | RA <sub>0</sub> | RA <sub>1</sub> | RA <sub>2</sub> | RАз | RA4             | RA <sub>5</sub> | RA6             | RA7             | RA8                 | RA9        | RA <sub>10</sub> | RA11 | RA <sub>12</sub> |

| Column Address | CA <sub>0</sub> | CA <sub>1</sub> | CA <sub>2</sub> | САз | CA <sub>4</sub> | CA <sub>5</sub> | CA <sub>6</sub> | CA <sub>7</sub> | CA8 <sup>Note</sup> | Х          | Х                | Х    | Х                |

Note: Column Address MSB (at x16 organization)

(X=Don't Care)

## (3) Each address is arranged as follows

for X32 operation

| ioi xoz oporation, | MSB  |      |      |         |     |     |     |         |     | LSB |     |

|--------------------|------|------|------|---------|-----|-----|-----|---------|-----|-----|-----|

| Address Register   | AR20 | AR19 | AR18 | <br>AR9 | AR8 | AR7 | AR6 | <br>AR3 | AR2 | AR1 | AR0 |

| Address            | RA12 | RA11 | RA10 | <br>RA1 | RA0 | CA7 | CA6 | <br>CA3 | CA2 | CA1 | CA0 |

\* Initial Address - BL=4(CA0,CA1) - BL=8(CA0,CA1,CA2)

BL=4 BL=8

for X16 operation, when CA8 is set to Low, data belonging to  $0\sim15$ th registers are output to  $Q0\sim215$  pins, and when CA8 is set to High, data belonging to  $16\sim31$ th registers are output to  $20\sim215$  pins.

<sup>-.</sup> After power up, when user wants to change mode register set, user must exit from power down mode and start mode register set before entering normal operation mode.

# x32 operation (double word mode)

|     | Column Address |     |     |     |     |     | D15 | D0 (U                  | ovadoci | mal) | D21    | D16 /L                  | lovadoo | imal) |   |

|-----|----------------|-----|-----|-----|-----|-----|-----|------------------------|---------|------|--------|-------------------------|---------|-------|---|

| CA7 | CA6            | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 | D15 ~ D0 (Hexadecimal) |         |      | iliai) | D31 ~ D16 (Hexadecimal) |         |       |   |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | A                      | A       | A    | A      | 0                       | 0       | 0     | 0 |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 1   | В                      | В       | В    | В      | 1                       | 1       | 1     | 1 |

| 0   | 0              | 0   | 0   | 0   | 0   | 1   | 0   | С                      | С       | С    | С      | 2                       | 2       | 2     | 2 |

| 0   | 0              | 0   | 0   | 0   | 0   | 1   | 1   | D                      | D       | D    | D      | 3                       | 3       | 3     | 3 |

| 0   | 0              | 0   | 0   | 0   | 1   | 0   | 0   | Е                      | Е       | Е    | Е      | 4                       | 4       | 4     | 4 |

| 0   | 0              | 0   | 0   | 0   | 1   | 0   | 1   | F                      | F       | F    | F      | 5                       | 5       | 5     | 5 |

# x16 operation (word mode)

|     | Column Address |     |     |     |     |     |     |     |     | ta Out (H  | evadeci | mal)   | Comment   |  |

|-----|----------------|-----|-----|-----|-----|-----|-----|-----|-----|------------|---------|--------|-----------|--|

| CA8 | CA7            | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 | Dai | ia Out (ii | exaueci | illaij | Comment   |  |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Α   | Α          | Α       | Α      | D15 ~ D0  |  |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 1   | В   | В          | В       | В      | D15 ~ D0  |  |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 1   | 0   | С   | С          | С       | С      | D15 ~ D0  |  |

| 0   | 0              | 0   | 0   | 0   | 0   | 0   | 1   | 1   | D   | D          | D       | D      | D15 ~ D0  |  |

| 0   | 0              | 0   | 0   | 0   | 0   | 1   | 0   | 0   | Е   | E          | Е       | Е      | D15 ~ D0  |  |

| 0   | 0              | 0   | 0   | 0   | 0   | 1   | 0   | 1   | F   | F          | F       | F      | D15 ~ D0  |  |

|     |                |     |     |     |     |     | :   |     |     |            |         |        |           |  |

| 1   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0          | 0       | 0      | D31 ~ D16 |  |

| 1   | 0              | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | 1          | 1       | 1      | D31 ~ D16 |  |

| 1   | 0              | 0   | 0   | 0   | 0   | 0   | 1   | 0   | 2   | 2          | 2       | 2      | D31 ~ D16 |  |

# **BURST SEQUENCE(BURST LENGTH = 4)**

| Initial | address |   | Segu | ential |   | Interleave |        |       |   |  |  |

|---------|---------|---|------|--------|---|------------|--------|-------|---|--|--|

| A1      | Α0      |   | Ocqu | Cittai |   |            | iiiioi | icuvo |   |  |  |

| 0       | 0       | 0 | 1    | 2      | 3 | 0          | 1      | 2     | 3 |  |  |

| 0       | 1       | 1 | 2    | 3      | 0 | 1          | 0      | 3     | 2 |  |  |

| 1       | 0       | 2 | 3    | 0      | 1 | 2          | 3      | 0     | 1 |  |  |

| 1       | 1       | 3 | 0    | 1      | 2 | 3          | 2      | 1     | 0 |  |  |

# BURST SEQUENCE(BURST LENGTH = 8)

| Init | ial addı  | ress |   |                       |   | Sequ | ential |   |   |   |   |   |   | Inter | leave |   |   |   |

|------|-----------|------|---|-----------------------|---|------|--------|---|---|---|---|---|---|-------|-------|---|---|---|

| A2   | <b>A1</b> | A0   |   |                       |   |      |        |   |   |   |   |   |   |       |       |   |   |   |

| 0    | 0         | 0    | 0 | 1                     | 2 | 3    | 4      | 5 | 6 | 7 | 0 | 1 | 2 | 3     | 4     | 5 | 6 | 7 |

| 0    | 0         | 1    | 1 | 2                     | 3 | 4    | 5      | 6 | 7 | 0 | 1 | 0 | 3 | 2     | 5     | 4 | 7 | 6 |

| 0    | 1         | 0    | 2 | 3                     | 4 | 5    | 6      | 7 | 0 | 1 | 2 | 3 | 0 | 1     | 6     | 7 | 4 | 5 |

| 0    | 1         | 1    | 3 | 4 5 6 7 0 1 2 3 2 1 0 |   |      |        |   |   | 7 | 6 | 5 | 4 |       |       |   |   |   |

| 1    | 0         | 0    | 4 | 5                     | 6 | 7    | 0      | 1 | 2 | 3 | 4 | 5 | 6 | 7     | 0     | 1 | 2 | 3 |

| 1    | 0         | 1    | 5 | 6                     | 7 | 0    | 1      | 2 | 3 | 4 | 5 | 4 | 7 | 6     | 1     | 0 | 3 | 2 |

| 1    | 1         | 0    | 6 | 7                     | 0 | 1    | 2      | 3 | 4 | 5 | 6 | 7 | 4 | 5     | 2     | 3 | 0 | 1 |

| 1    | 1         | 1    | 7 | 0                     | 1 | 2    | 3      | 4 | 5 | 6 | 7 | 6 | 5 | 4     | 3     | 2 | 1 | 0 |

## **DEVICE OPERATIONS**

#### **CLOCK (CLK)**

The clock input is used as a reference for SMROM operation. A square wave signal(CLK) must be applied externally at cycle time tCC. All operations are synchronized to the rising edge of the clock. The clock transitions must be monotonic between VIL and VIH. During operation with CKE high, all inputs are assumed to be in valid state (low or high) for the duration of set-up and hold time around the positive edge of the clock for proper functionality and Icc specifications.

#### **CLOCK ENABLE (CKE)**

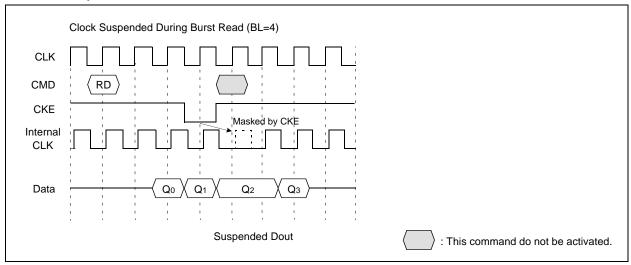

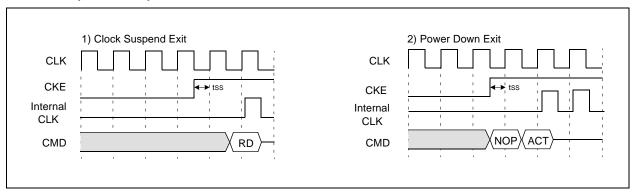

The clock enable(CKE) gates the clock into the SMROM and is asserted high during all cycles, except for power down, stand-by and clock suspend mode. If CKE goes low synchronously with clock (set-up and hold time same as other inputs), the internal clock is suspended from the next clock cycle and the state of output and burst address is frozen for as long as the CKE remains low. All other inputs are ignored from the next clock cycle after CKE goes low. The SMROM remains in the power down mode ignoring other inputs for as long as CKE remains low. The power down exit is synchronous as the internal clock is suspended. When CKE goes high at least "1 CLK + tss" before the rising edge of the clock, then the SMROM becomes active from the same clock edge accepting all the input commands.

#### NOP and DEVICE DESELECT

When RAS, CAS and MR are high, the SMROM performs no operation (NOP). NOP does not initiate any new operation. Device deselect is also a NOP and is entered by asserting CS high. CS high disables the command decoder so that RAS, CAS, MR and all the address inputs are ignored. In addition, entering a mode register set command in the middle of a normal operation, results in an illegal state in SMROM.

#### **POWER-UP**

The following power-up sequence is recommended.

- 1. Apply power and start clock, Attempt to maintain  $\overline{MR}$ , CKE and DQM inputs to pull them high and the other pins are NOP condition at the inputs before or along with VDD(and VDDQ) supply.

- 2. Maintain stable power, stable clock and NOP input condition for a minimum of 20us.

- 3. When user wants to change the default mode register set values, perform a MODE REGISTER SET cycle to program the RAS latency, CAS latency, burst length and burst type.

- 4. At the end of three clock cycles after the mode register set cycle, the device is ready for operation. When the above sequence is used for power-up, all outputs will be in high impedance state. The high impedance of outputs is not guaranteed in any other power-up sequence.

#### MODE SELECTION CONTROL

Mode selection control is decided simultaneously with column access, and according to WORD pin voltage level. High level signifies double word mode(x32) and low level signifies word mode(x16).

#### **ADDRESS DECODING**

The address bits required to decode one of the available cell locations out of the total depth are multiplexed onto the address select pins and latched by externally applying two commands. The first command, RAS asserted low, latches the row address into the device. A second command, CAS asserted low, subsequently latches the column address.

#### **DEVICE OPERATIONS**

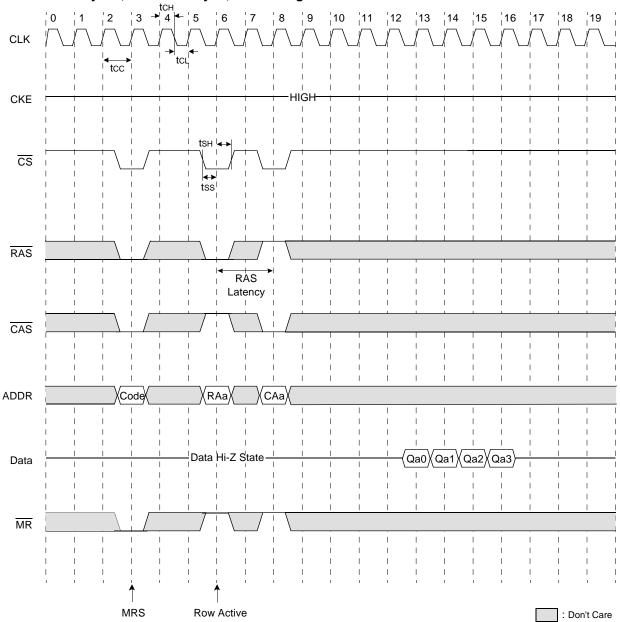

#### **MODE REGISTER SET (MRS)**

The mode register stores the data for controlling the various operating modes of SMROM. It programs the RAS latency, CAS latency, burst length, burst type. The default value of the mode register is defined as RAS latency=2, CAS latency=5, Burst length=4, Sequential Burst Type. When and if the user wants to change its values, the user must exit from power down mode and start mode register set before entering normal operation mode. The mode register is reprogrammed by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{MR}$  (The SMROM should be in active mode with CKE already high prior to writing the mode register). The state of address pins A0 ~ A7 in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{MR}$  going low is the data written in the mode register. Three clock cycles are required to complete the program in the mode register, therefore after mode register set command is completed, no new commands can be issued for 3 clock cycles and  $\overline{CS}$  or  $\overline{MR}$  must be fixed to high within 3 clock cycles. The mode register is divided into various fields depending on functionality. The burst length field uses A0 ~ A1, burst type uses A2, CAS latency (read latency from column address) uses A3 ~ A5, RAS latency uses A6 ( $\overline{RAS}$  to  $\overline{CAS}$  delay). Refer to the table for specific codes for various burst length, burst type, CAS latencies and RAS latencies.

#### **LATENCY**

There are latencies between the issuance of a Row active command and when data is available on the I/O buffers. The RAS to CAS delay is defined as the RAS latency. The CAS to data out delay is the CAS latency. The CAS and RAS latencies are programmable through the mode register. RAS latencies of 1 and 2, and CAS latencies of 3 through 6 are supported. It is understood that some RAS and CAS latency values are reserved for future use, and may not be available in the first generation for SMROM. The followings are the supported minimum values in the first generation. RAS latency=2, and CAS latency=5 for 100MHz operation, and RAS latency=2, and CAS latency=4 for 66MHz operation, and RAS latency=1, and CAS latency=4 for 50MHz operation, and RAS latency=1, and CAS latency=3 for 33MHz operation.

#### **DQM OPERATION**

The DQM is used to mask output operations when a complete burst read is not required. It works similar to  $\overline{\text{OE}}$  during a read operation. The read latency is two cycles from DQM, which means DQM masking occurs two cycles later in the read cycle. DQM operation is synchronous with the clock. The masking occurs for a complete cycle. (Also refer to the DQM timing diagram)

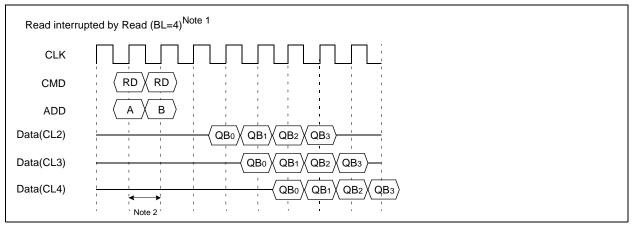

#### **BURST READ**

The burst read command is used to access a burst of data on consecutive clock cycles from an active row state. The burst read command is issued by asserting low  $\overline{\text{CS}}$  and  $\overline{\text{CAS}}$  with  $\overline{\text{MR}}$  being high on the rising edge of the clock. The first output appears in CAS latency number of clock cycles after the issuance of the burst read command. The burst length, burst sequence and latency from the burst read command are determined by the mode register which is already programmed. Burst read can be initiated on any column address of the active row. The output goes into high-impedance at the end of the burst, unless a new burst read is initiated to keep the data output gapless. The burst read can be terminated by issuing another burst read.

# **BASIC FEATURE AND FUNCTION DESCRIPTIONS**

#### 1. MRS

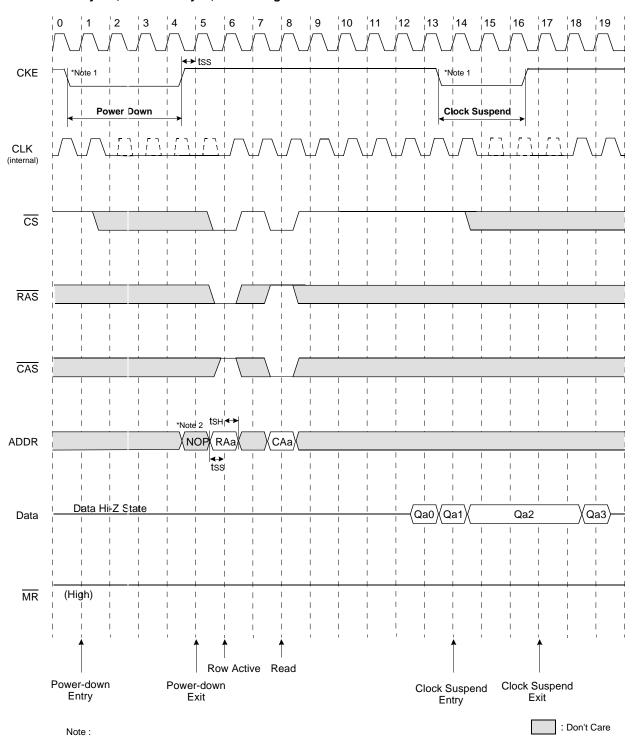

#### 2. CLOCK Suspend

# 3. Clock Suspend Exit & power Down Exit

#### Note:

1. After mode register set command is completed, no new commands can be issued for 3 clock cycles, and MR or CS should be fixed "H" within a minimum of 3 clock cycles.

# 4. DQM Operation

\*Note:

1. DQM makes data out Hi-Z after 2CLKs which should masked by CKE " L"

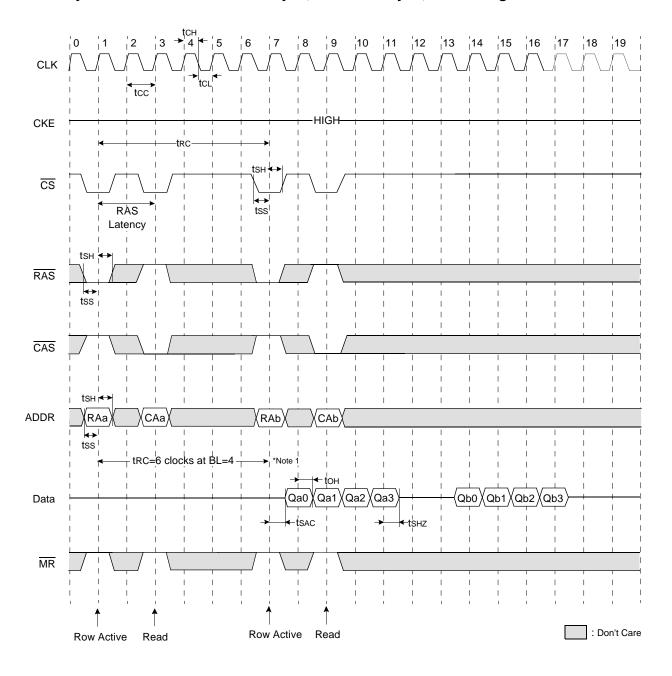

# Read Cycle I: Normal @RAS Latency=2, CAS Latency=5, Burst Length=4

\*Note:

1. When the burst length is 4 at 100MHz, tRC is equal to 6 clock cycles.

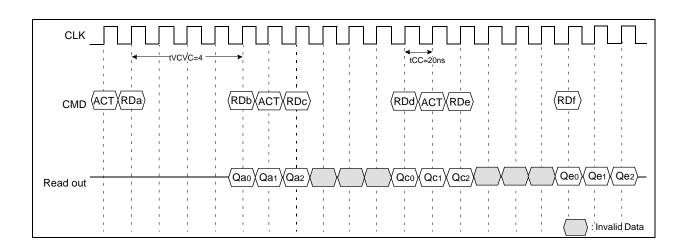

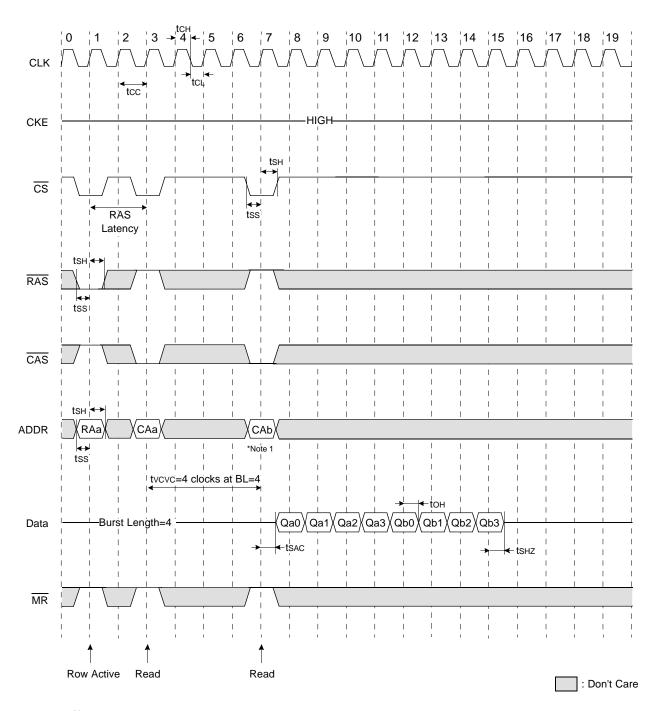

Read Cycle II: Consecutive Column Access @RAS Latency = 2, CAS Latency=5, BL = 4

Note:

When column access is initiated beyond tvcvc,

1. at BL=4, CAa access read is completed, CAb access read begins.

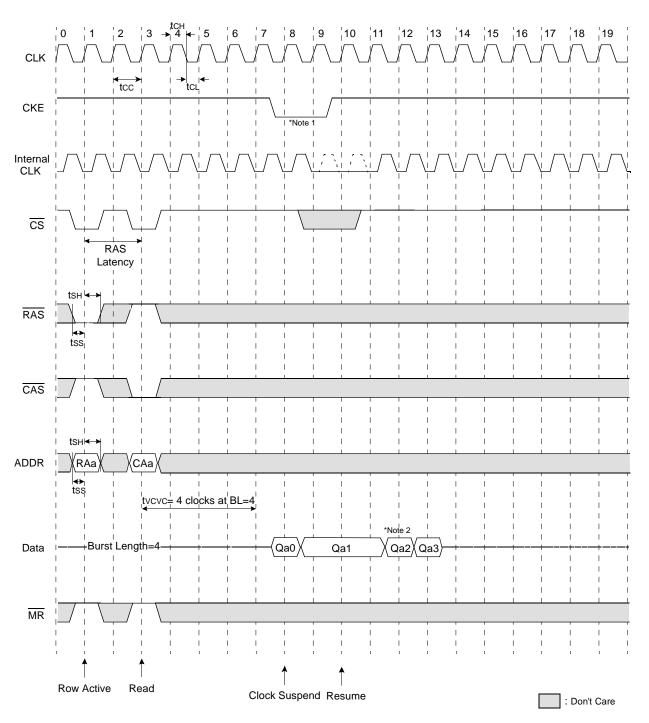

# Read Cycle III: Clock Suspend @RAS Latency = 2, CAS Latency=5, Burst Length=4

#### Note:

- 1. From next clock after CKE goes low, clock suspension begins.

- 2. For clock suspension, data output state is held & maintained.

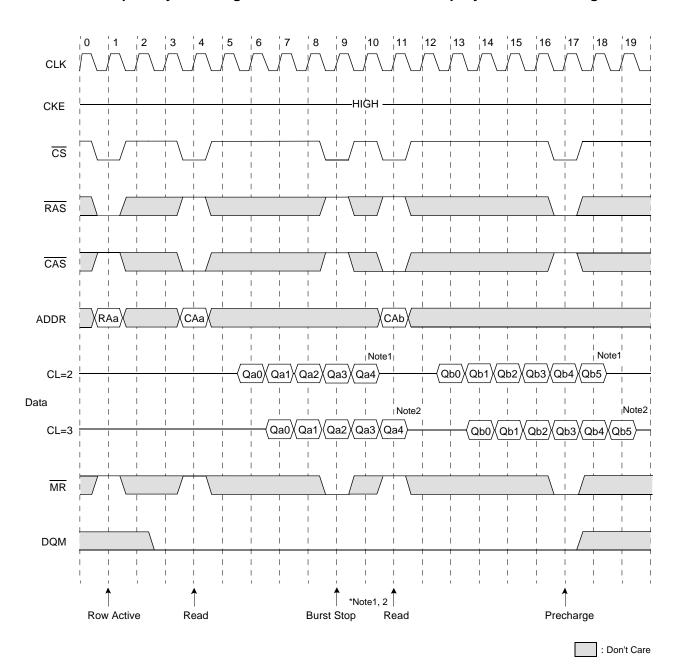

# Read Interrupted by Precharge Command & Burst Read Stop Cycle @Burst Length=8

\*Note:

<sup>1.</sup> The burst stop command is valid at every page burst length.

The data bus goes to High-Z after the CAS latency from the burst stop command is issued.

<sup>2.</sup> The interval between read command (column address presented) and burst stop command is 1 cycle(min).

# Power Down & Clock Suspend Cycle:

@RAS Latency = 2, CAS Latency=5, Burst Length=4

1. From next clock after CKE goes low, clock suspend and power down begins.

2. After power down exit, NOP should be issued and new command can be issued after 1clock.

# **Mode Register Set:**

#### Note:

- 1. After the mode register set is completed, no new commands can be issued for 3CLK cycles.

- 2. After power up, necessarily mode register set should be completed at least one time and CS or MR must be fixed "H" within 3clock cycles, and when user wants to change mode register set, user must exit from power down mode and start mode register set before chip enters normal operation mode.

# **FUNCTION TRUTH TABLE**

| Current            |     |    | Input | Signal |    |      | Next State Operation                                                                                                                                                                  |

|--------------------|-----|----|-------|--------|----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| State              | CKE | cs | RAS   | CAS    | MR | Add. | Next State Operation                                                                                                                                                                  |

|                    | L   | Х  | Х     | Х      | Х  | Х    | Power Down                                                                                                                                                                            |

| After<br>Power Up* | Н   | L  | L     | Н      | Н  | RA   | Row Active ; latch RA                                                                                                                                                                 |

| . one. op          | Н   | L  | L     | L      | L  | Code | Mode Register Set                                                                                                                                                                     |

|                    | Н   | L  | L     | Н      | Н  | RA   | If consecutive <u>row</u> access is issued within tromin. without <u>CAS</u> enabling, only the final RA is valid.                                                                    |

| Row Active         | Н   | L  | Н     | L      | Н  | CA   | Begin READ ; latch CA                                                                                                                                                                 |

|                    | Н   | L  | L     | L      | L  | Code | Illegal *                                                                                                                                                                             |

|                    | L   | Х  | Х     | Х      | Х  | Х    | Clock Suspend                                                                                                                                                                         |

|                    | Н   | L  | L     | Н      | Н  | RA   | Row Access in Read State, within the tRC, previous read is ignored and new row is activated. beyond the tRC, previous read is completed and new read begins.                          |

| READ               | Н   | L  | Н     | L      | Н  | CA   | Consecutive Column Access, within the tvcvc, only the final CA is valid and the previous burst read is ignored. Beyond the tvcvc, the previous read is completed and new read begins. |

|                    | Н   | L  | L     | Н      | L  | Х    | NOP (After Burst Read) / Read Interrupt                                                                                                                                               |

|                    | Н   | L  | Н     | Н      | L  | Х    | NOP (After Burst Read) / Read Interrupt                                                                                                                                               |

|                    | Н   | L  | L     | L      | L  | Code | Illegal *                                                                                                                                                                             |

|                    | L   | Х  | Х     | Х      | Х  | Х    | Clock Suspend / Power Down                                                                                                                                                            |

| Any State          | L   | L  | L     | L      | Н  | Х    | Low Power Consumption Mode                                                                                                                                                            |

| Any State          | Н   | L  | Н     | Н      | Н  | Х    | NOP                                                                                                                                                                                   |

| Any State          | Н   | L  | L     | L      | Н  | Х    | Illegal                                                                                                                                                                               |

| Any State          | Н   | L  | Н     | L      | L  | CA   | Illegal                                                                                                                                                                               |

<sup>\* :</sup> After the power up, when user wants to change MR set, user must exit from power down mode and start MR set before chip enters normal operation mode.

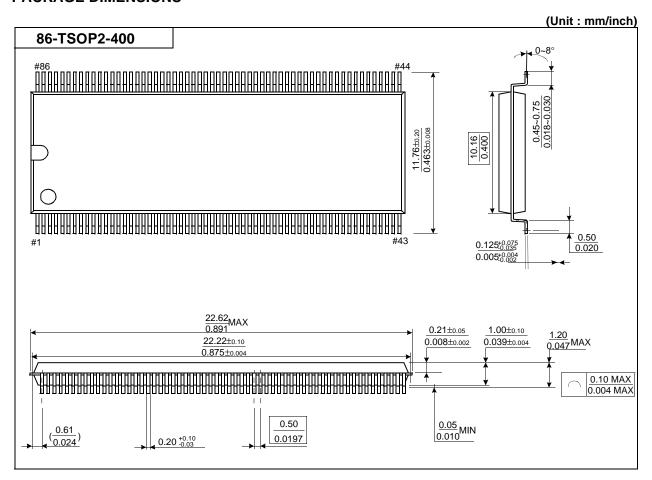

# **PACKAGE DIMENSIONS**

# **Technical Notes**

# 1. Frequency vs. AC Parameter Relationship Table

#### KM23SV64205T-10

( unit : number of clock )

| Burst Length | RAS Latency | CAS Latency | tRCmin. | tVCVCmin. |

|--------------|-------------|-------------|---------|-----------|

| 4            | 2           | 5           | 6       | 4*        |

| 4            | 2           | 6           | 7       | 5         |

| 0            | 2           | 5           | 10      | 8*        |

| 8            | 2           | 6           | 11      | 9         |

#### KM23SV64205T-12

( unit : number of clock )

| Burst Length | RAS Latency | CAS Latency | tRCmin. | tVCVCmin. |

|--------------|-------------|-------------|---------|-----------|

| 4            | 2           | 5           | 6       | 4*        |

| 4            | 2           | 6           | 7       | 5         |

| o            | 2           | 5           | 10      | 8*        |

| 8            | 2           | 6           | 11      | 9         |

#### KM23SV64205T-15

( unit : number of clock )

| Burst Length | RAS Latency | CAS Latency | tRCmin. | tVCVCmin. |

|--------------|-------------|-------------|---------|-----------|

|              |             | 4           | 4*      | 3/ 4*     |

|              | 1           | 5           | 5       | 4*        |

| 4            |             | 6           | 6       | 5         |

| 4            |             | 4           | 5       | 3/ 4*     |

|              | 2           | 5           | 6       | 4*        |

|              |             | 6           | 7       | 5         |

|              |             | 4           | 8*      | 7/ 8*     |

|              | 1           | 5           | 9       | 8*        |

| 8            |             | 6           | 10      | 9         |

| 0            |             | 4           | 9       | 7/8*      |

|              | 2           | 5           | 10      | 8*        |

|              |             | 6           | 11      | 9         |

KM23SV64205T-20 ( unit : number of clock )

| Burst Length | RAS Latency | CAS Latency | tRCmin. | tVCVCmin. |

|--------------|-------------|-------------|---------|-----------|

|              |             | 4           | 4*      | 3/ 4*     |

|              | 1           | 5           | 5       | 4*        |

| 4            |             | 6           | 6       | 5         |

| 4            |             | 4           | 5       | 3/4*      |

|              | 2           | 5           | 6       | 4*        |

|              |             | 6           | 7       | 5         |

|              |             | 4           | 8*      | 7/8*      |

|              | 1           | 5           | 9       | 8*        |

| 8            |             | 6           | 10      | 9         |

| ٥            | 2           | 4           | 9       | 7/ 8*     |

|              |             | 5           | 10      | 8*        |

|              |             | 6           | 11      | 9         |

KM23SV32205T-30 ( unit : number of clock )

| Burst Length | RAS Latency | CAS Latency | tRCmin. | tVCVCmin.     |

|--------------|-------------|-------------|---------|---------------|

|              |             | 3           | 3/ 4*   | 2/ 4*         |

|              |             | 4           | 4*      | 3/ 4*         |

|              | 1           | 5           | 5       | 4*            |

| 4            |             | 6           | 6       | 5             |

| 4            |             | 3           | 4*      | 2 <b>/4</b> * |

|              | 2           | 4           | 5       | 3/4*          |

|              |             | 5           | 6       | 4*            |

|              |             | 6           | 7       | 5             |

|              |             | 3           | 7/ 8*   | 6/ 8*         |

|              | 1           | 4           | 8*      | 7/ 8*         |

|              | I           | 5           | 9       | 8*            |

| 8            |             | 6           | 10      | 9             |

| 0            |             | 3 8*        |         | 6 <b>/8</b> * |

|              | 2           | 4           | 9       | 7/8*          |

|              | 2           | 5           | 10      | 8*            |

|              |             | 6           | 11      | 9             |

Above tables are not specification values, rather actual values. There are no gapless operations for CAS latency 6.

<sup>\*:</sup> Minimum clocks for Gapless Operation.

# Technical Notes (Continuous)

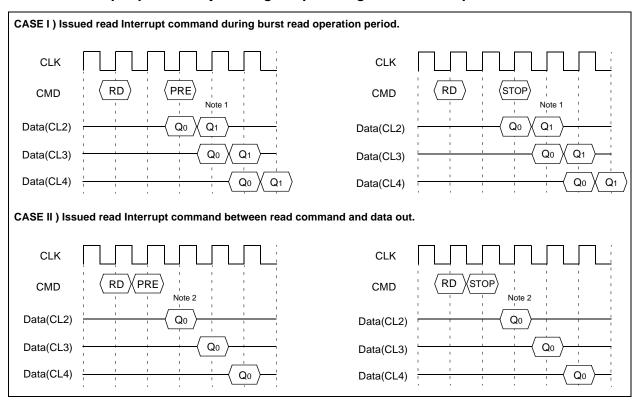

# 2. CAS Interrupt

2. CAS to CAS delay. (=1CLK)

## 3. Read interrupt operation by issuing the precharge or Burst Stop Command

2. Valid output data will last up to CL-1 clock cycle from PRE command.

<sup>\*</sup>Note:

1. By "Interrupt", It is meant to stop burst read by external command before the end of burst. By "CAS Interrupt", to stop burst read by CAS access.

<sup>1.</sup> The data bus goes to High-Z after CAS Latency from the burst stop (or precharge) command.

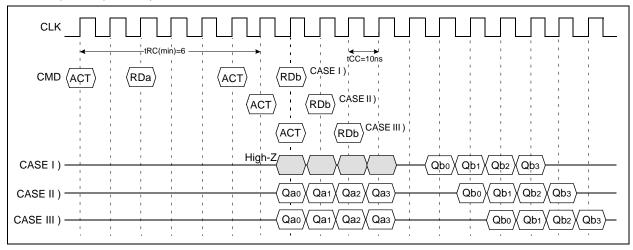

# 4. Read cycle depending on tRC

@ RL = 2, CL = 5, BL = 4; 100MHz

# @ RL = 2, CL = 5, BL = 4; 83MHz

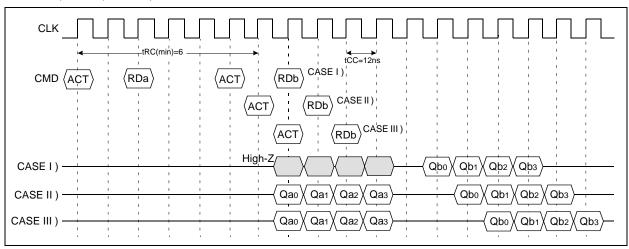

# @ RL = 1, CL = 4, BL = 4; 66MHz

# @ RL = 1, CL = 4, BL = 4; 50MHz

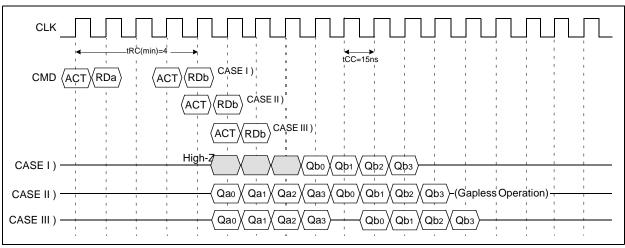

## @ RL = 1, CL = 3, BL = 4; 33MHz

## 5. Read cycle depending on tVCVC

#### @ RL = 2, CL = 5, BL = 4; 100MHz

#### @ RL = 2, CL = 5, BL = 4; 83MHz

## @ RL = 1, CL = 4, BL = 4; 66MHz

# @ RL = 1, CL = 4, BL = 4; 50MHz

#### @ RL = 1, CL = 3, BL = 4; 33MHz

# 6. Read Cycle depending on tvcvc and tRC

#### @ RL = 1, CL = 4, BL = 4; 50MHz (Gapless Operation)

#### @ RL = 1, CL = 4, BL = 4; 50MHz

## @ RL = 1, CL = 4, BL = 4; 50MHz