# Jz4725 Multimedia Application Processor

**Programming Manual**

Revision: 1.0 Date: May 2009

# **Jz4725 Multimedia Application Processor**

# **Programming Manual**

Copyright © Ingenic Semiconductor Co. Ltd 2007. All rights reserved.

# Release history

| Date     | Revision | Change        |

|----------|----------|---------------|

| May 2009 | 1.0      | First release |

# **Disclaimer**

This documentation is provided for use with Ingenic products. No license to Ingenic property rights is granted. Ingenic assumes no liability, provides no warranty either expressed or implied relating to the usage, or intellectual property right infringement except as provided for by Ingenic Terms and Conditions of Sale.

Ingenic products are not designed for and should not be used in any medical or life sustaining or supporting equipment.

All information in this document should be treated as preliminary. Ingenic may make changes to this document without notice. Anyone relying on this documentation should contact Ingenicfor the current documentation and errata.

Ingenic Semiconductor Co., Ltd.

Room 108, Building A, Information Center, Zhongguancun Software Park 8 Dongbeiwang West Road, Haidian District, Beijing, China,

Tel: 86-10-82826661 Fax: 86-10-82825845 Http://www.ingenic.cn

| 1 | Overvi    | ew                                     | 1  |

|---|-----------|----------------------------------------|----|

|   | 1.1 Bloc  | k Diagram                              | 2  |

|   | 1.2 Feat  | tures                                  | 3  |

|   | 1.2.1     | CPU core                               | 3  |

|   | 1.2.2     | Multimedia support                     | 3  |

|   | 1.2.3     | Memory sub-system                      | 3  |

|   | 1.2.4     | Clock generation and power management  | 4  |

|   | 1.2.5     | On-chip peripherals                    | 4  |

|   | 1.3 Cha   | racteristic                            | 6  |

| 2 | CPU C     | Core                                   | 7  |

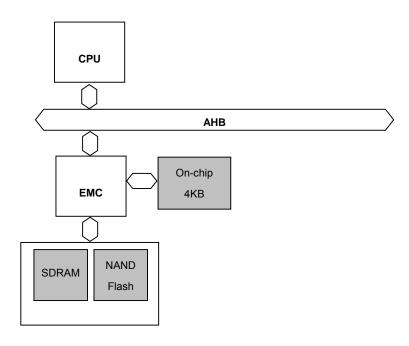

| 3 | Extern    | al Memory Controller                   | 9  |

|   | 3.1 Ove   | rview                                  | 9  |

| ; | 3.2 Pin I | Description                            | 10 |

| ; | 3.3 Phys  | sical Address Space Map                | 11 |

| ; | 3.4 Stati | c Memory Interface                     | 13 |

|   | 3.4.1     | Register Description                   | 14 |

|   | 3.4.2     | Example of Connection                  | 19 |

|   | 3.4.3     | Basic Interface                        | 21 |

|   | 3.4.4     | Byte Control                           | 25 |

|   | 3.4.5     | Burst ROM Interface                    | 28 |

| ; | 3.5 NAN   | ID Flash Interface                     | 29 |

|   | 3.5.1     | Register Description                   | 29 |

|   | 3.5.2     | NAND Flash Boot Loader                 | 36 |

|   | 3.5.3     | NAND Flash Operation                   | 37 |

| ; | 3.6 SDF   | RAM Interface                          | 41 |

|   | 3.6.1     | Register Description                   | 42 |

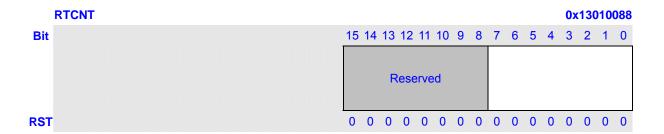

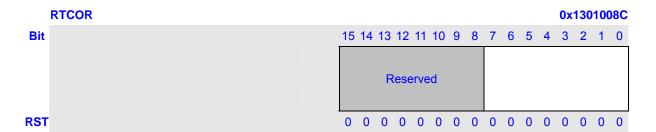

|   | 3.6.2     | Refresh Time Constant Register (RTCOR) | 49 |

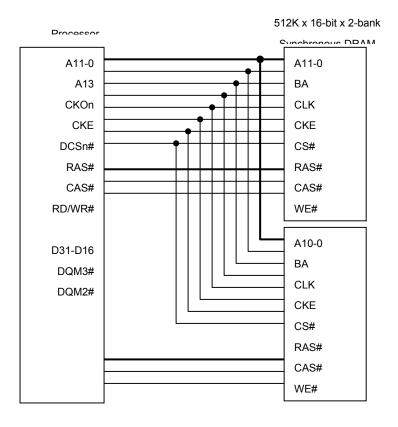

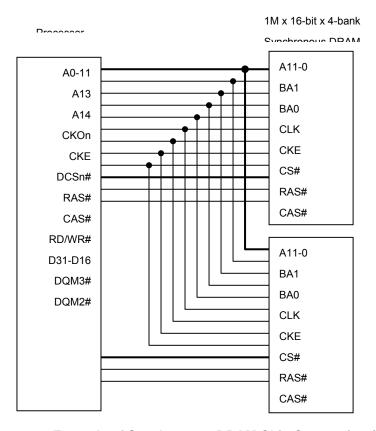

|   | 3.6.3     | Example of Connection                  | 51 |

|   | 3.6.4     | Address Multiplexing                   | 53 |

|   | 3.6.5     | SDRAM Command                          | 56 |

|   | 3.6.6     | SDRAM Timing                           | 57 |

|   | 3.6.7     | Power-Down Mode                        | 71 |

|   | 3.6.8     | Refreshing                             | 72 |

|   | 3.6.9     | Initialize Sequence                    | 76 |

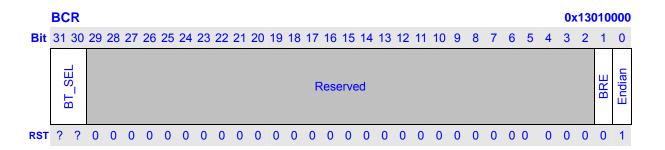

| ; | 3.7 Bus   | Control Register (BCR)                 | 80 |

| 4 | DMA C     | Controller                             | 82 |

| 4.1 F  | Features                                             | 82  |

|--------|------------------------------------------------------|-----|

| 4.2 F  | Register Descriptions                                | 83  |

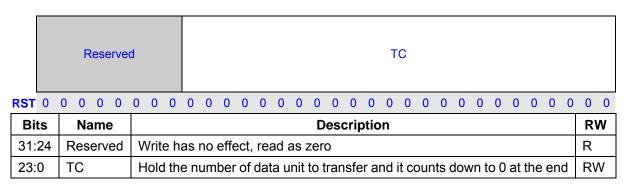

| 4.2.1  | DMA Source Address (DSAn, n = 0 ~ 5)                 | 84  |

| 4.2.2  | DMA Target Address (DTAn, n = 0 ~ 5)                 | 84  |

| 4.2.3  | DMA Transfer Count (DTCn, n = 0 ~ 5)                 | 84  |

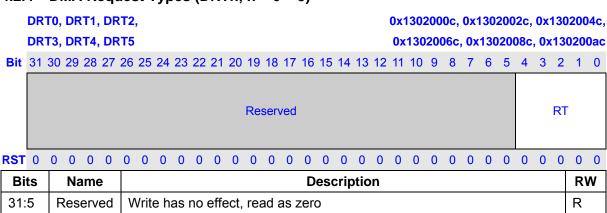

| 4.2.4  | DMA Request Types (DRTn, n = 0 ~ 5)                  | 85  |

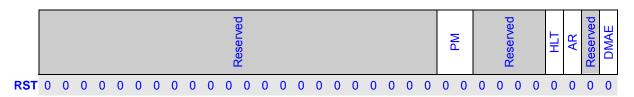

| 4.2.5  | DMA Channel Control/Status (DCSn, n = 0 ~ 5)         | 86  |

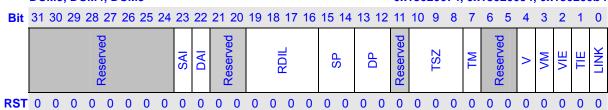

| 4.2.6  | DMA Channel Command (DCMn, n = 0 ~ 5)                | 87  |

| 4.2.7  | DMA Descriptor Address (DDAn, n = 0 ~ 5)             | 88  |

| 4.2.8  | DMA Control                                          | 88  |

| 4.2.9  | DMA Doorbell (DDR)                                   | 89  |

| 4.2.10 | DMA Interrupt Pending (DIRQP)                        | 90  |

| 4.3    | DMA manipulation                                     | 91  |

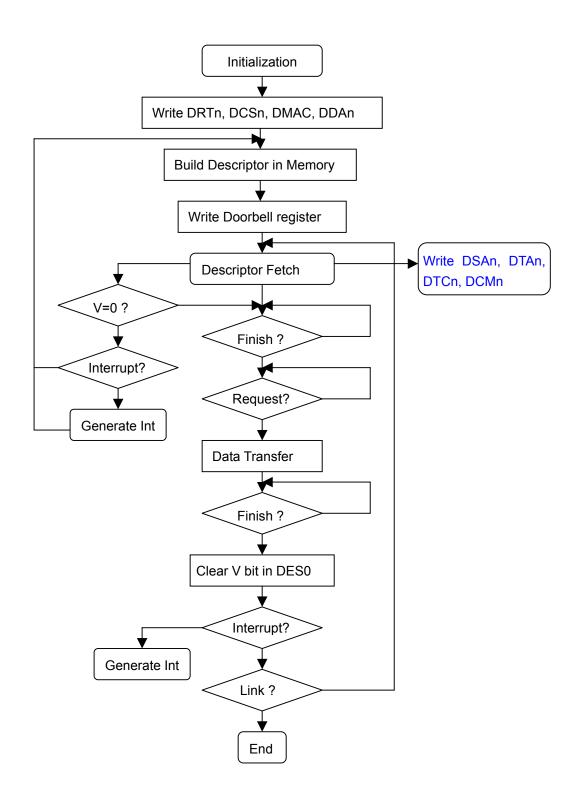

| 4.3.1  | Descriptor Transfer                                  | 91  |

| 4.3.2  | No-Descriptor Transfer                               | 94  |

| 4.4    | DMA Requests                                         | 94  |

| 4.4.1  | Auto Request                                         | 94  |

| 4.4.2  | On-Chip Peripheral Request                           | 94  |

| 4.5    | DMA Transfer Modes                                   | 95  |

| 4.5.1  | Single Mode                                          | 95  |

| 4.5.2  | Block Mode                                           | 95  |

| 4.6    | Channel Priorities                                   | 95  |

| 4.6.1  | Fixed Mode                                           | 95  |

| 4.6.2  | Round Robin Mode                                     | 95  |

| 4.7 E  | Examples                                             | 96  |

| 4.7.1  | Memory-to-memory auto request No-Descriptor Transfer | 96  |

| 5 Clo  | ck Reset and Power Controller                        | 97  |

| 5.1    | Overview                                             | 97  |

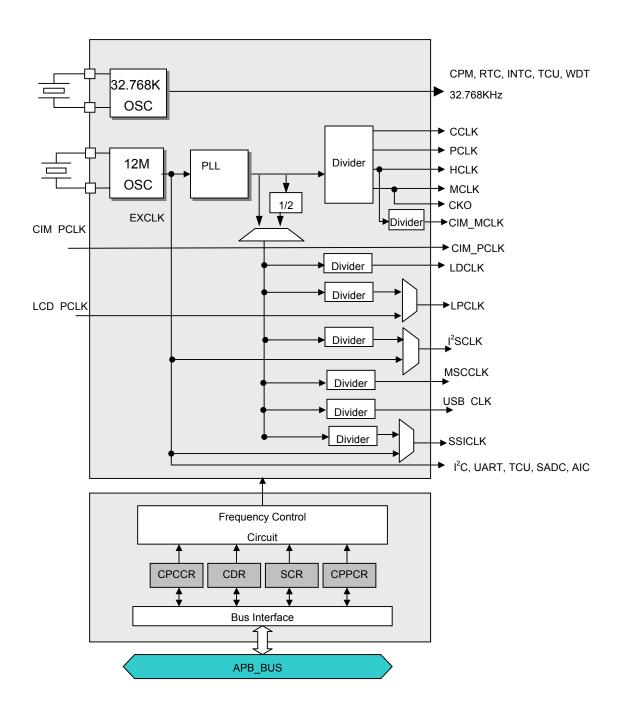

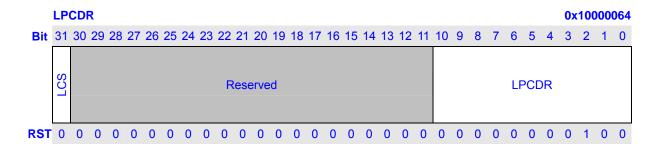

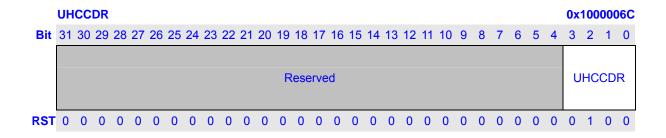

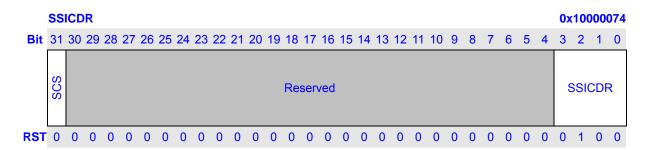

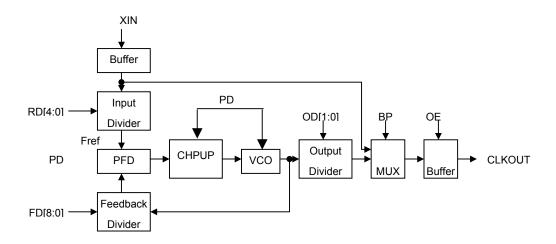

| 5.2    | Clock Generation UNIT                                | 98  |

| 5.2.1  | Pin Description                                      | 99  |

| 5.2.2  | CGU Block Diagram                                    | 100 |

| 5.2.3  | Clock Overview                                       | 101 |

| 5.2.4  | CGU Registers                                        | 102 |

| 5.2.5  | PLL Operation                                        | 109 |

| 5.2.6  | Main Clock Division Change Sequence                  | 110 |

| 5.2.7  | Change Other Clock Frequencies                       | 111 |

| 5.2.8  | Change Clock Source Selection                        |     |

| 5.2.9  | EXCLK Oscillator                                     | 112 |

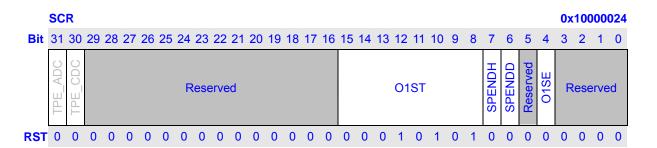

| 5.3 F  | Power Manager                                        | 113 |

| 5.3.1  | Low-Power Modes and Function                         | 113 |

| 5.3.2  | Register Description                                 | 114 |

| 533    | Doze Mode                                            | 118 |

|   | 5.3.4             | IDLE Mode                                                       | 118 |

|---|-------------------|-----------------------------------------------------------------|-----|

|   | 5.3.5             | SLEEP Mode                                                      | 119 |

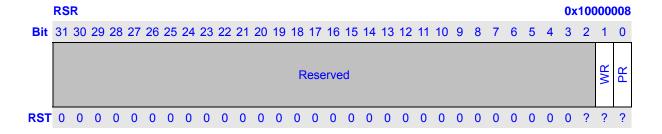

| Ę | 5.4 Res           | et Control Module                                               | 119 |

|   | 5.4.1             | Register Description                                            | 119 |

|   | 5.4.2             | Power On Reset                                                  | 120 |

|   | 5.4.3             | WDT Reset                                                       | 120 |

| 6 | Real-1            | Fime Clock (RTC)                                                | 121 |

| 6 | 6.1 Ove           | erview                                                          | 121 |

|   | 6.1.1             | Features                                                        | 121 |

|   | 6.1.2             | Signal Descriptions                                             | 121 |

| 6 | 6.2 Reg           | jister Description                                              | 123 |

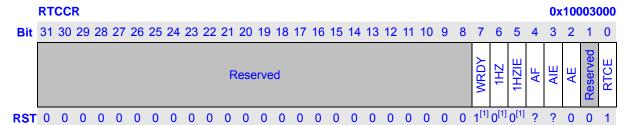

|   | 6.2.1             | RTC Control Register (RTCCR)                                    | 124 |

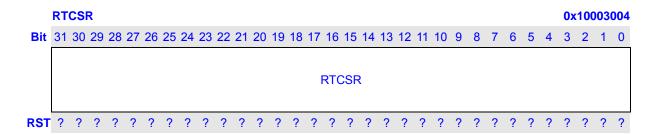

|   | 6.2.2             | RTC Second Register (RTCSR)                                     |     |

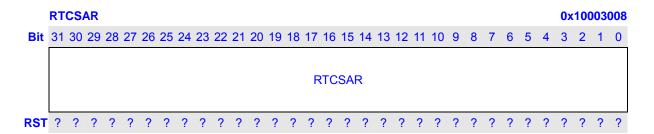

|   | 6.2.3             | RTC Second Alarm Register (RTCSAR)                              | 127 |

|   | 6.2.4             | RTC Regulator Register (RTCGR)                                  | 128 |

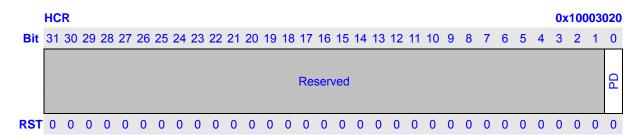

|   | 6.2.5             | Hibernate Control Register (HCR)                                |     |

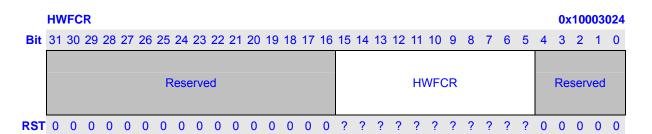

|   | 6.2.6             | HIBERNATE mode Wakeup Filter Counter Register (HWFCR)           |     |

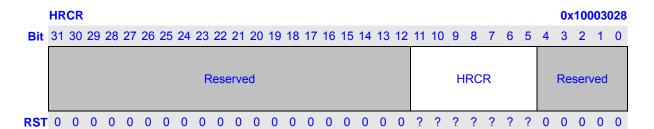

|   | 6.2.7             | Hibernate Reset Counter Register (HRCR)                         |     |

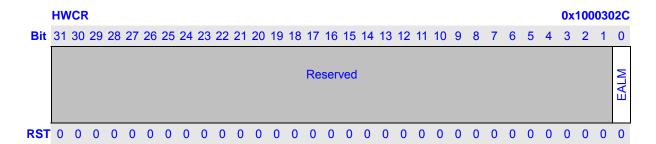

|   | 6.2.8             | HIBERNATE Wakeup Control Register (HWCR)                        |     |

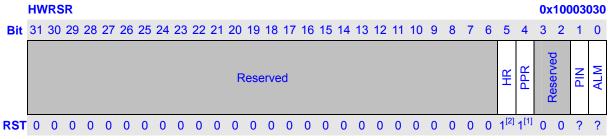

|   | 6.2.9             | HIBERNATE Wakeup Status Register (HWRSR)                        |     |

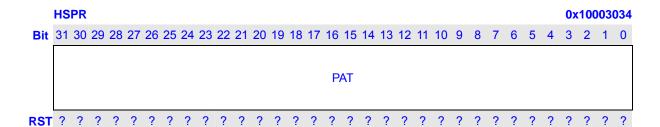

|   | 6.2.10            | Hibernate Scratch Pattern Register (HSPR)                       |     |

| 6 | 6.3 Tim           | e Regulation                                                    |     |

|   | 6.3.1             | HIBERNATE Mode                                                  |     |

| 7 | Interru           | ıpt Controller                                                  | 137 |

| - |                   | rview                                                           |     |

|   |                   | pister Description                                              |     |

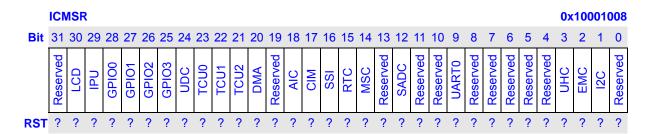

| , | 7.2.1             | Interrupt Controller Source Register (ICSR)                     |     |

|   | 7.2.1<br>7.2.2    | Interrupt Controller Mask Register (ICMR)                       |     |

|   | 7.2.2             |                                                                 |     |

|   | 7.2.3<br>7.2.4    | Interrupt Controller Mask Set Register (ICMSR)                  |     |

|   |                   |                                                                 |     |

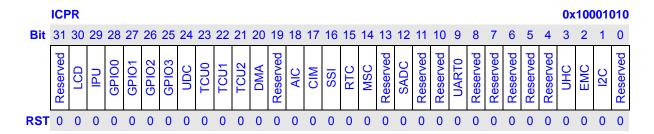

| - | 7.2.5<br>7.3 Soft | Interrupt Controller Pending Register (ICPR)ware Considerations |     |

| 8 |                   | Counter Unit                                                    |     |

|   |                   |                                                                 |     |

|   |                   | rview                                                           |     |

|   |                   | Description                                                     |     |

| 8 | _                 | jister Description                                              |     |

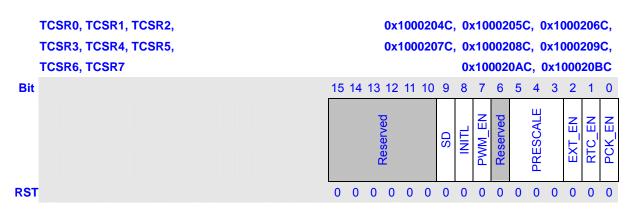

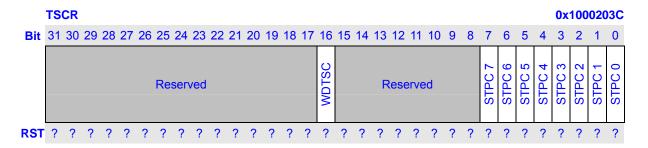

|   | 8.3.1             | Timer Control Register (TCSR)                                   |     |

|   | 8.3.2             | Timer Data FULL Register (TDFR)                                 |     |

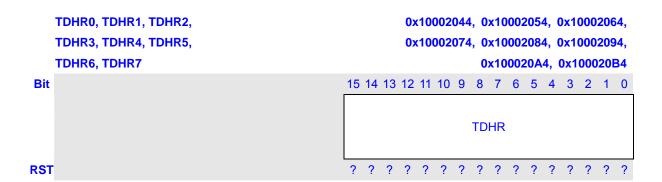

|   | 8.3.3             | Timer Data HALF Register (TDHR)                                 |     |

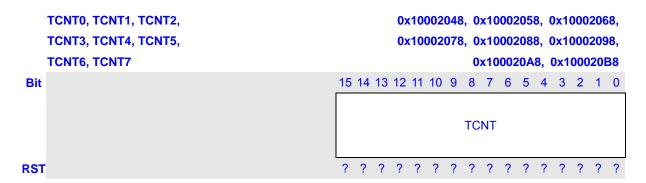

|   | 8.3.4             | Timer Counter (TCNT)                                            | 148 |

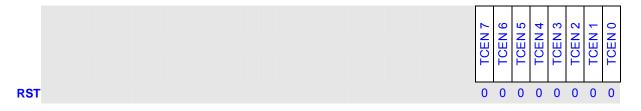

| 8.3.5   | Timer Counter Enable Register (TER)                           | 148 |

|---------|---------------------------------------------------------------|-----|

| 8.3.6   | Timer Counter Enable Set Register (TESR)                      | 149 |

| 8.3.7   | Timer Counter Enable Clear Register (TECR)                    | 150 |

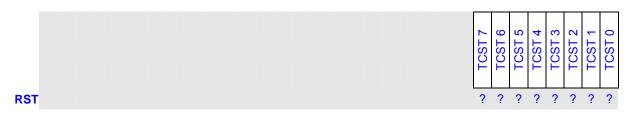

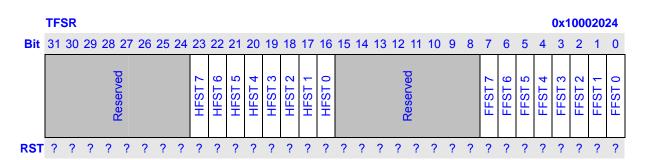

| 8.3.8   | Timer Flag Register (TFR)                                     | 151 |

| 8.3.9   | Timer Flag Set Register (TFSR)                                | 152 |

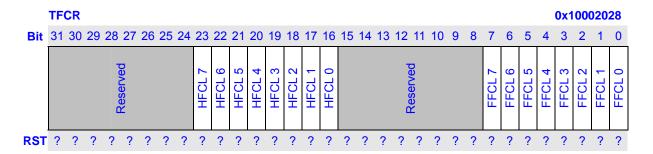

| 8.3.10  | Timer Flag Clear Register (TFCR)                              | 153 |

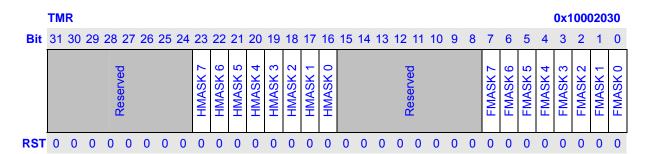

| 8.3.11  | Timer Mast Register (TMR)                                     | 153 |

| 8.3.12  | Timer Mask Set Register (TMSR)                                | 154 |

| 8.3.13  | Timer Mask Clear Register (TMCR)                              | 154 |

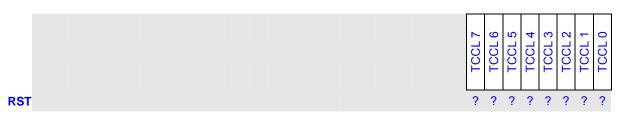

| 8.3.14  | Timer Stop Register (TSR)                                     | 155 |

| 8.3.15  | Timer Stop Set Register (TSSR)                                | 156 |

| 8.3.16  | Timer Stop Clear Register (TSCR)                              | 157 |

| 8.4 Op  | eration                                                       | 158 |

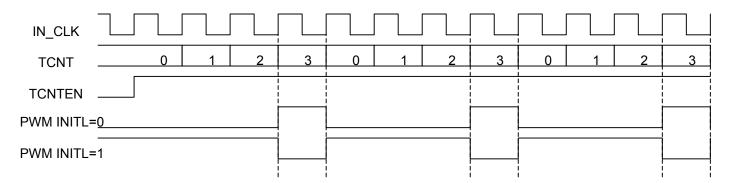

| 8.4.1   | Basic Operation                                               | 158 |

| 8.4.2   | Disable and Shutdown Operation                                | 159 |

| 8.4.3   | Pulse Width Modulator (PWM)                                   | 159 |

| 8.4.4   | The flow of using TCU5                                        | 159 |

| 9 Watch | ndog Timer                                                    | 161 |

|         |                                                               |     |

|         | erview                                                        |     |

|         | gister Description                                            |     |

| 9.2.1   | Watchdog Control Register (TCSR)                              |     |

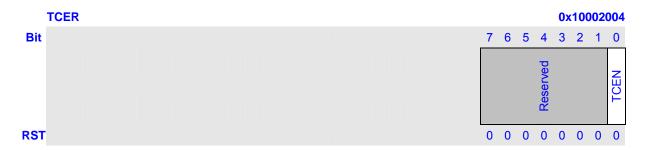

| 9.2.2   | Watchdog Enable Register (TCER)                               |     |

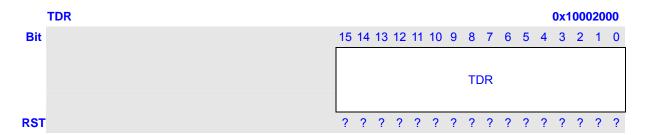

| 9.2.3   | Watchdog Timer Data Register (TDR)                            |     |

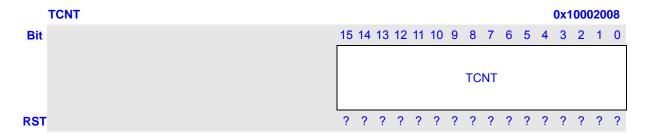

| 9.2.4   | Watchdog Timer Counter (TCNT)                                 |     |

| 9.3 Wa  | tchdog Timer Function                                         | 164 |

| 10 Gene | ral-Purpose I/O Ports                                         | 165 |

| 10.1 Ov | erview                                                        | 165 |

| 10.2 Re | gister Description                                            |     |

| 10.2.1  | PORT PIN Level Register (PAPIN, PBPIN, PCPIN, PDPIN)          |     |

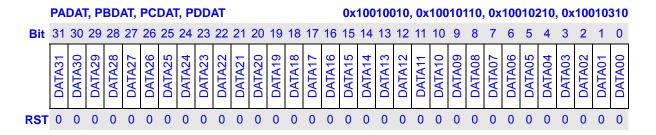

| 10.2.2  | PORT Data Register (PADAT, PBDAT, PCDAT, PDDAT)               | 175 |

| 10.2.3  | PORT Data Set Register (PADATS, PBDATS, PCDATS, PDDATS)       | 176 |

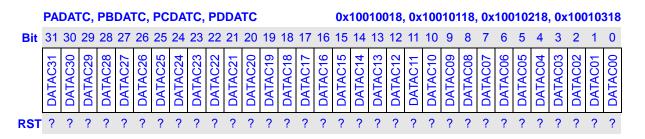

| 10.2.4  | PORT Data Clear Register (PADATC, PBDATC, PCDATC, PDDATC)     | 176 |

| 10.2.5  | PORT Mask Register (PAIM, PBIM, PCIM, PDIM)                   | 177 |

| 10.2.6  | PORT Mask Set Register (PAIMS, PBIMS, PCIMS, PDIMS)           | 177 |

| 10.2.7  | PORT Mask Clear Register (PAIMC, GBPIMC, PCIMC, PDIMC)        | 178 |

| 10.2.8  | PORT PULL Disable Register (PAPE, PBPE, PCPE, PDPE)           | 178 |

| 10.2.9  | PORT PULL Set Register (PAPES, PBPES, PCPES, PDPES)           | 179 |

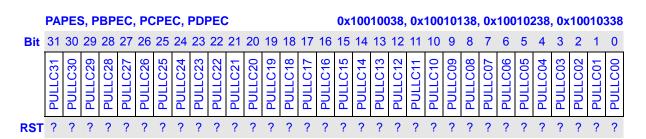

| 10.2.10 | PORT PULL Clear Register (PAPEC, PBPEC, PCPEC, PDPEC)         | 179 |

| 10.2.11 | PORT Function Register (PAFUN, PBFUN, PCFUN, PDFUN)           | 180 |

| 10.2.12 | PORT Function Set Register (PAFUNS, PBFUNS, PCFUNS, PDFUNS)   | 180 |

| 10.2.13 | PORT Function Clear Register (PAFUNC, PBFUNC, PCFUNC, PDFUNC) | 181 |

|   | 10.2.14  | PORT Select Register (PASEL, PBSEL, PCFSEL, PDSEL)               | 181 |

|---|----------|------------------------------------------------------------------|-----|

|   | 10.2.15  | PORT Select Set Register (PASELS, PBSELS, PCSELS, PDSELS)        | 182 |

|   | 10.2.16  | PORT Select Clear Register (PASELC, PBSELC, PCSELC, PDSELC)      |     |

|   | 10.2.17  | PORT Direction Register (PADIR, PBDIR, PCDIR, PDDIR)             | 182 |

|   | 10.2.18  | PORT Direction Set Register (PADIRS, PBDIRS, PCDIRS, PDDIRS)     | 183 |

|   | 10.2.19  | PORT Direction Clear Register (PADIRC, PBDIRC, PCDIRC, PDDIRC)   | 184 |

|   | 10.2.20  | PORT Trigger Register 0, 1, 2 and 3 (PATRG, PBTRG, PCTRG, PDTRG) | 184 |

|   | 10.2.21  | PORT Trigger Set Register (PATRGS, PBTRGS, PCTRGS, PDTRGS)       | 185 |

|   | 10.2.22  | PORT Trigger Clear Register (PATRGC, PBTRGC, PCTRGC, PDTRGC)     | 185 |

|   | 10.2.23  | PORT FLAG Register (PAFLG, PBFLG, PCFLG, PDFLG)                  | 185 |

|   | 10.2.24  | PORT FLAG Clear Register (PAFLGC, PBFLGC, PCFLGC, PDFLGC)        | 186 |

|   | 10.3 Pro | gram Guide                                                       | 187 |

|   | 10.3.1   | GPIO Function Guide                                              | 187 |

|   | 10.3.2   | Alternate Function Guide                                         | 187 |

|   | 10.3.3   | Interrupt Function Guide                                         | 187 |

|   | 10.3.4   | Disable Interrupt Function Guide                                 | 188 |

| 1 | 1 I CD ( | Controller                                                       | 189 |

| • |          |                                                                  |     |

|   |          | erview                                                           |     |

|   |          | Description                                                      |     |

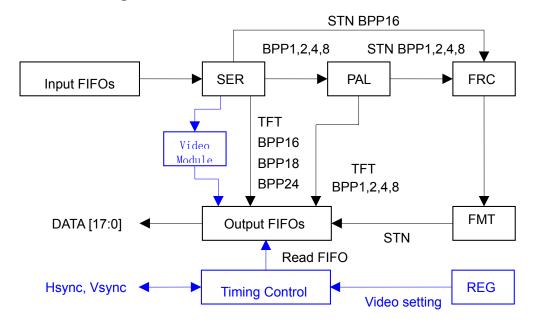

|   |          | ck Diagram                                                       |     |

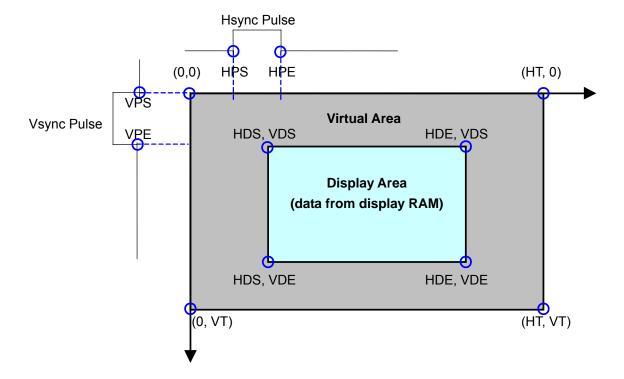

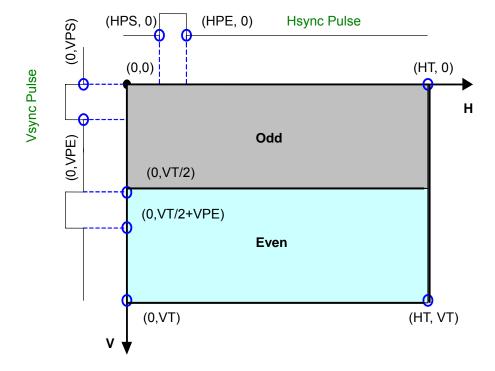

|   |          | D Display Timing                                                 |     |

|   |          | Encoder Timing                                                   |     |

|   |          | gister Description                                               |     |

|   | 11.6.1   | Configure Register (LCDCFG)                                      |     |

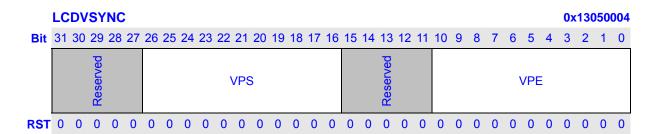

|   | 11.6.2   | Vertical Synchronize Register (LCDVSYNC)                         |     |

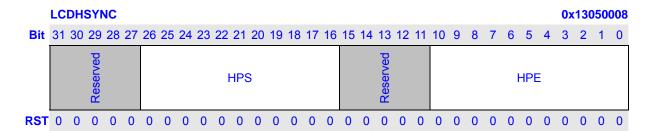

|   | 11.6.3   | Horizontal Synchronize Register (LCDHSYNC)                       |     |

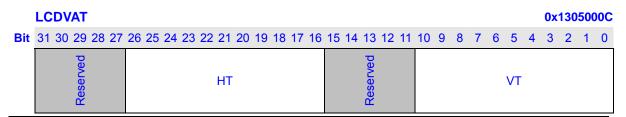

|   | 11.6.4   | Virtual Area Setting (LCDVAT)                                    |     |

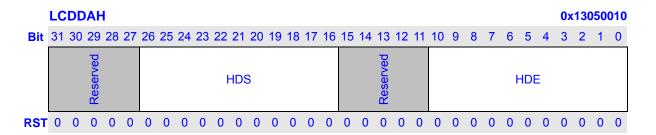

|   | 11.6.5   | Display Area Horizontal Start/End Point (LCDDAH)                 |     |

|   | 11.6.6   | Display Area Vertical Start/End Point (LCDDAV)                   |     |

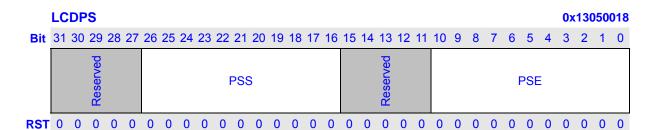

|   | 11.6.7   | PS Signal Setting (LCDPS)                                        |     |

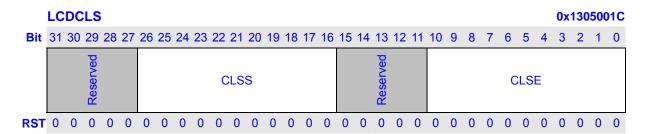

|   | 11.6.8   | CLS Signal Setting (LCDCLS)                                      |     |

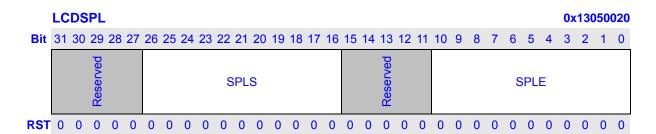

|   | 11.6.9   | SPL Signal Setting (LCDSPL)                                      |     |

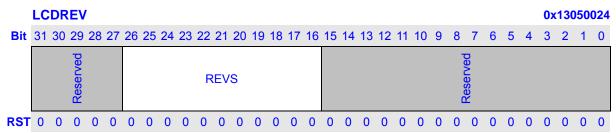

|   | 11.6.10  | REV Signal Setting (LCDREV)                                      |     |

|   | 11.6.11  | Control Register (LCDCTRL)                                       |     |

|   | 11.6.12  | Status Register (LCDSTATE)                                       |     |

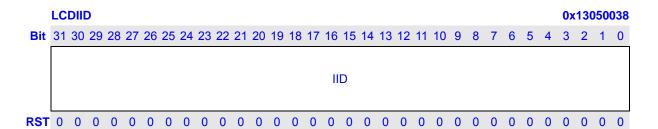

|   | 11.6.13  | Interrupt ID Register (LCDIID)                                   |     |

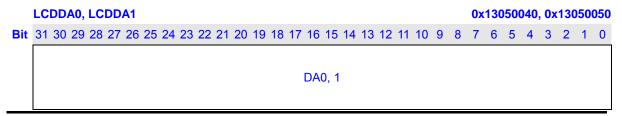

|   | 11.6.14  | Descriptor Address Register0, 1 (LCDDA0, 1)                      |     |

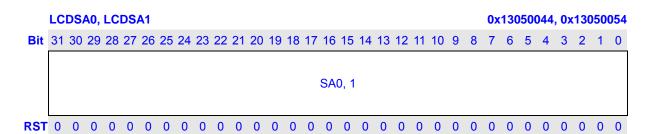

|   | 11.6.15  | Source Address Register0, 1 (LCDSA0, 1)                          |     |

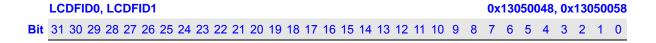

|   | 11.6.16  | Frame ID Register0 (LCDFID0,1)                                   |     |

|   | 11.6.17  | DMA Command Register0, 1 (LCDCMD0, 1)                            |     |

|   |          | Controller Pin Mapping                                           |     |

|   | 11.7.1   | TFT and CCIR656 Pin Mapping                                      | ∠∪6 |

| 11.7.2    | Single STN Pin Mapping                          | 208 |

|-----------|-------------------------------------------------|-----|

| 11.7.3    | Dual Panel STN Pin Mapping                      | 209 |

| 11.8 Dis  | play Timing                                     | 210 |

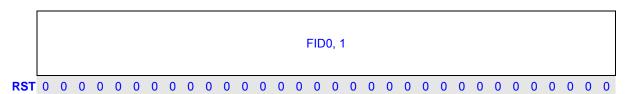

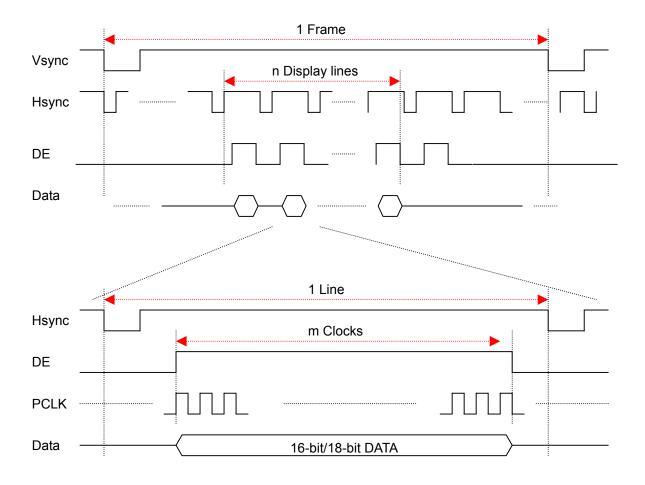

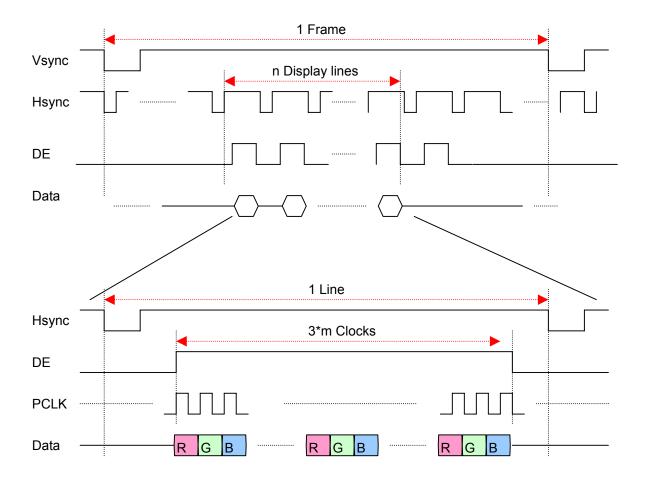

| 11.8.1    | General 16-bit and 18-bit TFT Timing            | 210 |

| 11.8.2    | 8-bit Serial TFT Timing                         | 211 |

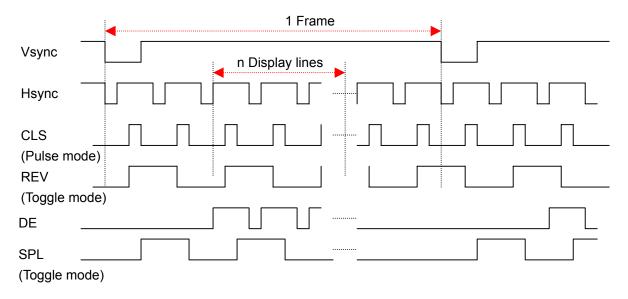

| 11.8.3    | Special TFT Timing                              | 212 |

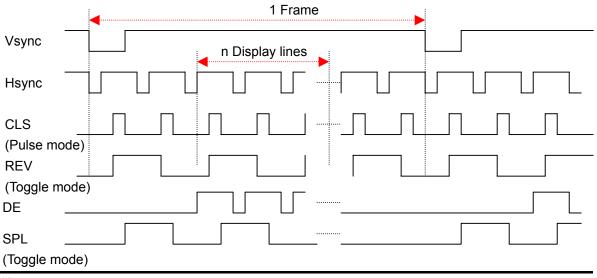

| 11.9 For  | mat of Palette                                  | 214 |

| 11.9.1    | STN                                             | 214 |

| 11.9.2    | TFT                                             | 214 |

| 11.10 F   | ormat of Frame Buffer                           | 215 |

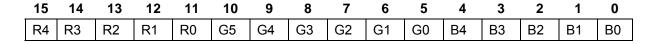

| 11.10.1   | 16bpp                                           | 215 |

| 11.10.2   | 18bpp                                           | 215 |

| 11.10.3   | 24bpp                                           | 215 |

| 11.11 F   | ormat of Data Pin Utilization                   | 215 |

| 11.11.1   | Mono STN                                        | 215 |

| 11.11.2   | Color STN                                       | 216 |

| 11.11.3   | 18-bit Parallel TFT                             | 216 |

| 11.11.4   | 16-bit Parallel TFT                             | 216 |

| 11.11.5   | 8-bit Serial TFT (24bpp)                        | 216 |

| 11.12 L   | CD Controller Operation                         | 216 |

| 11.12.1   | Set LCD Controller Device Clock and Pixel Clock | 216 |

| 11.12.2   | Enabling the Controller                         | 217 |

| 11.12.3   | Disabling the Controller                        | 217 |

| 11.12.4   | Resetting the Controller                        | 218 |

| 11.12.5   | Frame Buffer & Palette Buffer                   | 218 |

| 12 Smart  | LCD Controller                                  | 219 |

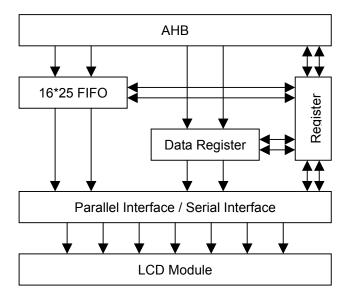

| 12.1 Ove  | erview                                          | 219 |

|           | icture                                          |     |

|           | Description                                     |     |

|           | gister Description                              |     |

| 12.4.1    | SLCD Configure Register (MCFG)                  |     |

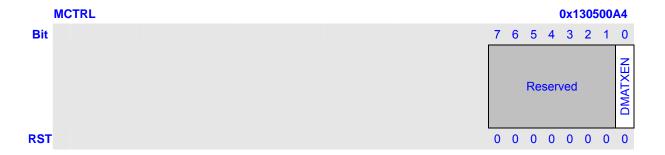

| 12.4.2    | SLCD Control Register (MCTRL)                   |     |

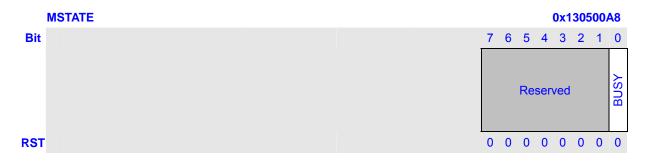

| 12.4.3    | SLCD Status Register (MSTATE)                   | 223 |

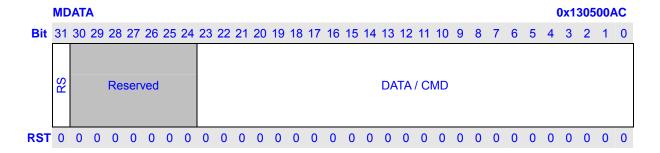

| 12.4.4    | SLCD Data Register (MDATA)                      | 223 |

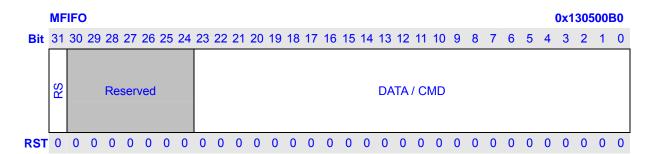

| 12.4.5    | SLCD FIFO (MFIFO)                               | 224 |

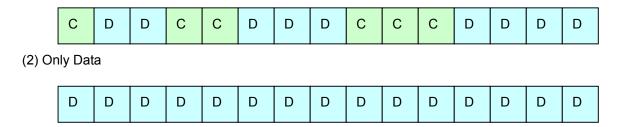

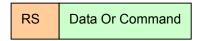

| 12.5 Sys  | tem Memory Format                               | 225 |

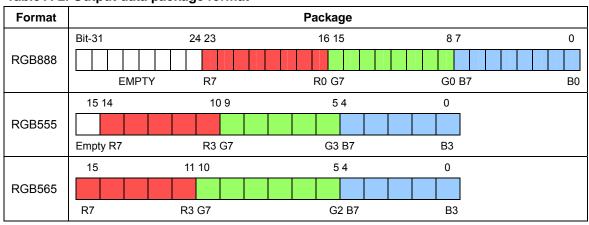

| 12.5.1    | Data format                                     | 225 |

| 12.5.2    | Command Format                                  | 226 |

| 12.6 Trai | nsfer Mode                                      |     |

| 12.6.1    | DMA Transfer Mode                               | 227 |

| 12.6.2    | Register Transfer Mode                          |     |

| 12.7 Tim  | ing                                             | 227 |

|           |                                                 |     |

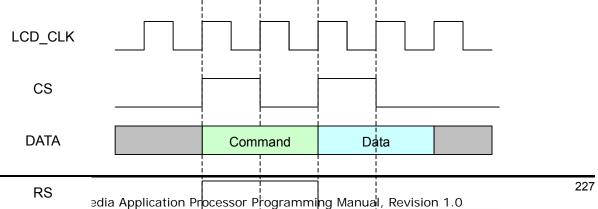

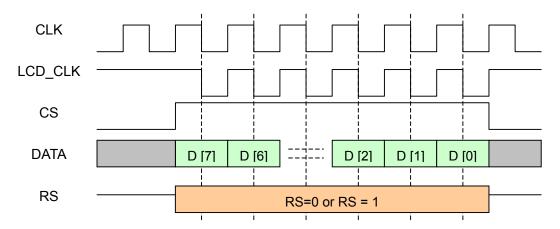

| 12.7.1   | Parallel Timing                                                        | 227   |

|----------|------------------------------------------------------------------------|-------|

| 12.7.2   | Serial Timing                                                          | 228   |

| 12.8 Ope | eration Guide                                                          | 228   |

| 12.8.1   | DMA Operation                                                          | 228   |

| 12.8.2   | Register Operation                                                     | 228   |

| 13 AC97/ | /I2S Controller                                                        | 230   |

| 13.1 Ove | erview                                                                 | 230   |

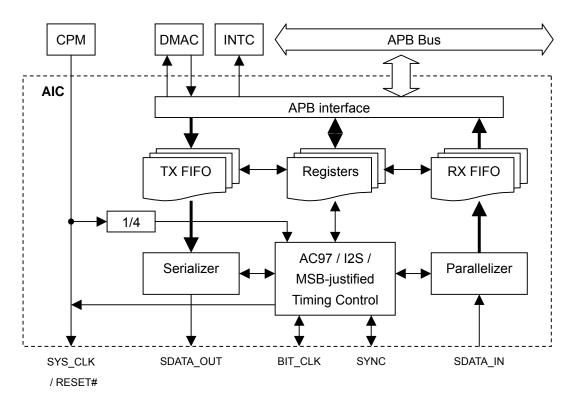

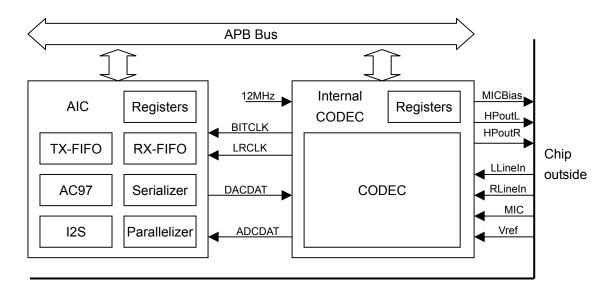

| 13.1.1   | Block Diagram                                                          | 231   |

| 13.1.2   | Features                                                               | 231   |

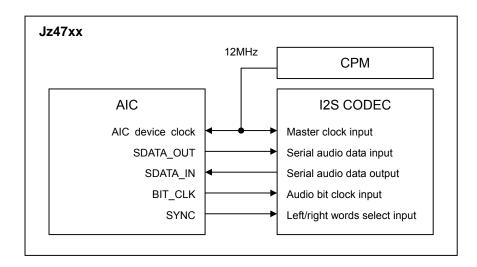

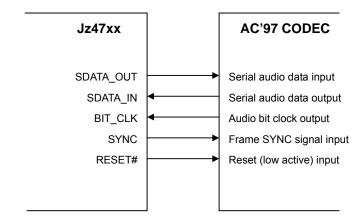

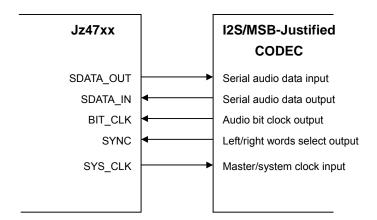

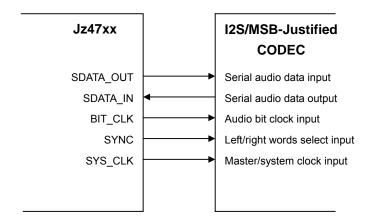

| 13.1.3   | Interface Diagram                                                      | 232   |

| 13.1.4   | Signal Descriptions                                                    | 234   |

| 13.1.5   | RESET# / SYS_CLK Pin                                                   | 234   |

| 13.1.6   | BIT_CLK Pin                                                            | 234   |

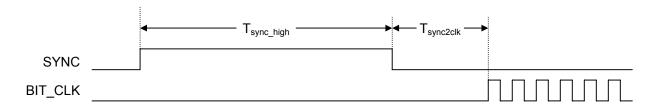

| 13.1.7   | SYNC Pin                                                               | 234   |

| 13.1.8   | SDATA_OUT Pin                                                          | 235   |

| 13.1.9   | SDATA_IN Pin                                                           | 235   |

| 13.2 Reg | gister Descriptions                                                    | 236   |

| 13.2.1   | AIC Configuration Register (AICFR)                                     | 238   |

| 13.2.2   | AIC Common Control Register (AICCR)                                    | 240   |

| 13.2.3   | AIC AC-link Control Register 1 (ACCR1)                                 | 243   |

| 13.2.4   | AIC AC-link Control Register 2 (ACCR2)                                 | 244   |

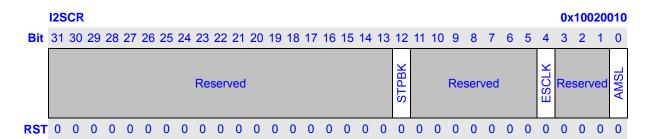

| 13.2.5   | AIC I2S/MSB-justified Control Register (I2SCR)                         | 246   |

| 13.2.6   | AIC Controller FIFO Status Register (AICSR)                            | 247   |

| 13.2.7   | AIC AC-link Status Register (ACSR)                                     | 249   |

| 13.2.8   | AIC I2S/MSB-justified Status Register (I2SSR)                          | 251   |

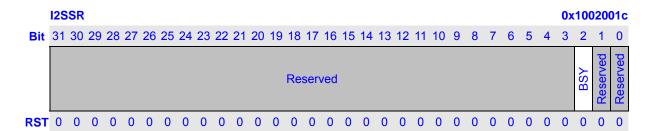

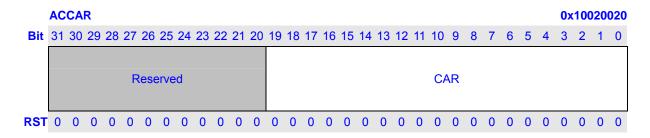

| 13.2.9   | AIC AC97 CODEC Command Address Register (ACCAR) & Data Register (ACCD  | R)252 |

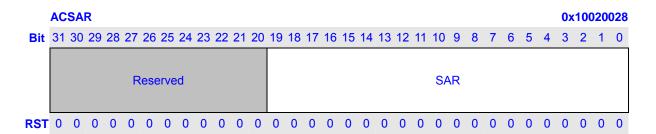

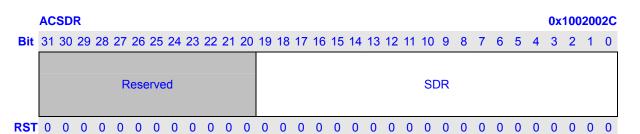

| 13.2.10  | AIC AC97 CODEC Status Address Register (ACSAR) & Data Register (ACSDR) | . 253 |

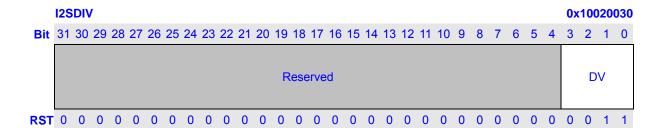

| 13.2.11  | AIC I2S/MSB-justified Clock Divider Register (I2SDIV)                  | 254   |

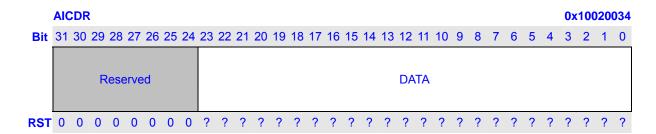

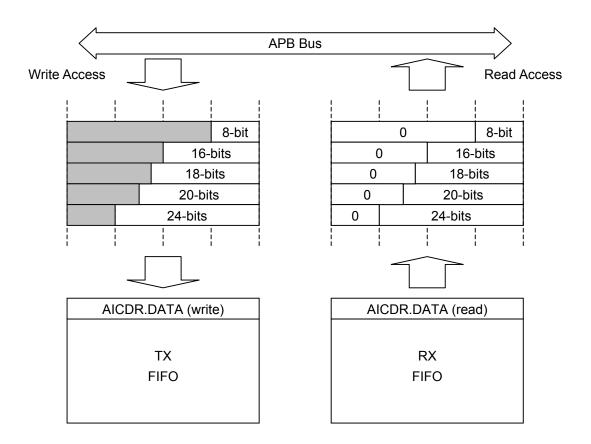

| 13.2.12  | AIC FIFO Data Port Register (AICDR)                                    | 255   |

| 13.3 Ser | ial Interface Protocol                                                 | 256   |

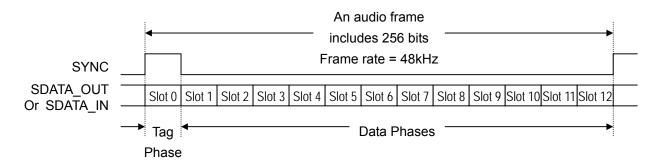

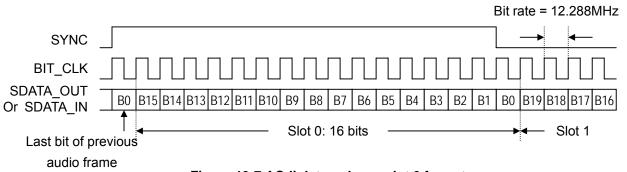

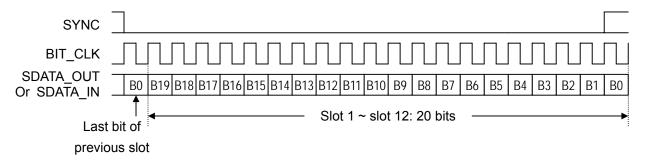

| 13.3.1   | AC-link serial data format                                             | 256   |

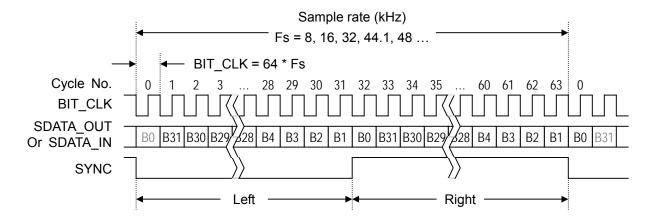

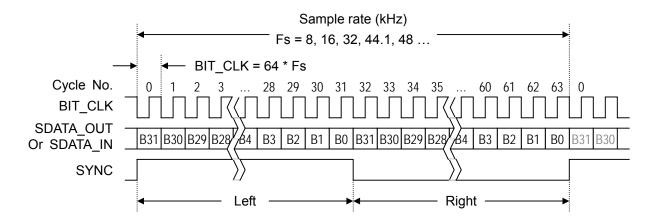

| 13.3.2   | I2S and MSB-justified serial audio format                              | 257   |

| 13.3.3   | Audio sample data placement in SDATA_IN/SDATA_OUT                      | 259   |

| 13.4 Ope | eration                                                                | 260   |

| 13.4.1   | Initialization                                                         | 261   |

| 13.4.2   | AC '97 CODEC Power Down                                                | 262   |

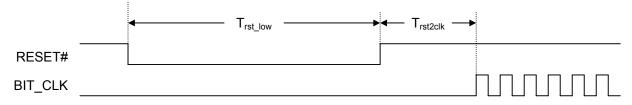

| 13.4.3   | Cold and Warm AC '97 CODEC Reset                                       | 262   |

| 13.4.4   | External CODEC Registers Access Operation                              | 264   |

| 13.4.5   | Audio Replay                                                           | 265   |

| 13.4.6   | Audio Record                                                           | 266   |

| 13.4.7   | FIFOs operation                                                        | 267   |

| 13 4 8   | Data Flow Control                                                      | 269   |

|        | 4.9  | Serial Audio Clocks and Sampling Frequencies                              |     |

|--------|------|---------------------------------------------------------------------------|-----|

|        | 4.10 | Interrupts                                                                |     |

| 14 Int | ern  | al CODEC                                                                  | 275 |

| 14.1   | Ove  | erview                                                                    | 275 |

| 14.    | 1.1  | Features                                                                  | 275 |

| 14.    | 1.2  | Signal Descriptions                                                       | 275 |

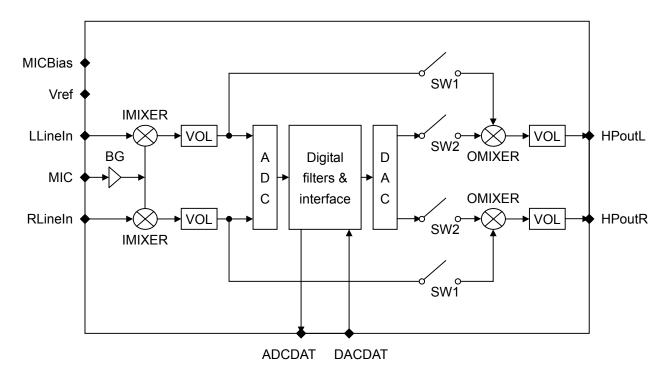

| 14.    | 1.3  | Block Diagram                                                             | 276 |

| 14.2   | Reg  | gister Descriptions                                                       | 277 |

| 14.    | 2.1  | CODEC Control Register 1 (CDCCR1)                                         | 278 |

| 14.    | 2.2  | CODEC Control Register 2 (CDCCR2)                                         | 280 |

| 14.3   | Оре  | eration                                                                   | 282 |

| 14.    | 3.1  | Initialization                                                            | 282 |

| 14.3   | 3.2  | CODEC controlling and typical operations                                  | 283 |

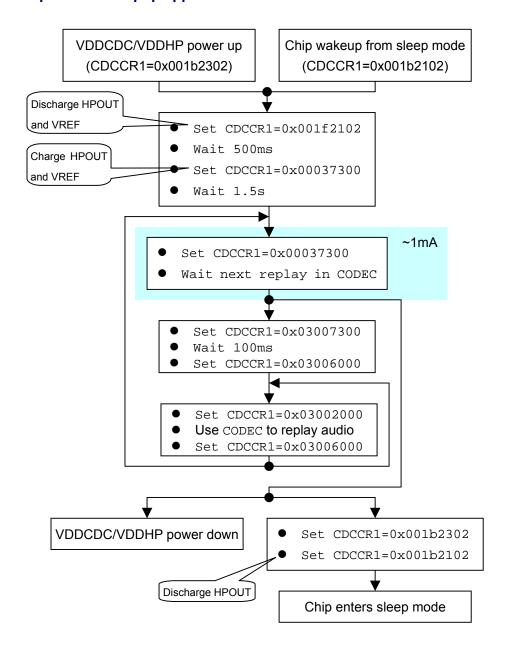

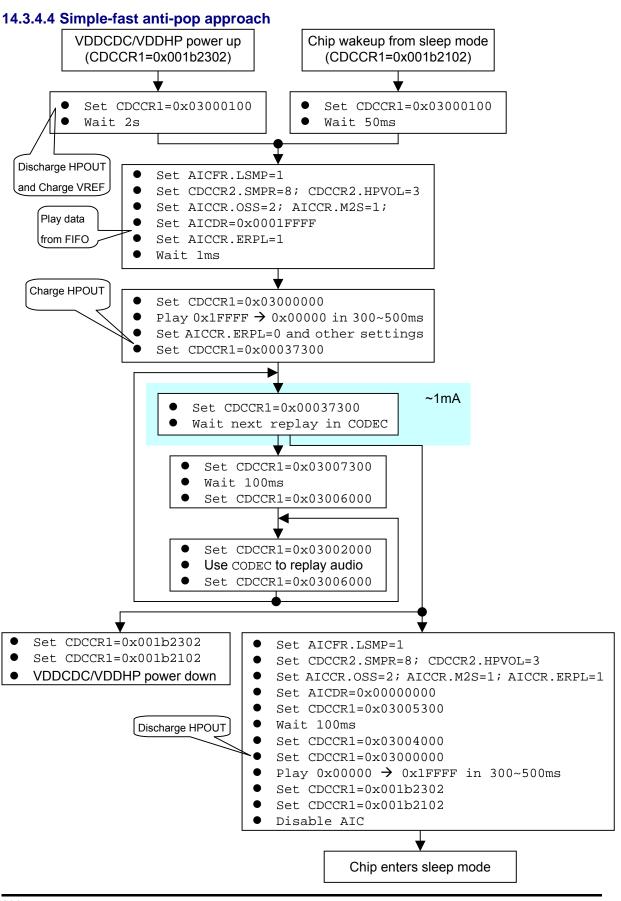

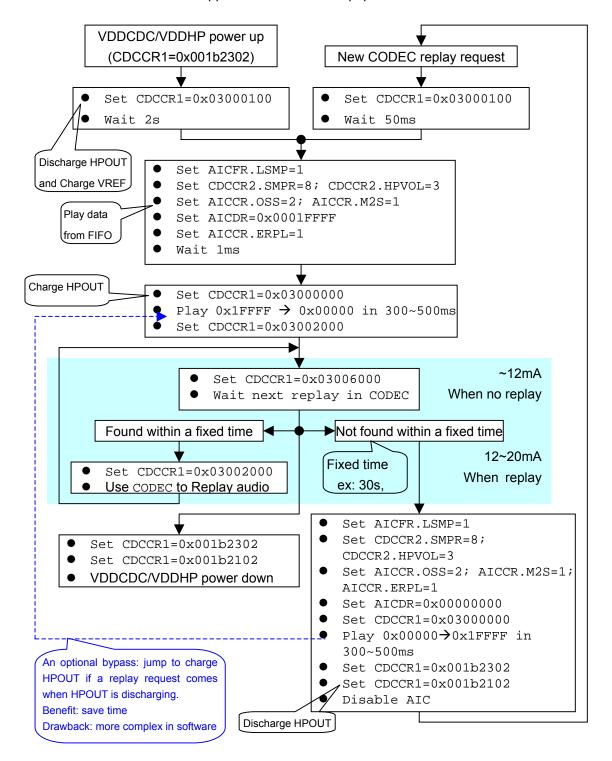

| 14.    | 3.3  | Power saving                                                              | 285 |

| 14.    | 3.4  | Pop noise and the reduction of it                                         | 286 |

| 14.4   | Tim  | ing parameters                                                            | 293 |

| 14.5   | AC   | & DC parameters                                                           | 293 |

| 15 SA  | AR A | VD Controller                                                             | 294 |

| 15.1   | Ove  | erview                                                                    | 294 |

| 15.2   | Pin  | Description                                                               | 294 |

| 15.3   | Reg  | gister Description                                                        | 295 |

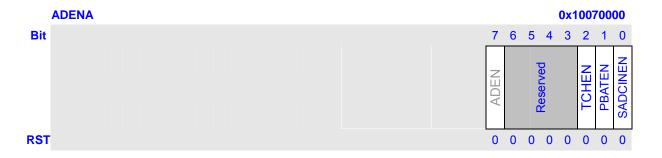

| 15.    | 3.1  | ADC Enable Register (ADENA)                                               | 296 |

| 15.    | 3.2  | ADC Configure Register (ADCFG)                                            | 297 |

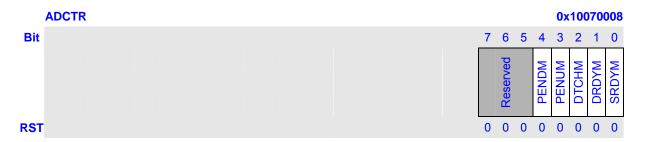

| 15.    | 3.3  | ADC Control Register (ADCTRL)                                             | 299 |

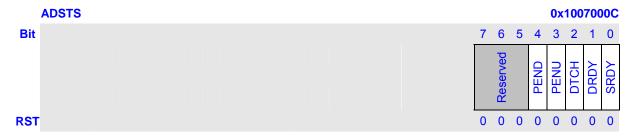

| 15.    | 3.4  | ADC Status Register (ADSTATE)                                             | 300 |

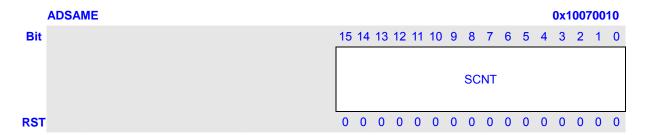

| 15.    | 3.5  | ADC Same Point Time Register (ADSAME)                                     |     |

| 15.3   | 3.6  | ADC Wait Pen Down Time Register (ADWAIT)                                  |     |

| 15.3   | 3.7  | ADC Touch Screen Data Register (ADTCH)                                    |     |

| 15.    | 3.8  | ADC PBAT Data Register (ADBDAT)                                           |     |

| 15.    | 3.9  | ADC SADCIN Data Register (ADSDAT)                                         |     |

| 15.    | 3.10 | ADC IP DATA PIN (ADDPIN)                                                  |     |

| 15.4   | SAI  | R A/D Controller Guide                                                    |     |

| 15.4   |      | Single Operation (only used as a test mode to check the channel function) |     |

| 15.4   |      | A simple Touch Screen Operation                                           |     |

| 15.4   |      | PBAT Sample Operation                                                     |     |

| 15.4   |      | SADCIN Sample Operation                                                   |     |

| 15.4   |      | Use TSC to support keypad                                                 |     |

|        |      | /lediaCard/Secure Digital Controller                                      |     |

|        |      | · ·                                                                       |     |

| 16.1   |      | erview                                                                    |     |

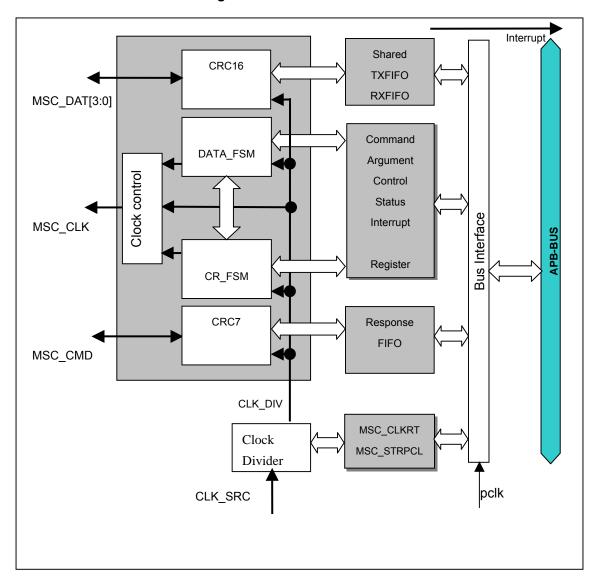

| 16.2   | RI0  | ck Diagram                                                                | 313 |

| 16.3 | ММ   | C/SD Controller Signal I/O Description                               | 314 |

|------|------|----------------------------------------------------------------------|-----|

| 16.4 |      | ister Description                                                    |     |

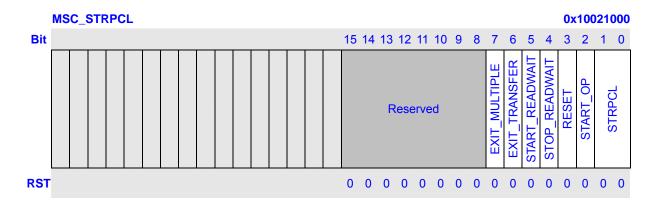

| 16.4 | ·    | Start/stop MMC/SD clock Register (MSC_STRPCL)                        |     |

| 16.4 |      | MSC Status Register (MSC_STAT)                                       |     |

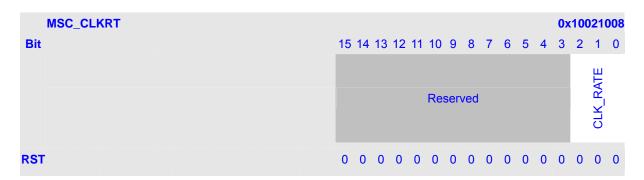

| 16.4 |      | MSC Clock Rate Register (MSC_CLKRT)                                  |     |

| 16.4 |      | MMC/SD Command and Data Control Register (MSC_CMDAT)                 |     |

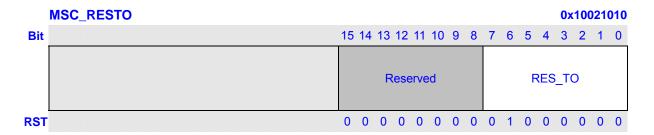

| 16.4 | 1.5  | MMC/SD Response Time Out Register (MSC_RESTO)                        |     |

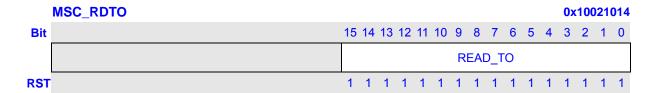

| 16.4 | ł.6  | MMC/SD Read Time Out Register (MSC RDTO)                             |     |

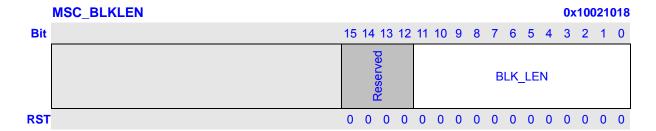

| 16.4 | 1.7  | MMC/SD Block Length Register (MSC_BLKLEN)                            |     |

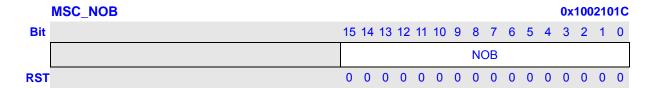

| 16.4 | 1.8  | MSC/SD Number of Block Register (MSC_NOB)                            |     |

| 16.4 | 1.9  | MMC/SD Number of Successfully-transferred Blocks Register (MSC_SNOB) |     |

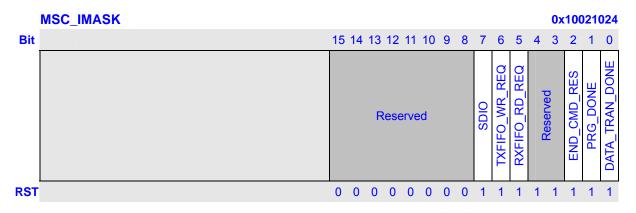

| 16.4 | 1.10 | MMC/SD Interrupt Mask Register (MSC_IMASK)                           |     |

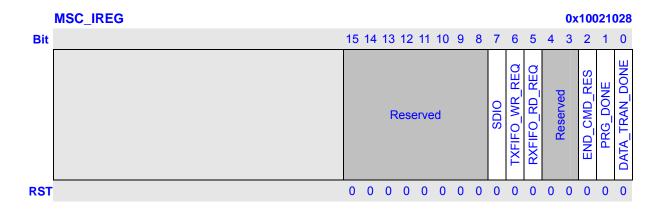

| 16.4 | l.11 | MMC/SD Interrupt Register (MSC_IREG)                                 | 324 |

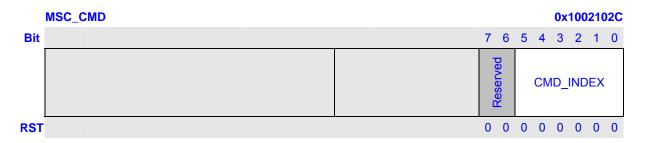

| 16.4 | 1.12 | MMC/SD Command Index Register (MSC_CMD)                              | 325 |

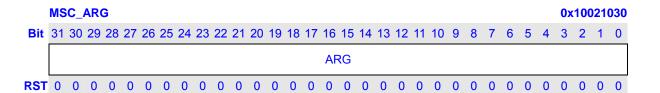

| 16.4 | 1.13 | MMC/SD Command Argument Register (MSC_ARG)                           | 325 |

| 16.4 | 1.14 | MMC/SD Response FIFO Register (MSC_RES)                              | 325 |

| 16.4 | 1.15 | MMC/SD Receive Data FIFO Register (MSC_RXFIFO)                       | 326 |

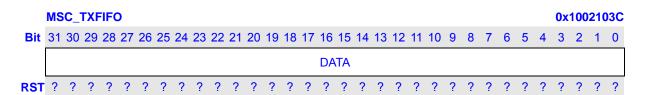

| 16.4 | 1.16 | MMC/SD Transmit Data FIFO Register (MSC_TXFIFO)                      | 326 |

| 16.5 | MM   | C/SD Functional Description                                          | 327 |

| 16.5 | 5.1  | MSC Reset                                                            | 327 |

| 16.5 | 5.2  | MSC Card Reset                                                       | 327 |

| 16.5 | 5.3  | Voltage Validation                                                   | 327 |

| 16.5 | 5.4  | Card Registry                                                        | 328 |

| 16.5 | 5.5  | Card Access                                                          | 329 |

| 16.5 | 5.6  | Protection Management                                                | 330 |

| 16.5 | 5.7  | Card Status                                                          | 334 |

| 16.5 | 5.8  | SD Status                                                            | 337 |

| 16.5 | 5.9  | SDIO                                                                 | 338 |

| 16.5 | 5.10 | Clock Control                                                        | 339 |

| 16.5 | 5.11 | Application Specified Command Handling                               | 339 |

| 16.6 | MM   | C/SD Controller Operation                                            | 341 |

| 16.6 | 6.1  | Data FIFOs                                                           | 341 |

| 16.6 | 6.2  | DMA and Program I/O                                                  | 342 |

| 16.6 | 6.3  | Start and Stop clock                                                 | 342 |

| 16.6 | 6.4  | Software Reset                                                       | 343 |

| 16.6 | 6.5  | Voltage Validation and Card Registry                                 | 343 |

| 16.6 | 6.6  | Single Data Block Write                                              | 345 |

| 16.6 | 6.7  | Single Block Read                                                    | 346 |

| 16.6 | 8.8  | Multiple Block Write                                                 | 346 |

| 16.6 | 6.9  | Multiple Block Read                                                  | 347 |

| 16.6 | 3.10 | Stream Write (MMC)                                                   | 348 |

| 16.6 | 3.11 | Stream Read (MMC)                                                    | 348 |

| 16.6 | 12   | Frase Select/Deselect and Ston                                       | 349 |

| 16.6.13                | SDIO Suspend/Resume                                  | 349 |

|------------------------|------------------------------------------------------|-----|

| 16.6.14                | SDIO ReadWait                                        | 350 |

| 16.6.15                | Operation and Interrupt                              | 350 |

| 17 I2C B               | us Interface                                         | 352 |

| 17.1 Ove               | erview                                               | 352 |

| 17.2 Pin               | Description                                          | 353 |

| 17.3 Reg               | gister Description                                   | 354 |

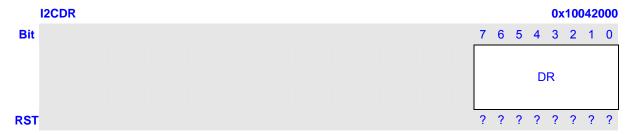

| 17.3.1                 | Data Register (I2CDR)                                |     |

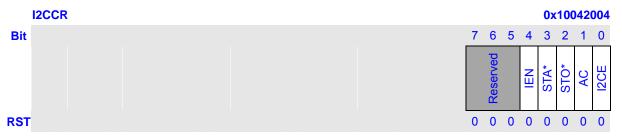

| 17.3.2                 | Control Register (I2CCCR)                            | 354 |

| 17.3.3                 | Status Register (I2CSR)                              |     |

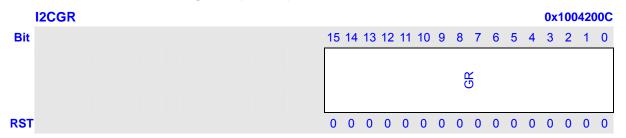

| 17.3.4                 | Clock Generator Register (I2CGR)                     | 355 |

| 17.4 I <sup>2</sup> C- | -Bus Protocol                                        | 356 |

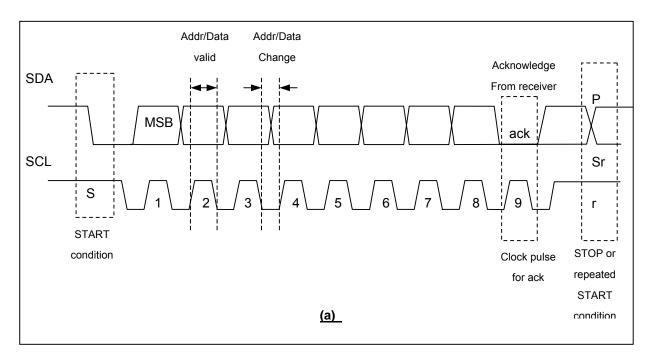

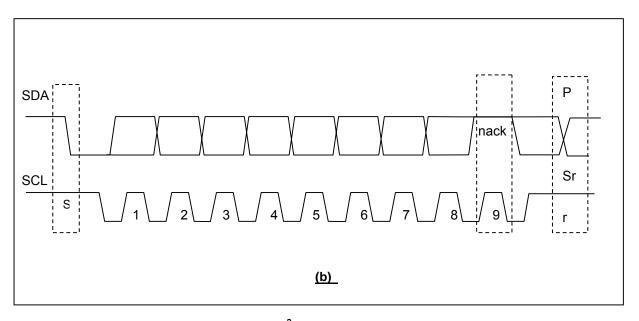

| 17.4.1                 | Bit Transfer                                         | 356 |

| 17.4.2                 | Data Validity                                        | 356 |

| 17.4.3                 | START and STOP Conditions                            | 356 |

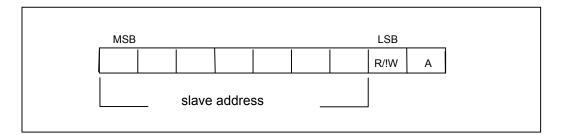

| 17.4.4                 | Byte Format                                          | 356 |

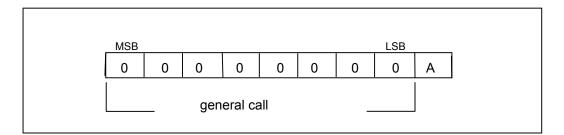

| 17.4.5                 | Data Transfer Format                                 | 358 |

| 17.5 I2C               | Operation                                            | 362 |

| 17.5.1                 | I2C Initialization                                   | 362 |

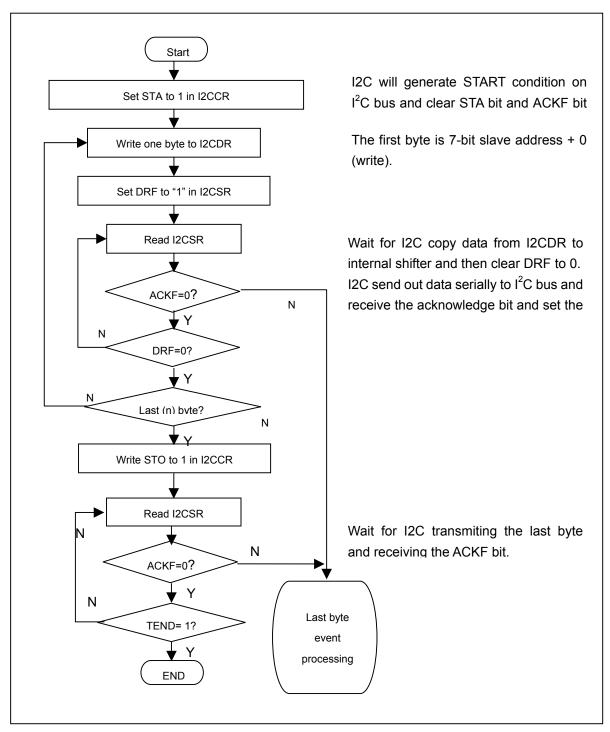

| 17.5.2                 | Write Operation                                      | 363 |

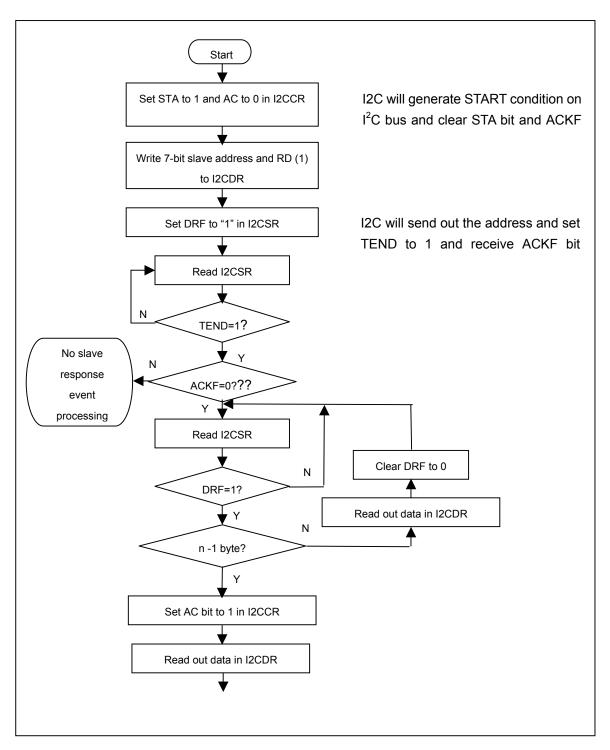

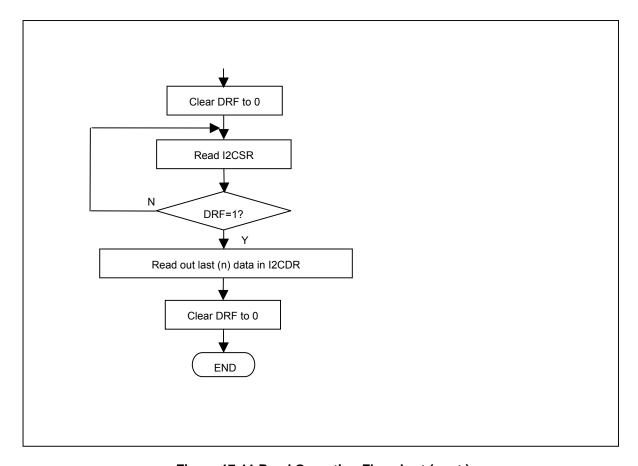

| 17.5.3                 | Read Operation                                       | 364 |

| 12 I I A D T           | Interface                                            | 366 |

| IO OAITI               | interrace                                            | 500 |

|                        | erview                                               |     |

| 18.2 Pin               | Description                                          | 367 |

| 18.3 Re                | gister Description                                   |     |

| 18.3.1                 | UART Receive Buffer Register (URBR)                  |     |

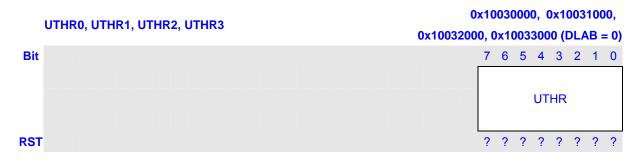

| 18.3.2                 | UART Transmit Hold Register (UTHR)                   | 369 |

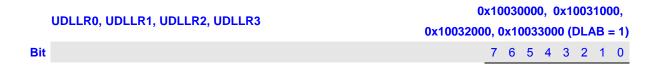

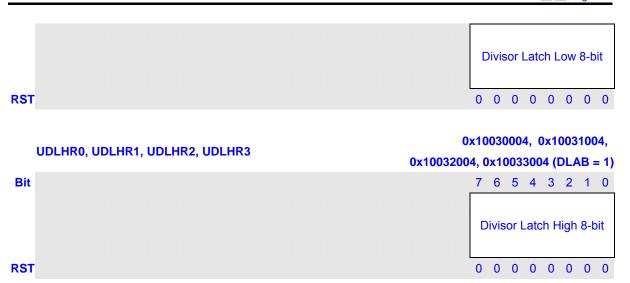

| 18.3.3                 | UART Divisor Latch Low/High Register (UDLLR / UDLHR) | 369 |

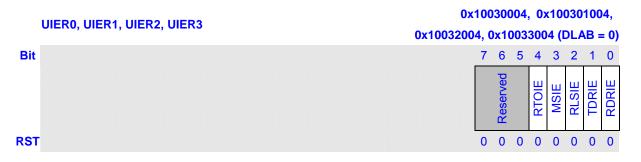

| 18.3.4                 | UART Interrupt Enable Register (UIER)                | 370 |

| 18.3.5                 | UART Interrupt Identification Register (UIIR)        |     |

| 18.3.6                 | UART FIFO Control Register (UFCR)                    | 372 |

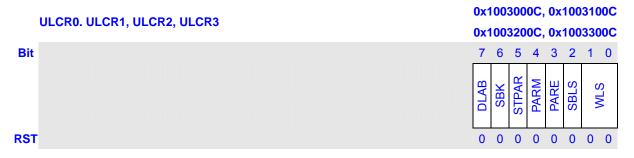

| 18.3.7                 | UART Line Control Register (ULCR)                    | 373 |

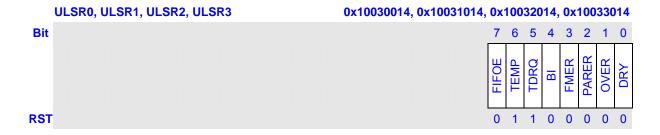

| 18.3.8                 | UART Line Status Register (ULSR)                     | 374 |

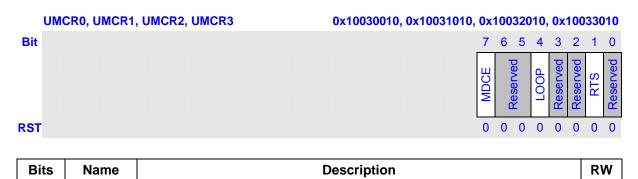

| 18.3.9                 | UART Modem Control Register (UMCR)                   | 376 |

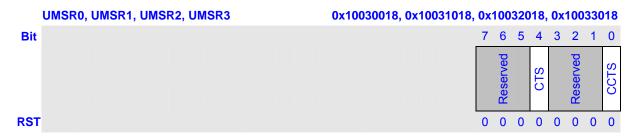

| 18.3.10                | UART Modem Status Register (UMSR)                    | 377 |

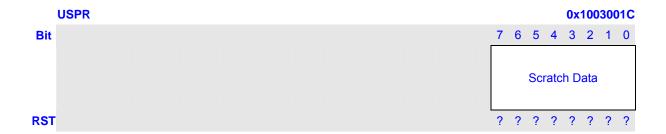

| 18.3.11                | UART Scratchpad Register                             | 378 |

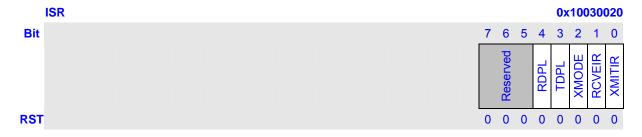

| 18.3.12                | Infrared Selection Register (ISR)                    | 378 |

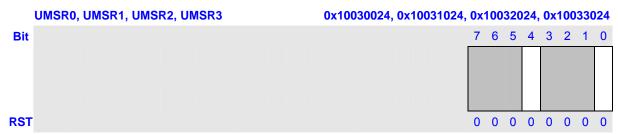

| 18.3.13                | Uart M Register (UMR)                                | 379 |

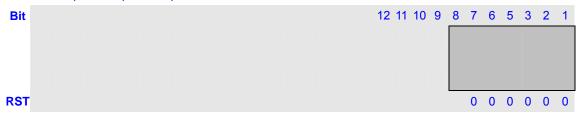

| 18.3.14                | Uart Add Cycle Register(UACR)                        |     |

| 18.4 Op                | eration                                              | 380 |

| 18 4 1                 | LIART Configuration                                  | 380 |

| 18.4   | 4.2 Data Transmission                                      | 380         |

|--------|------------------------------------------------------------|-------------|

| 18.4   | 4.3 Data Reception                                         | 381         |

| 18.4   | 4.4 Receive Error Handling                                 | 381         |

| 18.4   | 4.5 Modem Transfer                                         | 382         |

| 18.4   | 4.6 DMA Transfer                                           | 382         |

| 18.4   | 4.7 Slow IrDA Asynchronous Interface                       | 382         |

| 18.4   | 4.8 For any frequency clock to use the Uart                | 383         |

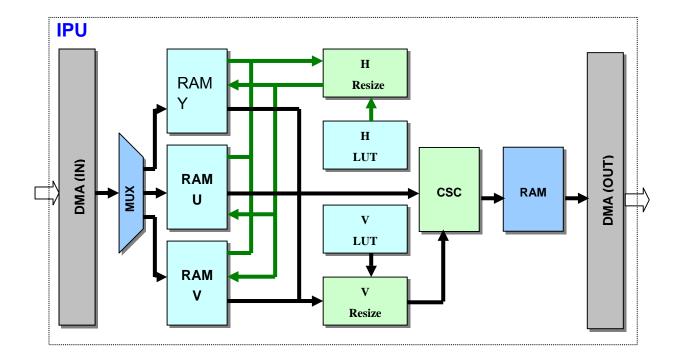

| 19 lma | age Process Unit                                           | 385         |

| 19.1   | Overview                                                   | 385         |

| 19.2   | Features                                                   | 385         |

| 19.3   | Block Diagram                                              | 385         |

| 19.4   | Data flow                                                  | 386         |

| 19.4   | 4.1 Input Data                                             | 386         |

| 19.4   | 4.2 Output Data                                            | 386         |

| 19.4   | 4.3 Resize Coefficients LUT                                | 386         |

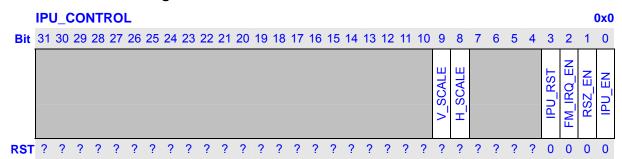

| 19.5   | Register definition                                        | 387         |

| 19.5   | 5.1 IPU Control Register                                   | 387         |

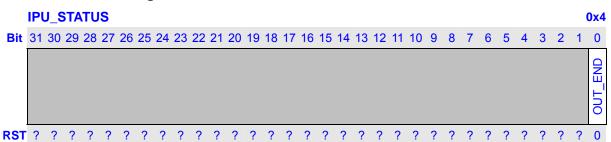

| 19.5   | 5.2 IPU Status Register                                    | 387         |

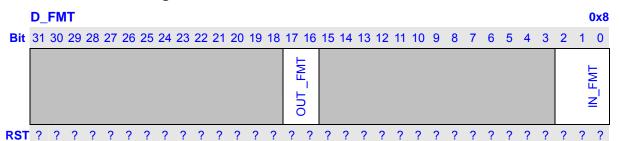

| 19.5   | 5.3 Data Format Register                                   | 388         |

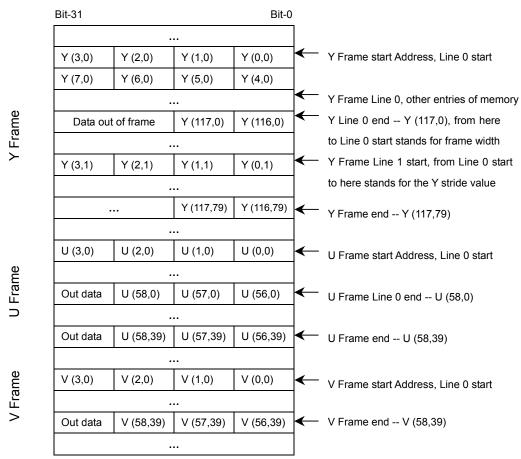

| 19.5   | 5.4 Input Y Data Address Register                          | 388         |

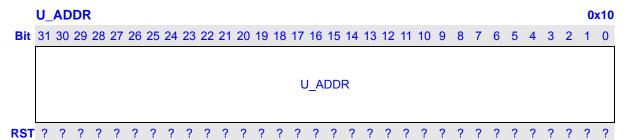

| 19.5   | 5.5 Input U Data Address Register                          | 389         |

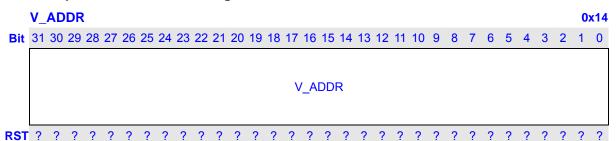

| 19.5   | 5.6 Input V Data Address Register                          | 389         |

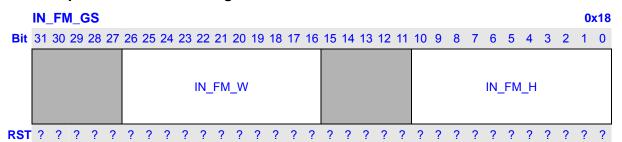

| 19.5   | 5.7 Input Geometric Size Register                          | 389         |

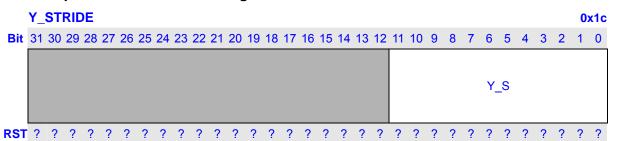

| 19.5   | 5.8 Input Y Data Line Stride Register                      | 390         |

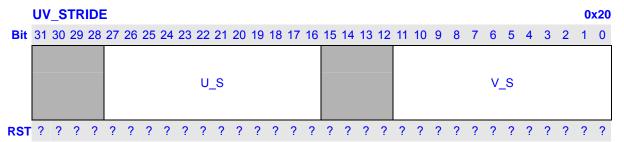

| 19.5   | 5.9 Input UV Data Line Stride Register                     | 390         |

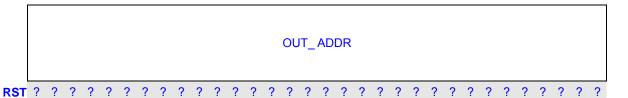

| 19.5   | 5.10 Output Frame Start Address Register                   | 390         |

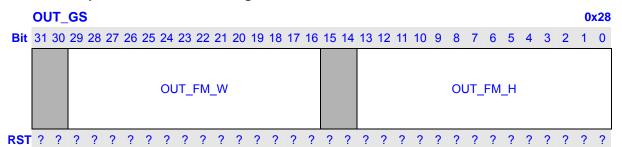

| 19.5   | 5.11 Output Geometric Size Register                        | 391         |

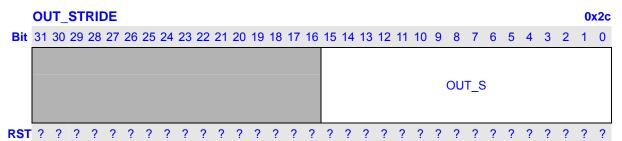

| 19.5   | 5.12 Output Data Line Stride Register                      | 391         |

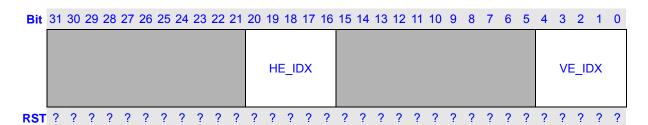

| 19.5   | 5.13 Resize Coefficients Table Index Register              | 391         |

| 19.5   | 5.14 CSC C0 Coefficient Register                           | 392         |

| 19.5   | 5.15 CSC C1 Coefficient Register                           | 392         |

| 19.5   | 5.16 CSC C2 Coefficient Register                           | 393         |

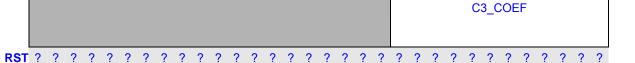

| 19.5   | 5.17 CSC C3 Coefficient Register                           | 393         |

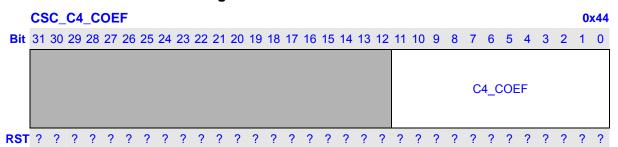

| 19.5   | 5.18 CSC C4 Coefficient Register                           | 395         |

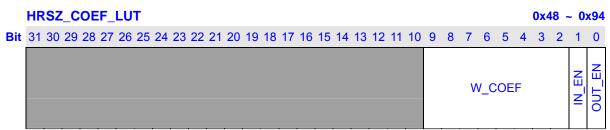

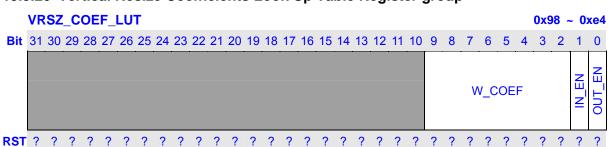

| 19.5   | 5.19 Horizontal Resize Coefficients Look Up Table Registe  | er group395 |

| 19.5   | 5.20 Vertical Resize Coefficients Look Up Table Register ( | group 397   |

| 19.6   | Calculation for Resized width and height                   | 398         |

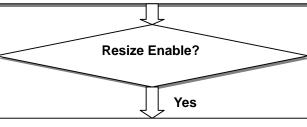

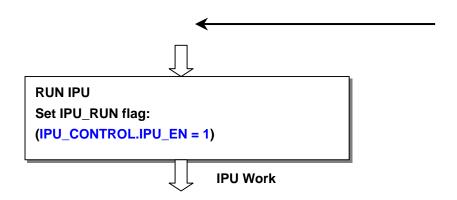

| 19.7   | IPU Initialization Flow                                    |             |

| 20 Jz4 | 4725 Boot ROM Specification                                | 405         |

| 20.1   | Boot Select                                                | 405         |

| 20.2   | Poot Coguence                                              |             |

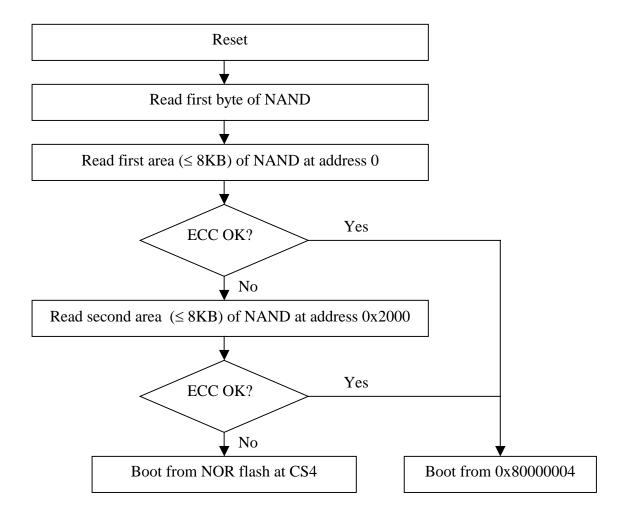

| 20.3 | NAND Boot Specification | .405 |

|------|-------------------------|------|

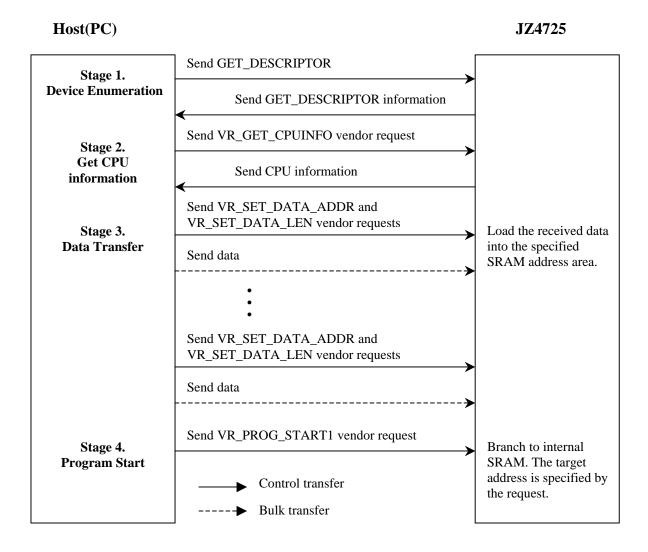

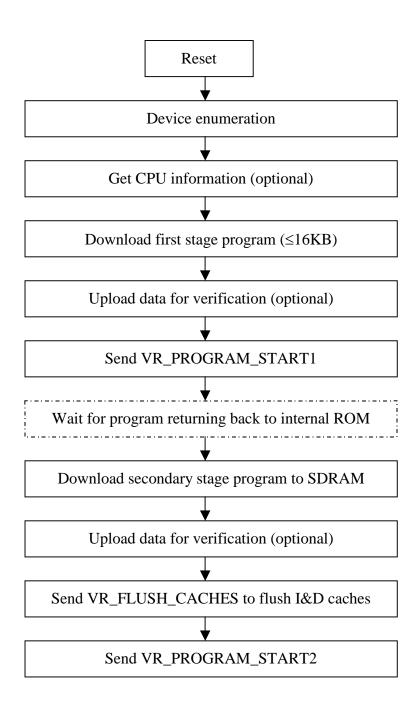

| 20.4 | USB Boot Specification  | .407 |

xii www.DataSheet4U.com

# **TABLES**

| Table 2-1 JzRISC Core Features                                                                                                                                                                                                                                                                                                                           | 7                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Table 3-1 EMC Pin Description                                                                                                                                                                                                                                                                                                                            | 10                                                                            |

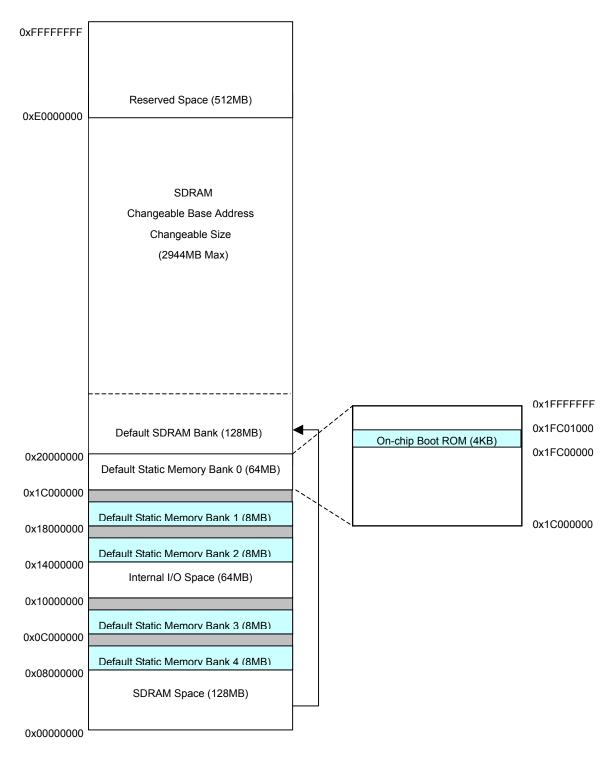

| Table 3-2 Physical Address Space Map                                                                                                                                                                                                                                                                                                                     | 12                                                                            |

| TABLE 3-3 DEFAULT CONFIGURATION OF EMC CHIP SELECT SIGNALS                                                                                                                                                                                                                                                                                               | 12                                                                            |

| Table 3-4 Static Memory Interface Registers                                                                                                                                                                                                                                                                                                              | 14                                                                            |

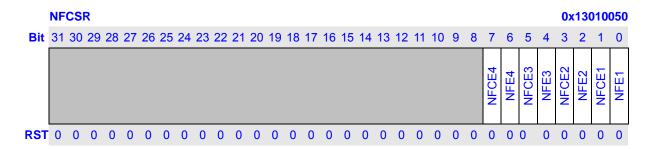

| Table 3-5 NAND Flash Interface Registers                                                                                                                                                                                                                                                                                                                 | 29                                                                            |

| Table 3-6 512-Byte ECC Parity Code Assignment Table For 8-bit NAND Flash                                                                                                                                                                                                                                                                                 | 38                                                                            |

| Table 3-7 256-Byte ECC Parity Code Assignment Table For 8-bit NAND Flash                                                                                                                                                                                                                                                                                 | 38                                                                            |

| Table 3-8 256-Halfword ECC Parity Code Assignment Table For 16-bit NAND Flash                                                                                                                                                                                                                                                                            | 38                                                                            |

| Table 3-9 SDRAM Registers                                                                                                                                                                                                                                                                                                                                | 42                                                                            |

| Table 3-10 SDRAM Address Multiplexing (32-bit data width) $st^4$                                                                                                                                                                                                                                                                                         | 54                                                                            |

| Table 3-11 SDRAM Address Multiplexing (16-bit data width) *4                                                                                                                                                                                                                                                                                             | 55                                                                            |

| Table 3-12 SDRAM Command Encoding (Notes: 1)                                                                                                                                                                                                                                                                                                             | 56                                                                            |

| Table 3-13 SDRAM Mode Register Setting Address Example (32-bit)                                                                                                                                                                                                                                                                                          | 76                                                                            |

| Table 3-14 SDRAM Mode Register Setting Address Example (16-bit)                                                                                                                                                                                                                                                                                          | 76                                                                            |

| Table 3-15 Boot Configuration                                                                                                                                                                                                                                                                                                                            | 80                                                                            |

| Table 4-1 DMAC Registers                                                                                                                                                                                                                                                                                                                                 | 83                                                                            |

| Table 4-2 Transfer Request Types                                                                                                                                                                                                                                                                                                                         | 85                                                                            |

| Table 4-3 Detection Interval Length                                                                                                                                                                                                                                                                                                                      | 88                                                                            |

| Table 4-4 Descriptor Structure                                                                                                                                                                                                                                                                                                                           | 92                                                                            |

| Table 4-5 Relationship among DMA Transfer connection, Request Mode and Transfer Mode                                                                                                                                                                                                                                                                     | 96                                                                            |

| Table 5-1 CGU Registers Configuration                                                                                                                                                                                                                                                                                                                    | . 102                                                                         |

| TABLE 5-2 TYPICAL CL AND THE CORRESPONDING MAXIMUM ESR                                                                                                                                                                                                                                                                                                   | . 112                                                                         |

| Table 5-3 Power/Reset Management Controller Registers Configuration                                                                                                                                                                                                                                                                                      | . 114                                                                         |

| Table 6-1 Registers for real time clock                                                                                                                                                                                                                                                                                                                  | . 123                                                                         |

| Table 6-2 Registers for hibernating mode                                                                                                                                                                                                                                                                                                                 | . 123                                                                         |

| Table 7-1 INTC Register                                                                                                                                                                                                                                                                                                                                  | . 138                                                                         |

| Table 8-1 PWM Pins Description                                                                                                                                                                                                                                                                                                                           | 1.40                                                                          |

|                                                                                                                                                                                                                                                                                                                                                          | . 143                                                                         |

| Table 10-1 GPIO Port A summary                                                                                                                                                                                                                                                                                                                           |                                                                               |

| Table 10-1 GPIO Port A summary                                                                                                                                                                                                                                                                                                                           | . 167                                                                         |

|                                                                                                                                                                                                                                                                                                                                                          | . 167<br>. 172                                                                |

| Table 10-2 GPIO Registers                                                                                                                                                                                                                                                                                                                                | . 167<br>. 172<br>. 190                                                       |

| Table 10-2 GPIO Registers                                                                                                                                                                                                                                                                                                                                | . 167<br>. 172<br>. 190<br>. 194                                              |

| Table 10-2 GPIO Registers                                                                                                                                                                                                                                                                                                                                | . 167<br>. 172<br>. 190<br>. 194<br>. 220                                     |

| TABLE 10-2 GPIO REGISTERS  TABLE 11-1 LCD CONTROLLER PINS DESCRIPTION  TABLE 11-2 LCD CONTROLLER REGISTERS DESCRIPTION  TABLE 12-1 SLCD PINS DESCRIPTION                                                                                                                                                                                                 | . 167<br>. 172<br>. 190<br>. 194<br>. 220<br>. 234                            |

| TABLE 10-2 GPIO REGISTERS  TABLE 11-1 LCD CONTROLLER PINS DESCRIPTION  TABLE 11-2 LCD CONTROLLER REGISTERS DESCRIPTION  TABLE 12-1 SLCD PINS DESCRIPTION  TABLE 13-1 AIC PINS DESCRIPTION                                                                                                                                                                | . 167<br>. 172<br>. 190<br>. 194<br>. 220<br>. 234                            |

| TABLE 10-2 GPIO REGISTERS  TABLE 11-1 LCD CONTROLLER PINS DESCRIPTION  TABLE 11-2 LCD CONTROLLER REGISTERS DESCRIPTION  TABLE 12-1 SLCD PINS DESCRIPTION  TABLE 13-1 AIC PINS DESCRIPTION  TABLE 13-2 AIC REGISTERS DESCRIPTION                                                                                                                          | . 167<br>. 172<br>. 190<br>. 194<br>. 220<br>. 234<br>. 236                   |

| TABLE 10-2 GPIO REGISTERS  TABLE 11-1 LCD CONTROLLER PINS DESCRIPTION  TABLE 11-2 LCD CONTROLLER REGISTERS DESCRIPTION  TABLE 12-1 SLCD PINS DESCRIPTION  TABLE 13-1 AIC PINS DESCRIPTION  TABLE 13-2 AIC REGISTERS DESCRIPTION  TABLE 13-3 SAMPLE DATA BIT RELATE TO SDATA_IN/SDATA_OUT BIT                                                             | . 167<br>. 172<br>. 190<br>. 194<br>. 220<br>. 234<br>. 236<br>. 259          |

| TABLE 10-2 GPIO REGISTERS  TABLE 11-1 LCD CONTROLLER PINS DESCRIPTION.  TABLE 11-2 LCD CONTROLLER REGISTERS DESCRIPTION  TABLE 12-1 SLCD PINS DESCRIPTION.  TABLE 13-1 AIC PINS DESCRIPTION.  TABLE 13-2 AIC REGISTERS DESCRIPTION.  TABLE 13-3 SAMPLE DATA BIT RELATE TO SDATA_IN/SDATA_OUT BIT.  TABLE 13-4 COLD AC '97 CODEC RESET TIMING PARAMETERS. | . 167<br>. 172<br>. 190<br>. 194<br>. 220<br>. 234<br>. 236<br>. 259<br>. 262 |

# **TABLES**

| TABLE 13-8 APPROXIMATE COMMON MULTIPLE OF SYS_CLK FOR ALL SAMPLE RATES                   | 272 |

|------------------------------------------------------------------------------------------|-----|

| Table 13-9 CPM/AIC clock divider setting for various sampling rate if PLL = $270.64$ MHz | 272 |

| TABLE 13-10 PLL PARAMETERS AND AUDIO SAMPLE ERRORS FOR EXCLK=12MHz                       | 273 |

| ΓABLE 14-1 CODEC SIGNAL IO PIN DESCRIPTION                                               | 275 |

| TABLE 14-2 INTERNAL CODEC REGISTERS DESCRIPTION                                          | 277 |

| TABLE 14-3 CODEC SETTINGS IN VARIOUS APPLICATIONS                                        | 283 |

| ΓABLE 14-4 CHARGE VREF TO THE MIDDLE VOLTAGE VM                                          | 286 |

| ΓABLE 14-5 CHARGE HPOUT TO THE MIDDLE VOLTAGE VM                                         | 286 |

| TABLE 14-6 CHARGE VREF AND HPOUT TO THE MIDDLE VOLTAGE VM                                | 286 |

| ΓABLE 14-7 DISCHARGE HPOUT TO 0V                                                         | 287 |

| Γable 14-8 Discharge VREF to 0V                                                          | 287 |

| ΓABLE 14-9 DISCHARGE VREF AND HPOUT TO 0V                                                | 287 |

| TABLE 15-1 SADC PINS DESCRIPTION                                                         | 294 |

| TABLE 16-1 MMC/SD CONTROLLER SIGNAL DESCRIPTION                                          | 314 |

| Γable 16-2 Command Token Format                                                          | 314 |

| Гавle 16-3 MMC/SD Data Token Format                                                      | 315 |

| TABLE 16-4 MMC/SD CONTROLLER REGISTERS DESCRIPTION                                       | 316 |

| Гавle 16-5 Command Data Block Structure                                                  | 331 |

| ΓABLE 16-6 CARD STATUS DESCRIPTION                                                       | 334 |

| Γable 16-7 SD Status Structure                                                           | 337 |

| ΓABLE 16-8 HOW TO STOP MULTIPLE BLOCK WRITE                                              | 346 |

| ΓABLE 16-9 HOW TO STOP MULTIPLE BLOCK READ                                               | 347 |

| ΓABLE 16-10 THE MAPPING BETWEEN COMMANDS AND STEPS                                       | 350 |

| TABLE 17-1 SMART CARD CONTROLLER PINS DESCRIPTION                                        | 353 |

| ΓABLE 17-2 I2C REGISTERS DESCRIPTION                                                     | 354 |

| ΓABLE 18-1 UART PINS DESCRIPTION                                                         | 367 |

| ΓABLE 18-2 UART REGISTERS DESCRIPTION                                                    | 367 |

| ΓABLE 18-3 UART INTERRUPT IDENTIFICATION REGISTER DESCRIPTION                            | 372 |

| Γable 20-1 Boot Configuration of Jz4725                                                  | 405 |

| ΓABLE 20-2 NAND FIRST DATA BYTE DEFINITION                                               | 406 |

| Γable 20-3 NAND Spare Area Definition                                                    | 406 |

| ΓABLE 20-4 JZ4725 NAND BOOT SEQUENCE                                                     | 407 |

| ΓABLE 20-5 TRANSFER TYPES USED BY THE BOOT PROGRAM                                       | 408 |

| ΓABLE 20-6 VENDOR REQUEST 0 SETUP COMMAND DATA STRUCTURE                                 | 410 |

| ΓABLE 20-7 VENDOR REQUEST 1 SETUP COMMAND DATA STRUCTURE                                 | 411 |

| ΓABLE 20-8 VENDOR REQUEST 2 SETUP COMMAND DATA STRUCTURE                                 | 411 |

| ΓABLE 20-9 VENDOR REQUEST 3 SETUP COMMAND DATA STRUCTURE                                 | 411 |

| ΓABLE 20-10 VENDOR REQUEST 4 SETUP COMMAND DATA STRUCTURE                                | 412 |

| Carle 20-11 Vendor Reguest 5 Setud Command Data Structure                                | 412 |

# **FIGURES**

| Figure 1-1 Jz4725 Diagram                                                          | 2  |

|------------------------------------------------------------------------------------|----|

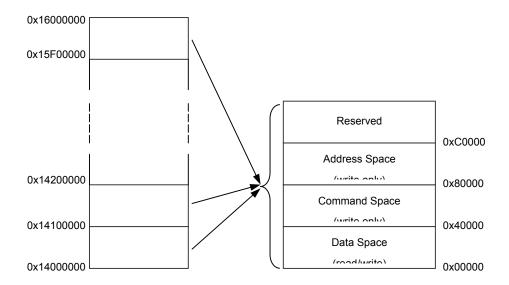

| FIGURE 3-1 PHYSICAL ADDRESS SPACE MAP                                              | 11 |

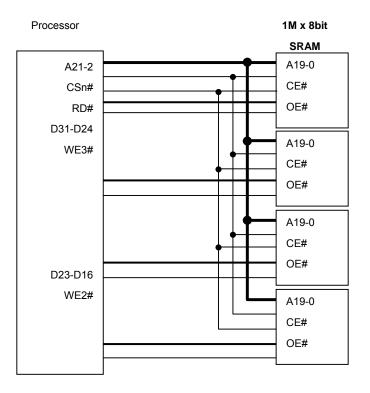

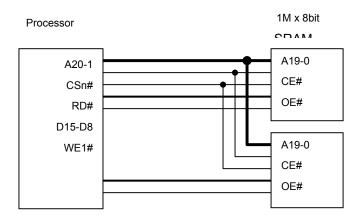

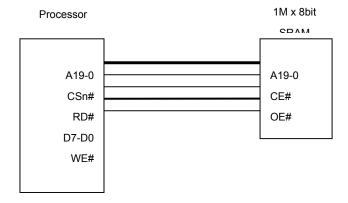

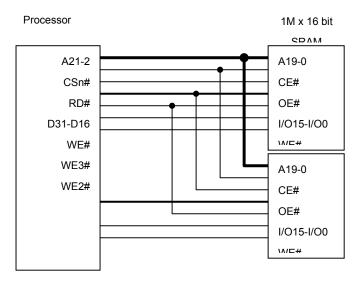

| FIGURE 3-2 EXAMPLE OF 32-BIT DATA WIDTH SRAM CONNECTION                            | 19 |

| FIGURE 3-3 EXAMPLE OF 16-BIT DATA WIDTH SRAM CONNECTION                            | 20 |

| FIGURE 3-4 EXAMPLE OF 8-BIT DATA WIDTH SRAM CONNECTION                             | 20 |

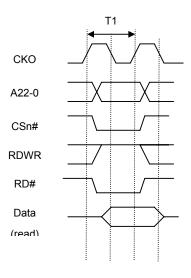

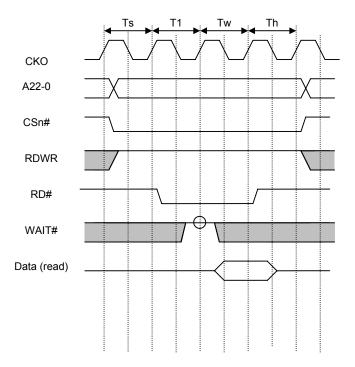

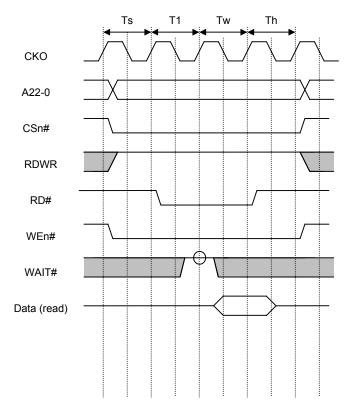

| FIGURE 3-5 BASIC TIMING OF NORMAL MEMORY READ                                      | 22 |

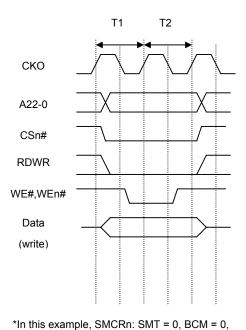

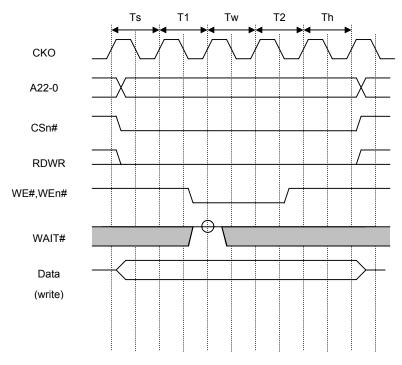

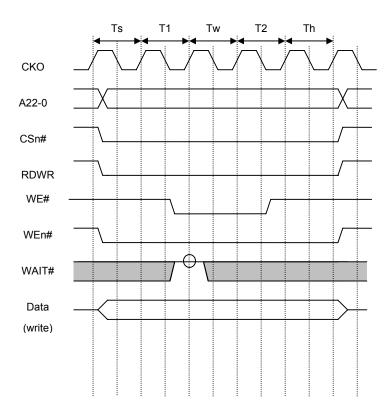

| FIGURE 3-6 BASIC TIMING OF NORMAL MEMORY WRITE                                     | 22 |

| FIGURE 3-7 NORMAL MEMORY READ TIMING WITH WAIT (SOFTWARE WAIT ONLY)                | 23 |

| FIGURE 3-8 NORMAL MEMORY WRITE TIMING WITH WAIT (SOFTWARE WAIT ONLY)               | 23 |

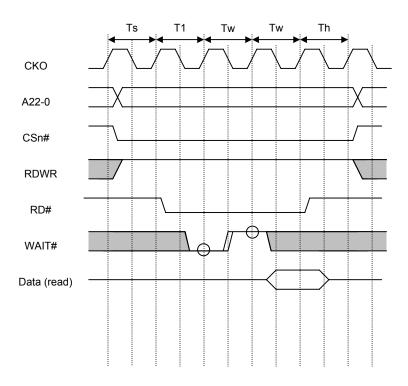

| FIGURE 3-9 NORMAL MEMORY READ TIMING WITH WAIT (WAIT CYCLE INSERTION BY WAIT# PIN) | 24 |

| FIGURE 3-10 EXAMPLE OF 32-BIT DATA WIDTH BYTE CONTROL SRAM CONNECTION              | 25 |

| FIGURE 3-11 BYTE CONTROL SRAM READ TIMING                                          | 26 |

| FIGURE 3-12 BYTE CONTROL SRAM WRITE TIMING                                         | 27 |

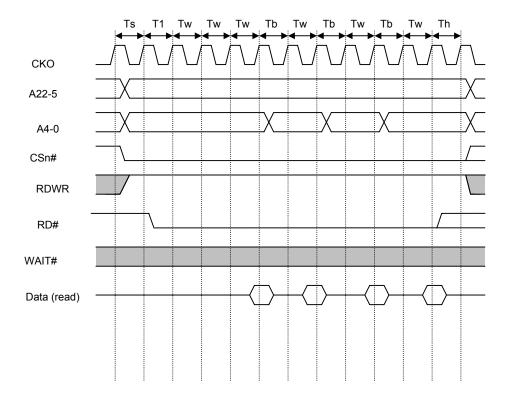

| FIGURE 3-13 BURST ROM READ TIMING (SOFTWARE WAIT ONLY)                             | 28 |

| FIGURE 3-14 STRUCTURE OF NAND FLASH BOOT LOADER                                    | 36 |

| FIGURE 3-15 STATIC BANK 2 PARTITION WHEN NAND FLASH IS USED (AN EXAMPLE)           | 37 |

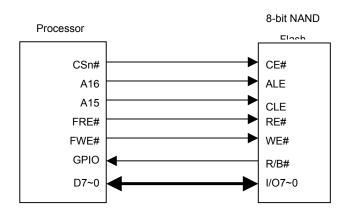

| FIGURE 3-16 EXAMPLE OF 8-BIT NAND FLASH CONNECTION                                 | 38 |

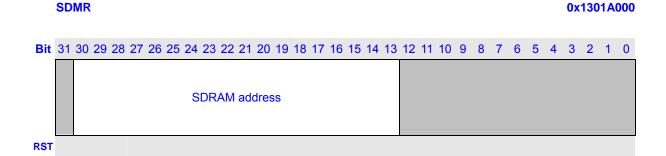

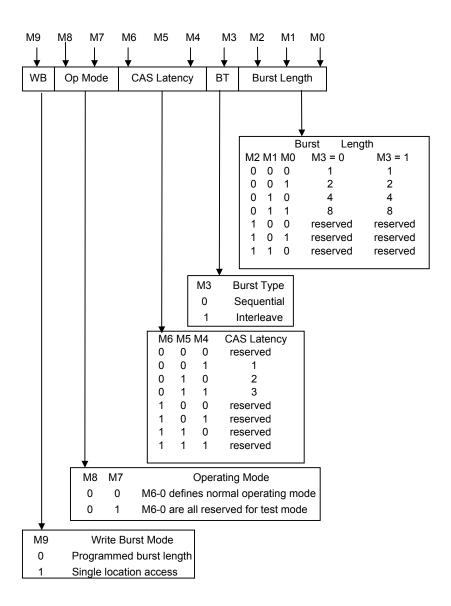

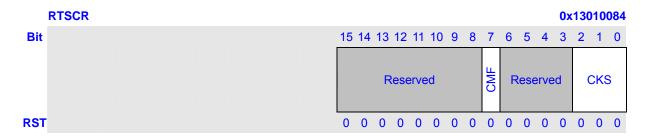

| FIGURE 3-17 SYNCHRONOUS DRAM MODE REGISTER CONFIGURATION                           | 47 |

| FIGURE 3-18 EXAMPLE OF SYNCHRONOUS DRAM CHIP CONNECTION (1)                        | 51 |

| FIGURE 3-19 EXAMPLE OF SYNCHRONOUS DRAM CHIP CONNECTION (2)                        | 52 |

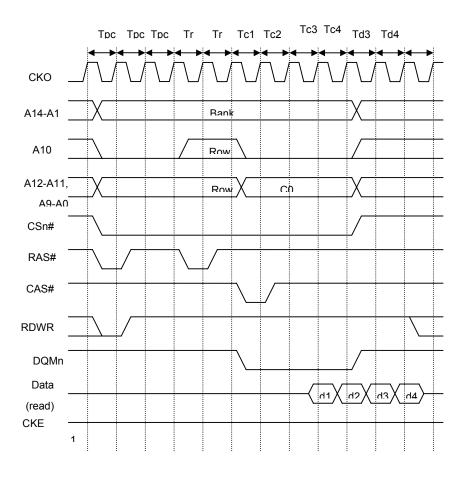

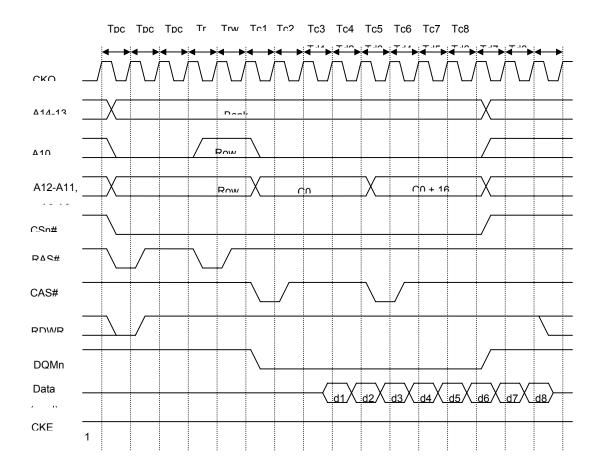

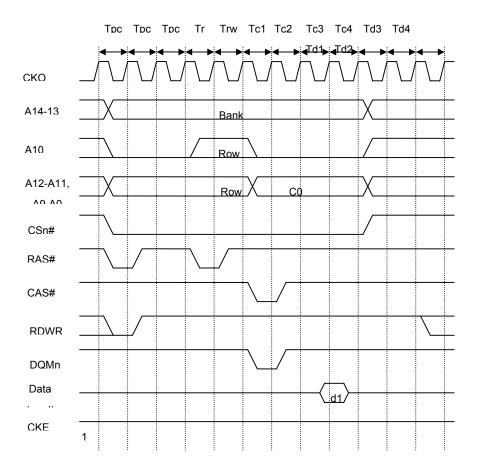

| FIGURE 3-20 SYNCHRONOUS DRAM 4-BEAT BURST READ TIMING (DIFFERENT ROW)              | 59 |

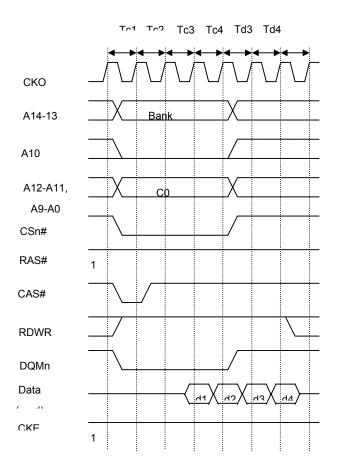

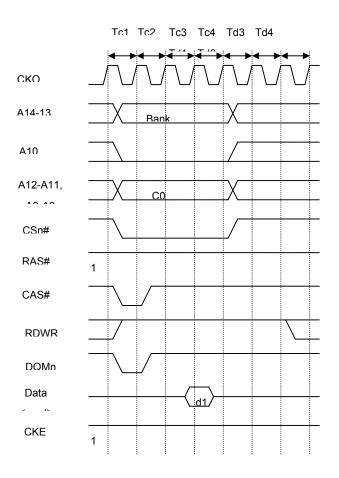

| FIGURE 3-21 SYNCHRONOUS DRAM 4-BEAT BURST READ TIMING (SAME ROW)                   | 60 |

| FIGURE 3-22 SYNCHRONOUS DRAM 4-BEAT BURST WRITE TIMING (DIFFERENT ROW)             | 61 |

| FIGURE 3-23 SYNCHRONOUS DRAM 4-BEAT BURST WRITE TIMING (SAME ROW)                  | 62 |

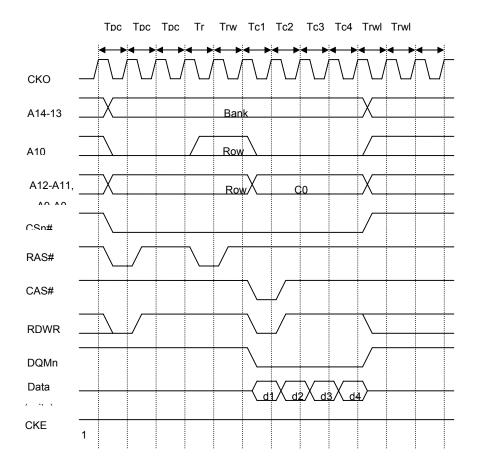

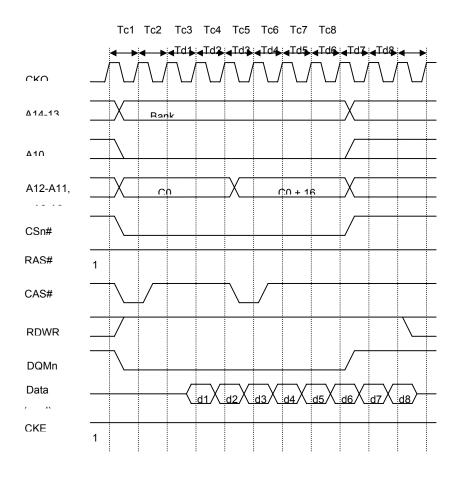

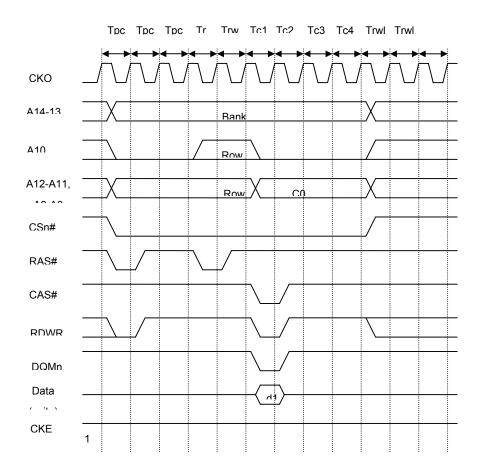

| FIGURE 3-24 SYNCHRONOUS DRAM 8-BEAT BURST READ TIMING (DIFFERENT ROW)              | 63 |

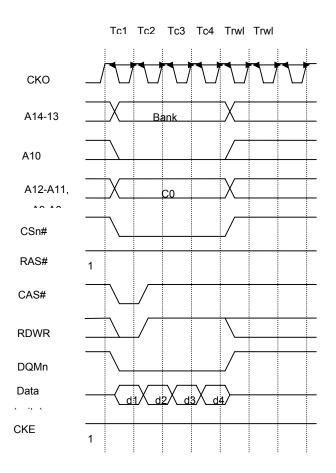

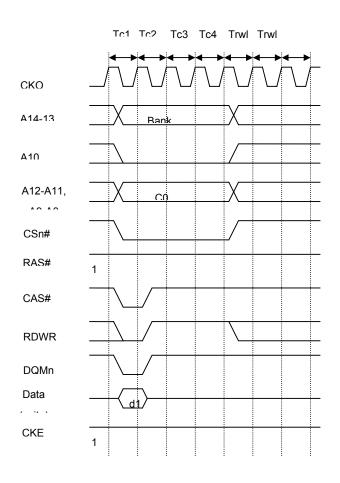

| FIGURE 3-25 SYNCHRONOUS DRAM 8-BEAT BURST READ TIMING (SAME ROW)                   | 64 |

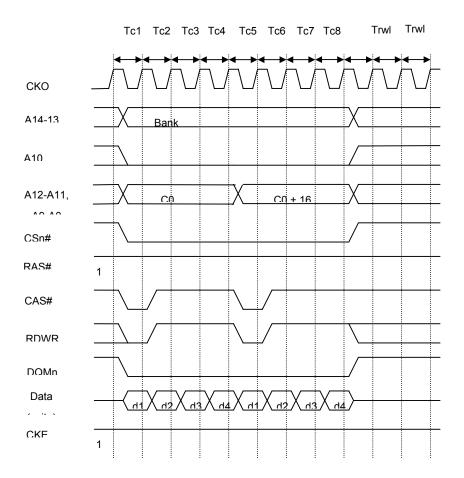

| FIGURE 3-26 SYNCHRONOUS DRAM 8-BEAT BURST WRITE TIMING (SAME ROW)                  | 65 |

| FIGURE 3-27 SYNCHRONOUS DRAM 8-BEAT BURST WRITE TIMING (DIFFERENT ROW)             | 66 |

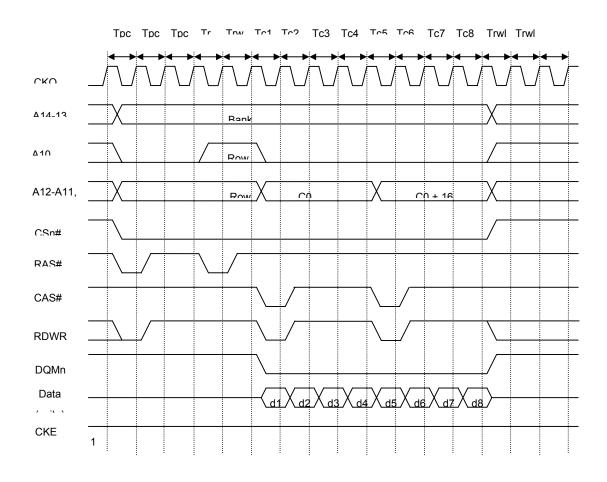

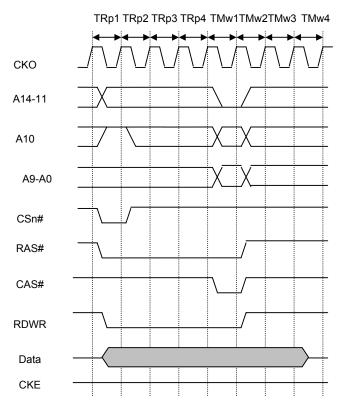

| FIGURE 3-28 SYNCHRONOUS DRAM SINGLE READ TIMING (DIFFERENT ROW)                    | 67 |

| FIGURE 3-29 SYNCHRONOUS DRAM SINGLE READ TIMING (SAME ROW)                         | 68 |

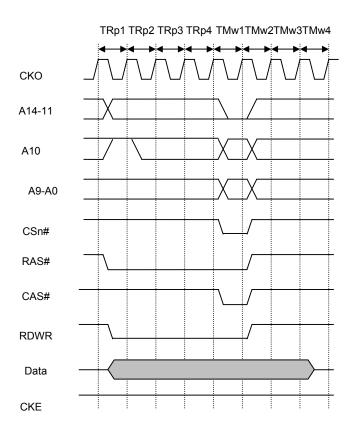

| FIGURE 3-30 SYNCHRONOUS DRAM SINGLE WRITE TIMING (DIFFERENT ROW)                   | 69 |

| FIGURE 3-31 SYNCHRONOUS DRAM SINGLE WRITE TIMING (SAME ROW)                        | 70 |

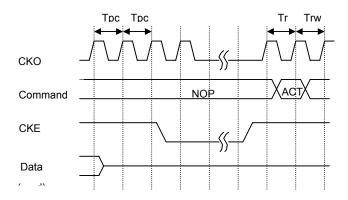

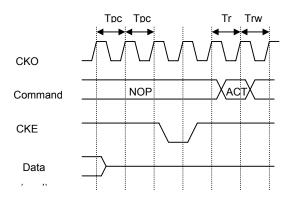

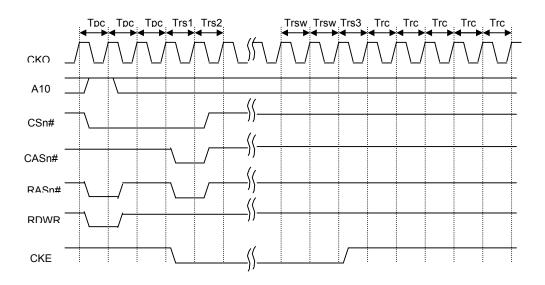

| FIGURE 3-32 SDRAM POWER-DOWN MODE TIMING (CKO STOPPED)                             | 71 |

| FIGURE 3-33 SDRAM POWER-DOWN MODE TIMING (CLOCK SUPPLIED)                          | 71 |

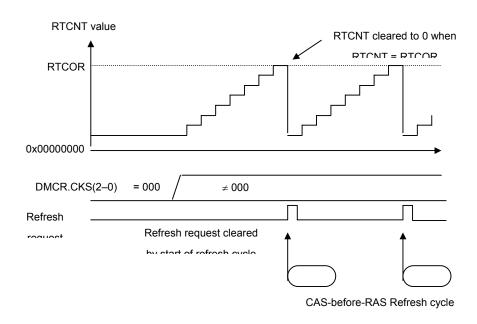

| FIGURE 3-34 SYNCHRONOUS DRAM AUTO-REFRESH OPERATION                                | 72 |

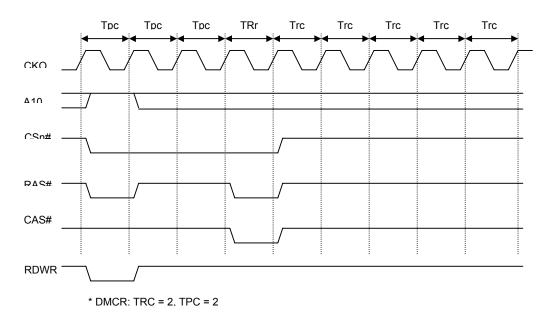

| FIGURE 3-35 SYNCHRONOUS DRAM AUTO-REFRESH TIMING                                   | 73 |

| FIGURE 3-36 SYNCHRONOUS DRAM SELF-REFRESH TIMING                                   | 75 |

| FIGURE 3-37 SDRAM MODE REGISTER WRITE TIMING 1 (PRE-CHARGE ALL BANKS)              | 78 |

| FIGURE 3-38 SDRAM MODE REGISTER WRITE TIMING 2 (MODE REGISTER SET)                 | 79 |

| FIGURE 4-1 DESCRIPTOR TRANSFER FLOW                                                | 93 |

# **FIGURES**

| FIGURE 5-1 CGU BLOCK DIAGRAM                                                            | 100 |

|-----------------------------------------------------------------------------------------|-----|

| FIGURE 5-2 BLOCK DIAGRAM OF PLL                                                         | 109 |

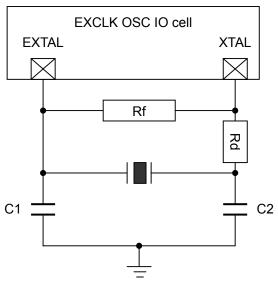

| FIGURE 5-3 OSCILLATING CIRCUIT FOR FUNDAMENTAL MODE                                     | 112 |

| Figure 11-1 Block Diagram                                                               | 191 |

| FIGURE 11-2 GENERAL 16-BIT AND 18-BIT TFT LCD TIMING                                    | 210 |

| FIGURE 11-3 SPECIAL TFT LCD TIMING 1                                                    | 212 |

| FIGURE 11-4 SPECIAL TFT LCD TIMING 2                                                    | 213 |

| FIGURE 13-1 AIC BLOCK DIAGRAM                                                           | 231 |

| FIGURE 13-2 INTERFACE TO THE INTERNAL I2S CODEC DIAGRAM                                 | 232 |

| FIGURE 13-3 INTERFACE TO AN EXTERNAL AC'97 CODEC DIAGRAM                                | 232 |

| FIGURE 13-4 INTERFACE TO AN EXTERNAL MASTER MODE I2S/MSB-JUSTIFIED CODEC DIAGRAM        | 232 |

| FIGURE 13-5 INTERFACE TO AN EXTERNAL SLAVE MODE I2S/MSB-JUSTIFIED CODEC DIAGRAM         | 233 |

| FIGURE 13-6 AC-LINK AUDIO FRAME FORMAT                                                  | 256 |

| FIGURE 13-7 AC-LINK TAG PHASE, SLOT 0 FORMAT                                            | 256 |

| FIGURE 13-8 AC-LINK DATA PHASES, SLOT 1 ~ SLOT 12 FORMAT                                | 256 |

| Figure 13-9 I2S data format                                                             | 257 |

| FIGURE 13-10 MSB-JUSTIFIED DATA FORMAT                                                  | 257 |

| FIGURE 13-11 COLD AC '97 CODEC RESET TIMING                                             | 262 |

| FIGURE 13-12 WARM AC '97 CODEC RESET TIMING                                             | 263 |

| FIGURE 13-13 TRANSMITTING/RECEIVING FIFO ACCESS VIA APB BUS                             | 267 |

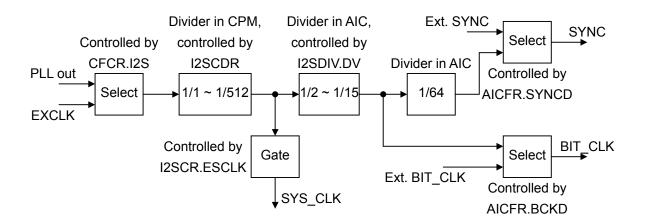

| FIGURE 13-14 SYS_CLK, BIT_CLK AND SYNC GENERATION SCHEME                                | 271 |

| FIGURE 14-1 CODEC BLOCK DIAGRAM                                                         | 276 |

| FIGURE 14-2 INTERNAL CODEC WORKS WITH AIC                                               | 276 |

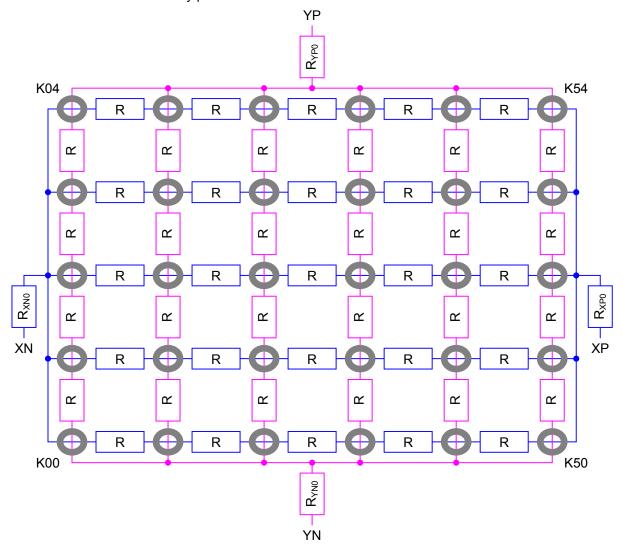

| Figure 15-1 6x5 keypad circuit                                                          | 308 |

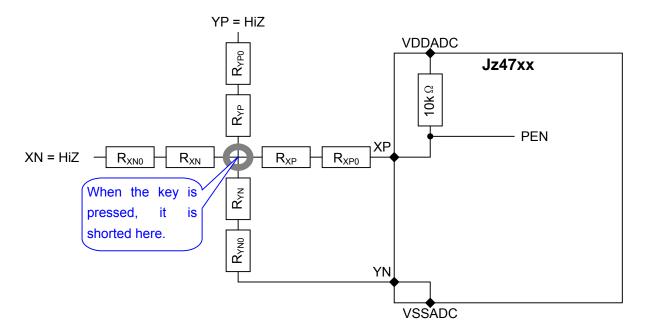

| Figure 15-2 Wait for Pen-down (C=1100) circuit                                          | 309 |

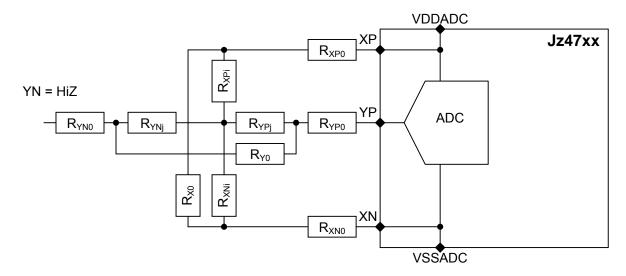

| FIGURE 15-3 MEASURE X-POSITION (C=0010) CIRCUIT                                         | 310 |

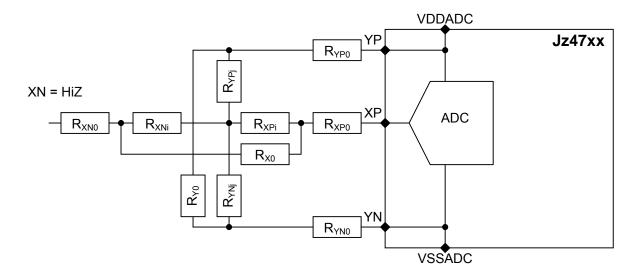

| FIGURE 15-4 MEASURE Y-POSITION (C=0011) CIRCUIT                                         | 310 |

| FIGURE 16-1 MMC/SD CONTROLLER BLOCK DIAGRAM                                             | 313 |

| FIGURE 17-1 I2C-BUS PROTOCOL                                                            | 357 |

| FIGURE 17-2 I <sup>2</sup> C-BUS PROTOCOL (CONT.)                                       | 357 |

| FIGURE 17-3 NORMAL 7 BIT ADDRESS AFTER START CONDITION                                  | 358 |

| FIGURE 17-4 GENERAL CALL ADDRESS AFTER START CONDITION                                  | 359 |

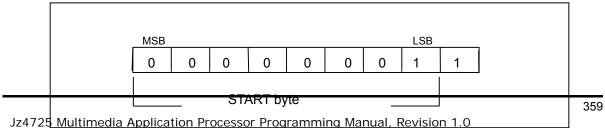

| FIGURE 17-5 START BYTE AFTER START CONDITION                                            | 360 |

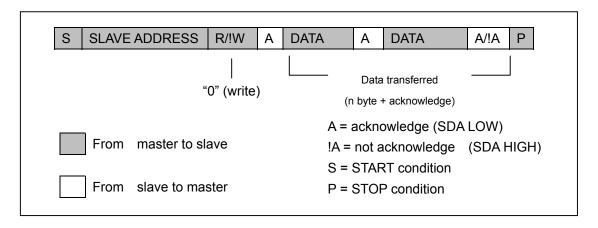

| FIGURE 17-6 A MASTER-TRANSMITTER ADDRESSES A SLAVE RECEIVER WITH A 7-BIT ADDRESS        | 361 |

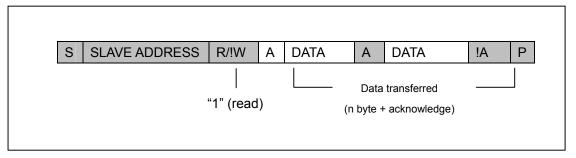

| FIGURE 17-7 A MASTER READS THE SLAVE IMMEDIATELY AFTER THE FIRST BYTE (MASTER-RECEIVER) | 361 |

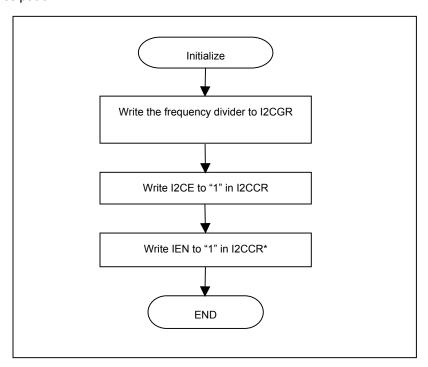

| Figure 17-8 I2C Initialization                                                          | 362 |

| FIGURE 17-9 I2C WRITE OPERATION FLOWCHART                                               | 363 |

| FIGURE 17-10 I2C READ OPERATION FLOWCHART                                               | 364 |

| FIGURE 17-11 READ OPERATION FLOWCHART (CONT.)                                           | 365 |

| FIGURE 20-1 USB COMMUNICATION FLOW                                                      | 408 |

| FIGURE 20-2 Typical Procedure of USR Root                                               | 410 |

# 1 Overview

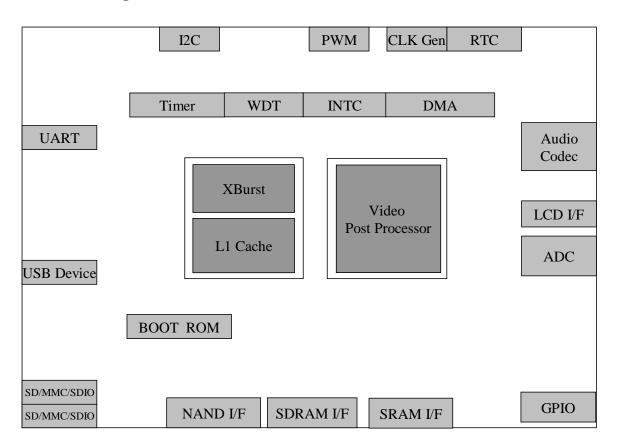

Jz4725 is a multimedia application processor targeting for PMP. Incorporate the XBurst<sup>®</sup> CPU core based on leading micro-architecture technology, this processor provides high integration, high performance and low power consumption solution for embedded device.

XBurst<sup>®</sup> is a high performance and power-efficient 32-bit RISC core with 16K instruction cache and 16K data cache, operating at speed up to 360MHz. The SIMD instruction set implemented by XBurst<sup>®</sup> core, in together with the on chip Image Processing Unit, provides strong decoding capability. The memory interface supports a variety of memory types that allow flexible design requirements, include the glueless connection to SLC/MLC NAND Flash for cost sensitive applications. On-chip modules such as LCD controller, audio CODEC, 2-channel SAR-ADC and AC97/I2S controller offer designers a rich suite of peripherals for multimedia application.

# 1.1 Block Diagram

Figure 1-1 Jz4725 Diagram

#### 1.2 Features

#### 1.2.1 CPU core

- XBurst<sup>®</sup> RISC instruction set to support Linux and WinCE

- XBurst<sup>®</sup> SIMD instruction set to support multimedia acceleration

- XBurst<sup>®</sup> 8-stage pipeline micro-architecture up to 360MHz

- 16K I-Cache, 16K D-Cache

- 32-entry dual-pages joint-TLB, 4 entry Instruction TLB and 4 entry data TLB

- Smart prefetch to accelerate multimedia applications

# 1.2.2 Multimedia support

- IPU (Image Processing Unit)

- Video frame resize

- Color space conversion: 420/444/422 YUV to RGB convert

#### 1.2.3 Memory sub-system

- NAND Flash interface

- Support MLC NAND as well as SLC NAND

- Support all 8-bit/16-bit NAND Flash devices regardless of density and organization

- Hamming and Reed-Solomon Hardware ECC for error detection and correction

- Support automatic boot up from NAND Flash devices

- Two chip select

- Synchronous DRAM Interface

- 1 banks with programmable size and base address

- 16-bit data bus width

- Multiplexes row/column addresses according to SDRAM capacity

- Two-bank or four-bank SDRAM is supported

- Supports auto-refresh and self-refresh functions

- Supports power-down mode to minimize the power consumption of SDRAM

- Supports page mode

- Direct Memory Access Controller

- Six independent DMA channels

- Descriptor supported

- Transfer data units: 8-bit, 16-bit, 32-bit, 16-byte or 32-byte

- Transfer requests can be: auto-request within DMA; and on-chip peripheral module request

- Interrupt on transfer completion or transfer error

- Supports two transfer modes: single mode or block mode

- The Jz4725 processor system supports little endian only

#### 1.2.4 Clock generation and power management

- On-chip oscillator circuit for an 32768Hz clock and an 12MHz clock

- On-chip phase-locked loops (PLL) with programmable multiple-ratio. Internal counter are used to ensure PLL stabilize time

- PLL on/off is programmable by software

- ICLK, PCLK, SCLK, MCLK and LCLK frequency can be changed separately for software by setting division ratio

- Supports six low-power modes and function: NORMAL mode; DOZE mode; IDLE mode;

SLEEP mode; HIBERNATE mode; and MODULE-STOP function.

#### 1.2.5 On-chip peripherals

- General-Purpose I/O ports

- Total GPIO pin number is 81

- Each pin can be configured as general-purpose input or output or multiplexed with internal chip functions

- Each pin can act as a interrupt source and has configurable rising/falling edge or high/low level detect manner, and can be masked independently

- Each pin can be configured as open-drain when output

- Each pin can be configured as internal resistor pull-up

- RTC (Real Time Clock)

- 32-bit second counter

- 1Hz from 32768hz

- Alarm interrupt

- Independent power

- A 32-bits scratch register used to indicate whether power down happens for RTC power

- Interrupt controller

- Total 28 maskable interrupt sources from on-chip peripherals and external request through GPIO ports

- Interrupt source and pending registers for software handling

- Unmasked interrupts can wake up the chip in sleep or standby mode

- Timer and counter unit with PWM output

- Provide five separate channels

- 16-bit A counter and 16-bit B counter with auto-reload function every channel

- Support interrupt generation when the A counter underflows

- Three clock sources: RTCLK (real time clock), EXCLK (external clock input), PCLK

(APB Bus clock) selected with 1, 4, 16, 64, 256 and 1024 clock dividing selected

- PWM output supported

- Watchdog timer

- 16-bit counter in RTC clock with 1, 4, 16, 64, 256 and 1024 clock dividing selected

#### Generate power-on reset

#### LCD controller

- Single-panel display in active mode, and single- or dual-panel displays in passive mode

- 2, 4, 16 grayscales and up to 4096 colors in STN mode

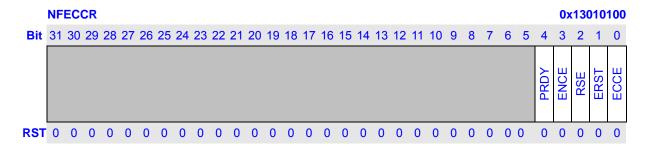

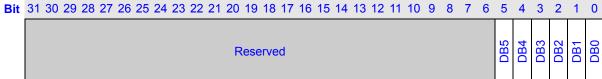

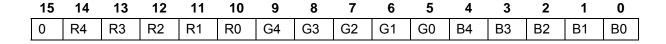

- 2, 4, 16, 256, 4K, 32K, 64K, 256K and 16M colors in TFT mode