# **JWH5084**

17V/12A

Sync. Step-Down Converter

Preliminary Specifications Subject to Change without Notice

#### DESCRIPTION

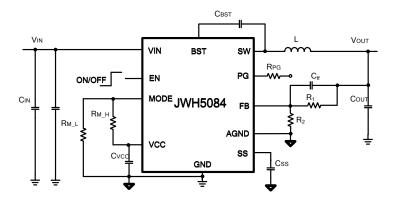

The JW®H5084 is a monolithic buck switching regulator based on I2 architecture for fast transient response. Operating with an input range of 4.5V~17V, JWH5084 delivers 12A of continuous output current with two integrated N-Channel MOSFETs. The internal synchronous power switches provide high efficiency without the use of an external Schottky diode. The operation frequency is set easily to 400 kHz, 800 kHz, or 1200 kHz with the MODE configuration, allowing the JWH5084 frequency to remain constant regardless of the input/output voltages. JWH5084 guarantees robustness with output short protection, over-voltage protection, thermal protection and under voltage protection.

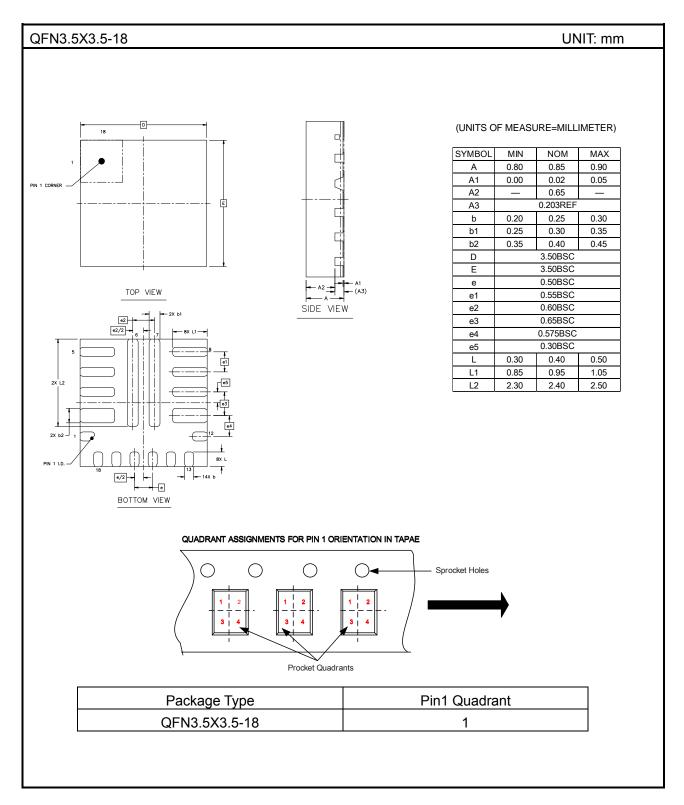

JWH5084 is available in QFN3.5 X 3.5-18 package, which provide a compact solution with minimal external components.

Company's Logo is Protected, "JW" and "JOULWATT" are Registered Trademarks of JoulWatt technology Inc.

#### **FEATURES**

- 4.5V to 17V operating input range

- 12A continuous

- Selectable accurate current limit level

- $\pm$ 1% reference voltage over -40°C to +125°C junction temperature range

- Selectable PFM or FCCM

- Power good indicator

- Programmable soft-start time

- Selectable switching frequency from 400kHz, 800kHz, and 1200kHz

- Output discharge function

- Non-latch OCP, UVP, OVP, UVLO, Thermal protection

- Available in QFN3.5X3.5-18 package

#### **APPLICATIONS**

- Telecom and Networking Systems

- Server, Cloud-Computing, Storage

- Base Stations

- General Purpose Point-of-Load

# TYPICAL APPLICATION

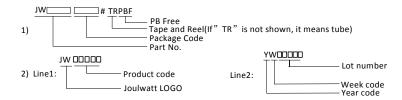

## **ORDER INFORMATION**

| DEVICE <sup>1)</sup>   | PACKAGE       | TOP MARKING <sup>2)</sup> |  |

|------------------------|---------------|---------------------------|--|

| NAU IFOO AO FNIZHTDDDF | OFN2 FV2 F 10 | JWH5084                   |  |

| JWH5084QFNZ#TRPBF      | QFN3.5X3.5-18 | YW□□□□                    |  |

#### Notes:

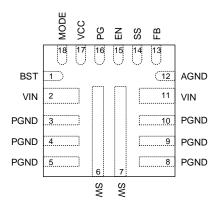

# **PIN CONFIGURATION**

#### **TOP VIEW**

# **ABSOLUTE MAXIMUM RATING**<sup>1)</sup>

| VIN Pin                                                   | 0.3V to 20V                                |

|-----------------------------------------------------------|--------------------------------------------|

| SW Pin                                                    | -0.3V (-5V for 25ns) to 20V (25V for 25ns) |

| EN Pin                                                    | 0.3V to 20V                                |

| BST Pin                                                   | SW-0.3V to SW+4V                           |

| VCC Pin                                                   | 0.3V to 4V                                 |

| PG Pin                                                    | 0.3V to 6V                                 |

| All other Pins                                            | 0.3V to 4V                                 |

| Junction Temperature 2)                                   | 150°C                                      |

| Lead Temperature                                          | 260°C                                      |

| ESD Susceptibility (Human Body Model)                     | ±2kV                                       |

| Charged device model (CDM), per JEDEC specification JESD2 | 22- V C101±500V                            |

# **RECOMMENDED OPERATING CONDITIONS<sup>3)</sup>**

| Input Voltage VIN                             | 4.5V to 17V                                                                                                                                                                          |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Voltage Vout                           |                                                                                                                                                                                      |

| Maximum Output Current I <sub>OUT_MAX</sub>   | 12A                                                                                                                                                                                  |

| Operation Junction Temperature T <sub>j</sub> | 40°C to 125°C                                                                                                                                                                        |

| THERMAL PERFORMANCE <sup>4)</sup>             | $	heta_{{\scriptscriptstyle J\!B}}{}^{{\scriptscriptstyle 5}{\scriptscriptstyle )}}$ $	heta_{{\scriptscriptstyle J\!C}\_{T\!O\!P}}{}^{{\scriptscriptstyle 5}{\scriptscriptstyle )}}$ |

| OEN3 5Y3 5-18                                 | 8 6 17 0°C \\\\                                                                                                                                                                      |

#### Note:

- 1) Exceeding these ratings may damage the device. These stress ratings do not imply function operation of the device at any other conditions beyond those indicated under RECOMMENDE OPERATING CONDITIONS.

- 2) The JWH5084 includes thermal protection that is intended to protect the device in overload conditions. Continuous operation over the specified absolute maximum operating junction temperature may damage the device.

- 3) The device is not guaranteed to function outside its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

- 5)  $\theta_{m}$  Thermal resistance from junction to board around PGND pin soldering point.

$\theta_{s_c,rop}$  Thermal resistance from junction to top of package.

# **ELECTRICAL CHARACTERISTICS**

| VIN=12V, $T_J$ =-40 $C$ ~125 $C$ , Unless otherwise stated. |                        |                                                |       |       |        |                  |

|-------------------------------------------------------------|------------------------|------------------------------------------------|-------|-------|--------|------------------|

| Item                                                        | Symbol                 | Conditions                                     | Min.  | Тур.  | Max.   | Unit             |

| V. Linder Voltage Leek out Threshold                        | V <sub>IN_HTH</sub>    | V <sub>IN</sub> rising, V <sub>CC</sub> =3.3V  | 2.1   | 2.4   | 2.7    | V                |

| V <sub>IN</sub> Under Voltage Lock-out Threshold            | V <sub>IN_LTH</sub>    | V <sub>IN</sub> falling, V <sub>CC</sub> =3.3V | 1.55  | 1.85  | 2.15   | V                |

| Shutdown Current                                            | Isd                    | V <sub>EN</sub> =0                             |       | 7     |        | μΑ               |

| Supply Current                                              | IQ                     | V <sub>EN</sub> =3.3V, V <sub>FB</sub> =0.7V   |       | 550   | 800    | μΑ               |

| Enable Input Rising Threshold                               | V <sub>EN_HTH</sub>    |                                                | 1.17  | 1.225 | 1.27   | V                |

| Enable Hysteresis                                           | V <sub>EN_TH_HYS</sub> |                                                |       | 0.121 |        | V                |

| I <sub>ENP1</sub>                                           | EN pull-up             | V <sub>EN</sub> =1.0V                          | 0.35  | 1.91  | 2.95   | μA               |

| I <sub>ENP2</sub>                                           | current                | V <sub>EN</sub> =1.3V                          | 3     | 4.197 | 5.5    | μA               |

| Feedback Voltage                                            | V <sub>REF</sub>       |                                                | 594   | 600   | 606    | mV               |

| Top Switch Resistance                                       | R <sub>DS(ON)T</sub>   |                                                |       | 13.3  | 21     | mΩ               |

| Bottom Switch Resistance                                    | R <sub>DS(ON)B</sub>   |                                                |       | 4.3   | 8.4    | mΩ               |

| Top Switch Leakage Current                                  | ILEAK_TOP              | V <sub>IN</sub> =17V, V <sub>SW</sub> =0V      |       |       | 10     | μA               |

| Bottom Switch Leakage Current                               | ILEAK_BOT              | V <sub>IN</sub> =17V, V <sub>SW</sub> =17V     |       |       | 10     | μΑ               |

| Valley current limit                                        | ILIM_POS1              |                                                | 9.775 | 11.5  | 13.225 | Α                |

| valiey current limit                                        | I <sub>LIM_POS2</sub>  |                                                | 11.73 | 13.8  | 15.87  | Α                |

| Bottom Switch Negative Current Limit                        | I <sub>LIM_NEG</sub>   |                                                |       | -4    |        | Α                |

| Minimum On Time <sup>6)</sup>                               | Ton_min                |                                                |       | 50    |        | ns               |

| Minimum Off Time                                            | T <sub>OFF_MIN</sub>   |                                                |       | 100   | 180    | ns               |

|                                                             | Fsw                    |                                                | 340   | 400   | 460    | kHz              |

| Switching Frequency 7)                                      |                        |                                                | 680   | 800   | 920    | kHz              |

|                                                             |                        |                                                | 1020  | 1200  | 1380   | kHz              |

| Discharge FET Ron                                           | R <sub>DIS</sub>       |                                                |       | 80    | 150    | Ω                |

| Soft-Start Charge Current                                   | Iss_char               | V <sub>SS</sub> =0V                            | 4.9   | 6     | 7.1    | μA               |

| Soft-Start Discharge FET Ron                                | Rss_dischar            | V <sub>CC</sub> =3V                            | 1     | 1.5   | 2      | kΩ               |

| Soft-Start Time <sup>6)</sup>                               | T <sub>SS</sub>        | Internal soft-start time                       |       | 1     |        | ms               |

| VCC Under-voltage Lockout                                   | V <sub>CC_НТН</sub>    | VCC rising                                     | 2.65  | 2.8   | 2.95   | V                |

| Threshold                                                   | Vcc_lth                | VCC falling                                    | 2.35  | 2.5   | 2.65   | V                |

| VCC Regulator                                               | Vcc                    |                                                | 3.28  | 3.38  | 3.48   | V                |

| VCC Load Regulation                                         |                        | I <sub>CC</sub> =25mA                          |       | 0.5   |        | %                |

| D 0 1111 T 111                                              | 50                     | FB from low to high                            | 90%   | 93%   | 96%    | V <sub>REF</sub> |

| Power Good High Threshold                                   | PG <sub>HTH</sub>      | FB from high to low                            | 104%  | 107%  | 110%   | $V_{REF}$        |

| Power Good Low Threshold                                    | PG <sub>LTH</sub>      | FB from low to high                            | 113%  | 116%  | 119%   | $V_{REF}$        |

| VIN=12V, $T_J$ =-40 $C$ ~125 $C$ , Unless otherwise stated. |                       |                         |      |      |      |           |

|-------------------------------------------------------------|-----------------------|-------------------------|------|------|------|-----------|

| ltem                                                        | Symbol                | Conditions              | Min. | Тур. | Max. | Unit      |

|                                                             |                       | FB from high to low     | 81%  | 84%  | 87%  | $V_{REF}$ |

| Power Good Delay Time                                       | PG_DLY                | PG from low to high     | 140  | 200  | 260  | us        |

| Power Good Sink Current                                     | l <sub>PG</sub>       | PG=0.5V                 | 10   |      |      | mA        |

| Output Over-voltage Threshold                               |                       | V <sub>FB</sub> Rising  | 118% | 121% | 124% | $V_{REF}$ |

| Output Under-voltage Threshold <sup>6)</sup>                |                       | V <sub>FB</sub> Falling | 65%  | 68%  | 71%  | $V_{REF}$ |

| Thermal Shutdown <sup>6)</sup> T <sub>TSD</sub>             |                       |                         |      | 160  |      | °C        |

| Thermal Shutdown Hysteresis <sup>6)</sup>                   | T <sub>TSD_HYST</sub> |                         |      | 15   |      | °C        |

| VCC Regulator Thermal Shutdown <sup>6)</sup>                |                       |                         |      | 171  |      | °C        |

| VCC Regulator Thermal Shutdown Hysteresis <sup>6)</sup>     |                       |                         |      | 18   |      | °C        |

#### Note:

- 6) Guaranteed by design.

- 7) Guaranteed by design over all temperature range

# **PIN DESCRIPTION**

| Pin          | Name                                                                                                                         | Description                                                                                                                                                                                                                 |

|--------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | BST                                                                                                                          | Connect a 0.1uF capacitor between BST and SW pin to supply current for the top switch driver.                                                                                                                               |

| 2,11         | VIN                                                                                                                          | Input voltage pin. VIN supplies power to the IC. Connect a 4.5V to 17V supply to VIN and bypass VIN to GND with a suitably large capacitor to eliminate noise on the input to the IC                                        |

| 3,4,5,8,9,10 | GND                                                                                                                          | Power ground pin                                                                                                                                                                                                            |

| 6,7          | SW                                                                                                                           | SW is the switching node that supplies power to the output. Connect the output LC filter from SW to the output load.                                                                                                        |

| 12           | AGND                                                                                                                         | Analog ground pin. Select AGND as the control circuit reference point.                                                                                                                                                      |

| 13           | FB                                                                                                                           | Feedback. An external resistor divider from the output to AGND (tapped to FB) sets the output voltage. It is recommended to place the resistor divider as close to FB as possible. Vias should be avoided on the FB traces. |

| 14           | SS                                                                                                                           | Soft-start time setting pin. The soft-start time is determined by the capacitance between SS pin and AGND.                                                                                                                  |

| 15           | EN                                                                                                                           | Enable control pin. Pull this pin high to turn on the regulator. Do not leave this pin floating.                                                                                                                            |

| 16           | PGOOD Power good monitor output. Open drain output when the output voltage is within 93% 116% of internal reference voltage. |                                                                                                                                                                                                                             |

| 17           | VCC                                                                                                                          | Internal LDO Output. Power supply for internal analog circuits and driving circuit.  Decouple this pin to ground with a minimum 1uF ceramic capacitor.                                                                      |

| 18           | MODE                                                                                                                         | Operation mode selection. Program MODE to select CCM, pulse skip mode, the operating switching frequency, and current limit selection.                                                                                      |

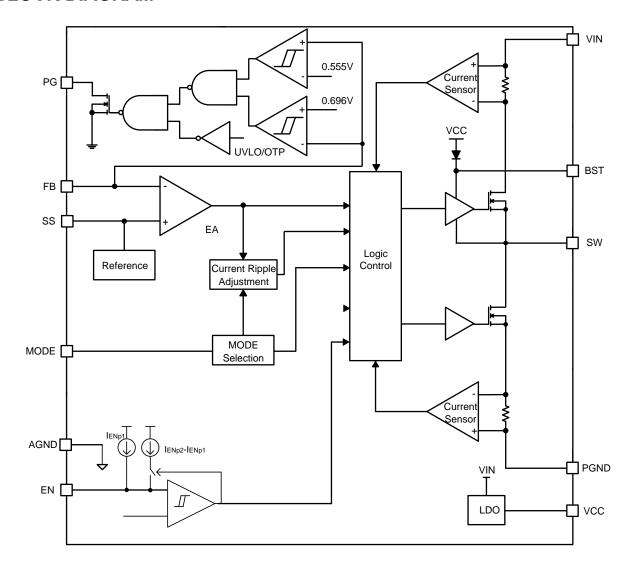

# **BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

JWH5084 is a synchronous step-down regulator based on I2 control architecture. It regulates input voltages from 4.5V to 17V down to as low as 0.6V output voltage, and is capable of supplying up to 12A of load current.

#### **Power Switch**

N-Channel MOSFET switches are integrated on the JWH5084 to down convert the input voltage to the regulated output voltage. Since the top MOSFET needs a gate voltage greater than the input voltage, a boost capacitor connected between BST and SW pins is required to drive the gate of the top switch. The boost capacitor is charged by the internal LDO when SW is low.

#### **CCM Operation**

Continuous conduction mode (CCM) occurs when the output current is high, and the inductor current is always above zero amps. The JWH5084 can also be configured to operate in forced CCM operation when the output current is low (See *Mode Selection* section for details). In CCM operation, the switching frequency is fairly constant; hence the output ripple keeps almost the same throughout the whole load range.

#### **PFM Operation**

At light load condition, the JWH5084 can be configured to work in PFM mode to optimize the efficiency. When the load decreases, the inductor current will decrease as well. Once the inductor current reaches zero, the part transitions from CCM to PFM mode if the JWH5084 is configured so (see *Mode Selection* section for details).

In PFM mode operation, the high side MOSFET

is turned off by the peak current reference and the low side MOSFET turns on until the inductor current reaches zero. At this time, the output voltage is still higher than the target value which causes the internal COMP voltage lower than a clamp value, and the high side MOSFET is not allowed to turn on until the COMP voltage rises above its clamp voltage.

At light load condition, the high side MOSFET is not turned on as frequently in PFM mode as it is in forced CCM. As a result, the efficiency in pulse skip mode is improved greatly, comparing with that in forced CCM operation.

As the output current increases from the light load condition, the time period within which the current modulator regulates becomes shorter. The high side MOSFET is turned on more frequently. Hence, the switching frequency increases accordingly. The output current reaches the critical level when the current modulator time is zero. The critical level of the output current is determined with the following equation:

$$I_{OUT} := \frac{(V_{IN} - V_{OUT}) \cdot V_{OUT}}{2 \cdot L \cdot f_{SW} \cdot V_{IN}}$$

The part enters PWM mode once the output current exceeds the critical level. After that, the switching frequency stays fairly constant over the output current range.

#### Mode Selection

The JWH5084 provides both forced CCM operation and PFM mode operation in a light-load condition. The JWH5084 has three options for switching frequency selection.

Selecting the operation mode under light load condition and the switching frequency is done

by choosing the resistance value of the resistor connected between MODE and AGND or VCC (See Table 1).

Table 1 --- MODE selection

| R <sub>M_</sub> L<br>(ΚΩ) | R <sub>M_H</sub><br>(ΚΩ) | Mode | Current<br>limit      | Fs    |

|---------------------------|--------------------------|------|-----------------------|-------|

| 5.1                       | 300                      | FCCM | I <sub>LIM_POS1</sub> | 400k  |

| 10                        | 200                      | FCCM | I <sub>LIM_POS2</sub> | 400k  |

| 20                        | 160                      | FCCM | I <sub>LIM_POS1</sub> | 800k  |

| 20                        | 120                      | FCCM | I <sub>LIM_POS2</sub> | 800k  |

| 51                        | 200                      | FCCM | I <sub>LIM_POS1</sub> | 1200k |

| 51                        | 180                      | FCCM | I <sub>LIM_POS2</sub> | 1200k |

| 51                        | 150                      | PFM  | ILIM_POS1             | 400k  |

| 51                        | 120                      | PFM  | I <sub>LIM_POS2</sub> | 400k  |

| 51                        | 91                       | PFM  | I <sub>LIM_POS1</sub> | 800k  |

| 51                        | 82                       | PFM  | I <sub>LIM_POS2</sub> | 800k  |

#### **Shut-Down Mode**

The JWH5084 shuts down when voltage at EN pin is below 0.3V. The entire regulator is off and the supply current consumed by the JWH5084 drops below 7uA.

#### **VIN Under-Voltage Protection**

In addition to the enable function, the JWH5084 provides an Under Voltage Lock-out (UVLO) function that monitors the input voltage. To prevent operation without fully-enhanced internal MOSFET switches, this function inhibits switching when input voltage drops below the UVLO-falling threshold. The IC resumes switching when input voltage exceeds the UVLO-rising threshold.

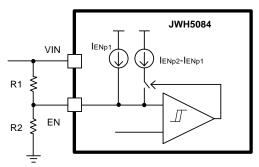

# Enable and Adjustable UVLO Protection

The JWH5084 is enabled when the VIN pin voltage rises above 2.4V and the EN pin voltage

exceeds the enable threshold of 1.22V. The JWH5084 is disabled when the VIN pin voltage falls below 1.85V or when the EN pin voltage is below around 1.1V. Do not leave this pin floating.

If an application requires a different turn-on and turn-off thresholds respectively, use a resistive divider connected between VIN and ground with the central tap connected to EN to adjust the input voltage UVLO. (Shown in Figure 1). The EN pin has a pull-up current  $I_{\text{ENP1}}$  that sets the default state of the pin when it is floating. This current increases to  $I_{\text{ENP2}}$  when the EN pin voltage crosses the turn-on threshold. The UVLO thresholds can be set by following equation:

Fig. 1 Adjustable UVLO

The input voltage UVLO threshold ( $V_{UVLO}$ ) and hysteresis ( $V_{UVLO\_HYS}$ ) can be calculated by the following equation.

$$R_{1} = \frac{V_{START} \times \frac{V_{EN\_LTH}}{V_{EN\_HTH}} - V_{STOP}}{I_{ENP1} \left( 1 - \frac{V_{EN\_LTH}}{V_{EN\_HTH}} \right) + \left( I_{ENP2} - I_{ENP1} \right)}$$

$$R_2 = \frac{R_1 \times V_{\text{EN\_HTH}}}{V_{\text{START}} + (R_1 \times I_{\text{ENP1}}) - V_{\text{EN HTH}}}$$

where

$V_{EN\_HTH} = 1.225V$

$V_{EN\ LTH} = 1.104V$

$I_{ENP2} = 4.197uA$

$I_{ENP1} = 1.91uA$

#### Soft Start

Soft-start is designed in JWH5084 to prevent the converter output voltage from overshooting during startup and short-circuit recovery. An internal current source ( $I_{SS}$ ) of 6uA is designed to charge the external soft-start capacitor ( $C_{SS}$ ) and generates a soft-start (SS) voltage ramping up from 0V to 1.5V. When it is less than internal reference voltage ( $V_{REF}$ , typ. 0.6V), SS voltage overrides  $V_{REF}$  and the error amplifier uses SS voltage as the reference. When SS exceeds  $V_{REF}$ ,  $V_{REF}$  regains control.

The soft start time (10% to 90%)  $T_{SS}$  can be calculated by the following equation.

$${\rm T_{SS}\left(ms\right)} \, := \frac{{\rm C_{SS}\left(nF\right) \cdot V_{REF}\left(V\right) \cdot 0.8}}{{\rm I_{SS}\left(\mu A\right)}}$$

where  $C_{SS}$  is the soft-start capacitance connected between SS pin and AGND pin.

At power up, the soft start pin is discharged before MOSFETs switching to ensure a proper power up. Also, during normal operation, the JWH5084 will stop switching and the soft-start pin will be discharged, when the VIN UVLO is exceeded, EN pin pulled below 1.1V, or a thermal shutdown event occurs.

# Current Sense and Over-Current Protection (OCP)

The JWH5084 features an on-die current sense and two programmable positive current limit thresholds.

The current limit is active when the JWH5084 is enabled. During the low side MOSFET on state, the SW current (inductor current) is sensed, and compared with current limit cycle-by-cycle. The high side MOSFET is only allowed to turn on when the sensed current is below the internal OCP threshold  $I_{LIM}$  (during the low side MOSFET on state) to limit the SW valley current

cycle-by-cycle.

The OCP HICCUP is active during soft start, once OCP HICCUP is active, if the JWH5084 detects over-current condition for consecutive 1000 cycles, it enters HICCUP mode. After soft start, when the current is limited by OCP, the output voltage tends to drop, if the FB drops below under-voltage protection (UVP) threshold for 1ms, it enters HICCUP mode. In HICCUP mode, the JWH5084 latches off the high side MOSFET immediately, and latches off low side MOSFET. Meanwhile, the SS capacitor is also discharged. After about 31ms, the JWH5084 will try to soft start automatically. If the over-current condition still holds, the JWH5084 repeats this operation cycle until the over-current condition disappears, and the output voltage rises smoothly back to the regulation level.

### **Negative Inductor Current limit**

When the low side MOSFET detects a -4A current, the part turns off the low side MOSFET to limit the negative current.

## Pre-Bias Start-Up

The JWH5084 has been designed for a monotonic start-up into pre-biased loads. If the output is pre-biased to a certain voltage during start-up, the IC disables switching for both the high-side and low-side MOSFETs until the voltage on the SS capacitor exceeds the sensed output voltage at FB. Before SS voltage reaches pre-biased FB level, if the BST voltage (from BST to SW) is lower than 1.8V, the low-side MOSFET is turned on to allow the BST voltage to be charged through VCC. The low-side MOSFET is turned on for very narrow pulses, so the drop in pre-biased level is negligible.

#### **Output Voltage Discharge**

When the JWH5084 is disabled through EN, it

enables the output voltage discharge mode. This causes both the high side MOSFET and the low side MOSFET to latch off. A discharge FET connected between SW and PGND is turned on to discharge the output voltage. The typical switch on resistance of this FET is about  $80\Omega$ . Once the FB voltage drops below 10% V<sub>REF</sub>, the discharge FET is turned off.

#### **Output Over-voltage Protection**

The JWH5084 monitors the output voltage by connecting FB to the tap of the output voltage feedback resistor divider to detect an overvoltage condition. This provides auto-recovery OVP mode.

In PFM mode, if the FB voltage exceeds 109% of the REF voltage, the low side MOSFET is turned on until it hits the low-side negative current limit (NOCP). Once it hits NOCP, the low side MOSFET is turned off and the high side MOSFET is turned on. If the FB voltage is still higher than 104% of REF voltage, the low side MOSFET is then turned on again. The JWH5084 keeps this operation until the FB voltage drops below 104% of the REF voltage. Once it does, the JWH5084 exit this mode, the low side MOSFET is allowed to turn off for PFM operation. If FB rises back to more than 109% of the REF voltage, the low side MOSFET turns on again until FB drops back below 104% of the REF voltage.

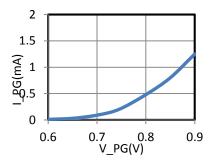

#### **Power Good**

The JWH5084 has power-good (PG) output. The PG pin is the open drain of a MOSFET. Connect to VCC or another voltage source through a resistor. After applying the input voltage, the MOSFET turns on, so PG is pulled to GND before SS is ready. After the FB voltage reaches 93% of the REF voltage, PG is pulled

high after a certain time elapsed.

When the FB voltage drops to 84% of the REF voltage, PG is pulled low. When the FB voltage rises above 93% of the REF voltage, PG is pulled high again.

When the FB voltage exceeds 116% of the REF voltage, PG is pulled low. When the FB voltage drops to 107% of the REF voltage, PG is pulled high again.

Once EN UVLO, OVP, UVP or OTP is triggered, PG is pulled low within 1us deglitch time. If the input supply fails to power the JWH5084, PG is clamped low even though PG is tied to an external DC source through a pull-up resistor. The relationship between the PG voltage and the pull-up current is shown in Figure 2 below:

Fig. 2 Power Good clamped voltage vs. pull-up current

#### **Thermal Protection**

When the temperature of the JWH5084 rises above 160°C, it is forced into thermal shut-down. This is a non-latch protection, the regulator becomes active again when the temperature goes below the thermal shutdown threshold.

There is a second higher thermal protection, the threshold is at typically 171°C. The internal LDO will shut down once temperature goes beyond 171°C. The LDO re-starts working when the temperature goes below the second thermal shutdown threshold.

## **PACKAGE OUTLINE**

## **IMPORTANT NOTICE**

Joulwatt Technology Inc. reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein.

- Any unauthorized redistribution or copy of this document for any purpose is strictly forbidden.

- Joulwatt Technology Inc. does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Copyright © 2021 JWH5084 Incorporated.

All rights are reserved by Joulwatt Technology Inc.