# IT8212F

## **IDE RAID Controller**

# **Preliminary Specification V0.3**

Copyright © 2002 ITE, Inc.

This is Preliminary document release. All specifications are subject to change without notice.

The material contained in this document supersedes all previous documentation issued for the related products included herein. Please contact ITE, Inc. for the latest document(s). All sales are subject to ITE's Standard Terms and Conditions, a copy of which is included in the back of this document.

ITE, IT8212F is a trademark of ITE, Inc.

All other trademarks are claimed by their respective owners.

All specifications are subject to change without notice.

Additional copies of this manual or other ITE literature may be obtained from:

ITE, Inc. Phone: (02) 29126889

Marketing Department Fax: (02) 2910-2551, 2910-2552

8F, No. 233-1, Bao Chiao RD., Hsin Tien,

Taipei County 231, Taiwan, R.O.C.

ITE (USA) Inc.

Phone:

(408) 530-8860

Marketing Department

Fax:

(408) 530-8861

1235 Midas Way Sunnyvale, CA 94086

U.S.A.

ITE (USA) Inc. Phone: (512) 388-7880 Eastern U.S.A. Sales Office Fax: (512) 388-3108

896 Summit St., #105 Round Rock, TX 78664

U.S.A.

If you have any marketing or sales questions, please contact:

Lawrence Liu, at ITE Taiwan: E-mail: lawrence.liu@ite.com.tw, Tel: 886-2-29126889 X6071,

Fax: 886-2-29102551

David Lin, at ITE U.S.A: E-mail: david.lin@iteusa.com, Tel: (408) 530-8860 X238,

Fax: (408) 530-8861

Don Gardenhire, at ITE Eastern USA Office: E-mail: don.gardenhire@iteusa.com

Tel: (512) 388-7880, Fax: (512) 388-3108

To find out more about ITE, visit our World Wide Web at:

http://www.ite.com.tw http://www.iteusa.com

Or e-mail <a href="mailto:itesupport@ite.com.tw">itesupport@ite.com.tw</a> for more product information/services.

## **Contents**

| 1. | Featu | ıres       |           |                                                                         | 1  |

|----|-------|------------|-----------|-------------------------------------------------------------------------|----|

| 2. | Gene  | ral Descri | iption    |                                                                         | 3  |

| 3. | Syste | m Block [  | Diagran   | n                                                                       | 5  |

|    | 3.1   |            | _         |                                                                         |    |

|    | 3.2   |            |           | s Space                                                                 |    |

| 4. | Pin C | onfigurati | on        |                                                                         | 7  |

| 5. | IT821 | I2F Pin De | escripti  | ons                                                                     | 9  |

| 6. | Funct | tional Des | cription  | 1                                                                       | 13 |

|    | 6.1   |            | •         | iption                                                                  |    |

|    |       |            |           | er List                                                                 |    |

|    |       |            |           | PCI Configuration Registers                                             |    |

|    |       | 6.1.3      | List of F | PCI I/O Registers                                                       | 15 |

|    |       |            |           | Local CPU Access Registers                                              |    |

|    |       |            |           | JART Registers                                                          |    |

|    |       | 6.1.6      | PCI Co    | nfiguration Registers Definition                                        |    |

|    |       | 6.         | 1.6.1     | Vendor ID Register (VIDR) — Offset 0x0                                  |    |

|    |       | 6.         | 1.6.2     | Device ID Register (DIDR) — Offset 0x2                                  |    |

|    |       | 6.         | 1.6.3     | Command Register (CMDR) — Offset 0x4                                    |    |

|    |       | 6.         | 1.6.4     | Device Status Register (DSTR) — Offset 0x6                              | 22 |

|    |       | 6.         | 1.6.5     | Revision Register (RID) — Offset 0x8                                    | 22 |

|    |       | 6.         | 1.6.6     | Program Interface (PIR) — Offset 0x9                                    |    |

|    |       | 6.         | 1.6.7     | Sub-class Code Register (SCC) — Offset 0xA                              |    |

|    |       | 6.         | 1.6.8     | Base Class Code Register (BCC) — Offset 0xB                             |    |

|    |       |            |           | Cache Line Size Register (CLS) — Offset 0xC                             |    |

|    |       |            |           | Master Latency Timer Register (MLT) — Offset 0xD                        |    |

|    |       | 6.         | 1.6.11    | Header Type Register (HTYPE) — Offset 0xE                               | 23 |

|    |       |            |           | Built-in Self Test Register (BISTR) — Offset 0xF                        |    |

|    |       | 6.         | 1.6.13    | Primary Channel Command Block Register Base Address (PCMDBA) — Offset 0 |    |

|    |       | 6          | 1611      | Primary Channel Control Block Base Address (PCNTBA) — Offset 0x14       | 24 |

|    |       |            |           | Secondary Channel Command Block Base Address (SCMDBA) — Offset 0x14     |    |

|    |       |            |           | Secondary Channel Control Block Base Address (SCNTBA) — Offset 0x10     |    |

|    |       |            |           | Bus Master Base Address Register (BMBA) — Offset 0x20                   |    |

|    |       |            |           | Sub-system Vendor ID Register (SVID) — Offset 0x20                      |    |

|    |       |            |           |                                                                         |    |

|    |       |            |           | Sub-system Device ID Register (SID) — Offset 0x2E                       |    |

|    |       |            |           | Expansion ROM Base Address Register (ROMBAR) — Offset 0x30              |    |

|    |       |            |           | Interrupt Line Register (ILR) — Offset 0x3C                             |    |

|    |       |            |           |                                                                         |    |

|    |       |            |           | Interrupt Pin Register (IPR) — Offset 0x3D                              |    |

|    |       |            |           | MIN_GNT Register (MGR) — Offset 0x3E                                    |    |

|    |       |            |           | MAX_LAT Register (MLR) — Offset 0x3F                                    |    |

|    |       |            |           | IDE I/O Configuration Register (IOCFG) — Offset 0x40                    |    |

|    |       |            |           | IDE Driving Current Register (DCR) — Offset 0x42                        |    |

|    |       |            |           | IDE Virtual Channel Exist Register (IDEENR) — Offset 0x43               |    |

|    |       |            |           | PCI Burst Threshold Register (PCIBRSTR) — Offset 0x44                   |    |

|    |       | 6.         | 1.6.30    | PLL1 Control Register (PLL1CR) — Offset 0x48                            | 29 |

|       |                  | PLL2 Control Register (PLL2CR) — Offset 0x49                                      |    |

|-------|------------------|-----------------------------------------------------------------------------------|----|

|       | 6.1.6.32         | IDE Bus Skew Control Register (IDEBSCR) — Offset 0x4C                             | 30 |

|       | 6.1.6.33         | PCI Mode Control Register (PCICR) — Offset 0x50                                   | 30 |

|       |                  | RAID Function Control Registers (RAIDCR) — Offset 0x51                            |    |

|       |                  | RAID Transfer Sector Count Register (RAIDTSCR) — Offset 0x52                      |    |

|       |                  | PCI Mode Primary PIO and DMA Timing Registers (PMPIOTR) — Offset 0x54             |    |

|       |                  | PCI Mode Primary Device 0 Ultra DMA Timing Registers (PMPD0UDTR) — Offs           |    |

|       | 0.1.0.57<br>0x56 | - Chiviode Filmary Device o Olira Diviz Filming Registers (Fivir Dood ITX) — Ons  |    |

|       |                  | PCI Mode Primary Device 1 Ultra DMA Timing Registers (PMPD1UDTR) — Offs           |    |

|       |                  |                                                                                   |    |

|       | 0x57             | DOLM LO L DIO LENATI I D I L (DMODIOTE) OF LO S                                   |    |

|       | 6.1.6.39         | PCI Mode Secondary PIO and DMA Timing Registers (PMSPIOTR) — Offset 0x5           |    |

|       | 0.4.0.40         |                                                                                   |    |

|       |                  | PCI Mode Secondary Device 0 Ultra DMA Timing Registers (PMSD0UDTR)                |    |

|       |                  | 5A                                                                                |    |

|       |                  | PCI Mode Secondary Device 1 Ultra DMA Timing Registers (PMSD1UDTR)                |    |

|       |                  | 5B                                                                                |    |

|       |                  | Test Mode Register (TMR) — Offset 0x5C                                            |    |

|       |                  | CPU NMI Control Register (CNMIR) — Offset 0x5D                                    |    |

|       | 6.1.6.44         | CPU Control Register (CCR) — Offset 0x5E                                          | 34 |

|       | 6.1.6.45         | Capability Identifier Register (CAPIDR) — Offset 0x80                             | 34 |

|       | 6.1.6.46         | Next Item Pointer Register (NEXT_PTR) — Offset 0x81                               | 34 |

|       | 6.1.6.47         | Power Management Capabilities Register (PMCR) — Offset 0x82                       | 34 |

|       |                  | Power Management Control/Status Register (PMCSR) — Offset 0x84                    |    |

|       |                  | PMCSR PCI to PCI Bridge Support Extensions — Offset 0x86                          |    |

|       |                  | Data Register (DR) — Offset 0x87                                                  |    |

| 617   |                  | Register Bus Master IDE I/O Registers                                             |    |

| 0.1.7 | 6.1.7.1          | Bus Master IDE Command Registers (BMICR) — Offset 0x0 (Primary) /                 |    |

|       |                  | iry)                                                                              |    |

|       | `                | Bus Master IDE Command and Status Registers (BMICSR) — Offset 0x2, 0xA            |    |

|       |                  | Bus Master IDE Descriptor Table Pointer Registers (BMIDTPR) — Offset 0x4, 0x6     |    |

|       | 0.1.7.5          | Dus iviaster IDE Descriptor Table Fornter Registers (Divid 11 R) — Onset 0X4, 0X0 |    |

| 618   | Virtual          | DE Interface and Status Registers                                                 |    |

| 0.1.0 |                  | Primary/Secondary IDE Data Registers — PCI IO Space: Offset 0x0, CPU Memo         |    |

|       |                  | k08000/0x08020                                                                    |    |

|       | •                | Primary/Secondary IDE Error/Feature Registers — PCI IO Space: Offset 0x1, CF      |    |

|       |                  | Space: 0x08001/0x08021 (0x0800E/0x0802E)                                          |    |

|       | •                | Primary/Secondary IDE Sector Count (Ext.) Registers — PCI IO Space: Offset 0x     |    |

|       |                  | nory Space: 0x08002/0x08022 (0x0800A/0x0802A)                                     |    |

|       |                  | ,                                                                                 |    |

|       | 6.1.8.4          | Primary/Secondary IDE Sector Number (Ext.) Registers — PCI IO Space: Offset 0x    |    |

|       |                  | nory Space: 0x08003/0x08023 (0x0800B/0x0802B)                                     |    |

|       | 6.1.8.5          | Primary/Secondary IDE Cylinder Low (Ext.) Registers — PCI IO Space: Offset 03     |    |

|       |                  | nory Space: 0x08004/0x08024 (0x0800C/0x0802C)                                     |    |

|       | 6.1.8.6          | Primary/Secondary IDE Cylinder High (Ext.) Registers — PCI IO Space: Offset 0x    |    |

|       |                  | nory Space: 0x08005/0x08025 (0x0800D/0x0802D)                                     |    |

|       | 6.1.8.7          | Primary/Secondary IDE Device/Head Registers — PCI IO Space: Offset 0x6, CF        |    |

|       | •                | Space: 0x08006/0x08026                                                            |    |

|       | 6.1.8.8          | Primary/Secondary IDE Status/Command Registers — PCI IO Space: Offset 0x          |    |

|       |                  | nory Space: 0x08007/0x08027 (0x0800F/0x0802F)                                     |    |

|       | 6.1.8.9          | Primary/Secondary IDE Alternate Status/Device Control Registers — PCI IO Space    |    |

|       | Offset 0x        | 6, CPU Memory Space: 0x08016/0x08036 (0x0801A/0x0803A)                            | 42 |

| 6.1.9 | Local C            | PU Registers            |               |                  |             |                                       |           |                                        |                           |                 |

|-------|--------------------|-------------------------|---------------|------------------|-------------|---------------------------------------|-----------|----------------------------------------|---------------------------|-----------------|

|       | 6.1.9.1            | IDE Transfei            | r Contro      | ol Regist        | ers         |                                       |           |                                        |                           | 43              |

|       |                    | 6.1.9.1.1<br>0x08100, 0 | x08110        | )                |             |                                       |           |                                        |                           | 43              |

|       |                    | 6.1.9.1.2<br>0x08112    |               |                  |             |                                       |           | DEOPR)-                                |                           |                 |

|       |                    | 6.1.9.1.3<br>Address 0x | IDE<br>08103. | PIO ar<br>0x0811 | nd DMA<br>3 | Timing                                | Registe   | rs (PPIO                               | TMR/SPIC                  | TMR) —          |

|       |                    | 6.1.9.1.4               | IDE           | Ultra D          | MA Timi     | ng Regi                               | isters (P | UDMATM                                 | R/SUDMA                   | TMR) —          |

|       |                    | Address 0x              | 08104.        | 0x0811           | 4           |                                       |           |                                        |                           | 44              |

|       | 6.1.9.2            | FIFO Access             | S Contro      | ol Regist        | ers (PFIF   | OCR/SF                                | IFOCR)    | — Addres                               | s 0x08105                 | , 0x08115<br>45 |

|       | 6.1.9.3            | FIFO Status             | Regist        | ers (PFII        | FOSR/SF     | IFOSR)                                | — Addre   | ess 0x0810                             | 06, 0x081 <sup>2</sup>    | 1645            |

|       | 6.1.9.4<br>0x08118 |                         |               |                  |             | · · · · · · · · · · · · · · · · · · · |           | ······································ |                           | 45              |

|       | 6.1.9.5<br>0x0811A | FIFO High               | Word          | Access           | Registers   | (PFIF                                 | OHR/SFI   | FOHR)—                                 | Address                   | 0x0810A,        |

|       |                    | IDE Interface           |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 6.1.9.6.1               |               |                  |             |                                       |           | ress 0x08                              |                           |                 |

|       |                    | 6.1.9.6.2<br>0x08141    |               |                  |             | -                                     | •         | SEFR) —                                |                           |                 |

|       |                    | 6.1.9.6.3<br>0x08142    |               |                  |             |                                       |           | SSCR) —                                |                           |                 |

|       |                    | 6.1.9.6.4<br>0x08143    | IDE           | Sector N         | Number F    | Registers                             | (PSNR/    | SSNR) —                                | - Address                 | 0x08123,        |

|       |                    | 6.1.9.6.5<br>0x08144    | IDE           | Cylinde          | Low R       | egisters                              | (PCLR/S   | SCLR) —                                | Address                   | 0x08124,        |

|       |                    | 6.1.9.6.6<br>0x08145    | IDE           | Cylinder         | High R      | egisters                              | (PCHR/S   | SCHR) —                                | Address                   | 0x08125,        |

|       |                    | 6.1.9.6.7               | IDE           | Device/l         | Head Re     | gisters                               | (PHDR/S   | SHDR) —                                | Address                   | 0x08126,        |

|       |                    | 0x08146                 |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 6.1.9.6.8<br>6.1.9.6.9  |               |                  |             |                                       |           | lress 0x08<br>legisters (              |                           |                 |

|       |                    | Address 0x              |               |                  |             |                                       |           |                                        |                           |                 |

|       | 6.1.9.7            | PCI Channe              |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 6.1.9.7.1<br>0x08200, 0 | Char          | nnel Tra         | ansfer C    | ount R                                | egisters  | (PTCR/S                                | TCR) —                    | Address         |

|       |                    | 6.1.9.7.2               |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 0x0820A                 |               |                  |             |                                       |           | ·······                                |                           | 48              |

|       | 6.1.9.8            | Rebuild Reg             |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 6.1.9.8.1               | Rebu          | uild Bloc        | k Countei   | Registe                               | er (RBCT  | R) — Add                               | ress 0x08                 | 210 50          |

|       |                    | 6.1.9.8.2               |               |                  |             |                                       |           | <ul><li>Address</li></ul>              |                           |                 |

|       | 6.1.9.9            | Interrupt Reg           |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 6.1.9.9.1               |               |                  |             |                                       |           | Address 0                              |                           |                 |

|       |                    | 6.1.9.9.2               |               |                  |             |                                       |           | ddress 0x                              |                           |                 |

|       |                    | 6.1.9.9.3               |               |                  |             |                                       |           | dress 0x08                             |                           |                 |

|       | 6.1.9.10           | Timer Regist            |               |                  |             |                                       |           |                                        |                           |                 |

|       |                    | 6.1.9.10.1<br>0x08238   | 53            |                  | Ü           | `                                     |           | 1CTLR) –                               |                           | ·               |

|       |                    | 6.1.9.10.2              | Time          | er 0/1 Co        | unt Regis   | sters (T0                             | CNTR/T    | 1CNTR) -                               | <ul><li>Address</li></ul> | 0x08232,        |

| 0x0823A                                                                                        | 53 |

|------------------------------------------------------------------------------------------------|----|

| 6.1.9.10.3 Timer 0 /1 Max. Count Registers (T0MAXR)/T1MAXR) —                                  |    |

| 0x08234, 0x0823C<br>6.1.9.11 Miscellaneous Registers                                           |    |

| 6.1.9.11.1 IDE Clock Register (IDECLK) — Address 0x08252                                       |    |

| 6.1.9.11.2 GPIO Register (GPIOR) — Address 0x08254                                             |    |

| 6.1.10 UART Registers Definition                                                               |    |

| 6.1.10.1 UART Receiver Buffer Register (URBR) — Address 0x09000                                |    |

| 6.1.10.2 UART Transmitter Buffer Register (UTBR) — Address 0x09000                             |    |

| 6.1.10.3 UART Interrupt Enable Register (UIER) — Address 0x09002                               |    |

| 6.1.10.5 UART FIFO Control Register (UFCR) — Address 0x09004                                   |    |

| 6.1.10.6 UART Divisor Latch LSB Register (UDLL) — Address 0x09000                              |    |

| 6.1.10.7 UART Divisor Latch MSB Register (UDLM) — Address 0x09002                              |    |

| 6.1.10.8 UART Line Control Register (ULCR) — Address 0x09006                                   |    |

| 6.1.10.9 UART Line Status Register (ULSR) — Offset 0x0900A                                     |    |

| 6.2 UART Operation                                                                             |    |

| 6.2.2 Programming                                                                              |    |

| 6.2.2.1 Programming Sequence                                                                   |    |

| 6.2.3 Software Reset                                                                           |    |

| 6.2.4 Clock Input Operation                                                                    |    |

| 6.2.5.1 RCVR Interrupt                                                                         |    |

| 6.2.5.2 XMIT Interrupt                                                                         |    |

| 7. DC Characteristics                                                                          | 65 |

| 8. AC Characteristics                                                                          | 67 |

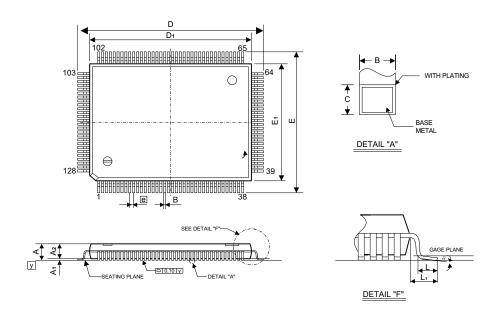

| 9. Package Information                                                                         | 73 |

| 10. Ordering Information                                                                       | 75 |

|                                                                                                |    |

|                                                                                                |    |

| Tables                                                                                         |    |

| Table 4-1. Pins Listed in Numeric Order                                                        | 8  |

| Table 5-1. Pin Descriptions of PCI Bus Interface                                               |    |

| Table 5-2. Pin Descriptions of IDE Primary Channel Interface                                   |    |

| Table 5-3. Pin Descriptions of IDE Secondary Channel Interface                                 |    |

| Table 5-4. Pin Descriptions of Flash/ROM Interface*                                            |    |

| Table 5-5. Pin Descriptions of Miscellaneous Signal                                            |    |

| Table 5-6. Pin Descriptions of Power/Ground Signals                                            |    |

| Table 6-1. List of PCI Configuration Registers                                                 |    |

| Table 6-2. List of PCI I/O Register Bus Master IDE I/O Registers                               |    |

| Table 6-3. List of PCI I/O Register From Local CPU View Bus Master IDE I/O Registers           |    |

| Table 6-4. Virtual IDE Interface and Status Registers from PCI I/O View (PCI IO Space Mapping) | 16 |

## **Contents**

| Table 6-5. Virtual IDE Interface and Status Registers from Local CPU View | 17 |

|---------------------------------------------------------------------------|----|

| Table 6-6. List of IDE Control Registers for Local CPU                    | 18 |

| Table 6-7. List of UART Registers                                         | 20 |

| Table 6-8. Status Register                                                | 41 |

| Table 6-9. Command Register                                               | 41 |

| Table 6-10. List of IDE I/O Port Primary Channel Address Mapping          | 46 |

| Table 6-11. UART Interrupt Identification Register                        | 57 |

| Table 6-12. Baud Rates Using (1.8432 MHz) Clock                           | 59 |

| Table 6-13. Line Status Register Bits                                     | 62 |

| Table 6-14. Reset Control of Register and Pinout Signals                  | 62 |

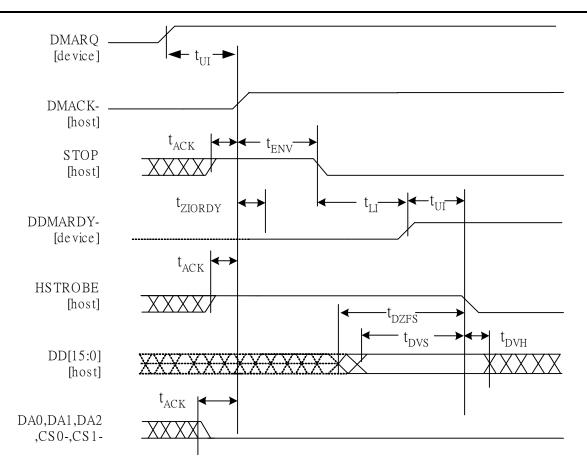

| Table 8-1. Register transfer to/from device                               | 67 |

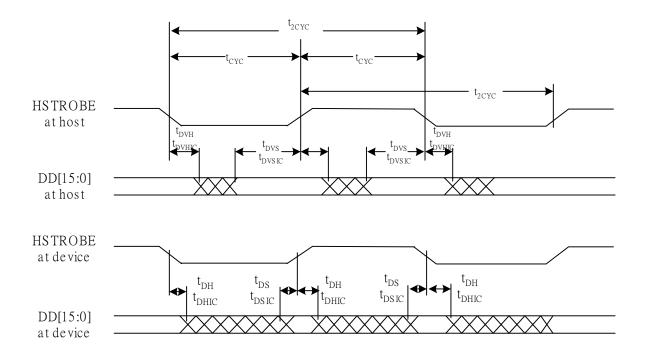

| Table 8-2. Ultra DMA data burst timing requirements                       | 68 |

|                                                                           |    |

|                                                                           |    |

| Figures                                                                   |    |

| Figure 3-1. Block Diagram                                                 | 5  |

| Figure 3-2. System Address Space                                          | 6  |

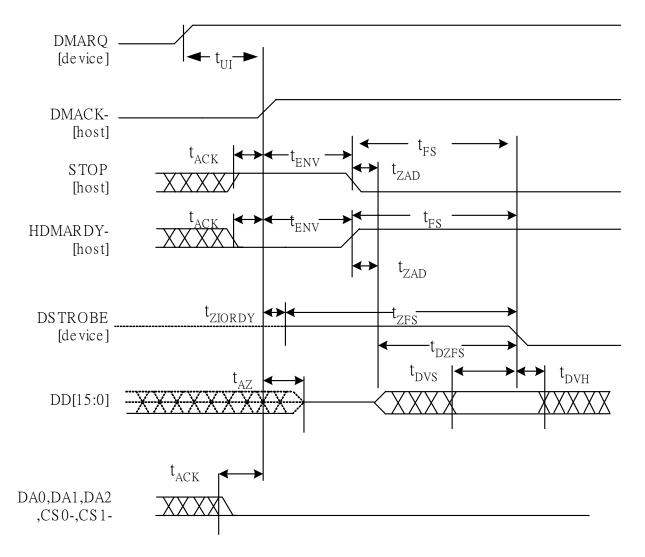

| Figure 8-1. Register transfer to/from device                              | 67 |

| Figure 8-2. Initiating an Ultra DMA data-in burst                         | 68 |

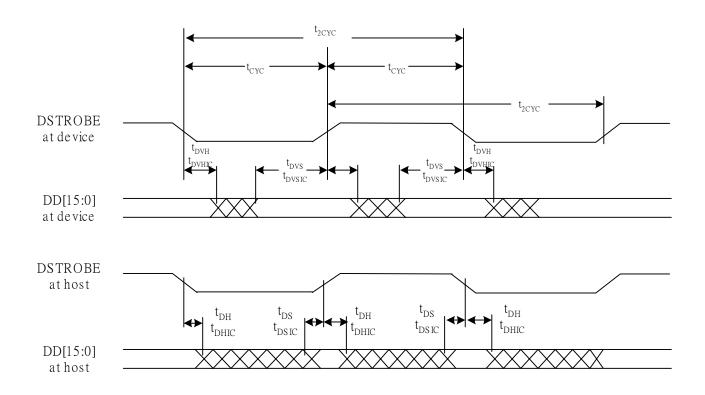

| Figure 8-3. Sustained Ultra DMA data-in burst                             | 69 |

| Figure 8-4. Initiating an Ultra DMA data-out burst                        | 70 |

| Figure 8-5. Sustained Ultra DMA data-out burst                            | 71 |

|                                                                           |    |

#### 1. Features

#### ■ RAID Function

- Compatible with the ATA/ATAPI-6 specification and supports two IDE channels with 4 drives

- Supports ANSI ATA proposal PIO Modes 0, 1, 2, 3, 4 with flow control, DMA Modes 0, 1, 2 and Ultra DMA modes 0, 1, 2, 3, 4, 5, 6

- Programmable active pulses and recovery time for data port access timing

- 512 bytes FIFO for data transfer per IDE channel

- Supports RAID 0/1/0+1 function

- Supports JBOD function

- Supports Scatter/Gather function for DMA/UDMA transfer

- Supports pre-fetch and post-write function for PIO mode per IDE channel

- Includes one embedded CPU and firmware on our chip to handle the RAID function. It can reduce the driver's loading and improve the system's stability

#### ■ PCI Interface

- Host interface compiles with PCI local bus specification revision 2.2

- Supports PCI Power Management v1.1 capability

- Supports one Flash/ROM interface for expansion ROM of the PCI card

#### ■ Miscellaney

Supports the drivers for Windows 98SE/Me/XP, Windows NT 4.0, Windows 2000 and Linux

#### ■ 128-pin PQFP

## **General Description**

#### 2. General Description

The IDE RAID controller, which is compatible with the ATA/ATAPI-6 specification and supports the IDE RAID 0/1/0+1 function, acts as an interface between the system and IDE device. It supports not only a Scatter/Gather DMA mechanism that complies with the Programming Interface for Bus Master IDE Controller Revision 1.0 but also 2 IDE channels and up to 4 IDE devices.

Different from using traditional software to handle the RAID function, IT8212F features one embedded CPU and firmware to handle it. The methodology is able to improve the system's stability and reduce the drivier's loading.

IT8212F is availabe in the 128-pin PQFP package.

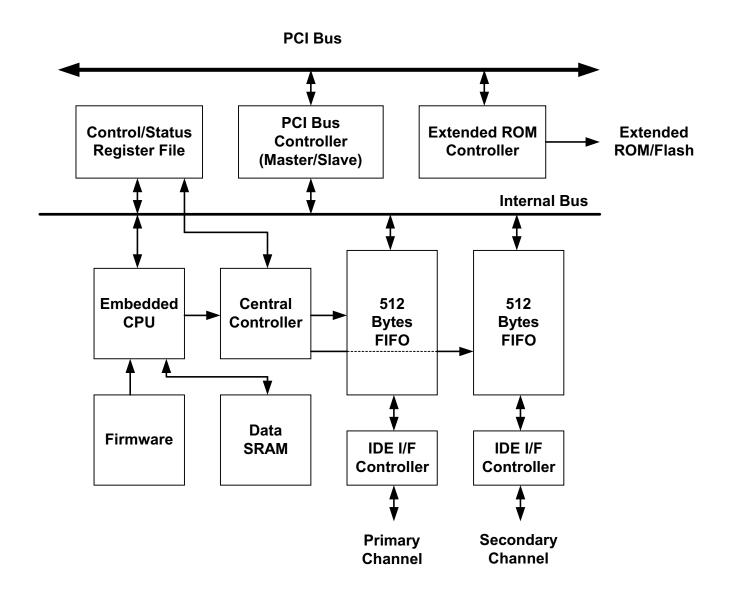

#### 3. System Block Diagram

#### 3.1 Block Diagram

Figure 3-1. Block Diagram

## 3.2 System Address Space

| 0xFFFFFh |                        |

|----------|------------------------|

|          | ROM (Max. 512K)        |

| 0x80000h |                        |

|          | Reserved               |

| 0x09000h |                        |

| 0x08000h | UART                   |

| 0x08000h | User Defined Registers |

|          | SRAM                   |

| 0x00000h |                        |

Figure 3-2. System Address Space

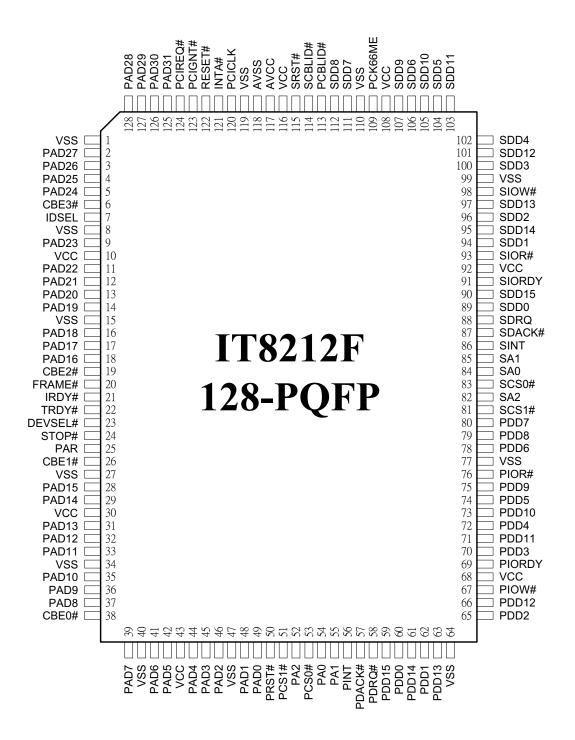

#### 4. Pin Configuration

Table 4-1. Pins Listed in Numeric Order

| Pin | Signal  | Pin | Signal       | Pin | Signal       | Pin | Signal  |

|-----|---------|-----|--------------|-----|--------------|-----|---------|

| 1   | VSS     | 33  | PAD11        | 65  | PDD2 / FD2   | 97  | SDD13   |

| 2   | PAD27   | 34  | VSS          | 66  | PDD12 / FA4  | 98  | SIOW#   |

| 3   | PAD26   | 35  | PAD10        | 67  | PIOW#        | 99  | VSS     |

| 4   | PAD25   | 36  | PAD9         | 68  | VCC          | 100 | SDD3    |

| 5   | PAD24   | 37  | PAD8         | 69  | PIORDY       | 101 | SDD12   |

| 6   | CBE3#   | 38  | CBE0#        | 70  | PDD3 / FD3   | 102 | SDD4    |

| 7   | IDSEL   | 39  | PAD7         | 71  | PDD11 / FA3  | 103 | SDD11   |

| 8   | VSS     | 40  | VSS          | 72  | PDD4 / FD4   | 104 | SDD5    |

| 9   | PAD23   | 41  | PAD6         | 73  | PDD10 / FA2  | 105 | SDD10   |

| 10  | VCC     | 42  | PAD5         | 74  | PDD5 / FD5   | 106 | SDD6    |

| 11  | PAD22   | 43  | VCC          | 75  | PDD9 / FA1   | 107 | SDD9    |

| 12  | PAD21   | 44  | PAD4         | 76  | PIOR#        | 108 | VCC     |

| 13  | PAD20   | 45  | PAD3         | 77  | VSS          | 109 | PCK66ME |

| 14  | PAD19   | 46  | PAD2         | 78  | PDD6 / FD6   | 110 | VSS     |

| 15  | VSS     | 47  | VSS          | 79  | PDD8 / FA0   | 111 | SDD7    |

| 16  | PAD18   | 48  | PAD1         | 80  | PDD7 / FD7   | 112 | SDD8    |

| 17  | PAD17   | 49  | PAD0         | 81  | SCS1# / FOE# | 113 | PCBLID# |

| 18  | PAD16   | 50  | PRST#        | 82  | SA2 / FA11   | 114 | SCBLID# |

| 19  | CBE2#   | 51  | PCS1# / FA13 | 83  | SCS0# / FWE# | 115 | SRST#   |

| 20  | FRAME#  | 52  | PA2 / FA10   | 84  | SA0 / FA16   | 116 | VCC     |

| 21  | IRDY#   | 53  | PCS0# / FA12 | 85  | SA1 / FA15   | 117 | AVCC    |

| 22  | TRDY#   | 54  | PA0 / FA8    | 86  | SINT         | 118 | AVSS    |

| 23  | DEVSEL# | 55  | PA1 / FA9    | 87  | SDACK#       | 119 | VSS     |

| 24  | STOP#   | 56  | PINT         | 88  | SDRQ         | 120 | PCICLK  |

| 25  | PAR     | 57  | PDACK#       | 89  | SDD0         | 121 | INTA#   |

| 26  | CBE1#   | 58  | PDRQ#        | 90  | SDD15 / FA14 | 122 | RESET#  |

| 27  | VSS     | 59  | PDD15 / FA7  | 91  | SIORDY       | 123 | PCIGNT# |

| 28  | PAD15   | 60  | PDD0 / FD0   | 92  | VCC          | 124 | PCIREQ# |

| 29  | PAD14   | 61  | PDD14 / FA6  | 93  | SIOR#        | 125 | PAD31   |

| 30  | VCC     | 62  | PDD1 / FD1   | 94  | SDD1         | 126 | PAD30   |

| 31  | PAD13   | 63  | PDD13 / FA5  | 95  | SDD14        | 127 | PAD29   |

| 32  | PAD12   | 64  | VSS          | 96  | SDD2         | 128 | PAD28   |

## 5. IT8212F Pin Descriptions

Table 5-1. Pin Descriptions of PCI Bus Interface

| Signal         | Pin(s) No.                                                                                       | Attribute | Description                      |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------|-----------|----------------------------------|--|--|--|--|

| PCI Bus Interf | PCI Bus Interface (3.3V CMOS I/F, 5V tolerant)                                                   |           |                                  |  |  |  |  |

| RESET#         | 122                                                                                              | PI        | System Reset                     |  |  |  |  |

| PCICLK         | 120                                                                                              | PI        | PCI Clock                        |  |  |  |  |

| PAD31-0        | 125-128,<br>2-5, 9,<br>11-14,<br>16-18, 28,<br>29, 31-33,<br>35-37, 39,<br>41, 42,<br>44-46, 48, | PIO       | PCI Address Data                 |  |  |  |  |

| CBE3-0#        | 6, 19, 26, 38                                                                                    | PIO       | PCI Command Byte Enable          |  |  |  |  |

| FRAME#         | 20                                                                                               | PIO       | PCI FRAME# Signal                |  |  |  |  |

| DEVSEL#        | 23                                                                                               | PIO       | PCI DEVSEL# Signal               |  |  |  |  |

| IRDY#          | 21                                                                                               | PIO       | PCI IRDY# Signal                 |  |  |  |  |

| TRDY#          | 22                                                                                               | PIO       | PCI TRDY# Signal                 |  |  |  |  |

| STOP#          | 24                                                                                               | PIO       | PCI STOP# Signal                 |  |  |  |  |

| PAR            | 25                                                                                               | PIO       | PCI Parity                       |  |  |  |  |

| IDSEL          | 7                                                                                                | PI        | PCI Initialization Device Select |  |  |  |  |

| INTA#          | 121                                                                                              | PO        | PCI Interrupt A Output           |  |  |  |  |

| PCIREQ#        | 124                                                                                              | PO        | PCI Request Output               |  |  |  |  |

| PCIGNT#        | 123                                                                                              | PI        | PCI Grant Input                  |  |  |  |  |

Table 5-2. Pin Descriptions of IDE Primary Channel Interface

| Signal        | Pin(s) No.                                                                    | Attribute | Description                                        |  |  |  |  |

|---------------|-------------------------------------------------------------------------------|-----------|----------------------------------------------------|--|--|--|--|

| IDE Primary C | DE Primary Channel Interface (3.3V CMOS I/F, 5V tolerant)                     |           |                                                    |  |  |  |  |

| PDD15-0       | 59, 61, 63,<br>66, 71, 73,<br>75, 79, 80,<br>78, 74, 72,<br>70, 65, 62,<br>60 | IOP       | IDE Primary Channel Data Bus                       |  |  |  |  |

| PA2-0         | 52, 55, 54                                                                    | OP        | IDE Primary Channel Device Address                 |  |  |  |  |

| PCS1#         | 51                                                                            | OP        | IDE Primary Channel Chip Select 1                  |  |  |  |  |

| PCS0#         | 53                                                                            | OP        | IDE Primary Channel Chip Select 0                  |  |  |  |  |

| PIOW#         | 67                                                                            | OP        | IDE Primary Channel IO Write Strobe                |  |  |  |  |

| PIOR#         | 76                                                                            | OP        | IDE Primary Channel IO Read Strobe                 |  |  |  |  |

| PDRQ          | 58                                                                            | 1         | IDE Primary Channel DMA Request                    |  |  |  |  |

| PDACK#        | 57                                                                            | OP        | IDE Primary Channel DMA Acknowledge                |  |  |  |  |

| PIORDY        | 69                                                                            | ĺ         | IDE Primary Channel IO Channel Ready               |  |  |  |  |

| PINT          | 56                                                                            | I         | IDE Primary Channel Interrupt                      |  |  |  |  |

| PCBLID#       | 113                                                                           | I         | IDE Primary Channel Cable Assembly Type Identifier |  |  |  |  |

| PRST#         | 50                                                                            | OP        | IDE Primary Channel Reset                          |  |  |  |  |

www.ite.com.tw 9 IT8212F V0.3

Table 5-3. Pin Descriptions of IDE Secondary Channel Interface

| Signal                                                       | Pin(s) No.  | Attribute | Description                                          |  |  |  |

|--------------------------------------------------------------|-------------|-----------|------------------------------------------------------|--|--|--|

| IDE Secondary Channel Interface (3.3V CMOS I/F, 5V tolerant) |             |           |                                                      |  |  |  |

| SDD15-0                                                      | 90, 95, 97, | IOP       | IDE Secondary Channel Data Bus                       |  |  |  |

|                                                              | 101, 103,   |           |                                                      |  |  |  |

|                                                              | 105, 107,   |           |                                                      |  |  |  |

|                                                              | 112, 111,   |           |                                                      |  |  |  |

|                                                              | 106, 104,   |           |                                                      |  |  |  |

|                                                              | 102, 100,   |           |                                                      |  |  |  |

|                                                              | 96, 94, 89  |           |                                                      |  |  |  |

| SA2-0                                                        | 82, 85, 84  | OP        | IDE Secondary Channel Device Address                 |  |  |  |

| SCS1-0#                                                      | 81, 83      | OP        | IDE Secondary Channel Chip Select                    |  |  |  |

| SIOW#                                                        | 98          | OP        | IDE Secondary Channel IO Write Strobe                |  |  |  |

| SIOR#                                                        | 93          | OP        | IDE Secondary Channel IO Read Strobe                 |  |  |  |

| SDRQ                                                         | 88          | I         | IDE Secondary Channel DMA Request                    |  |  |  |

| SDACK#                                                       | 87          | OP        | IDE Secondary Channel DMA Acknowledge                |  |  |  |

| SIORDY                                                       | 91          | I         | IDE Secondary Channel IO Channel Ready               |  |  |  |

| SINT                                                         | 86          | I         | IDE Secondary Channel Interrupt                      |  |  |  |

| SCBLID#                                                      | 114         | I         | IDE Secondary Channel Cable Assembly Type Identifier |  |  |  |

| SRST#                                                        | 115         | OP        | IDE Secondary Channel Reset                          |  |  |  |

Table 5-4. Pin Descriptions of Flash/ROM Interface\*

| Signal       | Pin(s) No.                                                                        | Attribute | Description                                                                                                                                                    |

|--------------|-----------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Flash/ROM In | nterface (3.3V C                                                                  | MOS I/F)  |                                                                                                                                                                |

| FWE#         | 83                                                                                | OP        | Flash/ROM Memory Write Enable This signal is multiplex with SCS0#.                                                                                             |

| FOE#         | 81                                                                                | OP        | Flash/ROM Memory Output Enable This signal is multiplex with SCS1#.                                                                                            |

| FCS#         | 109                                                                               | O8        | Flash/ROM Memory Chip Select This signal is multiplex with PCK66ME.                                                                                            |

| FA16-0       | 84, 85, 90,<br>51, 53, 82,<br>52, 55, 54,<br>59, 61, 63,<br>66, 71, 73,<br>75, 79 | OP        | Flash/ROM Memory Address These signals are multiplex with the following signals (from MSB to LSB): SA0, SA1, SDD15, PCS1#, PCS0#, SA2, PA2, PA1, PA0, PDD15-8. |

| FD7-0        | 80, 78, 74,<br>72, 70, 65,<br>62, 60                                              | IOP       | Flash/ROM Memory Output Enable These signals are multiplex with PDD7-0.                                                                                        |

<sup>\*:</sup> The above pins are multiplex function pins.

## **Pin Descriptions**

#### Table 5-5. Pin Descriptions of Miscellaneous Signal

| Signal       | Pin(s) No.      | Attribute | Description                                                                                                                                                                                                                                                                                                                     |

|--------------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miscellaneou | us Signal (3.3\ | CMOS I/F) |                                                                                                                                                                                                                                                                                                                                 |

| PCK66ME      | 109             | ID        | PCI Clock 66 MHz Input Enable This signal indicates the PCI clock frequency is 66 MHz or 33 MHz. The signal is only detected when the RESET# signal is changed from low to high. If the signal is high, the PCICLK frequency is 66 MHz; otherwise the frequency is 33 MHz. When the RESET# is high, the signal is used as FCS#. |

#### Table 5-6. Pin Descriptions of Power/Ground Signals

| Signal     | Pin(s) No.                                              | Attribute | Description                  |

|------------|---------------------------------------------------------|-----------|------------------------------|

| Power Grou | nd Signals                                              |           |                              |

| VSS        | 1, 8, 15, 27,<br>34, 40, 47,<br>64, 77, 99,<br>110, 119 | I         | Ground                       |

| VCC        | 10, 30, 43,<br>68, 92, 108,<br>116                      | _         | Power Supply of 3.3V         |

| AVSS       | 118                                                     | I         | Analog Ground for analog PLL |

| AVCC       | 117                                                     |           | Analog VCC for analog PLL    |

Notes: IO cell types are described as below:

I: Input PAD.

ID: Input PAD (integrate a 75k-ohm pull-down resistor).

IK: Schmitt Trigger Input PAD.

PI: PCI Bus Specified Input PAD.

O8: 8mA Output PAD.

OP: Programming Output PAD, the output driving can be programmed to be 2~12mA, the default value is 8mA.

PO: PCI Bus Specified Ouput PAD.

PIO: PCI Bus Specified Input/Output PAD.

IOP: Programming Input/Output PAD, the output driving can be programmed to be 2~12mA, the default value is 8mA.

**6.1 Register Description**

6.1.1

Register List List of PCI Configuration Registers 6.1.2

Table 6-1. List of PCI Configuration Registers

| 31                                          | 16                                      | 15                         | 00                                   | Index   |

|---------------------------------------------|-----------------------------------------|----------------------------|--------------------------------------|---------|

| Device ID                                   | (8212h)                                 | Vendor II                  | O (1283h)                            | 00h-03h |

| Status (                                    | 0230h)                                  | Comman                     | d (0000h)                            | 04h-07h |

| Base Class Code (01h)                       | Sub-class code (04h)                    | Program Interface<br>(00h) | Revision ID (10h)                    | 08h-0Bh |

| Reserved                                    | Header Type (00h)                       | Latency Timer (20h)        | Cache Line Size (00h)                | 0Ch-0Fh |

| Primary (                                   | Channel Command Block                   | Register Base Address      | (1F1h)                               | 10h-13h |

| Primar                                      | y channel Control Block I               | Register Base Address (    | 3F5h)                                | 14h-17h |

| Secondar                                    | y Channel Command Blo                   | ck Register Base Addres    | ss (171h)                            | 18h-1Bh |

| Seconda                                     | ary Channel Control Blocl               | k Register Base Address    | (375h)                               | 1Ch-1Fh |

|                                             | Bus Master Base Addr                    | ress Register (0001h)      |                                      | 20h-23h |

|                                             | Rese                                    | rved                       |                                      | 24h-2Bh |

| Sub-system Dev                              | vice ID (0000h)                         | Sub-system Ve              | ndor ID (0000h)                      | 2Ch-2Fh |

|                                             | Expansion ROM Base Address (0000h)      |                            |                                      |         |

| Reserved                                    | Reserved                                | Reserved Cap. Pointer (80h |                                      | 34h-37h |

|                                             | Rese                                    | rved                       |                                      | 38h-3Bh |

| MAX_LAT (08h)                               | MIN_GNT (08h)                           | INTERRUPT PIN<br>(01h)     | INTERRUPT LINE<br>(00h)              | 3Ch-3Fh |

| IDE Virtual Channel<br>Exist Register (01h) | IDE Pad Driving<br>Current Register     | IDE I/O Configu            | uration Register                     | 40h-43h |

| Reserved                                    | PCI Burst Threshold (08h)               | Reserved                   | Primary PCI Burst<br>Threshold (08h) | 44h-47h |

| Reserved                                    | Reserved                                | PLL2 Control (02h)         | PLL1 Control (02h)                   | 48h-4Bh |

|                                             | IDE Bus Skew Control                    | Register (40044004h)       |                                      | 4Ch-4Fh |

| RAID Transfer Sec                           | tor Count (0000h)                       | RAID Control (00h)         | PCI Mode (01h)                       | 50h-53h |

| P-CH Device 1 Ultra<br>DMA Timing (31h)     | P-CH Device 0 Ultra<br>DMA Timing (31h) | Reserved                   | P-CH PIO/MDMA<br>Timing (A3h)        | 54h-57h |

| S-CH Device 1 Ultra<br>DMA Timing (31h)     | S-CH Device 0 Ultra<br>DMA Timing (31h) | Reserved                   | S-CH PIO/MDMA<br>Timing (A3h)        | 58h-5Bh |

| Reserved                                    | CPU Control (00h)                       | CPU NMI Control<br>(1Ah)   | Test Mode (00h)                      | 5Ch-5Fh |

|                                             | Rese                                    | rved                       |                                      | 60h-7Fh |

## IT8212F

## List of PCI Configuration Registers [cont'd]

| Power Management Capabilities (PMC) (02h) |                                                 | Next Item Pointer (0h) Capability ID ( |   | 80h-83h |

|-------------------------------------------|-------------------------------------------------|----------------------------------------|---|---------|

| Data (00h)                                | PMCSR_BSE Bridge<br>Support Extensions<br>(00h) | Power Management C<br>(PMCSR)          | • | 84h-87h |

|                                           | Rese                                            | rved                                   |   | 88h-FFh |

#### 6.1.3 List of PCI I/O Registers

Table 6-2. List of PCI I/O Register -- Bus Master IDE I/O Registers

| Register Name                                                                 | R/W  | Offset (note) | Default   | Register<br>Size |

|-------------------------------------------------------------------------------|------|---------------|-----------|------------------|

| Bus Master IDE Command Register for Primary Channel (BMICRP)                  | R/W  | 0x0           | 00h       | 8 bits           |

| Bus Master IDE Status Register for Primary Channel (BMISRP)                   | R/WC | 0x2           | 00h       | 8 bits           |

| Bus Master Descriptor Table Pointer Register for Primary Channel (BMIDTPRP)   | R/W  | 0x4           | 00000000h | 32 bits          |

| Bus Master IDE Command Register for Secondary Channel (BMICRS)                | R/W  | 0x8           | 00h       | 8 bits           |

| Bus Master IDE Status Register for Secondary Channel (BMISRS)                 | R/WC | 0xA           | 00h       | 8 bits           |

| Bus Master Descriptor Table Pointer Register for Secondary Channel (BMIDTPRS) | R/W  | 0xC           | 00000000h | 32 bits          |

(Note)The Base Address depends on Bus Master Base Address Register (BMBA).

Table 6-3. List of PCI I/O Register From Local CPU View-- Bus Master IDE I/O Registers

| Register Name                                                 | R/W | Address        | Default | Register<br>Size |

|---------------------------------------------------------------|-----|----------------|---------|------------------|

| Bus Master IDE Status Register for Primary Channel (BMISRP)   | WO  | 0x08052h(Note) | 00h     | 8 bits           |

| Bus Master IDE Status Register for Secondary Channel (BMISRS) | WO  | 0x0805Ah(Note) | 00h     | 8 bits           |

Note: Only Bit 2 (Interrupt bit) can be set by the local CPU.

Table 6-4. Virtual IDE Interface and Status Registers from PCI I/O View (PCI IO Space Mapping)

| Register Name                                                   | R/W | Offset          | Default | Register<br>Size |

|-----------------------------------------------------------------|-----|-----------------|---------|------------------|

| Primary IDE Data Register (VPDR)                                | R/W | 0x0 (Note 1)    | 0000h   | 16 bits          |

| Primary IDE Error/Feature Register (VPEFR)                      | R/W | 0x1(Note 1)     | 00h     | 8 bits           |

| Primary IDE Sector Count (Ext) Register (VPSCR)                 | R/W | 0x2 (Note 1, 5) | 00h     | 8 bits           |

| Primary IDE Sector Number (Ext) Register (VPSNR)                | R/W | 0x3 (Note 1, 5) | 00h     | 8 bits           |

| Primary IDE Cylinder Low (Ext) Register (VPCLR)                 | R/W | 0x4 (Note 1, 5) | 00h     | 8 bits           |

| Primary IDE Cylinder High (Ext) Register (VPCHR)                | R/W | 0x5 (Note1, 5)  | 00h     | 8 bits           |

| Primary IDE Device/Head Register (VPHDR)                        | R/W | 0x6 (Note1)     | 00h     | 8 bits           |

| Primary IDE Command/Status Register (VPCMR)                     | R/W | 0x7 (Note1)     | 00h     | 8 bits           |

| Primary IDE Device Control/Alternate Status Register (VPSTUR)   | R/W | 0x6 (Note2)     |         | 8 bits           |

| Secondary IDE Data Register (VSDR)                              | R/W | 0x0 (Note3)     | 0000h   | 16 bits          |

| Secondary IDE Error/Feature Register (VSEFR)                    | R/W | 0x1 (Note3)     | 00h     | 8 bits           |

| Secondary IDE Sector Count (Ext) Register (VSSCR)               | R/W | 0x2 (Note 3, 5) | 00h     | 8 bits           |

| Secondary IDE Sector Number (Ext) Register (VSSNR)              | R/W | 0x3 (Note 3, 5) | 00h     | 8 bits           |

| Secondary IDE Cylinder Low (Ext) Register (VSCLR)               | R/W | 0x4 (Note 3, 5) | 00h     | 8 bits           |

| Secondary IDE Cylinder High (Ext) Register (VSCHR)              | R/W | 0x5 (Note 3, 5) | 00h     | 8 bits           |

| Secondary IDE Device/Head Register (VSHDR)                      | R/W | 0x6 (Note 3)    | 00h     | 8 bits           |

| Secondary IDE Command /Status Register (VSCMR)                  | R/W | 0x7 (Note 3)    | 00h     | 8 bits           |

| Secondary IDE Device Control/Alternate Status Register (VSSTUR) | R/W | 0x6 (Note4)     |         | 8 bits           |

#### **Definition of R/W Attributes:**

**RO READ ONLY**. If a register is read only, writing will have no effect.

**R/W READ/WRITE**. A register with this attribute can be read and written.

**R/WC READ/WRITE CLEAR**. A register bit with this attribute can be read and written. However, a write of 1 clears the corresponding bit and a write of 0 will have no effect.

#### Notes:

- 1. The base address of the Primary IDE Command Registers is defined in PCI Configuration Register 10h~13h (Primary Channel Command Block Register)

- 2. The base address of the Primary IDE Control Register is defined in PCI Configuration Register 14h~17h (Primary Channel Control Block Register).

- 3. The base address of the Secondary IDE Command Register is defined in PCI Configuration Register 18h~1Bh (Secondary Channel Command Block Register).

- 4. The base address of the Secondary IDE Control Register is defined in PCI Configuration Register 1Ch~1Fh (Secondary Channel Control Block Register).

- 5. When the Primary/Secondary Device Control register bit 7 is set to 1, these registers are regarded as Extended registers, which are used for 48-bit address feature set.

### 6.1.4 List of Local CPU Access Registers

Table 6-5. Virtual IDE Interface and Status Registers from Local CPU View (CPU memory address mapping)

| Register Name                                       | R/W | Address | Default | Register<br>Size |

|-----------------------------------------------------|-----|---------|---------|------------------|

| Primary IDE Data Register (PDR)                     | R/W | 0x08000 | 0000h   | 16 bits          |

| Primary IDE Error Register (PEFR)                   | R/W | 0x08001 | 00h     | 8 bits           |

| Primary IDE Sector Count Register (PSCR)            | R/W | 0x08002 | 00h     | 8 bits           |

| Primary IDE Sector Number Register (PSNR)           | R/W | 0x08003 | 00h     | 8 bits           |

| Primary IDE Cylinder Low Register (PCLR)            | R/W | 0x08004 | 00h     | 8 bits           |

| Primary IDE Cylinder High Register (PCHR)           | R/W | 0x08005 | 00h     | 8 bits           |

| Primary IDE Device/Head Register (PHDR)             | R/W | 0x08006 | 00h     | 8 bits           |

| Primary IDE Status Register (PSTAR)                 | R/W | 0x08007 | 00h     | 8 bits           |

| Primary IDE Sector Counter Ext. Register (PSCEXR)   | R/W | A0080x0 | 00h     | 8 bits           |

| Primary IDE Sector Number Ext. Register (PSNEXR)    | R/W | 0x0800B | 00h     | 8 bits           |

| Primary IDE Cylinder Low Ext. Register (PCLEXR)     | R/W | 0x0800C | 00h     | 8 bits           |

| Primary IDE Cylinder High Ext. Register (PCHEXR)    | R/W | 0x0800D | 00h     | 8 bits           |

| Primary Feature Register (PFEAR)                    | R/W | 0x0800E | 00h     | 8 bits           |

| Primary Command Register (PCMR)                     | R/W | 0x0800F | 00h     | 8 bits           |

| Primary IDE Alternate Status Register (PSTUR)       | R/W | 0x08016 |         | 8 bits           |

| Primary IDE Device Control Status Register (PDCR)   | R/W | 0x0801A | 00h     | 8 bits           |

| Secondary IDE Data Register (SDR)                   | R/W | 0x08020 | 0000h   | 16 bits          |

| Secondary IDE Error/Feature Register (SEFR)         | R/W | 0x08021 | 00h     | 8 bits           |

| Secondary IDE Sector Count Register (SSCR)          | R/W | 0x08022 | 00h     | 8 bits           |

| Secondary IDE Sector Number Register (SSNR)         | R/W | 0x08023 | 00h     | 8 bits           |

| Secondary IDE Cylinder Low Register (SCLR)          | R/W | 0x08024 | 00h     | 8 bits           |

| Secondary IDE Cylinder High Register (SCHR)         | R/W | 0x08025 | 00h     | 8 bits           |

| Secondary IDE Device/Head Register (SHDR)           | R/W | 0x08026 | 00h     | 8 bits           |

| Secondary IDE Status Register (SCMR)                | R/W | 0x08027 | 00h     | 8 bits           |

| Secondary IDE Sector Counter Ext. Register (SSCEXR) | R/W | 0x0802A | 00h     | 8 bits           |

| Secondary IDE Sector Number Ext. Register (SSNEXR)  | R/W | 0x0802B | 00h     | 8 bits           |

| Secondary IDE Cylinder Low Ext. Register (SCLEXR)   | R/W | 0x0802C | 00h     | 8 bits           |

Table 6-5. Virtual IDE Interface and Status Registers from Local CPU View (CPU memory address mapping) [Cont'd]

| Register Name                                      | R/W | Address | Default | Register<br>Size |

|----------------------------------------------------|-----|---------|---------|------------------|

| Secondary IDE Cylinder High Ext. Register (SCHEXR) | R/W | 0x0802D | 00h     | 8 bits           |

| Secondary Feature Register (SFEAR)                 | R/W | 0x0802E | 00h     | 8 bits           |

| Secondary Command Register (SCMR)                  | R/W | 0x0802F | 00h     | 8 bits           |

| Secondary IDE Alternate Status Register (SSTUR)    | R/W | 0x08036 |         | 8 bits           |

| Secondary IDE Device Control Register (SDVR)       | R/W | 0x0803A | 00h     | 8 bits           |

Note: The registers of Table 6-4 and Table 6-5 are the same. They just have different address mapping between the CPU and PCI access.

Table 6-6. List of IDE Control Registers for Local CPU

| Register Name                                       | R/W | Address | Default | Register<br>Size |

|-----------------------------------------------------|-----|---------|---------|------------------|

| Primary IDE Transfer Counter Register (PIDETCR)     | R/W | 0x08100 | 0000h   | 16 bits          |

| Primary IDE Operation Register (PIDEOPR)            | R/W | 0x08102 | 00h     | 8 bits           |

| Primary IDE PIO and DMA Timing Register (PPIOTMR)   | R/W | 0x08103 | 00h     | 8 bits           |

| Primary IDE Ultra DMA Timing Register (PUDMATMR)    | R/W | 0x08104 | 00h     | 8 bits           |

| Primary FIFO Access Control Register (PFIFOCR)      | R/W | 0x08105 | 00h     | 8 bits           |

| Primary FIFO Status Register (PFIFOSR)              | RO  | 0x08106 | 80h     | 8 bits           |

| Primary FIFO Low Word Access Register (PFIFOLR)     | R/W | 0x08108 | 0000h   | 16 bits          |

| Primary FIFO High Word Access Register (PFIFOHR)    | R/W | 0x0810A | 0000h   | 16 bits          |

| Secondary IDE Transfer Counter Register (SIDETCR)   | R/W | 0x08110 | 0000h   | 16 bits          |

| Secondary IDE Operation Register (SIDEOPR)          | R/W | 0x08112 | 00h     | 8 bits           |

| Secondary IDE PIO and DMA Timing Register (SPIOTMR) | R/W | 0x08113 | 00h     | 8 bits           |

| Secondary IDE Ultra DMA Timing Register (PUDMATMR)  | R/W | 0x08114 | 00h     | 8 bits           |

| Secondary FIFO Access Control Register (SFIFOCR)    | R/W | 0x08115 | 00h     | 8 bits           |

| Secondary Status Control Register (SFIFOSR)         | RO  | 0x08116 | 80h     | 8 bits           |

| Secondary FIFO Low Word Access Register (SFIFOLR)   | R/W | 0x08118 | 0000h   | 16 bits          |

Table 6-6. List of IDE Control Registers for Local CPU[cont'd]

| Register Name                                      | R/W | Address | Default | Register<br>Size |

|----------------------------------------------------|-----|---------|---------|------------------|

| Secondary FIFO High Word Access Register (SFIFOHR) | R/W | 0x0811A | 0000h   | 16 bits          |

| Primary IDE Data Register (PDR)                    | R/W | 0x08120 | 0000h   | 16 bits          |

| Primary IDE Error/Feature Register (PEFR)          | R/W | 0x08121 | 00h     | 8 bits           |

| Primary IDE Sector Count Register (PSCR)           | R/W | 0x08122 | 00h     | 8 bits           |

| Primary IDE Sector Number Register (PSNR)          | R/W | 0x08123 | 00h     | 8 bits           |

| Primary IDE Cylinder Low Register (PCLR)           | R/W | 0x08124 | 00h     | 8 bits           |

| Primary IDE Cylinder High Register (PCHR)          | R/W | 0x08125 | 00h     | 8 bits           |

| Primary IDE Device/Head Register (PHDR)            | R/W | 0x08126 | 00h     | 8 bits           |

| Primary IDE Command Register (PCMR)                | R/W | 0x08127 | 00h     | 8 bits           |

| Primary IDE Alternate Status Register (PSTUR)      | R/W | 0x08136 |         | 8 bits           |

| Secondary IDE Data Register (SDR)                  | R/W | 0x08140 | 0000h   | 16 bits          |

| Secondary IDE Error/Feature Register (SEFR)        | R/W | 0x08141 | 00h     | 8 bits           |

| Secondary IDE Sector Count Register (SSCR)         | R/W | 0x08142 | 00h     | 8 bits           |

| Secondary IDE Sector Number Register (SSNR)        | R/W | 0x08143 | 00h     | 8 bits           |

| Secondary IDE Cylinder Low Register (SCLR)         | R/W | 0x08144 | 00h     | 8 bits           |

| Secondary IDE Cylinder High Register (SCHR)        | R/W | 0x08145 | 00h     | 8 bits           |

| Secondary IDE Device/Head Register (SHDR)          | R/W | 0x08146 | 00h     | 8 bits           |

| Secondary IDE Command Register (SCMR)              | R/W | 0x08147 | 00h     | 8 bits           |

| Secondary IDE Alternate Status Register (SSTUR)    | R/W | 0x08156 |         | 8 bits           |

| Primary Channel Transfer Count Register (PTCR)     | R/W | 0x08200 | 0000h   | 16 bits          |

| Primary Channel Operation Register (POPR)          | R/W | 0x08202 | 0000h   | 16 bits          |

| Secondary Channel Transfer Count Register (STCR)   | R/W | 0x08208 | 0000h   | 16 bits          |

| Secondary Channel Operation Register (SOPR)        | R/W | 0x0820A | 0000h   | 16 bits          |

| Rebuild Block Counter Register (RBCR)              | R/W | 0x08210 | 0000h   | 16 bits          |

| Rebuild Operation Register (RBOPR)                 | R/W | 0x08212 | 00h     | 8 bits           |

| Interrupt Pending Register (INTPR)                 | R/W | 0x08218 | 0000h   | 16 bits          |

| Interrupt Mask Register (INTMSR)                   | R/W | 0x0821A | FFF8h   | 16 bits          |

| End of Interrupt Register (EOIR)                   | R/W | 0x0821C | 00h     | 8 bits           |

| Timer 0 Control Register (T0CTLR)                  | R/W | 0x08230 | 00h     | 8 bits           |

| Timer 0 Count Register (T0CNTR)                    | RO  | 0x08232 | 0000h   | 16 bits          |

| Timer 0 Max. Count Register (T0MAXR)               | R/W | 0x08234 | FFFFh   | 16 bits          |

| Timer 1 Control Register (T1CTLR)                  | R/W | 0x08238 | 00h     | 8 bits           |

| Timer 1 Count Register (T1CNTR)                    | RO  | 0x0823A | 0000h   | 16 bits          |

Table 6-6. List of IDE Control Registers for Local CPU [cont'd]

| Name                                   | R/W | Address | Default | Register<br>Size |

|----------------------------------------|-----|---------|---------|------------------|

| Timer 1 Max. Count Register (T1MAXR)   | R/W | 0x0823C | FFFFh   | 16 bits          |

| IDE Clock Frequency Register (IDECLKR) | R/W | 0x08252 | 00h     | 8 bits           |

| GPIO Register (GPIOR)                  | R/W | 0x08254 | 00h     | 8 bits           |

#### 6.1.5 List of UART Registers

Table 6-7. List of UART Registers

| Register Name                                 | R/W | Address         | Default | Register<br>Size |

|-----------------------------------------------|-----|-----------------|---------|------------------|

| UART Receiver Buffer Register (URBR)          | RO  | 0x09000         | -       | 8 bits           |

|                                               |     | DLAB=0*Note1    |         |                  |

| UART Transmitter Buffer Register (UTBR)       | WO  | 0x09000         | -       | 8 bits           |

|                                               |     | DLAB=0*Note1    |         |                  |

| UART Interrupt Enable Register (UIER)         | R/W | 0x09002         | 00h     | 8 bits           |

|                                               |     | DLAB=0*Note1    |         |                  |

| UART Interrupt Identification Register (UIIR) | RO  | 0x09004         | 01h     | 8 bits           |

| UART FIFO Control Register (UFCR)             | WO  | 0x09004         | 00h     | 8 bits           |

| UART Line Control Register (ULCR)             | R/W | 0x09006         | 00h     | 8 bits           |

| UART Line Status Register (ULSR)              | R/W | 0x0900A         | 60h     | 8 bits           |

| UART Divisor Latch LSB Register (UDLL)        | R/W | 0x09000(Note 1) | 00h     | 8 bits           |

| UART Divisor Latch MSB Register (UDLM)        | R/W | 0x09002(Note1)  | 00h     | 8 bits           |

#### **Definition of R/W Attributes:**

**RO READ ONLY**. If a register is read only, writing will have no effect.

**R/W READ/WRITE**. A register with this attribute can be read and written.

**WO WRITE ONLY**. If a register is written only, the data written to this register cannot be read from this register.

Note: The registers are valuable when bit 7 (DLAB) of the UART Line Control Register is 1.

#### 6.1.6 PCI Configuration Registers Definition

### 6.1.6.1 Vendor ID Register (VIDR) — Offset 0x0

| Bit  | R/W | Default | Description                                                              |

|------|-----|---------|--------------------------------------------------------------------------|

| 15-0 | RO  | 1283h   | Vendor ID (VID)                                                          |

|      |     |         | This is a 16-bit value assigned to the ITE IDE RAID Controller function. |

### 6.1.6.2 Device ID Register (DIDR) — Offset 0x2

| Bit  | R/W | Default | Description                                                              |

|------|-----|---------|--------------------------------------------------------------------------|

| 15-0 | RO  | 8212h   | Device ID (DID)                                                          |

|      |     |         | This is a 16-bit value assigned to the ITE IDE RAID Controller function. |

### 6.1.6.3 Command Register (CMDR) — Offset 0x4

| Bit  | R/W | Default | Description                                         |

|------|-----|---------|-----------------------------------------------------|

| 15-7 | -   | 0h      | Reserved                                            |

| 6    | RO  | 0h      | Parity Error Response (PER)                         |

|      |     |         | 1: Enabled                                          |

|      |     |         | 0: Disabled                                         |

| 5-3  | -   | 0h      | Reserved                                            |

| 2    | R/W | 0h      | DMA Bus Master Enable (DBME)                        |

|      |     |         | 1: Enabled                                          |

|      |     |         | 0: Disabled                                         |

| 1    | R/W | 0h      | Memory Access Enable                                |

|      |     |         | 1: Allow the chip to respond to I/O space accesses. |

|      |     |         | 0: Disable I/O space accesses.                      |

| 0    | R/W | 0h      | I/O Access Enable (IOAE)                            |

|      |     |         | 1: Allow the chip to respond to I/O space accesses. |

|      |     |         | 0: Disable I/O space accesses.                      |

www.ite.com.tw 21 IT8212F V0.3

## 6.1.6.4 Device Status Register (DSTR) — Offset 0x6

| Bit   | R/W  | Default | Description                                                                                                                                                                                                                                                        |

|-------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-14 | -    | 0h      | Reserved                                                                                                                                                                                                                                                           |

| 13    | R/WC | 0h      | Master Abort Status (MAST)  This bit is set to high when the IDE RAID Controller acts as a PCI master and has issued a Master-Abort.  Write 1 to clear this bit.                                                                                                   |

| 12    | R/WC | 0h      | Received Target Abort (RTA)  This bit is set to high when the IDE RAID controller is a PCI master and the PCI transaction is terminated by receiving a Target-Abort.  Write 1 to clear this bit.                                                                   |

| 11    | R/WC | 0h      | Signal Target Abort (STA)  This bit is set to high when the IDE RAID controller is a PCI target and has terminated the PCI transaction with a Target-Abort.  Writing 1 to this bit to clear it.                                                                    |

| 10-9  | RO   | 1h      | DEVSEL Timing (DEVT[1:0])  Medium timing is selected for DEVSEL# assertion when the PCI target performs the positive decode.                                                                                                                                       |

| 8     | -    | 0h      | Reserved                                                                                                                                                                                                                                                           |

| 7     | RO   | 0h      | Fast Back-to-Back Capable (FBC) Always read as 0. Not supported                                                                                                                                                                                                    |

| 6     | -    | 0h      | Reserved                                                                                                                                                                                                                                                           |

| 5     | RO   | 1h      | 66 MHz Capable A "1" indicates that the function supports 66 MHz. A "0" indicates that the function just supports 33 MHz.                                                                                                                                          |