# 16Meg x 16 256-MBIT DDR SDRAM

#### **FEATURES**

- Clock Frequency: 200, 166 MHz

- Power supply (VDD and VDDQ)

DDR 333: 2.5V ± 0.2V

DDR 400: 2.6V + 0.1V

- SSTL 2 interface

- Four internal banks to hide row Pre-charge and Active operations

- Commands and addresses register on positive clock edges (CK)

- Bi-directional Data Strobe signal for data capture

- Differential clock inputs (CK and CK) for two data accesses per clock cycle

- Data Mask feature for Writes supported

- DLL aligns data I/O and Data Strobe transitions with clock inputs

- Half-strength and Full-strength drive strength options

- Programmable burst length for Read and Write operations

- Programmable CAS Latency (2, 2.5, or 3 clocks)

- Programmable burst sequence: sequential or interleaved

- Burst concatenation and truncation supported for maximum data throughput

- Auto Pre-charge option for each Read or Write burst

- 8192 refresh cycles every 64ms

- Auto Refresh and Self Refresh Modes

- Pre-charge Power Down and Active Power Down Modes

- Lead-free available

# PRELIMINARY INFORMATION NOVEMBER 2005

# **DEVICE OVERVIEW**

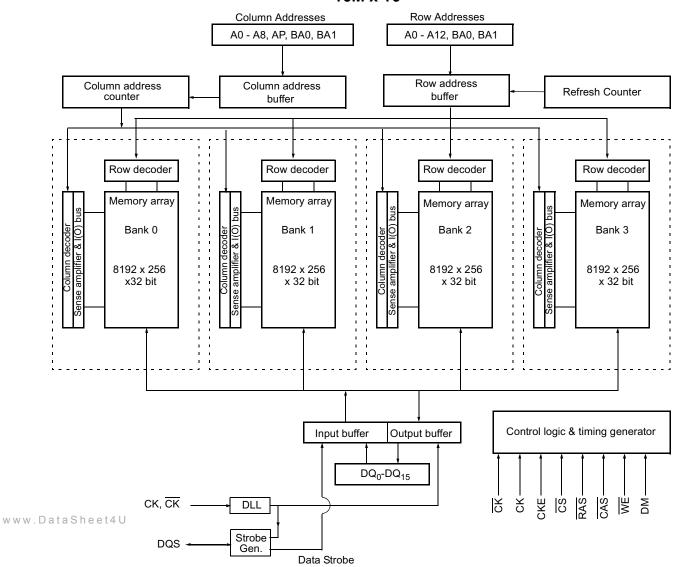

ISSI's 256-Mbit DDR SDRAM achieves high-speed data transfer using pipeline architecture and two data word accesses per clock cycle. The 268,435,456-bit memory array is internally organized as four banks of 64M-bit to allow concurrent operations. The pipeline allows Read and Write burst accesses to be virtually continuous, with the option to concatenate or truncate the bursts. The programmable features of burst length, burst sequence and CAS latency enable further advantages. The device is available in 16-bit data word size. Input data is registered on the I/O pins on both edges of Data Strobe signal(s), while output data is referenced to both edges of Data Strobe and both edges of CK. Commands are registered on the positive edges of CK. Auto Refresh, Active Power Down, and Pre-charge Power Down modes are enabled by using clock enable (CKE) and other inputs in an industry-standard sequence. All input and output voltage levels are compatible with SSTL 2.

#### **KEY TIMING PARAMETERS**

| Parameter         | -5     | -6     | Unit |

|-------------------|--------|--------|------|

|                   | DDR400 | DDR333 |      |

| Clock Cycle Time  |        |        |      |

| CAS Latency = 3   | 5      | 6      | ns   |

| CAS Latency = 2.5 | 6      | 6      | ns   |

| CAS Latency = 2   | 7.5    | 7.5    | ns   |

| Clock Frequency   |        |        |      |

| CAS Latency = 3   | 200    | 166    | MHz  |

| CAS Latency = 2.5 | 166    | 166    | MHz  |

| CAS Latency = 2   | 133    | 133    | MHz  |

Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

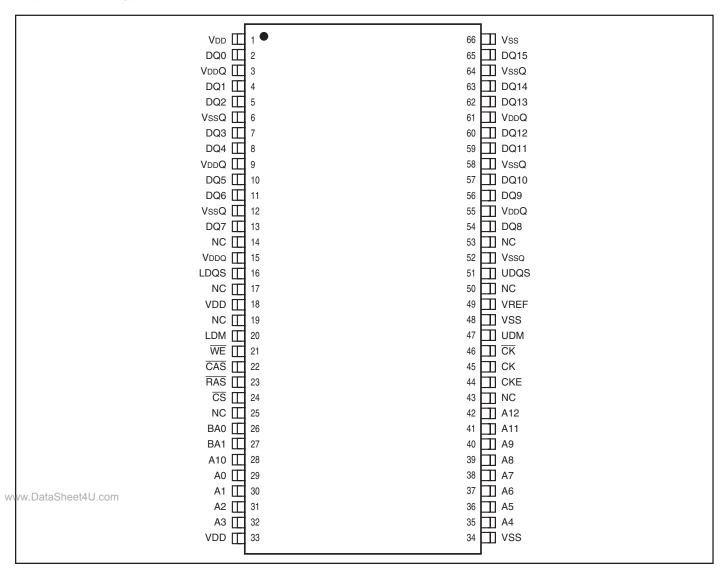

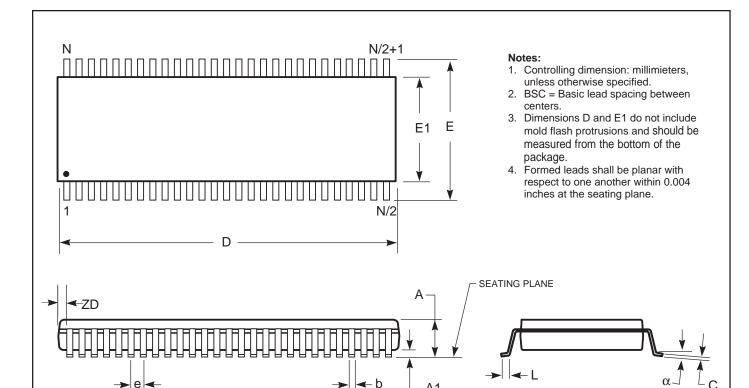

# PIN CONFIGURATIONS 66 pin TSOP - Type II for x16

### PIN DESCRIPTIONS

| A0-A12            | Row Address Input             |

|-------------------|-------------------------------|

| A0-A8             | Column Address Input          |

| BA0, BA1          | Bank Select Address           |

| DQ0 to DQ15       | Data I/O                      |

| CK, <del>CK</del> | System Clock Input            |

| CKE               | Clock Enable                  |

| CS                | Chip Select                   |

| RAS               | Row Address Strobe Command    |

| CAS               | Column Address Strobe Command |

| WE              | Write Enable             |

|-----------------|--------------------------|

| LDM, UDM        | x16 Input Mask           |

| LDQS, UDQS      | Data Strobe              |

| V <sub>DD</sub> | Power                    |

| Vss             | Ground                   |

| VDDQ            | Power Supply for I/O Pin |

| Vssq            | Ground for I/O Pin       |

| VREF            | Input Reference Voltage  |

| NC              | No Connection            |

# **PIN FUNCTIONS**

| Symbol                    | Туре             | Function (In Detail)                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A12                    | Input Pin        | Address inputs are sampled during several commands. During an Active command, A0-A12 select a row to open. During a Read or Write command, A0-A8 select a starting column for a burst. During a Pre-charge command, A10 determines whether all banks are to be pre-charged, or a single bank. During a Load Mode Register command, the address inputs select an operating mode.                                                                    |

| BA0, BA1                  | Input Pin        | Bank Address inputs are used to select a bank during Active, Pre-charge, Read, or Write commands. During a Load Mode Register command, BA0 and BA1 are used to select between the Base or Extended Mode Register                                                                                                                                                                                                                                   |

| CAS                       | Input Pin        | CAS is Column Access Strobe, which is an input to the device command along with RAS and WE. See "Command Truth Table" for details.                                                                                                                                                                                                                                                                                                                 |

| CKE                       | Input Pin        | Clock Enable: CKE High activates and CKE Low de-activates internal clock signals and input/output buffers. When CKE goes Low, it can allow Self Refresh, Pre-charge Power Down, and Active Power Down. CKE must be High during entire Read and Write accesses. Input buffers except CK, CK, and CKE are disabled during Power Down. CKE uses an SSTL 2 input, but will detect a LVCMOS Low level after VDD is applied.                             |

| CK, CK                    | Input Pin        | All address and command inputs are sampled on the rising edge of the clock input CK and the falling edge of the differential clock input $\overline{\text{CK}}$ .  Output data is referenced from the crossings of CK and $\overline{\text{CK}}$ .                                                                                                                                                                                                 |

| CS                        | Input Pin        | The Chip Select input enables the Command Decoding block of the device. When $\overline{\textbf{CS}}$ is disabled, a NOP occurs. See "Command Truth Table" for details. Multiple DDR SDRAM devices can be managed with $\overline{\textbf{CS}}$ .                                                                                                                                                                                                  |

| LDM, UDM                  | Input Pin        | These are the Data Mask inputs. During a Write operation, the Data Mask input allows masking of the data bus. DM is sampled on each edge of DQS. There are two Data Mask input pins for the x16 DDR SDRAM. Each input applies to DQ0-DQ7, or DQ8-DQ15.                                                                                                                                                                                             |

| LDQS, UDQS ataSheet4U.com | Input/Output Pin | These are the Data Strobe inputs. The Data Strobe is used for data capture. During a Read operation, the DQS output signal from the device is edgealigned with valid data on the data bus. During a Write operation, the DQS input should be issued to the DDR SDRAM device when the input values on DQ inputs are stable. There are two Data Strobe pins for the x16 DDR SDRAM. Each of the two Data Strobe pins applies to DQ0-DQ7, or DQ8-DQ15. |

| DQ0-DQ15                  | Input/Output Pin | The pins DQ0 to DQ15 represent the data bus. For Write operations, the data bus is sampled on Data Strobe. For Read operations, the data bus is sampled on the crossings of CK and CK.                                                                                                                                                                                                                                                             |

| NC                        | _                | No Connect: This pin should be left floating. These pins could be used for 256Mbit or higher density DDR SDRAM.                                                                                                                                                                                                                                                                                                                                    |

| RAS                       | Input Pin        | RAS is Row Access Strobe, which is an input to the device command along with CAS and WE. See "Command Truth Table" for details.                                                                                                                                                                                                                                                                                                                    |

| WE                        | Input Pin        | WE is Write Enable, which is an input to the device command along with RAS and CAS. See "Command Truth Table" for details.                                                                                                                                                                                                                                                                                                                         |

| VDDQ                      | Power Supply Pin | VDDQ is the output buffer power supply.                                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD                       | Power Supply Pin | VDD is the device power supply.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VREF                      | Power Supply Pin | VREF is the reference voltage for SSTL 2.                                                                                                                                                                                                                                                                                                                                                                                                          |

| VSSQ                      | Power Supply Pin | VSSQ is the output buffer ground.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VSS                       | Power Supply Pin | VSS is the device ground.                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### **Block Diagram**

# 16M x 16

# Capacitance\*

$T_A$  = 0 to 70°C,  $V_{CC}$  = 2.5V  $\pm$  0.2V,  $V_{CC}$  = 2.6V  $\pm$  0.1V for DDR400, f = 1 Mhz

| Input Capacitance                         | Symbol           | Min | Max | Unit |

|-------------------------------------------|------------------|-----|-----|------|

| BA0, BA1, CKE, CS, RAS, (CAS, A0-A11, WE) | C <sub>INI</sub> | 2   | 3.0 | pF   |

| Input Capacitance (CK, CK)                | C <sub>IN2</sub> | 2   | 3.0 | pF   |

| Data & DQS I/O Capacitance                | C <sub>OUT</sub> | 4   | 5   | pF   |

| Input Capacitance (DM)                    | C <sub>IN3</sub> | 4   | 5.0 | pF   |

<sup>\*</sup>Note: Capacitance is sampled and not 100% tested.

# Absolute Maximum Ratings\*

| Absolute Maximum Natings                                               |

|------------------------------------------------------------------------|

| Operating temperature range 0 to 70 °C                                 |

| Storage temperature range55 to 150 °C                                  |

| V <sub>DD</sub> Supply Voltage Relative to V <sub>SS</sub> 1V to +3.6V |

| V <sub>DDO</sub> Supply Voltage Relative to V <sub>SS</sub>            |

| 1V to +3.6V                                                            |

| VREF and Inputs Voltage Relative to V <sub>SS</sub>                    |

| 1V to +3.6V                                                            |

| I/O Pins Voltage Relative to V <sub>SS</sub>                           |

| 0.5V to V <sub>DDQ</sub> +0.5V                                         |

| Power dissipation 1.6 W                                                |

| Data out current (short circuit)50 mA                                  |

|                                                                        |

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Functional Description

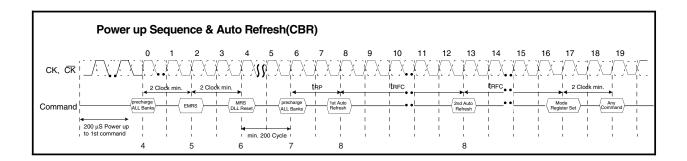

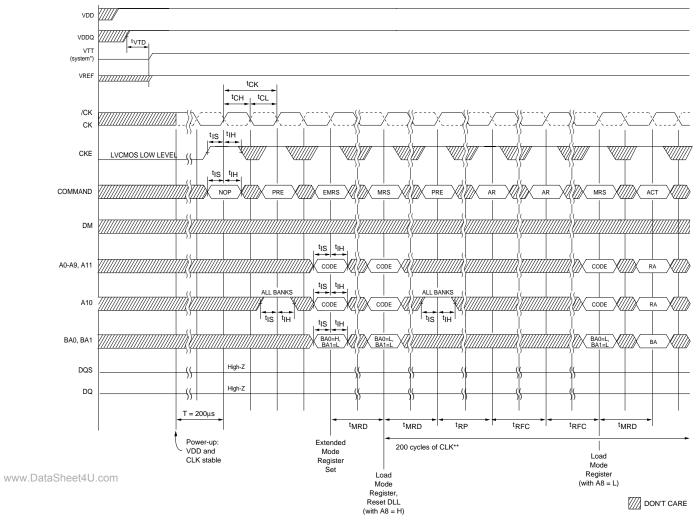

# ■ Power-Up Sequence

The following sequence is required for POWER UP.

- 1. Apply power and attempt to maintain CKE at a low state (all other inputs may be undefined.)

- Apply VDD before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT & Vref.

- 2. Start clock and maintain stable condition for a minimum of 200us.

- 3. The minimum of 200us after stable power and clock (CLK, CLK), apply NOP & take CKE high.

- 4. Precharge all banks.

- 5. Issue EMRS to enable DLL.(To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low" to all of the rest address pins, A1~A11 and BA1)

- 6. Issue a mode register set command for "DLL reset". The additional 200 cycles of clock input is required to lock the DLL. (To issue DLL reset command, provide "High" to A8 and "Low" to BA0)

- 7. Issue precharge commands for all banks of the device.

- 8. Issue 2 or more auto-refresh commands.

- 9. Issue a mode register set command to initialize device operation.

Note1 Every "DLL enable" command resets DLL. Therefore sequence 6 can be skipped during power up. Instead of it, the additional 200 cycles of clock input is required to lock the DLL after enabling DLL.

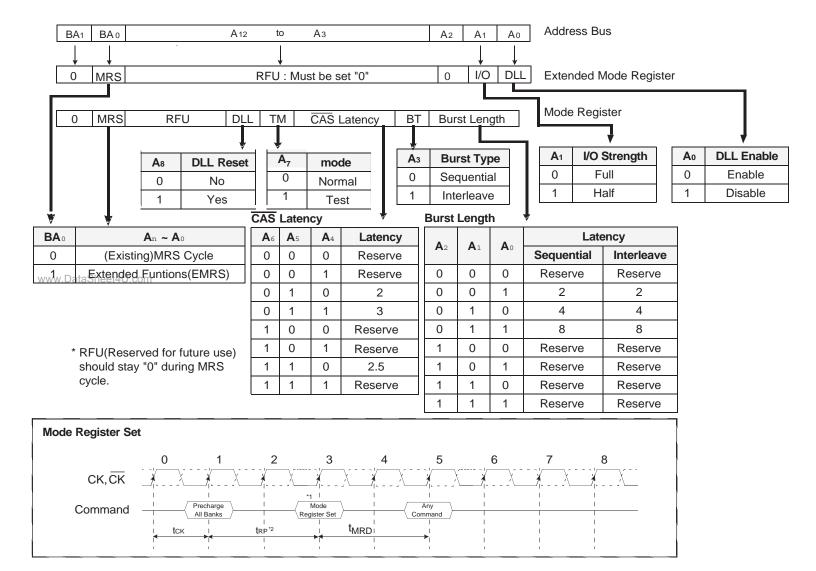

# www.DataSheet4U.com Extended Mode Register Set (EMRS)

The extended mode register stores the data for enabling or disabling DLL. The default value of the extended mode register is not defined, therefore the extended mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and high on BA $_0$  (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register). The state of address pins  $A_0 \sim A_{12}$  and  $\overline{BA}_1$  in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  low is written in the extended mode register. Two clock cycles are required to complete the write operation in the extended mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state.  $A_0$  is used for DLL enable or disable. "High" on  $BA_0$  is used for EMRS. All the other address pins except  $A_0$  and  $BA_0$  must be set to low for proper EMRS operation.  $A_1$  is used at EMRS to indicate I/O strength  $A_1 = 0$  full strength,  $A_1 = 1$  half strength. Refer to the table for specific codes.

# Mode Register Set (MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs  $\overline{CAS}$  latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make DDR SDRAM useful for a variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after  $\overline{EMRS}$  setting for proper DDR SDRAM operation. The mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and  $\overline{BA}_0$  (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register). The state of address pins  $A_0 \sim A_{12}$  in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and  $\overline{BA}_0$  low is written in the mode register. Two clock cycles are required to meet  $t_{MRD}$  spec. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses  $A_0 \sim A_2$ , addressing mode uses  $A_3$ ,  $\overline{CAS}$  latency (read latency from column address) uses  $A_4 \sim A_6$ .  $A_7$  is a specific test mode during production test.  $A_8$  is used for DLL reset.  $A_7$  must be set to low for normal MRS operation. Refer to the table for specific codes for various burst length, addressing modes and  $\overline{CAS}$  latencies.

- 1. MRS can be issued only at all banks precharge state.

- 2. Minimum tRP is required to issue MRS command.

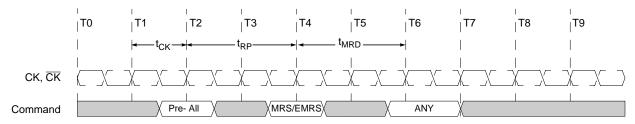

# Mode Register Set Timing

Mode Register set (MRS) or Extended Mode Register Set (EMRS) can be issued only when all banks are in the idle state.

If a MRS command is issued to reset the DLL, then an additional 200 clocks must occur prior to issuing any new command to allow time for the DLL to lock onto the clock.

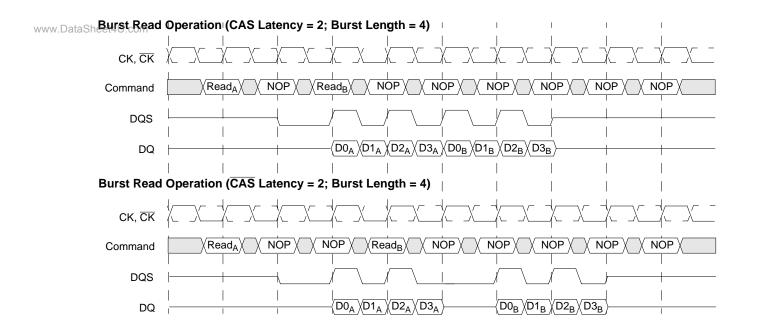

## **Burst Mode Operation**

Burst Mode Operation is used to provide a constant flow of data to memory locations (Write cycle), or from memory locations (Read cycle). Two parameters define how the burst mode will operate: burst sequence and burst length. These parameters are programmable and are determined by address bits  $A_0$ — $A_3$  during the Mode Register Set command. Burst type defines the sequence in which the burst data will be delivered or stored to the SDRAM. Two types of burst sequence are supported: sequential and interleave. The burst length controls the number of bits that will be output after a Read command, or the number of bits to be input after a Write command. The burst length can be programmed to values of 2, 4, or 8. See the Burst Length and Sequence table below for programming information.

# **Burst Length and Sequence**

| Burst Length        | Starting Length (A <sub>2</sub> , A <sub>1</sub> , A <sub>0</sub> ) | Sequential Mode        | Interleave Mode        |

|---------------------|---------------------------------------------------------------------|------------------------|------------------------|

| 2                   | xx0                                                                 | 0, 1                   | 0, 1                   |

| 2                   | xx1                                                                 | 1, 0                   | 1, 0                   |

|                     | x00                                                                 | 0, 1, 2, 3             | 0, 1, 2, 3             |

| 4                   | x01                                                                 | 1, 2, 3, 0             | 1, 0, 3, 2             |

| www.DataSheet4U.com | x10                                                                 | 2, 3, 0, 1             | 2, 3, 0, 1             |

|                     | x11                                                                 | 3, 0, 1, 2             | 3, 2, 1, 0             |

|                     | 000                                                                 | 0,1, 2, 3, 4, 5, 6, 7  | 0,1, 2, 3, 4, 5, 6, 7  |

|                     | 001                                                                 | 1, 2, 3, 4, 5, 6, 7, 0 | 1, 0, 3, 2, 5, 4, 7, 6 |

|                     | 010                                                                 | 2, 3, 4, 5, 6, 7, 0, 1 | 2, 3, 0, 1, 6, 7, 4, 5 |

| 0                   | 011                                                                 | 3, 4, 5, 6, 7, 0, 1, 2 | 3, 2, 1, 0, 7, 6, 5, 4 |

| 8                   | 100                                                                 | 4, 5, 6, 7, 0, 1, 2, 3 | 4, 5, 6, 7, 0, 1, 2, 3 |

|                     | 101                                                                 | 5, 6, 7, 0, 1, 2, 3, 4 | 5, 4, 7, 6, 1, 0, 3, 2 |

|                     | 110                                                                 | 6, 7, 0, 1, 2, 3, 4, 5 | 6, 7, 4, 5, 2, 3, 0, 1 |

|                     | 111                                                                 | 7, 0, 1, 2, 3, 4, 5, 6 | 7, 6, 5, 4, 3, 2, 1, 0 |

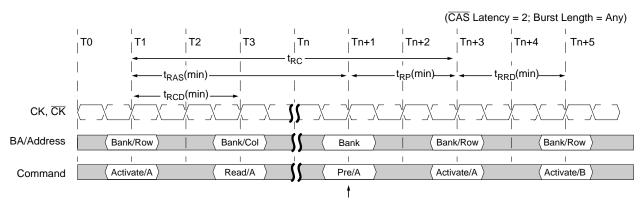

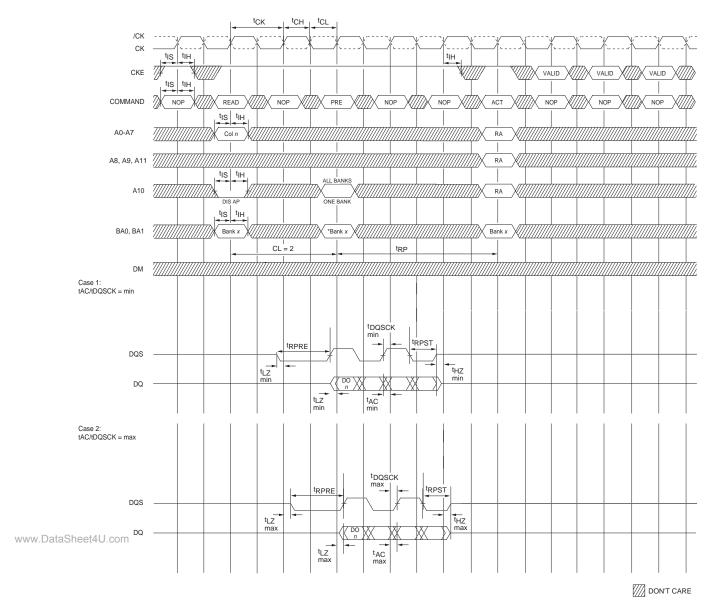

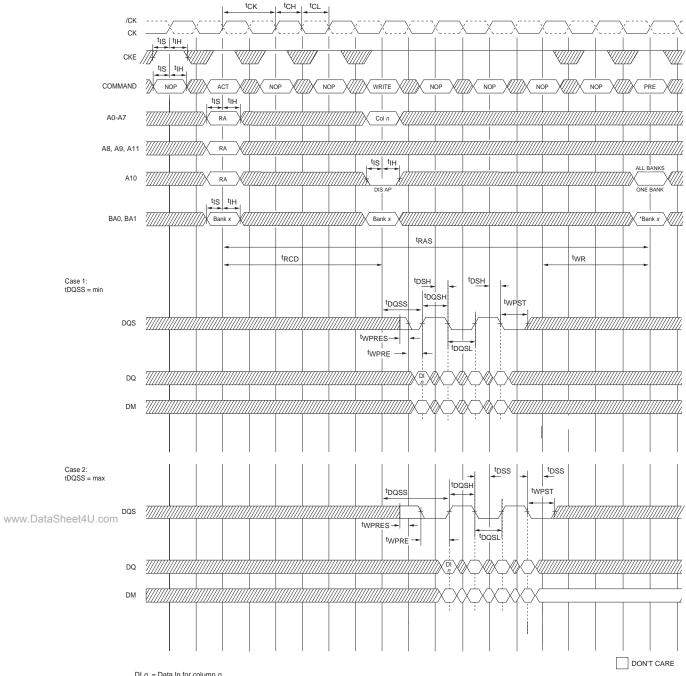

#### Bank Activate Command

The Bank Activate command is issued by holding  $\overline{CAS}$  and  $\overline{WE}$  high with  $\overline{CS}$  and  $\overline{RAS}$  low at the rising edge of the clock. The DDR SDRAM has four independent banks, so two Bank Select addresses (BA $_0$  and BA $_1$ ) are supported. The Bank Activate command must be applied before any Read or Write operation can be executed. The delay from the Bank Activate command to the first Read or Write command must meet or exceed the minimum  $\overline{RAS}$  to  $\overline{CAS}$  delay time (t $_{RCD}$  min). Once a bank has been activated, it must be precharged before another Bank Activate command can be applied to the same bank. The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time (t $_{RRD}$  min).

# **Bank Activation Timing**

Begin Precharge Bank A

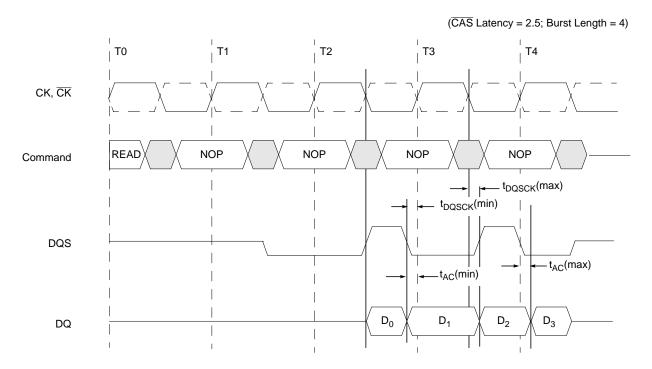

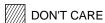

#### Read Operation

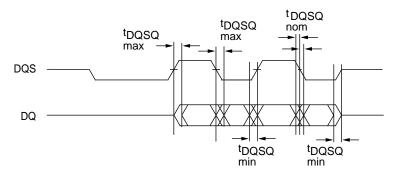

With the DLL enabled, all devices operating at the same frequency within a system are ensured to have the same timing relationship between DQ and DQS relative to the CK input regardless of device density, process variation, or technology generation.

The data strobe signal (DQS) is driven off chip simultaneously with the output data (DQ) during each read cycle. The same internal clock phase is used to drive both the output data and data strobe signal off chip to www.Dataminimize skew between data strobe and output data. This internal clock phase is nominally aligned to the input differential clock (CK, CK) by the on-chip DLL. Therefore, when the DLL is enabled and the clock frequency is within the specified range for proper DLL operation, the data strobe (DQS), output data (DQ), and the system clock (CK) are all nominally aligned.

Since the data strobe and output data are tightly coupled in the system, the data strobe signal may be delayed and used to latch the output data into the receiving device. The tolerance for skew between DQS and DQ ( $t_{DQSO}$ ) is tighter than that possible for CK to DQ ( $t_{AC}$ ) or DQS to CK ( $t_{DQSCK}$ ).

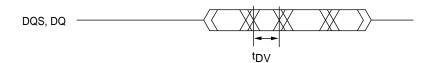

# Output Data (DQ) and Data Strobe (DQS) Timing Relative to the Clock (CK) During Read Cycles

The minimum time during which the output data (DQ) is valid is critical for the receiving device (i.e., a memory controller device). This also applies to the data strobe during the read cycle since it is tightly coupled to the output data. The minimum data output valid time  $(t_{DV})$  and minimum data strobe valid time  $(t_{DQSV})$  are derived from the minimum clock high/low time minus a margin for variation in data access and hold time due to DLL jitter and power supply noise.

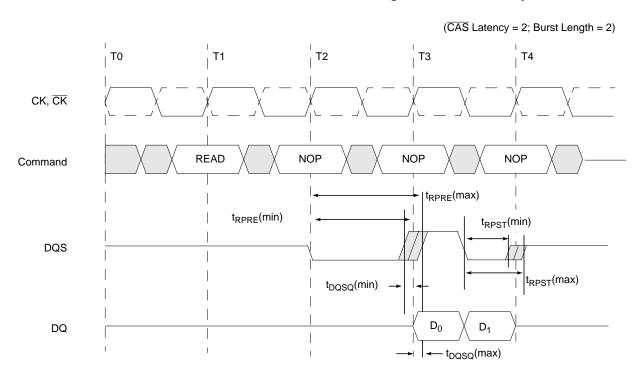

#### Read Preamble and Postamble Operation

Prior to a burst of read data and given that the controller is not currently in burst read mode, the data strobe www.Datsignal/(DQS), must transition from Hi-Z to a valid logic low. The is referred to as the data strobe "read preamble" (t<sub>RPRE</sub>). This transition from Hi-Z to logic low nominally happens one clock cycle prior to the first edge of valid data

Once the burst of read data is concluded and given that no subsequent burst read operations are initiated, the data strobe signal (DQS) transitions from a logic low level back to Hi-Z. This is referred to as the data strobe "read postamble" (t<sub>RPST</sub>). This transition happens nominally one-half clock period after the last edge of valid data.

Consecutive or "gapless" burst read operations are possible from the same DDR SDRAM device with no requirement for a data strobe "read" preamble or postamble in between the groups of burst data. The data strobe read preamble is required before the DDR device drives the first output data off chip. Similarly, the data strobe postamble is initiated when the device stops driving DQ data at the termination of read burst cycles.

# Data Strobe Preamble and Postamble Timings for DDR Read Cycles

# Consecutive Burst Read Operation and Effects on the Data Strobe Preamble and Postamble

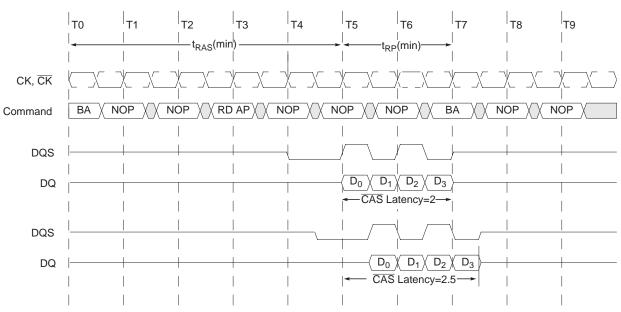

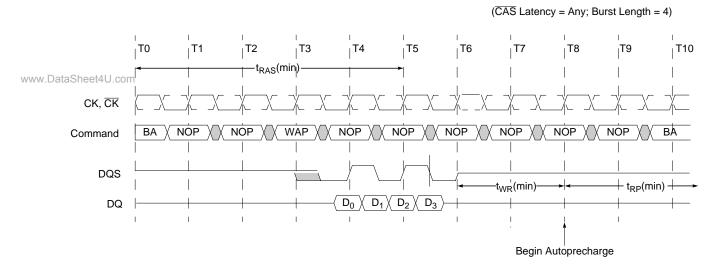

# **Auto Precharge Operation**

The Auto Precharge operation can be issued by having column address  $A_{10}$  high when a Read or Write command is issued. If  $A_{10}$  is low when a Read or Write command is issued, then normal Read or Write burst operation is executed and the bank remains active at the completion of the burst sequence. When the Auto Precharge command is activated, the active bank automatically begins to precharge at the earliest possible moment during the Read or Write cycle once  $t_{RAS}$ (min) is satisfied.

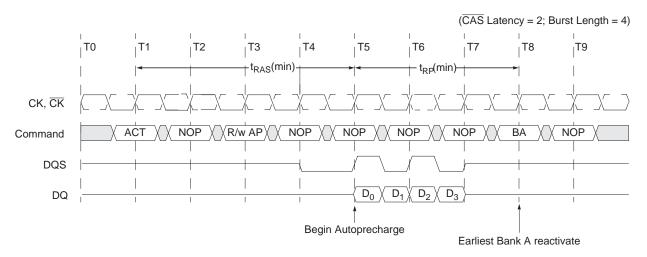

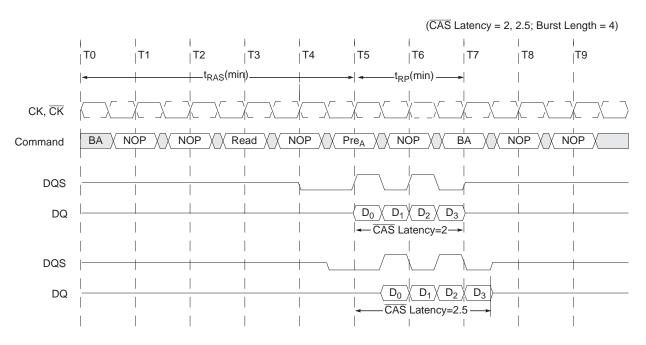

## **Read with Auto Precharge**

If a Read with Auto Precharge command is initiated, the DDR SDRAM will enter the precharge operation N-clock cycles measured from the last data of the burst read cycle where N is equal to the CAS latency programmed into the device. Once the autoprecharge operation has begun, the bank cannot be reactivated until the minimum precharge time ( $t_{RP}$ ) has been satisfied.

# Read with Autoprecharge Timing

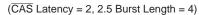

# Read with Autoprecharge Timing as a Function of CAS Latency

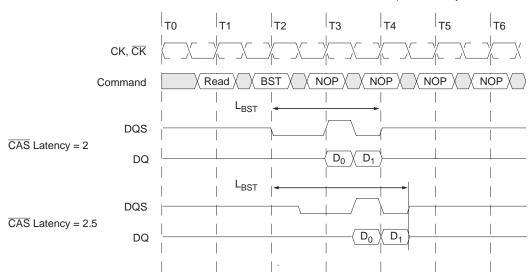

# **Precharge Timing During Read Operation**

For the earliest possible Precharge command without interrupting a Read burst, the Precharge command may be issued on the rising clock edge which is  $\overline{\text{CAS}}$  latency (CL) clock cycles before the end of the Read burst. A new Bank Activate (BA) command may be issued to the same bank after the  $\overline{\text{RAS}}$  precharge time ( $t_{\text{RP}}$ ). A Precharge command can not be issued until  $t_{\text{RAS}}$ (min) is satisfied.

# Read with Precharge Timing as a Function of CAS Latency

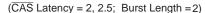

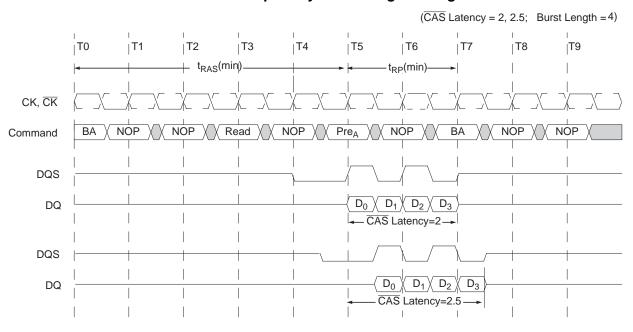

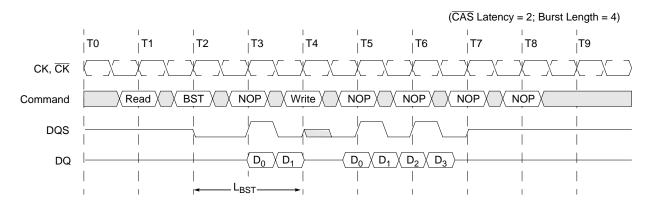

# **Burst Stop Command**

The Burst Stop command is valid only during burst read cycles and is initiated by having RAS and CAS high with CS and WE low at the rising edge of the clock. When the Burst Stop command is issued during a burst Read cycle, both the output data (DQ) and data strobe (DQS) go to a high impedance state after a delay (L<sub>BST</sub>) equal to the CAS latency programmed into the device. If the Burst Stop command is issued during a burst Write cycle, the command will be treated as a NOP command.

# Read Terminated by Burst Stop Command Timing

#### Read Interrupted by a Precharge

A Burst Read operation can be interrupted by a precharge of the same bank. The Precharge command to Output Disable latency is equivalent to the CAS latency.

# Read Interrupted by a Precharge Timing

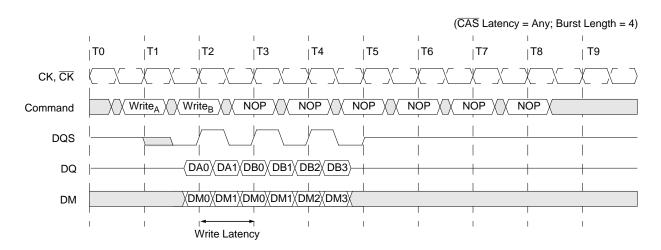

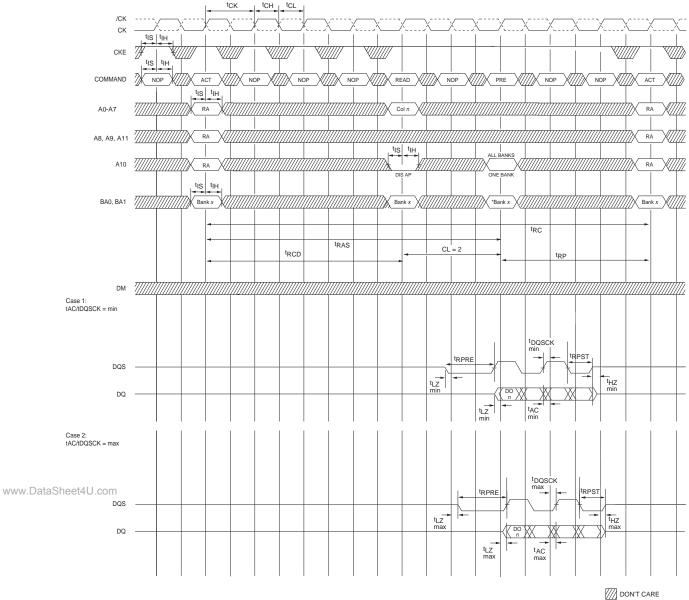

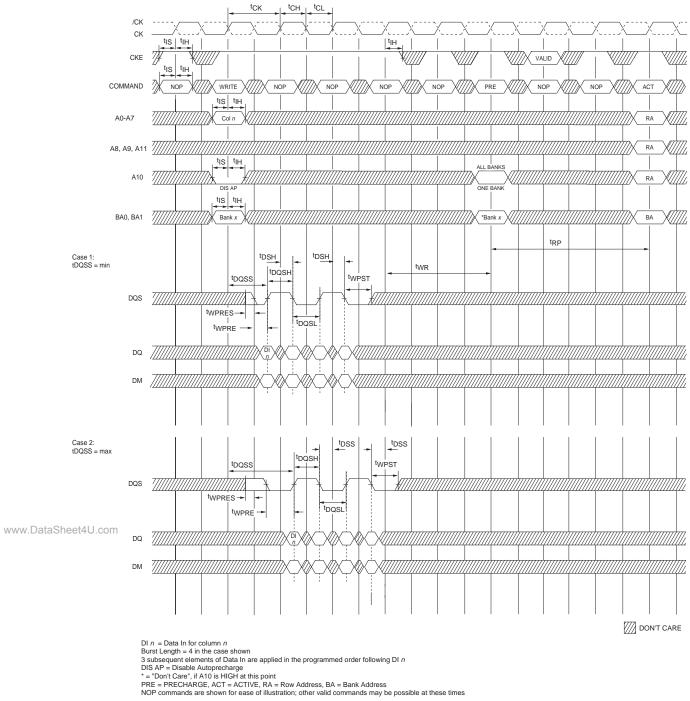

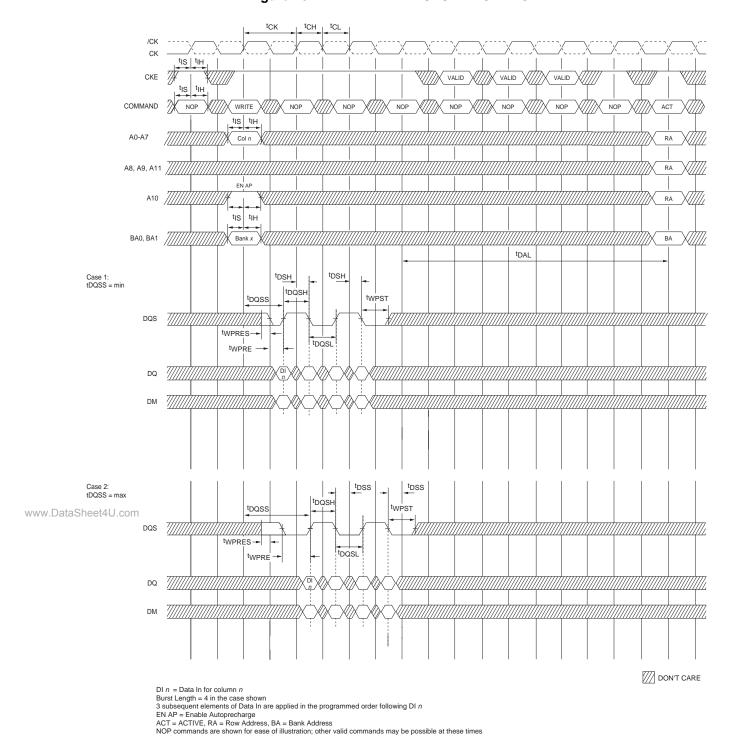

**Burst Write Operation**

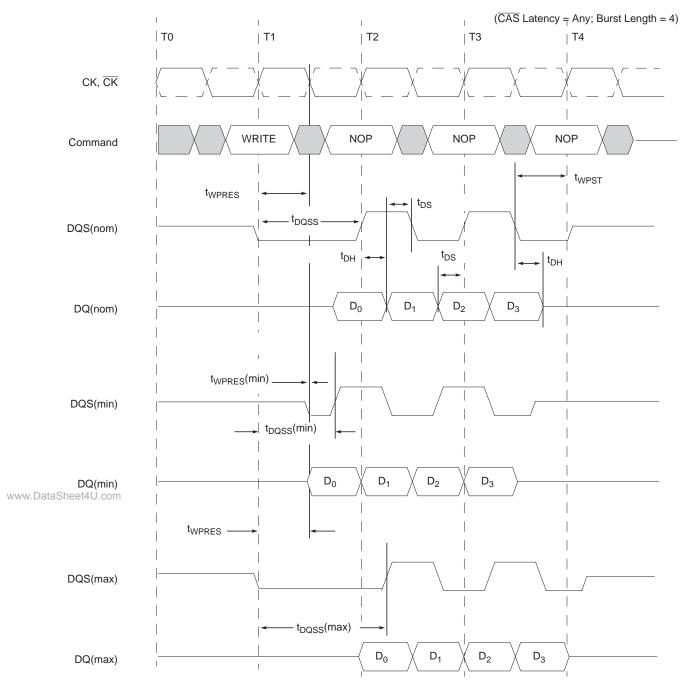

The Burst Write command is issued by having CS, CAS, and WE low while holding RAS high at the rising edge of the clock. The address inputs determine the starting column address. The memory controller is required to provide an input data strobe (DQS) to the DDR SDRAM to strobe or latch the input data (DQ) and data mask (DM) into the device. During Write cycles, the data strobe applied to the DDR SDRAM is required to be nominally centered within the data (DQ) and data mask (DM) valid windows. The data strobe must be driven high nominally one clock after the write command has been registered. Timing parameters to be driven high.

Input data for the first Burst Write cycle must be applied one clock cycle after the Write command is registered into the device (WL=1). The input data valid window is nominally centered around the midpoint of the data strobe signal. The data window is defined by DQ to DQS setup time ( $t_{QDQSS}$ ) and DQ to DQS hold time ( $t_{QDQSH}$ ). All data inputs must be supplied on each rising and falling edge of the data strobe until the burst length is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored.

# **Write Preamble and Postamble Operation**

Prior to a burst of write data and given that the controller is not currently in burst write mode, the data strobe signal (DQS), must transition from Hi-Z to a valid logic low. This is referred to as the data strobe "write preamble". This transition from Hi-Z to logic low nominally happens on the falling edge of the clock after the write command has been registered by the device. The preamble is explicitly defined by a setup time (t<sub>WPRES</sub>(min)) and hold time (t<sub>WPREH</sub>(min)) referenced to the first falling edge of CK after the write command.

# **Burst Write Timing**

Once the burst of write data is concluded and given that no subsequent burst write operations are initiated, the data strobe signal (DQS) transitions from a logic low level back to Hi-Z. This is referred to as the data strobe "write postamble". This transition happens nominally one-half clock period after the last data of the burst cycle is latched into the device.

# Write Interrupted by a Precharge

A Burst Write can be interrupted before completion of the burst by a Precharge command, with the only restriction being that the interval that separates the commands be at least one clock cycle.

# Write Interrupted by a Precharge Timing

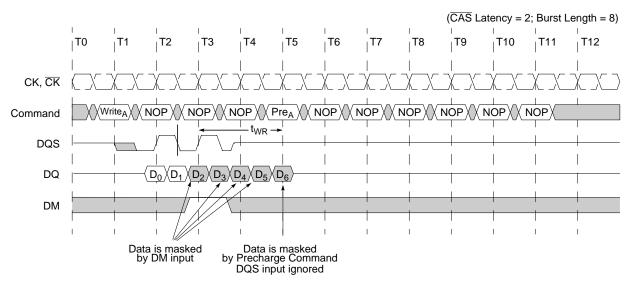

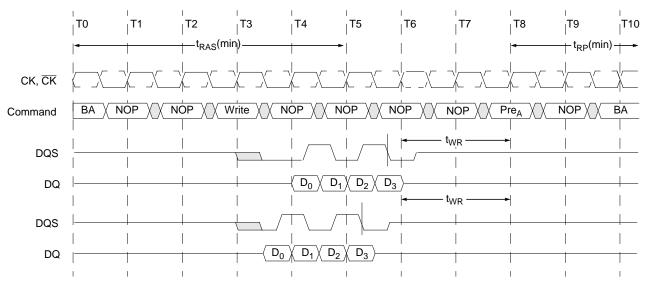

#### Write with Auto Precharge

If A<sub>10</sub> is high when a Write command is issued, the Write with auto Precharge function is performed. Any new command to the same bank should not be issued until the internal precharge is completed. The internal precharge begins after keeping t<sub>WR</sub> (min.).

# Write with Auto Precharge Timing

# **Precharge Timing During Write Operation**

Precharge timing for Write operations in DRAMs requires enough time to satisfy the write recovery requirement. This is the time required by a DRAM sense amp to fully store the voltage level. For DDR SDRAMs, a timing parameter ( $t_{WR}$ ) is used to indicate the required amount of time between the last valid write operation and a Precharge command to the same bank.

The "write recovery" operation begins on the rising clock edge after the last DQS edge that is used to strobe in the last valid write data. "Write recovery" is complete on the next 2nd rising clock edge that is used to strobe in the Precharge command.

# Write with Precharge Timing

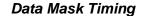

#### **Data Mask Function**

The DDR SDRAM has a Data Mask function that is used in conjunction with the Write cycle, but not the Read cycle. When the Data Mask is activated (DM high) during a Write operation, the Write is blocked (Mask to Data Latency = 0).

When issued, the Data Mask must be referenced to both the rising and falling edges of Data Strobe.

## **Burst Interruption**

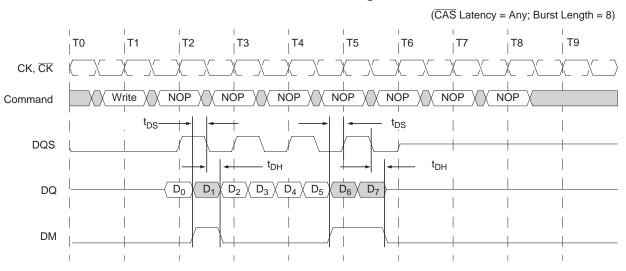

#### Read Interrupted by a Read

A Burst Read can be interrupted before completion of the burst by issuing a new Read command to any bank. When the previous burst is interrupted, the remaining addresses are overridden with a full burst length starting with the new address. The data from the first Read command continues to appear on the outputs until the CAS latency from the interrupting Read command is satisfied. At this point, the data from the interrupting Read command appears on the bus. Read commands can be issued on each rising edge of the system clock. It is illegal to interrupt a Read with autoprecharge command with a Read command.

#### Read Interrupted by a Read Command Timing

#### Read Interrupted by a Write

To interrupt a Burst Read with a Write command, a Burst Stop command must be asserted to stop the burst read operation and 3-state the DQ bus. Additionally, control of the DQS bus must be turned around to allow the memory controller to drive the data strobe signal (DQS) into the DDR SDRAM for the write cycles. Once the Burst Stop command has been issued, a Write command can not be issued until a minimum delay or latency ( $L_{BST}$ ) has been satisfied. This latency is measured from the Burst Stop command and is equivalent to the CAS latency programmed into the mode register. In instances where  $\overline{CAS}$  latency is measured in half clock cycles, the minimum delay ( $L_{BST}$ ) is rounded up to the next full clock cycle (i.e., if CL=2 then  $L_{BST}$ =2, if CL=2.5 then  $L_{BST}$ =3). It is illegal to interrupt a Read with autoprecharge command with a Write command.

# Read Interrupted by Burst Stop Command Followed by a Write Command Timing

#### Write Interrupted by a Write

A Burst Write can be interrupted before completion by a new Write command to any bank. When the previous burst is interrupted, the remaining addresses are overridden with a full burst length starting with the new address. The data from the first Write command continues to be input into the device until the Write Latency of the interrupting Write command is satisfied (WL=1) At this point, the data from the interrupting Write command is input into the device. Write commands can be issued on each rising edge of the system clock. It is allegal to interrupt a Write with autoprecharge command with a Write command.

### Write Interrupted by a Write Command Timing

www.Dat

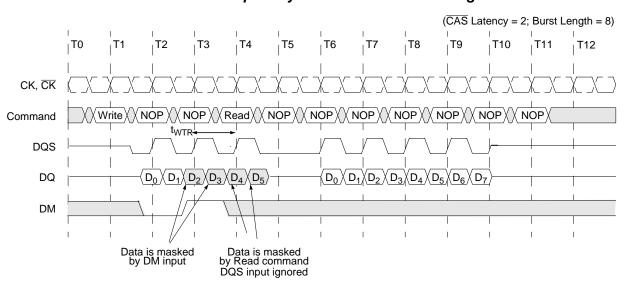

# Write Interrupted by a Read

A Burst Write can be interrupted by a Read command to any bank. If a burst write operation is interrupted prior to the end of the burst operation, then the last two pieces of input data prior to the Read command must be masked off with the data mask (DM) input pin to prevent invalid data from being written into the memory array. Any data that is present on the DQ pins coincident with or following the Read command will be masked off by the Read command and will not be written to the array. The memory controller must give up control of both the DQ bus and the DQS bus at least one clock cycle before the read data appears on the outputs in order to avoid contention. In order to avoid data contention within the device, a delay is required (t<sub>WTR</sub>) from the last valid data input before a Read command can be issued to the device. It is illegal to interrupt a Write with autoprecharge command with a Read command.

# Write Interrupted by a Read Command Timing

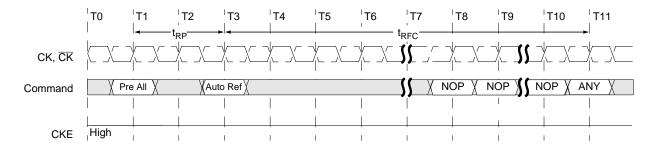

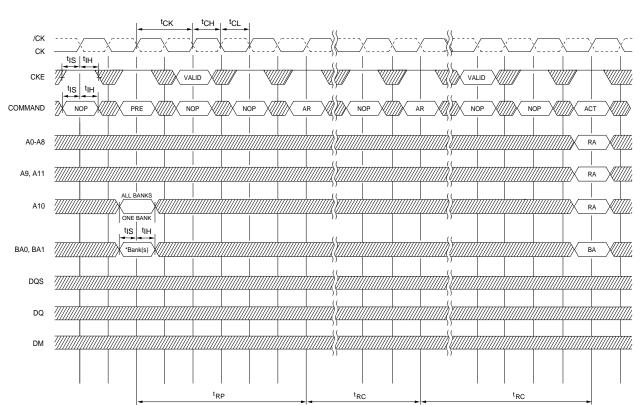

#### Auto Refresh

The Auto Refresh command is issued by having  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ , and  $\overline{\text{CAS}}$  held low with CKE and  $\overline{\text{WE}}$  high at the rising edge of the clock. All banks must be precharged and idle for a  $t_{RP}(\text{min})$  before the Auto Refresh command is applied. No control of the address pins is required once this cycle has started because of the internal address counter. When the Auto Refresh cycle has completed, all banks will be in the idle state. A delay between the Auto Refresh command and the next Activate command or subsequent Auto Refresh command must be greater than or equal to the  $t_{RFC}(\text{min})$ . Commands may not be issued to the device once an Auto Refresh cycle has begun.  $\overline{\text{CS}}$  input must remain high during the refresh period or NOP commands must be registered on each rising edge of the CK input until the refresh period is satisfied.

#### Auto Refresh Timing

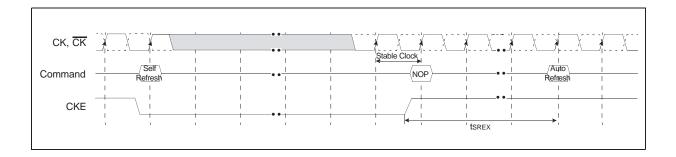

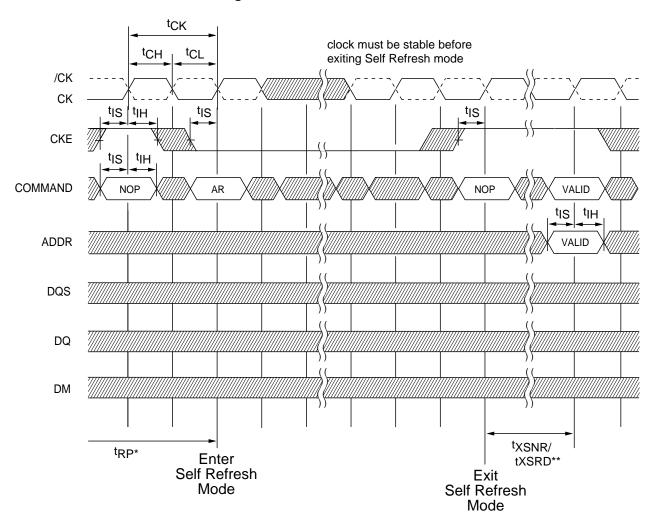

#### Self Refresh

A self refresh command is defined by having  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  and CKE held low with  $\overline{\text{WE}}$  high at the rising edge of the clock (CK). Once the self refresh command is initiated, CKE must be held low to keep the device in self refresh mode. During the self refresh operation, all inputs except CKE are ignored. The clock is internally disabled during self refresh operation to reduce power consumption. The self refresh is exited by supplying stable clock input before returning CKE high, asserting deselect or NOP command and then asserting CKE high for longer than  $t_{\text{SREX}}$  for locking of DLL. The auto refresh is required before self refresh entry and after self refresh exit.

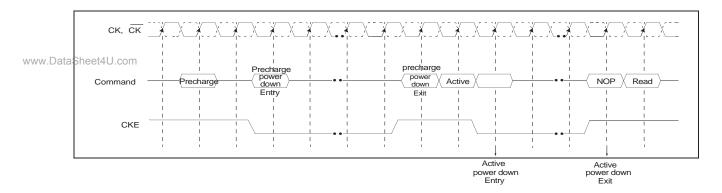

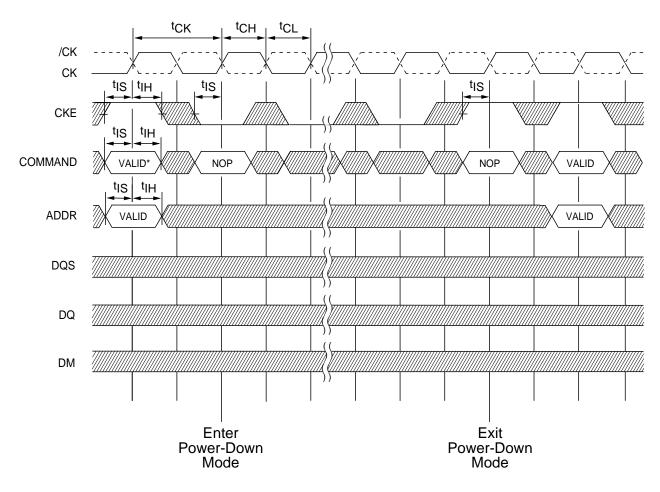

#### Power Down Mode

The power down mode is entered when CKE is low and exited when CKE is high. Once the power down mode is initiated, all of the receiver circuits except clock, CKE and DLL circuit are gated off to reduce power consumption. All banks should be in idle state prior to entering the precharge power down mode and CKE should be set high at least 1tck+tlS prior to row active command. During power down mode, refresh operations cannot be performed, therefore the device cannot remain in power down mode longer than the refresh period ( $t_{\rm RFF}$ ) of the device.

### TRUTH TABLE 2 - CKE

(Notes: 1-4)

| CKEn-1 | CKEn | CURRENT STATE  | COMMANDn          | ACTIONn                    | NOTES |

|--------|------|----------------|-------------------|----------------------------|-------|

|        |      | Power-Down     | Х                 | Maintain Power-Down        |       |

| L      | L    | Self Refresh   | Х                 | Maintain Self Refresh      |       |

|        |      |                |                   |                            |       |

|        |      | Power-Down     | DESELECT or NOP   | Exit Power-Down            |       |

| L      | Н    | Self Refresh   | DESELECT or NOP   | Exit Self Refresh          | 5     |

|        |      |                |                   |                            |       |

|        |      | All Banks Idle | DESELECT or NOP   | Precharge Power-Down Entry |       |

| Н      | L    | Bank(s) Active | DESELECT or NOP   | Active Power-Down Entry    |       |

|        |      | All Banks Idle | AUTO REFRESH      | Self Refresh Entry         |       |

| Н      | Н    |                | See Truth Table 3 |                            |       |

#### NOTE:

- 1.  $CKE_n$  is the logic state of CKE at clock edge n;  $CKE_{n-1}$  was the state of CKE at the previous clock edge.

- 2. Current state is the state of the DDR SDRAM immediately prior to clock edge *n*.

- 3. COMMANDn is the command registered at clock edge n, and ACTIONn is a result of COMMANDn.

- 4. All states and sequences not shown are illegal or reserved.

- 5. DESELECT or NOP commands should be issued on any clock edges occurring during the <sup>t</sup>XSR period.

A minimum of 200 clock cycles is needed before applying a read command, for the DLL to lock.

# DDR SDRAM SIMPLIFIED COMMAND TRUTH TABLE

| Comman                         | d                                           | CKEn-1 | CKEn | cs | RAS | CAS | WE  | ADDR | A10/<br>AP | ВА  | Note |

|--------------------------------|---------------------------------------------|--------|------|----|-----|-----|-----|------|------------|-----|------|

| Mode Registe                   | r Set                                       | Н      | Х    | L  | L   | L   | L   | C    | P code     | ı   | 1,2  |

| Extended Mode Re               | egister Set                                 | Н      | Х    | L  | L   | L   | L   | C    | P code     |     | 1,2  |

| Device Dese                    | lect                                        | Н      | Х    | Н  | Х   | Х   | Х   |      | Х          |     | 1    |

| No Operat                      | ion                                         | ] ''   | ^    | L  | Н   | Н   | Н   |      | ^          |     | '    |

| Bank Activ                     | /e                                          | Н      | Х    | L  | L   | Н   | Н   | R/   | Ą          | V   | 1    |

| Read                           |                                             | Н      | Х    | L  | Н   | L   | Н   | CA   | L          | V   | 1    |

| Read with Autop                | recharge                                    | ] ''   | ^    | _  | ''  |     | ''  | CA . | Н          | ľ   | 1,3  |

| Write                          |                                             | Н      | Х    | L  | Н   | L   | L   | CA   | L          | V   | 1    |

| Write with Autop               | Write with Autoprecharge                    |        |      |    |     | CA  | Н   | Ů    | 1,4        |     |      |

| Precharge All                  | Precharge All Banks Precharge selected Bank |        | Х    | L  | L   | Н   | L X | Н    | Х          | 1,5 |      |

| Precharge select               |                                             |        | ^    |    |     |     |     |      | L          | V   | 1    |

| Read Burst S                   | Stop                                        | Н      | Х    | L  | Н   | Н   | L   | Х    |            | 1   |      |

| Auto Refre                     | sh                                          | Н      | Н    | L  | L   | L   | Н   |      | Χ          |     | 1    |

|                                | Entry                                       | Н      | L    | L  | L   | L   | Н   |      |            |     | 1    |

| Self Refresh                   | Exit                                        | L      | Н    | Н  | Х   | Х   | Х   |      | Χ          |     | 1    |

|                                | EXIT                                        | _      |      | L  | Н   | Н   | Н   |      |            |     |      |

|                                | Entry                                       | Н      | L    | Н  | Х   | Х   | Х   |      |            |     | 1    |

| Precharge Power                |                                             |        | _    | L  | Н   | Н   | Н   | ×    |            |     | 1    |

| Precharge Power Down Mode Exit |                                             | L      | Н    | Н  | Х   | Х   | Х   | ^    |            |     | 1    |

|                                | LXII                                        | _      |      | L  | Н   | Н   | Н   |      |            |     | 1    |

| aSheet4U.com<br>Active Power   | Entry                                       | Н      | L    | Н  | Х   | Х   | Х   |      |            |     | 1    |

| Active Power  Down Mode        | Linuy                                       |        | _    | L  | V   | V   | V   | Х    |            |     | 1    |

|                                | Exit                                        | L      | Н    |    | )   | X   |     |      |            |     | 1    |

( H=Logic High Level, L=Logic Low Level, X=Don't Care, V=Valid Data Input, OP Code=Operand Code, NOP=No Operation )

#### Note:

www.Dat

- 1. LDM/UDM states are Don't Care. Refer to below Write Mask Truth Table.

- 2. OP Code(Operand Code) consists of A0~A11 and BA0~BA1 used for Mode Register setting during Extended MRS or MRS. Before entering Mode Register Set mode, all banks must be in a precharge state and MRS command can be issued after tRP period from Prechagre command.

- 3. If a Read with Autoprecharge command is detected by memory component in CK(n), then there will be no command presented to activated bank until CK(n+BL/2+tRP).

- 4. If a Write with Autoprecharge command is detected by memory component in CK(n), then there will be no command presented to activated bank until CK(n+BL/2+1+tDPL+tRP). Last Data-In to Prechage delay(tDPL) which is also called Write Recovery Time (tWR) is needed to guarantee that the last data has been completely written.

- 5. If A10/AP is High when Precharge command being issued, BA0/BA1 are ignored and all banks are selected to be precharged.

#### TRUTH TABLE 3 - Current State Bank n - Command to Bank n

(Notes: 1-6; notes appear below and on next page)

| CURRENT STATE                      | /CS                              | /RAS | /CAS                                        | /WE | COMMAND/ACTION                                    | NOTES  |

|------------------------------------|----------------------------------|------|---------------------------------------------|-----|---------------------------------------------------|--------|

| A                                  | Н                                | Х    | Х                                           | Х   | DESELECT (NOP/continue previous operation)        |        |

| Any                                | L                                | Н    | Н                                           | Н   | NO OPERATION (NOP/continue previous operation)    |        |

|                                    | L                                | L    | Н                                           | Н   | ACTIVE (select and activate row)                  |        |

| Idle                               | L                                | L    | L                                           | Н   | AUTO REFRESH                                      | 7      |

|                                    | L                                | L    | L                                           | L   | MODE REGISTER SET                                 | 7      |

|                                    | L                                | Н    | L                                           | Н   | READ (select column and start READ burst)         | 10     |

| Row Active                         | Row Active L H L L WRITE (select |      | WRITE (select column and start WRITE burst) | 10  |                                                   |        |

|                                    | L                                | L    | Н                                           | L   | PRECHARGE (deactivate row in bank or banks)       | 8      |

|                                    | L                                | Н    | L                                           | Н   | READ (select column and start new READ burst)     | 10     |

| Read (Auto Precharge<br>Disabled)  | L                                | L    | Н                                           | L   | PRECHARGE (truncate READ burst, start PRECHARGE)  | 8      |

| ,                                  | L                                | Н    | Н                                           | L   | BURST TERMINATE                                   | 9      |

|                                    | L                                | Н    | L                                           | Н   | READ (select column and start READ burst)         | 10, 11 |

| Write (Auto Precharge<br>Disabled) | L                                | Н    | L                                           | L   | WRITE (select column and start new WRITE burst)   | 10     |

|                                    | L                                | L    | Н                                           | L   | PRECHARGE (truncate WRITE burst, start PRECHARGE) | 8, 11  |

#### NOTE:

- This table applies when CKE<sub>n-1</sub> was HIGH and CKE<sub>n</sub> is HIGH (see Truth Table 2) and after <sup>t</sup>XSR has been met (if the previous state was self refresh).

- 2. This table is bank-specific, except where noted, i.e., the current state is for a specific bank and the commands shown are those allowed to be issued to that bank when in that state. Exceptions are covered in the notes below.

- 3. Current state definitions:

Idle: The bank has been precharged, and <sup>t</sup>RP has been met.

www.DataSheet4U.com Row Active: A row in the bank has been activated, and <sup>t</sup>RCD has been met.

No data bursts/accesses and no register accesses are in progress.

Read: A READ burst has been initiated, with AUTO PRECHARGE disabled,

and has not yet terminated or been terminated.

Write: A WRITE burst has been initiated, with AUTO PRECHARGE disabled,

and has not yet terminated or been terminated.

4. The following states must not be interrupted by a command issued to the same bank. DESELECT or NOP commands,

or allowable commands to the other bank should be issued on any clock edge occurring during these states. Allowable commands to the other bank are determined by its current state and Truth Table 3, and according to Truth Table 4.

Precharging: Starts with registration of a PRECHARGE command and ends when <sup>t</sup>RP is

met. Once <sup>t</sup>RP is met, the bank will be in the idle state.

# **NOTE: (continued)**

Row Activating: Starts with registration of an ACTIVE command and ends when <sup>t</sup>RCD is

met. Once <sup>t</sup>RCD is met, the bank will be in the "row active" state.

Read w/Auto-Precharge Enabled: Starts with registration of a READ command with AUTO PRECHARGE

enabled and ends when <sup>t</sup>RP has been met. Once <sup>t</sup>RP is met, the bank will

be in the idle state.

Write w/Auto-Precharge Enabled: Starts with registration of a WRITE command with AUTO PRECHARGE

enabled and ends when <sup>t</sup>RP has been met. Once <sup>t</sup>RP is met, the bank will

be in the idle state.

5. The following states must not be interrupted by any executable command; DESELECT or NOP commands must be applied on each positive clock edge during these states.

Refreshing: Starts with registration of an AUTO REFRESH command and ends when

<sup>t</sup>RC is met. Once <sup>t</sup>RFC is met, the DDR SDRAM will be in the "all banks"

idle" state.

Accessing Mode Register: Starts with registration of a MODE REGISTER SET command and ends

when <sup>t</sup>MRD has been met. Once <sup>t</sup>MRD is met, the DDR SDRAM will be in

the "all banks idle" state.

Precharging All: Starts with registration of a PRECHARGE ALL command and ends when

<sup>t</sup>RP is met. Once <sup>t</sup>RP is met, all banks will be in the idle state.

6. All states and sequences not shown are illegal or reserved.

7. Not bank-specific; requires that all banks are idle and no bursts are in progress.

8. May or may not be bank-specific; if multiple banks are to be precharged, each must be in a valid state for precharging.

Not bank-specific; BURST TERMINATE affects the most recent READ burst, regardless of bank.

10. READs or WRITEs listed in the Command/Action column include READs or WRITEs with AUTO PRECHARGE

enabled and READs or WRITEs with AUTO PRECHARGE disabled.

11. Requires appropriate DM masking.

#### TRUTH TABLE 4 - Current State Bank n - Command to Bank m

(Notes: 1-6; notes appear below and on next page)

| CURRENT STATE             | /CS | /RAS | /CAS | ΜE | COMMAND/ACTION                                  | NOTES    |

|---------------------------|-----|------|------|----|-------------------------------------------------|----------|

| Any                       | Н   | Х    | Х    | Х  | DESELECT (NOP/continue previous operation)      |          |

| Any                       | L   | Н    | Н    | Н  | NO OPERATION (NOP/continue previous operation)  |          |

| Idle                      | Х   | Х    | Х    | Х  | Any Command Otherwise Allowed to Bank m         |          |

|                           | L   | L    | Н    | Н  | ACTIVE (select and activate row)                |          |

| Row Activating,           | L   | Н    | L    | Н  | READ (select column and start READ burst)       | 7        |

| Active, or Precharging    | L   | Н    | L    | L  | WRITE (select column and start WRITE burst)     | 7        |

|                           | L   | L    | Н    | L  | PRECHARGE                                       |          |

| Read                      | L   | L    | Н    | Н  | ACTIVE (select and activate row)                |          |

| (Auto-Precharge           | L   | Н    | L    | Н  | READ (select column and start new READ burst)   | 7        |

| Disabled)                 | L   | L    | Н    | L  | PRECHARGE                                       |          |

|                           | L   | L    | Н    | Н  | ACTIVE (select and activate row)                |          |

| Write<br>(Auto- Precharge | L   | Н    | L    | Н  | READ (select column and start READ burst)       | 7, 8     |

| Disabled)                 | L   | Н    | L    | L  | WRITE (select column and start new WRITE burst) | 7        |

|                           | L   | L    | Н    | L  | PRECHARGE                                       |          |

|                           | L   | L    | Н    | Н  | ACTIVE (select and activate row)                |          |

| Read                      | L   | Н    | L    | Н  | READ (select column and start new READ burst)   | 3a, 7    |

| (With Auto-Precharge)     | L   | Н    | L    | L  | WRITE (select column and start WRITE burst)     | 3a, 7, 9 |

|                           | L   | L    | Н    | L  | PRECHARGE                                       |          |

|                           | L   | L    | Н    | Н  | ACTIVE (select and activate row)                |          |

| Write                     | L   | Н    | L    | Н  | READ (select column and start READ burst)       | 3a, 7    |

| (With Auto-Precharge)     | L   | Н    | L    | L  | WRITE (select column and start new WRITE burst) | 3a, 7    |

| ataShee                   | L   | L    | Н    | L  | PRECHARGE                                       |          |

#### NOTE:

- 1. This table applies when CKE<sub>n-1</sub> was HIGH and CKE<sub>n</sub> is HIGH (see Truth Table 2) and after <sup>t</sup>XSR has been met (if the previous state was self refresh).

- 2. This table describes alternate bank operation, except where noted, i.e., the current state is for bank *n* and the commands shown are those allowed to be issued to bank m (assuming that bank m is in such a state that the given command is allowable). Exceptions are covered in the notes below.

- 3. Current state definitions:

Idle: The bank has been precharged, and <sup>t</sup>RP has been met.

Row Active: A row in the bank has been activated, and <sup>t</sup>RCD has been met. No data bursts/accesses and no register accesses are in progress.

Read: A READ burst has been initiated, with AUTO PRECHARGE disabled, and has not yet terminated or been terminated.

Write: A WRITE burst has been initiated, with AUTO PRECHARGE disabled, and

has not yet terminated or been terminated.

# **NOTE: (continued)**

Read with Auto Precharge Enabled: See following text

Write with Auto Precharge Enabled: See following text

3a. The Read with Auto Precharge Enabled or Write with Auto Precharge Enabled states can each be broken into two parts: the access period and the precharge period. For Read with Auto Precharge, the precharge period is defined as if the same burst was executed with Auto Precharge disabled and then followed with the earliest possible PRECHARGE command that still accesses all of the data in the burst. For Write with Auto Precharge, the precharge period begins when tWR ends, with tWR measured as if Auto Precharge was disabled. The access period starts with registration of the command and ends where the precharge period (or <sup>1</sup>RP) begins.

During the precharge period of the Read with Auto Precharge Enabled or Write with Auto Precharge Enabled states, ACTIVE, PRECHARGE, READ and WRITE commands to the other bank may be applied; during the access period, only ACTIVE and PRECHARGE commands to the other bank may be applied. In either case, all other related limitations apply (e.g. contention between READ data and WRITE data must be avoided).

- 4. AUTO REFRESH and MODE REGISTER SET commands may only be issued when all banks are idle.

- 5. A BURST TERMINATE command cannot be issued to another bank; it applies to the bank represented by the current state only.

- 6. All states and sequences not shown are illegal or reserved.

- 7. READs or WRITEs listed in the Command/Action column include READs or WRITEs with AUTO PRECHARGE enabled and READs or WRITEs with AUTO PRECHARGE disabled.

- 8. Requires appropriate DM masking.

- 9. A WRITE command may be applied after the completion of data output.

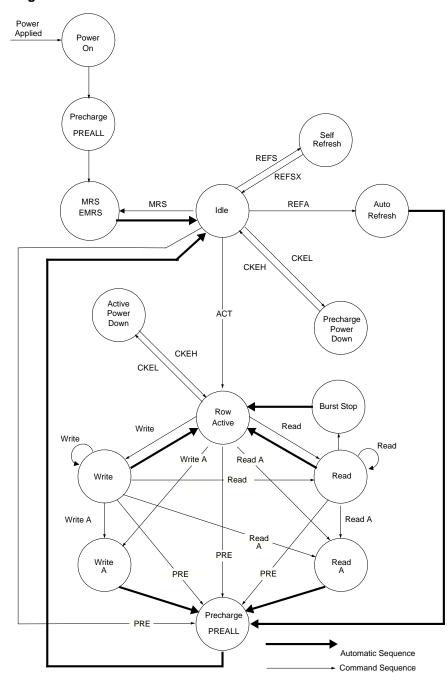

# **Simplified State Diagram**

www.DataSheet4U.com

PREALL = Precharge All Banks

MRS = Mode Register Set

EMRS = Extended Mode Register Set

REFS = Enter Self Refresh

REFSX = Exit Self Refresh REFA = Auto Refresh CKEL = Enter Power Down CKEH = Exit Power Down

ACT = Active

Write A = Write with Autoprecharge

Read A = Read with Autoprecharge

PRE = Precharge

# **DC Operating Conditions & Specifications**

# **DC Operating Conditions**

Recommended operating conditions(Voltage referenced to VSS=0V, TA=0 to 70°C)

| Parameter                                                   | Symbol               | Min                    | Max                    | Unit | Note |

|-------------------------------------------------------------|----------------------|------------------------|------------------------|------|------|

| Supply voltage (for device with a nominal $V_{DD}$ of 2.5V) | V <sub>DD</sub>      | 2.3                    | 2.7                    |      |      |

| Supply voltage (V <sub>DD</sub> of 2.6V for DDR400 device)  | V <sub>DD</sub>      | 2.5                    | 2.7                    |      |      |

| I/O Supply voltage                                          | V <sub>DDQ</sub>     | 2.3                    | 2.7                    | V    |      |

| I/O Supply voltage for DDR400 device                        | V <sub>DDQ</sub>     | 2.5                    | 2.7                    | V    |      |

| I/O Reference voltage                                       | V <sub>REF</sub>     | 0.49*VDDQ              | 0.51*VDDQ              | V    | 1    |

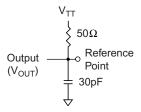

| I/O Termination voltage(system)                             | V <sub>TT</sub>      | V <sub>REF</sub> -0.04 | V <sub>REF</sub> +0.04 | V    | 2    |

| Input logic high voltage                                    | V <sub>IH</sub> (DC) | V <sub>REF</sub> +0.15 | V <sub>DDQ</sub> +0.3  | V    |      |

| Input logic low voltage                                     | V <sub>IL</sub> (DC) | -0.3                   | V <sub>REF</sub> -0.15 | V    |      |

| Input Voltage Level, CK and CK inputs                       | V <sub>IN</sub> (DC) | -0.3                   | V <sub>DDQ</sub> +0.3  | V    |      |

| Input Differential Voltage, CK and CK inputs                | V <sub>ID</sub> (DC) | 0.3                    | V <sub>DDQ</sub> +0.6  | V    | 3    |

| Input leakage current                                       | l <sub>l</sub>       | -2                     | 2                      | uA   |      |

| Output leakage current                                      | I <sub>OZ</sub>      | -5                     | 5                      | uA   |      |

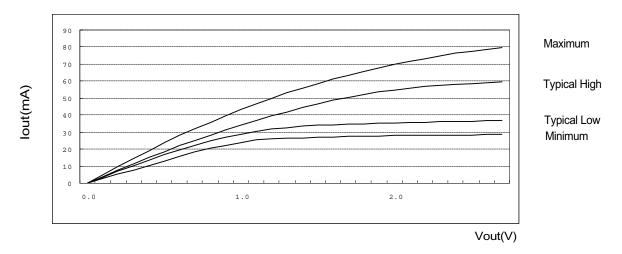

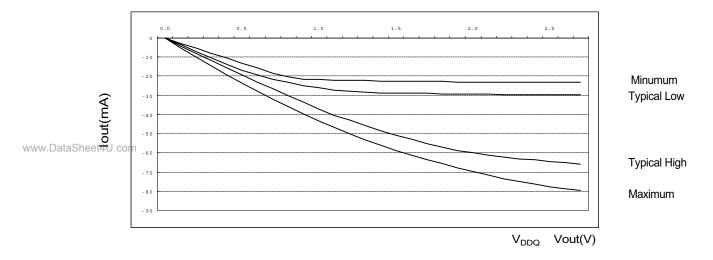

| Output High Current (V <sub>OUT</sub> = 1.95V)              | I <sub>OH</sub>      | -16.8                  |                        | mA   |      |

| Output Low Current (V <sub>OUT</sub> = 0.35V)               | I <sub>OL</sub>      | 16.8                   |                        | mA   |      |

Notes: 1. V<sub>REF</sub> is expected to be equal to 0.5\*V<sub>DDQ</sub> of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak noise on V<sub>REF</sub> may not exceed 2% of the DC value

2.V<sub>TT</sub> is not applied directly to the device. V<sub>TT</sub> is a system supply for signal termination resistors, is expected to be set equal to V<sub>REF</sub>, and must track variations in the DC level of V<sub>REF</sub>

3. V<sub>ID</sub> is the magnitude of the difference between the input level on CK and the input level on CK.

$\begin{tabular}{ll} \textbf{IDD Max Specifications and Conditions} \\ (0^{\circ}\text{C} \leq \text{TA} \leq 70^{\circ}\text{C}, \text{VDDQ} = 2.5 \\ \underline{+} \text{ 0.2V}, \text{VDD} = 2.5 \\ \underline{+} \text{ 0.2V}, \text{ for DDR400 device VDDQ} = 2.6 \\ \underline{+} \text{ 0.1V}, \text{ VDD} = 2.6 \\ \underline{+} \text{ 0.1V}) \\ \end{tabular}$

|                                                                                                                                                                                                                                                                               |        | Version |     |      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-----|------|--|

| Conditions                                                                                                                                                                                                                                                                    | Symbol | -5      | -6  | Unit |  |

| Operating current - One bank Active-Precharge; tRC=tRCmin;tCK= tCK (min); DQ, DM and DQS inputs changing twice per clock cycle; address and control inputs changing once per clock cycle                                                                                      | IDD0   | 120     | 110 | mA   |  |

| Operating current - One bank operation; One bank open, BL=4                                                                                                                                                                                                                   | IDD1   | 160     | 140 | mA   |  |

| Precharge power-down standby current; All banks idle; power - down mode; CKE = <vil(max); (min);="" and="" dm<="" dq,dqs="" for="" tck="tCK" td="" vin="Vref"><td>IDD2P</td><td>30</td><td>25</td><td>mA</td></vil(max);>                                                     | IDD2P  | 30      | 25  | mA   |  |

| Precharge Floating standby current; CS# > =VIH(min);All banks idle; CKE > = VIH(min); tCK= tCK (min); Address and other control inputs changing once per clock cycle; Vin = Vref for DQ, DQS and DM                                                                           | IDD2F  | 52      | 45  | mA   |  |

| Precharge Quiet standby current; CS# > = VIH(min); All banks idle; CKE > = VIH(min); tCK = tCK (min); Address and other control inputs stable with keeping >= VIH(min) or =< VIL (max); Vin = Vref for DQ ,DQS and DM                                                         | IDD2Q  | 50      | 44  | mA   |  |

| Active power - down standby current; one bank active; power-down mode; CKE=< VIL (max); tCK = tCK (min); Vin = Vref for DQ,DQS and DM                                                                                                                                         | IDD3P  | 30      | 25  | mA   |  |

| Active standby current; CS# >= VIH(min); CKE>=VIH(min); one bank active; active - precharge; tRC=tRASmax; tCK = tCK (min); DQ, DQS and DM inputs changing twice per clock cycle; address and other control inputs changing once per clock cycle                               | IDD3N  | 90      | 80  | mA   |  |

| Operating current - burst read; Burst length = 2; reads; continuous burst; One bank active; address and control inputs changing once per clock cycle; CL=2 at tCK= tCK(min); 50% of data changing at every burst; lout = 0 m A                                                | IDD4R  | 270     | 230 | mA   |  |

| Operating current - burst write; Burst length = 2; writes; continuous burst; One bank active address and control inputs changing once per clock cycle; CL=2 at tCK= tCK(min); DQ, DM and DQS inputs changing twice per clock cycle, 50% of input data changing at every burst | IDD4W  | 250     | 210 | mA   |  |

| heeा40 com<br>Auto refresh current; tRC = tRFC(min) - 8*tCK for DDR200 at 100Mhz, 10*tCK for DDR266A<br>& DDR266B at 133Mhz, 12*tCK for DDR333B; distributed refresh                                                                                                          | IDD5   | 210     | 200 | mA   |  |

| Self refresh current; CKE =< 0.2V; External clock should be on; tCK= tCK(min);                                                                                                                                                                                                | IDD6   | 3       | 3   | mA   |  |

| Operating current - Four bank operation; Four bank interleaving with BL=4                                                                                                                                                                                                     | IDD7   | 400     | 350 | mA   |  |

# **AC Operating Conditions & Timing Specification**

# **AC Operating Conditions**

| Parameter/Condition                                  | Symbol  | Min          | Max          | Unit | Note |

|------------------------------------------------------|---------|--------------|--------------|------|------|

| Input High (Logic 1) Voltage, DQ, DQS and DM signals | VIH(AC) | VREF + 0.31  |              | V    | 1    |

| Input Low (Logic 0) Voltage, DQ, DQS and DM signals. | VIL(AC) |              | VREF - 0.31  | V    | 2    |

| Input Differential Voltage, CK and CK inputs         | VID(AC) | 0.7          | VDDQ+0.6     | V    | 3    |

| Input Crossing Point Voltage, CK and CK inputs       | VIX(AC) | 0.5*VDDQ-0.2 | 0.5*VDDQ+0.2 | V    | 4    |

#### Note:

- 1.Vih(max) = 4.2V. The overshoot voltage duration is  $\leq$  3ns at VDD.

- 2. Vil(min) = -1.5V. The undershoot voltage duration is  $\leq 3$ ns at VSS.

- 3. VID is the magnitude of the difference between the input level on CK and the input on  $\overline{\text{CK}}$ .

- 4. The value of  $V_{IX}$  is expected to equal 0.5\* $V_{DDQ}$  of the transmitting device and must track variations in the DC level of the same.

# ELECTRICAL CHARACTERISTICS AND AC TIMING for PC400/PC333/PC266 -Absolute Specifications

(Notes: 1-5, 14-17) (0°C  $\leq$  T  $_{A}$   $\leq$  70°C;  $V_{DDQ}$  = +2.5V  $\pm$ 0.2V,  $V_{DD}$ =+2.5V  $\pm$ 0.2V for DDR400 device  $V_{DDQ}$  = +2.6V  $\pm$ 0.1V,  $V_{DD}$ =+2.6V  $\pm$ 0.1V)

|        | AC CHARACTERISTICS                                   |                     |                       | -     | 5    | -    | 6    |                 |       |

|--------|------------------------------------------------------|---------------------|-----------------------|-------|------|------|------|-----------------|-------|

|        | PARAMETER                                            |                     | SYM-<br>BOL           | MIN   | MAX  | MIN  | MAX  | UNITS           | NOTES |

|        | Access window of DQs from CK/CK  CK high-level width |                     | <sup>t</sup> AC       | -0.65 | 0.65 | -0.7 | 0.7  | ns              |       |

|        |                                                      |                     | <sup>t</sup> CH       | 0.45  | 0.55 | 0.45 | 0.55 | <sup>t</sup> CK | 30    |

|        | CK low-level width                                   |                     | <sup>t</sup> CL       | 0.45  | 0.55 | 0.45 | 0.55 | <sup>t</sup> CK | 30    |

|        | Clock cycle time                                     | CL = 3              | tCK(3)                | 5     | 10   | 6    | 12   | ns              | 52    |

|        | _                                                    | CL = 2.5            | <sup>t</sup> CK (2.5) | 6     | 10   | 6    | 12   | ns              | 52    |

| w Doto | Sheet4U.com                                          | CL = 2              | <sup>t</sup> CK (2)   | 7.5   | 10   | 7.5  | 12   | ns              | 52    |

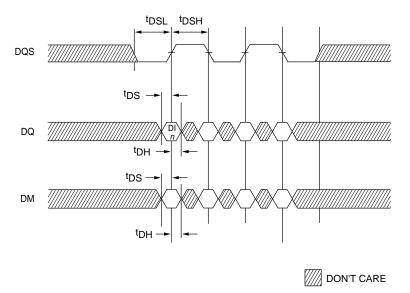

| w.Dala | DQ and DM input hold time relative to DQS            |                     | <sup>t</sup> DH       | 0.40  |      | 0.45 |      | ns              | 26,31 |

|        | DQ and DM input setup time relative to DQS           |                     | <sup>t</sup> DS       | 0.40  |      | 0.45 |      | ns              | 26,31 |

|        | DQ and DM input pulse put)                           | width (for each in- | <sup>t</sup> DIPW     | 1.75  |      | 1.75 |      | ns              | 31    |

|        | Access window of DQS                                 | From CK/CK          | <sup>t</sup> DQSCK    | -0.6  | 0.6  | -0.6 | 0.6  | ns              |       |

|        | DQS input high pulse v                               | vidth               | <sup>t</sup> DQSH     | 0.35  |      | 0.35 |      | <sup>t</sup> CK |       |

|        | DQS input low pulse w                                | idth                | <sup>t</sup> DQSL     | 0.35  |      | 0.35 |      | <sup>t</sup> CK |       |

|        | DQS-DQ skew, DQS to per group, per access            | o last DQ valid,    | <sup>t</sup> DQSQ     |       | 0.40 |      | 0.45 | ns              | 25,26 |

|        | Write command to first sition                        | DQS latching tran-  | <sup>t</sup> DQSS     | 0.72  | 1.25 | 0.75 | 1.25 | <sup>t</sup> CK |       |

|        | DQS falling edge to CK                               | rising - setup time | <sup>t</sup> DSS      | 0.2   |      | 0.2  |      | <sup>t</sup> CK |       |

|        | DQS falling edge from time                           | CK rising - hold    | <sup>t</sup> DSH      | 0.2   |      | 0.2  |      | <sup>t</sup> CK |       |

|                 | AC CHARACTERISTICS                                       |                              | -                                     | 5      | -6                                    |         |                 |        |

|-----------------|----------------------------------------------------------|------------------------------|---------------------------------------|--------|---------------------------------------|---------|-----------------|--------|

|                 | PARAMETER                                                | SYM-<br>BOL                  | MIN                                   | MAX    | MIN                                   | MAX     | UNITS           | NOTES  |

|                 | Half clock period                                        | <sup>t</sup> HP              | <sup>t</sup> CH,<br><sup>t</sup> CL   |        | <sup>t</sup> CH,<br><sup>t</sup> CL   |         | ns              | 34     |

|                 | Data-out high-impedance window from CK/CK                | <sup>t</sup> HZ              | -0.65                                 | +0.65  | -0.7                                  | +0.7    | ns              | 18     |

|                 | Data-out low-impedance window from CK/CK                 | <sup>t</sup> LZ              | -0.65                                 | +0.65  | -0.7                                  | +0.7    | ns              | 18     |

|                 | Address and control input hold time (fast slew rate)     | <sup>t</sup> IH <sub>F</sub> | 0.60                                  |        | 0.75                                  |         | ns              | 14     |

|                 | Address and control input setup time (fast slew rate)    | <sup>t</sup> IS <sub>F</sub> | 0.60                                  |        | 0.75                                  |         | ns              | 14     |

|                 | Address and control input hold time (slow slew rate)     | <sup>t</sup> IH <sub>S</sub> | 0.70                                  |        | 0.80                                  |         | ns              | 14     |

|                 | Address and control input setup time (slow slew rate)    | <sup>t</sup> IS <sub>S</sub> | 0.70                                  |        | 0.80                                  |         | ns              | 14     |

|                 | LOAD MODE REGISTER command cycle time                    | <sup>t</sup> MRD             | 2                                     |        | 2                                     |         | <sup>t</sup> CK |        |

|                 | DQ-DQS hold, DQS to first DQ to go non-valid, per access | <sup>t</sup> QH              | <sup>t</sup> HP<br>- <sup>t</sup> QHS |        | <sup>t</sup> HP<br>- <sup>t</sup> QHS |         | ns              | 25, 26 |

|                 | Data hold skew factor                                    | <sup>t</sup> QHS             |                                       | 0.50   |                                       | 0.55    | ns              |        |

|                 | ACTIVE to PRECHARGE command                              | <sup>t</sup> RAS             | 40                                    | 70,000 | 42                                    | 120,000 | ns              | 35     |

|                 | ACTIVE to READ with Auto precharge command               | <sup>t</sup> RAP             | 15                                    |        | 18                                    |         | ns              | 46     |

| ww.DataSheet4U. | coACTIVE to ACTIVE/AUTO REFRESH command period           | <sup>t</sup> RC              | 60                                    |        | 60                                    |         | ns              |        |

|                 | AUTO REFRESH command period                              | <sup>t</sup> RFC             | 70                                    |        | 72                                    |         | ns              | 50     |

|                 | ACTIVE to READ or WRITE delay                            | <sup>t</sup> RCD             | 15                                    |        | 18                                    |         | ns              |        |

|                 | PRECHARGE command period                                 | <sup>t</sup> RP              | 15                                    |        | 18                                    |         | ns              |        |

|                 | DQS read preamble                                        | <sup>t</sup> RPRE            | 0.9                                   | 1.1    | 0.9                                   | 1.1     | <sup>t</sup> CK | 42     |

|                 | DQS read postamble                                       | <sup>t</sup> RPST            | 0.4                                   | 0.6    | 0.4                                   | 0.6     | <sup>t</sup> CK |        |

|                 | ACTIVE bank a to ACTIVE bank b command                   | <sup>t</sup> RRD             | 10                                    |        | 12                                    |         | ns              |        |

|                 | DQS write preamble                                       | tWPRE                        | 0.25                                  |        | 0.25                                  |         | <sup>t</sup> CK |        |

|                 | DQS write preamble setup time                            | twPRES                       | 0                                     |        | 0                                     |         | ns              | 20, 21 |