# 3.8V TO 36V, 2A, 2.2MHZ, SYNCHRONOUS STEP-DOWN VOLTAGE REGULATOR

# Preliminary Information May 2024

#### **GENERAL DESCRIPTION**

The IS32PM3426 regulator is an easy-to-use synchronous step-down DC-DC converter capable of driving up to 2A of load current from an input voltage ranging of 3.8V to 36V. The IS32PM3426 provides exceptional efficiency, output accuracy and drop-out voltage in a very small solution size. Constant on-time control mode is employed to achieve simple controlloop compensation and fast transient response. The IS32PM3426 supports both Forced Continuous Conduction Mode (FCCM) and Pulse Frequency Modulation mode (PFM) at light-load condition, which is selected by the FPWM pin. It requires few external components. Pin arrangement allows simple, optimum PCB layout. Protection features include thermal shutdown, VDD under-voltage lockout, cycleby-cycle current limit, over-voltage and output shortcircuit protection.

The IS32PM3426 device is available in the WFCQFN-14 (3mm × 4mm) package.

#### **APPLICATIONS**

- General-purpose power supply

- Automotive LED lighting system

- · Automotive body electronics

#### **FEATURES**

- Input voltage range from 3.8V to 36V

- 1µA (Typ.) shutdown current

- 25µA quiescent current (typical, no switching)

- Up to 2A output current capability

- Adjustable output voltage, 1V to 24V

- Output regulation accuracy:

- ±1% at 25°C

- ±2% over -40°C ~150°C

- 93% efficiency at full load (5V/2A)

- >85% efficiency at light load (5V/100mA)

- · Integrated synchronous rectifier

- Operating frequency range: 100kHz to 2.2MHz

- Programmed by a single resistor

- Synchronized to external clock

- Pin-selectable FCCM or PFM operation mode

- Spread spectrum to minimize EMI

- Few external components

- Internal loop compensation

- Internal soft-start

- · Power good flag output

- · Fault protections

- Cycle by cycle current limit

- Precision enable to program system UVLO

- Output short-circuit protection with hiccup mode

- Output over-voltage protection

- VDD under-voltage lockout

- Thermal shutdown protection

- Operating junction temperature range from -40°C ~ +150°C

- WFCQFN-14 (3mm × 4mm) compact package

- AEC-Q100 qualification in progress with Temperature Grade 1: -40°C to 125°C

- RoHS & Halogen-Free Compliance

- TSCA Compliance

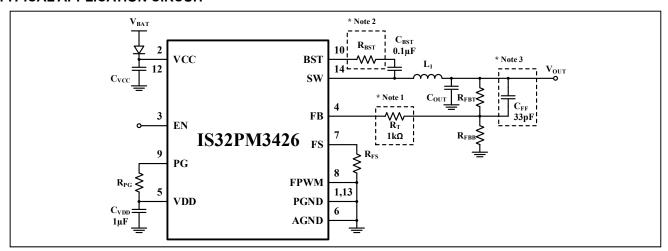

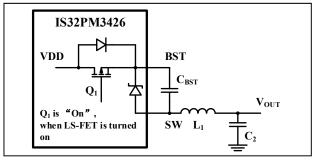

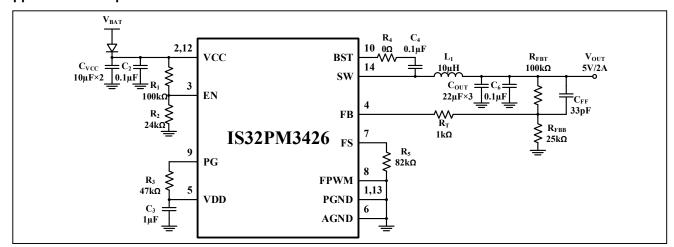

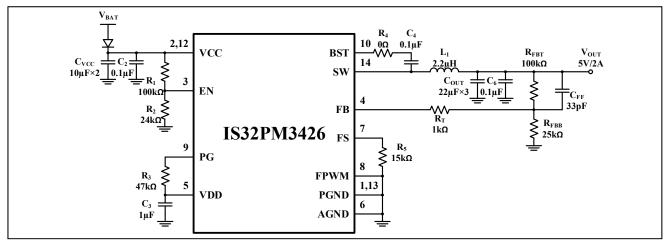

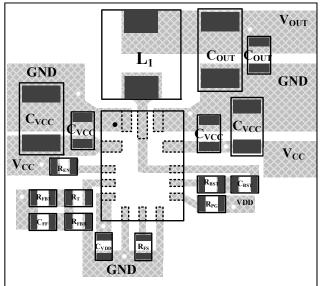

#### **TYPICAL APPLICATION CIRCUIT**

Figure 1 Typical Application Circuit

- **Note 1:** The resistor ( $R_T$ ) must be connected to FB pin with fixed value  $1k\Omega$ . **Note 2:** If add the resistor ( $R_{BST}$ ), the value must not exceed  $20\Omega$ .

- Note 3: The capacitor ( $C_{FF}$ ) must be connected in parallel to the resistor ( $R_{FBT}$ ) with fixed value 33pF.

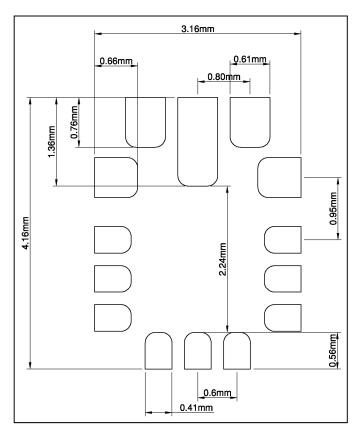

### **PIN CONFIGURATION**

| Package   | Pin Configuration (Top View) |  |  |  |  |

|-----------|------------------------------|--|--|--|--|

| WFCQFN-14 | VCC 2                        |  |  |  |  |

#### **PIN DESCRIPTION**

| No.   | Pin  | Description                                                                                                                                                                                                                                                     |

|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 13 | PGND | Power ground for the ground connection of internal synchronous rectifier FET.                                                                                                                                                                                   |

| 2, 12 | VCC  | Power supply input. Connect a bypass capacitor $C_{\text{VCC}}$ from this pin to ground. The path from $C_{\text{VCC}}$ to PGND and VCC pins should be as short as possible.                                                                                    |

| 3     | EN   | Enable input to the regulator. Pulled high to enable and pull low to disable. Connecting a resistor divider from VCC can program external system UVLO. Do not float.                                                                                            |

| 4     | FB   | Feedback input to regulator. Connect to the tap point of feedback voltage divider through a $1k\Omega$ resistor. Do not either float or ground.                                                                                                                 |

| 5     | VDD  | Internal 5V LDO output. Used as supply to internal control circuits. Do not connect to any external loads. Can be used as logic supply for control inputs. Connect a high quality 1µF X7R ceramic capacitor from this pin to GND.                               |

| 6     | AGND | Analog ground for internal references and control circuits.                                                                                                                                                                                                     |

| 7     | FS   | An external resistor to ground on this pin sets the operating frequency. This pin can also be used to synchronize two or more IS32PM3426s in the system. Apply an external clock signal to this pin on two or more ICs for operating frequency synchronization. |

| 8     | FPWM | Regulator operation mode selection pin. Connect to VDD for FCCM mode and connect to AGND for PFM mode. Do not float.                                                                                                                                            |

| 9     | PG   | Open drain power-good flag output. Connect to suitable voltage supply through a current limit resistor. High=power ok. Low=power bad. Can be left open or grounded if not used.                                                                                 |

| 10    | BST  | Bootstrap supply voltage for internal high-side MOSFET gate driver. Connect a 0.1μF X7R ceramic capacitor from this pin to SW pin.                                                                                                                              |

| 11    | NC   | Not connect.                                                                                                                                                                                                                                                    |

| 14    | SW   | Regulator switch node. Connect it to power inductor.                                                                                                                                                                                                            |

**ORDERING INFORMATION**

Automotive Range: -40°C to +125°C

| Order Part No.       | Package              | QTY/Reel |

|----------------------|----------------------|----------|

| IS32PM3426-QWCLA3-TR | WFCQFN-14, Lead-free | 2500     |

Copyright © 2024 Lumissil Microsystems. All rights reserved. Lumissil Microsystems reserves the right to make changes to this specification and its products at any time without notice. Lumissil Microsystems assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products.

Lumissil Microsystems does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Lumissil Microsystems receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Lumissil Microsystems is adequately protected under the circumstances

#### **ABSOLUTE MAXIMUM RATINGS**

| Input voltages of VCC and EN to AGND, PGND                                                                     | -0.3V ~ +42V                  |

|----------------------------------------------------------------------------------------------------------------|-------------------------------|

| Input voltages of FB, FS, FPWM to AGND, PGND                                                                   | -0.3V ~ +6V                   |

| Voltage of AGND to PGND                                                                                        | -0.3V ~ +0.3V                 |

| Output voltage of VDD to AGND, PGND                                                                            | -0.3V ~ +6V                   |

| Voltage of PG to AGND, PGND                                                                                    | -0.3V ~ V <sub>CC</sub> +0.3V |

| Voltage of SW to AGND, PGND                                                                                    | -0.3V ~ V <sub>CC</sub> +0.3V |

| Voltage of BST to SW                                                                                           | -0.3V ~ +6V                   |

| Storage temperature range, T <sub>STG</sub>                                                                    | -65°C ~ +150°C                |

| Operating temperature range, T <sub>A</sub> = T <sub>J</sub>                                                   | -40°C ~ +150°C                |

| Power dissipation, P <sub>D(MAX)</sub>                                                                         | 2.33W                         |

| Package thermal resistance, junction to ambient (4-layer standard test PCB based on JESD 51-2A), $\theta_{JA}$ | 53.7°C/W                      |

| Package thermal resistance, junction to pin (4-layer standard test PCB based on JESD 51-8), $\theta_{JP}$      | 17.7°C/W                      |

| ESD (HBM)                                                                                                      | ±2.5kV                        |

| ESD (CDM)                                                                                                      | ±750V                         |

**Note 4:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range (unless otherwise noted). (Note 5)

|                     | Parameter                         | Min. | Тур. | Max.     | Unit |

|---------------------|-----------------------------------|------|------|----------|------|

|                     | VCC to PGND                       | 3.8  |      | 36       | V    |

| Input voltages      | EN                                | 0    |      | Vcc      |      |

|                     | FB                                | 0    |      | 1.5      |      |

|                     | PG                                | 0    |      | Vcc      |      |

|                     | FPWM                              | 0    |      | $V_{DD}$ |      |

|                     | FS                                | 0    |      | $V_{DD}$ |      |

| Output voltage, Vo  | DUT                               | 1    |      | 24       | V    |

| Output current, Iou | л                                 | 0    |      | 2        | Α    |

| Operating junction  | temperature range, T <sub>J</sub> | -40  |      | 150      | °C   |

**Note 5:** Recommended Operating Conditions indicate conditions for which the device is intended to be functional, but do not ensure specific performance limits. For verified specifications, see Electrical Characteristics.

#### **ELECTRICAL CHARACTERISTICS**

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of -40°C to +150°C, unless otherwise stated. Minimum and Maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$ = 25°C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{CC}$ = 12V.

| Symbol       | Parameter                                   | Condition                                                               | Min. | Тур. | Max. | Unit |

|--------------|---------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| Power Supply |                                             |                                                                         |      |      |      |      |

| Vcc_uv       | VCC under-voltage lockout threshold         | V <sub>CC</sub> rising                                                  |      | 3.5  | 3.75 | V    |

| Vcc_uvhy     | VCC under-voltage lockout hysteresis        | Vcc falling                                                             |      | 200  |      | mV   |

| Isp          | Shutdown current                            | V <sub>EN</sub> = 0V                                                    |      | 1    | 5    | μΑ   |

| lcc          | Operating quiescent current (non-switching) | V <sub>EN</sub> = 5V, V <sub>FB</sub> = 1.05V,<br>T <sub>J</sub> = 25°C |      | 25   | 35   | μA   |

#### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of -40°C to +150°C, unless otherwise stated. Minimum and Maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$ = 25°C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{CC}$ = 12V.

| Symbol                    | Parameter                                                                   | Condition                                                                       | Min.     | Тур.  | Max.  | Unit |

|---------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------|-------|-------|------|

| Enable                    |                                                                             |                                                                                 |          |       |       |      |

| V <sub>EN_VDD_</sub> H    | Input voltage level to enable the internal LDO output, V <sub>DD</sub>      | V <sub>EN</sub> rising                                                          | 1.05     |       |       | ٧    |

| V <sub>EN_VDD_L</sub>     | Input voltage level to disable the internal LDO output, V <sub>DD</sub>     | V <sub>EN</sub> falling                                                         |          |       | 0.4   | >    |

| V <sub>EN_VOUT_H</sub>    | Precision enable level for switching and regulator output, V <sub>OUT</sub> | V <sub>EN</sub> rising                                                          | 1.16     | 1.2   | 1.24  | >    |

| $V_{\text{EN\_VOUT\_HY}}$ | Precision enable level hysteresis                                           | V <sub>EN</sub> falling                                                         |          | 100   |       | mV   |

| I <sub>EN_LKG</sub>       | EN pin input leakage current                                                | V <sub>EN</sub> = 5V                                                            |          | 0.2   | 50    | nA   |

| Soft-Start                |                                                                             |                                                                                 |          |       |       |      |

| tss                       | Internal soft-start time                                                    | Vout from 10% to 90%                                                            | 1.5      | 2     | 2.5   | ms   |

| Forced PW                 | M                                                                           |                                                                                 | <u>!</u> | •     |       |      |

| V <sub>FPWM_IH</sub>      | FPWM input high threshold                                                   |                                                                                 | 1.5      |       |       | V    |

| V <sub>FPWM_IL</sub>      | FPWM input low threshold                                                    |                                                                                 |          |       | 0.4   | V    |

| Internal LD               | 0                                                                           |                                                                                 |          |       |       |      |

| $V_{DD}$                  | Internal LDO output voltage                                                 | 5.5V≤ V <sub>CC</sub> ≤ 36V, I <sub>DD</sub> =10mA                              | 4.75     | 5     | 5.25  | V    |

| I <sub>DD_LIM</sub>       | Internal LDO output current limit                                           |                                                                                 | 20       | 45    |       | mA   |

| V <sub>DD_UV</sub>        | VDD under-voltage lockout thresholds                                        | V <sub>DD</sub> rising                                                          | 3        | 3.25  | 3.5   | ٧    |

| V <sub>DD_UVHY</sub>      | VDD under-voltage lockout hysteresis                                        | V <sub>DD</sub> falling                                                         |          | 200   |       | mV   |

| Voltage Ref               | ference                                                                     |                                                                                 |          |       |       |      |

| V                         | Farable and continue                                                        | T <sub>J</sub> = 25°C                                                           | 0.990    | 1.000 | 1.010 |      |

| $V_{FB\_TH}$              | Feedback voltage                                                            | T <sub>J</sub> = -40°C to 150°C                                                 | 0.98     | 1.000 | 1.02  | V    |

| I <sub>FB_LKG</sub>       | FB pin input leakage current                                                | V <sub>FB</sub> = 1V                                                            |          | 20    | 100   | nA   |

| MOSFETS                   |                                                                             |                                                                                 |          |       |       |      |

| R <sub>DSON_HS</sub>      | High-side MOSFET ON-resistance                                              | I <sub>SW</sub> = -1A                                                           |          | 80    |       | mΩ   |

| R <sub>DSON_LS</sub>      | Low-side MOSFET ON-resistance                                               | I <sub>SW</sub> = 1A                                                            |          | 40    |       | mΩ   |

| ton_min                   | Minimum switch ON-time                                                      |                                                                                 |          | 100   |       | ns   |

| toff_min                  | Minimum switch OFF-time                                                     |                                                                                 |          | 90    |       | ns   |

| Isw_LKG                   | SW pin leakage current                                                      | V <sub>EN</sub> = 0V, V <sub>SW</sub> = 36V,<br>T <sub>J</sub> = -40°C to 125°C |          |       | 5     | μΑ   |

#### **ELECTRICAL CHARACTERISTICS (CONTINUE)**

Limits apply over the recommended operating junction temperature ( $T_J$ ) range of -40°C to +150°C, unless otherwise stated. Minimum and Maximum limits are specified through test, design or statistical correlation. Typical values represent the most likely parametric norm at  $T_J$ = 25°C, and are provided for reference purposes only. Unless otherwise stated, the following conditions apply:  $V_{CC}$ = 12V.

| Symbol               | Parameter                               | Condition                                        | Min. | Тур. | Max. | Unit     |

|----------------------|-----------------------------------------|--------------------------------------------------|------|------|------|----------|

| Current Lin          | nit                                     |                                                  | •    | •    | •    | <u> </u> |

| I <sub>HSLIM</sub>   | High-side MOSFET current limit          |                                                  | 3    | 4    | 5    | Α        |

| I <sub>LSLIM</sub>   | Low-side MOSFET current limit           |                                                  | 2    | 2.5  | 3.7  | Α        |

| I <sub>L_ZC</sub>    | Zero cross detection threshold          |                                                  |      | -0.1 |      | Α        |

| I <sub>PK_MIN</sub>  | Minimum inductor peak current           |                                                  |      | 1    |      | Α        |

| I <sub>LSRS</sub>    | Negative current limit                  |                                                  |      | -2   |      | Α        |

| t <sub>HC</sub>      | Over current hiccup time                |                                                  | 16.5 | 22   | 27.5 | ms       |

| Power Goo            | d                                       |                                                  |      |      |      |          |

| $V_{PG\_PD}$         | PG pin pull down capability             | Sink current = 5mA                               |      | 0.1  | 0.4  | V        |

| I <sub>PG_LKG</sub>  | PG pin leakage current                  |                                                  |      |      | 100  | nA       |

| $V_{PG\_UP}$         | Power-good upper threshold              | V <sub>OUT</sub> rising, % of FB voltage         | 105  | 107  | 110  | %        |

| $V_{PG\_DN}$         | Power-good lower threshold              | V <sub>OUT</sub> falling, % of FB voltage        | 90   | 93   | 95   | %        |

| $V_{PG\_HY}$         | Power-good hysteresis                   | V <sub>OUT</sub> falling/rising, % of FB voltage |      | 2    |      | %        |

| t <sub>PG_RF</sub>   | PG rising/falling delay time            |                                                  |      | 120  | 200  | μs       |

| Oscillator           |                                         |                                                  |      |      |      |          |

| V <sub>FS</sub>      | FS pin voltage                          |                                                  |      | 1.2  |      | V        |

| fs_def               | Oscillator default frequency            | FS pin open circuit                              | 360  | 400  | 460  | kHz      |

| ť                    | Minimum adjustable frequency            | With 40/ mariatana at EC min                     |      | 100  |      | kHz      |

| fs                   | Maximum adjustable frequency            | With 1% resistors at FS pin                      | 1950 | 2100 | 2250 | kHz      |

| f <sub>SS_P</sub>    | Spread spectrum pattern frequency       | (Note 6)                                         |      | 800  |      | Hz       |

| fss_s                | Frequency span of spread spectrum       | (Note 6)                                         |      | ±5   |      | %        |

| Vsync_h              | Sync clock input logic high             |                                                  | 2    |      |      | V        |

| V <sub>SYNC_L</sub>  | Sync clock input logic low              |                                                  |      |      | 0.4  | V        |

| tsync_min            | Minimum sync clock ON-time and OFF-time |                                                  | 80   |      |      | ns       |

| f <sub>SYNC_RG</sub> | Sync clock frequency range              |                                                  | 100  |      | 2200 | kHz      |

| Thermal Sh           | utdown                                  |                                                  |      |      |      |          |

| T <sub>SD</sub>      | Thermal shutdown                        | (Note 6)                                         |      | 175  |      | 0.0      |

| T <sub>SDHY</sub>    | Thermal shutdown hysteresis             | (Note 6)                                         |      | 155  |      | °C       |

Note 6: Guaranteed by design.

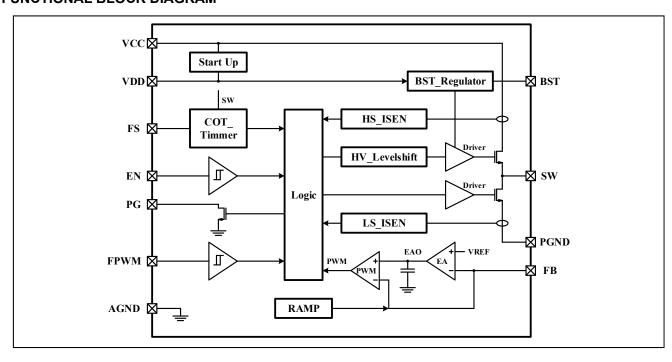

#### **FUNCTIONAL BLOCK DIAGRAM**

#### DETAILS DESCRIPTION

The IS32PM3426 is a fully integrated Synchronous rectified step-down switch-mode converter. Constanton time (COT) control is employed to provide fast transient response and easy loop stabilization. At the beginning of each cycle, the high-side MOSFET (HS-FET) is turned on when the FB pin voltage (VFB) is below the error amplifier output voltage (EAO), which indicates an insufficient output voltage. The on period is determined by the output voltage and input voltage to make the switching frequency fairly constant over the input voltage range.

After the on-period elapses, the HS-FET is turned off, The HS-FET is turned on again when V<sub>FB</sub> drops below EAO. By repeating operation in this way, the converter regulates the output voltage. The integrated low-side MOSFET (LS-FET) is turned on when the HS-FET is in its off state to minimize conduction loss. There is a dead short between the input and GND if both the HS-FET and LS-FET are turned on at the same time. This is called shoot-through. To avoid shoot-through, a dead-time (DT) is generated internally between the HS-FET off and LS-FET on period or the LS-FET off and HS-FET on period.

Internal compensation is applied for COT control to provide a more stable operation and fast transient response, even when ceramic capacitors are used as output capacitors.

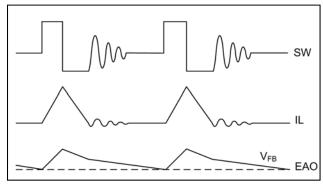

#### MODE SELECTION AT LIGHT-LOAD OPERATION

The IS32PM3426 has a FPWM pin that can offer two states of operations, FCCM mode and PFM mode, at light load condition. If the voltage of FPWM pin higher than V<sub>FPWM IH</sub>, IS32PM3426 operates in Forced Continuous Conduction Mode (FCCM) at light-load conditions and allows the inductor current to become negative. With FCCM mode, the operating frequency is maintained at a fairly constant level over the entire load range from light-load to full-load, that minimizes output voltage ripple and avoid the operating frequency dropping into audible frequency range (≤20kHz) which may introduce some audible noise.

However, if the voltage of FPWM pin is lower than V<sub>FPWM II</sub>. IS32PM3426 operates in Pulse-Frequency Modulation (PFM) mode during light-load operation and reduces the switching frequency automatically to maintain high efficiency, the inductor current drops almost to zero. The HS-FET turns on when the FB pin voltage (VFB) is below the error amplifier output voltage (EAO). The HS-FET turns off when the ontimer elapses and the inductor current is higher than its given threshold. When the inductor current reaches zero, the LS-FET driver goes into tri-state (Hi-Z). As shown in Figure 2. Therefore, the output capacitors discharge slowly to GND through the LS-FET and the resistors R<sub>FBT</sub> and R<sub>FBB</sub>. This operation improves device efficiency greatly when the output current is low.

Figure 2 PFM Operation Mode at Light-load

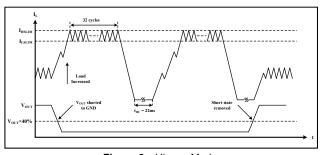

#### **OVER-CURRENT PROTECTION (OCP)**

The IS32PM3426 senses both HS-FET and LS-FET currents for cycle-by-cycle peak and valley current limit and uses to protect the output from an overcurrent or short-circuit protection condition. If the converter is over-current and eventually the HS-FET current hits the HS-FET current limit threshold IHSLIM, the HS-FET turns off to limit the increasing current. Then the LS-FET turns on and monitors the current flowing through it. The HS-FET waits until the LS-FET current ramps down to LS-FET current limit (ILSLIM) before turning on again. As a result, the converter operates in inductor current hysteretic control, upper threshold I<sub>HSLIM</sub> and lower threshold I<sub>LSLIM</sub>. This represents the maximum output current from the converter and is given approximately by the following equation:

$$I_{OUT\_MAX} = \frac{(I_{HSLIM} + I_{LSLIM})}{2} \tag{1}$$

When the load current is higher than IOUT MAX, the output voltage tends to drop because the load current demand is higher than what the converter can support. If the hysteretic control operating persists for 32 switching cycles and the output voltage falls below the output under-voltage threshold (Typ. 40% of the regulation voltage), the converter enters hiccup mode to restart the part periodically with the hiccup time t<sub>HC</sub> (Typ. 22ms). As shown in Figure 3. The hiccup protection mode is especially useful when the output is dead-shorted to ground. This reduces the average short-circuit current greatly, alleviating thermal issues and protecting the converter. The converter exits hiccup mode once the over-current or short-circuit condition is removed.

Figure 3 Hiccup Mode

Due to FCCM operation, when the output current is less than half of the peak-to-peak inductor current ripple, the inductor valley current ramps down to negative (LS-FET sinks current). The IS32PM3426 also incorporates a negative current limit to protect the LS-FET against sinking excessive current and possibly damaging the converter. If the LS-FET sink current hits the negative current limit (ILSRS), the LS-FET turns off until after the next HS-FET on-time.

#### **OVER-VOLTAGE PROTECTION (OVP)**

The IS32PM3426 monitors the FB pin voltage to detect over-voltage condition. When V<sub>FB</sub> becomes higher than 110% (Typ.) of the regulation feedback voltage V<sub>FB</sub> TH, the over-voltage protection (OVP) is triggered after a deglitch time of 16µs (Typ.). The converter stops switching and does not resume until the V<sub>FB</sub> drops to V<sub>FB\_TH</sub>. The OVP function protects the downstream devices from over-voltage damage.

#### **VDD REGULATOR**

The IS32PM3426 contains a linear regulator (VDD) with 5V (Typ.) output voltage to supply internal circuit blocks including the control logic circuits and the HS-/LS-FET gate drivers. The V<sub>DD</sub> regulator is internally current limited to IDD LIM (Min. 20mA). It operates in full V<sub>CC</sub> range, When the V<sub>CC</sub> voltage exceeds 5V, the regulator will stabilize at 5V (Typ.) output, but if V<sub>CC</sub> is lower than 5V, its output decreases with Vcc. During operation, driving HS-/LS-FET gates will draw transient high current from this linear regulator. Therefore, a 1µF low ESR, X7R type ceramic capacitor is necessary from VDD pin to GND; it must be placed as close to VDD pin as possible. V<sub>DD</sub> can be used to bias external low current circuitry requiring a reference supply, such as pulling up bias voltage for PG pin. However, to ensure system stability, do not recommend powering any high current external device with the VDD pin.

#### **FLOATING DRIVER** AND **BOOTSTRAP CHARGING**

The gate driver of the integrated HS-FET requires a voltage above Vcc as an input power supply. As the circuit diagram shown in Figure 4, the VDD regulator is the power supply of the gate driver. The BST pin is internally connected to the output of the VDD regulator through a P-FET switch. Connect a ceramic capacitor between BST and SW pins. The VDD regulator charges the CBST capacitor during HS-FET off and LS-FET on cycles. Then in HS-FET on cycles, the C<sub>BST</sub> charge voltage is used to boost the BST pin to 5V higher than SW pin.

A 0.1µF X7R ceramic capacitor will work well in most applications. The gate driver also has an undervoltage lockout detection. The gate driver is enabled when the voltage on the CBST rises to above 2.86V (Typ.) and disabled when the voltage on the CBST drops below 2.55V (Typ.).

Figure 4 Bootstrap Charging Circuit

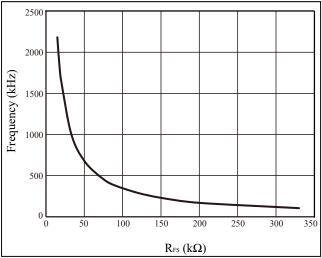

#### SWITCHING FREQUENCY

During switching, the IS32PM3426 operates in a constant on-time mode. The on-time is adjusted by the external resistor, RFS, which is connected from the FS pin to AGND. The IS32PM3426 supports switching frequency (fsw) from 100kHz to 2.2MHz which can be calculated by below Equation:

$$f_{SW} = \frac{1}{(1 + R_{FS}) \times 0.029}$$

(2)

Where  $f_{SW}$  is in MHz and  $R_{FS}$  is in  $k\Omega$ .

Figure 5 Frequency vs. R<sub>FS</sub>

Higher frequency operation results in smaller component size but increases the switching losses. It may also increase the high-side MOSFET gate driving current and may not allow sufficient high or low duty cycle. Lower frequency gives better performance but results in larger component size. In automotive applications, a switching frequency of 400kHz or 2.1MHz is good choice to compromise for both component size and efficiency while keeping the switching noise out of the sensitive frequency bands to easily pass EMI test.

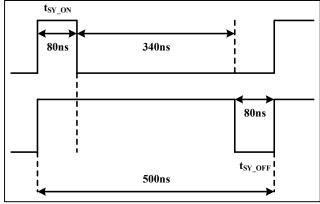

#### SWITCHING FREQUENCY SYNCHRONIZATION

The FS pin can also be used as a synchronization input, allowing the IS32PM3426 to operate with an external clock in the range of 100kHz to 2.2MHz as long as its pulse width satisfies the requirements of t<sub>SYNC MIN</sub>. Figure 6 shows the timing for a synchronization clock into the IS32PM3426 at 2MHz. Any pulse with a duty cycle of 16% to 84% at 2MHz

can be used to synchronize the IC. However, driving FS pin with a 50% duty cycle waveform is always a good choice.

Table 1 Synchronization Duty Cycle Range

| SYNC Clock<br>Frequency(kHz) | Duty Cycle Range (%) |

|------------------------------|----------------------|

| 2000                         | 16~84                |

| 1000                         | 8~92                 |

| 400                          | 3.2~96.8             |

Figure 6 2MHz SYNC Application Example

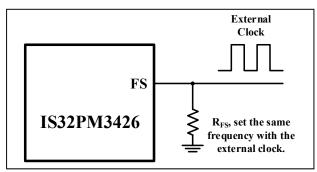

When an external synchronization clock is applied to the FS pin, the internal oscillator is over-driven so that each switching cycle begins at the rising edge of external clock. The high level of the external clock must be not lower than 2V and low level must be not higher than 0.4V. The FS pin should not be left floating. otherwise, the operating switching frequency will be 400kHz. It recommends connecting a resistor R<sub>FS</sub> from FS pin to GND, as shown in Figure 7, such that the internal oscillator frequency is the same as the target clock frequency when the IS32PM3426 is synchronized to an external clock. This allows the regulator to continue operating at approximately the same switching frequency if the external clock fails.

Figure 7 FS Pin Configuration

#### SPREAD SPECTRUM

A switch mode controller can be troublesome when EMI is concerned. To optimize EMI performance, IS32PM3426 includes a spread spectrum feature, which is an 800Hz (Typ.) with ±5% (Typ.) operating frequency jitter. lt can spread the

electromagnetic emitting energy into a wider range that significantly degrades the peak energy of EMI profile. With spread spectrum, the EMI test can be passed with smaller size and lower cost filter circuit.

#### **SOFT-START**

The IS32PM3426 features an internal 2ms (Typ.) softstart function. The soft-start function of IS32PM3426 allows the converter to gradually reach a steady-state operating point, thereby dampening the inrush current to an acceptable value at startup. When the EN pin is set to start the converter operation, the internal softstart circuitry generates a ramping up voltage with a controlled slope. When it is lower than the internal reference of error amplifier (EA), the soft-start voltage overrides EA's reference so the EA uses the soft-start voltage as the reference. Once the soft-start voltage exceeds EA's reference, EA's reference regains loop control. The soft-start period time is internally fixed at 2ms (Typ.) and not adjustable.

If the output capacitor is pre-biased at startup, the converter initiates switching and start ramping up only after the internal soft-start voltage becomes greater than the FB pin voltage V<sub>FB</sub>. This scheme ensures that the converters ramp up smoothly into regulation point.

#### **POWER GOOD (PG)**

The IS32PM3426 has a dedicated flag output pin, PG, to indicate output power good state. The PG pin is open drain structure which requires an external pullup resistor connected to a voltage source. The recommended pull-up resistor is 47kΩ. The PG pin goes high after a delay time t<sub>PG\_RF</sub> (Typ. 120µs) if the output voltage is within 93% to 107% of the nominal voltage; while it goes low after a delay time tpg RF (Typ. 120µs) if the output voltage is above 107% or below 93% of the nominal voltage. To prevent glitch both the upper and lower thresholds include 2% of hysteresis.

The PG pin is also actively pulled low during several other conditions, including EN low, VCC/VDD UVLO protection, output OVP protection and thermal shutdown protection.

#### LOW DROPOUT OPERATION

The IS32PM3426 supports low dropout operation. When the V<sub>CC</sub> voltage is close to the output voltage and the minimum off-time is triggered, the switching on timer is extended to avoid output voltage drops. The switching frequency decreases accordingly. After the maximum on time is triggered (Typ. 10µs), switching enters max duty cycle operation. If the Vcc voltage continues to decrease, the output voltage will begin to gradually decrease with the V<sub>CC</sub> voltage.

#### **ENABLE CONTROL**

The EN pin has a dual-level threshold. When the EN voltage is below V<sub>EN\_VDD\_L</sub>, the regulator is in an ultralow current shutdown mode. When the EN voltage is greater than V<sub>EN\_VDD\_H</sub>, but less than V<sub>EN\_VOUT\_H</sub>, the

$V_{\text{DD}}$  regulator is in standby mode. In standby mode, the  $V_{\text{CC}}$  bias  $V_{\text{DD}}$  regulator is active but converter switching remains disabled. When the voltage at the EN pin exceeds the threshold  $V_{\text{EN\_VOUT\_H}}$ , normal switching operation begins. Use an external resistor voltage divider from VCC to GND to set the minimum operating voltage of the convertor. If the EN voltage is lower than  $V_{\text{EN\_VDD\_L}}$ , the whole system will shut down.

Never leave the EN pin floating. The EN pin is high impedance and high-voltage tolerance and can be connected directly to VCC pin if the EN pin is unused. However, a series resistor (recommended value of  $47k\Omega$ ) is required to limit the current flowing in to EN pin if it is higher than the V<sub>CC</sub> voltage at any time.

#### **UNDER-VOLTAGE LOCKOUT PROTECTION**

The IS32PM3426 has two Under-voltage Lockout (UVLO) protections:  $V_{\text{DD}}$  UVLO and  $V_{\text{CC}}$  UVLO. The IS32PM3426 starts up only when both  $V_{\text{DD}}$  and  $V_{\text{CC}}$  exceed their respective UVLO threshold and shuts down when either  $V_{\text{DD}}$  is lower than the  $V_{\text{DD}}$  UVLO falling threshold voltage or  $V_{\text{CC}}$  is lower than the  $V_{\text{CC}}$  UVLO falling threshold. Both are non-latch off protections.

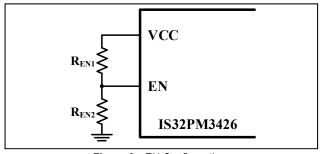

Besides this internal fixed UVLO, it may be desirable to externally set a higher UVLO threshold for some applications. A precise EN threshold voltage can be set by using a resistor voltage divider between VCC and GND with the center connected to the EN pin. As shown in Figure 8. The external UVLO threshold voltage can be computed by the following Equations:

$$V_{CC\_UVEXR} = \frac{(R_{EN1} + R_{EN2})}{R_{EN2}} \times V_{EN\_OUT\_H}$$

(3)

$$V_{CC\_UVEXF} = \frac{(R_{EN1} + R_{EN2})}{R_{EN2}} \times (V_{EN\_VOUT\_H} - V_{EN\_VOUT\_HY})$$

(4)

The output regulation is enabled when the  $V_{\text{CC}}$  voltage exceeds  $V_{\text{CC\_UVEXR}}$  and disabled when the  $V_{\text{CC}}$  voltage falls below  $V_{\text{CC\_UVEXF}}$ .

It is recommended that  $R_{\text{EN1}}$  and  $R_{\text{EN2}}$  be 1% accuracy resistors with good temperature characteristics to ensure a precise detection. On the PCB layout, this resistor divider must be placed as close as possible to the EN pin to avoid noise coupling into the UVLO detection.

Figure 8 EN Configuration

#### THERMAL SHUTDOWN

The temperature of the die is monitored to protect the converter from damage when the maximum junction temperature is exceeded. If the die temperature exceeds the thermal shutdown temperature of 175°C (Typ.) the converter will stop switching and enter standby mode. After a thermal shutdown event, the IS32PM3426 will try to restart when its die temperature has reduced to less than 155°C (Typ.).

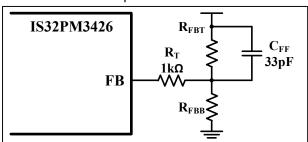

#### **SETTING THE OUTPUT VOLTAGE**

The external resistor divider, R<sub>FBT</sub> and R<sub>FBB</sub>, is used to set the output voltage (As shown in Figure 9), according to the following equation:

$$V_{OUT} = \frac{(R_{FBB} + R_{FBT})}{R_{FBB}} \times V_{FB\_TH}$$

(5)

Where V<sub>FB\_TH</sub>=1V (Typ.).

Choose a value for the resistor  $R_{\text{FBB}}$  should be reasonable. Usually, a small  $R_{\text{FBB}}$  leads to considerable quiescent current loss, while a large  $R_{\text{FBB}}$  makes the FB pin noise-sensitive and voltage errors from the  $V_{\text{FB}}$  input current to be noticeable.

In order to have an accurate output voltage, precision resistors are preferred ( $\pm 1\%$  recommended). The R<sub>FBT</sub> and R<sub>FBB</sub> resistors should be placed as close as possible to the IS32PM3426 with minimal trace length to the FB and AGND pins.

Figure 9 Feedback Network

In addition, it should be noted that the resistor  $R_T$  and capacitor  $C_{FF}$  are required, and the  $R_T$  is fixed at  $1k\Omega$ , while the  $C_{FF}$  is fixed at 33pF.

#### **SELECTING THE INDUCTOR**

An inductor is necessary for supplying constant current to the output load while being driven by the switched input voltage. Inductor value involves tradeoffs in performance. A larger inductance reduces output current ripple and output voltage ripple but brings a large physical size, higher Direct Current Resistance (DCR) and lower saturation current. A small inductance has compact physical size and lower cost but introduces higher ripple in the output. Use the following Equation (6) to estimate the approximate inductor value:

$$L = \frac{(V_{CC} - V_{OUT}) \times V_{OUT}}{f_{SW} \times \Delta I_L \times V_{CC}}$$

(6)

Where  $\Delta I_L$  is the peak-to-peak inductor current ripple which usually is chosen to be 30%~50% of the maximum output current.

Select an inductor with a rated current greater than the maximum output current. To prevent inductance saturation, the saturation current of the selected inductor ( $I_{SAT}$ ) must be higher than the maximum inductor peak current ( $I_{L_PK}$ ) with some safety margin. The peak current can be calculated with Equation (7):

$$I_{L\_PK} = I_{OUT\_MAX} + \frac{1}{2} \times \Delta I_L \tag{7}$$

Where IOUT\_MAX is the maximum output current.

Meantime, the  $I_{L\_PK}$  should not exceed the minimum value of the HS-FET current limit ( $I_{HSLIM}$ ), otherwise the converter may not be able to delivery desired output current. If needed, increase the inductor value to reduce the inductor current ripple ( $\Delta I_L$ ) and ensure that  $I_{L\_PK}$  does not exceed the HS-FET current limit level. A shielded type inductor with low DCR is recommended in most applications, which gives better EMI and efficiency performance.

#### **SELECTING THE INPUT CAPACITOR**

For step-down converter, the input current is discontinuous, which requires a capacitor to supply the AC input current to maintaining the DC input voltage. The X7R type ceramic capacitors are recommended for best performance, and make sure that the capacitors are placed as close to VCC pin as possible.

It requires the capacitor ripple current rating should higher than the maximum input ripple current of converter, which can be calculated with Equation (8):

$$I_{CVCC} = I_{OUT\_MAX} \times \sqrt{\frac{v_{OUT}}{v_{CC}}} \times (1 - \frac{v_{OUT}}{v_{CC}})$$

(8)

The worse-case condition occurs at  $V_{CC}$ =  $2V_{OUT}$ ,

As shown in Equation (9):

$$I_{CVCC} = \frac{I_{OUT\_MAX}}{2} \tag{9}$$

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current. The capacitance value determines the input voltage ripple of the converter. When select the desired input voltage ripple  $\Delta V_{CC}$ , the minimum input capacitor  $C_{VCC}$  can be calculated with Equation (10):

$$C_{VCC} = \frac{I_{OUT\_MAX}}{f_{SW} \times \Delta V_{CC}} \times \frac{V_{OUT}}{V_{CC}} \times \left(1 - \frac{V_{OUT}}{V_{CC}}\right)$$

(10)

The worse-case condition occurs at  $V_{CC}$ =  $2V_{OUT}$ .

As shown in Equation (11):

$$C_{VCC} = \frac{1}{4} \times \frac{I_{OUT\_MAX}}{f_{SW} \times \Delta V_{CC}}$$

(11)

#### SELECTING THE OUTPUT CAPACITOR

An output capacitor is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors can be used. But for best performance, use low ESR capacitors to keep output ripple low.

If the desired output voltage ripple  $\Delta V_{OUT}$  is determined, the minimum  $C_{OUT}$  can be calculated with Equation (12):

$$C_{OUT} = \frac{\Delta I_L}{8 \times f_{SW}(\Delta V_{OUT} - \Delta I_L \times ESR)}$$

(12)

However, in the case of ceramic applications, the output voltage ripple is caused mainly by the capacitance due to the low ESR of ceramic. For simplification, the minimum  $C_{\text{OUT}}$  can be estimated with Equation (13):

$$C_{OUT} = \frac{\Delta I_L}{8 \times f_{SW} \times \Delta V_{OUT}} \tag{13}$$

Note that the effective capacitance of ceramic capacitors decreases with DC bias. For larger bulk values of capacitance and lower cost, low ESR type electrolytic capacitors are usually used to be connected in parallel with the ceramic capacitors. However, electrolytic capacitors have poor tolerance, especially over temperature, and the selected value should be selected larger than the calculated value to allow for temperature variation.

Table 1 Recommended Component Values (Vcc= 12V Battery System)

| Switching<br>Frequency(kHz) | Output Voltage<br>(V) | R <sub>FBT</sub> (kΩ) | R <sub>FBB</sub> (kΩ) | L <sub>1</sub> (µH) | C <sub>FF</sub> (pF) | Соит (µF) |

|-----------------------------|-----------------------|-----------------------|-----------------------|---------------------|----------------------|-----------|

|                             | 3.3                   | 100                   | 43.5                  | 8.2                 | 33                   | 40 to 66  |

| 400                         | 5                     | 100                   | 25                    | 10                  | 33                   | 40 to 66  |

|                             | 8                     | 100                   | 14.3                  | 8.2                 | 33                   | 40 to 66  |

|                             | 3.3                   | 100                   | 43.5                  | 1.8                 | 33                   | 40 to 66  |

| 2100                        | 5                     | 100                   | 25                    | 2.2                 | 33                   | 40 to 66  |

|                             | 8                     | 100                   | 14.3                  | 1.8                 | 33                   | 40 to 66  |

#### **Application Example**

Figure 10 f<sub>SW</sub>= 400kHz 5V/2A Output Application Example

Figure 11 f<sub>SW</sub>= 2.1MHz 5V/2A Output Application Example

#### LAYOUT CONSIDERATION

As for all switching power supplies, especially those providing high current and using high switching frequencies, layout is an important design step. If layout is not carefully done, the operation could show instability as well as EMI problems.

The high dV/dt surface and dI/dt loops are big noise emission source. To optimize the EMI performance,

keep the area size of all high switching frequency points with high voltage compact. Meantime keep all traces carrying high current as short as possible to minimize the loops.

(1) Wide traces should be used for connection of the high current paths that helps to achieve better efficiency and EMI performance. Such as the traces of power supply, inductor L<sub>1</sub>, output load and ground.

LUMISSIL

- (2) Keep the traces of the switching points shorter. The inductor L<sub>1</sub> should be placed as close to SW pin as possible and the traces of connection between them should be as short and wide as possible.

- (3) To avoid ground jitter, the components of parameter setting should be placed close to the corresponding pins and return to the AGND and keep the traces length to the pins as short as possible. On the other side, to prevent the noise coupling, the output voltage setting resistor divider must be placed as close to FB and AGND as possible. the traces of FB should either be far away or be isolated from high-current paths and high-speed switching nodes. These practices are essential for better accuracy and stability.

- (4) The capacitors  $C_{VCC}$  and  $C_{VDD}$  must be placed as close as possible to VCC and VDD pins for good filtering.

- (5) Place the bootstrap capacitor C<sub>BST</sub> close to BST pin and SW pin to ensure the traces are as short as possible.

- (6) The connection to the output load should be kept short to minimize radiated emission.

- (7) The VCC and PGND pins must be soldered to enough size of copper ground plane with sufficient vias to conduct the heat to opposite side of the PCB for adequate cooling. Flood all unused areas on all layers with copper that reduces the temperature rise of the power components. Connect the copper areas to ground.

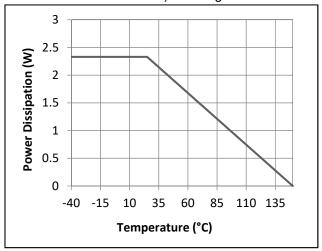

#### THERMAL CONSIDERATION

The package thermal resistance,  $\theta_{JA}$ , determines the amount of heat that can pass from the silicon die to the surrounding ambient environment. The  $\theta_{JA}$  is a measure of the temperature rise created by power dissipation and is usually measured in degree Celsius per watt (°C/W).

When operating the chip at high ambient temperatures, or when driving maximum load current, care must be taken to avoid exceeding the package power dissipation limits. The maximum power dissipation can be calculated using the following Equation (14):

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{\theta_{JA}} \qquad (14)$$

Where  $T_{J(MAX)}$  is the recommended maximum operating junction temperature. So.

$$P_{D(MAX)} = \frac{150 \,^{\circ}\!C - 25 \,^{\circ}\!C}{53.7 \,^{\circ}\!C/W} \approx 2.33W$$

Figure 12, shows the power derating of the IS32PM3426 on a JEDEC boards (in accordance with JESD 51-5 and JESD 51-7) standing in still air.

Figure 12 Dissipation Curve

The thermal resistance is achieved by mounting the IS32PM3426 on a standard FR4 double-sided printed circuit board (PCB) with a copper area of a few square inches on each side of the board under the IS32PM3426. The thermal resistance can be reduced by using a four-layer PCB board. A four-layer layout is strongly recommended to achieve better thermal and EMI performance.

Figure 13 PCB Layout Example (Top Layer)

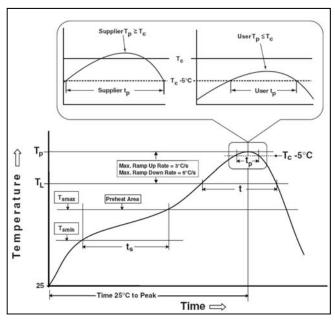

### **CLASSIFICATION REFLOW PROFILES**

| Profile Feature                                                                           | Pb-Free Assembly                 |

|-------------------------------------------------------------------------------------------|----------------------------------|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |

Figure 14 Classification Profile

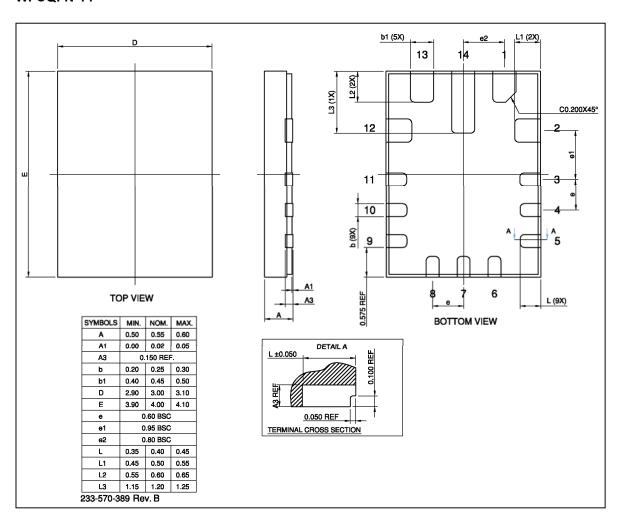

#### **PACKAGE INFORMATION**

#### WFCQFN-14

#### **RECOMMENDED LAND PATTERN**

#### WFCQFN-14

#### Note:

- 1. Land pattern complies to IPC-7351.

- 2. All dimensions in MM.

- 3. This document (including dimensions, notes & specs) is a recommendation based on typical circuit board manufacturing parameters. Since land pattern design depends on many factors unknown (e.g. user's board manufacturing specs), user must determine suitability for use.

### **REVISION HISTORY**

| Revision | Detail Information | Date       |

|----------|--------------------|------------|

| 0A       | Initial release    | 2024.05.06 |