# IQS243 Datasheet IQ Switch® - ProxSense® Series

3 Channel Capacitive Sensor with I<sup>2</sup>C<sup>TM</sup> compatible interface and Compensation for Sensitivity Reducing Objects

#### **Unparalleled Features**

Sub 3uA current consumption

Automatic tuning for optimal operation in various environments

The IQS243 ProxSense<sup>®</sup> IC is a fully integrated 3 channel capacitive contact and proximity sensor with market leading sensitivity and automatic tuning to the sense antenna. The IQS243 provides a cost effective implementation in a small outline package. The device is ready for use in a large range of applications while the I<sup>2</sup>C<sup>TM</sup> compatible interface provides full control to a host.

#### **Main Features**

3 Channel input device

Proximity & Touch on each channel

I2C<sup>™</sup> compatible data output

ATI: Automatic tuning to optimum sensitivity

Supply Voltage 1.8V (abs min) to 3.6V (abs max)

Multiple Power Modes

Internal voltage regulator and reference capacitor

Large proximity detection range

Automatic drift compensation

Development tools available (VisualProxSense and USB dongles)

Small outline MSOP-10

#### **Applications**

White goods and appliances

Office equipment, toys, sanitary ware

Proximity detection that enables backlighting activation (Patented)

Wake-up from standby applications

Replacement for electromechanical switches

GUI trigger and GUI control proximity detection

### Available options

| T <sub>A</sub> | MSOP-10 |

|----------------|---------|

| -40°C to 85°C  | IQS243  |

### **Functional Overview**

### 1 Introduction

The IQS243 is a three channel capacitive proximity and touch sensor featuring an internal voltage regulator and reference capacitor (Cs).

The device has three dedicated input pins for the connection of the sense antennas. Three output pins are used for serial data communication through the I<sup>2</sup>C<sup>TM</sup> compatible protocol, including an optional RDY pin.

The device automatically tracks slow varying environmental changes via various filters, detect noise and has an Automatic Antenna Tuning Implementation (Auto - ATI) to tune the device for optimal sensitivity.

### 1.1 Applicability

All specifications, except where specifically mentioned otherwise, provided by this datasheet are applicable to the following ranges:

Temperature -40℃ to +85℃ Supply voltage (VDDHI) 1.8V to 3.6V

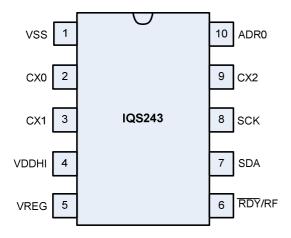

### 1.2 Pin-outs

Figure 1.1 IQS243 Pin layout

Table 1.1 IQS243 Pin-outs.

| Pin | IQS243<br>MSOP 10 | Function                                                  |  |  |

|-----|-------------------|-----------------------------------------------------------|--|--|

| 1   | VSS               | Ground                                                    |  |  |

| 4   | VDDHI             | Power Input                                               |  |  |

| 5   | VREG              | Regulator Pin                                             |  |  |

| 2   | 2 CX0 Sense Ele   |                                                           |  |  |

| 3   | CX1               | Sense Electrode                                           |  |  |

| 9   | CX2               | Sense Electrode                                           |  |  |

| 10  | ADR0              | I <sup>2</sup> C <sup>™</sup> Sub<br>Address<br>Selection |  |  |

| 6   | RDY/RF            | I <sup>2</sup> C <sup>™</sup> Ready or<br>RF input pin    |  |  |

| 7   | SDA               | I <sup>2</sup> C <sup>™</sup> Data                        |  |  |

| 8   | SCK               | I <sup>2</sup> C <sup>™</sup> Clock                       |  |  |

## 2 Analogue Functionality

The analogue circuitry measures the capacitance of the sense antennas attached to the Cx pins through a charge transfer process that is periodically initiated by the digital circuitry. The capacitance measurement circuitry makes use of an internal reference capacitor Cs and voltage reference (VREG).

The measuring process is referred to as a conversion and consists of the discharging of Cs and Cx capacitors, the charging of Cx and then a series of charge transfers from Cx to Cs until a trip voltage is reached. The number of charge transfers required to reach the trip voltage is referred to as the Current Sample (CS).

The analogue circuitry further provides functionality for:

Power On Reset (POR) detection. Brown Out Detection (BOD).

## 3 Digital Functionality

The digital processing functionality is responsible for:

Management of BOD and WDT events.

Initiation of conversions at the selected

Processing of CS and execution of algorithms.

Monitoring and automatic execution of the ATI algorithm.

Signal processing and digital filtering.

Detection of PROX and TOUCH events.

Managing outputs of the device.

Managing serial communications.

## **Detailed Description**

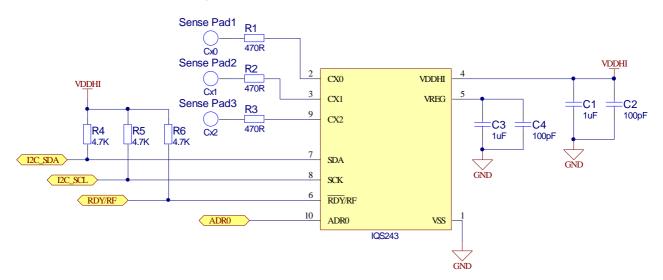

### 4 Reference Design

Figure 4.1 Reference Design.

Use C2 and C4 for added RF noise immunity.

Place C1-C4 as close as possible to IC, connected to good GND.

R4, R5 and R6 used as pull up resistors for  $I^2C^{TM}$  protocol (4.7k to 10k typical).

RDY Pin and R6 required for Event Mode.

Refer to Application Note (AZD008) on key pad design.

## 5 High Sensitivity

Through patented design and advanced signal processing, the device is able to provide extremely high sensitivity to detect proximity. This enables designs that can detect proximities at a much greater range than other capacitive sensors. When the device is used

in the presence of noise or floating metal that lower the sensitivity, a reduced proximity threshold is proposed to ensure reliable functioning of the sensor. The high sensitivity allows the device to sense accurately through overlays with low dielectric constant materials such as wood or even air-gaps.

Please refer to the Application Note Section on the Azoteg website for more design tips and other application dependent recommendations.

### **Adjustable Proximity Threshold**

The proximity threshold is selected by the The IQS243 samples in 4 timeslots. The between the specified limits.

A proximity event is identified when for at least Proximity can be detected by the distributed holds:

$P_{TH} = < LTA-CS$

Where LTA is the Long Term Average

### 7 Adjustable Touch **Thresholds**

The touch threshold is selected by the designer to obtain the desired touch sensitivity and is selectable between 1/255 sensitive) to 254/255 (least sensitive). The IQS243 has a default touch threshold (T<sub>TH</sub>) of 32/255 (for all 3 channels). The touch threshold is expressed as a fraction of the LTA as follows:

$T_{TH}$  = Selected Touch Threshold x LTA Where LTA is the Long Term Average

The touch event is triggered based on T<sub>TH</sub>, CS and LTA. A touch event is identified when for at least 2 consecutive samples the following equation holds:

$T_{TH} = < LTA-CS$

With lower average CS (therefore lower LTA) values the touch threshold will be lower and vice versa. Individual touch threshold can be set for each channel.

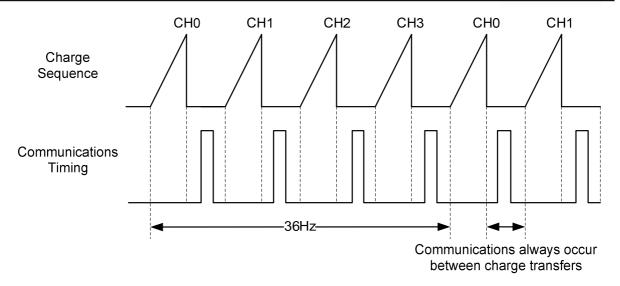

### **Charge Transfers**

designer to obtain the desired proximity charge sequence is shown in Figure 8.1, sensitivity and is selectable between 1 (most where CH0 is the Prox channel, which sensitive) to 254 (least sensitive). The IQS243 charges before each of the 3 input channels. has a default proximity threshold (P<sub>TH</sub>) of 4 for CH0 is realised by connecting all three touch all channels. Proximity thresholds for the electrodes with internal switches. Therefore: sense electrodes are individually adjustable CH0 is a distributed electrode formed by the 3 touch electrodes.

6 consecutive samples the following equation electrode (CRX0+CRX1+CRX2) AND each individual sense electrode (CRX0, CRX1 and CRX2).

### **I2C Communication**

The IQS243 device interfaces to a master controller via a 2 wire serial interface bus that is  $I^2C^{TM}$  compatible. An optional RDY pin is available to indicate the communication window (required for Event Mode).

The IQS243 has four available sub addresses, 44H (default) to 47H that is selected upon purchase of the IC. The ADR0 pin can also be pulled low to increase the I2C address by one decimal value (for example from 44H to 45H).

$I^2C^{TM}$ maximum compatible communication speed for the IQS243 is 400kbit/s.

Please refer to the IQS243 Communications Interface and Sample Code Document for further details.

Figure 8.1 Charging and communications sequence for the IQS243.

## 9.1 Memory Mapping

| Address | Size(Bytes) |                        |          |

|---------|-------------|------------------------|----------|

| 00h-0Fh | 16          | Device Information     | R/W<br>R |

| 10h-30h | 32          | Device Specific Data   | R/W      |

| 31h-34h | 4           | Proximity Status Bytes | R/W<br>R |

| 35h-38h | 4           | Touch Status Bytes     | R/W<br>R |

| 39h-3Ch | 4  | Halt Bytes                    | R/W |

|---------|----|-------------------------------|-----|

|         |    | Trait Bytoo                   | R   |

|         |    |                               |     |

| 3Dh-41h | 4  | Active Bytes (indicate cycle) | R/W |

|         |    | Active bytes (indicate cycle) | R   |

|         |    |                               |     |

| 42h-82h | 64 |                               | R/W |

|         |    |                               |     |

|         |    | Current Samples               |     |

|         |    | •                             |     |

|         |    |                               | R   |

|         |    |                               |     |

| 83h-C3h | 64 |                               | R/W |

|         |    |                               |     |

|         |    | LTAs                          |     |

|         |    |                               |     |

|         |    |                               | R   |

|         |    |                               |     |

| C4h-FDh | 64 |                               | R/W |

|         |    |                               |     |

|         |    | Davida a Callila sa           |     |

|         |    | Device Settings               |     |

|         |    |                               |     |

|         |    |                               | W   |

|         |    |                               |     |

#### 9.1.1 Device Information

Information regarding the device type and version is recorded here. Any other information specific to the device version can be stored here. Each Azoteq ROM has a unique Productand Version number.

00H

|     | Product Number (PROD_NUM) |   |   |   |   |   |   |   |  |  |

|-----|---------------------------|---|---|---|---|---|---|---|--|--|

| Bit | 7                         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|     | 36D                       |   |   |   |   |   |   |   |  |  |

01H

|   |    | Version Number (VERSION_NUM) |   |   |   |   |   |   |   |  |

|---|----|------------------------------|---|---|---|---|---|---|---|--|

| В | it | 7                            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|   |    | 01D                          |   |   |   |   |   |   |   |  |

### 9.1.2 Device Specific Data

10H

|     |            | System Status Flags (SYSFLAGS) |            |            |            |             |             |      |   |  |  |

|-----|------------|--------------------------------|------------|------------|------------|-------------|-------------|------|---|--|--|

| Bit | 7          | 6                              | 5          | 4          | 3          | 2           | 1           | 0    |   |  |  |

|     | System use | System use                     | System use | System use | System use | ATI<br>Busy | RF<br>Noise | Zoom | R |  |  |

| ATI BUSY | Indicates whether the device is performing an ATI '0': ATI not Busy '1': ATI Busy |

|----------|-----------------------------------------------------------------------------------|

| RF Noise | Indicates whether RF noise is detected "0": Not Detected "1": Detected            |

| Zoom     | Indicates whether the device is in Zoom mode "0": Not in Zoom "1": In Zoom        |

### 9.1.3 Proximity Status Bytes

The proximity status of all the channels on the device are shown here. If a byte is set it indicates a proximity condition on the specified channel.

31H

|    |            | Proximity (PROX_STAT) |            |            |     |     |     |     |   |  |  |

|----|------------|-----------------------|------------|------------|-----|-----|-----|-----|---|--|--|

| Bi | t 7        | 6                     | 5          | 4          | 3   | 2   | 1   | 0   |   |  |  |

|    | System use | System use            | System use | System use | CH3 | CH2 | CH1 | CH0 | R |  |  |

The SHOW\_RESET byte is automatically set whenever the device is reset. Setting the Ack Reset byte in the Proxsense Module Settings 2 register clears the SHOW\_RESET byte.

32H

|     |            | Show Reset (SHOW_RESET) R/ |            |            |            |            |            |            |   |  |  |

|-----|------------|----------------------------|------------|------------|------------|------------|------------|------------|---|--|--|

| Bit | 7          | 6                          | 5          | 4          | 3          | 2          | 1          | 0          |   |  |  |

|     | SHOW_RESET | System use                 | System use | System use | System use | System use | System use | System use | R |  |  |

### 9.1.4 Touch Status Bytes

The touch status of all the channels on the device are shown here. If a byte is set it indicates a touch condition on the specified channel.

35H

|           | Touch Status 0 (TOUCH_STAT0) |            |            |            |     |     |     |            |   |  |

|-----------|------------------------------|------------|------------|------------|-----|-----|-----|------------|---|--|

| Bit 7 6 5 |                              |            |            | 4          | 3   | 2   | 1   | 0          |   |  |

|           | System use                   | System use | System use | System use | СНЗ | CH2 | CH1 | System use | R |  |

36H

|     |            |            | Touch      | Status 1 ( | TOUCH_S    | STAT1)     |            |            | R/W |

|-----|------------|------------|------------|------------|------------|------------|------------|------------|-----|

| Bit | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |     |

|     | System use | R   |

### 9.1.5 Halt Bytes

The filter halt status of all the channels on the device are shown here. If a byte is set it indicates that the filters have been halted on the specified channel.

39H

|     | Halt 0 (HALT_STAT0) |            |            |            |     |     |     |     |   |  |

|-----|---------------------|------------|------------|------------|-----|-----|-----|-----|---|--|

| Bit | 7 6 5 4 3 2 1 0     |            |            |            |     |     |     |     |   |  |

|     | System use          | System use | System use | System use | СНЗ | CH2 | CH1 | CH0 | R |  |

3AH

|     |                 | Halt 1 (HALT_STAT1) |            |            |            |            |            |            |   |  |  |

|-----|-----------------|---------------------|------------|------------|------------|------------|------------|------------|---|--|--|

| Bit | 7 6 5 4 3 2 1 0 |                     |            |            |            |            |            |            |   |  |  |

|     | System use      | System use          | System use | System use | System use | System use | System use | System use | R |  |  |

#### 9.1.6 Channel Number

The decimal number in the Active Channel register indicates the active channel.

3DH

|     |   |                                                      | Activ | e Channe | el (ACT_CI | HAN) |  |  | R/W |  |  |  |

|-----|---|------------------------------------------------------|-------|----------|------------|------|--|--|-----|--|--|--|

| Bit | 7 | 7 6 5 4 3 2 1 0                                      |       |          |            |      |  |  |     |  |  |  |

|     |   | Decimal Number indicating active channel (CH0 – CH3) |       |          |            |      |  |  |     |  |  |  |

### 9.1.7 Current Samples

The Current Samples stored in this register are from the current cycle only as indicated in the Active Channel register.

42H

|     | Current Sample High (CUR_SAM_HI) |   |   |   |   |   |   |   |  |  |

|-----|----------------------------------|---|---|---|---|---|---|---|--|--|

| Bit | 7                                | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|     | HIGH byte                        |   |   |   |   |   |   |   |  |  |

43H

|     |   |                 | Current | Sample Lo | w (CUR_S | SAM_LO) |  |  | R/W |  |  |  |

|-----|---|-----------------|---------|-----------|----------|---------|--|--|-----|--|--|--|

| Bit | 7 | 7 6 5 4 3 2 1 0 |         |           |          |         |  |  |     |  |  |  |

|     |   | LOW byte        |         |           |          |         |  |  |     |  |  |  |

### 9.1.8 Long-Term Averages

The Long-Term Averages stored in this register are from the current cycle only.

83H

|     | Long-Term Average High (LTA_HI) |  |  |  |  |  |  |  |  |  |

|-----|---------------------------------|--|--|--|--|--|--|--|--|--|

| Bit | 7 6 5 4 3 2 1 0                 |  |  |  |  |  |  |  |  |  |

|     | HIGH byte                       |  |  |  |  |  |  |  |  |  |

84H

|     |          |                 | Long-To | erm Avera | ge Low (L | .TA_LO) |  |  | R/W |  |  |  |

|-----|----------|-----------------|---------|-----------|-----------|---------|--|--|-----|--|--|--|

| Bit | 7        | 7 6 5 4 3 2 1 0 |         |           |           |         |  |  |     |  |  |  |

|     | LOW byte |                 |         |           |           |         |  |  |     |  |  |  |

#### 9.1.9 Device Settings

Target Count 0 and 1 sets the target CS value for the respective channels. If data is written to one of these channels and the LTA is out of range a re-ATI event will occur, unless a touch condition is active on the channel where the re-ATI will wait until the touch condition is lifted. The default target CS for CH0 with a register value Target Count CH0 = 128 then becomes 128\*8=1024. The device will re-ATI when the LTA drifts out of the Target  $\pm$  128 (default) range.

C4H

|     | Target Count CH0 (TARGET_CNT0) |  |          |           |             |           |  |  |  |  |  |  |

|-----|--------------------------------|--|----------|-----------|-------------|-----------|--|--|--|--|--|--|

| Bit | 7 6 5 4 3 2 1 0                |  |          |           |             |           |  |  |  |  |  |  |

|     | Target Count Value (x8)        |  |          |           |             |           |  |  |  |  |  |  |

|     |                                |  | Default: | 128 Decim | nal (re-ATI | boundary) |  |  |  |  |  |  |

C5H

|     |                                        |                 | Targe | et Count ( | TARGET_0 | CNT1) |  |  | R/W |  |  |  |  |

|-----|----------------------------------------|-----------------|-------|------------|----------|-------|--|--|-----|--|--|--|--|

| Bit | 7                                      | 7 6 5 4 3 2 1 0 |       |            |          |       |  |  |     |  |  |  |  |

|     | Target Count Value (x8) for CH1 – CH3  |                 |       |            |          |       |  |  |     |  |  |  |  |

|     | Default: 128 Decimal (re-ATI boundary) |                 |       |            |          |       |  |  |     |  |  |  |  |

The compensation for each channel can be set by writing the appropriate value to the corresponding channels Compensation Register. The Compensation directly influences the sensitivity of a Channel and will trigger a re-ATI when the LTA of the respective channels are out of range.

C6H

|     | Channel 0 Compensation Setting (CH0_COMP) |                 |   |           |             |   |  |  |     |  |  |  |

|-----|-------------------------------------------|-----------------|---|-----------|-------------|---|--|--|-----|--|--|--|

| Bit | 7                                         | 7 6 5 4 3 2 1 0 |   |           |             |   |  |  |     |  |  |  |

|     |                                           |                 | C | Compensat | tion 0 <5:0 | > |  |  | R/W |  |  |  |

C7H

|     |                      | Cha             | nnel 1 Co | mpensatio | on Setting | (CH1_CO | MP) |  | R/W |  |  |  |

|-----|----------------------|-----------------|-----------|-----------|------------|---------|-----|--|-----|--|--|--|

| Bit | 7                    | 7 6 5 4 3 2 1 0 |           |           |            |         |     |  |     |  |  |  |

|     | Compensation 1 <5:0> |                 |           |           |            |         |     |  |     |  |  |  |

C8H

|     | Channel 2 Compensation Setting (CH2_COMP) |                 |  |  |  |  |  |  |  |  |  |  |

|-----|-------------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|--|

| Bit | 7                                         | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |

|     | Compensation 2 <5:0>                      |                 |  |  |  |  |  |  |  |  |  |  |

С9Н

|     |   | Cha             | nnel 3 Co | mpensatio | on Setting  | (CH3_CO | MP) |  | R/W |  |  |

|-----|---|-----------------|-----------|-----------|-------------|---------|-----|--|-----|--|--|

| Bit | 7 | 7 6 5 4 3 2 1 0 |           |           |             |         |     |  |     |  |  |

|     |   |                 | C         | Compensat | tion 3 <5:0 | >       |     |  | R/W |  |  |

CAH

|     |   |                 |  | Syste | m Use |  |  |  | R/W |  |  |

|-----|---|-----------------|--|-------|-------|--|--|--|-----|--|--|

| Bit | 7 | 7 6 5 4 3 2 1 0 |  |       |       |  |  |  |     |  |  |

|     |   |                 |  | Syste | m Use |  |  |  | R/W |  |  |

СВН

|     |   | System Use      |  |  |  |  |  |  |  |  |

|-----|---|-----------------|--|--|--|--|--|--|--|--|

| Bit | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |

|     |   | System Use      |  |  |  |  |  |  |  |  |

**CCH**

|     |   |   |   | Syste  | m Use |   |   |   | R/W |

|-----|---|---|---|--------|-------|---|---|---|-----|

| Bit | 7 | 6 | 5 | 4      | 3     | 2 | 1 | 0 |     |

|     |   |   |   | Syster | m Use |   |   |   | R/W |

**CDH**

|     | System Use      |            |  |  |  |  |  |  |  |  |

|-----|-----------------|------------|--|--|--|--|--|--|--|--|

| Bit | 7 6 5 4 3 2 1 0 |            |  |  |  |  |  |  |  |  |

|     |                 | System Use |  |  |  |  |  |  |  |  |

CEH

|     | System Use      |  |  |  |  |  |  |  |  |  |

|-----|-----------------|--|--|--|--|--|--|--|--|--|

| Bit | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |

|     | System Use      |  |  |  |  |  |  |  |  |  |

**CFH**

|     |   | System Use      |  |  |  |  |  |  |  |  |  |

|-----|---|-----------------|--|--|--|--|--|--|--|--|--|

| Bit | 7 | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |

|     |   | System Use      |  |  |  |  |  |  |  |  |  |

The Multiplier Setting register for each Channel sets the gain values which determine the sensitivity and compensation to reach the ATI routine target. The Table below provides a description of the bits that can be set in the CH0 – CH3 Multiplier Setting registers. By writing to the Multiplier Settings of a channel, the individual channel that is active in that specific time slot (indicated in the Channel Sequence 0 and 1 registers) will undergo a re-ATI event if the new multiplier settings results in the LTA being out of range

| .Mul5:Mul4 | Sensitivity Multiplier                                                                                                                                                            |  |  |  |  |  |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Mul3:0     | Compensation Multiplier                                                                                                                                                           |  |  |  |  |  |  |  |  |

| Base1:0    | The base value influences the overall sensitivity of the channel and establishes a base count from where the ATI algorithm starts executing. The following options are available: |  |  |  |  |  |  |  |  |

|            | "00" — 200                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|            | "01" — 50                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|            | "10" — 100                                                                                                                                                                        |  |  |  |  |  |  |  |  |

|            | "11" — 250                                                                                                                                                                        |  |  |  |  |  |  |  |  |

D<sub>0</sub>H

|   |                     |       | C     | channel 0 | Multiplier | Setting (N | NULT_CHO | ))   |      | R/W |

|---|---------------------|-------|-------|-----------|------------|------------|----------|------|------|-----|

| ı | Bit 7 6 5 4 3 2 1 0 |       |       |           |            |            |          |      |      |     |

|   |                     | Base1 | Base0 | Mul5      | Mul4       | Mul3       | Mul2     | Mul1 | Mul0 | R/W |

D1H

|     | Channel 1 Multiplier Setting (MULT_CH1) |       |      |      |      |      |      |      |     |  |

|-----|-----------------------------------------|-------|------|------|------|------|------|------|-----|--|

| Bit | it 7 6 5 4 3 2 1 0                      |       |      |      |      |      |      |      |     |  |

|     | Base1                                   | Base0 | Mul5 | Mul4 | Mul3 | Mul2 | Mul1 | Mul0 | R/W |  |

D2H

|     | Channel 2 Multiplier Setting (MULT_CH2) |       |      |      |      |      |      |      |     |

|-----|-----------------------------------------|-------|------|------|------|------|------|------|-----|

| Bit | Sit 7 6 5 4 3 2 1 0                     |       |      |      |      |      |      |      |     |

|     | Base1                                   | Base0 | Mul5 | Mul4 | Mul3 | Mul2 | Mul1 | Mul0 | R/W |

D3H

|     |                     | C     | Channel 3 | Multiplier | Setting (N | MULT_CH | 3)   |      | R/W |

|-----|---------------------|-------|-----------|------------|------------|---------|------|------|-----|

| Bit | Bit 7 6 5 4 3 2 1 0 |       |           |            |            |         |      |      |     |

|     | Base1               | Base0 | Mul5      | Mul4       | Mul3       | Mul2    | Mul1 | Mul0 | R/W |

D4H

|     |               | System Use      |               |               |               |               |               |               |     |  |  |  |  |

|-----|---------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|--|--|

| Bit | 7             | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |     |  |  |  |  |

|     | System<br>Use | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |  |  |

D5H

|     | System Use    |                 |               |               |               |               |               |               |     |  |  |

|-----|---------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7             | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |     |  |  |

|     | System<br>Use | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |

D<sub>6</sub>H

|     | System Use      |               |               |               |               |               |               |               |     |  |  |

|-----|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |               |     |  |  |

|     | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |

D7H

|     | System Use      |               |               |               |               |               |               |               |     |  |  |

|-----|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |               |     |  |  |

|     | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |

D8H

|     | System Use    |                 |               |               |               |               |               |               |     |  |  |  |

|-----|---------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|--|

| Bit | 7             | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |     |  |  |  |

|     | System<br>Use | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |  |

D9H

|     | System Use      |               |               |               |               |               |               |               |     |  |  |

|-----|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |               |     |  |  |

|     | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |

The proximity sensitivity settings of each respective channel sets the CS threshold for a proximity event on the specified channel (refer to Section 6). A custom value between 1 and 254 can be selected by setting bits PT\_7 to PT\_0.

DAH

|         |      | Proximity Sensitivity Settings CH0 (PROX_TH_CH0) |   |   |   |   |   |   |  |  |  |  |

|---------|------|--------------------------------------------------|---|---|---|---|---|---|--|--|--|--|

| Bit     | 7    | 6                                                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|         | PT_7 | PT_7 PT_6 PT_5 PT_4 PT_3 PT_2 PT_1 PT_0          |   |   |   |   |   |   |  |  |  |  |

|         |      | Custom value between 1 and 254                   |   |   |   |   |   |   |  |  |  |  |

| Default | 0    | 0 0 0 0 1 0 0                                    |   |   |   |   |   |   |  |  |  |  |

**DBH**

|         |      | Proximity Sensitivity Settings CH1 (PROX_TH_CH1) |   |   |   |   |   |   |  |  |  |  |

|---------|------|--------------------------------------------------|---|---|---|---|---|---|--|--|--|--|

| Bit     | 7    | 6                                                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|         | PT_7 | PT_7 PT_6 PT_5 PT_4 PT_3 PT_2 PT_1 PT_0          |   |   |   |   |   |   |  |  |  |  |

|         |      | Custom value between 1 and 254                   |   |   |   |   |   |   |  |  |  |  |

| Default | 0    | 0 0 0 0 1 0 0                                    |   |   |   |   |   |   |  |  |  |  |

**DCH**

|         |               | Proximity Sensitivity Settings CH 2 (PROX_TH_CH2) |  |  |  |  |  |  |  |  |  |  |  |

|---------|---------------|---------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Bit     | 7             | 7 6 5 4 3 2 1 0                                   |  |  |  |  |  |  |  |  |  |  |  |

|         | PT_7          | PT_7 PT_6 PT_5 PT_4 PT_3 PT_2 PT_1 PT_0 F         |  |  |  |  |  |  |  |  |  |  |  |

|         |               | Custom value between 1 and 254                    |  |  |  |  |  |  |  |  |  |  |  |

| Default | 0 0 0 0 1 0 0 |                                                   |  |  |  |  |  |  |  |  |  |  |  |

**DDH**

|         |      | Proximity Sensitivity Settings CH3 (PROX_TH_CH3) |  |  |  |  |  |  |  |  |  |  |

|---------|------|--------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Bit     | 7    | 7 6 5 4 3 2 1 0                                  |  |  |  |  |  |  |  |  |  |  |

|         | PT_7 | PT_7 PT_6 PT_5 PT_4 PT_3 PT_2 PT_1 PT_0          |  |  |  |  |  |  |  |  |  |  |

|         |      | Custom value between 1 and 254                   |  |  |  |  |  |  |  |  |  |  |

| Default | 0    | 0 0 0 0 1 0 0                                    |  |  |  |  |  |  |  |  |  |  |

**DEH**

|     |               | System Use R    |               |               |               |               |               |               |     |  |  |  |

|-----|---------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|--|

| Bit | 7             | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |     |  |  |  |

|     | System<br>Use | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |  |

The touch sensitivity setting of each respective channel sets the CS threshold for a touch event on the specified channel. A custom value between 1 and 254 can be selected by setting bits.

DFH

|         |      | Touch Sensitivity Settings CH1 (TOUCH_TH_CH1)     |  |  |  |  |  |  |  |  |  |  |  |

|---------|------|---------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Bit     | 7    | 7 6 5 4 3 2 1 0                                   |  |  |  |  |  |  |  |  |  |  |  |

|         | TT_7 | TT_7                                              |  |  |  |  |  |  |  |  |  |  |  |

|         |      | Custom value between 1 and 254, used as value/255 |  |  |  |  |  |  |  |  |  |  |  |

| Default |      | 32/255                                            |  |  |  |  |  |  |  |  |  |  |  |

E0H

|         |      | Touch                                             | Sensitivi | ty Setting | s CH2 (T | OUCH_TH | I_CH2) |   | R/W |  |

|---------|------|---------------------------------------------------|-----------|------------|----------|---------|--------|---|-----|--|

| Bit     | 7    | 6                                                 | 5         | 4          | 3        | 2       | 1      | 0 |     |  |

|         | TT_7 | TT_7 TT_6 TT_5 TT_4 TT_3 TT_2 TT_1 TT_0           |           |            |          |         |        |   |     |  |

|         |      | Custom value between 1 and 254, used as value/255 |           |            |          |         |        |   |     |  |

| Default |      |                                                   |           | 32/        | 255      |         |        |   |     |  |

E1H

|         |      | Touch Sensitivity Settings CH3 (TOUCH_TH_CH3)     |  |     |     |  |  |  |  |  |  |  |

|---------|------|---------------------------------------------------|--|-----|-----|--|--|--|--|--|--|--|

| Bit     | 7    | 7 6 5 4 3 2 1 0                                   |  |     |     |  |  |  |  |  |  |  |

|         | TT_7 | TT_7                                              |  |     |     |  |  |  |  |  |  |  |

|         |      | Custom value between 1 and 254, used as value/255 |  |     |     |  |  |  |  |  |  |  |

| Default |      |                                                   |  | 32/ | 255 |  |  |  |  |  |  |  |

E2H

|     |               | System Use    |               |               |               |               |               |               |     |  |  |

|-----|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |     |  |  |

|     | System<br>Use | R/W |  |  |

**E3H**

|     |               | System Use    |               |               |               |               |               |               |     |  |  |

|-----|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |     |  |  |

|     | System<br>Use | R/W |  |  |

E4H

|     |               | System Use    |               |               |               |               |               |               |     |  |  |  |

|-----|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|--|

| Bit | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |     |  |  |  |

|     | System<br>Use | R/W |  |  |  |

E5H

|     |               |               |               | Syste         | m Use         |               |               |               | R/W |

|-----|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|

| Bit | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |     |

|     | System<br>Use | R/W |

E6H

|     |               | System Use      |               |               |               |               |               |               |     |  |  |

|-----|---------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7             | 7 6 5 4 3 2 1 0 |               |               |               |               |               |               |     |  |  |

|     | System<br>Use | System<br>Use   | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |

E7H

|     |               | System Use    |               |               |               |               |               |               |     |  |  |

|-----|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|--|

| Bit | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |     |  |  |

|     | System<br>Use | R/W |  |  |

E8H

|     |            | Prox           | Sense Mo                  | dule Setting | gs 0 (PRO | X_SETTI    | NGS0)         |               | R/W |

|-----|------------|----------------|---------------------------|--------------|-----------|------------|---------------|---------------|-----|

| Bit | 7          | 6              | 5                         | 4            | 3         | 2          | 1             | 0             |     |

|     | ATI<br>Off | Partial<br>ATI | ATI<br>Current<br>Channel | Redo_ATI     | Reseed    | CS<br>Size | System<br>Use | System<br>Use | R/W |

| Default | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |  |

|---------|---|---|---|---|---|---|---|---|--|

|---------|---|---|---|---|---|---|---|---|--|

| ATI Off                | If this bit is set, the ATI routine will be disabled                                                                            |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                        | ʻ0': ATI On                                                                                                                     |

|                        | '1': ATI Off                                                                                                                    |

| Partial ATI            | Uses the Multipliers to determine the sensitivity and compensation to reach the ATI target, instead of the full ATI routine     |

|                        | "0": Disabled                                                                                                                   |

|                        | "1": Enabled                                                                                                                    |

| ATI Current<br>Channel | Performs a re-ATI on the current channel, as indicated by the Sequence register 3DH                                             |

| Redo ATI               | Forces the ATI routine to run when a '1' is written into this bit position. ATI Off in address E8H bit 7 takes priority         |

| Reseed                 | All channels are reseeded when a '1' is written into this bit position. The LTA's are set to 8 counts below the current samples |

| CS Size                | The internal charge capacitor is normally 29.9pF, if this bit is set the charge capacitor becomes 59.8pF                        |

E9H

|         |               | ProxSense Module Settings 1 (PROX_SETTINGS1) |               |                    |                       |               |               |               |     |  |  |  |  |

|---------|---------------|----------------------------------------------|---------------|--------------------|-----------------------|---------------|---------------|---------------|-----|--|--|--|--|

| Bit     | 7             | 6                                            | 5             | 4                  | 3                     | 2             | 1             | 0             |     |  |  |  |  |

|         | System<br>Use | CRX<br>Float                                 | Turbo<br>Mode | Halt<br>Charge/ULP | Noise<br>Detect<br>On | System<br>Use | System<br>Use | System<br>Use | R/W |  |  |  |  |

| Default | 0             | 0                                            | 0             | 0                  | 0                     | 0             | 0             | 0             |     |  |  |  |  |

| CRX Float          | During conversions the inactive channels are grounded in order to minimize noise coupling. If this bit is set the receiver electrodes will float when inactive |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Turbo mode         | If this bit is set, conversions are performed as fast as processing and communication allows, thereby maximizing detection speed                               |

| Halt<br>Charge/ULP | Set this bit to stop all conversions. The device will now draw the minimum amount of power                                                                     |

| Noise Detect<br>On | Enables the noise detection '0': Disabled '1': Enabled                                                                                                         |

### **EAH**

|         | ProxSense Module Settings 2 (PROX_SETTINGS2) |            |               |                         |                    |               |       |       |     |  |

|---------|----------------------------------------------|------------|---------------|-------------------------|--------------------|---------------|-------|-------|-----|--|

| Bit     | 7                                            | 6          | 5             | 4                       | 3                  | 2             | 1     | 0     |     |  |

|         | Ack<br>Reset                                 | WDT<br>Off | Force<br>Halt | AC<br>Filter<br>Disable | Timeout<br>Disable | Event<br>Mode | Halt1 | Halt0 | R/W |  |

| Default | 0                                            | 0          | 0             | 0                       | 0                  | 0             | 0     | 0     |     |  |

| Ack Reset            | Clears the reset bit  0 = Default                                             |

|----------------------|-------------------------------------------------------------------------------|

|                      | 1 = Clears SHOW_RESET                                                         |

| WDT Off              | Disable the watchdog timer                                                    |

|                      | 0 = Enabled                                                                   |

|                      | 1 = Disabled                                                                  |

| Force Halt           | Forces the Long Term Average of all channels to stop being calculated         |

|                      | '0': LTA updates normally                                                     |

|                      | '1': LTA is halted                                                            |

| AC filter<br>Disable | Set the AC filter. Disabling the AC filter will enable a faster response time |

|                      | 0 = Enabled                                                                   |

|                      | 1 = Disabled                                                                  |

| Timeout<br>Disable   | If this bit is set, a timeout will be allowed on the communication            |

|                      | 0 = Disabled                                                                  |

|                      | 1 = Enabled                                                                   |

| Event Mode           | Sets Event driven I <sup>2</sup> C communication                              |

|                      | 0 = Event Mode                                                                |

|                      | 1 = Streaming Mode                                                            |

| Halt1:Halt0          | Sets the Halt time for the LTA (time before recalibration)                    |

|                      | 00 = 20 Seconds                                                               |

|                      | 01 = 40 Seconds                                                               |

|                      | 10 = Never                                                                    |

|                      | 11 = Permanent                                                                |

**EBH**

|         | ProxSense Module Settings 3 (PROX_SETTINGS3) |              |       |       |                              |               |                              |                              |     |  |

|---------|----------------------------------------------|--------------|-------|-------|------------------------------|---------------|------------------------------|------------------------------|-----|--|

| Bit     | 7                                            | 6            | 5     | 4     | 3                            | 2             | 1                            | 0                            |     |  |

|         | Beta1<br>CH0                                 | Beta0<br>CH0 | Beta1 | Beta0 | Alternative<br>ATI<br>Enable | System<br>Use | Charge<br>Xfer<br>Speed<br>1 | Charge<br>Xfer<br>Speed<br>0 | R/W |  |

| Default | 0                                            | 1            | 0     | 1     | 0                            | n/a           | 0                            | 1                            |     |  |

| Beta CH0 CH0 "00": 1/32 "01": 1/64 "10": 1/128 "11": 1/256  Beta 1:0 Beta (CH1 to CH3) "00": 1/32 "01": 1/64 "10": 1/128 "11": 1/256  Alternative ATI Enable Charge Xfer Speed0:1  Charge Xfer Speed0:1  Beta CH0 "00": 1/32 "01": 1/64 "10": 1/128 "11": 1/256  Charge Transfer Speed "00": 1MHz "01": 500kHz |            |                                  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|--|--|--|--|--|

| "01": 1/64 "10": 1/128 "11": 1/256  Beta 1:0  Beta (CH1 to CH3) "00": 1/32 "01": 1/64 "10": 1/128 "11": 1/256  Alternative ATI Enable  Charge Xfer Speed0:1  "01": 1/64 "10": 1/256  Charge Transfer Speed "00": 1MHz                                                                                          | Beta1:0    | Beta CH0                         |  |  |  |  |  |

| "10": 1/128 "11": 1/256  Beta (CH1 to CH3)                                                                                                                                                                                                                                                                     | CH0        | "00": 1/32                       |  |  |  |  |  |

| #11": 1/256  Beta (CH1 to CH3)  "00": 1/32  "01": 1/64  "10": 1/128  "11": 1/256  Alternative ATI Enable  Charge Xfer Speed0:1  #10": 1/256  Charge Transfer Speed  "00": 1MHz                                                                                                                                 |            | "01": 1/64                       |  |  |  |  |  |

| Beta1:0  Beta (CH1 to CH3)  "00": 1/32  "01": 1/64  "10": 1/128  "11": 1/256  Alternative ATI Enable  Set the alternative ATI function  "0" = Disable  "1" = Enable  Charge Xfer Speed0:1  Charge Transfer Speed  "00": 1MHz                                                                                   |            | "10": 1/128                      |  |  |  |  |  |

| "00": 1/32 "01": 1/64 "10": 1/128 "11": 1/256  Alternative ATI function ATI Enable  Charge Xfer Speed0:1  "00": 1MHz                                                                                                                                                                                           |            | "11": 1/256                      |  |  |  |  |  |

| "01": 1/64 "10": 1/128 "11": 1/256  Alternative ATI function "0" = Disable "1" = Enable  Charge Xfer Speed0:1  Charge Transfer Speed "00": 1MHz                                                                                                                                                                | Beta1:0    | Beta (CH1 to CH3)                |  |  |  |  |  |

| "10": 1/128 "11": 1/256  Alternative ATI function  "0" = Disable "1" = Enable  Charge Xfer Speed0:1  Charge Transfer Speed "00": 1MHz                                                                                                                                                                          |            | "00": 1/32                       |  |  |  |  |  |

| "11": 1/256  Alternative ATI function  "0" = Disable  "1" = Enable  Charge Xfer Speed0:1  Charge Transfer Speed  "00": 1MHz                                                                                                                                                                                    |            | "01": 1/64                       |  |  |  |  |  |

| Alternative ATI Enable  "0" = Disable  "1" = Enable  Charge Xfer Speed0:1  Charge Transfer Speed  "00": 1MHz                                                                                                                                                                                                   |            | "10": 1/128                      |  |  |  |  |  |

| ATI Enable  "0" = Disable  "1" = Enable  Charge Xfer Speed0:1  Charge Transfer Speed  "00": 1MHz                                                                                                                                                                                                               |            | "11": 1/256                      |  |  |  |  |  |

| "0" = Disable  "1" = Enable  Charge Xfer                                                                                                                                                                                                                                                                       |            | Set the alternative ATI function |  |  |  |  |  |

| Charge Xfer Charge Transfer Speed Speed0:1 "00": 1MHz                                                                                                                                                                                                                                                          | ATI Enable | "0" = Disable                    |  |  |  |  |  |

| Speed0:1 "00": 1MHz                                                                                                                                                                                                                                                                                            |            | "1" = Enable                     |  |  |  |  |  |

| OO . HVIDZ                                                                                                                                                                                                                                                                                                     |            | Charge Transfer Speed            |  |  |  |  |  |

| "01": 500kHz                                                                                                                                                                                                                                                                                                   | Speed0:1   | "00": 1MHz                       |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                |            | "01": 500kHz                     |  |  |  |  |  |

| "10": 250kHz (Period will be too long and negatively impact times)                                                                                                                                                                                                                                             |            |                                  |  |  |  |  |  |

| "11": 125kHz (Period will be too long and negatively impact times)                                                                                                                                                                                                                                             |            |                                  |  |  |  |  |  |

**ECH**

|     |            | Channel Enable for CH0 – CH3 (CHAN_ENABLE) |               |               |     |     |     |     |     |  |  |

|-----|------------|--------------------------------------------|---------------|---------------|-----|-----|-----|-----|-----|--|--|

| Bit | 7          | 6                                          | 5             | 4             | 3   | 2   | 1   | 0   |     |  |  |

|     | System use | System<br>Use                              | System<br>Use | System<br>Use | CH3 | CH2 | CH1 | CH0 | R/W |  |  |

| CH3:CH0 | Software enable or disable of channels: |

|---------|-----------------------------------------|

|         | 0 = Channel Disabled                    |

|         | 1 = Channel Enabled                     |

**EDH**

|     |               | System Use    |               |               |               |               |               |               |     |  |

|-----|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|-----|--|

| Bit | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |     |  |

|     | System<br>Use | R/W |  |

**EEH**

|         | Low Power Settings (LOW_POWER)                            |                                             |  |  |  |  |  |  | R/W |  |

|---------|-----------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|-----|--|

| Bit     | 7                                                         | 7 6 5 4 3 2 1 0                             |  |  |  |  |  |  |     |  |

|         | Custom value between 1 and 256 – value x 16ms = LP period |                                             |  |  |  |  |  |  | R/W |  |

| Default |                                                           | Normal power default (00H). See Note below. |  |  |  |  |  |  | R/W |  |

NOTE: While in any power mode the device will zoom to Boost Power (BP) mode whenever a current sample (CS) indicates a possible proximity or touch event. This improves the response time. The device will remain in BP for  $t_{\text{ZOOM}}$  seconds and then return to the selected power mode. The Zoom function allows reliable detection of events with current samples being produced at the BP rate.

F<sub>0</sub>H

|         |   | Default Comms Pointer (DFLT_COMMS_PTR) |  |  |  |  |  |   | R/W |

|---------|---|----------------------------------------|--|--|--|--|--|---|-----|

| Bit     | 7 | 7 6 5 4 3 2 1 0                        |  |  |  |  |  |   |     |

| Default |   | 10H                                    |  |  |  |  |  | W |     |

### **10 Antenna Tuning Implementation (ATI)**

ATI is a sophisticated technology implemented The effects of auto-ATI on the application are in the latest generation ProxSense® devices the following: that optimises the performance of the sensor wide range of applications and environmental conditions (refer to application AZD0027 Antenna note Implementation).

ATI adjusts internal circuitry according to two parameters, the ATI multiplier and the ATI compensation. The ATI multiplier can be viewed as a course adjustment and the ATI compensation as a fine adjustment.

The adjustment of the ATI parameters will result in variations in the current sample and sensitivity. Sensitivity can be observed as the change in current sample as the result of a fixed change in sensed capacitance. The ATI parameters have been chosen to provide significant overlap. It may therefore be possible to select various combinations of ATI multiplier and ATI compensation settings to obtain the same current sample. sensitivity of the various options may however be different for the same current sample.

#### 10.1 Automatic ATI

The IQS243 implements an automatic ATI algorithm. This algorithm automatically adjusts the ATI parameters to optimise the sensing antennas' connection to the device.

The device will execute the ATI algorithm whenever the device starts-up (default target is 1024 counts for all the channels) and when Automatic ATI can be implemented the current samples are not within predetermined range (default target +- 128).

While the Automatic ATI algorithm is in progress this condition will be indicated in the streaming data and proximity and touch events cannot be detected. The device will only briefly remain in this condition and it will be entered only when relatively large shifts in the current sample is detected.

The automatic ATI function aims to maintain a constant current sample, regardless of the capacitance of the sense antenna (within the range of the device).

Automatic adjustment of the device configuration and processing parameters for a wide range of PCB and application designs to maintain an optimal configuration for proximity and touch detection.

Automatic tuning of the sense antenna at start-up to optimise the sensitivity of the application.

Automatic re-tuning when the device changes detects in the sensing antennas' capacitance to large accommodate а range changes in the environment of the application that influences the sensing

Re-tuning only occurs during device operation when a relatively large sensitivity reduction is detected. This is to ensure smooth operation of the device during operation.

Re-tuning may temporarily influences the normal functioning of the device, but in most instances the effect will be hardly noticeable.

Shortly after the completion of the retuning process the sensitivity Proximity detection may be reduced slightly for a few seconds as internal filters stabilises.

a effectively due to:

Excellent system signal to noise ratio (SNR).

Effective digital signal processing remove AC and other noise.

The very stable core of the devices.

The built in capability to accommodate a range of sensing capacitances.

#### 10.2 Partial ATI

Partial ATI allows the designer to manually adjust the gain of the various channels to fit the specific needs of the application.

By default (Address: E8H bit 6=0) the ATI routine sets the required base value of the touch channels to 250 counts. The required base value for the proximity channel is specified through I<sup>2</sup>C commands in address D0H bits [7:6] with the default being 200. The base value for each individual channel can be set via bits [7:6] on the address range D0H to D3H.

Alternatively, the user can set the multiplier bits [5:0] in addresses D0H through D3H which would determine the sensitivity, and compensation (scaled) to reach the ATI target.

With the base value set, the Partial ATI routine would use a convergence technique with a

fixed amount of steps to reach its aimed value.

### 10.3 Alternative ATI

The Alternative ATI implementation ensures that the base and multiplier values are identical for all the channels and adjusts only the compensation in order to achieve the desired current samples. The Alternative ATI can be enabled by setting bit [3] of address FBH.

### 11 Specifications

### 11.1 Absolute Maximum Specifications

The following absolute maximum parameters are specified for the device:

Exceeding these maximum specifications may cause damage to the device.

Operating temperature -40℃ to 85℃

Supply Voltage (VDDHI – VSS) 3.6V

Maximum pin voltage VDDHI + 0.5V (may not

exceed VDDHI max)

Maximum continuous current (for specific Pins)

Minimum pin voltage

VSS - 0.5V

Minimum power-on slope

100V/s

ESD protection ±4kV Human body model

Maximum pin temperature during soldering 350°C (10 seconds)

Maximum pin temperature during soldering  $350^{\circ}$ C (10 seconds) Maximum body temperature during soldering  $300^{\circ}$ C (10 seconds)

Package Moisture Sensitivity Level (MSL) 3

Table 11.1 IQS243 General Operating Conditions<sup>1</sup>

| DESCRIPTION               | Conditions                                              | PARAMETER               | MIN  | TYP  | MAX  | UNIT |

|---------------------------|---------------------------------------------------------|-------------------------|------|------|------|------|

| Supply voltage            | -                                                       | $V_{DDHI}$              | 1.8  | 3.3V | 3.6  | V    |

| Internal regulator output | 1.8 ≤ V <sub>DDHI</sub> ≤ 3.6                           | $V_{REG}$               | 1.63 | 1.7  | 1.77 | V    |

| Boost Operating<br>Power  | VDDHI: 3.3V<br>LOW_POWER register:0<br>Turbo Mode: ON   | I <sub>IQS243_BP</sub>  | -    | 152  | -    | μА   |

| Normal Operating<br>Power | VDDHI: 3.3V<br>LOW_POWER register: 0<br>Turbo Mode: OFF | I <sub>IQS243_NP</sub>  | -    | 148  | -    | μА   |

| LP Mode 1*                | VDDHI: 3.3V<br>LOW_POWER register: 4                    | I <sub>IQS243_LP1</sub> | -    | 45   | -    | μΑ   |

| LP Mode 2*                | LP Mode 2*  VDDHI: 3.3V  LOW_POWER register: 8          |                         | -    | 20.7 | -    | μA   |

| LP Mode 3*                | VDDHI: 3.3V<br>LOW_POWER register: 16                   | I <sub>IQS243_BP3</sub> | -    | 10.6 | -    | μA   |

<sup>&</sup>lt;sup>1</sup> Operating current shown in this datasheet, does not include power dissipation through I<sup>2</sup>C pull up resistors.

# IQ Switch<sup>®</sup> ProxSense<sup>®</sup> Series

| DESCRIPTION | Conditions                             | PARAMETER               | MIN | TYP | MAX | UNIT |

|-------------|----------------------------------------|-------------------------|-----|-----|-----|------|

| LP Mode 4*  | VDDHI: 3.3V<br>LOW_POWER register:32   | I <sub>IQS243_LP4</sub> | -   | 5.6 | -   | μΑ   |

| LP Mode 5*  | VDDHI: 3.3V<br>LOW_POWER register: 64  | I <sub>IQS243_LP5</sub> | -   | 3.5 | -   | μΑ   |

| LP Mode 6*  | VDDHI: 3.3V<br>LOW_POWER register: 128 | I <sub>IQS243_LP6</sub> | 1   | 2.5 | -   | μΑ   |

<sup>\*</sup>LP interval period = Low power value x 16ms

Table 11.2 Start-up and shut-down slope Characteristics

| DESCRIPTION         | Conditions                               | PARAMETER | MIN  | MAX  | UNIT     |

|---------------------|------------------------------------------|-----------|------|------|----------|

| Power On<br>Reset   | V <sub>DDHI</sub> Slope ≥ 100V/s<br>@25℃ | POR       | 1.2  | 1.6  | <b>V</b> |

| Brown Out<br>Detect | V <sub>DDHI</sub> Slope ≥ 100V/s<br>@25℃ | BOD       | 1.15 | 1.55 | V        |

**Table 11.3** Initial Touch Times

| DESCRIPTION     | PARAMETER        | Typical | Unit |

|-----------------|------------------|---------|------|

| BP <sup>1</sup> | Response<br>time | 13      | ms   |

| NP              | Response<br>time | 45      | ms   |

| LP6             | Response<br>time | 2000    | ms   |

<sup>&</sup>lt;sup>1</sup> Communication and charge frequency to comply with sample rate as reported earlier in this datasheet.

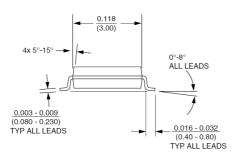

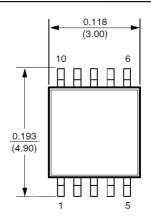

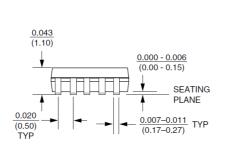

### **12 Mechanical Dimensions**

Figure 12.1 MSOP-10 Back view.

Figure 12.3 MSOP-10 Top view.

Figure 12.2 MSOP-10 Side view.

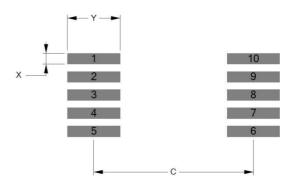

Figure 12.4 MSOP-10 Footprint.

Table 12.1 MSOP-10 Footprint Dimensions from Figure 12.4.

| Dimension | [mm] |

|-----------|------|

| Pitch     | 0.50 |

| С         | 4.40 |

| Y         | 1.45 |

| Х         | 0.30 |

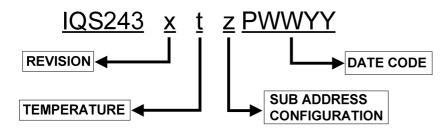

## 13 Device Marking

| REVISION          | Х  | =   | IC Revision Number                                                      |

|-------------------|----|-----|-------------------------------------------------------------------------|

| TEMPERATURE RANGE | t  | = = | I -40℃ to 85℃ (Industrial)<br>C 0℃ to 70℃ (Commercial)                  |

| IC CONFIGURATION  | z  | =   | Sub Address Configuration (Hexadecimal) 0 = 44H 1 = 45H 2 = 46H 3 = 47H |

| DATE CODE         | Р  | =   | Package House                                                           |

|                   | ww | =   | Week                                                                    |

|                   | YY | =   | Year                                                                    |

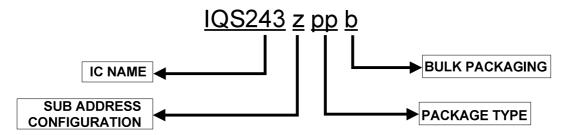

## **14 Ordering Information**

Orders will be subject to a MOQ (Minimum Order Quantity) of a full reel. Contact the official distributor for sample quantities. A list of the distributors can be found under the "Distributors" section of www.azoteq.com.

For large orders, Azoteq can provide pre-configured devices.

The Part-number can be generated by using USBProg.exe or the Interactive Part Number generator on the website.

| IC NAME        | IQS243 | = | IQS243                                  |

|----------------|--------|---|-----------------------------------------|

| CONFIGURATION  | z      | = | Sub Address Configuration (hexadecimal) |

| PACKAGE TYPE   | MS     | = | MSOP-10                                 |

| BULK PACKAGING | R      | = | Reel (4000pcs/reel) – MOQ = 4000pcs     |

|                | Т      | = | Tube (96pcs/tube) Special order only    |

### 15 Contact Information

Please visit the Azoteq website for a list of distributors and representations world wide.

#### **HEADQUARTERS:**

PRETORIA OFFICE PAARL OFFICE

Physical Address

160 Witch Hazel Avenue

109 Main Street

Hazel Court 1, 1<sub>st</sub> Floor Paarl Highveld Techno Park 7646

Centurion, Gauteng Western Cape

Republic of South Africa Republic of South Africa

Tel: +27 12 665 2880 Tel: +27 21 863 0033 Fax: +27 12 665 2883 Fax: +27 21 863 1512

Postal Address

PO Box 16767

PO Box 3534

PO Box 3534

Lyttelton Paarl 0140 7620

Republic of South Africa Republic of South Africa

The following patents relate to the device or usage of the device: US 6,249,089 B1, US 6,621,225 B2, US 6,650,066 B2, US 6,952,084 B2, US 6,984,900 B1, US 7,084,526 B2, US 7,084,531 B2, US 7,119,459 B2, US 7,265,494 B2, US 7,291,940 B2, US 7,329,970 B2, US 7,336,037 B2, US 7,443,101 B2, US 7,466,040 B2, US 7,498,749 B2, US 7,528,508 B2, US 7,755,219 B2, US 7,772,781, US 7,781,980 B2, US 7,915,765 B2, EP 1 120 018 B1, EP 1 206 168 B1, EP 1 308 913 B1, EP 1 530 178 B1, ZL 99 8 14357.X, AUS 761094

IQ Switch®, ProxSense®, LightSense™, AirButton® and the Ulogo are trademarks of Azoteq.

The information in this Datasheet is believed to be accurate at the time of publication. Azoteq assumes no liability arising from the use of the information or the product. The applications mentioned herein are used solely for the purpose of illustration and Azoteq makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Azoteq products are not authorized for use as critical components in life support devices or systems. No licenses to patents are granted, implicitly or otherwise, under any intellectual property rights. Azoteq reserves the right to alter its products without prior notification. For the most up-to-date information, please refer to <a href="https://www.azoteq.com">www.azoteq.com</a>.

WWW.AZOTEQ.COM

ProxSenseSupport@azoteq.com

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

$\frac{\text{Azoteq}:}{\text{IQS243MSR}}$