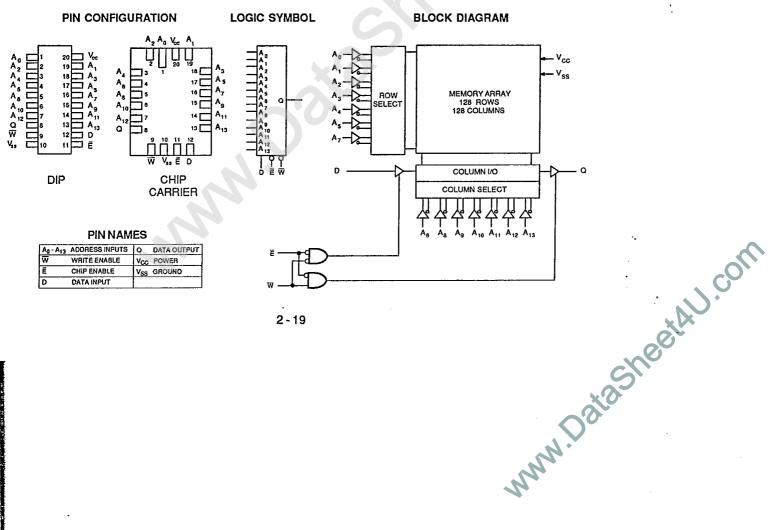

# **CMOS** High Performance 16K x 1 Static RAM

#### **FEATURES**

- INMOS' Very High Speed CMOS

- · Advanced Process 1.6 Micron Design Rules

- · 16K x 1 Bit Organization

- 25, 35, 45 and 55 nsec Access Times

- Fully TTL Compatible

- Separate Data Input & Output

- Three-state Output

- Power Down Function

- Single +5V ± 10% Operation

- 20-Pin, 300-mil DIP (JEDEC Std.)

- 20-Pin Ceramic LCC (JEDEC Std.)

#### DESCRIPTION

The INMOS IMS1403 is a high performance 16K x 1 CMOS Static RAM. The IMS1403 provides maximum density and speed enhancements with the additional CMOS benefits of lower power and superior reliability.

The IMS1403 features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1403 provides a Chip Enable (/E) function that can be used to place the device into a low-power standby mode.

The IMS1403M and IMS1403LM are MIL-STD-883 versions intended for military applications.

2-19

## IMS1403

## ABSOLUTE MAXIMUM RATINGS\*

Voltage on any pin relative to Vss......-2.0 to 7.0V

Voltage on Q .....-1.0 to (Vcc+0.5)

Temperature Under Bias...-55° C to 125°C

Storage Temperature ...-65° C to 150°C

Power Dissipation .....1W

DC Output Current......25mA

10E D 4802688 0002801 5 T-46-23-05

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### DC OPERATING CONDITIONS

| SYMBOL | PARAMETER                     | MIN   | TYP | MAX    | UNITS | NOTES                      |

|--------|-------------------------------|-------|-----|--------|-------|----------------------------|

| Vcc    | Supply Voltage                | 4.5   | 5.0 | 5.5    | >     |                            |

| Vss    | Supply Voltage                | 0     | 0   | 0      | >     |                            |

| ViH    | Input Logic "1" Voltage       | 2.0   |     | Vcc+.5 | ٧     | All inputs                 |

| Vil    | Input Logic "0" Voltage       | -1.0* |     | 0.8    | ٧     | All inputs                 |

| TA     | Ambient Operating Temperature | 0     | 25  | 70     | ဇင    | 400 linear ft/min air flow |

<sup>\*</sup>Vir.min = -3 volts for pulse width <20ns, note b.

#### DC FLECTRICAL CHARACTERISTICS (0°C \( \text{TA} \( \text{ \( 70°C \)} \) (Vcc = 5.0V \( \text{ \( 10% \)}\) a

| SYMBOL | PARAMETER                                                        | MIN | MAX | UNITS | NOTES                                                                                               |

|--------|------------------------------------------------------------------|-----|-----|-------|-----------------------------------------------------------------------------------------------------|

| lcc1   | Average Vcc Power<br>Supply Current                              |     | 75  | mA    | tavav = tavav (min)                                                                                 |

| lcc2   | Vcc Power Supply Current<br>(Standby,Stable TTL Input Levels)    |     | 15  | mA    | Ē Σ Viн . All other inputs at<br>Vin ζ Vi∟ or Σ Viн                                                 |

| lcc3   | Vcc Power Supply Current<br>(Standby, Stable CMOS Input Levels)  |     | 5   | mA    | $\vec{E}$ $\geq$ (Vcc - 0.2). All other inputs at V <sub>IN</sub> $\leq$ 0.2 or $\geq$ (Vcc - 0.2V) |

| lcc4   | Vcc Power Supply Current<br>(Standby, Cycling CMOS Input Levels) |     | 10  | mA    | Ē ≿ (Vcc - 0.2). Inputs cycling at Vin ≤ 0.2 or ≥ (Vcc - 0.2V)                                      |

| lılk   | Input Leakage Current (Any Input)                                |     | ±1* | μΑ    | Vcc = max<br>Vin = Vss to Vcc                                                                       |

| lork   | Off State Output Leakage Current                                 |     | ±5  | μΑ    | Vcc = max<br>Vin = Vss to Vcc                                                                       |

| Vон    | Output Logic "1" Voltage                                         | 2.4 |     | V     | IoL = -4mA                                                                                          |

| Vol    | Output Logic "0" Voltage                                         |     | 0.4 | v     | Іон = 16mA                                                                                          |

Note a: Icc is dependent on output loading and cycle rate, the specified values are obtained with the output unloaded.

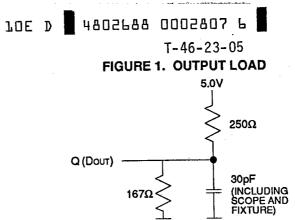

### **AC TEST CONDITIONS**

| Input Pulse Levels                          | Vss to 3V     |

|---------------------------------------------|---------------|

| Input Pulse LevelsInput Rise and Fall Times | 5ns           |

| Input and Output Timing Reference           | Levels1.5V    |

| Output Load                                 | .See Figure 1 |

## CAPACITANCEb (Ta=25°C, f=1.0MHZ)

| SYMBOL | PARAMETER          | MAX | UNITS | CONDITIONS             |

|--------|--------------------|-----|-------|------------------------|

| Cin    | Input Capacitance  | 4   | рF    | $\Delta V = 0$ to 3V   |

| Соит   | Output Capacitance | 4   | рF    | $\Delta V = 0$ to $3V$ |

Note b: This parameter is sampled and not 100% tested.

## RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C) ( $V_{CC}$ = 5.0V $\pm$ 10%,

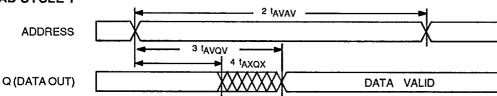

## **READ CYCLE**<sup>9</sup>

| NO. |                     | BOL              | PARAMETER                        |     | 1403-25 140<br>MIN MAX MIN |     | 1403-35 |     |     |     |     |        |      |  |  |  |  |  |  |  |  |  | 3-45 |  | 3-55 |  | NOTES |

|-----|---------------------|------------------|----------------------------------|-----|----------------------------|-----|---------|-----|-----|-----|-----|--------|------|--|--|--|--|--|--|--|--|--|------|--|------|--|-------|

|     | Standard            | Alternate        |                                  | MIN | MAX                        | MIN | MAX     | MIN | MAX | MIN | MAX | 0.11.0 |      |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| _1  | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 25                         |     | 35      |     | 45  |     | 55  | ns     |      |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 2   | t <sub>avav</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 25  |                            | 35  |         | 40  |     | 50  |     | ns     | С    |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 3   | t <sub>AVQV</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 25                         |     | 35      |     | 40  |     | 50  | ns     | d    |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 4   | t <sub>AXQX</sub>   | t <sub>он</sub>  | Output Hold After Address Change | 5   |                            | 5   | ,       | 5   |     | 5   |     | ns     |      |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 5   | t <sub>ELQX</sub>   | t <sub>LZ</sub>  | Chip Enable to Output Active     | 5   |                            | 5   |         | 5   |     | 5   |     | ns     | j ·  |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 6   | t <sub>EHQZ</sub>   | t <sub>HZ</sub>  | Chip Disable to Output Inactive  | 0   | 20                         | 0   | 20      | 0   | 20  | 0   | 25  | ns     | f, j |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 7   | t <sub>ELICCH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |                            | 0   |         | 0   |     | 0   |     | ns     | j    |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

| 8   | t <sub>EHICCL</sub> | t <sub>PD</sub>  | Chip Enable To Power Down        |     | 30                         |     | 30      |     | 30  |     | 30  | ns     | j    |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

|     |                     | tī               | Input Rise and Fall Times        |     | 50                         |     | 50      |     | 50  |     | 50  | ns     | e, j |  |  |  |  |  |  |  |  |  |      |  |      |  |       |

Note c: For READ CYCLE 1 & 2,  $\overline{W}$  is high for entire cycle. Note d: Device is continuously selected,  $\overline{E}$  low. Note e: Measured between  $V_{IL}$  max and  $V_{IH}$  min. Note f: Measured  $\pm$  200mV from steady state output voltage. Load capacitance is 5pF. Note g:  $\overline{E}$  and  $\overline{W}$  must transition between  $V_{IH}$  to  $V_{IL}$  or  $V_{IL}$  to  $V_{IH}$  in a monotonic fashion. Note j: Parameter guaranteed but not tested.

## READ CYCLE 2°

RECOMMENDED AC OPERATING CONDITIONS (0°C  $\leq$  T<sub>A</sub> $\leq$  70°C) (V<sub>CC</sub> = 5.0V  $\pm$  10%)

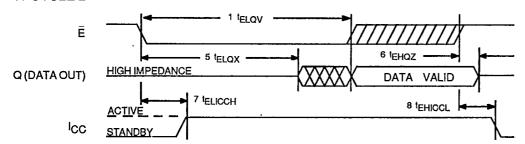

## WRITE CYCLE 1: W CONTROLLEDG, h

|     |                   |                 |                                      | 140 | 3-25 | 140 | 3-35 | 1403 |     |    | 3-55 | UNITS | NOTES    |

|-----|-------------------|-----------------|--------------------------------------|-----|------|-----|------|------|-----|----|------|-------|----------|

| NO. | SYM!<br>Standard  |                 | PARAMETER                            |     | MAX  |     | MAX  |      | MAX |    | MAX  |       |          |

| 9   | t <sub>AVAV</sub> | t <sub>wc</sub> | Write Cycle Time                     | 20  |      | 30  |      | 40   |     | 50 |      | ns    |          |

| 10  | twewn             | t <sub>we</sub> | Write Pulse Width                    | 15  |      | 20  |      | 20   |     | 25 |      | ns    |          |

| 11  | t <sub>ELWH</sub> | tcw             | Chip Enable to End of Write          | 20  |      | 30  |      | 35   |     | 45 |      | ns    |          |

| 12  |                   | t <sub>DW</sub> | Data Set-up to End of Write          | 15  |      | 15  |      | 15   |     | 20 |      | ns    |          |

| 13  |                   | t <sub>oH</sub> | Data Hold After End of Write         | 0   |      | 0   |      | 0    |     | 0  |      | ns    |          |

| 14  |                   | t <sub>AW</sub> | Address Set-up to End of Write       | 20  |      | 30  |      | 35   |     | 45 |      | ns    |          |

| 15  |                   | <del> </del>    | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0    |     | 0  |      | ns    |          |

| -   | 1                 | t <sub>AS</sub> | Address Hold After End of Write      | 0   |      | 0   |      | 0    |     | 0  |      | ns    |          |

| 16  |                   | t <sub>wa</sub> | Write Enable to Output Disable       | 0   | 20   | 0   | 20   | 0    | 20  | 0  | 20   | ns    | f, j     |

| 17  | 1                 | <u>├</u>        | Output Active After End of Write     | 0   | 1    | 0   | T    | 0    |     | 0  |      | ns    | <u>i</u> |

| 18  | TWHQX             | tow             | Output Aouto Autor End of Titue      |     |      |     |      |      |     |    |      |       |          |

Note f: Measured  $\pm$  200mV from steady state output voltage. Load capacitance is 5pF. Note g:  $\overline{E}$  and  $\overline{W}$  must transition between  $V_{IH}$  to  $V_{IL}$  or  $V_{IL}$  to  $V_{IH}$  in a monotonic fashion. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions. Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the output remains in the high impedance state.

Note j: Parameter guaranteed but not tested.

## RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C) ( $V_{cc}$ = 5.0V $\pm$ 10%)

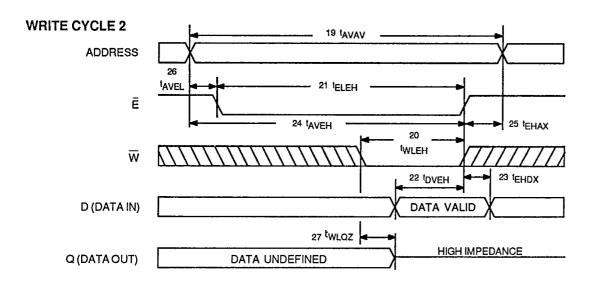

## WRITE CYCLE 2: E CONTROLLED<sup>g, h</sup>

| NO. |                   | BOL             | PARAMETER                            |     | 3-25 |     | 3-35 |     | 3-45 |     | 3-55 |       | NOTES |

|-----|-------------------|-----------------|--------------------------------------|-----|------|-----|------|-----|------|-----|------|-------|-------|

|     | Standard          | Alternate       | TANAMETER                            | MIN | MAX  | MIN | MAX  | MIN | MAX  | MIN | MAX  | UNIIS | MOIES |

| 19  | t <sub>avav</sub> | t <sub>wc</sub> | Write Cycle Time                     | 20  |      | 30  |      | 40  |      | 50  |      | ns    |       |

| 20  | t <sub>WLEH</sub> | t <sub>we</sub> | Write Pulse Width                    | 15  |      | 20  |      | 20  |      | 25  |      | ns    |       |

| 21  | t <sub>ELEH</sub> | t <sub>cw</sub> | Chip Enable to End of Write          | 20  |      | 30  |      | 35  |      | 45  |      | ns    |       |

| 22  | t <sub>DVEH</sub> | tow             | Data Set-up to End of Write          | 15  |      | 15  |      | 15  |      | 20  |      | ns    |       |

| 23  | t <sub>EHDX</sub> | t <sub>DH</sub> | Data Hold After End of Write         | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 24  | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write       | 20  |      | 30  |      | 35  |      | 45  |      | ns    |       |

| 25  | t <sub>ehax</sub> | t <sub>wa</sub> | Address Hold After End of Write      | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 26  | t <sub>avel</sub> | t <sub>AS</sub> | Address Set-up to Beginning of Write | 0   |      | 0   |      | 0   |      | 0   |      | ns    |       |

| 27  | t <sub>WLQZ</sub> | t <sub>wz</sub> | Write Enable to Output Disable       | 0   | 20   | 0   | 20   | 0   | 20   | 0   | 25   | ns    | f, j  |

Note f: Measured ± 200mV from steady state output voltage. Load capacitance is 5pF.

Note g:  $\overline{E}$  and  $\overline{W}$  must transition between  $V_{IH}$  to  $V_{IL}$  or  $V_{IL}$  to  $V_{IH}$  in a monotonic fashion. Note h:  $\overline{E}$  or  $\overline{W}$  must be  $\geq V_{IH}$  during address transitions. Note i: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the output remains in the high impedance state.

Note j: Parameter guaranteed but not tested.

IMS1403

T-46-23-05

DEVICE OPERATION

The IMS1403 has two control inputs, Chip Enable  $(\overline{E})$  and Write Enable  $(\overline{W})$ , fourteen address inputs  $(A_0 - A_{13})$ , a Data in (D) and a Data out (Q). The  $\overline{E}$  input controls device selection as well as active and standby modes. With  $\overline{E}$  low, the device is selected and the fourteen address inputs are decoded to select one bit out of 16K bits. Read and Write operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected, the output is disabled, and power consumption is reduced to less than one-fourth of the active mode power with TTL levels and even lower with CMOS levels.

#### READ CYCLE

A read cycle is defined as  $\overline{W} \ge V_{IH}$  min with  $\overline{E} \le V_{IL}$  max. Read access time is measured from either  $\overline{E}$

going low or from valid address.

The READ CYCLE 1 waveform shows a read access that is initiated by a change in the address inputs while  $\overline{E}$  is low. The output remains active throughout READ CYCLE 1 and is valid at the specified address access time. The address inputs may change at access time as long as  $\overline{E}$  remains low, the cycle time is equal to the address access time.

The READ CYCLE 2 waveform shows a read access that is initiated by  $\overline{E}$  going low. As long as address is stable when  $\overline{E}$  goes low, valid data is at the output at the specified Chip Enable Access time. If address is not

valid when  $\overline{E}$  goes low, the timing is as specified in READ CYCLE 1. Chip Enable access time is not affected by the duration of the deselect interval.

#### WRITE CYCLE

A write cycle of the IMS1403 is initiated by the latter of  $\overline{E}$  or  $\overline{W}$  to transition from a high to a low. In the case of  $\overline{W}$  falling last, the output buffer will be turned on  $t_{ELOX}$  after the falling edge of  $\overline{E}$  (just as in a read cycle). The output buffer is then turned off within  $t_{WLOZ}$  of the falling edge of  $\overline{W}$ . During this interval, it is possible to have bus contention between devices with D and Q connected together in a common I/O configuration. Contention can be avoided in a carefully designed system. During a write cycle, data on the input is written into the selected cells and the output is floating.

WRITE CYCLE 1 waveform shows a write cycle terminated by  $\overline{W}$  going high. Data set-up and hold times are referenced to the rising edge of  $\overline{W}$ . When  $\overline{W}$  goes high at the end of the cycle with  $\overline{E}$  active, the output of the memory becomes active. The data from the memory will be the same as the input data unless the

input data or address changes.

WRITE CYCLE 2 waveform shows a write cycle terminated by E going high. Data set-up and hold times are referenced to the rising edge of E. With E high, the outputs remain in the high impedance state.

#### **APPLICATION**

It is imperative when designing with any very high speed memory, such as the IMS1403, that the fundamental rules in regard to memory board layout be followed to ensure proper system operation.

#### **POWER DISTRIBUTION**

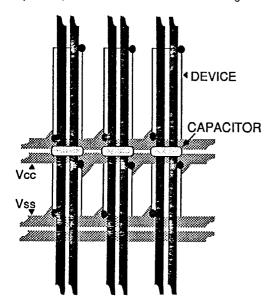

The recommended power distribution scheme combines proper power trace layout and placement of decoupling capacitors to maintain the operating margins of the IMS1403. The impedance in the decoupling path from the power pin through the decoupling capacitor, to the ground pin should be kept to a minimum. The impedance of this path is determined by the series impedance of the power line inductance and the inductance and reactance of the decoupling capacitor.

Since the current transients associated with the operation of the high speed IMS1403 have very high frequency components, the line inductance is the dominating factor.

V<sub>CC</sub>, V<sub>SS</sub> GRID SHOWING DECOUPLING CAPACITORS

To reduce the line inductance, the power trace and ground trace should be gridded or provided by separate power planes. The decoupling capacitor supplies energy for high frequency current transients and should be located as close to the devices with as short lead length as possible. The high frequency decoupling capacitor should have a value of  $0.1\mu F$ , and be placed between each row of devices in the array (see drawing). A larger tantalum capacitor, with a sufficient value to eliminate low frequency ripple, should be placed near the memory board edge connection where the power traces meet the backplane power distribution system. These larger capacitors provide bulk energy storage to prevent voltage drop due to the main supply being located off the memory board and at the end of a long inductive path.

The ground grid of the memory array should extend to the TTL periphery circuit. This will provide a solid ground reference for the TTL drivers and prevent loss of operating margin of the drivers due to differential ground noise.

#### **TERMINATION**

Trace lines on a memory board in the array look to TTL driver signals like low impedance, unterminated transmission lines. In order to reduce or eliminate the reflections of the TTL signals propagating down the lines, especially low going TTL signals, line termination is recommended. The termination may be either series or parallel.

The recommended technique is to use series termination. The series termination technique has the advantage of drawing no DC current and using a minimum number of components. This is accomplished by placing a series resistor in the signal line at the output of the TTL driver to dampen the reflection on the line. The resistor should be placed as close to the driver package as is practical. The line should be kept short by placing the driver-termination combination close to the memory array.

Some experimentation will have to be done to find the proper value to use for the series termination to minimize reflections, but generally a series resistor in the 10 to 33 ohm range will be required. Because each design will result in a different signal impedance, a resistor of predetermined value may not properly match the signal path impedance. The proper value of resistance should therefore be selected empirically.

## **ORDERING INFORMATION**

| DEVICE  | SPEED | PACKAGE     | PART NUMBER |

|---------|-------|-------------|-------------|

|         | 25ns  | PLASTIC DIP | IMS1403P-25 |

|         | 25ns  | CERAMIC DIP | IMS1403S-25 |

|         | 25ns  | CERAMIC LCC | IMS1403W-25 |

|         | 35ns  | PLASTIC DIP | IMS1403P-35 |

|         | 35ns  | CERAMIC DIP | IMS1403S-35 |

| IMS1403 | 35ns  | CERAMIC LCC | IMS1403W-35 |

|         | 45ns  | PLASTIC DIP | IMS1403P-45 |

|         | 45ns  | CERAMIC DIP | IMS1403S-45 |

|         | 45ns  | CERAMIC LCC | IMS1403W-45 |

|         | 55ns  | PLASTIC DIP | IMS1403P-55 |

|         | 55ns  | CERAMIC DIP | IMS1403S-55 |

|         | 55ns  | CERAMIC LCC | IMS1403W-55 |