## IMAGE ENHANCER ADD-ON BOARD FOR 120Hz PANEL

# Model: IE-2000

Part number : 41756002X-3 or up

## INSTRUCTIONS

## CONTENTS

Page: 2. Introduction, How to Proceed, Usage Note, Disclaimer

- 3. System design Diagram of a suggested system

- 4. Assembly notes Important information about system elements

- 6. Connection & Operation How to use the IE-2000

- 7. Connectors, pinouts & jumpers Essential connection information

- 16. Board dimensions

- 17. Troubleshooting

18. Specifications

19. Appendix I – Mapping definition

21.Warranty, Caution & Limitation of Liability, Trademarks

22.Contact details

It is essential that these instructions are read and understood before connecting or powering up the IE-2000

## Introduction

The IE-2000 is a Digital View add-on board providing:

• 10 bit panel support and 120Hz panel support.

The IE-2000 is currently matching with Digital View SVX-4096 controller to provide support for:

• Displays up to 4096x2160, 10 bit, 120Hz.

### HOW TO PROCEED

• As most panels require different connection settings and cables it is important to have the relevant Digital View Connection Diagram before assembly begins. This is obtainable from the Digital View website as follows:

### **Controller Solution Generator**

A web based resource matching controllers & panels with **connection diagrams** for download. Visit : <u>http://www.digitalview.com/controllers/csg.php</u>

- Ensure all parts are on hand.

- Check controller and add-on board switch & jumper settings (errors may damage the panel)

- Prepare the source

- Connect the parts

- Understand the operation & functions

### IMPORTANT USAGE NOTE

This equipment is for use by system manufacturers, developers and qualified integrators, the manufacturer accepts no liability for damage or injury caused by the use of this product. It is the responsibility of the developer, integrators or other user of this product to:

- Ensure that all necessary and appropriate safety measures are taken.

- Obtain suitable regulatory approvals as may be required.

- Check power settings to all component parts before connection.

### DISCLAIMER

There is no implied or expressed warranty regarding this material.

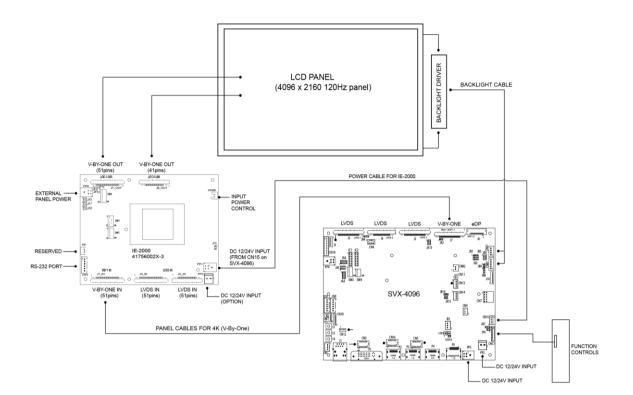

## SYSTEM DESIGN

A typical LCD based display system utilizing the IE-2000 is likely to comprise the following:

## ASSEMBLY NOTES

The IE-2000 is designed for monitor and custom display projects using 4096x2160 resolution 10 bit 120Hz TFT panels with connection with compatible Digital View controllers. The following provides some guidelines for installation and preparation of a finished display solution.

**Preparation**: Before proceeding it is important to familiarize yourself with the parts making up the system and the various connectors, mounting holes and general layout of the IE-2000. As much as possible connectors have been labeled. Guides to connectors and mounting holes are shown in the following relevant sections.

- 1. LCD Panel: The IE-2000 is designed for driving 10 bits 120Hz up to 4096x2160 V-by-One panels. Due to the variation between manufacturers of panels signal timing and other panel characteristics it is important to use the correct Digital View Connection Diagram (which can be downloaded from the Digital View Controller Solution Generator at www.digitalview.com/controllers/csg.php) before connecting to a panel.

- 2. Image Enhancer board, IE-2000 : With reference to the Connection Diagram ensure correct jumper and dip switches settings to match the target LCD panel. Caution: Handle with care as static charge may damage electronic components.

- 3. LCD main controller, eg SVX-4096 : With reference to the Connection Diagram ensure correct jumper and dip switches settings to match the target LCD panel. Caution: Handle the controller with care as static charge may damage electronic components.

- 4. Interconnect V-by-One cable : This cable connects between the IE-2000 and DigitalView controllers for transmission of V-by-One signal and panel power to IE-2000 board. It is recommended to organize loose wires with cable ties. Care should be taken when placing the cables to avoid signal interference. Additionally it may be necessary in some systems to add ferrite cores to the cable to minimize signal noise.

- 5. **Panel power cable** : This cable connects between IE-2000 and DigitalView controllers for panel power.

- 6. Panel cable for V-by-One panel : In order to provide a clean signal it is recommended that LCD signal cables should not be longer than 61cm (24 inches). It is recommended to organize loose wires with cable ties. Care should be taken when placing the cables to avoid signal interference. Additionally it may be necessary in some systems to add ferrite cores to the cable to minimize signal noise.

- 7. RS-232 port : This port is relevant for firmware upgrade only.

- 8. Power Input: 12V/24VDC is required, this should be a regulated supply. The power rating depends on the panel and inverter used. Normally a power supply with at least 15W power output should adequate. Although the controller provides power regulation for the LCD power this does not relate to the power supplied to the backlight inverter. If an unregulated power supply is provided to an inverter any fluctuations in power may affect operation, performance and lifetime of the inverter and or backlight tubes.

- **9. Power and inverter control cable :** Different inverter models require different cables and different pin assignments. Using the wrong cable may damage the inverter.

## **IMPORTANT NOTES**

- Power Safety: We strongly advise using appropriate insulation for all circuitry.

- EMI: Shielding will be required for passing certain regulatory emissions tests.

- Ground: The various PCB mounting holes are connected to the ground plane.

- Servicing: The board is not user serviceable or repairable. Warranty does not cover user error in connecting up to the IE-2000 and is invalidated by unauthorized modification or repairs.

- **Board Mounting**: It is recommended that a clearance of at least 10mm is provided above and 5mm below the board when mounted. Additionally consideration should be given to:

- Electrical insulation.

- Grounding.

- EMI shielding.

- Cable management. Note: It is important to keep panel signal cables apart from the inverter & backlight cables to prevent signal interference.

- Heat & Ventilation: Heat generated from other sources, for example the backlight of a very high brightness panel may generate significant heat which could adversely affect the IE-2000.

- Other system design issues that may affect safety or performance.

**IMPORTANT:** Please read the Application Notes section for more information.

## **CONNECTION & OPERATION**

**CAUTION**: Never connect or disconnect parts of the display system when the system is powered up as this may cause serious damage.

### CONNECTION

Connection and usage is quite straight forward (it is useful to have the relevant connection diagram available at this time):

- 1. **Connect the LCD panel & IE-2000** : Use the appropriate panel cable as indicated in the relevant Digital View Connection Diagram.

- 2. **Connect the Digital View main controller & IE-2000**: Use V-by-One cables P/N 426162300-3, 400mm to carry V-by-One signal from SVX-4096 controller board to IE-2000.

- 3. Connect a suitable OSD switch mount kit : Digital View offer a number of ready made options.

- 4. **Check all Jumpers & Switches**: Refer to the relevant Digital View Connection Diagram or the jumpers and switches setting table (in the following section).

- 5. **Connect the Power supply**: Use Power cable P/N 426307100-3, 300mm, this carries power from SVX-4096 controller board (CN15) to IE-2000 (PP1).

- 6. **Power on** : Switch on the controller board and panel by using the OSD switch mount. The following is the power status on LED.

Power status on LED5A and LED5A1:

| State           | LED color |

|-----------------|-----------|

| Power on state  | Green     |

| No signal state | Off       |

General:

- If you are using supplied cables & accessories, ensure they are correct for the model of panel and controller and IE-2000.

- If you are making your own cables & connectors refer carefully to both the panel & inverter specifications and the section in this manual, "Connectors, Pinouts & Jumpers" to ensure the correct pin to pin wiring.

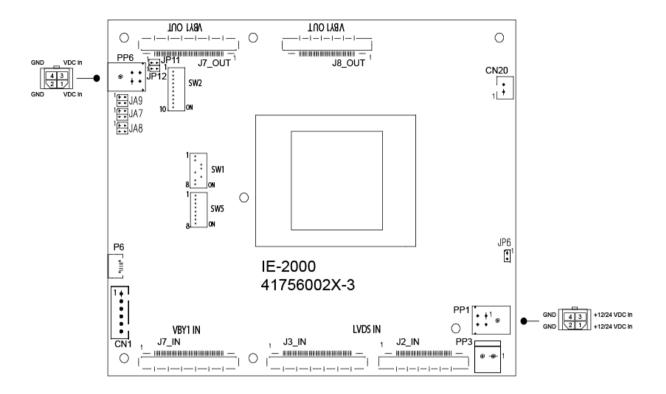

## **CONNECTORS, PINOUTS & JUMPERS**

The various connectors are:

#### Summary: Connectors

| Ref    | Purpose                           | D                                                       | Description                             |

|--------|-----------------------------------|---------------------------------------------------------|-----------------------------------------|

| J2_IN  | LVDS signal input 1 (41)          | JAE FI-RE41S-HF (Ma                                     | atching type : FI-RE41HL or compatible) |

| J3_IN  | LVDS signal input 2 (51)          | JAE FI-RE51S-HF (Ma                                     | atching type : FI-RE51HL or compatible) |

| J7_IN  | V-by-One panel signal input (51)  | JAE FI-RE51S-HF (Ma                                     | atching type : FI-RE51HL or compatible) |

| J7_OUT | V-by-One panel signal output (51) | JAE FI-RE51S-HF (Ma                                     | atching type : FI-RE51HL or compatible) |

| J8_OUT | V-by-One panel signal output (41) | JAE FI-RE41S-HF (Ma                                     | atching type : FI-RE41HL or compatible) |

| P6     | Reserved                          | Mini USB                                                |                                         |

| CN1    | RS-232 port                       | JST 6-way, B6B-XH-A                                     | (Matching type : XHP-6)                 |

| CN20   | Input power control               | JST 2-way, B2B-PH-K                                     | (Matching type : PHR-2)                 |

| PP1    | 12V/24VDC power input             | Molex 43045-0400 compatible                             |                                         |

|        |                                   |                                                         | tor type : Molex 43025-0400 compatible) |

|        |                                   | (Matching po                                            | ower cable : P/N 426307100-3, 300mm)    |

| PP3    | Alternative power input           | DC power Molex 2 pin 0.156" p                           | pitch                                   |

| PP6    | External panel power input        | Molex 43045-0400 compatible                             |                                         |

|        |                                   | (Matching connector type : Molex 43025-0400 compatible) |                                         |

|        |                                   | (Matching po                                            | ower cable : P/N 426013710-3,1000mm)    |

| Ref    | Purpose                                                                      | Note                                                                          |

|--------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| JP6    | Input power control                                                          | Short = Power control by SVX-4096<br>Open = External power control through S2 |

| JP11   | Panel power voltage select<br>CAUTION: Incorrect setting can damage<br>panel | See panel voltage setting table 2                                             |

| JP12   | Panel power voltage select<br>CAUTION: Incorrect setting can damage<br>panel | See panel voltage setting table 2                                             |

| JA9    | Panel power voltage select<br>CAUTION: Incorrect setting can damage<br>panel | See panel voltage setting table 1                                             |

| JA7    | Panel power voltage select<br>CAUTION: Incorrect setting can damage<br>panel | See panel voltage setting table 1                                             |

| JA8    | Panel power voltage select<br>CAUTION: Incorrect setting can damage<br>panel | See panel voltage setting table 1                                             |

| LED5A  | Power LED                                                                    | Green - normal<br>Off - no power                                              |

| LED5A1 | Power LED                                                                    | Green - normal<br>Off - no power                                              |

| SW1    | Function selection                                                           | See table 3                                                                   |

| SW2    | Function selection                                                           | See table 5                                                                   |

| SW5    | Panel selection                                                              | See table 4                                                                   |

### Table 1 : Panel voltage setting table (JA9, JA7 and JA8)

|                                     |                    |                    | ,                  |                                                                                                                                                                                |

|-------------------------------------|--------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input voltage via                   | JA9                | JA7                | JA8                | Jumper on board                                                                                                                                                                |

| PP1                                 | 1-2 & 3-4<br>OPEN  | 1-2 & 3-4<br>OPEN  | 1-2 & 3-4<br>CLOSE | $1 \bigcirc 0 \\ 3 \bigcirc 0 \\ 4 \end{bmatrix} JA9$ $1 \bigcirc 0 \\ 4 \end{bmatrix} JA7$ $1 \bigcirc 0 \\ 4 \end{bmatrix} JA8$ $3 \bigcirc 0 \\ 4 \end{bmatrix} JA8$        |

|                                     |                    |                    |                    |                                                                                                                                                                                |

| J7_IN (V-by-One)<br>or J3_IN (LVDS) | 1-2 & 3-4<br>OPEN  | 1-2 & 3-4<br>CLOSE | 1-2 & 3-4<br>OPEN  | $1 \bigcirc 0 & 2 \\ 3 \bigcirc 0 & 4 \\ 4 \end{bmatrix} JA9$ $1 \bigcirc 2 \\ 4 & JA7$ $1 \bigcirc 0 & 2 \\ 4 & JA7$ $1 \bigcirc 0 & 2 \\ 3 \bigcirc 0 & 4 \end{bmatrix} JA8$ |

|                                     |                    |                    |                    |                                                                                                                                                                                |

| PP6                                 | 1-2 & 3-4<br>CLOSE | 1-2 & 3-4<br>OPEN  | 1-2 & 3-4<br>OPEN  | $1 \bigoplus_{4}^{2} JA9$ $1 \bigoplus_{4}^{2} JA7$ $3 \bigoplus_{4}^{2} JA7$ $1 \bigoplus_{4}^{2} JA7$ $1 \bigoplus_{4}^{2} JA8$ $3 \bigoplus_{4}^{2} JA8$                    |

CAUTION: Incorrect setting can damage panel & controller

#### Table 2 : Panel voltage setting table (JP11 and JP12)

| Output power pin<br>selection on<br>J7_OUT | JP11      | JP12      | Jumper on board              |

|--------------------------------------------|-----------|-----------|------------------------------|

| Pin-44 to Pin-51<br>(Pin-1 to Pin-8)*      | 1-2 CLOSE | 1-2 CLOSE | 1 2 JP11<br>1 2 JP12         |

|                                            |           |           |                              |

| Pin-48 to Pin-51<br>(Pin-1 to Pin-4)*      | 1-2 CLOSE | 1-2 OPEN  | 1 2 JP11<br>1 0 0 2 JP12     |

|                                            |           |           |                              |

| Pin-44 to Pin-47<br>(Pin-5 to Pin-8)*      | 1-2 OPEN  | 1-2 CLOSE | 1 0 0 2 JP11<br>1 2 JP12     |

|                                            |           |           |                              |

| No power output<br>on pins                 | 1-2 OPEN  | 1-2 OPEN  | 1 0 0 2 JP11<br>1 0 0 2 JP12 |

## CAUTION: Incorrect setting can damage panel & controller

\*Pin # read at panel side

#### Table 3 : DIP switch selection (output to panel) - SW1

| Pos. # | Function            | Description                                                    |

|--------|---------------------|----------------------------------------------------------------|

| 1      | Image flip (H)      | OFF : Disable                                                  |

|        |                     | ON : Enable                                                    |

|        |                     |                                                                |

| 2      | Image flip (V)      | OFF : Disable                                                  |

|        |                     | ON : Enable                                                    |

|        |                     |                                                                |

| 3      | Data mapping select | OFF : Mapping B                                                |

|        |                     | ON : Mapping A                                                 |

| 4      |                     |                                                                |

| 4      | Lane count          | OFF : 8-lane (for 60Hz panel)<br>ON :16-lane (for 120Hz panel) |

|        |                     |                                                                |

|        |                     |                                                                |

#### Byte length

| I | Pos #5 | Pos #6 | Description     |

|---|--------|--------|-----------------|

|   | OFF    | OFF    | Byte length = 3 |

|   | OFF    | ON     | Byte length = 4 |

|   | ON     | OFF    | Reserved        |

|   | ON     | ON     | Reserved        |

Tcon mode

| Pos #7 | Pos #8 | Description |

|--------|--------|-------------|

| OFF    | OFF    | 1 division  |

| OFF    | ON     | 2 divisions |

| ON     | OFF    | 4 divisions |

| ON     | ON     | Reserved    |

#### Table 4 : DIP switch selection (input from controller) – SW5

|        | able 4. Dir Switch Sciection (input nom controller) – 000 |                                                                                          |  |  |  |

|--------|-----------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Pos. # | Function                                                  | Description                                                                              |  |  |  |

| 1      | Input signal selection                                    | OFF : 4096x2160 (4K UHD)<br>ON : 1920x1080 (FHD)                                         |  |  |  |

| 2      | V-by-One / LVDS selection                                 | OFF : V-by-One<br>ON : LVDS                                                              |  |  |  |

| 3      | Port select                                               | OFF* : V-by-One (8-lane) / LVDS (4-channel)<br>ON : V-by-One (4-lane) / LVDS (2-channel) |  |  |  |

| 4      | Bit mode                                                  | OFF : 10 bits<br>ON : 8 bits                                                             |  |  |  |

Note : \* Set to OFF if using 4K UHD input

### Data mapping select

| Pos #5 | Pos #6 | Desci                | ription      |

|--------|--------|----------------------|--------------|

| OFF    | OFF    | Mapping A (V-by-One) | VESA (LVDS)  |

| OFF    | ON     | Mapping B (V-by-One) | Reserved     |

| ON     | OFF    | Reserved             | JEIDA (LVDS) |

| ON     | ON     | Reserved             | Reserved     |

Tcon mode

| Toon mou | 0      |             |

|----------|--------|-------------|

| Pos #7   | Pos #8 | Description |

| OFF      | OFF    | 1 division  |

| OFF      | ON     | 2 divisions |

| ON       | OFF    | 4 divisions |

| ON       | ON     | Reserved    |

Note: \* Select 1 division when using input from LVDS

#### Table 5 : DIP switch selection – SW2\*

|        | Switch Sciection - OWZ  |                          |

|--------|-------------------------|--------------------------|

| Pos. # | Function*               | Description              |

| 1      | Pin 37 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 2      | Pin 36 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 3      | Pin 35 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 4      | Pin 34 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 5      | Pin 33 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 6      | Pin 32 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 7      | Pin 31 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 8      | Pin 30 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 9      | Pin 29 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| 10     | Pin 28 on V-By-One (J1) | ON = "Low", OFF = 'High' |

| IE-2000 | Panel  |

|---------|--------|

| side    | side   |

| Pin 37  | Pin 15 |

| Pin 36  | Pin 16 |

| Pin 35  | Pin 17 |

| Pin 34  | Pin 18 |

| Pin 33  | Pin 19 |

| Pin 32  | Pin 20 |

| Pin 31  | Pin 21 |

| Pin 30  | Pin 22 |

| Pin 29  | Pin 23 |

| Pin 28  | Pin 24 |

Note: \* The functions of pin are defined in the panel specification.

| PIN             | SYMBOL        | DESCRIPTION                                      |

|-----------------|---------------|--------------------------------------------------|

| 1               | NC            | No connection                                    |

| 2               | NC            | No connection                                    |

| 3               | NC            | No connection                                    |

| 4               | NC            | No connection                                    |

| 5               | NC            | No connection                                    |

| 6               | GND           | Ground                                           |

| 7               | GND           | Ground                                           |

| 8               | GND           | Ground                                           |

| 9               | GND           | Ground                                           |

| 10              | GND           | Ground                                           |

| 11              | GND           | Ground                                           |

| 12              | LVDS_OUT2_A4+ | Positive differential LVDS data bit A4           |

| 13              | LVDS_OUT2_A4- | Negative differential LVDS data bit A4           |

| 14              | GND           | Ground                                           |

| 15              | LVDS_OUT2_A3+ | Positive differential LVDS data bit A3           |

| 16              | LVDS_OUT2_A3- | Negative differential LVDS data bit A3           |

| 17              | GND           | Ground                                           |

| 18              | LVDS_OUT2_AC+ | Positive LVDS clock for A channel                |

| 19              | LVDS_OUT2_AC- | Negative LVDS clock for A channel                |

| 20              | LVDS_OUT2_A2+ | Positive differential LVDS data bit A2           |

| 21              | LVDS_OUT2_A2- | Negative differential LVDS data bit A2           |

| 22              | LVDS OUT2 A1+ | Positive differential LVDS data bit A1           |

| 23              | LVDS OUT2 A1- | Negative differential LVDS data bit A1           |

| 24              | LVDS_OUT2_A0+ | Positive differential LVDS data bit A0           |

| 25              | LVDS_OUT2_A0- | Negative differential LVDS data bit A0           |

| 26              | <br>GND       | Ground                                           |

| 27              | LVDS_OUT2_B4+ | Positive differential LVDS data bit B4           |

| 28              | LVDS_OUT2_B4- | Negative differential LVDS data bit B4           |

| 29              | GND           | Ground                                           |

| 30              | LVDS_OUT2_B3+ | Positive differential LVDS data bit B3           |

| 31              | LVDS_OUT2_B3- | Negative differential LVDS data bit B3           |

| 32              | GND           | Ground                                           |

| 33              | LVDS_OUT2_BC+ | Positive LVDS clock for B channel                |

| 34              | LVDS_OUT2_BC- | Negative LVDS clock for B channel                |

| 35              | LVDS_OUT2_B2+ | Positive differential LVDS data bit B2           |

| 36              | LVDS_0012_B2+ | Negative differential LVDS data bit B2           |

| 37              | LVDS_OUT2_B1+ | Positive differential LVDS data bit B2           |

| 38              | LVDS_OUT2_B1+ | Negative differential LVDS data bit B1           |

| 30              | LVDS_0012_B1- | Positive differential LVDS data bit B1           |

|                 |               |                                                  |

| <u>40</u><br>41 | LVDS_OUT2_B0- | Negative differential LVDS data bit B0<br>Ground |

| 41              | GND           | Ground                                           |

#### J3\_IN – LVDS\_2 input connector: JAE FI-RE51S-HF (Matching type : JAE FI-RE51HL)

| PIN | SYMBOL        | DESCRIPTION                            |

|-----|---------------|----------------------------------------|

| 1   | GND           | Ground                                 |

| 2   | LVDS_OUT1_B0- | Negative differential LVDS data bit B0 |

| 3   | LVDS_OUT1_B0+ | Positive differential LVDS data bit B0 |

| 4   | LVDS_OUT1_B1- | Negative differential LVDS data bit B1 |

| 5   | LVDS_OUT1_B1+ | Positive differential LVDS data bit B1 |

| 6   | LVDS_OUT1_B2- | Negative differential LVDS data bit B2 |

| 7   | LVDS_OUT1_B2+ | Positive differential LVDS data bit B2 |

| 8   | GND           | Ground                                 |

| 9   | LVDS_OUT1_BC- | Negative LVDS clock for B channel      |

| 10  | LVDS_OUT1_BC+ | Positive LVDS clock for B channel      |

| 11  | GND           | Ground                                 |

| 12  | LVDS_OUT1_B3- | Negative differential LVDS data bit B3 |

| 13  | LVDS_OUT1_B3+ | Positive differential LVDS data bit B3 |

| 14  | LVDS_OUT1_B4- | Negative differential LVDS data bit B4 |

| 15  | LVDS_OUT1_B4+ | Positive differential LVDS data bit B4 |

| 16  | GND           | Ground                                 |

| 17  | LVDS_OUT1_A0- | Negative differential LVDS data bit A0 |

| 18  | LVDS_OUT1_A0+ | Positive differential LVDS data bit A0 |

| 19  | LVDS_OUT1_A1- | Negative differential LVDS data bit A1 |

| 20  | LVDS_OUT1_A1+ | Positive differential LVDS data bit A1 |

| 21  | LVDS_OUT1_A2- | Negative differential LVDS data bit A2 |

| 22  | LVDS_OUT1_A2+ | Positive differential LVDS data bit A2 |

| 23  | GND           | Ground                                 |

| 24  | LVDS OUT1 AC- | Negative LVDS clock for A channel      |

| 25  | LVDS_OUT1_AC+ | Positive LVDS clock for A channel      |

| 26 | GND           | Ground                                 |

|----|---------------|----------------------------------------|

| 27 | LVDS_OUT1_A3- | Negative differential LVDS data bit A3 |

| 28 | LVDS_OUT1_A3+ | Positive differential LVDS data bit A3 |

| 29 | LVDS_OUT1_A4- | Negative differential LVDS data bit A4 |

| 30 | LVDS_OUT1_A4+ | Positive differential LVDS data bit A4 |

| 31 | GND           | Ground                                 |

| 32 | GND           | Ground                                 |

| 33 | NC            | No function                            |

| 34 | NC            | No function                            |

| 35 | OP2           | Reserved                               |

| 36 | OP1           | Reserved                               |

| 37 | GND           | Ground                                 |

| 38 | GND           | Ground                                 |

| 39 | GND           | Ground                                 |

| 40 | GND           | Ground                                 |

| 41 | GND           | Ground                                 |

| 42 | VLCD_LV       | No function                            |

| 43 | VLCD_LV       | No function                            |

| 44 | VLCD_LV       | No function                            |

| 45 | VLCD_LV       | No function                            |

| 46 | VLCD_LV       | No function                            |

| 47 | VLCD_HV       | Panel power supply                     |

| 48 | VLCD_HV       | Panel power supply                     |

| 49 | VLCD_HV       | Panel power supply                     |

| 50 | VLCD_HV       | Panel power supply                     |

| 51 | VLCD_HV       | Panel power supply                     |

### J7\_IN – V-by-One panel signal input connector: JAE FI-RE51S-HF (Matching type : JAE FI-RE51HL)

| PIN     | SYMBOL   | DESCRIPTION             |

|---------|----------|-------------------------|

| 1 (51)  | GND      | Ground                  |

| 2 (50)  | VB1_TX7P | V-by-One HS Data Lane 7 |

| 3 (49)  | VB1_TX7N | V-by-One HS Data Lane 7 |

| 4 (48)  | GND      | Ground                  |

| 5 (47)  |          | V-by-One HS Data Lane 6 |

| 6 (46)  | VB1_TX6N | V-by-One HS Data Lane 6 |

| 7 (45)  | GND      | Ground                  |

| 8 (44)  | VB1_TX5P | V-by-One HS Data Lane 5 |

| 9 (43)  | VB1_TX5N | V-by-One HS Data Lane 5 |

| 10 (42) |          | Ground                  |

| 11 (41) | VB1_TX4P | V-by-One HS Data Lane 4 |

| 12 (40) | VB1_TX4N | V-by-One HS Data Lane 4 |

| 13 (39) | GND      | Ground                  |

| 14 (38) | VB1_TX3P | V-by-One HS Data Lane 3 |

| 15 (37) | VB1_TX3N | V-by-One HS Data Lane 3 |

| 16 (36) | GND      | Ground                  |

| 17 (35) | VB1_TX2P | V-by-One HS Data Lane 2 |

| 18 (34) | VB1_TX2N | V-by-One HS Data Lane 2 |

| 19 (33) | GND      | Ground                  |

| 20 (32) | VB1_TX1P | V-by-One HS Data Lane 1 |

| 21 (31) | VB1_TX1N | V-by-One HS Data Lane 1 |

| 22 (30) | GND      | Ground                  |

| 23 (29) | VB1_TX0P | V-by-One HS Data Lane 0 |

| 24 (28) | VB1_TX0N | V-by-One HS Data Lane 0 |

| 25 (27) | GND      | Ground                  |

| 26 (26) | LOCKN    | V-by-One LOCK           |

| 27 (25) | HTPDN    | V-by-One HTPDN          |

| 28 (24) | OP10     | High/Low state control  |

| 29 (23) | OP9      | High/Low state control  |

| 30 (22) | OP8      | High/Low state control  |

| 31 (21) | OP7      | High/Low state control  |

| 32 (20) | OP6      | High/Low state control  |

| 33 (19) | OP5      | High/Low state control  |

| 34 (18) | OP4      | High/Low state control  |

| 35 (17) | OP3      | High/Low state control  |

| 36 (17) | OP2      | High/Low state control  |

| 37 (15) | OP1      | High/Low state control  |

| 38 (14) | GND      | Ground                  |

| 39 (13) | GND      | Ground                  |

|         | GND      |                         |

|         |          | Ground                  |

| 41 (11) |          | Ground                  |

| 42 (10) | GND      | Ground                  |

| 43 (9)  | NC       | No Connection           |

| 44 | (8) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

|----|-----|------------|--------------------------------------------|

| 45 | (7) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

| 46 | (6) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

| 47 | (5) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

| 48 | (4) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

| 49 | (3) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

| 50 | (2) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

| 51 | (1) | PVLCD_High | Panel power supply (selected by JP1 & JP2) |

J7\_OUT - V-by-One panel signal output connector: JAE FI-RE51S-HF (Matching type : JAE FI-RE51HL)

| PIN                     | SYMBOL               | DESCRIPTION                                                                              |

|-------------------------|----------------------|------------------------------------------------------------------------------------------|

|                         |                      |                                                                                          |

| 1 (51)                  |                      | Ground                                                                                   |

| 2 (50)                  |                      | V-by-One HS Data Lane 7                                                                  |

| 3 (49)                  |                      | V-by-One HS Data Lane 7                                                                  |

| <u>4 (48)</u><br>5 (47) |                      | Ground<br>V-by-One HS Data Lane 6                                                        |

| = ( )                   |                      |                                                                                          |

| 6 (46)                  |                      | V-by-One HS Data Lane 6<br>Ground                                                        |

| 7 (45)                  |                      |                                                                                          |

| <u> </u>                |                      | V-by-One HS Data Lane 5<br>V-by-One HS Data Lane 5                                       |

| 10 (42)                 |                      | Ground                                                                                   |

| 10 (42)                 |                      | V-by-One HS Data Lane 4                                                                  |

| 12 (40)                 |                      | V-by-One HS Data Lane 4                                                                  |

| 13 (39)                 |                      | Ground                                                                                   |

| 13 (39)                 |                      | V-by-One HS Data Lane 3                                                                  |

| 15 (37)                 | VB1_TX3P<br>VB1_TX3N | V-by-One HS Data Lane 3                                                                  |

| 16 (36)                 |                      | Ground                                                                                   |

| 17 (35)                 |                      | V-by-One HS Data Lane 2                                                                  |

| 18 (34)                 | VB1_TX2N             | V-by-One HS Data Lane 2                                                                  |

| 19 (33)                 |                      | Ground                                                                                   |

| 20 (32)                 | VB1 TX1P             | V-by-One HS Data Lane 1                                                                  |

| 21 (31)                 |                      | V-by-One HS Data Lane 1                                                                  |

| 22 (30)                 |                      | Ground                                                                                   |

| 23 (29)                 |                      | V-by-One HS Data Lane 0                                                                  |

| 24 (28)                 |                      | V-by-One HS Data Lane 0                                                                  |

| 25 (27)                 |                      | Ground                                                                                   |

| 26 (26)                 |                      | V-by-One LOCK                                                                            |

| 27 (25)                 |                      | V-by-One HTPDN                                                                           |

| 28 (24)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 29 (23)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 30 (22)                 | Panel option         | High/Low state control (Controlled by SW3)                                               |

| 31 (21)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 32 (20)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 33 (19)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 34 (18)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 35 (17)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 36 (17)                 |                      | High/Low state control (Controlled by SW3)                                               |

| 37 (15)                 | Panel option         | High/Low state control (Controlled by SW3)                                               |

| 38 (14)                 | GND                  | Ground                                                                                   |

| 39 (14)                 |                      | Ground                                                                                   |

| 40 (12)                 |                      | Ground                                                                                   |

| 40 (12)                 |                      | Ground                                                                                   |

| 41 (11)                 | GND                  | Ground                                                                                   |

| ( - /                   | -                    | No Connection                                                                            |

|                         |                      | Panel power supply (selected by JP1 & JP2)                                               |

| (-7                     | PVLCD_High           | Panel power supply (selected by JP1 & JP2)<br>Panel power supply (selected by JP1 & JP2) |

| 45 (7)                  |                      |                                                                                          |

| 46 (6)                  | PVLCD_High           | Panel power supply (selected by JP1 & JP2)                                               |

| 47 (5)                  |                      | Panel power supply (selected by JP1 & JP2)                                               |

| 48 (4)                  | PVLCD_High           | Panel power supply (selected by JP1 & JP2)                                               |

| 49 (3)                  |                      | Panel power supply (selected by JP1 & JP2)                                               |

| 50 (2)                  |                      | Panel power supply (selected by JP1 & JP2)                                               |

| 51 (1)                  | PVLCD_High           | Panel power supply (selected by JP1 & JP2)                                               |

#### J8\_OUT – V-by-One panel signal output connector: JAE FI-RE41S-HF (Matching type : JAE FI-RE41HL)

| PIN | SYMBOL | DESCRIPTION   |

|-----|--------|---------------|

| 1   | NC     | No connection |

| 2   | NC     | No connection |

| 3   | NC     | No connection |

| 4   | NC     | No connection |

| 5   | NC     | No connection |

| 6   | NC     | No connection |

| 7  | NC        | No connection    |

|----|-----------|------------------|

| 8  | NC        | No connection    |

| 9  | NC        | No connection    |

| 10 | NC        | No connection    |

| 11 | NC        | No connection    |

| 12 | NC        | No connection    |

| 13 | NC        | No connection    |

| 14 | NC        | No connection    |

| 15 | NC        | No connection    |

| 16 | NC        | No connection    |

| 17 | GND       | Ground           |

| 18 | VB1_TX15P | V-By-One Lane 15 |

| 19 | VB1_TX15N | V-By-One Lane 15 |

| 20 | GND       | Ground           |

| 21 | VB1_TX14P | V-By-One Lane 14 |

| 22 | VB1_TX14N | V-By-One Lane 14 |

| 23 | GND       | Ground           |

| 24 | VB1_TX13P | V-By-One Lane 13 |

| 25 | VB1_TX13N | V-By-One Lane 13 |

| 26 | GND       | Ground           |

| 27 | VB1_TX12P | V-By-One Lane 12 |

| 28 | VB1_TX12N | V-By-One Lane 12 |

| 29 | GND       | Ground           |

| 30 | VB1_TX11P | V-By-One Lane 11 |

| 31 | VB1_TX11N | V-By-One Lane 11 |

| 32 | GND       | Ground           |

| 33 | VB1_TX10P | V-By-One Lane 10 |

| 34 | VB1_TX10N | V-By-One Lane 10 |

| 35 | GND       | Ground           |

| 36 | VB1_TX9P  | V-By-One Lane 9  |

| 37 | VB1_TX9N  | V-By-One Lane 9  |

| 38 | GND       | Ground           |

| 39 | VB1_TX8P  | V-By-One Lane 8  |

| 40 | VB1 TX8N  | V-By-One Lane 8  |

| 41 | GND       | Ground           |

#### P6 - Reserved: Mini USB

| PIN | DESCRIPTION |

|-----|-------------|

| 1   | +5V VCC     |

| 2   | Data -      |

| 3   | Data +      |

| 4   | Ground      |

### CN1 – RS-232 port: JST B6B-XH-A (Matching type : XHP-6)

| PIN | SYMBOL        | DESCRIPTION    |

|-----|---------------|----------------|

| 1   | EXT_MSTR2_SCL | Reserved       |

| 2   | EXT_MSTR2_SDA | Reserved       |

| 3   | VCC           | +5V            |

| 4   | TXD           | RS-232 Tx data |

| 5   | GND           | Ground         |

| 6   | RXD           | RS-232 Rx data |

#### CN20 - Input power control : JST 2-way, B2B-PH-K (Matching type : PHR-2)

| PIN | DESCRIPTION      |  |  |  |  |  |  |

|-----|------------------|--|--|--|--|--|--|

| 1   | +5V logic signal |  |  |  |  |  |  |

| 2   | +5V logic signal |  |  |  |  |  |  |

#### PP1 - 12V/24VDC power input: Molex 43045-0400 or compatible (Matching type : Molex 43025-0400 or compatible)

| PIN | DESCRIPTION       |

|-----|-------------------|

| 1   | +12VDC / 24VDC in |

| 2   | Ground            |

| 3   | +12VDC / 24VDC in |

| 4   | Ground            |

#### PP3 – Alternate 12V/24VDC input power: Molex 2 pin 0.156" pitch

| PIN | DESCRIPTION       |

|-----|-------------------|

| 1   | +12VDC / 24VDC in |

| 2   | Ground            |

### PP6 – External panel power input: Molex 43045-0400 or compatible (Matching type : Molex 43025-0400 or compatible)

| PIN | DESCRIPTION          |

|-----|----------------------|

| 1   | External panel power |

| 2   | Ground               |

| 3   | External panel power |

| 4   | Ground               |

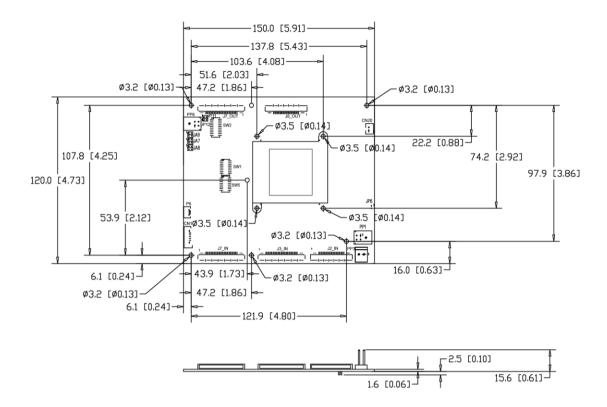

## **BOARD DIMENSIONS**

The maximum thickness of the IE-2000 is 20.65mm with or without video add-on board (measured from bottom of PCB to top of components, including any underside components & leads). We recommend clearances of:

- 5mm from bottom of PCB if mounting on a metal plate we also recommend a layer of suitable insulation material is added to the mounting plate surface.

- 10mm above the components

- 3~5mm around the edges

Any of the holes shown above can be used for mounting the PCB, they are 3.2mm in diameter.

CAUTION: Ensure adequate insulation is provided for all areas of the PCB with special attention to high voltage parts such as the inverter.

## TROUBLESHOOTING

### General

A general guide to troubleshooting a flat panel display system it is worth considering the system as separate elements, such as:

- Controller (jumpers, PC settings)

- Panel (Cabling, connection, panel, PC settings)

- Backlight (inverter, cabling, backlight tubes)

- Cabling

- Computer system (display settings, operating system)

Through step by step cross checking with instruction manuals and a process of elimination to isolate the problem it is usually possible to clearly identify the problem area.

### No image:

- > If the panel backlight is not working it may still be possible to just see some image on the display.

- A lack of image is most likely to be caused by incorrect connection, lack of power, failure to provide a signal or incorrect graphic card settings.

#### Image position:

If it is impossible to position the image correctly, i.e. the image adjustment controls will not move the image far enough, then test using another graphics card. This situation can occur with a custom graphics card that is not close to standard timings or if something is in the graphics line that may be affecting the signal such as a signal splitter (please note that normally a signal splitter will not have any adverse effect).

#### Image appearance:

- > A faulty panel can have blank lines, failed sections, flickering or flashing display

- Incorrect graphics card refresh rate, resolution or interlaced mode will probably cause the image to be the wrong size, to scroll, flicker badly or possibly even no image.

- Incorrect jumper settings on the controller & IE-2000 may cause everything from total failure to incorrect image. CAUTION: Do not set the panel power input incorrectly.

- Sparkling on the display: faulty panel signal cable.

### **Backlight:**

Items to check include: Power input, Controls, Inverter and Tubes generally in this order. If half the screen is dimmer than the other half:

- > Check cabling for the inverter.

- > For a specific backlight tube check the AC pins orientation (CAUTION: Never reverse any DC power pins).

Also:

- If adjusting brightness control has no effect the chances are that the VR rating or method of adjusting brightness is not compatible or correctly connected to the inverter.

- If system does not power down when there is a loss of signal

### **Continued failure:**

If unit after unit keeps failing consider and investigate whether you are short circuiting the equipment or doing something else seriously wrong.

Generally after common sense issues have been resolved we recommend step by step substitution of known working parts to isolate the problem.

## SPECIFICATIONS

| Panel compatibility          | Compatible with 120Hz panel with 4096x2160 resolutions.<br>A specified BIOS and some factory adjustment may be required for individual panel timings. |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. of colours               | Up to 10 bit per color, providing 1.07 billion colours.                                                                                               |

| Panel signal                 | V-By-One                                                                                                                                              |

| Board dimensions             | 150mm x 120mm (5.91 in x 4.73 in)                                                                                                                     |

| Power consumption            | 10W approx. (not including panel power consumption)                                                                                                   |

| Input voltage                | 12V/24VDC +/- 5%                                                                                                                                      |

| Storage temperature limits   | -40°C to +70°C                                                                                                                                        |

| Operating temperature limits | $0^{\circ}$ C to + $60^{\circ}$ C                                                                                                                     |

## NOTES

Please note the following:

- For specific panel setup a sample of an LCD may be required (this will be returned) and a copy of the full technical specifications for the panel from the manufacturer.

- Re-layout and custom development services are available.

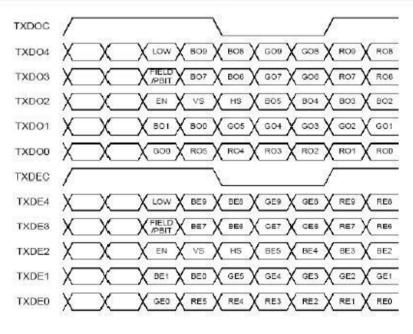

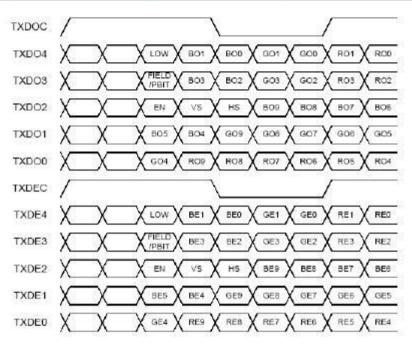

## Appendix I – Mapping definition

• Definition of VESA :

| DPort Output Pair | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|-----------|-------|-------|-------|-------|-------|-------|

| DB[7:6] / TXDEC   |           |       |       |       |       |       |       |

| DB[3:2] / TXDE0   | GE0       | RE5   | RE4   | RE3   | RE2   | RE1   | RE0   |

| DB[5:4] / TXDE1   | BE1       | BE0   | GE5   | GE4   | GE3   | GE2   | GE1   |

| DB[9:8] / TXDE2   | EN        | VS    | HS    | BE5   | BE4   | BE3   | BE2   |

| DG[3:2] / TXDE3   | field/prg | BE7   | BE6   | GE7   | GE6   | RE7   | RE6   |

| DG[5:4] / TXDE4   | low       | BE9   | BE8   | GE9   | GE8   | RE9   | RE8   |

| DG[7:6] / TXDO0   | GO0       | RO5   | RO4   | RO3   | RO2   | RO1   | RO0   |

| DG[9:8] / TXDO1   | BO1       | BO0   | GO5   | GO4   | GO3   | GO2   | GO1   |

| DR[5:4] / TXDO2   | EN        | VS    | HS    | B05   | BO4   | BO3   | BO2   |

| DR[7:6] / TXDO3   | field/prg | BO7   | BO6   | G07   | GO6   | RO7   | RO6   |

| DR[9:8] / TXDO4   | low       | BO9   | BO8   | GO9   | GO8   | RO9   | RO8   |

| DR[3:2] / TXDOC   |           |       | -     |       |       |       |       |

## • Definition of JEIDA :

| DPort Output Pair | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------------|-----------|-------|-------|-------|-------|-------|-------|

| DB[7:6] / TXDEC   |           |       |       |       |       |       |       |

| DB[3:2] / TXDE0   | GE4       | RE9   | RE8   | RE7   | RE6   | RE5   | RE4   |

| DB[5:4] / TXDE1   | BE5       | BE4   | GE9   | GE8   | GE7   | GE6   | GE5   |

| DB[9:8] / TXDE2   | EN        | VS    | HS    | BE9   | BE8   | BE7   | BE6   |

| DG[3:2] / TXDE3   | field/prg | BE3   | BE2   | GE3   | GE2   | RE3   | RE2   |

| DG[5:4] / TXDE4   | low       | BE1   | BEO   | GE1   | GE0   | RE1   | REO   |

| DG[7:6] / TXDO0   | GO4       | R09   | R08   | R07   | R06   | R05   | RO4   |

| DG[9:8] / TXDO1   | BO5       | BO4   | GO9   | GO8   | G07   | GOE   | GO5   |

| DR[5:4] / TXDO2   | EN        | VS    | HS    | BO9   | BO8   | BO7   | BO6   |

| DR[7:6] / TXDO3   | field/prg | BO3   | BO2   | GO3   | GO2   | RO3   | RO2   |

| DR[9:8] / TXDO4   | low       | BO1   | BO0   | G01   | GO0   | R01   | ROO   |

| DR[3:2] / TXDOC   |           |       |       |       |       |       |       |

## WARRANTY

The products are warranted against defects in workmanship and material for a period of three (3) year from the date of purchase provided no modifications are made to it and it is operated under normal conditions and in compliance with the instruction manual.

The warranty does not apply to:

- Product that has been installed incorrectly, this specifically includes but is not limited to cases where electrical short circuit is caused.

- Product that has been altered or repaired except by the manufacturer (or with the manufacturer's consent).

- Product that has subjected to misuse, accidents, abuse, negligence or unusual stress whether physical or electrical.

- Ordinary wear and tear.

Except for the above express warranties, the manufacturer disclaims all warranties on products furnished hereunder, including all implied warranties of merchantability and fitness for a particular application or purpose. The stated express warranties are in lieu of all obligations or liabilities on the part of the manufacturer for damages, including but not limited to special, indirect consequential damages arising out of or in connection with the use of or performance of the products.

## CAUTION

Whilst care has been taken to provide as much detail as possible for use of this product it cannot be relied upon as an exhaustive source of information. This product is for use by suitably qualified persons who understand the nature of the work they are doing and are able to take suitable precautions and design and produce a product that is safe and meets regulatory requirements.

## LIMITATION OF LIABILITY

The manufacturer's liability for damages to customer or others resulting from the use of any product supplied hereunder shall in no event exceed the purchase price of said product.

## TRADEMARKS

The following are trademarks of Digital View Ltd:

- Digital View

- IE-2000

## CONTACT DETAILS

Digital View has offices in Asia, Europe and USA :

### USA

Digital View Inc. 18440 Technology Drive Building 130 Morgan Hill, California, 95037 USA

**Tel**: (1) 408-782 7773 **Fax**: (1) 408-782 7883

Sales: <u>ussales@digitalview.com</u>

### EUROPE

Digital View Ltd. The Lake House Knebworth Park Herts, SG3 6PY UK

Tel: +44-(0)20-7631-2150 Fax: Fax: +44-(0)20-7631-2156

Sales: <u>uksales@digitalview.com</u>

### ASIA

Digital View Ltd 2nd Floor Bamboos Center 52 Hung To Road Kwun Tong Hong Kong

Tel: (852) 2861 3615

Fax: (852) 2520 2987

Sales: <u>hksales@digitalview.com</u>

### WEBSITE

www.digitalview.com