# WWW.FINDLCD.COM

# SPECIFICATIONS FOR LIQUID CRYSTAL DISPLAY MODULE

MODEL NO.: HY-1602H-201 DATE:2003/2/12

| Approved | Checked | epartment |

|----------|---------|-----------|

|          |         |           |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 1 of 26               |

# **CONTENTS**

| I . General Specification                        | (3-6)  |

|--------------------------------------------------|--------|

| II . The Characteristics and Reliability Test    | (7-8)  |

| III. The LCD Measuring Method and Equipment      | (9-11) |

| IV. Standard Specifications for Product Quality  | (12-13 |

| V. Instruction System and Description of Details | (19-26 |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 2 of 26               |

# I .General Specifications

#### 1. General

The AV-DISPLAY dot matrix LCD module consist of the liquid crystal display C-MOS driver and C-MOS LSI controller, the module utilizes 5\*7 dot matrix characters to provide full alphanumeric capability. All control, refresh and display functions are executed by a dedicated on-board controller, the module is capable of displaying the full 160-character JIS font set .data interfacing is via the 4-bit or 8-bit bi-directional data bus by using of simple control commands—the data can be—selective written to the data register.

- 2. Features

- A. Built-In Controller LSI.

- B. 5\*7 Dot Matrix With Cursor.

- C. Micro-Processor Compatible Data-Bus Interface(4-Bit Or 8-Bit).

- D. Character Generator ROM Built-In

5\*8 Dot: -----208 Character Fonts

5\*10 Dot: -----32 Character Fonts

E. Character Generator RAM-----Customer Rewritable

5\*8 Font:8 Characters

- F. Powerful Control Command

- (1) Display Clear

- (2) Return Home

- (3) Cursor Preset

- (4) Cursor On/Off Or Cursor Blinking

- (5) Cursor Display Shift

- (6) Display Shift

- (7) Display On/Off Control

- (8) Display Data Read/Write

- G. Low power consumption 5.0v power supply

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 3 of 26               |

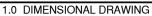

# H. Attaching drawing and general description.

QiuTian,ShiJia

# HY-1602H-201

16x2 CHARACTERS 1/16DUTY, 1/5BI AS

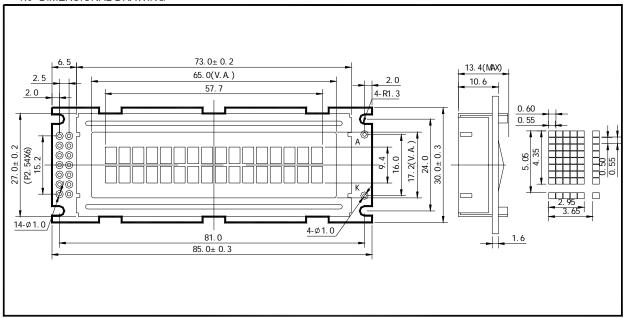

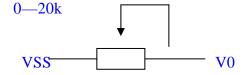

#### 2.0 BLOCK DIAGRAM & POWER SUPPLY

#### 3.0 MECHANICAL SPECIFICATIONS & FEATURE

| Item                 | Nominal Dimensions(mm) | FEA                   | JRE            |  |

|----------------------|------------------------|-----------------------|----------------|--|

| Itom                 | Normal Dimensions(min) | LCD Type              | STN            |  |

| Module Size (W*H*T)  | 85.0≠ 30.0≠ 13.4       | LCD Colour            | Yellow-Green   |  |

| View Area (W*H)      | 65.0≠ 17.2             | View Angle            | 6 O'clock      |  |

| Character Pitch(W*H) | 3.65 ≠ 5.05            | Display Type          | Positive Type  |  |

| Character Size(WxH)  | 2.95 ≠ 4.35            | Rear polarizer        | Transflective  |  |

| Character Font       | 5≠8                    | Operating Temperature | 0▲ C ~ 50▲ C   |  |

| Dot Pitch (W*H)      | 0.60≠ 0.55             | Storage Temperature   | -20▲ C ~ 70▲ C |  |

| Dot Size (W*H)       | 0.55≠ 0.50             | Blacklight            | LED (Yellow)   |  |

#### 4.0 ELECTRICAL CHARACTERISTICS

| Item                          | Symbol | Test Condition     | Min. | Тур. | Max. | Unit |

|-------------------------------|--------|--------------------|------|------|------|------|

| Operating Voltage             | Vdd    | Ta=25▲C            |      | 5.0  |      | V    |

| Operating Voltage for LCD     | Vlcd   | Ta=25▲C            |      | 4.2  |      | V    |

| Supply Current                | ldd    | Ta=25▲ C, Vdd=5.0V |      | 2.0  | 3.0  | mA   |

| Supply Current for Blacklight | If     | Ta=25▲ C, Vf=4.2V  |      | 120  |      | mA   |

#### 5.0 INTERFACE PIN CONNECTIONS

| Pin No | Symbol  | Level | Description                                                  |

|--------|---------|-------|--------------------------------------------------------------|

| 1      | VDD     |       | Power supply for Logic(+5.0V)                                |

| 2      | VSS     |       | GND                                                          |

| 3      | Vo      |       | Power supply for LCD drive                                   |

| 4      | RS      | H/L   | Register selection (H:Data registor, L:Instruction registor) |

| 5      | R/W     | H/L   | Read/write selection (H:Read,L:Write)                        |

| 6      | E       | H/H—L | Enable signal for LCM                                        |

| 7-14   | DB0-DB7 | H/L   | Data Bus lines                                               |

| A      | LEDA    |       | Power supply for Blacklight(+)                               |

| K      | LEDK    |       | Power supply for Blacklight(-)                               |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 4 of 26               |

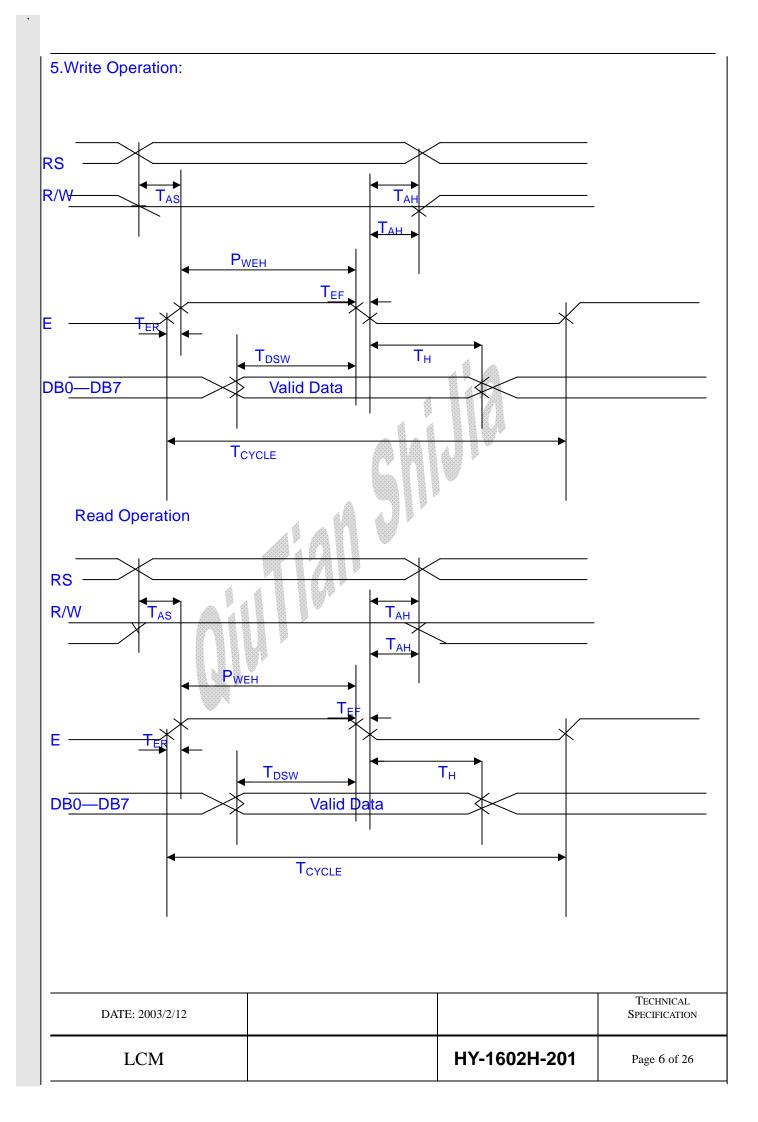

# 4. Timing Characteristics:

Write Operation and Read Operation

| Item                    | Symbol             | Min. | Тур. | Max. | Unit |

|-------------------------|--------------------|------|------|------|------|

| Enable Cycle Time       | T <sub>CYCLE</sub> | 500  |      |      | nS   |

| Enable Pulse Width      | P <sub>WEH</sub>   | 220  |      |      | nS   |

| Enable Rise & Fall Time | $T_{ER}, T_{EF}$   |      |      | 25   | nS   |

| Address Set-Up Time     | T <sub>AS</sub>    | 40   |      |      | nS   |

| Address Hold Time       | T <sub>AH</sub>    | 10   |      |      | nS   |

| Data Set-Up Time        | T <sub>DSW</sub>   | 60   |      |      | nS   |

| Data Hold Time          | T <sub>H</sub>     | 10   |      |      | nS   |

|                         |                                  |      | 11 4    |      |      |

|-------------------------|----------------------------------|------|---------|------|------|

| Item                    | Symbol                           | Min. | Тур.    | Max. | Unit |

| Enable Cycle Time       | T <sub>CYCLE</sub>               | 500  | 5       | -    | nS   |

| Enable Pulse Width      | P <sub>WEH</sub>                 | 220  |         | -    | nS   |

| Enable Rise & Fall Time | T <sub>ER</sub> ,T <sub>EF</sub> |      | <b></b> | 25   | nS   |

| Address Set-Up Time     | T <sub>AS</sub>                  | 40   |         | -    | nS   |

| Address Hold Time       | T <sub>AH</sub>                  | 10   |         | -    | nS   |

| Data Set-Up Time        | T <sub>DSW</sub>                 | -    |         | 120  | nS   |

| Data Hold Time          | THE                              | 20   |         |      | nS   |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 5 of 26               |

# II.The Characteristics and The Reliability Test

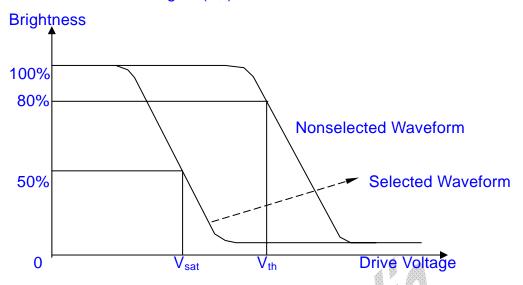

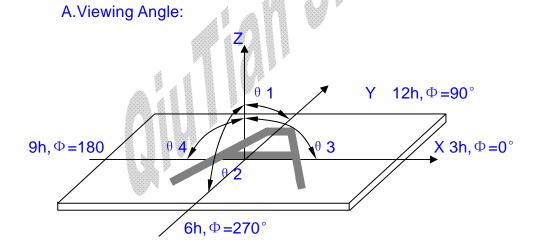

1. Electro-Optic Characteristics:

Condition: TEMP= $(21\pm3)^{\circ}$ C HUM= $(70\pm5)^{\circ}$ RH

V<sub>DD</sub>: 5.0V F<sub>OSC</sub>: 270KHZ

| N | Item                          |         | Symbol | Min. | Тур. | Max. | Unit | Remarks |

|---|-------------------------------|---------|--------|------|------|------|------|---------|

| 0 |                               |         |        |      |      |      |      |         |

| 1 | Operating Vol                 | tage    | Vop    |      | 5.0  |      | V    |         |

| 2 | Current Cons                  | umption | Is     |      | 1.30 |      | mA   |         |

| 3 | Response Tim                  | ne      | Ton    |      | 150  |      | ms   |         |

|   |                               |         | Toff   |      | 120  |      | ms   |         |

| 4 | Contrast                      |         | CR     | 3    |      |      |      |         |

| 5 | Viewing                       | 12H     | θ 1    |      | 15   |      |      |         |

|   | Angle (CR≥3.0)                | 6H      | θ 2    |      | 45   | 1    | Deg. |         |

|   | (011 > 0.0)                   | 3H      | θ 3    |      | 50   |      |      |         |

|   |                               | 9H      | θ 4    |      | 50   |      |      |         |

| 6 | Threshold Vol                 | tage    | Vth    |      | 1.14 |      | V    |         |

| 7 | Backlight Curl<br>Consumption | rent    |        |      |      | 8    | mA   |         |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 7 of 26               |

# 2.Reliability Test(No ITO heat)

| No | Items                         | Test Condition                                      |   | Test<br>Result |

|----|-------------------------------|-----------------------------------------------------|---|----------------|

| 1  | High Temp<br>Storage          | Temp:80±2°C<br>Time:96h<br>Restore:24h              |   | Passed         |

| 2  | Low Temp<br>Storage           | Temp:-30±3°C<br>Time:96h<br>Restore:24h             |   | Passed         |

| 3  | High Temp<br>Static drive     | Temp:70±2°C<br>Vop:5V<br>Time:96h<br>Restore:24h    | 4 | Passed         |

| 4  | Low Temp<br>Static drive      | Temp:-20±3°C<br>Vop:5V<br>Time:96h<br>Restore:24h   |   | Passed         |

| 5  | High Temp High<br>Hum Storage | Temp:40±2°C<br>Hum:95%Rh<br>Time:96h<br>Restore:24h |   | Passed         |

| 6  | Thermal<br>Shock              | Temp:(°C)  70  25  -20  30  5 Cycles Restore:24h    |   | Passed         |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 8 of 26               |

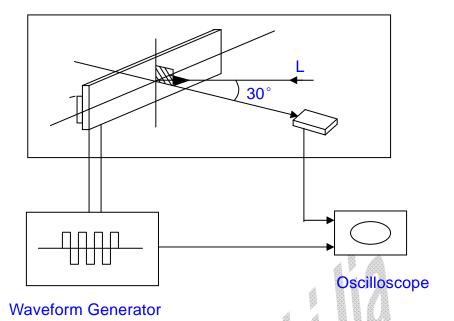

# **III. The LCD Measuring Method and Equipment**

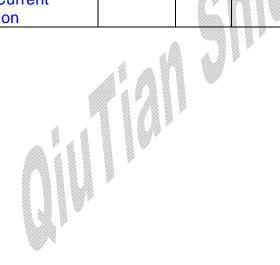

- 1. Current Consumption Measuring

- (1) Equipment

(2) Condition

Operating Frequency: 64HZ

Operating Voltage (RMS): Selected Voltage

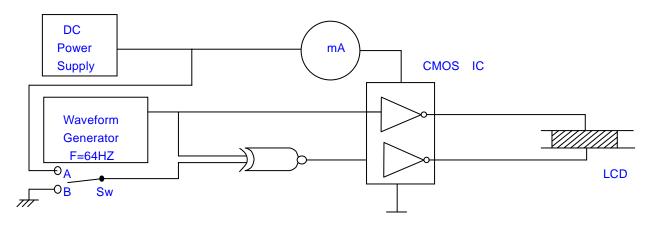

- 2. Threshold Voltage and Response Time Measuring

- (1) Equipment

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 9 of 26               |

# (2) Definition

# A. Threshold Voltage $(V_{th})$

# B. Response Time

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 10 of 26              |

# 3. Contrast Measuring

# (1) Equipment

# (2)Definition:

# B. Contrast Ratio (Positive)

CR= Brightness of non-selected wave-form

Brightness of selected wave-form

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 11 of 26              |

# **W.Standard Specifications for Product Quality**

#### 1. Manner of Test::

- 1.1.The Test Must Be Under 40w Flourescent Light, And The Distance Of View Must Be At 30cm.

- 1.2. The Test Direction Is Based On Around 15° 45° Of Vertical Line.

#### 2. Definition Of Defects

- 2.1 Major Defects

- A:Non-Display

- **B:Segment Missing**

- C:Over Current

- **D:Segment Short**

- E:Sealant Dishardexn

- F:Wrong Polarizer Direction

- 2.2 Interface Circuit and Drive Programe on LCM of character series.

#### A. Interface circuit:

| MPU8031 | LCM |

|---------|-----|

| P1.0    | DB0 |

| P1.1    | DB1 |

| P1.2    | DB2 |

| P1.3    | DB3 |

| P1.4    | DB4 |

| P1.5    | DB5 |

| P1.6    | DB6 |

| P1.7    | DB7 |

| P3.0    | RS  |

| P3.1    | E   |

| P3.2    | RW  |

|         |     |

|         |     |

# B.Drive programme for testing LCM of character series.

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 12 of 26              |

| ORG  | 0000H                            |                            |

|------|----------------------------------|----------------------------|

| AJMP | MAIN                             |                            |

|      |                                  |                            |

| ORG  | 0300H                            |                            |

| DB   | 58H,58H,58H,58H,58H,58H,58H,     |                            |

| DB   | 58H,58H,58H,58H,58H,58H,         |                            |

| DB   | 58H,58H,58H,58H,58H,58H,58H,     |                            |

| DB   | 58H,58H,58H,58H,58H,58H,58H,     |                            |

| DB   | 58H,58H,58H,58H,58H,58H,58H,     |                            |

| ORG  | 0350H                            |                            |

| DB   | 2AH,59H,55H,53H,55H,4EH,47H,2AH, |                            |

| DB   | 45H,4CH,45H,43H,2EH,4CH,54H,44H, |                            |

| DB   | 2AH,44H,4FH,54H,2AH,4DH,41H,54H, |                            |

| DB   | 52H,49H,58H,2AH,4CH,43H,44H,2AH, |                            |

| DB   | 4BH,65H,5AH,6FH,6EH,48H,75H,69H, |                            |

| DB   | 2AH,59H,55H,53H,55H,4EH,47H,2AH, |                            |

| DB   | 45H,4CH,45H,43H,2EH,4CH,54H,44H, |                            |

| DB   | 2AH,44H,4FH,54H,2AH,4DH,41H,54H, |                            |

| DB   | 52H,49H,58H,2AH,4CH,43H,44H,2AH, |                            |

| DB   | 4BH,65H,5AH,6FH,6EH,48H,75H,69H, |                            |

| DB   | 2AH,2AH,2AH,2AH,2AH,2AH,         |                            |

| DB   | 44H,4FH,54H,20H,4DH,41H,54H,52H, |                            |

| DB   | 49H,58H,20H,4CH,49H,51H,55H,49H, |                            |

| DB   | 44H,20H,43H,52H,59H,53H,54H,41H, |                            |

| DB   | 4CH,20H,44H,49H,53H,50H,4CH,41H, |                            |

| DB   | 59H,20H,4DH,4FH,55H,44H,4CH,45H, |                            |

| DB   | 2AH,2AH,2AH,2AH,2AH,2AH,         |                            |

| DB   | 2AH,2AH,2AH,2AH,2AH,2AH,         |                            |

|      |                                  | Trowns                     |

| DA   | ATE: 2003/2/12                   | TECHNICAL<br>SPECIFICATION |

|      |                                  |                            |

HY-1602H-201

Page 13 of 26

LCM

```

DB

54H,4DH,0B0H,44H,4DH,43H,34H,30H,

DB

32H,2AH,2AH,2AH,2AH,2AH,2AH,

DB

2AH,2AH,2AH,2AH,2AH,2AH,2AH,

DB

2AH,2AH,2AH,2AH,2AH,2AH,2AH,

MAIN:

MOV

SP, #60H

;Initial for the first display

MOV

P1, #38H

;set function

LCALL

WINST

MOV

P1, #0EH

;set display on/off control

LCALL WINST

MOV

P1, #06H

;set Entry mode

LCALL WINST

;clear display,write code 20h into all DDRAM

MOV

P1, #01H

LCALL WINST

LCALL DELAY1

MOV

DPTR, #0300H

;Set Pointer

MOV

R0, #28H

MOV

R2, #00H

A, #00H

MOV

MOV

P1, #80H

set DDRAM address 0000h

LCALL

WINST

LOOP1:

MOVC

A, @A+DPTR

MOV

P1, A

LCALL

WDATA

INC

R2

MOV

A, R2

DJNZ

R0, LOOP1

MOV

DPTR, #0328H

MOV

R0, #28H

MOV

R2, #00H

TECHNICAL

DATE: 2003/2/12

SPECIFICATION

HY-1602H-201

LCM

Page 14 of 26

```

```

MOV

A, #00H

MOV

P1, #0C0H

LCALL

WINST

LOOP2:

MOVC

A, @A+DPTR

MOV

P1, A

LCALL

WDATA

INC

R2

MOV

A, R2

DJNZ

R0, LOOP2

;The first display is over

LCALL DELAY2

;paused about 5ms

;initial for the second display

MOV

SP, #60H

MOV

P1, #38H

LCALL

WINST

MOV

P1, #0EH

LCALL WINST

MOV

P1, #06H

LCALL WINST

MOV

P1, #01H

WINST

LCALL

LCALL

DELAY1

MOV

DPTR, #0350H

;ready for the first line display

MOV

R0, #28H

MOV

R2, #00H

MOV

A, #00H

MOV

P1, #80H

LCALL

WINST

LOOP3:

MOVC

A, @A+DPTR

MOV

P1, A

LCALL

WDATA

TECHNICAL

DATE: 2003/2/12

SPECIFICATION

HY-1602H-201

LCM

Page 15 of 26

```

```

INC

R2

MOV

A, R2

DJNZ

;THE first line display is over

R0, LOOP3

DPTR, #0378H ; ready for the second line display

MOV

MOV

R0, #28H

MOV

R2, #00H

MOV

A, #00H

MOV

P1, #0C0H

LCALL

WINST

LOOP4:

MOVC

A, @A+DPTR

MOV

P1, A

LCALL WDATA

INC

R2

MOV

A, R2

;main program is end upto here

DJNZ

R0, LOOP4

LOOP5:

LCALL DELAY2

AJMP

MAIN

WINST:

;write to instruction register

CLR

P3.0

CLR

P3.2

SETB

P3.1

LCALL DELAY1

CLR

P3.1

LCALL DELAY1

RET

WDATA:

CLR

;write to data register

P3.2

SETB

P3.0

P3.1

SETB

TECHNICAL

DATE: 2003/2/12

SPECIFICATION

HY-1602H-201

LCM

Page 16 of 26

```

```

LCALL DELAY1

CLR

P3.1

LCALL DELAY1

RET

DELAY1:

MOV

50H, #08H

;delay 1648 us

ADDR1: PUSH

50H

ADDR2: PUSH

50H

ADDR3: PUSH

50H

ADDR4: DJNZ

50H, ADDR4

POP

50H

50H, ADDR3

DJNZ

POP

50H

DJNZ

50H, ADDR2

POP

50H

DJNZ

50H, ADDR1

RET

DELAY2:

MOV

R0, #0CCH

R2, #66H

MOV

ADDR5:

LCALL DELAY1

;delay ccH X 1648us

DJNZ

R0, ADDR5

ADDR6:

LCALL DELAY1

;delay 66H X 1648us total 5.05ms

DJNZ

R2, ADDR6

RET

END

```

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 17 of 26              |

# 3.Inspection Item and Standards

| Item                                        | The Standard Of Quality Inspection                                                                                                                                                                              | Checking<br>Manner                                                      | Quality<br>Ratio |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|

| Frame                                       | Smooth and even surface,no crack,no scratch,no rusty,and not be wrenched out of shape.the range between convex and concave is:d≤0.35mm,and the frame must be connected to the ground.                           | Checking With<br>Eyes<br>And Using<br>Vernier<br>Caliper,<br>Multimeter | 100%             |

| LCD                                         | The major defects would be reject.no scratch and no dusty on the LCD glass surface.d $\leq$ 0.15mm n $\leq$ 2 diameter of bubble:d $\leq$ 0.5 n $\leq$ 2 damaged size of polarizer:d $\leq$ 0.15mm, n $\leq$ 2. | Check It When Displaying                                                | 100%             |

| The Relative Position of LCD and Frame      | The sealant mouth of the LCD must be at the same side with the frame's.                                                                                                                                         | Checking With<br>Eyes                                                   | 100%             |

| The Relative Position of PCB Paneland Frame | The frame installing direction must be correct.the twisted angle of the pin is from 45° to 60°, the pin is vertical to PCB panel and it must be in the middle position of the installing holes.                 | Checking With<br>Eyes                                                   | 100%             |

| Function<br>Test                            | <ol> <li>The major defects must be reject.</li> <li>Test flow chart (see attached chart)</li> <li>Background changes evenly and no disorderly displaying phenomenon.</li> <li>Display no shortage.</li> </ol>   | Check It When Displaying                                                | 100%             |

Note:D~Diameter N~Quantity Unit:mm

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 18 of 26              |

# V. Instruction System and Description of Details 1.Instruction System

Only two SPLC780A OR KS0066 registers, the Instruction Register (IR) and the Data Register (DR) can be directly controlled by the MPU. Prior to internal operation start, control information is temporarily stored in these registers, to allow interface form SPLC780A OR KS0066 internal operation to various types of MPUs which operate in different speeds or to allow interface to peripheral control ICS. SPLC780A OR KS0066 internal operation is determined by signals sent from the MPU. These signals include register selection signal(RS), read/write signals (R/W) and data bus signals (DB0—DB7), and are called instructions, here. Table 1 shows the instructions and their execution time. Details are explained in subsequent sections.

Instructions are of 4 types, those that,

- (1) Designate SPLC780A OR KS0066 functions such as display format, data length, etc.

- (2) Give internal RAM addresses.

- (3) Perform data transfer with internal RAM.

- (4) Others.

In normal use, category (3) instructions are used most frequently. However, automatic incrementing by +1 (or decrementing by -1) of SPLC780A OR KS0066 internal RAM addresses after each data write lessens the MPU program load. The display shift is especially able to perform concurrently with display data write, enabling the user to develop systems in minimum time with maximum programming efficiency. For an explanation of the shift function in its relation to display, . When an instruction is executing during internal operation, no instruction other than the busy flag/address read instruction will be executed.

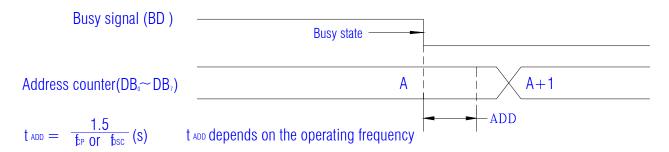

Because the busy flag is set to "1" while an instruction is being executed, check to make sure it is on "1" before sending an instruction from the MPU.

#### Note 1

Make sure the SPLC780A OR KS0066 is not in the busy state (BF=0) before sending the instruction from the MPU to the SPLC780A OR KS0066. If the instruction is sent without checking the busy flag the time between first and next instructions is much longer than the instruction time.

See Table 1 for a list of each instruction execution time.

#### Note 2

After executing instruction of writing data to CG/DD RAM or reading data from CG/DD RAM,RAM address counter is automatically incremented by 1 (or decremented

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 19 of 26              |

by 1). In this case, this shift is executed after Busy flag is set to "Low". Tadd is stipulated the time from the fall edge of busy flag to the end of address counter's renewal.

| Та                           | Table 1 Instructions                                         |         |                                                        |                              |                       |                                                      |                 |     |     |     |                                                                                                                                                                                           |                                             |                                             |

|------------------------------|--------------------------------------------------------------|---------|--------------------------------------------------------|------------------------------|-----------------------|------------------------------------------------------|-----------------|-----|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------|

| Instruction                  | RS                                                           | R/W     | DB7                                                    | DB6                          | Coc<br>DB5            | DB4                                                  | DB3             | DB2 | DB1 | DB0 | Description                                                                                                                                                                               | Execution time<br>(when Fose is<br>250 KHz) | Execution time<br>(when Fose is<br>160 KHz) |

| Clear<br>display             | 0                                                            | 0       | 0                                                      | 0                            | 0                     | 0                                                    | 0               | 0   | 0   | 1   | Clears all display and returns theCursor to home position (Address 0).                                                                                                                    | Note 1 82us~1.64ms                          | Note 2<br>120us~4.9ms                       |

| Return home                  | 0                                                            | 0       | 0                                                      | 0                            | 0                     | 0                                                    | 0               | 0   | 1   | *   | Returns the cursor to the home position (Address 0).Also returns the display being shifted to the original position. DDRAM contents remain unchanged.                                     | 40us~1.6ms                                  | 120us~4.8ms                                 |

| Entry mode set               | 0                                                            | 0       | 0                                                      | 0                            | 0                     | 0                                                    | 0               | 1   | I/D | S   | Sets the cursor move direction<br>and specifies or not to shift the<br>display. These operations are<br>performed during data write<br>and read                                           | 40us                                        | 120us                                       |

| Display ON/OFF control       | 0                                                            | 0       | 0                                                      | 0                            | 0                     | 0                                                    | 1               | ۵   | U   | В   | Sets ON/OFF of all display (D),<br>cursor ON/OFF (C), and blink of<br>cursor position character (B).                                                                                      | 40us                                        | 120us                                       |

| Cursor and display shift     | 0                                                            | 0       | 0                                                      | 0                            | 0                     | 1                                                    | S/C             | R/L | *   | *   | Moves the cursor and shites the display without changing DD RAM contents.                                                                                                                 | 40us                                        | 120us                                       |

| Function set                 | 0                                                            | 0       | 0                                                      | 0                            | 1                     | DL                                                   | N               | F   | *   | *   | Sets interface data length (DL)<br>number of display lines (L) and<br>character font (F).                                                                                                 | 40us                                        | 120us                                       |

| Set CG RAM address           | 0                                                            | 0       | 0                                                      | 1                            |                       |                                                      | A               | CG  |     |     | Sets the CG RAM address.CG<br>RAM data is sent and received<br>After this setting.                                                                                                        | 40us                                        | 120us                                       |

| Set DD RAM address           | 0                                                            | 0       | 1                                                      |                              |                       |                                                      | A <sub>DD</sub> |     |     |     | Sets the DD address. DD RAM data is sent and received After this setting .                                                                                                                | 40us                                        | 120us                                       |

| Read busy flag<br>& address  | 0                                                            | 1       | BF                                                     |                              |                       |                                                      | AC              |     |     |     | Reads Busy flag (BF) indicating internal operation is being performed and reads address counter contents.                                                                                 | 1us                                         | 1us                                         |

| Write data to CG o           | 1                                                            | 0       |                                                        |                              | \                     | Vrite                                                | Dat             | a   |     |     | Writes data into DD RAM or CG RAM.                                                                                                                                                        | 40us                                        | 120us                                       |

| Read data to CG<br>or DD RAM | 1                                                            | 1       |                                                        | 7                            | F                     | Read                                                 | Dat             | a   |     |     | Reads data from DD RAM or CG RAM                                                                                                                                                          | 40us                                        | 120us                                       |

|                              | S =1<br>S/C=<br>R/L=<br>R/L=<br>DL =<br>N =1<br>F =1<br>BF = | : Accor | mpanies blay shi t to righ t to left s s dots rnally o | s displa ft S/C= it  peratin | DL =0<br>N =0: 5<br>g | rement<br>or move<br>: 4 bits<br>1 lines<br>5x7 dots | e               |     |     |     | DD RAM: Display data RAM CG RAM: Character generator RAM ACG: CG RAM address ADD: DD RAM address Corresponds to cursor address AC: Address counter used For both of DD and CG RAM address |                                             | r changes.<br>mple)<br>is 270k Hz:          |

<sup>\*</sup> No effect

Notes 1: Applied to models driven by 1/8 duty or 1/11 duty.

2: Applied to models driven by 1/16 duty.

#### 2. Description of details

(1) Clear display

|      | RS | R/W | DB7 · |   |   |   |   |   |   | DB0 |

|------|----|-----|-------|---|---|---|---|---|---|-----|

| Code | 0  | 0   | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 1   |

|      |    |     |       |   |   |   |   |   |   |     |

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 20 of 26              |

Writes space code "20" (hexadecimal) (character pattern for character code "20" must be blank pattern) into all DD RAM address.Set DD RAM address 0 in address counter.Returns display to its original status if it was shifted. In other words.the display disappears and the cursor or blink go to the left edge of the display (the first if 2 lines are displayer).Set I/D= 1 (Increment Mode) of Entry Mode.S of Entry Mode doesn't change.

(2) Return home

|      | RS | R/W | DB7 |   |   |   |   |   |   | DB0 |

|------|----|-----|-----|---|---|---|---|---|---|-----|

| Code | 0  | 0   | 0   | 0 | 0 | 0 | 0 | 0 | 1 | *   |

\*No effect

Sets the DD RAM address 0 in address counter. Returns display to its original status if it was shifted. DD RAM contents do not change. The cursor or blink go to the left edge of the display (the first line if 2 lines are displayed).

(3) Entry mode set

|      | RS | R/W | DB7 |   | <del></del> |   |   |   |     | DB0 |

|------|----|-----|-----|---|-------------|---|---|---|-----|-----|

| Code | 0  | 0   | 0   | 0 | 0           | 0 | 0 | 1 | I/D | S   |

- I/D: Increments (I/D = 1) or decrement s (I/D) the DD RAM address by 1 when a character code is written into or read from the DD RAM .The cursor blink moves to the right when incremented by 1 and to the left when decremented by 1. The same applies to writing and reading of CG RAM.

- **S**: Shifts the entire display either to the right or to the left when **S** is 1; to the left when I/D = 1 and to the right when I/D = 0. Thus it looks as if the cursor stands still and the display moves. The display does not shift when reading from the DD RAM when writing into or reading out from the CG RAM does it shift when S = 0.

- (4) Display ON/OFF control

|      | RS | R/W | DB7 - |   |   |   |   |   |   | DB0 |   |

|------|----|-----|-------|---|---|---|---|---|---|-----|---|

| Code | 0  | 0   | 0     | 0 | 0 | 0 | 1 | D | С | В   | 7 |

- **D:** The display is ON when D = 1 and OFF when D = 0, when off due to D = 0, display Data remains in the DD RAM.It can be displayed immediately by setting D = 1.

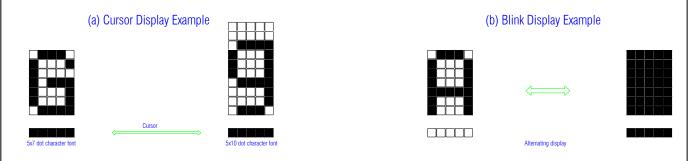

- **C:** The cursor displays when C = 1 and does not display when C = 0. Even if the Cursor disappears,the function of I/D,etc.does not change during display data write.

The cursor is displayed using 5 dots in the 8th line when the 5x7 dot character font Is selected and 5 dots in the 11th line when the 5x10 dot character font is selected.

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 21 of 26              |

**B:** The character indicated by the cursor blink when B = 1.The blink is displayed by Switching between all blank dots and display characters at 409.6 ms interval when fcp or fosc =250Khz. The cursor and the blink can be set to display simultaneously. (The blink frequency changes according to the reciprocal of fcp or fose. 409.6x250/270 = 379.2ms when fcp = 270kHz).

(5) Cursor or display shift

|      | RS | R/W | DB7 |   |   |     | <br>-44 |     |   | DB0 |

|------|----|-----|-----|---|---|-----|---------|-----|---|-----|

| Code | 0  | 0   | 0   | 0 | 0 | . 1 | S/c     | R/I | * | *   |

\*No effect

Shifts Cursor position or display to the right or left without writing or reading display data. This function is used to correct or search for the display .In a 2-lines display, the cursor moves to the 2nd line when its passes the 40th digit of the 1st line. Notice that the 1st and 2nd line display will shift at the same time. When the displayed data is shifted repeatedly each line only moves horizontally. The 2nd line display does not shift into the 1st line position

#### S/C R/L

- 0 Shifts the cursor position to the left.(AC is decremented by one.)

- O 1 Shifts the cursor position to the right. (AC is decremented by one.)

- 1 0 Shifts the entire display to the left. The cursor follows the display shift.

- 2 1 Shifts the entire display to the right. The cursor follows the display shift.

Address counter (AC) contents do not change if the only action performed is shift

#### (6) Function set

|      | RS | R/W | DB7 |   |   |    |   |   |   | DB0 |

|------|----|-----|-----|---|---|----|---|---|---|-----|

| Code | 0  | 0   | 0   | 0 | 1 | DL | N | F | * | *   |

\*No effect

**DL:** Sets interface data length. Data is sent or received in 8 bit lengths (DB7~DB0) when DL = 1 and in 4 bit lengths (DB7~DB4) when DL = 0. when the 4 bit length is selected Data must be sent or received twice.

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 22 of 26              |

N: Sets number of display lines Sets character font. (Note) Perform the function at the head of the program before executing all instruction (expect "Busy flag/address read"). From this point, the function set instruction cannot be executed unless the interface data length is changed. N F No.of display lines Character font **Duty factor** Remarks 5x7 dots 0 1/8 0 1 5x10 dots 1/11 1 Cannot display 2 lines with 5x10 1 2 5x7 dots 1/16 dot character font. \*No effect (7) Set CG RAM address R/W RS DB7 -----DB0 Code 0 0 A 0 ← Higher Order Bits Lower Order Bits→ Sets the CG RAM address into the address counter in binary AAAAAA.Data is then Written or read from the MPU for the CG RAM (8) Set DD RAM address RS R/W DB7 -----DB0 Code Α Α Α Α Α Α ←Higher Order Bits Lower Order Bits→ Sets the DD RAM address into the address counter in binary AAAAAAA.Data is then Written or read from the MPU for the DD RAM. When N = 0 (1-line display), AAAAAAA is "00" ~ "4F" (hexadecimal). When N = 1 (2-line display), AAAAAAA is "00" ~ "27" (hexadecimal) for the first line, and "40" ~ "67" (hexadecimal) for the second line. (9) Read busy flag & address RS R/W DB7 --DB0 Code BF Α Α Α ← Higher Order Bits Lower Order Bits→ Reads the busy flag (BF) that indicates the system is now internally operating by a previously received instruction.BF=1 indicates that internal operation is in progress. The next instruction will not be accepted until BF is set to "0".check the BF status before the next write operation. At the same time, the value of the address counter expressed in binary AAAAAAA is read out. The address counter is used by both CG and DD RAM address, and its value is determined by the previous instruction. TECHNICAL DATE: 2003/2/12 SPECIFICATION

**LCM**

HY-1602H-201

Page 23 of 26

Address contents are the same as in terms (7) and (8).

#### (10) Write data to CG or DD RAM

|      | RS | R/W | DB7 |   |   |   |   |   |   | DB0 |

|------|----|-----|-----|---|---|---|---|---|---|-----|

| Code | 1  | 0   | D   | D | D | D | D | D | D | D   |

←Higher Order Bits

Lower Order Bits→

Writes binary 8 bit data DDDDDDDD to the CG or the DD RAM.Whether the CG or DD RAM is to be written into is determined by the previous specification of CG RAM or DD RAM address setting .After write ,the address is automatically incremented or decremented by 1 according to entry mode.The entry mode also determines display shift.

#### (11) Read data from CG or DD RAM

|      | RS  | R/M      | DR7  |   |   | 900 | - 10 |        | # B  |   |   | DB0 |

|------|-----|----------|------|---|---|-----|------|--------|------|---|---|-----|

|      | INO | 1 X/ V V | וטטו |   | 4 | 4   |      |        | 8.JP |   |   | 000 |

| Code | 1   | 1        | D    | D | D |     | D    | 200000 | W D  | D | D | D   |

← Higher Order Bits

Lower Order Bits→

Reads binary 8 bits data DDDDDDDD from the CG or DD RAM. The previous designation determines whether the CG or DD RAM is to be read. Before entering the read instruction, you must execute either the CG RAM or DD RAM address set instruction. If you don't, the first read data will be invalidated. When serially executing the "read" instruction, the next address data is normally read from the second read. The "address set" instruction need not be executed just before the "read" instruction when shifting the cursor by cursor shift instruction (when reading out DD RAM). The cursor shift instruction operation is the same as that of the DD RAM 's address set instruction.

After a read, the entry mode automatically increases or decreases the address by 1. However, display shift is not executed no matter what the entry mode is. (Note) The address counter (AC) is automatically incremented or decremented by 1 after "write" instructions to either CG RAM or DD RAM. RAM data selected by the AC cannot than be read out even if "read" instructions are executed. The conditions for correct data read out are: execute either the address set instruction or cursor shift instruction (only with DD RAM), just before reading out execute the "read" instruction from the second time the "read" instruction is serial.

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 24 of 26              |

#### 3 Precaution on programming

#### (1) Instruction of function set

Perform the function at the head of program that accesses SPLC780A OR KS0066 before executing all instructions, and not change the data of the instruction Register in the program. The data of function register can be changed by the program as follow;

- a. Changing of DL (Data Length)

- when DL is changed from 8-bit length mode.

- when DL is changed from 4-bit length mode.

- b. Changing of N (Column Number)

- Perform the instruction of function set after executing instruction of display clear or display off.

In this case, sequence of AC and DD RAM must be changed. Thus, rewrite the address set register after that.

- c. Changing of F (Font)

- There is no problem in this case, but for dual-line display, the font mode of 5x11 cannot be selected (this mode is forbidden by hardware).

When N of F is changed, power supply voltage for LCD must be changed. If not Changed, crosstalk will appear, or contrast will be poor.

### (2) Busy flag check

SPLC780A OR KS0066 is produced in the CMOS process, therefore internal executing time is long.

Standard time is 40us~1.6ms. (This varies by instruction).

When the high speed MPU controls it, check the busy flag before performing Instruction or reading data.

While internal operation is active, Enable signal is not accepted. (Enable signal at Reading status register for checking busy flag is accepted) Busy flag signal is output through DB7, as shown in Table 3, when RS = "0",R/W = "1",and Enable="1"

#### (3) Iuput of unidentified instruction code

Undefined instruction code of SPLC780A OR KS0066 is only as follows;

RS R/W DB7~DB 0 0 0~

(Others are included to defined instruction)

When the undefined instruction code is loaded to SPLC780A OR KS0066, it accepts

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 25 of 26              |

the code, but Does not change the internal states (RAM and other status of Flags). Busy state,

However continues for maximum 40us by the acceptance of the code.

Table 2 The relation between the operation and the combination of RS,R/W

| RS | R/W | Е | Operation                          |  |  |

|----|-----|---|------------------------------------|--|--|

| 0  | 0   |   | Write instruction code             |  |  |

| 0  | 1   |   | Read busy flag and address counter |  |  |

| 1  | 0   |   | Write data                         |  |  |

| 1  | 1   |   | Read data                          |  |  |

When performing data and instruction code by 4 bit, transfer RS, R/W every time.

| DATE: 2003/2/12 |              | TECHNICAL<br>SPECIFICATION |

|-----------------|--------------|----------------------------|

| LCM             | HY-1602H-201 | Page 26 of 26              |