# 8-Channel High Voltage Switch with Decoded Switch Selection

### **Ordering Information**

|                   |                 |                  | Package Options                   |                       |                    |  |  |  |  |  |

|-------------------|-----------------|------------------|-----------------------------------|-----------------------|--------------------|--|--|--|--|--|

| $\mathbf{V}_{PP}$ | V <sub>NN</sub> | V <sub>SIG</sub> | 20-pin ceramic<br>side-brazed DIP | 20-pin Plastic<br>DIP | Die in waffle pack |  |  |  |  |  |

| +70V              | -70V            | 110V P-P         | HV1414C                           | HV1414P               | HV1414X            |  |  |  |  |  |

| +80V              | -80V            | 130V P-P         | HV1416C                           | HV1416P               | HV1416X            |  |  |  |  |  |

#### **Features**

- ☐ HVCMOS® Technology

- ☐ Up to 130V peak to peak switching capability

- ☐ Output On-resistance typically 40 ohms

- □ Low parasitic capacitances

- ☐ DC to 10MHz analog signal frequency

- ☐ 45 dB typical output off isolation at 5 MHz

- CMOS logic circuitry for low power and excellent noise immunity

- On-chip decode, latch and chip select logic circuitry

# **Absolute Maximum Ratings\***

| V <sub>DD</sub> Logic power supply voltage   | -0.5V to +18V                  |  |  |  |  |

|----------------------------------------------|--------------------------------|--|--|--|--|

| V <sub>PP</sub> Positive high voltage supply | -0.5V to +90                   |  |  |  |  |

| V <sub>NN</sub> Negative high voltage supply | +0.5V to -90V                  |  |  |  |  |

| Logic input voltages                         | -0.5V to V <sub>DD</sub> +0.3V |  |  |  |  |

| Peak analog signal current/channel           | 1.5A                           |  |  |  |  |

| Storage temperature                          | -65°C to +150°C                |  |  |  |  |

| Power dissipation                            | 800mW                          |  |  |  |  |

<sup>\*</sup> Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability.

### **General Description**

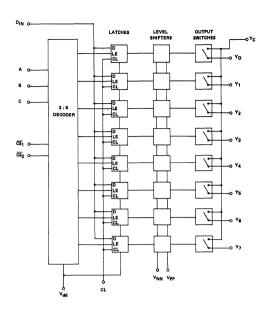

This device is an 8-channel high-voltage integrated circuit (HVIC), configured as a 1 of 8 decode function, intended for use in applications requiring high voltage switching controlled by low voltage signals; e.g., ultrasound imaging and printers. On-chip latches are provided for the decoded data.

The unique control logic on this device provides individual control of each switch, allowing more than one switch to be turned on at a time. The clear function turns off all switches simultaneously. The chip select inputs control the latches, holding the output stable while the address and data are changed. Using HVCMOS technology, this HVIC combines high voltage bi-lateral DMOS switches and low power CMOS logic to provide efficient control of high voltage analog signals.

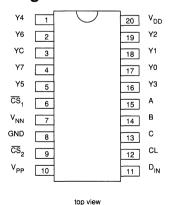

# **Pin Configuration**

20-pin DIP

# Electrical Characteristics (over recommended operating conditions unless noted)

#### **DC Characteristics**

| Characteristics         | Sym 0°C          |     |      | +25°C +70°C |       |      |     |      | Units    | Test Conditions                            |  |

|-------------------------|------------------|-----|------|-------------|-------|------|-----|------|----------|--------------------------------------------|--|

| Characteristics         | Sylli            | min | max  | min         | typ   | max  | min | max  | Units    | Test Conditions                            |  |

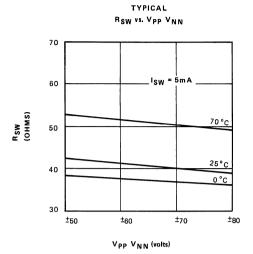

| Switch (ON) Resistance  | $R_{sw}$         |     | 50   |             | 40    | 50   |     | 60   | ohms     | I <sub>sw</sub> = 5mA                      |  |

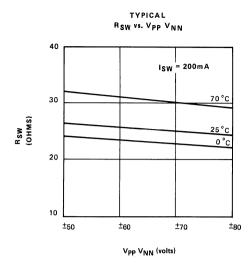

| Switch (ON) Resistance  | R <sub>sw</sub>  |     | 35   |             | 25    | 35   |     | 45   | ohms     | I <sub>SW</sub> = 200mA                    |  |

| Switch (ON) Resistance  | R <sub>sw</sub>  |     | 55   |             | 45    | 55   |     | 65   | ohms     | V <sub>PP</sub> = +50V                     |  |

|                         |                  |     |      |             |       |      |     |      |          | V <sub>NN</sub> = -50V                     |  |

|                         |                  |     |      |             |       |      |     |      |          | I <sub>SW</sub> = 5mA                      |  |

| Switch (ON) Resistance  | $R_{sw}$         |     | 40   |             | 25    | 40   |     | 50   | ohms     | PP                                         |  |

|                         |                  |     |      |             |       |      |     |      |          | V <sub>NN</sub> = -50V                     |  |

|                         |                  |     |      |             |       |      |     |      |          | I <sub>sw</sub> = 200mA                    |  |

| Switch (ON) Resistance  | $R_{sw}$         |     | 30   |             | 10    | 30   | ].  | 30   | %        | I <sub>sw</sub> = 5mA                      |  |

| Matching                |                  |     |      |             |       |      |     |      | <u> </u> | $V_{PP} = +50V, V_{NN} = -50V$             |  |

| Switch Off Leakage      | $I_{SWL}$        |     | 50   |             | 0.5   | 50   |     | 150  | μA       | $V_{OUT} = V_{PP} - 10V \text{ thru } 10K$ |  |

|                         |                  |     |      |             |       |      |     |      |          | with 8 SWS in parallel                     |  |

| DC Offset Switch Off    |                  |     | 500  |             | 100   | 500  |     | 500  | mV       | RL = 100K                                  |  |

| DC Offset Switch On     |                  |     | 500  |             | 100   | 500  |     | 500  | mV       | RL = 100K                                  |  |

| Pole to Pole            | C <sub>sw</sub>  |     | 10   |             | 4.5   | 10   |     | 10   | pF       | DC Bias = 40V                              |  |

| Switch Capacitance      |                  |     |      |             |       |      |     |      |          | f = 1MHz                                   |  |

| Logic Input Capacitance | CIN              |     |      |             | 3.5   |      |     |      | pF       |                                            |  |

| Pos. HV Supply Current  | I <sub>PPQ</sub> |     | 200  |             | 50    | 200  |     | 200  | μA       | ALL SWS OFF                                |  |

| Neg. HV Supply Current  | I <sub>NNQ</sub> |     | -200 |             | -50   | -200 |     | -200 | μA       |                                            |  |

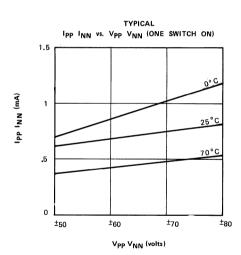

| Pos. HV Supply Current  | l <sub>PP</sub>  |     |      |             | 0.8   | 1.6  |     |      | mA       | 1 SW ON                                    |  |

| Neg. HV Supply Current  | I <sub>NN</sub>  |     |      |             | -0.8  | -1.6 |     |      | mA       | I <sub>sw</sub> = 5mA                      |  |

| Pos. HV Supply Current  | I <sub>PP</sub>  |     |      |             | 0.6   | 1.2  |     |      | mA       | V <sub>PP</sub> = +50V                     |  |

| Neg. HV Supply Current  | I <sub>NN</sub>  |     |      |             | -0.6  | -1.2 | 1   |      | mA       | V <sub>NN</sub> = -50V                     |  |

|                         |                  |     |      |             |       |      |     |      |          | 1 SW ON, I <sub>SW</sub> = 5mA             |  |

| Switch Output           | 7                |     |      |             | 1.5   |      |     |      | Α        |                                            |  |

| Peak Current            |                  |     |      |             |       |      |     |      | ļ        |                                            |  |

| Logic Supply Current    | l <sub>oo</sub>  |     |      |             | 0.001 | 0.5  |     |      | mA       |                                            |  |

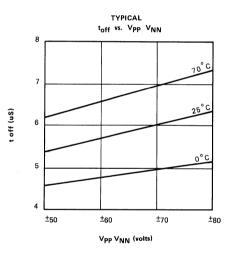

# **AC Characteristics**

| Characteristics                                | C                | 0   | °C  | +25°C |     |     | +70°C |     | Units | Test Conditions |  |

|------------------------------------------------|------------------|-----|-----|-------|-----|-----|-------|-----|-------|-----------------|--|

| Characteristics                                | Sym              | min | max | min   | typ | max | min   | max | Units | lest Conditions |  |

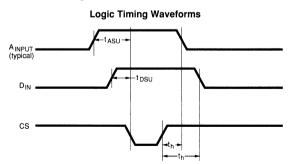

| D <sub>IN</sub> Set Up Time<br>Before CS Rises | t <sub>DSU</sub> |     |     | 260   |     |     |       |     | ns    |                 |  |

| Address Set Up Time<br>Before CS Falls         | t <sub>ASU</sub> |     |     | 120   |     |     |       |     | ns    |                 |  |

| Hold Time After CS Rises                       | t <sub>h</sub>   |     |     | 35    |     |     |       |     | ns    |                 |  |

| Minimum Clear Pulse Width                      | twcL             |     |     | 150   |     |     |       |     | ns    |                 |  |

| Minimum Chip Select<br>Low Pulse Width         | t <sub>wcs</sub> |     |     | 300   |     |     |       |     | ns    |                 |  |

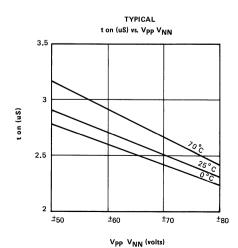

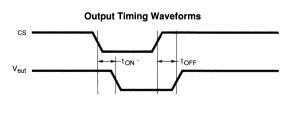

| Turn On Time                                   | t <sub>on</sub>  |     | 5   |       | 2.5 | 5   |       | 5   | μs    |                 |  |

| Turn Off Time                                  | t <sub>OFF</sub> |     | 10  |       | 5.0 | 10  |       | 10  | μs    |                 |  |

| Off Isolation                                  | КО               |     |     | 35    | 45  |     |       |     | dB    | f = 5MHz        |  |

#### 11

# **Recommended Operating Conditions**

| Cumbal           | Dovemeter                          | Dev    | vice   | Value                                        |  |  |

|------------------|------------------------------------|--------|--------|----------------------------------------------|--|--|

| Symbol           | Parameter                          | HV1414 | HV1416 | Value                                        |  |  |

| V <sub>DD</sub>  | Logic power supply voltage         | X      | Х      | +10.0V to +15.5V                             |  |  |

| V <sub>PP</sub>  | Positive high voltage supply       | X      |        | +50.0V to +70.0V                             |  |  |

|                  |                                    |        | Х      | +50.0V to +80.0V                             |  |  |

| V <sub>NN</sub>  | Negative high voltage supply       | Х      |        | -50.0V to -70.0V                             |  |  |

|                  |                                    |        | Х      | -50.0V to -80.0V                             |  |  |

| V <sub>IH</sub>  | High level input voltage           | X      | Х      | V <sub>DD</sub> -2V to V <sub>DD</sub>       |  |  |

| V <sub>IL</sub>  | Low-level input voltage            | X      | Х      | 0 to 2.0V                                    |  |  |

| V <sub>SIG</sub> | Analog signal voltage peak to peak | X      | X      | V <sub>NN</sub> +15V to V <sub>PP</sub> -15V |  |  |

| T <sub>A</sub>   | Operating free air-temperature     | Х      | Х      | 0° to 70°C                                   |  |  |

|                  |                                    | 1      |        |                                              |  |  |

Note: For non-ground referenced systems the following must be used:

Power up sequence: GND VNN VDD VPP Power down sequence: VPP VDD VNN GND

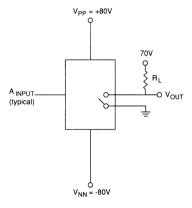

# $T_{ON}/T_{OFF}$ Measurement Circuit

# **Switching Waveforms**

# **Logic Diagram**

### **Truth Table**

| С | В | A | ĈS₁ | ĊS₂ | DIN | CL | Υ0                   | Y1  | Y2  | <b>Y3</b> | Y4  | <b>Y</b> 5 | Y6  | <b>Y7</b> |

|---|---|---|-----|-----|-----|----|----------------------|-----|-----|-----------|-----|------------|-----|-----------|

| L | L | L | L   | L   | L   | L  | OFF                  |     |     |           |     |            |     |           |

| L | L | L | L   | L   | Н   | L  | ON                   |     |     |           |     |            |     |           |

| L | L | Н | L   | L   | L   | L  |                      | OFF |     |           |     |            |     |           |

| L | L | Н | L   | L   | Н   | L  |                      | ON  |     |           |     |            |     |           |

| L | Н | L | L   | L   | L   | L  |                      |     | OFF |           |     |            |     |           |

| L | Н | L | L   | L   | Н   | L  |                      |     | ON  |           |     |            |     |           |

| L | Н | Н | L   | , L | L   | L  |                      |     |     | OFF       |     |            |     |           |

| L | Н | Н | L   | L   | Н   | L  |                      |     |     | ON        |     |            |     |           |

| Н | L | L | L   | L   | L   | L  |                      |     |     |           | OFF |            |     |           |

| Н | L | L | L   | L   | Н   | L  |                      |     |     |           | ON  |            |     |           |

| Н | L | Н | L   | L   | L   | L  |                      |     |     |           |     | OFF        |     |           |

| Н | L | Н | L   | L   | Н   | L  |                      |     |     |           |     | ON         |     |           |

| Н | Н | L | L   | L   | L   | L  |                      |     |     |           |     |            | OFF |           |

| Н | Н | L | L   | L   | Н   | L  |                      |     |     |           |     |            | ON  |           |

| Н | Н | Н | L   | L   | L   | L  |                      |     |     |           |     |            |     | OFF       |

| Н | Н | Н | L   | L   | Н   | L  |                      |     |     |           |     |            |     | ON        |

| Х | Х | Х | Н   | X'  | х   | L  | HOLDS PREVIOUS STATE |     |     |           |     |            |     |           |

| Х | Х | Х | х   | Н   | Х   | L  | HOLDS PREVIOUS STATE |     |     |           |     |            |     |           |

| Х | Х | Х | Х   | Х   | Х   | Н  | ALL OUTPUTS OFF      |     |     |           |     |            |     |           |

Notes: 1.  $D_{IN}$  controls the switches through flow-through latches, which are clocked (enabled) by an 8-way decoder controlled by A, B, C,  $\overline{\text{CS}}_1$ , and  $\overline{\text{CS}}_2$ . Therefore, the latch for a particular switch goes into the HOLD state when any of the above inputs prevents selection.  $\overline{CS}_1$  or  $\overline{CS}_2$  can be used as an active LOW clock input.

- 2. Spurious clocking may occur if A, B, or C is changed with  $\overline{\text{CS}}_1$  and  $\overline{\text{CS}}_2$  both low.

3. The clear input CL overrides all other

- inputs.

- 4. The eight switches operate independently.

# 11

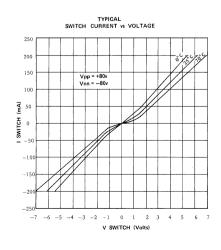

# **Typical Performance Curves**