# HT49RA0-6 Remote Type 8-Bit MCU with LCD

### Features

- Operating voltage:

- f<sub>SYS</sub> = 4MHz at V<sub>DD</sub> = 2.0V~3.6V (LVR enabled)

Oscillator types:

- External High Frequency crystal -- HXT

- Internal High Frequency RC -- HIRC

- External 32768Hz crystal -- LXT

- Internal 32kHz RC -- LIRC

- Fully integrated internal 4095kHz oscillator requires no external components

- Program Memory: 2K×16

- Data Memory: 96×8

- 4 subroutine nesting levels

- Up to 23 bidirectional I/O lines

- Two external interrupt lines shared with I/O pins

- One 8-bit programmable timer/event counter

- Real Time Clock -- RTC

- 8-bit prescaler for RTC

- One programmable carrier output -- using 9-bit timer

# **General Description**

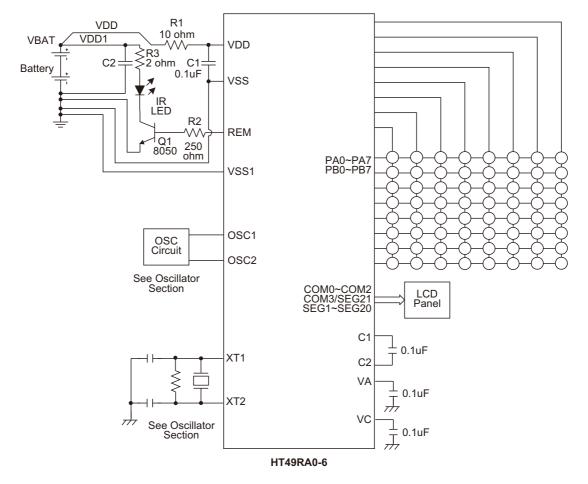

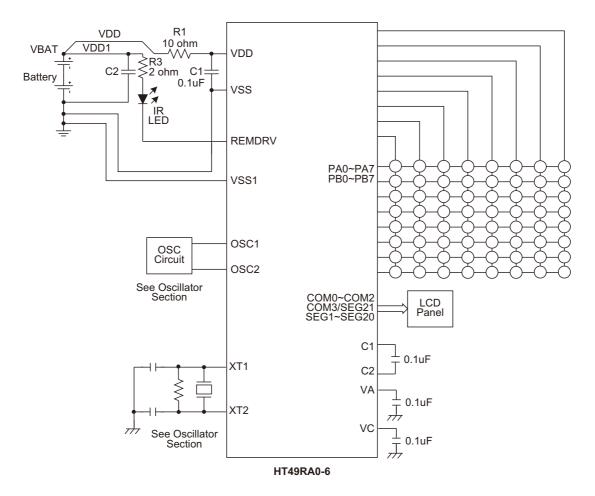

The HT49RA0-6 is 8-bit high performance, RISC architecture microcontroller devices specifically designed for multiple I/O control product applications. The advantages of low power consumption, I/O flexibility, timer functions, oscillator options, watchdog timer, power-down and wake-up functions, as well as

- Independent Carrier output pin (REM/REMDRV)

- Integrated IR driver (560mA at 3.0V)

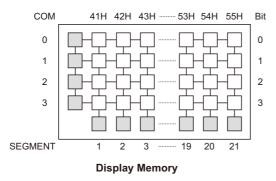

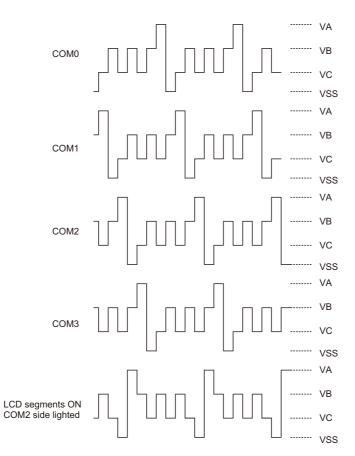

- LCD driver with 21×2, 21×3 or 20×4 segments

- LCD display duty and bias

- Duty: 1/2, 1/3 or 1/4

- Bias: 1/2 or 1/3

- Software enable control for LCD and RTC function

- Watchdog Timer

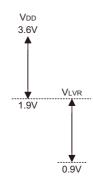

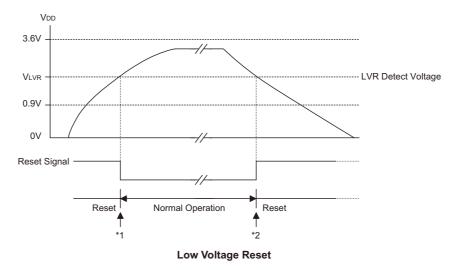

- Low Voltage Reset/Detect function

- Power-down and wake-up features reduce power consumption

- 16-bit table read instruction

- Bit manipulation instruction

- 63 powerful instructions

- Up to  $1\mu s$  instruction cycle with 4MHz system clock

- All instructions in 1 or 2 machine cycles

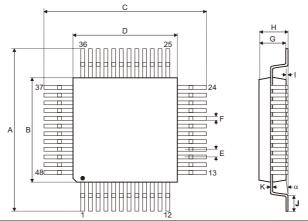

- 48-pin LQFP package

low cost, enhance the versatility of this device to suit a wide range of application possibilities such as industrial control, consumer products, and particularly suitable for use in products such as infrared LCD remote controllers and various subsystem controllers.

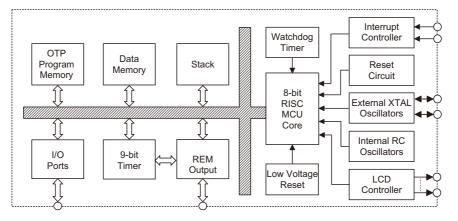

# **Block Diagram**

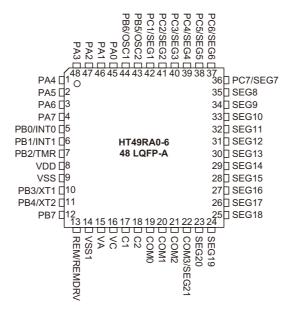

# **Pin Assignment**

# **Pin Description**

| Pin Name       | Function | ΟΡΤ   | I/T | O/T  | Description                                                                              |

|----------------|----------|-------|-----|------|------------------------------------------------------------------------------------------|

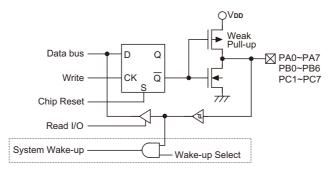

| PA0~PA7        | PAn      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

| PB0/INT0       | PB0      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | INT0     | со    | ST  | _    | External interrupt 0 input                                                               |

| PB1/INT1       | PB1      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | INT1     | со    | ST  | _    | External interrupt 1 input                                                               |

| PB2/TMR        | PB2      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | TMR      | TMRC  | ST  | _    | External Timer clock input                                                               |

| PB3/XT1        | PB3      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | XT1      | со    | LXT | _    | Oscillator pin                                                                           |

| PB4/XT2        | PB4      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | XT2      | со    |     | LXT  | Oscillator pin                                                                           |

| PB5/OSC2       | PB5      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | OSC2     | со    |     | HXT  | Oscillator pin                                                                           |

| PB6/OSC1       | PB6      | со    | ST  | NMOS | General purpose I/O with pull-up resistor. Configuration option enabled wake-up.         |

|                | OSC1     | со    | НХТ | _    | Oscillator pin                                                                           |

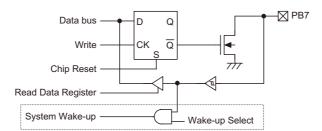

| PB7            | PB7      | со    | ST  | NMOS | General purpose I/O without pull-up resistor. Configura-<br>tion option enabled wake-up. |

| PC1/SEG1~      | PCn      |       | ST  | NMOS | General purpose I/O with pull-up resistor.                                               |

| PC7/SEG7       | SEGn     | SEGCR |     | CMOS | LCD segment output                                                                       |

| SEG8~SEG20     | SEGn     | LCDC  |     | CMOS | LCD segment output                                                                       |

| COM2/8E 021    | COM3     | со    |     | CMOS | LCD common output                                                                        |

| COM3/SEG21     | SEG21    | со    |     | CMOS | LCD segment output                                                                       |

| COM0~COM2      | COMn     | LCDC  |     | CMOS | LCD common output                                                                        |

| VA, VC, C1, C2 | Vn, Cn   | LCDC  |     | CMOS | LCD voltage pump                                                                         |

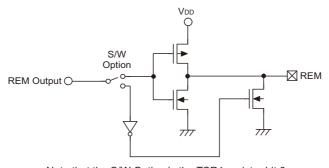

|                | REM      | TSR1  |     | CMOS | Carrier output                                                                           |

| REM/REMDRV     | REMDRV   | TSR1  |     | NMOS | High sink carrier output                                                                 |

| VDD            | VDD      | _     | PWR |      | Power supply                                                                             |

| VSS            | VSS      |       | PWR |      | Ground                                                                                   |

| VSS1           | VSS      |       | PWR |      | Ground, of REM/REMDRV                                                                    |

Note: I/T: Input type; O/T: Output type

OPT: Optional by configuration option (CO) or register option PWR: Power; CO: Configuration option; ST: Schmitt Trigger input CMOS: CMOS output; NMOS: NMOS output

HXT: High frequency crystal oscillator

LXT: Low frequency crystal oscillator

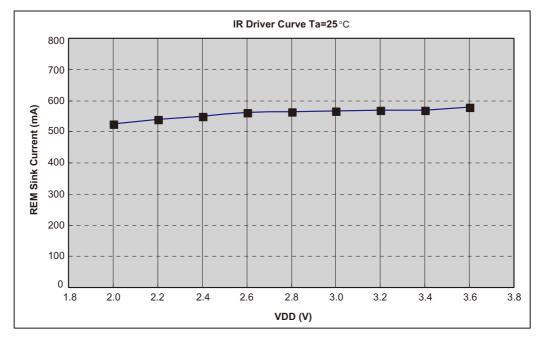

Ta=25°C

# **Absolute Maximum Ratings**

| Supply Voltage          | V <sub>SS</sub> –0.3V to V <sub>SS</sub> +4.0V | Storage Temperature   | –50°C to 125°C |

|-------------------------|------------------------------------------------|-----------------------|----------------|

| Input Voltage           | V <sub>SS</sub> –0.3V to V <sub>DD</sub> +0.3V | Operating Temperature | –20°C to 70°C  |

| I <sub>OL</sub> Total   | 150mA                                          | I <sub>OH</sub> Total | –100mA         |

| Total Power Dissipation | 500mW                                          |                       |                |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **D.C. Characteristics**

**Test Conditions** Symbol Min. Unit Parameter Тур. Max. Conditions VDD  $V_{DD}$ **Operating Voltage** LVR enable 2.0 3.6 V \_\_\_\_ \_\_\_\_ **Operating Current**  $I_{DD}$ 3V No load, f<sub>SYS</sub>=4MHz 0.7 1.5 mΑ (RC OSC) Standby Current No load, system HALT, 3V μA I<sub>STB1</sub> 0.1 1.0  $(*f_S=T1=f_{SYS})$ LCD off at HALT Standby Current No load, system HALT, μA I<sub>STB2</sub> 3V 2.5 5.0 \_\_\_\_ (\*f<sub>S</sub>=32.768kHz,QOSC=1) LCD On at HALT, C type Standby Current No load, system HALT 3V μA I<sub>STB3</sub> 2.0 5.0 (\*f<sub>S</sub>=WDT RC OSC) LCD On at HALT, C type Input Low Voltage for I/O Ports, V<sub>IL1</sub> 3V 0  $0.2V_{DD}$ V TMR, INT0 and INT1 Input High Voltage for I/O Ports, V<sub>IH1</sub> 3V  $0.8V_{DD}$  $V_{DD}$ V TMR, INT0 and INT1 PA0~PA7, PB0~PB6, PC1~PC7, 3V  $V_{OL}=0.1V_{DD}$ I<sub>OL1</sub> 6 12 mΑ **REM** sink current I<sub>OH1</sub> **REM Source Current** 3V  $V_{OH}$ =0.9 $V_{DD}$ -7 mΑ -5 LCD Common and Segment I<sub>OL2</sub> 3V V<sub>OL</sub>=0.1V<sub>DD</sub> 210 420 μΑ Current LCD Common and Segment 3V V<sub>OH</sub>=0.9V<sub>DD</sub> I<sub>OH2</sub> -80 -160 μΑ Current V<sub>OL</sub>=0.1V<sub>DD</sub> PB7 Sink Current I<sub>OL3</sub> 3V 0.8 1.2 mΑ I<sub>OL4</sub> **REMDRV Sink Current** 3V V<sub>OL</sub>=0.6V, Ta=25°C 500 560 mΑ  $\mathsf{R}_{\mathsf{PH}}$ Pull-high Resistance of I/O Ports 3V 100 150 200 kΩ **V**<sub>LVR</sub> Low Voltage Reset Voltage Ta=25°C 1.8 1.9 2.0 V \_\_\_\_  $V_{LVD}$ Low Voltage Detector Voltage Ta=25°C 2.0 2.1 2.2 V

Note: "\*" for the value of VA refer to the LCD driver section.

$"^*f_S"$  please refer to WDT clock option

Ta=25°C

# A.C. Characteristics

| C                   | Demonster                                                               |                            | Test Conditions                                                   |      | True  |      | Unit              |  |

|---------------------|-------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------|------|-------|------|-------------------|--|

| Symbol              | Parameter                                                               | V <sub>DD</sub> Conditions |                                                                   | Min. | Тур.  | Max. | Unit              |  |

| f <sub>SYS</sub>    | System Clock                                                            | 1.8V~<br>3.6V              | Ta= -20°C~70°C                                                    | 400  |       | 4000 | kHz               |  |

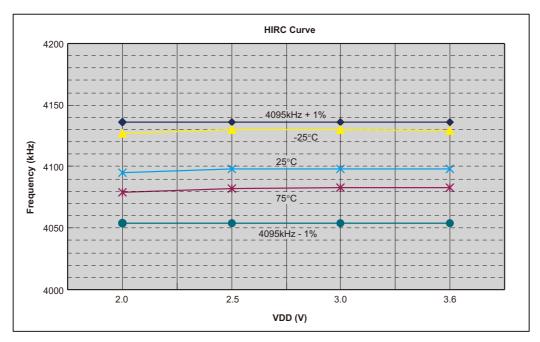

| f <sub>HIRC</sub>   | System Clock (HIRC)                                                     | 2.2V~<br>3.6V              | Ta= -10°C~50°C                                                    | -1%  | 4095  | +1%  | kHz               |  |

| $\mathbf{f}_{LXT}$  | LXT oscillator frequency                                                |                            | _                                                                 | —    | 32768 | _    | Hz                |  |

| f <sub>LIRC</sub>   | Cystem Clock (LIRC)                                                     | 3V                         | Ta=25°C                                                           | -10% | 32    | +10% | kHz               |  |

| f <sub>TIMER</sub>  | Timer I/P frequency (TMR)                                               | 3V                         |                                                                   | 0    | _     | 4000 | kHz               |  |

|                     |                                                                         |                            | Power-up or Wake-up<br>from HALT (HXT)                            | _    | 128   | _    | *t <sub>SYS</sub> |  |

| t <sub>SST</sub>    | System Start-up Timer Period                                            |                            | Power-up from HALT<br>(HIRC)                                      | _    | 128   | _    | *t <sub>SYS</sub> |  |

|                     |                                                                         |                            | Wake-up from HALT<br>(HIRC)                                       |      | 2     | _    | *t <sub>SYS</sub> |  |

| t <sub>INT</sub>    | Interrupt pulse width                                                   |                            |                                                                   | 1    |       | _    | μs                |  |

| t <sub>LVR</sub>    | Low voltage width to reset                                              |                            |                                                                   | 0.25 | 1.00  | 2.00 | ms                |  |

| f <sub>READYB</sub> | REMDRV output function stable<br>time; polling READYB register<br>bit=0 |                            | Wake-up from HALT or<br>change REMDRV<br>register bit from 1 to 0 |      | 250   |      | μs                |  |

Note: \*t<sub>SYS</sub>=1/f<sub>SYS</sub>

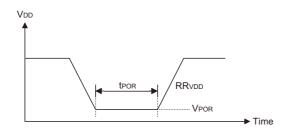

# **Power-on Reset Characteristics**

| Cumhal            | Demonster                                                                  | -               | Test Conditions | Min   | True | Mari | 11   |  |

|-------------------|----------------------------------------------------------------------------|-----------------|-----------------|-------|------|------|------|--|

| Symbol            | Parameter                                                                  | V <sub>DD</sub> | Conditions      | Min.  | Тур. | Max. | Unit |  |

| V <sub>POR</sub>  | VDD Start Voltage to Ensure<br>Power-on Reset                              |                 |                 | _     | _    | 100  | mV   |  |

| RR <sub>VDD</sub> | VDD raising rate to Ensure<br>Power-on Reset                               |                 |                 | 0.035 | _    | _    | V/ms |  |

| t <sub>POR</sub>  | Minimum Time for VDD Stays at<br>V <sub>POR</sub> to Ensure Power-on Reset |                 |                 | 1     |      |      | ms   |  |

# **Characteristics Curves**

HIRC Oscillator Voltage/Temperature vs. Frequency

IR Sink Current vs. VDD

## **Functional Description**

### **Execution Flow**

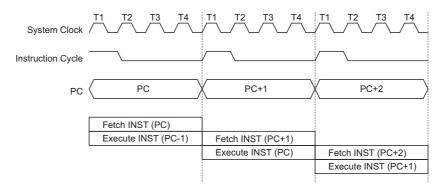

The main system clock is derived from either an external crystal oscillator which requires the connection of the external crystal or resonator or an internal RC oscillator which requires no external component for its operation. It is internally divided into four non-overlapping clocks. One instruction cycle consists of four system clock cycles.

Instruction fetching and execution are pipelined in such a way that a fetch takes one instruction cycle while decoding and execution takes the next instruction cycle. However, the pipelining scheme causes each instruction to effectively execute within one cycle. If an instruction changes the program counter, two cycles are required to complete the instruction.

#### **Program Counter – PC**

The program counter (PC) is 11 bits wide and controls

the sequence in which the instructions stored in the program ROM are executed. The contents of the PC can specify a maximum of 2048 addresses.

After accessing a program memory word to fetch an instruction code, the value of the PC is incremented by one. The PC then points to the memory word containing the next instruction code.

When executing a jump instruction, conditional skip execution, loading a PCL register, a subroutine call, an initial reset, an internal interrupt, an external interrupt, or returning from a subroutine, the PC manipulates the program transfer by loading the address corresponding to each instruction.

The conditional skip is activated by instructions. Once the condition is met, the next instruction, fetched during the current instruction execution, is discarded and a dummy cycle replaces it to get a proper instruction; otherwise proceed with the next instruction.

| Mode                         |                     | Program Counter |    |    |    |    |    |    |    |    |    |

|------------------------------|---------------------|-----------------|----|----|----|----|----|----|----|----|----|

| wode                         | *10                 | *9              | *8 | *7 | *6 | *5 | *4 | *3 | *2 | *1 | *0 |

| Initial Reset                | 0                   | 0               | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| External Interrupt 0         | 0                   | 0               | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| External Interrupt 1         | 0                   | 0               | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| Timer/Event Counter overflow | 0                   | 0               | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0  |

| Time Base Interrupt          | 0                   | 0               | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| RTC Interrupt                | 0                   | 0               | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  |

| Skip                         | Program Counter + 2 |                 |    |    |    |    |    |    |    |    |    |

| Loading PCL                  | *10                 | *9              | *8 | @7 | @6 | @5 | @4 | @3 | @2 | @1 | @0 |

| Jump, Call Branch            | #10                 | #9              | #8 | #7 | #6 | #5 | #4 | #3 | #2 | #1 | #0 |

| Return From Subroutine       | S10                 | S9              | S8 | S7 | S6 | S5 | S4 | S3 | S2 | S1 | S0 |

#### Execution Flow

#### **Program Counter**

Note: \*10~\*0: Program counter bits #10~#0: Instruction code bits S10~S0: Stack register bits @7~@0: PCL bits

The lower byte of the PC (PCL) is a readable and writeable register (06H). Moving data into the PCL performs a short jump. The destination is within 256 locations. When a control transfer takes place, an additional dummy cycle is required.

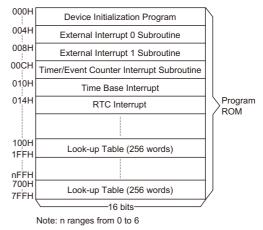

### **Program Memory – ROM**

The program memory (ROM) is used to store the program instructions which are to be executed. It also contains data, table, and interrupt entries, and is organized into  $2048 \times 16$  bits which are addressed by the program counter and table pointer.

Certain locations in the ROM are reserved for special usage:

Location 000H

Location 000H is reserved for program initialization. After chip reset, the program always begins execution at this location.

Location 004H

Location 004H is reserved for the external interrupt service program. If the INTO input pin is activated, and the interrupt is enabled, and the stack is not full, the program begins execution at location 004H.

Location 008H

Location 008H is reserved for the external interrupt service program also. If the INT1 input pin is activated, and the interrupt is enabled, and the stack is not full, the program begins execution at location 008H.

• Location 00CH

Location 00CH is reserved for the Timer/Event Counter interrupt service program. If a timer interrupt results from a Timer/Event Counter overflow, and if the interrupt is enabled and the stack is not full, the program begins execution at location 00CH.

Location 010H

Location 010H is reserved for the Time Base interrupt service program. If a Time Base interrupt occurs, and the interrupt is enabled, and the stack is not full, the program begins execution at location 010H.

Location 014H

Location 014H is reserved for the real time clock interrupt service program. If a real time clock interrupt occurs, and the interrupt is enabled, and the stack is not full, the program begins execution at location 014H.

Table location

Any location in the ROM can be used as a look-up table. The instructions TABRDC [m] (the current page, 1 page=256 words) and TABRDL [m] (the last page) transfer the contents of the lower-order byte to the specified data memory, and the contents of the higher-order byte to TBLH (Table Higher-order byte register) (08H). Only the destination of the lower-order byte in the table is well-defined; the other bits of the table word are all transferred to the lower portion of TBLH, and the remaining 2 bit is read as "0". The TBLH is read only, and the table pointer (TBLP) is a read/write register (07H), indicating the table location. Before accessing the table, the location should be placed in TBLP. All the table related instructions require 2 cycles to complete the operation. These areas may function as a normal ROM depending upon the user's requirements.

Program Memory

|                | Table Location |    |    |    |    |    |    |    |    |    |    |

|----------------|----------------|----|----|----|----|----|----|----|----|----|----|

| Instruction(s) | *10            | *9 | *8 | *7 | *6 | *5 | *4 | *3 | *2 | *1 | *0 |

| TABRDC [m]     | P10            | P9 | P8 | @7 | @6 | @5 | @4 | @3 | @2 | @1 | @0 |

| TABRDL [m]     | 1              | 1  | 1  | @7 | @6 | @5 | @4 | @3 | @2 | @1 | @0 |

**Table Location**

Note: \*10~\*0: Table location bits @7~@0: Table pointer bits P10~P8: Current program Counter bits

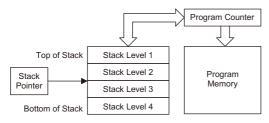

#### Stack Register – STACK

The stack register is a special part of the memory used to save the contents of the program counter. The stack is organized into 4 levels and is neither part of the data nor part of the program, and is neither readable nor writeable. Its activated level is indexed by a stack pointer (SP) and is neither readable nor writeable. At a commencement of a subroutine call or an interrupt acknowledgment, the contents of the program counter is pushed onto the stack. At the end of the subroutine or interrupt routine, signaled by a return instruction (RET or RETI), the contents of the program counter is restored to its previous value from the stack. After chip reset, the SP will point to the top of the stack.

If the stack is full and a non-masked interrupt takes place, the interrupt request flag is recorded but the acknowledgment is still inhibited. Once the SP is decremented (by RET or RETI), the interrupt is serviced. This feature prevents stack overflow, allowing the programmer to use the structure easily. Likewise, if the stack is full, and a "CALL" is subsequently executed, a stack overflow occurs and the first entry is lost (only the most recent 4 return addresses are stored).

#### Data Memory – RAM

The data memory is divided into two functional groups: special function registers and general purpose data memory (96×8). Most of them are read/write, but some are read only. The unused space before 20H is reserved for future expanded usage and reading these locations will return the result 00H. The general purpose data memory, addressed from 20H to 7FH, is used for data and control information under instruction command. The areas in the RAM can directly handle arithmetic, logic, increment, decrement, and rotate operations. Except some dedicated bits, each bit in the RAM can be set and reset by "SET [m].i" and "CLR [m].i". They are also indirectly accessible through the Memory pointer register 0 (MP0; 01H) or the Memory pointer register 1 (MP1; 03H).

#### Indirect Addressing Register - IAR0, IAR1

Location 00H and 02H are indirect addressing registers that are not physically implemented. Any read/write operation of [00H] and [02H] accesses the RAM pointed to by MP0 (01H) and MP1 (03H) respectively. Reading location 00H or 02H indirectly returns the result 00H. While, writing it indirectly leads to no operation. The

|            | Bank 0     | Bank 1          |

|------------|------------|-----------------|

| 00H        | IA         | R0              |

| 01H        |            | P0              |

| 02H        | IA         | R1              |

| 03H        |            | P1              |

| 04H        | E          | 3P              |

| 05H        | A          | 20              |

| 06H        | P          | CL              |

| 07H        | TE         | BLP             |

| 08H        | TE         | BLH             |

| 09H        |            | CC              |

| 0AH        | ÷          | TUS             |

| 0BH        |            | FC0             |

| 0CH        |            | RL              |

| 0DH        |            | ИR              |

| 0EH        |            | IRC             |

| 0FH        | WE         | DTC             |

| 10H        |            |                 |

| 11H        |            |                 |

| 12H        | F          | PA              |

| 13H        |            |                 |

| 14H        | F          | 'B              |

| 15H        | _          |                 |

| 16H        |            | C               |

| 17H        | -          | GCR             |

| 18H        |            | R0              |

| 19H        |            | R1              |

| 1AH        | -          | RL0             |

| 1BH        | -          | RL1             |

| 1CH        |            | RH0             |

| 1DH        |            | RH1             |

| 1EH        |            | IC1             |

| 1FH<br>20H | LC         | DC              |

| 2011       |            |                 |

| 3FH        | General    |                 |

| 3FH<br>40H | Purpose    |                 |

| -011       | Data       | LCD             |

| 55H        | Memory     | RAM             |

| 56H        | (96 Bytes) |                 |

| 0011       | (1 ,       |                 |

| 7FH        |            |                 |

| :u         | nimplement | ted, read as "0 |

#### RAM Mapping

function of data movement between two indirect addressing registers is not supported. The memory pointer registers, MP0 and MP1, are both 7-bit registers used to access the RAM by combining corresponding indirect addressing registers. MP0 can only be applied to data memory, while MP1 can be applied to data memory and LCD display memory.

#### Memory Pointers – MP0, MP1

Two Memory Pointers, known as MP0 and MP1 are provided. These Memory Pointers are physically implemented in the Data Memory and can be manipulated in the same way as normal registers providing a convenient way with which to address and track data. When any operation to the relevant Indirect Addressing Registers is carried out, the actual address that the microcontroller is directed to, is the address specified by the related Memory Pointer. MP0, together with Indirect Addressing Register, IAR0, are used to access data from Bank 0, while MP1 and IAR1 are used to access data from all banks according to BP register. Direct Addressing can only be used with Bank 0, all other Banks must be addressed indirectly using MP1 and IAR1.

#### Bank Pointer - BP

Depending upon which device is used, the Program and Data Memory are divided into several banks. Selecting the required Program and Data Memory area is achieved using the Bank Pointer. Bit 0 of the Bank Pointer is used to select Data Memory Banks 0~1. The Data Memory is initialised to Bank 0 after a reset, except for a WDT time-out reset in the Power-down Mode, in which case, the Data Memory bank remains unaffected. It should be noted that the Special Function Data Memory is not affected by the bank selection, which means that the Special Function Registers can be accessed from within any bank. Directly addressing the Data Memory will always result in Bank 0 being accessed irrespective of the value of the Bank Pointer. Accessing data from banks other than Bank 0 must be implemented using Indirect addressing mode. As both the Program Memory and Data Memory share the same Bank Pointer Register, care must be taken during programming.

### Accumulator – ACC

The accumulator (ACC) is related to the ALU operations. It is also mapped to location 05H of the RAM and is capable of operating with immediate data. The data movement between two data memory locations must pass through the ACC.

#### Arithmetic and Logic Unit – ALU

This circuit performs 8-bit arithmetic and logic operations and provides the following functions:

- Arithmetic operations (ADD, ADC, SUB, SBC, DAA)

- Logic operations (AND, OR, XOR, CPL)

- Rotation (RL, RR, RLC, RRC)

- Increment and Decrement (INC, DEC)

- Branch decision (SZ, SNZ, SIZ, SDZ etc.)

The ALU not only saves the results of a data operation but also changes the status register.

### Status Register – STATUS

The status register (0AH) is of 8 bits wide and contains, a carry flag (C), an auxiliary carry flag (AC), a zero flag (Z), an overflow flag (OV), a power down flag (PDF), and a watchdog time-out flag (TO). It also records the status information and controls the operation sequence.

Except the TO and PDF flags, bits in the status register can be altered by instructions similar to other registers. Data written into the status register does not alter the TO or PDF flags. Operations related to the status register, however, may yield different results from those intended. The TO and PDF flags can only be changed by a Watchdog Timer overflow, chip power-up, or clearing the Watchdog Timer and executing the "HALT" instruction. The Z, OV, AC, and C flags reflect the status of the latest operations.

| Bit No. | Label | Function                                                |

|---------|-------|---------------------------------------------------------|

| 0       | BP0   | BP0: Select Data Memory Banks<br>0: Bank 0<br>1: Bank 1 |

| 1~7     |       | Unused bit, read as "0"                                 |

#### **BP Register**

| Bit No. | Label | Function                                                                                                                                                                                                                       |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | С     | C is set if the operation results in a carry during an addition operation or if a borrow does not take place during a subtraction operation; otherwise C is cleared. C is also affected by a rotate through carry instruction. |

| 1       | AC    | AC is set if the operation results in a carry out of the low nibbles in addition or no borrow from the high nibble into the low nibble in subtraction; otherwise AC is cleared.                                                |

| 2       | Z     | Z is set if the result of an arithmetic or logic operation is zero; otherwise Z is cleared.                                                                                                                                    |

| 3       | OV    | OV is set if the operation results in a carry into the highest-order bit but not a carry out of the highest-order bit, or vice versa; otherwise OV is cleared.                                                                 |

| 4       | PDF   | PDF is cleared by either a system power-up or executing the "CLR WDT" instruction. PDF is set by executing the "HALT" instruction.                                                                                             |

| 5       | то    | TO is cleared by a system power-up or executing the "CLR WDT" or "HALT" instruction. TO is set by a WDT time-out.                                                                                                              |

| 6, 7    |       | Unused bit, read as "0"                                                                                                                                                                                                        |

#### Status (0AH) Register

On entering the interrupt sequence or executing the subroutine call, the status register will not be automatically pushed onto the stack. If the contents of the status is important, and if the subroutine is likely to corrupt the status register, the programmer should take precautions and save it properly.

### Interrupts

The devices provides two external interrupts, one internal timer/event counter interrupts, an internal time base interrupt, and an internal real time clock interrupt. The interrupt control register 0 (INTC0;0BH) and interrupt control register 1 (INTC1;1EH) both contain the interrupt control bits that are used to set the enable/disable status and interrupt request flags.

Once an interrupt subroutine is serviced, other interrupts are all blocked (by clearing the EMI bit). This scheme may prevent any further interrupt nesting. Other interrupt requests may take place during this interval, but only the interrupt request flag will be recorded. If a certain interrupt requires servicing within the service routine, the EMI bit and the corresponding bit of the INTC0 or of INTC1 may be set in order to allow interrupt nesting. Once the stack is full, the interrupt request will not be acknowledged, even if the related interrupt is enabled, until the Stack Pointer is decremented. If immediate service is desired, the stack should be prevented from becoming full. All these interrupts can support a wake-up function. As an interrupt is serviced, a control transfer occurs by pushing the contents of the program counter onto the stack followed by a branch to a subroutine at the specified location in the ROM. Only the contents of the program counter is pushed onto the stack. If the contents of the register or of the status register (STATUS) is altered by the interrupt service program which corrupts the desired control sequence, the contents should be saved in advance.

External interrupts are triggered by a high to low or low to high or both transition of INT0 or INT1, and the related interrupt request flag (EIF0;bit 4 of INTC0, EIF1;bit 5 of INTC0) is set as well. After the interrupt is enabled, the stack is not full, and the external interrupt is active, a subroutine call to location 04H or 08H occurs. The interrupt request flag (EIF0 or EIF1) and EMI bits are all cleared to disable other interrupts.

The internal Timer/Event Counter interrupt is initialized by setting the Timer/Event Counter interrupt request flag (TF;bit 6 of INTCO), which is normally caused by a timer overflow. After the interrupt is enabled, and the stack is not full, and the TF bit is set, a subroutine call to location 0CH occurs. The related interrupt request flag (TF) is reset, and the EMI bit is cleared to disable further interrupts.

The time base interrupt is initialized by setting the time base interrupt request flag (TBF;bit 4 of INTC1), that is caused by a regular time base signal. After the interrupt

| Bit No. | Label | Function                                                           |

|---------|-------|--------------------------------------------------------------------|

| 0       | EMI   | Controls the master (global) interrupt (1=enabled; 0=disabled)     |

| 1       | EEI0  | Controls the external interrupt 0 (1=enabled; 0=disabled)          |

| 2       | EEI1  | Controls the external interrupt 1 (1=enabled; 0=disabled)          |

| 3       | ETI   | Controls the Timer/Event Counter interrupt (1=enabled; 0=disabled) |

| 4       | EIF0  | External interrupt 0 request flag (1=active; 0=inactive)           |

| 5       | EIF1  | External interrupt 1 request flag (1=active; 0=inactive)           |

| 6       | TF    | Internal Timer/Event Counter request flag (1=active; 0=inactive)   |

| 7       |       | Unused bit, read as "0"                                            |

### INTC0 (0BH) Register

| Bit No. | Label | Function                                                       |

|---------|-------|----------------------------------------------------------------|

| 0       | ETBI  | Controls the time base interrupt (1=enabled; 0:disabled)       |

| 1       | ERTI  | Controls the real time clock interrupt (1=enabled; 0:disabled) |

| 2, 3    | —     | Unused bit, read as "0"                                        |

| 4       | TBF   | Time base request flag (1=active; 0=inactive)                  |

| 5       | RTF   | Real time clock request flag (1=active; 0=inactive)            |

| 6, 7    | —     | Unused bit, read as "0"                                        |

### INTC1 (1EH) Register

is enabled, and the stack is not full, and the TBF bit is set, a subroutine call to location 10H occurs. The related interrupt request flag (TBF) is reset and the EMI bit is cleared to disable further interrupts.

The real time clock interrupt is initialized by setting the real time clock interrupt request flag (RTF; bit 5 of INTC1), that is caused by a regular real time clock signal. After the interrupt is enabled, and the stack is not full, and the RTF bit is set, a subroutine call to location 14H occurs. The related interrupt request flag (RTF) is reset and the EMI bit is cleared to disable further interrupts.

During the execution of an interrupt subroutine, other interrupt acknowledgments are all held until the "RETI" instruction is executed or the EMI bit and the related interrupt control bit are set both to 1 (if the stack is not full). To return from the interrupt subroutine, "RET" or "RETI" may be invoked. RETI sets the EMI bit and enables an interrupt service, but RET does not.

Interrupts occurring in the interval between the rising edges of two consecutive T2 pulses are serviced on the latter of the two T2 pulses if the corresponding interrupts are enabled. In the case of simultaneous requests, the priorities in the following table apply. These can be masked by resetting the EMI bit.

| Interrupt Source             | Priority | Vector |

|------------------------------|----------|--------|

| External interrupt 0         | 1        | 04H    |

| External interrupt 1         | 2        | 08H    |

| Timer/Event Counter overflow | 3        | 0CH    |

| Time base interrupt          | 4        | 10H    |

| Real time clock interrupt    | 5        | 14H    |

The EMI, EEI0, EEI1, ETI, ETBI and ERTI are all used to control the enable/disable status of interrupts. These bits prevent the requested interrupt from being serviced. Once the interrupt request flags (RTF, TBF, TF, EIF1, EIF0) are all set, they remain in the INTC1 or INTC0 respectively until the interrupts are serviced or cleared by a software instruction.

It is recommended that a program not use the "CALL subroutine" within the interrupt subroutine. It's because interrupts often occur in an unpredictable manner or require to be serviced immediately in some applications. At this time, if only one stack is left, and enabling the interrupt is not well controlled, operation of the "call" in the interrupt subroutine may damage the original control sequence.

#### **Oscillator Configuration**

In this device there are two methods of generating the system clock, one external crystal oscillator and one internal RC oscillator.

In addition to the main system clock oscillators, there is an external 32768Hz crystal (LXT) oscillator to provide the clock sources for Real Time and Time Base Interrupts and LCD display.

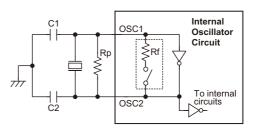

• External Crystal/Resonator Oscillator – HXT

The External Crystal/Ceramic System Oscillator is one of the system oscillator choices, which is selected via a configuration option. For the crystal oscillator configuration, the connection of a crystal across OSC1 and OSC2 will create the necessary phase shift and feedback for oscillation. Two external capacitors may be required to be connected as shown. However, the feedback resistor named Rf shown in the following diagram for the crystal oscillator to oscillate properly can be selected as either an internally or externally connected type via a configuration option. When the external connection type of the feedback resistor is selected, the recommended value of the external connected feedback resistor ranges from  $300k\Omega$  to 500kΩ. Using a ceramic resonator will usually require two small value capacitors, C1 and C2, to be connected as shown for oscillation to occur. The values of C1 and C2 should be selected in consultation with the crystal or resonator manufacturer's specification.

| Crystal Oscillator C1 and C2 Values           |     |      |  |  |  |

|-----------------------------------------------|-----|------|--|--|--|

| Crystal Frequency C1 C2                       |     |      |  |  |  |

| 4MHz                                          | 8pF | 10pF |  |  |  |

| Note: C1 and C2 values are for guidance only. |     |      |  |  |  |

**Crystal Recommended Capacitor Values**

Note: 1. Rp is normally not required. C1 and C2 are required.

2. Although not shown OSC1/OSC2 pins have a parasitic capacitance of around 7pF.

#### Crystal/Resonator Oscillator – HXT

• Internal RC Oscillator - HIRC

The internal RC oscillator is a fully integrated system oscillator requiring no external components. The internal RC oscillator has a fixed frequency of 4095kHz. Device trimming during the manufacturing process and the inclusion of internal frequency compensation circuits are used to ensure that the influence of the power supply voltage, temperature and process variations on the oscillation frequency are minimised. As a result, at a power supply ranging from 1.8V to 3.6V and in a temperature range from -20°C to 50°C degrees, the fixed oscillation frequency of 4095kHz will have a tolerance within 2%. Note that if this internal system clock option is selected, as it requires no external pins for its operation, I/O pins PB5 and PB6 are free for use as normal I/O pins.

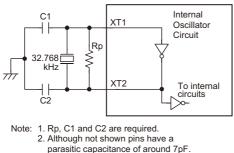

• External 32.768kHz Crystal Oscillator - LXT

The External 32.768kHz Crystal Oscillator is one of the oscillator choices for WDT function, Real Time and Time Base interrupts and LCD display, which is selected via configuration options. This clock source has a fixed frequency of 32.768 kHz and requires a 32.768 kHz crystal to be connected between pins XT1 and XT2. The external resistor and capacitor components connected to the 32.768kHz crystal are necessary to provide oscillation. For applications where precise frequencies are essential, these components may be required to provide frequency compensation due to different crystal manufacturing tolerances. During power-up there is a time delay associated with the LXT oscillator waiting for it to start-up.

However, for some crystals, to ensure oscillation and accurate frequency generation, it is necessary to add two small value external capacitors, C1 and C2. The exact values of C1 and C2 should be selected in consultation with the crystal or resonator manufacturer's specification. The external parallel feedback resistor,  $R_{P}$ , is required.

Some configuration options determine if the XT1/XT2 pins are used for the LXT oscillator or as I/O pins.

- If the LXT oscillator is not used for any clock source, the XT1/XT2 pins should be left as floating states.

- If the LXT oscillator is used for any clock source, the 32.768 kHz crystal should be connected to the XT1/XT2 pins.

External Oscillator – LXT

| LXT Oscillator C1 and C2 Values                    |                                                  |      |      |  |  |

|----------------------------------------------------|--------------------------------------------------|------|------|--|--|

| Crystal Frequency C1 C2                            |                                                  |      |      |  |  |

| 32.768kHz                                          |                                                  | 10pF | 10pF |  |  |

| Note:                                              | Note: 1. C1 and C2 values are for guidance only. |      |      |  |  |

| 2. R <sub>P</sub> =5M~10M $\Omega$ is recommended. |                                                  |      |      |  |  |

32.768kHz Crystal Recommended Capacitor Values

#### LXT Oscillator Low Power Function

The LXT oscillator can function in one of two modes, the Quick Start Mode and the Low Power Mode. The mode selection is executed using the QOSC bit in the RTCC register.

| QOSC Bit | LXT Mode    |

|----------|-------------|

| 0        | Quick Start |

| 1        | Low-power   |

After power-on the QOSC bit will be automatically cleared to zero ensuring that the LXT oscillator is in the Quick Start operating mode. In the Quick Start Mode the LXT oscillator will power up and stabilise quickly. However, after the LXT oscillator has fully powered up it can be placed into the Low-power mode by setting the QOSC bit high. The oscillator will continue to run but with reduced current consumption, as the higher current consumption is only required during the LXT oscillator start-up. In power sensitive applications, such as battery applications, where power consumption must be kept to a minimum, it is therefore recommended that the application program sets the QOSC bit high about 2 seconds after power-on.

It should be noted that, no matter what condition the QOSC bit is set to, the LXT oscillator will always function normally and the only difference is that it will take more time to start up if in the Low-power mode.

#### Internal Low Speed Oscillator - LIRC

The LIRC is a fully self-contained on-chip RC oscillator with a typical frequency of 32kHz at 3V requiring no external components. Device trimming during the manufacturing process and the inclusion of internal frequency compensation circuits are used to ensure that the influence of the power supply voltage, temperature and process variations on the oscillation frequency are minimised. When the device enters the Power-Down Mode, the system clock will stop running but the LIRC oscillator continues to run and to keep the watchdog active if the WDT function is enabled. However, to preserve power in certain applications the LIRC can be disabled via a configuration option together with software register control bits.

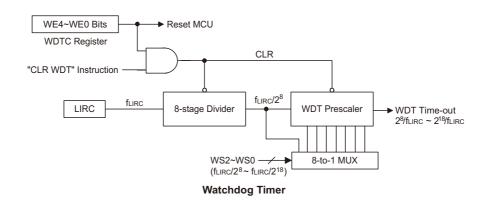

#### Watchdog Timer - WDT

The Watchdog Timer is provided to prevent program malfunctions or sequences from jumping to unknown locations, due to certain uncontrollable external events such as electrical noise.

• Watchdog Timer clock source

The Watchdog Timer clock source is provided by the internal clock which is supplied by the LIRC oscillator. The LIRC internal oscillator has an approximate period of 32kHz at a supply voltage of 5V. However, it should be noted that this specified internal clock period can vary with VDD, temperature and process variations. The Watchdog Timer source clock is then subdivided by a ratio of 28 to 218 to give longer timeouts, the actual value being chosen using the WS2~WS0 bits in the WDTC register.

• Watchdog Timer control register

A single register, WDTC, controls the required timeout period as well as the enable/disable operation. This register together with the corresponding configuration option control the overall operation of the Watchdog Timer.

#### WDTC Register

| Bit     | 7                                              | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------|------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| Name    | WE4                                            | WE3 | WE2 | WE1 | WE0 | WS2 | WS1 | WS0 |

| R/W     | R/W                                            | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR     | 0                                              | 1   | 0   | 1   | 0   | 0   | 1   | 1   |

| Bit 7~3 | Bit 7~3 WE4~WE0: WDT function software control |     |     |     |     |     |     |     |

Bit 7~3

10101: Disabled

01010: Enabled

other: Reset MCU

When these bits are changed by the environmental noise to reset the microcontroller, the reset operation will be activated after 2~3 LIRC clock cycles and the WRF bit in the CTRL register will be set to 1.

Bit 2~0 WS2~WS0: WDT Time-out period selection 000:  $2^{8}/f_{LIRC}$ 001:  $2^{10}/f_{LIRC}$ 010:  $2^{12}/f_{LIRC}$ 011:  $2^{14}/f_{LIRC}$ 100: 2<sup>15</sup>/f<sub>LIRC</sub> 100. 2 //LIRC 101: 2<sup>16</sup>/f<sub>LIRC</sub> 110: 2<sup>17</sup>/f<sub>LIRC</sub> 111: 2<sup>18</sup>/f<sub>LIRC</sub>

#### CTRL Register

| Bit  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|------|---|---|---|---|---|---|---|-----|

| Name |   |   |   |   | _ |   | _ | WRF |

| R/W  |   |   |   | _ | _ |   | _ | R/W |

| POR  |   |   |   |   |   |   | _ | 0   |

Bit 7~1 Unimplemented, read as 0

Bit 0

WRF: WDT Control register software reset flag

0: not occur 1: occurred

This bit is set to 1 by the WDT Control register software reset and cleared by the application program. Note that this bit can only be cleared to 0 by the application program.

Watchdog Timer Operation

The Watchdog Timer operates by providing a device reset when its timer overflows. This means that in the application program and during normal operation the user has to strategically clear the Watchdog Timer before it overflows to prevent the Watchdog Timer from executing a reset. This is done using the clear watchdog instructions. If the program malfunctions for whatever reason, jumps to an unknown location, or enters an endless loop, these clear instructions will not be executed in the correct manner, in which case the Watchdog Timer will overflow and reset the device. Some of the Watchdog Timer options, such as always on select and clear instruction type are selected using configuration options. With regard to the Watchdog Timer enable/disable function, there are also five bits, WE4~WE0, in the WDTC register to offer additional enable/disable and reset control of the Watchdog Timer. If the WDT configuration option is determined that the WDT function is always enabled, the WE4~WE0 bits still have effects on the WDT function. When the WE4~WE0 bits value is equal to 01010B or 10101B, the WDT function is enabled. However, if the WE4~WE0 bits are changed to any other values except 01010B and 10101B, which is caused by the environmental noise, it will reset the microcontroller after 2~3 LIRC clock cycles. If the WDT configuration option is determined that the WDT function is controlled by the WDT control register, the WE4~WE0 values can determine which mode the WDT operates in. The WDT function will be disabled when the WE4~WE0 bits are set to a value of 10101B. The WDT function will be enabled if the WE4~WE0 bits value is equal to 01010B. If the WE4~WE0 bits are set to any other values by the environmental noise, except 01010B and 10101B, it will reset the device after 2~3 LIRC clock cycles. After power on these bits will have the value of 01010B

| WDT<br>Configuration Option | WE4 ~ WE0<br>Bits   | WDT<br>Function |

|-----------------------------|---------------------|-----------------|

|                             | 01010B or<br>10101B | Enable          |

| Always Enable               | Any other value     | Reset MCU       |

|                             | 10101B              | Disable         |

| Controlled by WDT           | 01010B              | Enable          |

| Control Register            | Any other value     | Reset MCU       |

Watchdog Timer Enable/Disable Control

Under normal program operation, a Watchdog Timer time-out will initialise a device reset and set the status bit TO. However, if the system is in the Power Down Mode, when a Watchdog Timer time-out occurs, the TO bit in the status register will be set and only the Program Counter and Stack Pointer will be reset. Three methods can be adopted to clear the contents of the Watchdog Timer. The first is a WDT reset, which means a certain value except 01010B and 10101B written into the WE4~WE0 bit filed, the second is using the Watchdog Timer software clear instructions and the third is via a HALT instruction.

There is only one method of using software instruction to clear the Watchdog Timer. That is to use the single "CLR WDT" instruction to clear the WDT.

The maximum time out period is when the  $2^{18}$  division ratio is selected. As an example, with a 32kHz LIRC oscillator as its source clock, this will give a maximum watchdog period of around 8 second for the  $2^{18}$  division ratio, and a minimum timeout of 7.8ms for the  $2^{8}$  division ration.

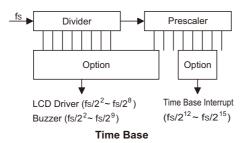

#### **Time Base**

The time base offers a periodic time-out period to generate a regular internal interrupt. Its time-out period ranges from  $f_S/2^{12}$  to  $f_S/2^{15}$  selected by options. If time base time-out occurs, the related interrupt request flag (TBF; bit 4 of INTC1) is set. But if the interrupt is enabled, and the stack is not full, a subroutine call to location 10H occurs.

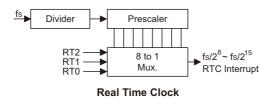

### Real Time Clock – RTC

The real time clock (RTC) is operated in the same manner as the time base that is used to supply a regular internal interrupt. Its time-out period ranges from  $f_S/2^8$  to  $f_S/2^{15}$  by software programming . Writing data to RT2, RT1 and RT0 (bit2, 1, 0 of RTCC;09H) yields various time-out periods. If the RTC time-out occurs, the related interrupt request flag (RTF; bit 5 of INTC1) is set. But if the interrupt is enabled, and the stack is not full, a subroutine call to location 14H occurs. The real time clock time-out signal also can be applied to be a clock source of Timer/Event Counter for getting a longer time-out period.

| RT2 | RT1 | RT0 | <b>RTC Clock Divided Factor</b> |

|-----|-----|-----|---------------------------------|

| 0   | 0   | 0   | 2 <sup>8*</sup>                 |

| 0   | 0   | 1   | 2 <sup>9*</sup>                 |

| 0   | 1   | 0   | 2 <sup>10*</sup>                |

| 0   | 1   | 1   | 2 <sup>11*</sup>                |

| 1   | 0   | 0   | 2 <sup>12</sup>                 |

| 1   | 0   | 1   | 2 <sup>13</sup>                 |

| 1   | 1   | 0   | 2 <sup>14</sup>                 |

| 1   | 1   | 1   | 2 <sup>15</sup>                 |

Note: "\*" not recommended to be used

#### **Power Down Operation – HALT**

The HALT mode is initialized by the "HALT" instruction and results in the following.

- The system oscillator turns off but the LIRC OSC keeps running (if WDT is enabled or the LIRC oscillator or real time clock is selected).

- The contents of the on-chip RAM and of the registers remain unchanged.

- The WDT is cleared and start recounting (if WDT is enabled).

- All I/O ports maintain their original status.

- The PDF flag is set but the TO flag is cleared.

The system quits the HALT mode by an interrupt, an external falling edge signal on port B, or a WDT overflow. The WDT overflow performs a "warm reset". After examining the TO and PDF flags, the reason for chip reset can be determined. The PDF flag is cleared by system power-up or by executing the "CLR WDT" instruction, and is set by executing the "HALT" instruction. On the other hand, the TO flag is set if WDT time-out occurs, and causes a wake-up that only resets the program counter and Stack Pointer, and leaves the others at their original state.

The port A and port B wake-up and interrupt methods can be considered as a continuation of normal execution. Each bit in port A and port B can be independently selected to wake-up the device by option. Awakening from an I/O port stimulus, the program resumes execution of the next instruction. On the other hand, awakening from an interrupt, two sequences may occur. If the related interrupt is disabled or the interrupt is enabled but the stack is full, the program resumes execution at the next instruction. But if the interrupt is enabled, and the stack is not full, the regular interrupt response takes place.

When an interrupt request flag is set before entering the "HALT" status, the system cannot be awaken using that interrupt.

If wake-up events occur, it takes a certain period known as the  $t_{SST}$  period to resume normal operation. In other words, a dummy period is inserted after the wake-up. If the wake-up results from an interrupt acknowledgment, the actual interrupt subroutine execution is delayed by more than one cycle. However, if the Wake-up results in the next instruction execution, the execution will be performed immediately after the dummy period is finished.

To minimize power consumption, all the I/O pins should be carefully managed before entering the HALT status.

When at HALT state and  $f_{\rm S}\text{=}f_{\rm SYS}/4,$  the LCD and RTC will be turned off no matter the bit value of (LCDEN, RTCEN).

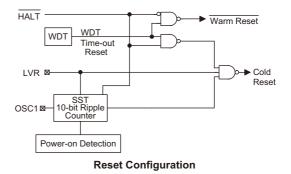

### Reset

There are three ways in which reset may occur.

- Power-on reset

- LVR is reset during normal operation

- WDT time-out is reset during normal operation

The WDT time-out during HALT differs from other chip reset conditions, for it can perform a "warm reset" that resets only the program counter and stack pointer and leaves the other circuits at their original state. Some registers remain unaffected during any other reset conditions. Most registers are reset to the "initial condition" once the reset conditions are met. Examining the PDF and TO flags, the program can distinguish between different "chip resets".

| то | PDF | RESET Conditions                     |

|----|-----|--------------------------------------|

| 0  | 0   | Power-on reset                       |

| u  | u   | LVR reset during normal operation    |

| 1  | u   | WDT time-out during normal operation |

| 1  | 1   | WDT Wake-up HALT                     |

Note: "u" means unchanged

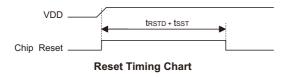

To guarantee that the system oscillator is started and stabilized, the SST (System Start-up Timer) provides an extra-delay of 1024 system clock pulses when the system awakes from the HALT state. Awaking from the HALT state, the SST delay is added.

An extra SST delay is added during the power-up period and any wakeup from the HALT may enable only the SST delay.

| The first and  |           |              | 1        |        |

|----------------|-----------|--------------|----------|--------|

| The functional | unit chip | reset status | is snowr | Delow. |

| Program Counter        | 000H                                                |

|------------------------|-----------------------------------------------------|

| Interrupt              | Disabled                                            |

| Prescaler, Divider     | Cleared                                             |

| WDT, RTC,<br>Time base | Cleared. After master reset,<br>WDT starts counting |

| Timer/Event Counter    | Off                                                 |

| Input/output ports     | Input mode                                          |

| Stack Pointer          | Points to the top of the stack                      |

| Carrier Output         | Floating state                                      |

| SEG/COM outputs        | High state                                          |

| Register | Reset<br>(Power-on) | WDT Time-out Reset<br>(Normal Operation) | LVR Reset<br>(Normal Operation) | WDT Time-out<br>(HALT)* |

|----------|---------------------|------------------------------------------|---------------------------------|-------------------------|

| MP0      | 1xxx xxxx           | 1սսս սսսս                                | 1սսս սսսս                       | 1นนน นนนน               |

| MP1      | 1xxx xxxx           | 1uuu uuuu                                | 1սսս սսսս                       | 1սսս սսսս               |

| BP       | 0                   | 0                                        | 0                               | u                       |

| ACC      | XXXX XXXX           | นนนน นนนน                                | นนนน นนนน                       | นนนน นนนน               |

| PCL      | 0000 0000           | 0000 0000                                | 0000 0000                       | 0000 0000               |

| TBLP     | XXXX XXXX           | นนนน นนนน                                | นนนน นนนน                       | นนนน นนนน               |

| TBLH     | XXXX XXXX           | นนนน นนนน                                | นนนน นนนน                       | นนนน นนนน               |

| RTCC     | 00 0111             | 00 0111                                  | 00 0111                         | uu uuuu                 |

| STATUS   | 00 xxxx             | 1u uuuu                                  | นน นนนน                         | 11 uuuu                 |

| INTC0    | -000 0000           | -000 0000                                | -000 0000                       | -uuu uuuu               |

| CTRL     | 0                   | 0                                        | 0                               | u                       |

| TMR      | XXXX XXXX           | XXXX XXXX                                | XXXX XXXX                       | นนนน นนนน               |

| TMRC     | 0000 1              | 0000 1                                   | 0000 1                          | uuuu u                  |

| WDTC     | 0101 0011           | 0101 0011                                | 0101 0011                       | นนนน นนนน               |

| PA       | 1111 1111           | 1111 1111                                | 1111 1111                       | นนนน นนนน               |

| РВ       | 1111 1111           | 1111 1111                                | 1111 1111                       | นนนน นนนน               |

| PC       | 1111 111x           | 1111 111x                                | 1111 111x                       | นนนน นนนน               |

| SEGCR    | 0000 000x           | 0000 000x                                | 0000 000x                       | นนนน นนนน               |

| TSR0     | 0000 0000           | 0000 0000                                | 0000 0000                       | นนนน นนนน               |

| TSR1     | 10000               | 10000                                    | 10000                           | uuuuu                   |

| CARL0    | 0000 0000           | 0000 0000                                | 0000 0000                       | นนนน นนนน               |

| CARL1    | 0000 0000           | 0000 0000                                | 0000 0000                       | นนนน นนนน               |

| CARH0    | 0000 0000           | 0000 0000                                | 0000 0000                       | นนนน นนนน               |

| CARH1    | 0000 0000           | 0000 0000                                | 0000 0000                       | นนนน นนนน               |

| INTC1    | 0000                | 0000                                     | 0000                            | uuuu                    |

| LCDC     | 11                  | 11                                       | 11                              | uu                      |

The chip reset register status is summarised in the following table:

Note: "\*" refers to warm reset

"u" means unchanged

"x" means unknown

"-" means unimplemented

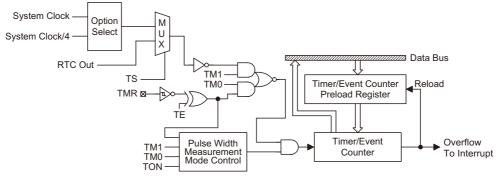

#### **Timer/Event Counter**

One timer/event counters are implemented in the devices. It contains an 8-bit programmable count-up counter.

The timer/event counter clock source may come from the system clock or system clock/4 or RTC time-out signal or external source. System clock source or system clock/4 is selected by option.

Using external clock input allows the user to count external events, measure time internals or pulse widths, or generate an accurate time base. While using the internal clock allows the user to generate an accurate time base.

There are two registers related to the timer/event counter, i.e., TMR (0DH) and TMRC (0EH). There are also two physical registers are mapped to TMR location; writing TMR places the starting value in the timer/event counter preload register, while reading it yields the contents of the timer/event counter. TMRC is timer/event counter control register used to define some options.

The TM0 and TM1 bits define the operation mode. The event count mode is used to count external events, which means that the clock source is from an external (TMR) pin. The timer mode functions as a normal timer with the clock source coming from the internal selected clock source. Finally, the pulse width measurement

mode can be used to count the high or low level duration of the external signal (TMR), and the counting is based on the internal selected clock source.

In the event count or timer mode, the timer/event counter starts counting at the current contents in the timer/event counter and ends at FFH. Once an overflow occurs, the counter is reloaded from the timer/event counter preload register, and generates an interrupt request flag (TF;bit 6 of INTC0).

In the pulse width measurement mode with the values of the TON and TE bit equal to one, after the TMR has received a transient from low to high (or high to low if the TE bit is "0"), it will start counting until the TMR returns to the original level and resets the TON. The measured result remains in the timer/event counter even if the activated transient occurs again. In other words, only one cycle measurement can be made until the TON is set. The cycle measurement will re-function as long as it receives further transient pulse. In this operation mode, the timer/event counter begins counting according not to the logic level but to the transient edges. In the case of counter overflows, the counter is reloaded from the timer/event counter preload register and issues an interrupt request, as in the other two modes, i.e., event and timer modes.

| Bit No. | Label      | Function                                                                                                                                                                           |

|---------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0~2     |            | Unused bit, read as "0"                                                                                                                                                            |

| 3       | TE         | To define the TMR active edge of timer/event counter<br>(0=active on low to high; 1=active on high to low)                                                                         |

| 4       | TON        | To enable/disable timer counting<br>(0=disabled; 1=enabled)                                                                                                                        |

| 5       | TS         | 2 to 1 multiplexer control inputs to select the timer/event counter clock source (0=RTC outputs; 1= system clock or system clock/4)                                                |

| 6<br>7  | TM0<br>TM1 | To define the operating mode (TM1, TM0)<br>01=Event count mode (External clock)<br>10=Timer mode (Internal clock)<br>11=Pulse Width measurement mode (External clock)<br>00=Unused |

### TMRC (0EH) Register

Timer/Event Counter

To enable the counting operation, the Timer ON bit (TON: bit 4 of TMRC) should be set to 1. In the pulse width measurement mode, the TON is automatically cleared after the measurement cycle is completed. But in the other two modes, the TON can only be reset by instructions. The overflow of the timer/event counter is one of the wake-up sources. No matter what the operation mode is, writing a 0 to ETI disables the related interrupt service.

In the case of timer/event counter OFF condition, writing data to the timer/event counter preload register also reloads that data to the timer/event counter. But if the timer/event counter is turn on, data written to the timer/event counter is kept only in the timer/event counter preload register. The timer/event counter still continues its operation until an overflow occurs.

When the timer/event counter (reading TMR) is read, the clock is blocked to avoid errors. As this may results in a counting error, blocking of the clock should be taken into account by the programmer.

It is strongly recommended to load a desired value into the TMR register first, then turn on the related

timer/event counter for proper operation. Because the initial value of TMR is unknown.

Due to the timer/event scheme, the programmer should pay special attention on the instruction to enable then disable the timer for the first time, whenever there is a need to use the timer/event function, to avoid unpredicatable result. After this procedure, the timer/event function can be operated normally.

### **Carrier Generator**

The device provides a carrier generator of which the signal appears on the REM/REMDRV pin. The carrier output is generated by a 9-bit down-count counter enabled by a control bit together with a carrier signal generator.

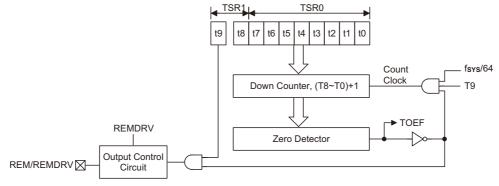

• Timer Configuration

This timer is an internal unit for creating a remote control transmission pattern. As shown, it consists of a 9-bit down-count counter (T8 to T0), a flag (T9) permitting the 1-bit timer output and a zero detector. There are two registers related to this timer known as TSR0 and TSR1 registers.

| Bit No. | Label | Function      |

|---------|-------|---------------|

| 0~7     | T7~T0 | Timer bit 7~0 |

**TSR0** Register

| Bit No. | Label  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Т8     | Timer bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1       | Т9     | T9: Timer enable control<br>0: Disable<br>1: Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2~4     |        | Unused bit, read as "0"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5       | READYB | READYB: REMDRV output driver ready flag<br>0: REMDRV driver is ready for carrier output<br>1: REMDRV driver is not ready for carrier output<br>This bit is used to indicate that whether the REMDRV output driver gets ready to deliver the<br>carrier signal or not. When the REMDRV function is first enabled, including a wake-up from<br>HALT instruction or an output function switch from REM to REMDRV mode, a certain period<br>delay is necessary for the output driver to become stable before the REMDRV carrier signal<br>is sent on the REMDRV pin. Users should make sure that the REMDRV output driver is<br>ready by polling the READYB bit before the Timer is enabled. Note that in REM output func-<br>tion the READYB bit is not available and is always read as 0. |

| 6       | REMDRV | REM/REMDRV output function selection<br>0: REMDRV<br>1: REM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7       | TOEF   | Timer Operation End Flag<br>0: Timer operation is in progress<br>1: Timer operation is ended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **TSR1** Register

**Timer Configuration**

• Timer Operation

The timer starts counting down when a value other than "0" is set for the down counter with a timer manipulation instruction. The timer manipulation instructions for making the timer start operation are shown below:

| MOV<br>MOV      | A,XXH<br>TSR0,A | ; Load T7~T0 into TSR0; XX = 00H ~ FFH                                                                                           |

|-----------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|

| MOV<br>MOV      | A,01H<br>TSR1,A | ; Load T8 into TSR1 and operate in REMDRV output mode                                                                            |

| LOOP: SZ<br>JMP | READYB<br>LOOP  | ; recommended to add the code to the program when a wake-up from HALT,<br>; or an output function switch from REM to REMDRV mode |

| SET             | TSR1.1          | ; after READYB=0, set T9 to 1 to enable the carrier timer                                                                        |

- Additional notes for the 9-bit timer

- Writing to the TSR0 register will only put the written data to the TSR0 register (T7~T0) while writing to the TSR1 register (T8) will transfer the specified data together with the TSR0 register contents to the 9-bit Down Counter. The TOEF bit will be cleared after the data transferred from TSR1 and TSR0 registers to the Down Counter is completed and then wait until the TSR1 register bit 1 is set by user.

- Setting the TSR1 register bit 1 to 1, the timer will start to count. The timer will stop when the counter content is equal to 0 and then the TOEF bit is set to 1.

- If the TSR1 register bit 1 is cleared during the timer counting, the timer will be stopped. Once the TSR1 register bit 1 is set by a specific sequence, i.e. 1→0→1, the down counter will reload the data from T8~T0, and then the down counter begins counting down with the new load data.

- If the TSR1 register bit 1 and the TOEF bit both are equal to 1, the timer can re-start, after a new data is written to the TSR0 and TSR1 register, i.e. T8~T0, in sequence.

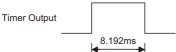

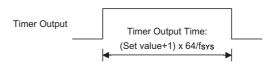

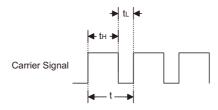

Note: If the Down counter content is equal to 000H, set the T9 bit to start the timer counting, the timer will only count 1 step. The timer output time =  $64/f_{SYS}$ .  $\rightarrow$  [(0+1) ×  $64/f_{SYS}$ = $64/f_{SYS}$ ]