1Mbit(1Mx1bit) Fast Page Mode, 1K Refresh, 20Pin ZIP, 5V Design Part No. HMD1M1Z1

#### **DESCRIPTION**

The HMD1M1Z1 is an 1M x 1 bits Fast Page Mode CMOS DRAMs. Fast Page Mode offers high speed random access of memory cells

within the same row. Power supply voltage (+5V), access time (-5, -6), power consumption(Normal or Low power), and package type (ZIP) are optional features of this Module. The HMD1M1Z1 have CAS-before-RAS refresh, RAS-only refresh and Hidden refresh capabilities.

The HMD1M1Z1 is optimized for application to the systems, which are required high density and large capacity such as main memory for main frames and mini computers, personal computer and high performance microprocessor systems.

The HMD1M1Z1 provides common data and outputs.

#### **Features**

www.Dat

- w Fast Page Mode operation

- w CAS-before-RAS refresh capability

- w RAS-only and Hidden refresh capability

- w Fast parallel test mode capability

- w TTL(5V) compatible inputs and outputs

- w Early write or output enable controlled write

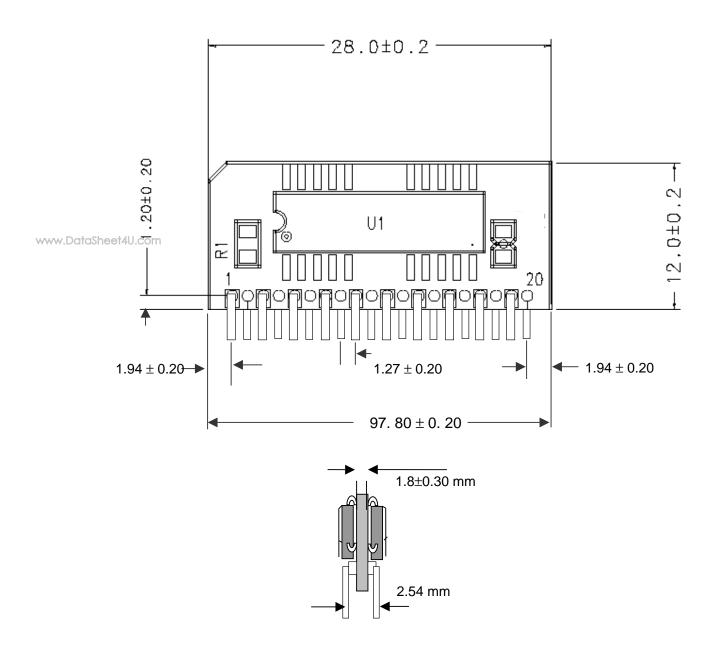

- w Available in 20pin ZIP packages

- w Single +5V±10% power supply

- w 1,024 Refresh Cycles/16ms

- w Performance Range

| Speed      | <b>t</b> <sub>RAC</sub> | t <sub>CAC</sub> | <b>t</b> <sub>RC</sub> | t <sub>PC</sub> |

|------------|-------------------------|------------------|------------------------|-----------------|

| HMD1M1Z1-5 | 50                      | 15               | 90                     | 35              |

| HMD1M1Z1-6 | 60                      | 15               | 110                    | 40              |

### **PIN DESCRIPTION**

| PIN          | FUNCTION                 | PIN | FUNCTION             |

|--------------|--------------------------|-----|----------------------|

| A0 – A8      | Address Inputs           | /WE | Read/Write<br>Enable |

| DQ0 –<br>DQ3 | Data<br>Input/Output     | Vcc | Power<br>(+5V)       |

| /RAS         | Row Address<br>Strobe    | Vss | Ground               |

| /CAS         | Column<br>Address Strobe | NC  | No<br>Connection     |

#### **PIN ASSIGNMENT**

| PIN | SYMBOL          |  |  |  |  |

|-----|-----------------|--|--|--|--|

| 1   | NC              |  |  |  |  |

| 2   | /CAS            |  |  |  |  |

| 3   | DOUT            |  |  |  |  |

| 4   | V <sub>SS</sub> |  |  |  |  |

| 5   | DIN             |  |  |  |  |

| 6   | /WE             |  |  |  |  |

| 7   | /RAS            |  |  |  |  |

| 8   | NC              |  |  |  |  |

| 9   | NC              |  |  |  |  |

| 10  | A9NC            |  |  |  |  |

| 11  | A0              |  |  |  |  |

| 12  | A1              |  |  |  |  |

| 13  | A2              |  |  |  |  |

| 14  | A3              |  |  |  |  |

| 15  | V <sub>CC</sub> |  |  |  |  |

| 16  | A4              |  |  |  |  |

| 17  | A5              |  |  |  |  |

| 18  | A6              |  |  |  |  |

| 19  | A7              |  |  |  |  |

| 20  | A8              |  |  |  |  |

## **ABSOLUTE MAXIMUM RATINGS\***

| SYMBOL                            | PARAMETER                          | RATING            | UNIT |

|-----------------------------------|------------------------------------|-------------------|------|

| TA                                | Ambient Temperature under Bias     | 0 ~ 70            | С    |

| TSTG                              | Storage Temperature (Plastic)      | -55 ~ <b>1</b> 50 | С    |

| VIN/VOUT                          | Voltage on any Pin Relative to Vss | -1.0 ~ 7.0        | V    |

| VCC                               | VCC Power Supply Voltage           |                   | V    |

| IOUT Short Circuit Output Current |                                    | 50                | mA   |

| PD                                | PD Power Dissipation               |                   | mW   |

<sup>\*</sup>NOTE: 1. Stress greater than above absolute Maximum Ratings? May cause permanent damage to the device.

# **RECOMMENDED DC OPERATING CONDITIONS** $(T_A = 0 \sim 70C)$

| www.DataSheet4Uparameter | SYMBOL          | MIN  | TYP. | MAX   | UNIT |

|--------------------------|-----------------|------|------|-------|------|

| Supply Voltage           | Vcc             | 4.5  | 5.0  | 5.5   | V    |

| Ground                   | Vss             | 0    | 0    | 0     | V    |

| Input High Voltage       | V <sub>IH</sub> | 2.4  | -    | Vcc+1 | V    |

| Input Low Voltage        | $V_{IL}$        | -1.0 | -    | 0.8   | V    |

<sup>\*</sup>NOTE: All voltages referenced to Vcc

## DC AND OPERATING CHARACTERISTICS

| SYMBOL            | PARAMETER                                                                                           |                                                | MIN | MAX | UNIT |

|-------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------|-----|-----|------|

| V <sub>OH</sub>   | Output High Level Voltage (IOUT = -5mA)                                                             |                                                | 2.4 |     | V    |

| V <sub>OL</sub>   | Output Low Level Voltage (IOUT = 4.2mA)                                                             | Output Low Level Voltage (IOUT = 4.2mA)        |     |     |      |

|                   | Operating Current                                                                                   | -5                                             |     | 85  |      |

| I <sub>CC1</sub>  | (/RAS,/CAS,Address Cycling : tRC = tRC min)                                                         | -6                                             |     | 75  | mA   |

| I <sub>CC2</sub>  | Standby Current (/RAS,/CAS = V <sub>IH</sub> )                                                      | Standby Current (/RAS,/CAS = V <sub>IH</sub> ) |     |     |      |

|                   | /RAS Only Refresh Current -5                                                                        |                                                |     | 85  |      |

| Іссз              | (/RAS Cycling, /CAS = V <sub>IH</sub> ,: tRC = tRC min)                                             | -6                                             |     | 75  | mA   |

|                   | Fast Page Mode Current                                                                              |                                                | 65  | mA  |      |

| I <sub>CC4</sub>  | (/RAS =V <sub>IL</sub> , /CAS, Address Cycling : tPC = tPC min)                                     | -6                                             |     | 55  | mA   |

| I <sub>CC5</sub>  | Standby Current (/RAS,/CAS >= Vcc -0.2V)                                                            |                                                | 1   | mA  |      |

|                   |                                                                                                     | -5                                             |     | 85  |      |

| I <sub>CC6</sub>  | /CAS before /RAS Refresh Current (tRC = tRC min)                                                    | -6                                             |     | 75  | mA   |

|                   | Self Refresh Current                                                                                |                                                |     |     |      |

| I <sub>ccs</sub>  | (/RAS=/UCAS=/LCAS=V <sub>IL,</sub> /WE=/OE=A0~A9= Vcc -0.2V                                         | or 0.2V,                                       | -   | -   | uA   |

|                   | DQ0~DQ31= Vcc -0.2V, 0.2V or Open)                                                                  |                                                |     |     |      |

|                   | Input Leakage Current (Any Input (0V<= $V_{IN}$ <= $V_{IN}$ + 0.5V, All Other Pins Not Under Test = |                                                |     |     |      |

| I <sub>I(L)</sub> |                                                                                                     |                                                |     | 5   | uA   |

|                   | 0V)                                                                                                 |                                                |     |     |      |

| I <sub>O(L)</sub> | Output Leakage Current(DOUT is Disabled, 0V<=V <sub>OUT</sub> <=                                    | Vcc)                                           | -5  | 5   | uA   |

Note: 1. Icc depends on output load condition when the device is selected.

Icc (max) is specified at the output open condition.

- 2. Address can be changed once or less while  $/RAS = V_{IL}$

- 3. Address can be changed once or less while  $/CAS = V_{IH}$

**CAPACITANCE**  $(T_A=25^{\circ}C, Vcc = 5V+/-10\%, f = 1Mhz)$

|         | DESCRIPTION                                         | SYMBOL           | MIN | MAX | UNITS | NOTE |

|---------|-----------------------------------------------------|------------------|-----|-----|-------|------|

|         | Input Capacitance (A0-A9)                           | C <sub>I1</sub>  | -   | 5   | pF    | 1    |

| www.Dat | Input Capacitance (/WE,/RAS, /CAS0-<br>p/CAS3,/OE)m | C <sub>12</sub>  | -   | 7   | pF    | 1,2  |

| www.bai | Input/Output Capacitance (DQ0-31)                   | C <sub>DQ1</sub> | -   | 7   | pF    | 1,2  |

Note: 1. Capacitance measured with Boonton Meter or effective capacitance measuring method.

2. /CAS = VIH to disable DOUT.

**AC CHARACTERISTICS** (0  $^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  70 $^{\circ}$ C , Vcc = 5V±10%, V<sub>IH</sub>/V<sub>IL</sub> = 2.4/0.8V, V<sub>OH</sub>/V<sub>OL</sub> =2.4/0.4V, See notes 1,2)

|                  | PARAMETER                         | -   | -5  |     | ·6  |      |        |

|------------------|-----------------------------------|-----|-----|-----|-----|------|--------|

| SYMBOL           |                                   | MIN | MAX | MIN | MAX | UNIT | NOTE   |

| t <sub>RC</sub>  | Random Read or Write Cycle Time   | 90  |     | 110 |     | ns   |        |

| t <sub>RWC</sub> | Read-modify-writer cycle time     | 110 |     | 130 |     | ns   |        |

| t <sub>RAC</sub> | Access Time from /RAS             |     | 50  |     | 60  | ns   | 3,4,10 |

| t <sub>CAC</sub> | Access Time from /CAS             |     | 15  |     | 15  | ns   | 3,4,5  |

| t <sub>aa</sub>  | Access Time from Column Address   |     | 25  |     | 30  | ns   | 3,10   |

| t <sub>OFF</sub> | Output Buffer Turn-off Time       | 0   | 12  | 0   | 12  | ns   | 6      |

| t <sub>T</sub>   | Transition Time (Rise and Fall)   | 3   | 50  | 3   | 50  | ns   | 2      |

| t <sub>RP</sub>  | /RAS Precharge Time               | 30  |     | 40  |     | ns   |        |

| t <sub>RAS</sub> | /RAS Pulse Width                  | 50  | 10K | 60  | 10K | ns   |        |

| t <sub>RSH</sub> | /RAS Hold Time                    | 15  |     | 15  |     | ns   |        |

| t <sub>CSH</sub> | /CAS Hold Time                    | 50  |     | 60  |     | ns   |        |

| t <sub>CAS</sub> | /CAS Pulse Width                  | 15  | 10K | 15  | 10K | ns   |        |

| t <sub>RCD</sub> | /RAS to /CAS Delay Time           | 20  | 35  | 20  | 45  | ns   | 4      |

| t <sub>RAD</sub> | /RAS to Column Address Delay Time | 15  | 25  | 15  | 30  | ns   | 10     |

| t <sub>CRP</sub> | /CAS to /RAS Precharge Time       | 5   |     | 5   |     | ns   |        |

| t <sub>ASR</sub> | Row Address Setup Time            | 0   |     | 0   |     | ns   |        |

| t <sub>RAH</sub> | Row Address Hold Time             | 10  |     | 10  |     | ns   |        |

| t <sub>ASC</sub> | Column Address Setup Time         | 0   |     | 0   |     | ns   | 11     |

| t <sub>CAH</sub> | Column Address Hold Time          | 10  |     | 10  |     | ns   | 11     |

| t <sub>RAL</sub> | Column Address to /RAS Lead Time  | 25  |     | 30  |     | ns   |        |

| t <sub>RCS</sub> | Read Command Setup Time           | 0   |     | 0   |     | ns   |        |

| -        |                                         |                                       |     |      |     |      |    |      |

|----------|-----------------------------------------|---------------------------------------|-----|------|-----|------|----|------|

|          | t <sub>RCH</sub>                        | Read Command Hold Time to /CAS        | 0   |      | 0   |      | ns | 8    |

|          | t <sub>RRH</sub>                        | Read Command Hold Time to /RAS        | 0   |      | 0   |      | ns | 8    |

|          | t <sub>wch</sub>                        | Write Command Hold Time               | 10  |      | 10  |      | ns |      |

|          | t <sub>WP</sub>                         | Write Command Pulse Width             | 10  |      | 10  |      | ns |      |

|          | t <sub>RWL</sub>                        | Write Command to /RAS Lead Time       | 15  |      | 15  |      | ns |      |

|          | t <sub>CWL</sub>                        | Write Command to /CAS Lead Time       | 13  |      | 15  |      | ns |      |

|          | t <sub>DS</sub>                         | Data-in Setup Time                    | 0   |      | 0   |      | ns | 9    |

|          | t <sub>DH</sub>                         | Data-in Hold Time                     | 10  |      | 10  |      | ns | 9    |

|          | t <sub>REF</sub>                        | Refresh Period (1024 Cycle)           |     | 16   |     | 16   | ms |      |

|          | t <sub>wcs</sub>                        | Write Command Setup Time              | 0   |      | 0   |      | ms | 7    |

| www.Date | aSh <b>t<sub>cwb</sub>∕</b> U.co        | r/CAS to /WE delay time               | 15  |      | 15  |      | ms | 7,13 |

|          | t <sub>RWD</sub>                        | /RAS to /WE delay time                | 50  |      | 60  |      | ns | 7    |

| -        | t <sub>AWD</sub>                        | Column Address to /WE delay time      | 25  |      | 30  |      | ns | 7    |

|          | t <sub>CPWD</sub>                       | /CAS precharge to /WE delay time      | 30  |      | 35  |      | ns | 7    |

|          | t <sub>CSR</sub>                        | /CAS Setup Time                       | 40  |      | 10  |      | ns | 15   |

|          |                                         | (/CAS-before-/RAS Refresh Cycle)      | 10  |      |     |      |    |      |

|          |                                         | /CAS Hold Time                        | 10  |      | 10  |      |    | 16   |

|          | t <sub>CHR</sub>                        | (/CAS-before-/RAS Refresh Cycle)      | 10  |      | 10  |      | ns | 16   |

|          | t <sub>RPC</sub>                        | /RAS Precharge to /CAS Hold Time      | 5   |      | 5   |      | ns |      |

|          | t <sub>CPA</sub>                        | Access Time from /CAS Precharge       |     | 30   |     | 35   | ns | 3    |

|          | t <sub>PC</sub>                         | Fast Page Mode Cycle Time             | 35  |      | 40  |      | ns |      |

|          | t <sub>CP</sub>                         | Fast Page Mode /RAS Precharge Time    | 10  |      | 10  |      | ns | 12   |

|          | t <sub>RASP</sub>                       | Fast Page Mode /CAS Pulse Time        | 50  | 200K | 60  | 200K | ns |      |

|          | /RAS Hold Time time from /CAS Precharge |                                       | 30  |      | 35  |      | 20 |      |

|          |                                         |                                       | 30  |      | 35  |      | ns |      |

|          | t <sub>RASS</sub>                       | /RAS Pulse Width(CBR self refresh)    | 100 |      | 100 |      | us |      |

|          | t <sub>PRS</sub>                        | /RAS Precharge Time(CBR self refresh) | 90  |      | 110 |      | ns |      |

|          | t <sub>CHS</sub>                        | /CAS Hold Time(CBR self refresh)      | -50 |      | -50 |      | ns |      |

Note: 1. An initial pause of 200us is required after power-up followed by any 8 /RAS-only refresh or /CAS-before-/RAS refresh cycles

before proper device operation is achieved.

- 2. Input voltage levels are  $V_{IH} / V_{IL} / V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals. Also, transition times are measured between  $V_{IH}$  and  $V_{IL}$  are assumed to be 5ns for all inputs.

- 3. Measured with a load circuit equivalent to 2TTL loads and 100pF.

- 4. Operation with the  $\mathbf{t}_{RCD}$  (max) limit insures that  $\mathbf{t}_{RAC}$  (max) can be met,  $\mathbf{t}_{RCD}$  (max) is specified as a reference point only, if  $\mathbf{t}_{RCD}$  is greater than the specified  $\mathbf{t}_{RCD}$ (max) limit, then access time is controlled exclusively by  $\mathbf{t}_{CAC}$ .

- 5. Assumes that  $\mathbf{t}_{RCD} \leftarrow \mathbf{t}_{RCD}$  (max).

- 6. This parameter defines the time at which the output achieves the open circuit condition and is not referenced to  $V_{OH}$  /

$V_{\mathsf{OL}}$

7.  $T_{WCS}$ ,  $T_{RWD}$ ,  $T_{CWD}$ ,  $T_{CPWD}$  are non restrictive operating parameter. They are included in the data sheet as electrical characteristics

only. If  $\mathbf{t}_{wcs} >= \mathbf{t}_{wcs}$  (min), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout

the entire cycle. If  $\mathbf{t}_{\text{CWD}} >= \mathbf{t}_{\text{CWD}}$  (min),  $\mathbf{t}_{\text{RWD}} >= \mathbf{t}_{\text{RWD}}$  (min),  $T_{\text{CPWD}} >= T_{\text{CPWD}}$  (min), then the cycle is a read-modify-write cycle and the data output will contain the data read from the selected address. If neither of the above conditions is satisfied, the condition of the data out is indeterminate.

- 8. Either tRCH or tRRH must be satisfied for a read cycles.

- These parameters are referenced to /CAS falling edge in early write cycles and to /WE falling edge in /OE controlled write cycle and read-modify-write cycles.

- 10. Operation with the  $\mathbf{t}_{RAD}$  (max) limit insures that  $\mathbf{t}_{RAC}$  (max) can be met,  $\mathbf{t}_{RAD}$  (max) is specified as a reference point only, if  $\mathbf{t}_{RAD}$  is greater than the specified  $\mathbf{t}_{RAD}$  (max) limit, then access time is controlled exclusively by  $\mathbf{t}_{AA}$ .

- 11.  $t_{ASC}$ ,  $t_{CAH}$  are are referenced to the earlier /CAS falling edge.

- 12. t<sub>CP</sub> is specified from the later /CAS rising edge in the previous cycle to the earlier /CAS falling edge in the next cycle.

- 13. t<sub>CWD</sub> is referenced to the later /CAS falling edge at word read-modify-write cycle.

- 14.  $t_{\text{CWL}}$  is specified from /WE falling edge to the earlier /CAS rising edge .

- 15. t<sub>CSR</sub> is referenced to the earlier /CAS falling edge before /RAS transition low.

- 16.  $t_{\text{CHR}}$  is referenced to the later /CAS rising edge after /RAS transition low.

## **ORDERING INFORMATION**

| Part Number | Density | Org.      | Package    | Component<br>Number | Vcc | MODE | SPEED |

|-------------|---------|-----------|------------|---------------------|-----|------|-------|

| HMD1M1Z1-5  | 1Mbit   | 1M x 1Bit | 20 Pin-ZIP | 1EA                 | 5V  | FP   | 50ns  |

| HMD1M1Z1-6  | 1Mbit   | 1M x 1Bit | 20 Pin-ZIP | 1EA                 | 5V  | FP   | 60ns  |