# (160-Channel 4-Level Grayscale Display Column Driver with Internal Bit-Map RAM)

**Preliminary**

# **HITACHI**

# **Description**

The HD66520 is a column driver for liquid crystal dot-matrix graphic display systems. This LSI incorporates 160 liquid crystal drive circuits and a  $160 \times 240 \times 2$ -bit bit-map RAM, which is suitable for LCDs in portable information devices. It also includes a general-purpose SRAM interface so that draw access can be easily implemented from a general-purpose CPU. The HD66520 also has a new arbitration method which prevents flicker when the CPU performs draw access asynchronously. The on-chip display RAM greatly decreases power consumption compared to previous liquid crystal display systems because there is no need for high-speed data transfer. The chip also incorporates a four-level grayscale controller for enhanced graphics capabilities, such as icons on a screen.

#### **Features**

- Duty cycle: 1/64 to 1/240

- Liquid crystal drive circuits: 160

- Low-voltage logic circuit: 3.0 to 3.6-V operation power supply voltage

- High-voltage liquid crystal drive circuit: 8 to 28-V liquid crystal drive voltage

- Grayscale display: FRC four-level grayscale display

- · Grayscale memory management: Packed pixel

- Internal bit-map display RAM: 76800 bits (160 × 240 lines × two planes)

- · CPU interface

- SRAM interface

- Address bus: 16 bits, data bus: 8 bits

- High-speed draw function: Supports burst transfer mode

- Arbitration function: Implemented internally (draw access has priority)

- · Access time

- 180 ns (write access)

- 300 ns (read access)

- Low power consumption:

$V_{CC} = 3.3 - V$  operation

- 270 μA during display (logic circuit, liquid crystal drive circuit)

- 7 mA during RAM access (logic circuit)

- · On-chip address management function

- · Refresh unnecessary

- Internal display off function

- Package: 208-pin TCP

# **Pin Description**

| Classi-<br>fication | Symbol                                 | Pin No.      | Pin Name                                | I/O   | Number of Pins | Function                                                                                                                                                                                                       |

|---------------------|----------------------------------------|--------------|-----------------------------------------|-------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply        | V <sub>CC</sub> 1<br>V <sub>CC</sub> 2 |              | V <sub>CC</sub><br>V <sub>CC</sub>      | _     |                | V <sub>CC</sub> –GND: logic power supply                                                                                                                                                                       |

|                     | GND1<br>GND2                           |              | GND<br>GND                              | _     |                |                                                                                                                                                                                                                |

|                     | V <sub>EE</sub> 1<br>V <sub>EE</sub> 2 |              | LCD drive<br>circuit power<br>supply    | _     |                | V <sub>CC</sub> -V <sub>EE</sub> : LCD drive circuit power supply                                                                                                                                              |

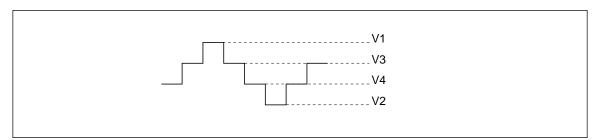

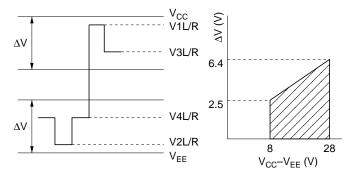

|                     | V1L,<br>V1R                            |              | LCD select<br>high-level<br>voltage     | Input | 2              | LCD drive level power supplies See figure 1. The user should apply the same                                                                                                                                    |

|                     | V2L,<br>V2R                            |              | LCD select<br>low-level<br>voltage      | Input | 2              | potential to the L and R side.                                                                                                                                                                                 |

|                     | V3L,<br>V3R                            |              | LCD deselect<br>high-level<br>voltage   | Input | 2              |                                                                                                                                                                                                                |

|                     | V4L,<br>V4R                            |              | LCD de-<br>select low-<br>level voltage | Input | 2              |                                                                                                                                                                                                                |

| Control signals     | LS0,<br>LS1                            |              | LSI ID select<br>switch pin<br>0 and 1  | Input | 2              | Pins for setting LSI ID no (refer to <b>Pin Functions</b> for details).                                                                                                                                        |

|                     | SHL                                    |              | Shift direction control signal          | Input | 1              | Reverses the relationship between LCD drive output pins Y and addresses.                                                                                                                                       |

|                     | FLM                                    |              | First line<br>marker                    | Input | 1              | First line select signal.                                                                                                                                                                                      |

|                     | CL1                                    |              | Data transfer clock                     | Input | 1              | Clock signal to transfer the line data to an LCD display driver block.                                                                                                                                         |

|                     | M                                      |              | AC switching signal                     | Input | 1              | Switching signal to convert LCD drive output to AC.                                                                                                                                                            |

|                     | DISPOFF                                | <del>.</del> | Display off<br>signal                   | Input | 1              | Control signal to fix LCD driver outputs to LCD select high level. When low, LCD drive outputs Y1 to Y160 are set to V1, or LCD select high level. Display can be turned off by setting a common driver to V1. |

| Classi-<br>fication    | Symbol        | Pin No. | Pin Name              | I/O    | Number of Pins | Function                                                                                                                                                                          |

|------------------------|---------------|---------|-----------------------|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus<br>inter-<br>face  | A0 to<br>A15  |         | Address<br>input      | Input  | 16             | Upper 9 bits (A15–A7) are used for the duty-directional addresses, and lower 7 bits (A6–A0) for the output-pin directional addresses (refer to <b>Pin Functions</b> for details). |

|                        | DB0 to<br>DB7 |         | Data input/<br>output | I/O    | 8              | Packed-pixel 2-bit/pixel display data transfer (refer to <b>Pin Functions</b> for details).                                                                                       |

|                        | CS            |         | Chip select signal    | Input  | 1              | LSI select signal during draw access (refer to <b>Pin Functions</b> for details).                                                                                                 |

|                        | WE            |         | Write signal          | Input  | 1              | Write-enable signal during draw access (refer to <b>Pin Functions</b> for details).                                                                                               |

|                        | ŌĒ            |         | Output enable signal  | Input  | 1              | Output-enable signal during draw access (refer to <b>Pin Functions</b> for details).                                                                                              |

| LCD<br>drive<br>output | Y1 to<br>Y160 |         | LCD drive output      | Output | 160            | Each Y outputs one of the four voltage levels V1, V2, V3, or V4, depending on the combination of the M signal and data levels.                                                    |

Note: The number of input outer leads: 48

Figure 1 LCD Drive Levels

#### **Pin Functions**

#### **Control Signals**

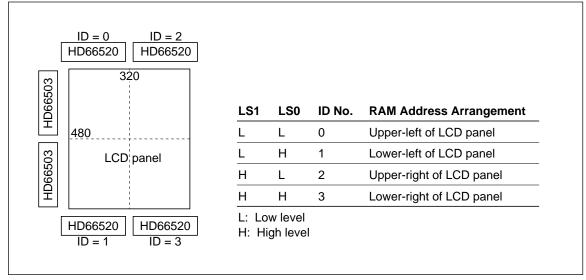

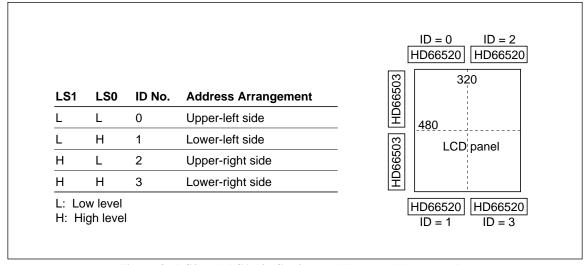

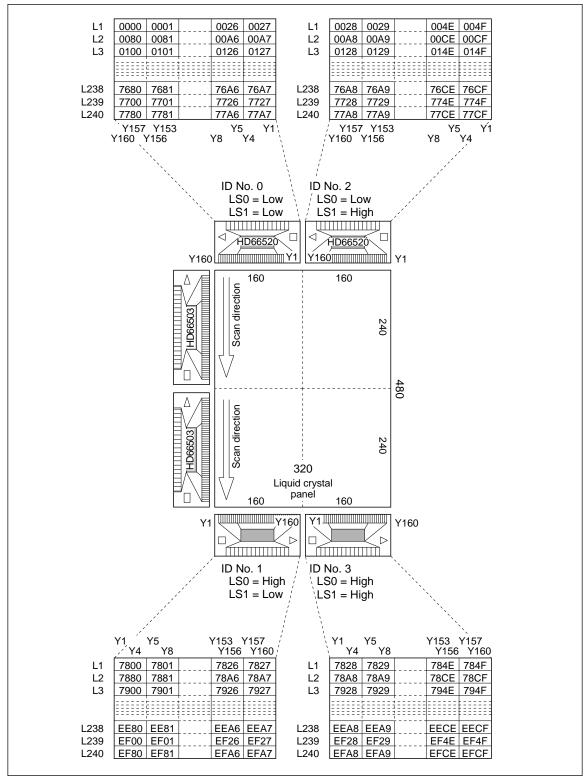

**LS0 and LS1 (Input):** The LS pins can assign four (0 to 3) ID numbers to four LSIs, thus making it possible to connect a maximum of four HD66520s sharing the same  $\overline{CS}$  pin to the same bus (figure 2.)

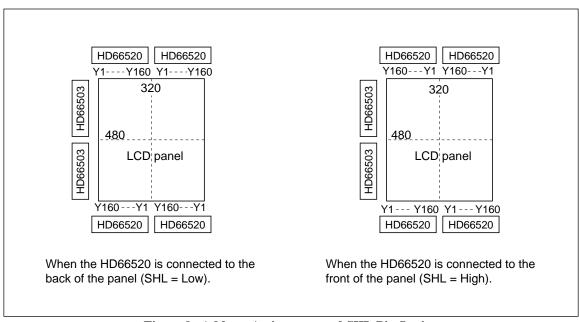

**SHL** (**Input**): This pin reverses the relationship between LCD drive output pins Y1 to Y160 and addresses. There is no need to change the address assignment for the display regardless of whether the HD66520 is mounted from the back or the front of the LCD panel. Refer to Driver Layout and Address Management for details.

**FLM** (**Input**): When the pin is high, it resets the display line counter, returns the display line to the start line, and synchronizes common signals with frame timing.

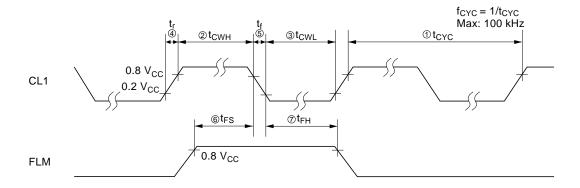

**CL1 (Input):** At each falling edge of data-transfer clock pulses input to this pin, the latch circuits

latch display data and output it to the liquid crystal display driver section.

**M** (**Input**): AC voltage needs to be applied to liquid crystals to prevent deterioration due to DC voltage application. The M pin is a switch signal for liquid crystal drive voltage and determines the AC cycle.

DISPOFF (Input): A control signal to fix liquid crystal driver output to liquid crystal select high level. When this pin is low, liquid crystal drive outputs Y1 to Y160 are set to liquid crystal select high level V1. The display can be turned off by setting the outputs of the common driver to level V1. In this case, display RAM data will be retained. Therefore, if signal DISPOFF returns to high level, liquid crystal drive outputs will return to normal display state. Draw access can be executed when signal DISPOFF is either in high or low state.

Figure 2 LS Pins and Address Assignment

#### **Power Supply Pins**

V<sub>CC</sub>1-2 and GND1-2: These pins supply power to the logic circuit.

$V_{CC}1$ -2 and  $V_{EE}1$ -2: These pins supply power to the liquid crystal circuits.

V1L, V1R, V2L, V2R, V3L, V3R, V4L, V4R: These pins are used to input the level power supply to drive the liquid crystal.

#### **Bus Interface**

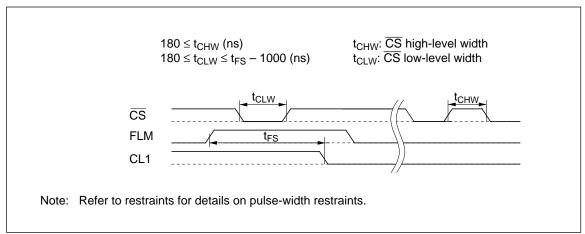

**CS** (**Input**): A basic signal of the RAM area. When  $\overline{CS}$  is low (active), the system can access the on-chip RAM of the LSI whose address space, set by LSO, LS1, and SHL pins, contains the input address. When  $\overline{CS}$  is high, the RAM is in standby.

In addition, this signal is used for arbitration control when draw access from the CPU competes with display access that is used to transfer line data to the liquid crystal panel. Note that there are restraints for the pulse width, as shown in figure 3. The example shown here is when  $V_{CC}=3~V$  for a write operation.

**A0 to A15 (Input):** A bus to transfer addresses during RAM access. Upper nine bits (A15 to A7) are duty-direction addresses, and lower seven bits (A6 to A0) are output pin-direction addresses.

$\overline{\text{WE}}$  (Input): Signal  $\overline{\text{WE}}$  is in active state during low level and standby state during high level and is used to write display data to the RAM. Only the LSI whose address space, set by pins LS0, LS1, and SHL, contains the input address can be written to when  $\overline{\text{CS}}$  is low.

$\overline{\text{OE}}$  (Input): Signal  $\overline{\text{OE}}$  is in active state during low level and standby state during high level and is used to read display data from the RAM. Only the LSI whose address space, set by pins LSO, LS1, and SHL, contains the input address can be read from when  $\overline{\text{CS}}$  is low.

**DB0 to DB7 (Input/Output):** The pins function as data input/output pins. They can accommodate to a data format with 2 bits/pixel, which implement packed-pixel four-level grayscale display.

Figure 3  $\overline{\text{CS}}$  (Input)

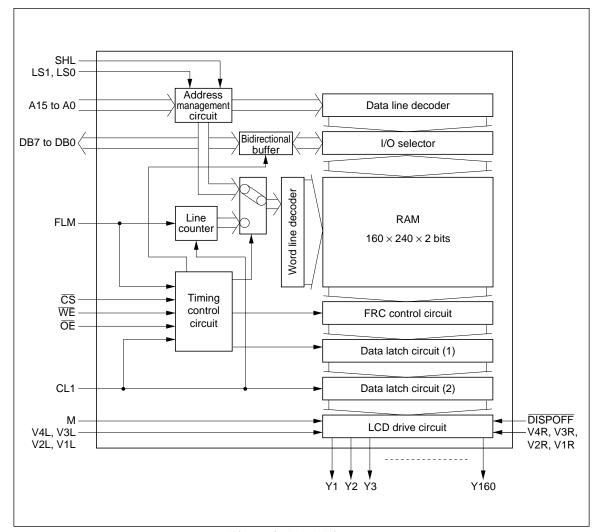

# **Block Diagram**

Figure 4 Block Diagram

Address Management Circuit: Converts the addresses input via A15–A0 from the system to the addresses for a memory map of the on-chip RAM. When several LSIs (HD66520s) are used, only the LSI whose address space, set by pins LSO, LS1, and SHL, contains the input address, accepts the access from the system, and enables the inside. The address management circuit enables configuration of the LCD display system with memory addresses not affected by the connection direction, and reduces burdens of software and hardware in the system. Refer to the How to Use the LS1 and LS0 Pins to set pins LS0, LS1, and SHL.

Timing Control Circuit: This circuit controls arbitration between display access and draw access. Specifically, it controls access timing while receiving signals FLM, CL1,  $\overline{CS}$ ,  $\overline{WE}$ , and  $\overline{OE}$  as input. FLM and CL1 are used to perform refresh (display access), that is, to transfer line data to the liquid crystal circuit.  $\overline{CS}$ ,  $\overline{WE}$ , and  $\overline{OE}$  are used for the CPU to perform draw operation (draw access), that is, to read and write display data from and to the internal RAM. This circuit also generates a timing signal for the FRC control circuit to implement four-level grayscale display.

Line Counter: Operates refresh functions. When FLM is high, the counter clears the count value and generates an address to select the first line in the RAM section. The counter increments its value whenever CL1 is valid and generates an address to select subsequent lines in the RAM section.

**Bidirectional Buffer:** Controls the transfer direction of the display data according to signals from pins  $\overline{\text{WE}}$  and  $\overline{\text{OE}}$  in draw operation from the system.

**Word Line Decoder:** Decodes duty addresses (A15 to A7) and selects one of 240 lines in the display RAM section, and activates one-line memory cells in the display RAM section.

**Data Line Decoder:** Decodes pin addresses (A6 to A0) and selects a data line in the display RAM section for the 7-bit memory cells in one-line memory cells activated by the word line decoder.

**I/O Selector:** Reads and writes 8-bit display data for the memory cells in the RAM section.

**Display RAM:**  $160 \times 240 \times 2$ -bit memory cell array. Since the memory is static, display data can be held without refresh operation during power supply.

**FRC Circuit:** Implements FRC (frame rate control) function for four-level grayscale display. For details, refer to **Half Tone Display.**

**Data Latch Circuit** (1): Latches 160-pixel grayscale display data processed by the FRC control circuit after being read from the display RAM section by refresh operation. This circuit is needed to arbitrate between display access for performing liquid crystal display and draw access from the CPU.

**Data Latch Circuit (2):** This circuit again outputs the data in data latch circuit (1) synchronously with signal CL1.

LCD Drive Circuit: Selects one of LCD select/deselect power levels V4R to V1R and V4L to V1L according to the grayscale display data, AC signal M, and display-off signal DISPOFF. The circuit is configured with 160 circuits each generating LCD voltage to turn on/off the display.

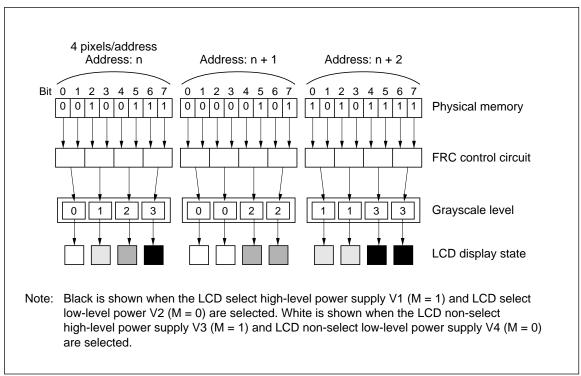

# **Configuration of Display Data Bit**

#### Packed Pixel Method

For grayscale display, multiple bits are needed for one pixel. In the HD66520, two bits are assigned to one pixel, enabling a four-level grayscale display.

One address (eight bits) specifies four pixels, and pixel bits 0 and 1 are managed as consecutive bits.

When grayscale display data is manipulated in bit units, one memory access is sufficient, which enables smooth high-speed data rewriting.

The bit data to input to pin DB7, DB5, DB3, and DB1 becomes MSB and the bit data to input via pin DB6, DB4, DB2, and DB0 is LSB.

Figure 5 Packed Pixel System

# **Half Tone Display (FRC: Frame Rate Control Function)**

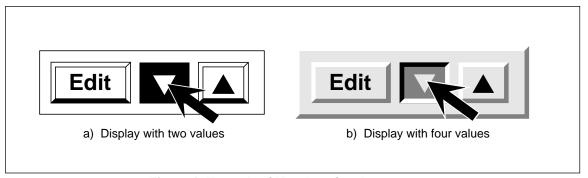

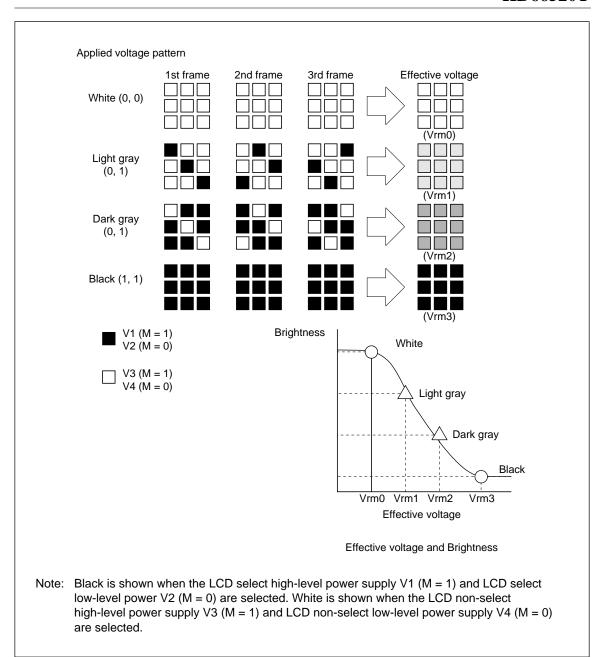

The HD66520 incorporates an FRC function to display four-level grayscale half tone.

The FRC function utilizes liquid crystal characteristics whose brightness is changed by an effective value of applied voltage. Different voltages are applied to each frame and half brightness is expressed in addition to display on/off.

Since the HD66520 has two-bit grayscale data per one pixel, it can display four-level grayscale and improve user interface (figure 6). Figure 7 shows the relationships between voltage patterns applied to each frame, the effective voltage value, and brightness obtained.

Figure 6 Example of User Interface Improvement

Figure 7 Effective Voltage Values vs. Brightness

# **Address Management**

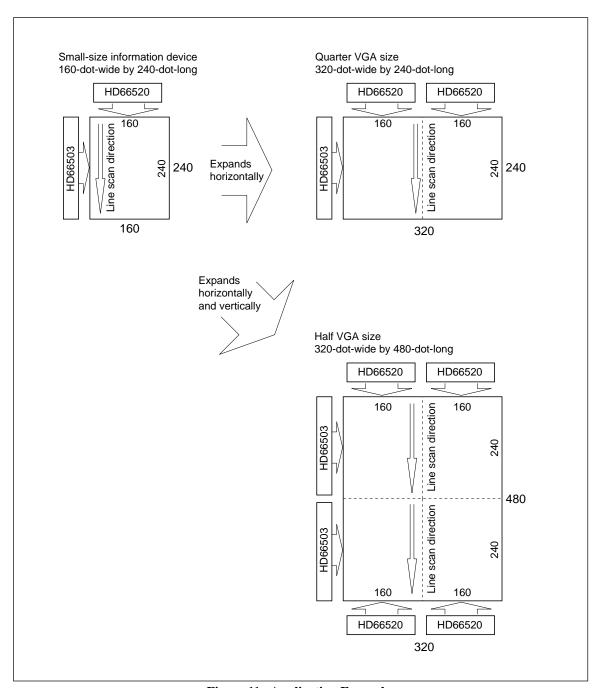

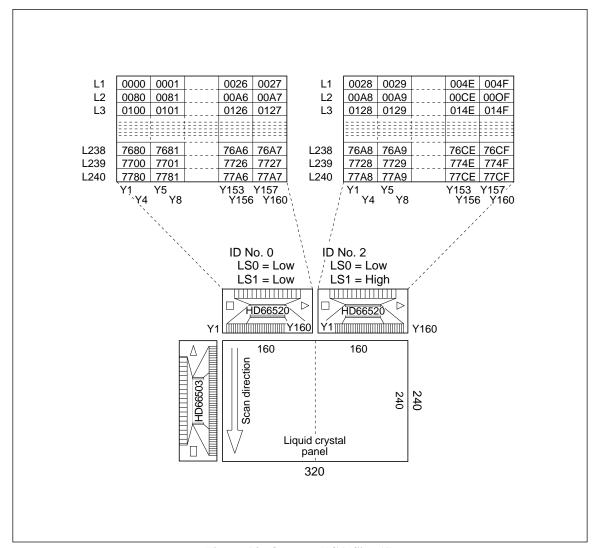

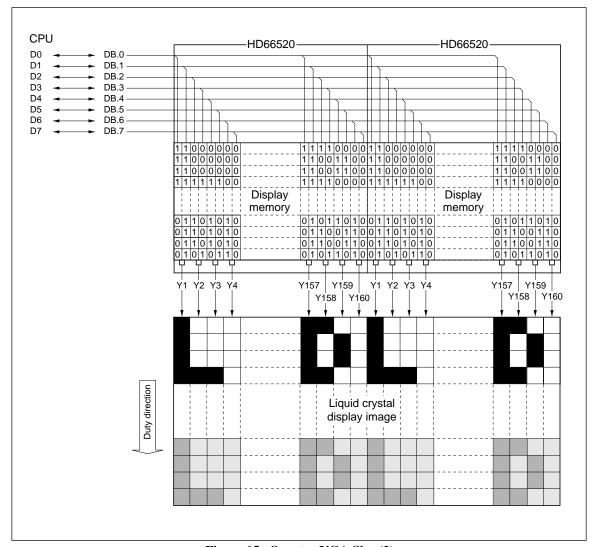

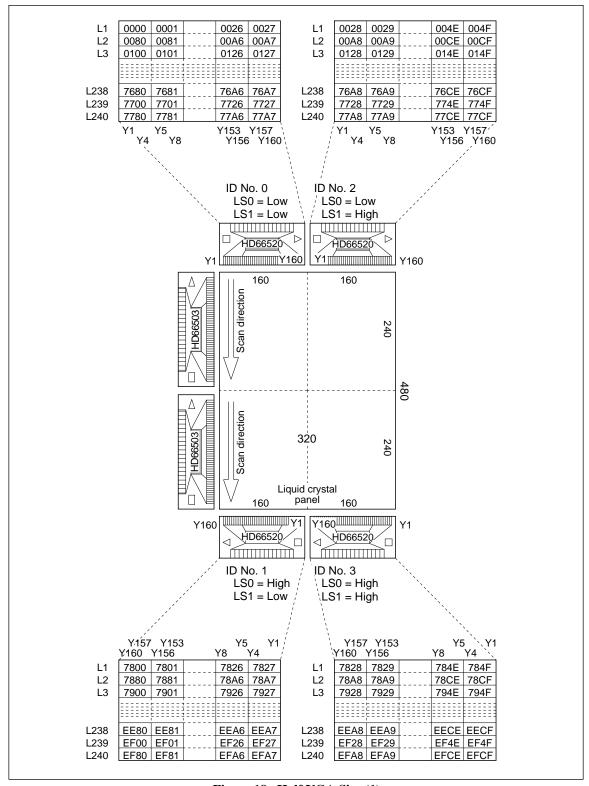

The HD66520 has an address management function that corresponds to three display sizes all of which are standard sizes for portable information devices: a 160-dot-wide by 240-dot-long display (small information devices); a 320-dot-wide by 240-dot-long display (quarter VGA size); and a 320-dot-wide by 480-dot-long display (half VGA size). Up to four HD66520s can be connected to at a time to configure easily liquid crystal displays with the resolutions mentioned above.

#### **Driver Layout and Address Management**

The Y lines on a liquid crystal panel and memory data in a driver are inverted horizontally depending on the connection side of the liquid crystal panel and the driver. When several drivers are connected, address management is needed for each driver. Although reinverted bit-map plotting or address management by the  $\overline{CS}$  pin in each driver are possible by using special write addressing, the load on the software is significantly increased. To avoid this, the HD66520 provides memory addresses independent of connection side, but responds to the setting of pins LS0, LS1, and SHL.

#### How to Use the LS1 and LS0 Pins

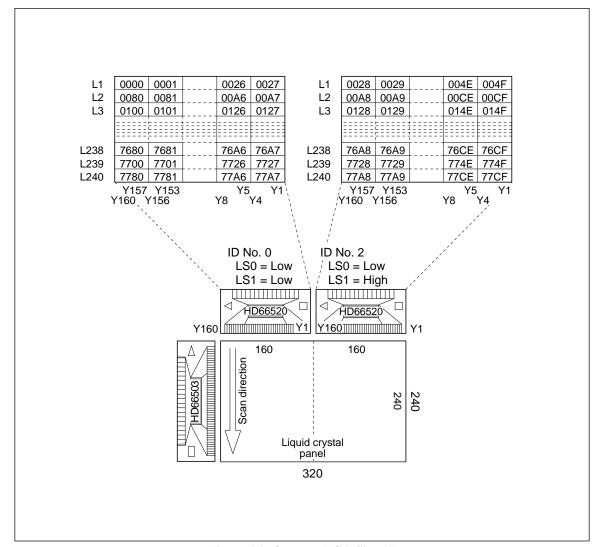

Pins LS1 and LS0 set the LSI position (up to four) as shown in figure 8 by assigning ID numbers 0 to 3 to each HD66520.

Figure 8 LS0 and LS1 Pin Setting and Internal Memory Map

#### How to Use the SHL Pin

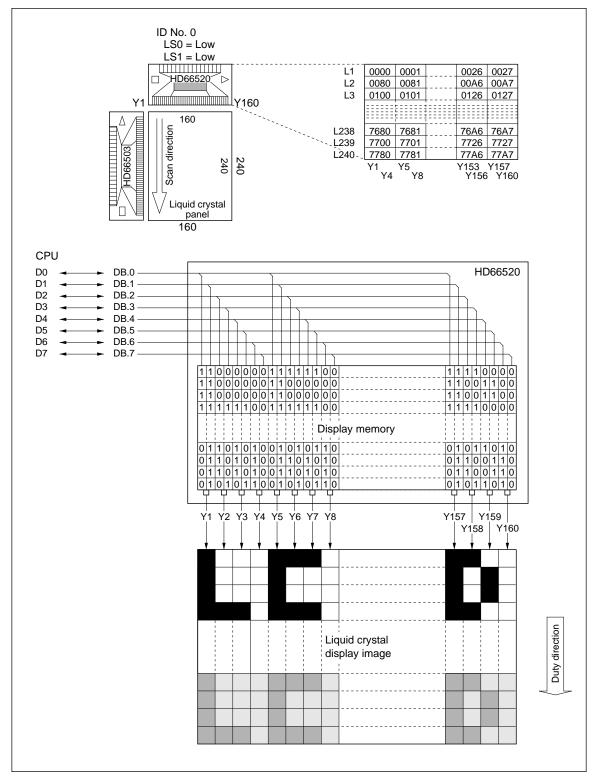

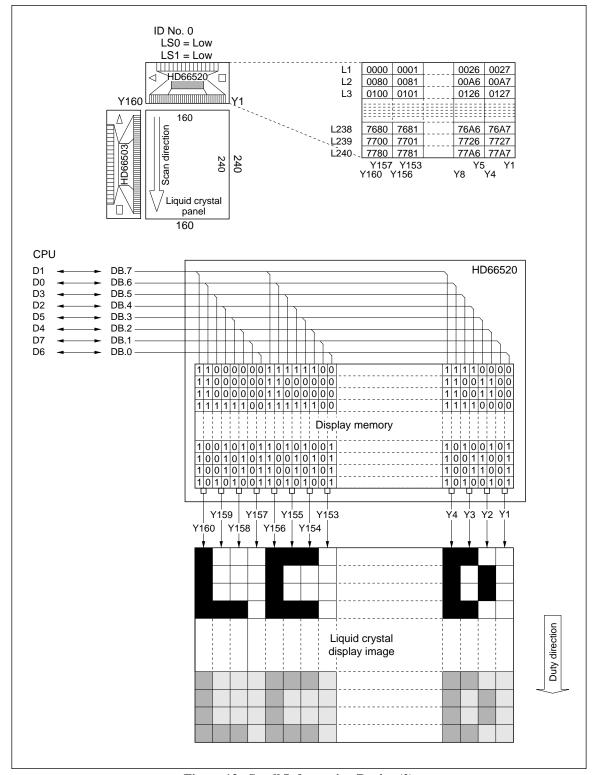

It is possible to invert the relationship between the addresses and output pins Y1 to Y160 by setting the SHL pin (figure 9). The upper left section on the screen can be assigned to address H'0000 regardless of which side of the LCD panel the HD66520 is connected to.

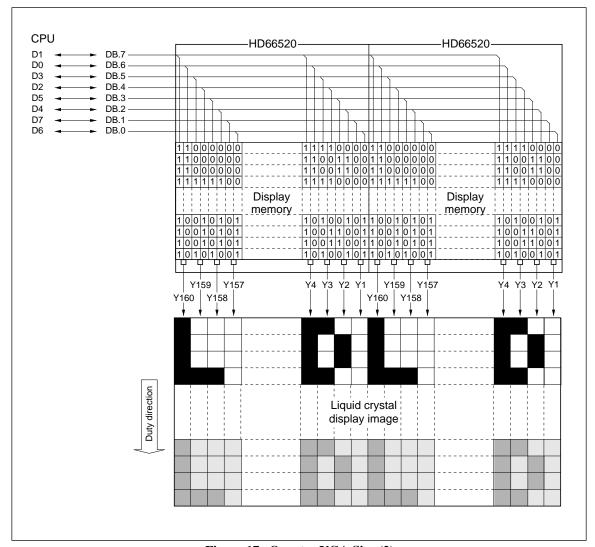

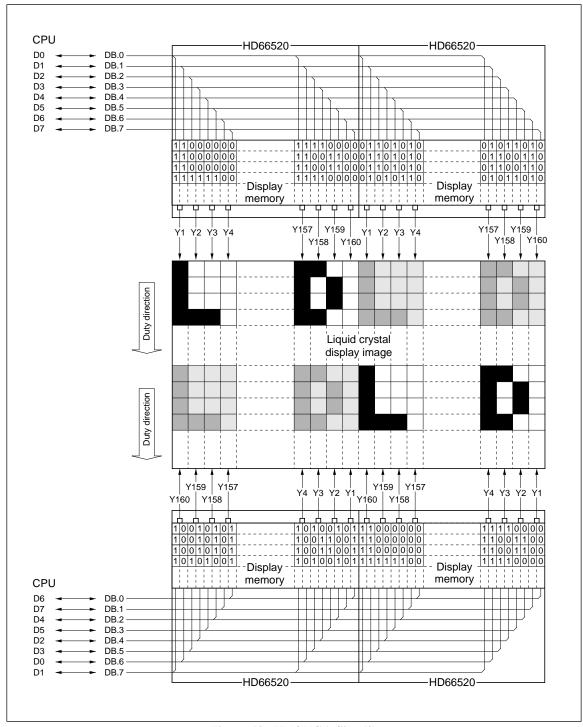

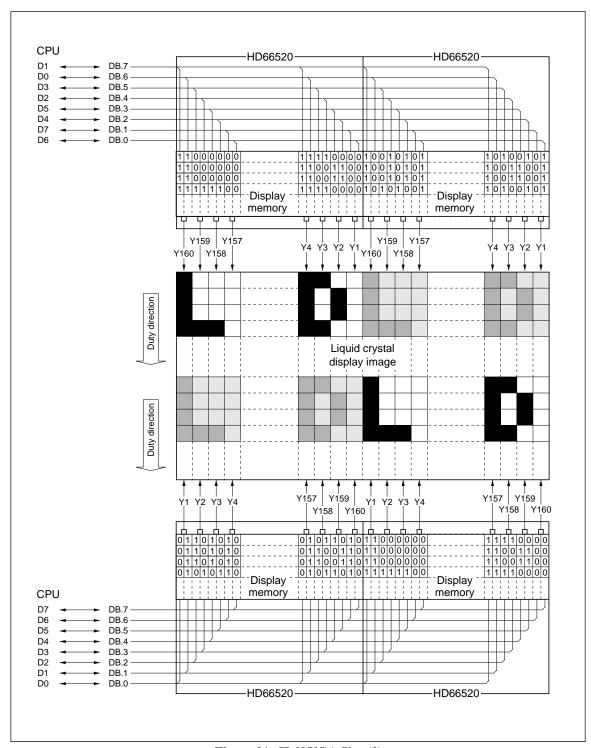

# The Relationship between the Data Bus and Output Pins

The 8-bit data on the data bus has a 2-bit/pixel configuration for a 4-level grayscale display. In addition, the 8-bit data on the data bus has a relationship as shown in table regardless of the relationship between pins LSO, LS1, and SHL.

| Table 1  | Data Bus and Outpu | ıt Pins |          |      |  |

|----------|--------------------|---------|----------|------|--|

| Data Bus | Output Pins        |         |          |      |  |

| DB 0.1   | Y1                 | Y5      | <br>Y153 | Y157 |  |

| DB 2.3   | Y2                 | Y6      | <br>Y154 | Y158 |  |

| DB 4.5   | Y3                 | Y7      | <br>Y155 | Y159 |  |

| DB 6.7   | Y4                 | Y8      | <br>Y156 | Y160 |  |

Figure 9 Address Assignment and SHL Pin Setting

Since the relationship between data bus pins DB0 to DB7 and the output pins are fixed, connect the data from the CPU to data bus pins DB0 to DB7

according to the driver arrangement on the panel as shown in figure 10.

| Drive Arrangement                                                                            | Data Bus Connection                |

|----------------------------------------------------------------------------------------------|------------------------------------|

| When Y1 is placed on the left side of the liquid crystal panel  Y1  Liquid crystal panel     | CPU data  HD66520 data bus pin  D0 |

| When Y160 is placed on the left side of the liquid crystal panel  Y160  Liquid crystal panel | CPU data    HD66520 data   bus pin |

Figure 10 Relationship between Data Bus Pins DB0 to DB7 and Output Pins

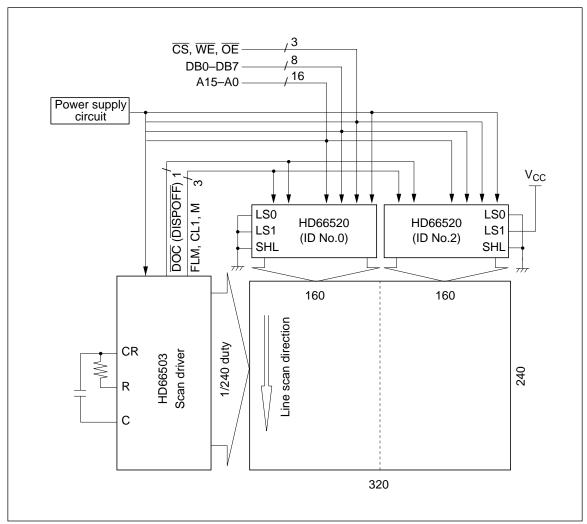

#### **Application Example**

The HD66520 is suitable for a 160-dot-wide by 240-dot-long display (small information devices); a 320-dot-wide by 240-dot-long display (quarter

VGA size); and a 320-dot-wide by 480-dot-long display (half VGA size). All of these are standard sizes for portable information devices. The following shows the system configuration.

Figure 11 Application Examples

# **Small Information Device (SHL = Low)**

Figure 12 Small Information Device (1)

# **Small Information Device (SHL = High)**

Figure 13 Small Information Device (2)

# **Quarter VGA Size (SHL = Low)**

Figure 14 Quarter VGA Size (1)

Figure 15 Quarter VGA Size (2)

# **Quarter VGA Size (SHL = High)**

Figure 16 Quarter VGA Size (1)

Figure 17 Quarter VGA Size (2)

## **Half VGA Size (SHL = Low)**

Figure 18 Half VGA Size (1)

Figure 19 Half VGA Size (2)

# Half VGA Size (SHL = High)

Figure 20 Half VGA Size (1)

Figure 21 Half VGA Size (2)

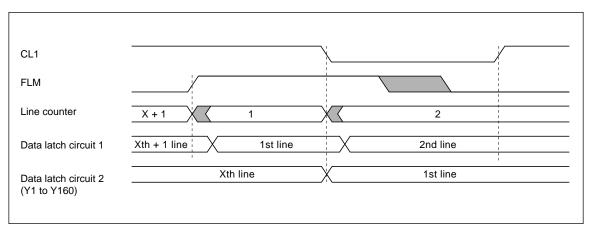

## **Display-Data Transfer**

Display RAM data is transferred to 160-bit data latch circuits 1 and 2 at each falling edge of the CL1 clock pulse. Since display data transfer and RAM access to draw data are completely synchronous-separated in the LSI, there will be no draw data loss or display flickering due to display data transfer timing.

The first line data transfer involves the first line marker (FLM), which initializes a line counter, and transfers the first line data to data latch circuits 1 and 2. Subsequent line data transfers involve transferring the second and the subsequent line data to data latch circuits 1 and 2 while incrementing the line counter value.

#### First Line Data Transfer

The line counter is initialized synchronously with an FLM signal. The first line is transferred to data latch circuits 1 and 2 at the falling edge of the CL1 (figure 22).

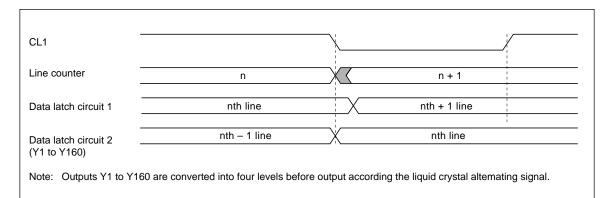

#### Subsequent Line Data Transfer

The second and the subsequent line data are transferred to data latch circuits 1 and 2 at the falling edge of the CL1 to update the line counter value (figure 23).

Figure 22 First Line Data Transfer

Figure 23 Subsequent Line Data Transfer

#### **Draw Access**

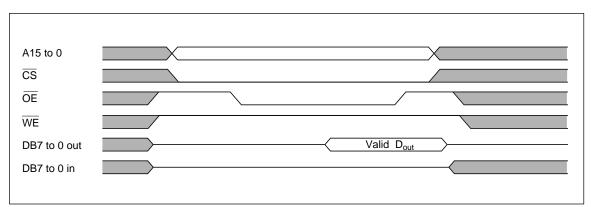

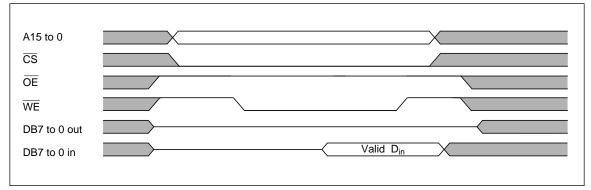

## **Random Cycle**

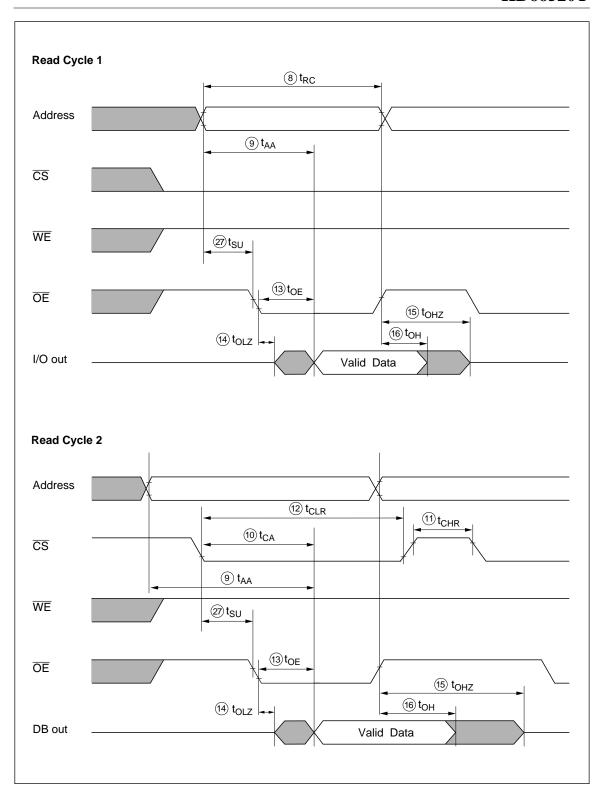

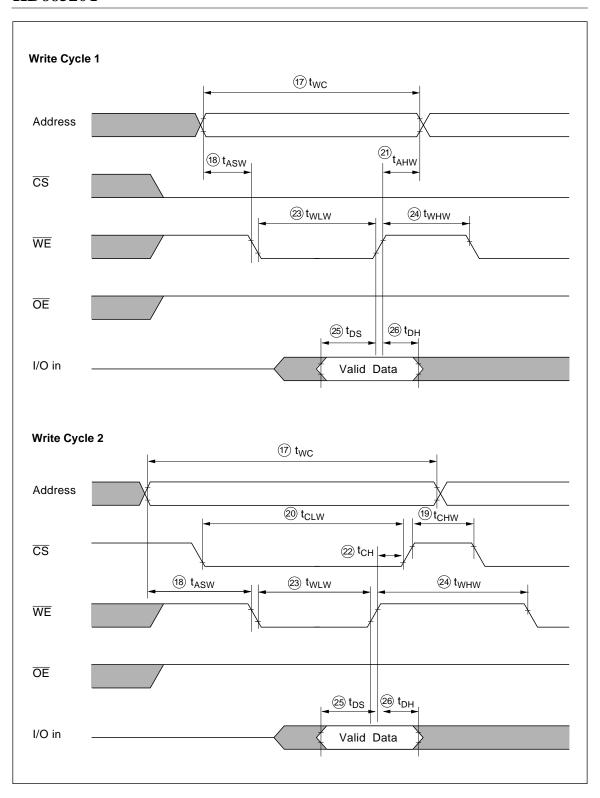

Random cycle sequence is the same as that for the general-purpose SRAM interface (figures 24 and

25). It can easily be connected to a CPU address bus and data bus.

Figure 24 Read Cycle

Figure 25 Write Cycle

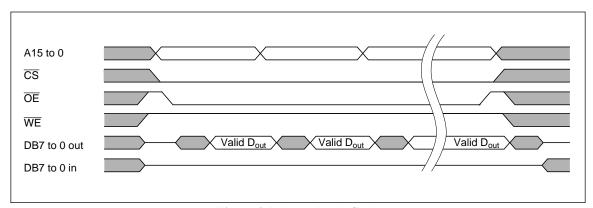

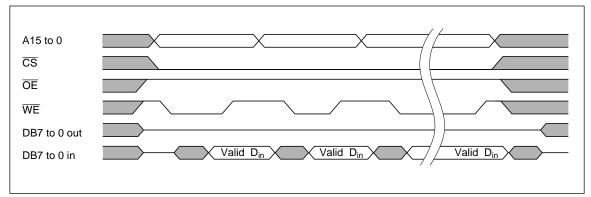

## **Burst Cycle**

Continuous access (burst cycle) can be performed by enabling addresses and  $\overline{OE}$  or  $\overline{WE}$  when  $\overline{CS}$  is

low (figures 26 and 27). Refer to restraints for the period of continuous transfer.

Figure 26 Burst Read Cycle

Figure 27 Burst Write Cycle

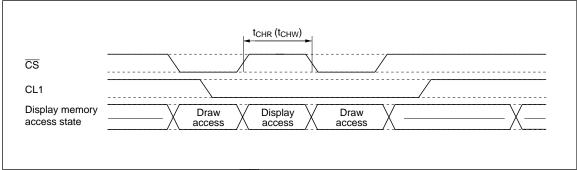

#### **Arbitration Control**

The HD66520 controls the arbitration between draw access and display access. The draw access reads and writes display data of the display memory incorporated in the HD66520. The display access outputs display memory line data to the liquid crystal panel. In this case, draw access is performed before display access, so continuous access is enabled without having the system to wait. For arbitration control, draw access is recognized as valid when signal  $\overline{\text{CS}}$  is low.

The following describes the typical examples of display memory access state during arbitration control.

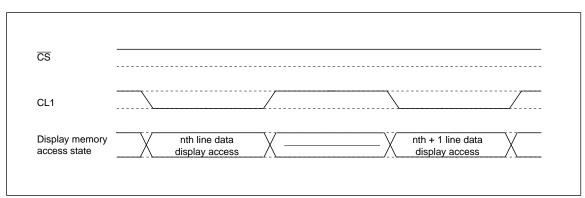

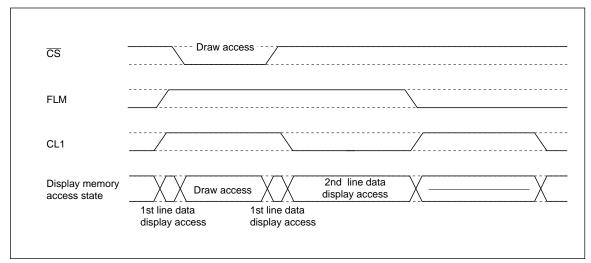

# Sequence Line Data Transfer Display Access Performed by Subsequent Line Data Transfer

If no draw access is attempted, normal display access is performed when signal CL1 is low (figure 28).

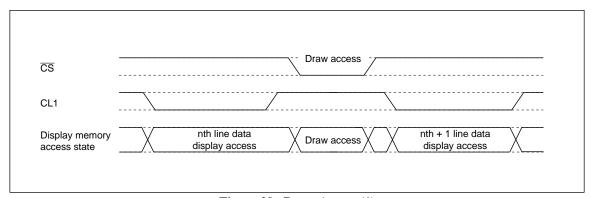

#### **Draw Access 1**

If draw access is attempted when signal CL1 is high, draw access is performed regardless of the display access (figure 29).

Figure 28 Sequence Line Data Transfer

Figure 29 Draw Access (1)

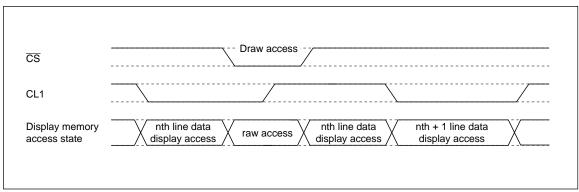

#### **Draw Access 2**

If draw access is attempted when signal CL1 is low, the display access is suspended to perform draw access (figure 30). After the draw access, the display access is performed again. As a result, even if draw access is attempted asynchronously, at least one of the display accesses will be performed.

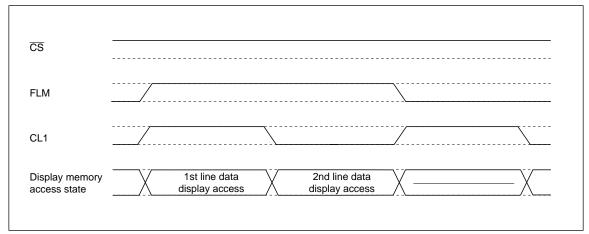

#### Display Access by First Line Data Transfer

If no draw access is attempted, display access for the first line is performed when signal FLM is high and CL1 is low. The display access for the second line is performed when signal CL1 is low (figure 31).

Figure 30 Draw Access (2)

Figure 31 First Line Data Transfer

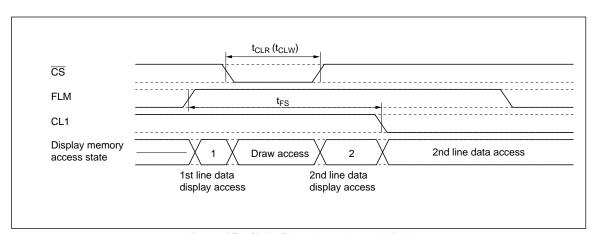

#### **Draw Access 3**

If draw access is attempted when signal FLM is high, stop the display access is suspended to perform the draw access (figure 32). After the draw access, the display access is performed again. As a result, even if draw access is attempted asynchronously, at least one of the two display accesses will be performed.

Note: In order to satisfy draw access 3 and transfer the first line data, there are restraints for the period when pins FLM and CL1 are both high and for the low level pulse width of pin  $\overline{\text{CS}}$ . Refer to Restraints for details on the restraints for the pulse width.

Figure 32 Draw Access (3)

# **Example of System Configuration**

Figure 33 shows a system configuration for a 320-dot-wide by 240-dot-long LCD panel using HD66520s and common driver HD66503 with internal liquid crystal display timing control cir-

cuits. All required functions can be prepared for liquid crystal display with just three chips except for liquid crystal display power supply circuit functions.

Figure 33 System Configuration

#### **Restraints**

The HD66520 can perform continuous draw access (burst access) when signal  $\overline{\text{CS}}$  is low. As a result, display data can be rewritten at high speed.

However, since signal  $\overline{CS}$  is necessary to perform arbitration control between draw access and display access to the display memory, the following restraints exist for the pulse width of signal

## $\overline{\text{CS}}$ .

# • Read operation

| Item                         | Symbol           | Min | Max                    | Unit |

|------------------------------|------------------|-----|------------------------|------|

| Chip select high level width | t <sub>CHR</sub> | 180 | _                      | ns   |

| Chip select low level width  | t <sub>CLR</sub> | 300 | t <sub>FS</sub> – 1000 | ns   |

# • Write operation

| Item                         | Symbol           | Min | Max | Unit |

|------------------------------|------------------|-----|-----|------|

| Chip select high level width | t <sub>CHR</sub> | 180 | _   | ns   |

| Chip select low level width | $t_{CLR}$              |

|-----------------------------|------------------------|

| 180                         | t <sub>FS</sub> – 1000 |

| ns                          |                        |

# **Chip Select High Level Width**

Display access is performed when signal  $\overline{\text{CS}}$  is high during normal draw access. Therefore, only the

minimum display access time is necessary for the chip select high level width (figure 34).

Figure 34 Chip Select High Level Width

#### **Chip Select Low Level Width**

When continuous draw access (burst access) is performed when signal  $\overline{CS}$  is low, the maximum display access time, that is, tFS-1000 (ns) is necessary for the chip select low level width (figure 35). This is needed to secure the display access period for the first line.

When common driver HD66503 is used together with the HD66520, tFS can be calculated with the following formula.

$$f_{FS} = \frac{1}{4 \cdot n_{DUTY} \cdot f_{FLM}}$$

f<sub>FLM</sub>: frame frequency

n<sub>DUTY</sub>: duty

When write operation is performed with the burst access having a frame frequency of 70 Hz and a duty cycle of 1/240, display data of 77 bytes can be consequtively written in one burst access (write cycle is 180 ns).

Figure 35 Chip Select Low Level Width

# **Absolute Maximum Ratings**

| Item                  |                   | Symbol           | Ratings                           | Unit | Notes |

|-----------------------|-------------------|------------------|-----------------------------------|------|-------|

| Power voltage         | Logic circuit     | $V_{CC}$         | -0.3 to +7.0                      | V    | 1     |

|                       | LCD drive circuit | $V_{EE}$         | $V_{CC}$ – 30.0 to $V_{CC}$ + 0.3 | V    |       |

| Input voltage (1)     |                   | $V_{T1}$         | $-0.3$ to $V_{CC} + 0.3$          | V    | 1, 2  |

| Input voltage (2      | )                 | $V_{T2}$         | $V_{EE}$ – 0.3 to $V_{CC}$ + 0.3  | V    | 1, 3  |

| Operating temperature |                   | T <sub>opr</sub> | –20 to +75                        | °C   |       |

| Storage temperature   |                   | T <sub>stg</sub> | -40 to +125                       | °C   |       |

Notes: 1. The reference point is GND (0 V).

- 2. Applies to pins LS0, LS1, SHL, FLM, CL1, M, A0 to A15, DB0 to DB7, DISPOFF, CS, WE, and OE.

- 3. Applies to pins V1L, V1R, V2L. V2R, V3L, V3R, V4L, V4R.

- 4. If the LSI is used beyond its absolute maximum rating, it may be permanently damaged. It should always be used within the limits of its electrical characteristics in order to prevent malfunction or unreliability.

976

#### **Electrical Characteristics**

**DC Characteristics 1** ( $V_{CC} = 3.0 \text{ to } 3.6 \text{ V}, \text{GND} = 0 \text{ V}, V_{CC} - V_{EE} = 8 \text{ to } 28 \text{ V}, \text{Ta} = -20 \text{ to } +75^{\circ}\text{C}$ )

| Item                            | Symbol           | Applicable<br>Pins            | Min  | Тур | Max | Unit | Measurement<br>Condition      | Notes |

|---------------------------------|------------------|-------------------------------|------|-----|-----|------|-------------------------------|-------|

| Input leakage current (1)       | I <sub>IL1</sub> | Except for DB0 to DB7         | -2.5 | _   | 2.5 | μΑ   | $V_{IN} = V_{CC}$ to GND      |       |

| Input leakage current (2)       | I <sub>IL2</sub> | V1L/R, V2L/R,<br>V3L/R, V4L/R | -25  | _   | 25  | μΑ   | $V_{IN} = V_{CC}$ to $V_{EE}$ |       |

| Tri-state<br>leakage<br>current | I <sub>IST</sub> | DB0 to DB7                    | -10  | _   | 10  | μA   | $V_{IN} = V_{CC}$ to GND      |       |

| Vi-Yj on resistance             | R <sub>ON</sub>  | Y1 to Y160                    | _    | 1.0 | 2.0 | kΩ   | I <sub>ON</sub> = 100 μA      | 1     |

Note: 1. Indicates the resistance between one pin from Y1 to Y160 and another pin from V1L/V1R, V2L/V2R, V3L/V3R, V4L/V4R when load current is applied to the Y pin; defined under the following conditions:

$$V_{CC}-V_{EE} = 28 \text{ V}$$

V1L/V1R, V3L/V3R =  $V_{CC} - 2/10 \text{ (V}_{CC}-V_{EE})$

V4L/V4R, V2L/V2R =  $V_{EE} + 2/10 \text{ (V}_{CC}-V_{EE})$

V1L/V1R and V3L/V3R should be near the V<sub>CC</sub> level, and V2L/V2R and V4L/V4R should be near the V<sub>EE</sub> level. All voltage must be within  $\Delta V$ .  $\Delta V$  is the range within which R<sub>ON</sub>, the LCD drive circuits' output impedance, is stable. Note that  $\Delta V$  depends on power supply voltage V<sub>CC</sub>–V<sub>EE</sub>.

Relationship between Driver Output Waveform and Output Voltage

**DC Characteristics 2** ( $V_{CC} = 3.0 \text{ to } 3.6 \text{ V}, \text{GND} = 0 \text{ V}, V_{CC} - V_{EE} = 8 \text{ to } 28 \text{ V}, \text{Ta} = -20 \text{ to } +75^{\circ}\text{C}$ )

| Item                                           | Symbol           | Applicable<br>Pins                 | Min                   | Тур | Max                  | Unit | Measurement Condition                                                          | Notes |

|------------------------------------------------|------------------|------------------------------------|-----------------------|-----|----------------------|------|--------------------------------------------------------------------------------|-------|

| Input high level voltage (1)                   | V <sub>IH1</sub> | LS0-1, SHL,<br>FLM, CL1, M,        | $0.8 \times V_{CC}$   | _   | V <sub>CC</sub>      | V    |                                                                                |       |

| Input low level voltage (1)                    | V <sub>IL1</sub> | DISPOFF                            | 0                     | _   | $0.2 \times V_{CC}$  | V    |                                                                                |       |

| Input high level voltage (2)                   | V <sub>IH2</sub> | DB0 to DB7,<br>CS, A0 to A15,      | $0.7 \times V_{CC}$   | _   | V <sub>CC</sub>      | V    |                                                                                |       |

| Input low level voltage (2)                    | V <sub>IL2</sub> | WE, OE                             | 0                     | _   | $0.15 \times V_{CC}$ | V    |                                                                                |       |

| Output high level voltage                      | V <sub>OH</sub>  | DB0 to DB7                         | 0.9 × V <sub>CC</sub> | _   | _                    | V    | I <sub>OH</sub> = -50 μA                                                       |       |

| Output low level voltage                       | V <sub>OL</sub>  |                                    | _                     | _   | $0.1 \times V_{CC}$  | V    | $I_{OL} = 50 \mu A$                                                            |       |

| Current<br>consumption<br>during RAM<br>access | I <sub>CC</sub>  | Measurement pin V <sub>CC</sub>    | _                     | _   | 18                   | mA   | Access time 300 ns $V_{CC} = 3.3 \text{ V}$                                    | 2     |

| Current consumption in LCD drive part          | I <sub>EE</sub>  | Measurement<br>pin V <sub>EE</sub> | _                     | _   | 200                  | μΑ   | $V_{CC}$ - $V_{EE}$ = 28 V $V_{CC}$ = 3.3 V $t_{CYC}$ = 59.5 $\mu$ s No access | 2, 3  |

| Current consumption during display operation   | I <sub>DIS</sub> | Measurement<br>pin GND             | _                     | _   | 120                  | μА   |                                                                                |       |

Notes: 1. Input and output currents are excluded. When a CMOS input is floating, excess current flows from the power supply through to the input circuit. To avoid this, V<sub>IH</sub> and V<sub>IL</sub> must be held to V<sub>CC</sub> and GND levels, respectively.

2. Indicates the current when the memory access is stopped and the still image of a zig-zag pattern is displayed in its place.

$\textbf{AC Characteristics 1} \ (V_{CC} = 3.0 \ to \ 3.6 \ V, \ GND = 0 \ V, \ V_{CC} - V_{EE} = 8 \ to \ 28 \ V, \ Ta = -20 \ to \ +75 ^{\circ}C)$

• Display-Data Transfer Timing

| No. | Item                 | Symbol           | Applicable Pins | Min | Max | Unit | Notes |

|-----|----------------------|------------------|-----------------|-----|-----|------|-------|

| 1   | Clock cycle time     | t <sub>CYC</sub> | CL1             | 10  | _   | μs   | 1     |

| 2   | CL1 high-level width | t <sub>CWH</sub> | CL1             | 1.0 | _   | μs   |       |

| 3   | CL1 low-level width  | $t_{CWL}$        | CL1             | 1.0 | _   | μs   |       |

| 4   | CL1 rise time        | t <sub>r</sub>   | CL1             | _   | 50  | ns   |       |

| 5   | CL1 fall time        | t <sub>f</sub>   | CL1             | _   | 50  | ns   |       |

| 6   | FLM setup time       | t <sub>FS</sub>  | FLM, CL1        | 2.0 | _   | μs   | 2     |

| 7   | FLM hold time        | t <sub>FH</sub>  | FLM, CL1        | 1.0 | _   | μs   | _     |

Notes: 1.

2. When executing draw access with burst transfer, the period described in the restrains must be satisfied in the relationship with the arbitration control.

AC Characteristics 2 ( $V_{CC} = 3.0$  to 3.6 V, GND = 0 V,  $V_{CC} - V_{EE} = 8$  to 28 V, Ta = -20 to  $+75^{\circ}C$ )

• Draw Access Timing

- Read Cycle

Measurement conditions:

Input level:  $V_{IH} = 2.4 \text{ V}, V_{IL} = 0.8 \text{ V}$

Output level:  $V_{OH}/V_{OL} = 1.5 \text{ V}$

Output load: 1 TTL gate + 100 pF capacitor

| No. | Item                           | Symbol           | Min | Max                   | Unit | Note |

|-----|--------------------------------|------------------|-----|-----------------------|------|------|

| 8   | Read cycle time                | t <sub>RC</sub>  | 300 | _                     | ns   | _    |

| 9   | Address access time            | t <sub>AA</sub>  | _   | 300                   | ns   |      |

| 10  | Chip select access time        | t <sub>CA</sub>  | _   | 300                   | ns   |      |

| 11  | CS high level width            | t <sub>CHR</sub> | 180 | _                     | ns   |      |

| 12  | CS low level width             | t <sub>CLR</sub> | 300 | t <sub>FS</sub> -1000 | ns   |      |

| 13  | OE delay time                  | t <sub>OE</sub>  | _   | 150                   | ns   |      |

| 14  | OE delay time (low impedance)  | t <sub>OLZ</sub> | 5   | _                     | ns   |      |

| 15  | Output-disable delay time      | t <sub>OHZ</sub> | 0   | 30                    | ns   |      |

| 16  | Output hold time               | t <sub>OH</sub>  | 5   | <del>_</del>          | ns   |      |

| 27  | Address/chip select setup time | t <sub>SU</sub>  | 0   | _                     | ns   | 1    |

#### — Write Cycle

Measurement conditions:

Input level:  $V_{IH} = 2.4 \text{ V}, V_{IL} = 0.8 \text{ V}$

| No. | Item                     | Symbol           | Min | Max                   | Unit | Note |

|-----|--------------------------|------------------|-----|-----------------------|------|------|

| 17  | Write cycle time         | $t_{WC}$         | 180 | _                     | ns   |      |

| 18  | Address-to-WE setup time | t <sub>ASW</sub> | 30  | _                     | ns   |      |

| 19  | CS high level width      | t <sub>CHW</sub> | 180 | _                     | ns   |      |

| 20  | CS low level width       | $t_{CLW}$        | 180 | t <sub>FS</sub> -1000 | ns   |      |

| 21  | Address-to-WE hold time  | t <sub>AHW</sub> | 0   | _                     | ns   |      |

| 22  | CS-to-WE hold time       | t <sub>CH</sub>  | 0   | _                     | ns   |      |

| 23  | WE low level width       | $t_{WLW}$        | 100 | _                     | ns   |      |

| 24  | WE high level width      | $t_{WHW}$        | 30  | _                     | ns   |      |

| 25  | Data-to-WE setup time    | t <sub>DS</sub>  | 80  | _                     | ns   |      |

| 26  | Data-to-WE hold time     | t <sub>DH</sub>  | 30  | _                     | ns   |      |

Note: 1. This is a setup time between  $\overline{OE}$  and either address or  $\overline{CS}$ , whichever enabled later.