The revision list can be viewed directly by clicking the title page.

The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

32

SH7065

Hardware Manual

Renesas 32-Bit RISC Microcomputer SuperH™ RISC engine Family/SH7000 Series

SH7065

HD6437065A HD64F7065SF

HD64F7065AF

ardware

Rev. 5.00 Revision Date: Sep 11, 2006 www.DataSheet4U.com RenesasTechnology www.renesas.com

### Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

### Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

## **General Precautions on Handling of Product**

www.datasheet4u.com

### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

## **Preface**

www.datasheet4u.com

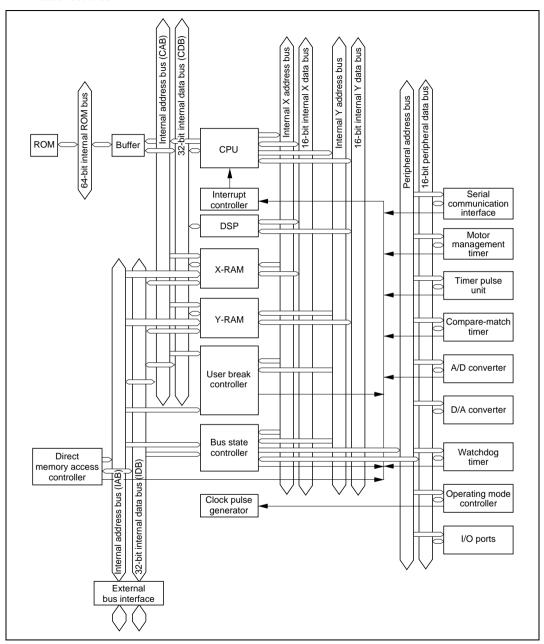

The SH7065 is a microprocessor that integrates peripheral functions necessary for system configuration with a 32-bit internal architecture SH2-DSP CPU as its core.

On-chip peripheral functions include large-capacity ROM and RAM, an interrupt controller, four kinds of timers, a serial communication interface, user break controller (UBC), bus state controller (BSC), direct memory access controller (DMAC), A/D converter, D/A converter, and I/O ports, enabling the SH7065 to be used as a microcontroller for electronic products requiring high speed and low power consumption. Flash memory (F-ZTAT<sup>TM\*</sup>) and mask ROM are available as on-chip ROM, enabling users to respond quickly and flexibly to changing application specifications and the demands of the transition from initial to full-fledged volume production.

Note: \* F-ZTAT is a trademark of Renesas Technology Corp.

Intended Readership: This manual is intended for users undertaking the design of an application system using the SH7065. Readers using this manual require a basic knowledge of electrical circuits, logic circuits, and microcomputers.

Purpose: The purpose of this manual is to give users an understanding of the hardware

functions and electrical characteristics of the SH7065. Details of execution instructions can be found in the SH-1, SH-2, SH-DSP Programming Manual,

which should be read in conjunction with the present manual.

### Using this Manual:

• For an overall understanding of the SH7065's functions Follow the Table of Contents. This manual is broadly divided into sections on the CPU, system control functions, peripheral functions, and electrical characteristics.

• For a detailed understanding of CPU functions Refer to the separate publication SH-1, SH-2, SH-DSP Programming Manual.

Note on bit notation: Bits are shown in high-to-low order from left to right.

Related Material: The latest information is available at our Web Site. Please make sure that you

have the most up-to-date information available.

http://www.renesas.com/

## User's Manuals on the SH7065:

| Manual Title t4u.com               | Document No.    |

|------------------------------------|-----------------|

| SH7065 Hardware Manual             | This manual     |

| SH-1, SH-2, SH-DSP Software Manual | REJ09B0171-0500 |

## Users manuals for development tools:

| Manual Title                                                       | Document No.    |

|--------------------------------------------------------------------|-----------------|

| C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual | REJ10B0047-0100 |

| Simulator/Debugger User's Manual                                   | REJ10B0210-0200 |

| High-performance Embedded Workshop User's Manual                   | REJ10B0025-0200 |

## Application Note:

| Manual Title   | Document No.    |

|----------------|-----------------|

| C/C++ Compiler | REJ05B0463-0300 |

# Main Revisions for This Edition

| Item                                                             | Page     | Revis                                                                                                                                 | ion (See Manual for Detai                                                                                                                    | ls)                          |                           |                             |                 |  |

|------------------------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|-----------------------------|-----------------|--|

| All                                                              | _        | <ul> <li>Notification of change in company name amended</li> <li>(Before) Hitachi, Ltd. → (After) Renesas Technology Corp.</li> </ul> |                                                                                                                                              |                              |                           |                             |                 |  |

|                                                                  |          |                                                                                                                                       |                                                                                                                                              |                              |                           |                             |                 |  |

| 9.3.4 Types of DMA<br>Transfer                                   | 340      | Table<br>Address                                                                                                                      | amended                                                                                                                                      | Request                      | Bus                       | Transfer                    | Usable          |  |

| Relationship between                                             |          | Mode                                                                                                                                  | Type of Transfer                                                                                                                             | Mode                         | Mode                      | Size (Bits)                 | Channel         |  |

| DMA Transfer Type,                                               |          | Dual                                                                                                                                  | External memory and external memory                                                                                                          | Any*1                        | B/C                       | 8/16/32                     | 0–3             |  |

| Request Mode, and Bus                                            |          |                                                                                                                                       | External memory and memory-mapped external device                                                                                            | Any*1                        | B/C                       | 8/16/32                     | 0–3             |  |

| Mode                                                             |          |                                                                                                                                       | Memory-mapped external device and memory-mapped external device                                                                              | Any*1                        | B/C                       | 8/16/32                     | 0–3             |  |

| Table 9.6 Relationship                                           |          |                                                                                                                                       | External memory and on-chip memory                                                                                                           | Any*1                        | B/C                       | 8/16/32                     | 0–3             |  |

| between DMA Transfer                                             |          |                                                                                                                                       | External memory and on-chip peripheral module                                                                                                | Any*2                        | B/C                       | 8/16/32*3                   | 0–3             |  |

| Гуре, Request Mode,<br>and Bus Mode                              |          |                                                                                                                                       | Memory-mapped external device and on-chip memory                                                                                             | Any*1                        | B/C                       | 8/16/32                     | 0–3             |  |

|                                                                  |          |                                                                                                                                       | Memory-mapped external device and on-chip peripheral module                                                                                  | Any*2                        | B/C                       | 8/16/32*3                   | 0–3             |  |

|                                                                  |          |                                                                                                                                       | On-chip memory and on-chip memory                                                                                                            | Any*1                        | B/C                       | 8/16/32                     | 0–3             |  |

|                                                                  |          |                                                                                                                                       | On-chip memory and on-chip peripheral module                                                                                                 | Any*2                        | B/C                       | 8/16/32*3                   | 0–3             |  |

|                                                                  |          |                                                                                                                                       | On-chip peripheral module and on-chip peripheral module                                                                                      | Any*2                        | B/C                       | 8/16/32*3                   | 0–3             |  |

| 11.6 Usage Notes                                                 | 484      | Descri                                                                                                                                | iption added                                                                                                                                 |                              |                           |                             |                 |  |

|                                                                  |          | into th<br>Regist<br>Case                                                                                                             | ttention to the Notices Beloe Timer General Register Uter V (TGRV), Timer Generof Written into Free Operator Consertion into Times Register. | J (TGR<br>al Regi<br>ion Add | U), Ti<br>ster V<br>dress | mer Gene<br>/ (TGRW<br>(*): | eral<br>'), and |  |

|                                                                  |          | Writing Operation into Timer Period Data Register (TF Timer Dead Time Data Register (TDDR) When MMT I Operating:                      |                                                                                                                                              |                              |                           |                             |                 |  |

|                                                                  |          | Notes                                                                                                                                 | on Halting TCNT Counter                                                                                                                      | Operati                      | on:                       | •                           |                 |  |

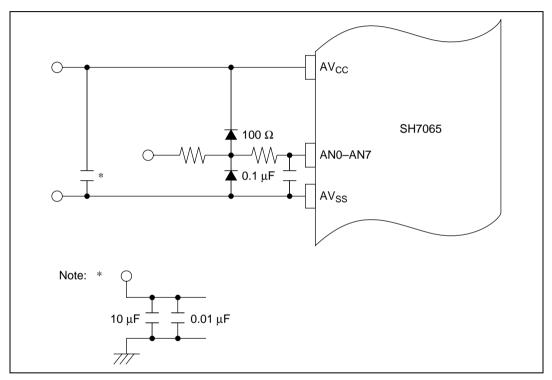

| 15.7.2 Handling of<br>Analog Input Pins                          | 619, 620 | Descri                                                                                                                                | ption of preliminary deleted                                                                                                                 | d                            |                           |                             |                 |  |

| Figure 15.8 Example<br>of Analog Input Pin<br>Protection Circuit |          |                                                                                                                                       |                                                                                                                                              |                              |                           |                             |                 |  |

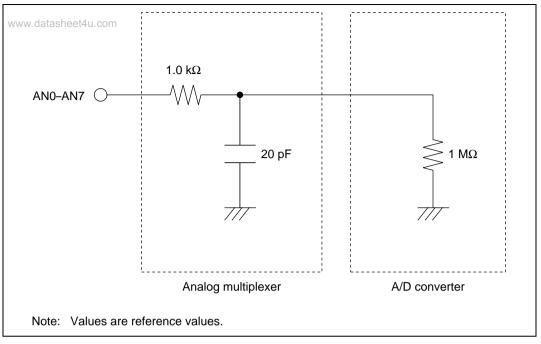

| Figure 15.9 Analog<br>Input Pin Equivalent<br>Circuit            |          |                                                                                                                                       |                                                                                                                                              |                              |                           |                             |                 |  |

| Table 15.5 Analog<br>Input Pin<br>Specifications                 |          |                                                                                                                                       |                                                                                                                                              |                              |                           |                             |                 |  |

| Item | Page | Revision (See Manual for Details) |

|------|------|-----------------------------------|

|      |      |                                   |

796

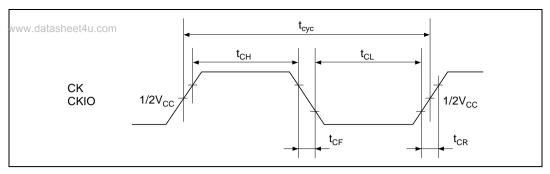

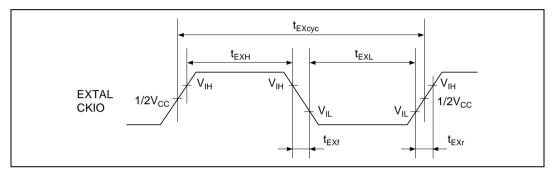

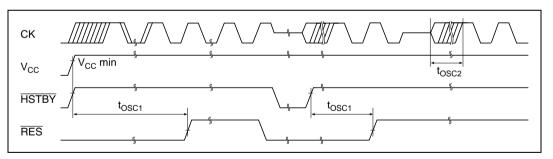

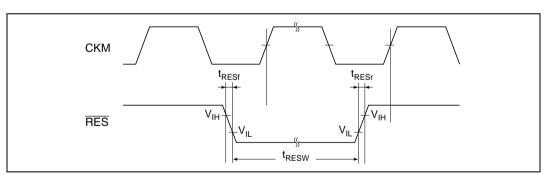

22.3.1 Clock Timing

Table 22.4 Clock Timing

## Table amended

| Item                                          | Symbol             | Min  | Max | Unit | Figure      |

|-----------------------------------------------|--------------------|------|-----|------|-------------|

| Operating frequency (master clock)            | fop                | 20   | 60  | MHz  | Figure 22.2 |

| Clock cycle time                              | t <sub>cyc</sub>   | 16.7 | 50  | ns   | =           |

| Clock low-level pulse width                   | t <sub>CL</sub>    | 4.4  | _   | ns   | _           |

| Clock high-level pulse width                  | tсн                | 4.4  | _   | ns   | =           |

| Clock rise time                               | t <sub>CR</sub>    | _    | 4   | ns   | _           |

| Clock fall time                               | tcF                | _    | 4   | ns   | =           |

| EXTAL/CKIO clock input frequency              | f <sub>EX</sub>    | 5    | 30  | MHz  | Figure 22.3 |

| EXTAL/CKIO clock input cycle time             | t <sub>EXcyc</sub> | 33.3 | 200 | ns   | _           |

| EXTAL/CKIO clock input low-level pulse width  | t <sub>EXL</sub>   | 11.6 | _   | ns   | _           |

| EXTAL/CKIO clock input high-level pulse width | t <sub>EXH</sub>   | 11.6 | _   | ns   | _           |

| EXTAL/CKIO clock input rise time              | t <sub>EXR</sub>   | _    | 5   | ns   | =           |

| EXTAL/CKIO clock input fall time              | t <sub>EXF</sub>   | _    | 5   | ns   | =           |

| Reset oscillation settling time               | tosc1              | 10   | _   | ms   | Figure 22.4 |

| Standby recovery oscillation settling time    | t <sub>OSC2</sub>  | 10   | _   | ms   | =           |

## Contents

| Secti | on 1   | Overview                                   | 1         |

|-------|--------|--------------------------------------------|-----------|

| 1.1   | Featur | res of SH7065                              | 1         |

| 1.2   | Block  | Diagram                                    | 8         |

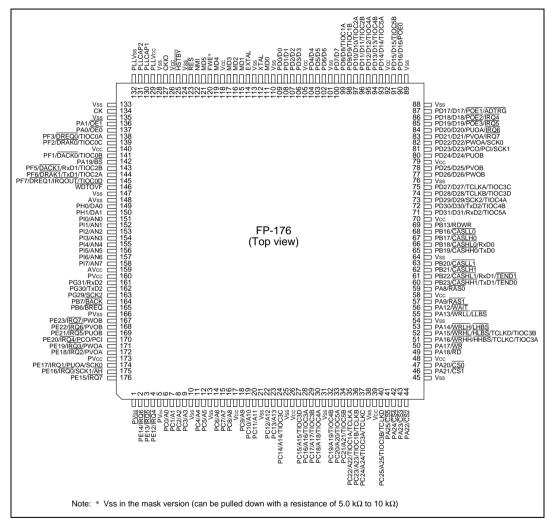

| 1.3   | Pin A  | rrangement and Pin Functions               | 9         |

|       | 1.3.1  | Pin Arrangement                            | 9         |

|       | 1.3.2  | Pin Functions                              | 10        |

| Secti | on 2   | CPU                                        | 21        |

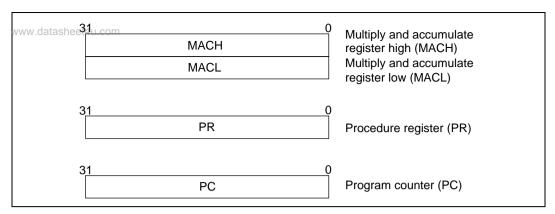

| 2.1   | Regist | ter Configuration                          | 21        |

|       | 2.1.1  | General Registers                          | 21        |

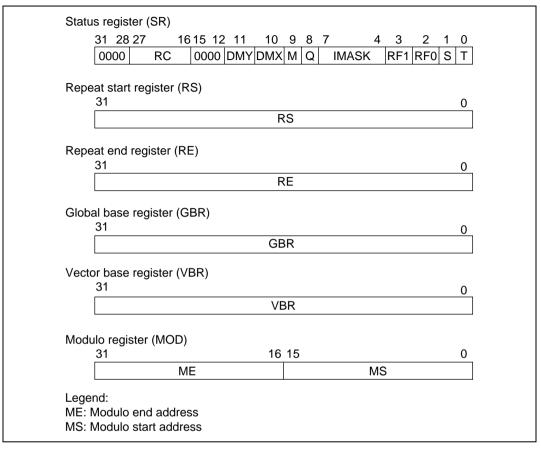

|       | 2.1.2  | Control Registers                          | 23        |

|       | 2.1.3  | System Registers                           | 26        |

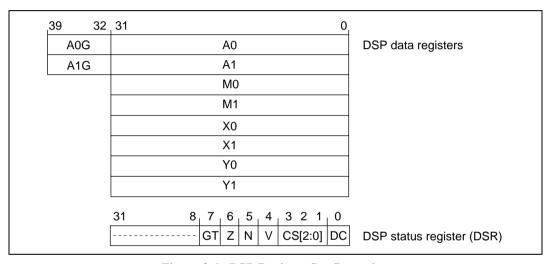

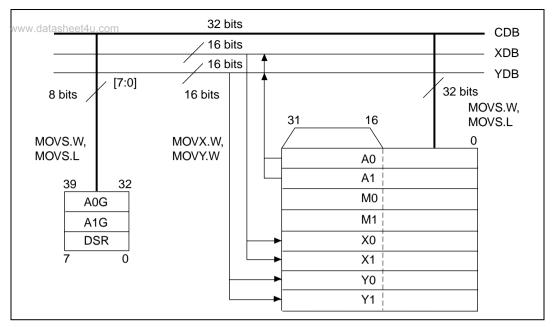

|       | 2.1.4  | DSP Registers                              | 27        |

|       | 2.1.5  | Notes on Guard Bits and Overflow Treatment | 30        |

|       | 2.1.6  | Initial Register Values                    | 31        |

| 2.2   | Data I | Formats                                    | 32        |

|       | 2.2.1  | Register Data Formats                      | 32        |

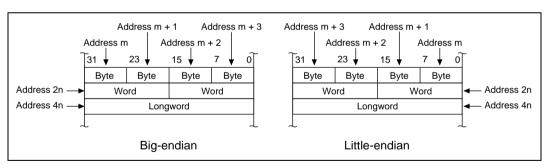

|       | 2.2.2  | Memory Data Formats                        | 32        |

|       | 2.2.3  | Immediate Data Formats                     | 33        |

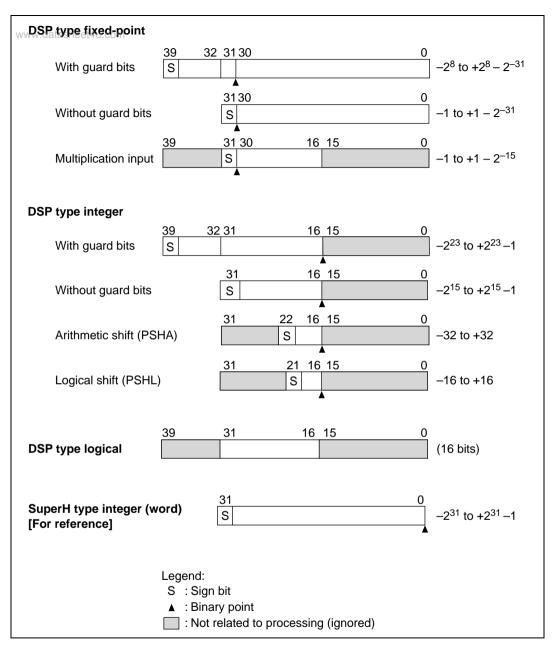

|       | 2.2.4  | DSP Type Data Formats                      | 33        |

|       | 2.2.5  | DSP Type Instructions and Data Formats     | 35        |

| 2.3   | Featur | res of CPU Core Instructions               | 40        |

| 2.4   | Instru | ction Formats                              | 43        |

|       | 2.4.1  | CPU Instruction Addressing Modes           | 43        |

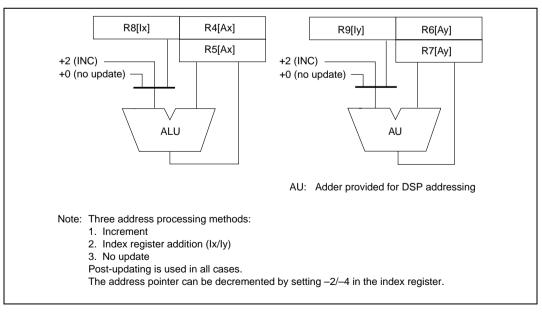

|       | 2.4.2  | DSP Data Addressing                        | 47        |

|       | 2.4.3  | CPU Instruction Formats                    | 54        |

|       | 2.4.4  | DSP Instruction Formats                    | 57        |

| 2.5   | Instru | ction Set                                  | 63        |

|       | 2.5.1  | CPU Instruction Set                        | 63        |

|       | 2.5.2  | DSP Data Transfer Instruction Set          | 79        |

|       | 2.5.3  | DSP Operation Instruction Set              | 83        |

| 2.6   | Usage  | Note                                       | 96        |

| Secti | on 3   | Operating Modes                            | 99        |

| 3.1   | Opera  | ting Mode Selection                        | 99        |

|       | 3.1.1  | Operating Modes                            | 101       |

|       | 3.1.2  | Din Configuration                          | 102       |

|       | 3.1.3  | Register Configuration                     | 102       |

|       |        | Register Configuration                     | n<br>XXII |

| 3.2  | Register Descriptions                                            | 103   |

|------|------------------------------------------------------------------|-------|

|      | 3.2.1 Mode Status Register (MSR)                                 | 103   |

| www. | datasheetdu com<br>3.2.2 Mode Control Register (MODECR)          | 104   |

| Sect | ion 4 Clock Pulse Generator (CPG) and Power-Down Modes           | 105   |

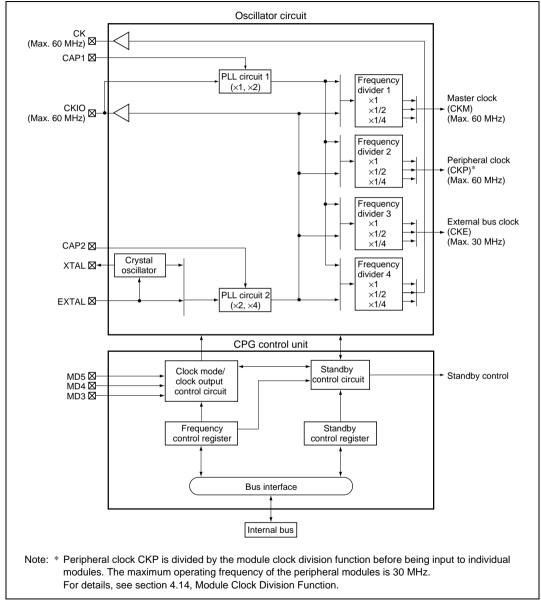

| 4.1  | Overview                                                         |       |

|      | 4.1.1 Features                                                   |       |

|      | 4.1.2 Block Diagram of CPG                                       |       |

|      | 4.1.3 CPG Pin Configuration                                      |       |

|      | 4.1.4 CPG Register Configuration                                 |       |

| 4.2  | Clock Operating Modes                                            |       |

| 4.3  | CPG Register Description                                         | 112   |

|      | 4.3.1 Frequency Control Register (FRQCR)                         |       |

| 4.4  | Changing the Frequency                                           |       |

| 4.5  | Output Clock Control                                             | 135   |

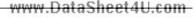

| 4.6  | Oscillator                                                       | 136   |

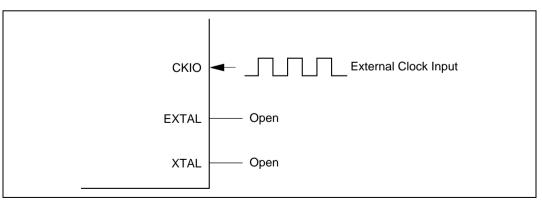

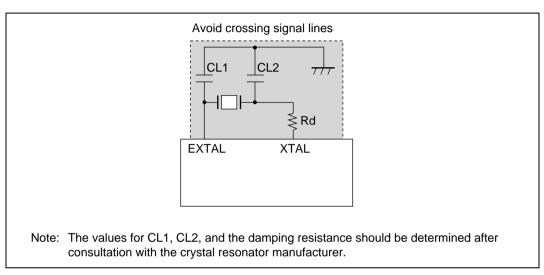

|      | 4.6.1 Connecting a Crystal Resonator                             | 136   |

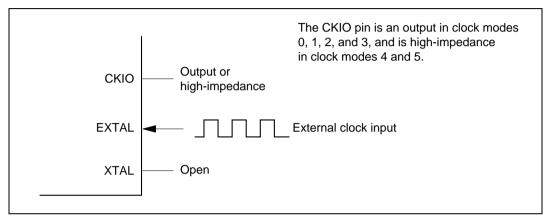

|      | 4.6.2 External Clock Input Methods                               | 137   |

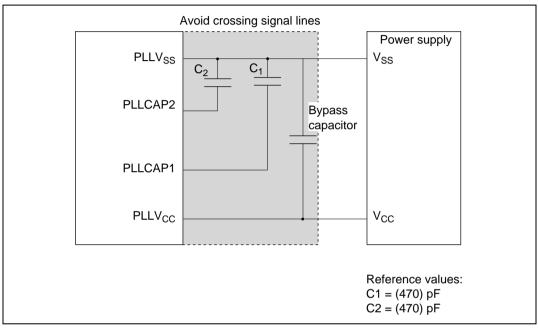

|      | 4.6.3 Notes on Board Design                                      | 138   |

| 4.7  | Oscillation Stoppage Detection Function                          | 141   |

| 4.8  | Power-Down Modes                                                 | 142   |

|      | 4.8.1 States in Power-Down Modes                                 | 142   |

|      | 4.8.2 Pin Configuration                                          | 143   |

| 4.9  | Register Descriptions                                            | 144   |

|      | 4.9.1 Standby Control Register (SBYCR)                           | 144   |

|      | 4.9.2 Module Stop Control Registers 1 and 2 (MSTPCR1, MSTPCR2)   | 145   |

|      | 4.9.3 Module Clock Control Registers 1 to 5 (MCLKCR1 to MCLKCR5) | 146   |

| 4.10 | Sleep Mode                                                       | 149   |

|      | 4.10.1 Transition to Sleep Mode                                  | 149   |

|      | 4.10.2 Exit from Sleep Mode                                      | 149   |

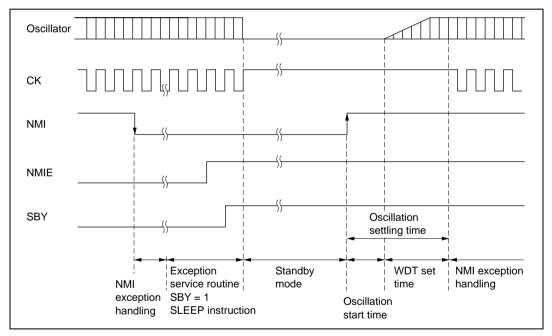

| 4.11 | Software Standby Mode                                            | 150   |

|      | 4.11.1 Transition to Software Standby Mode                       | 150   |

|      | 4.11.2 Exit from Software Standby Mode                           | 152   |

|      | 4.11.3 Software Standby Mode Application Example                 | 153   |

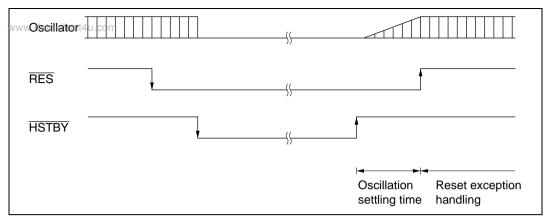

| 4.12 | Hardware Standby Mode                                            | 154   |

|      | 4.12.1 Transition to Hardware Standby Mode                       | 154   |

|      | 4.12.2 Exit from Hardware Standby Mode                           | 154   |

|      | 4.12.3 Hardware Standby Mode Timing                              | 154   |

| 4.13 | Module Standby Function                                          | 155   |

|      | 4.13.1 Transition to Module Standby Function                     | 155   |

|      | 4.13.2 Exit from Module Standby Function                         | 157   |

| _    | www.DataSheet4                                                   | U.com |

RENESAS

| 4.14  | Modul   | e Clock Division Function                                             | 157 |

|-------|---------|-----------------------------------------------------------------------|-----|

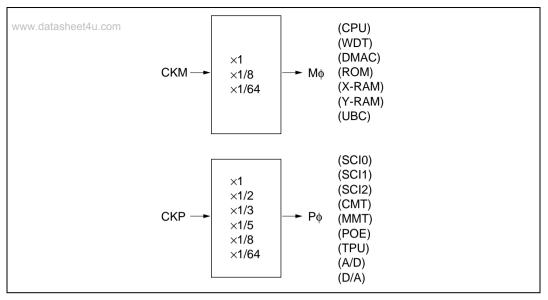

|       | 4.14.1  | Clock Definitions                                                     | 157 |

| www.d | 4.14.2  | Transition to Module Clock Division Function                          | 158 |

|       | 4.14.3  | Exit from Module Clock Division Function                              | 160 |

|       | 4.14.4  | Notes on Use of Module Clock Division Function                        | 160 |

| 4.15  | Note o  | n Initialization                                                      | 161 |

| Secti | ion 5   | Exception Handling                                                    | 163 |

| 5.1   | Overvi  | ew                                                                    | 163 |

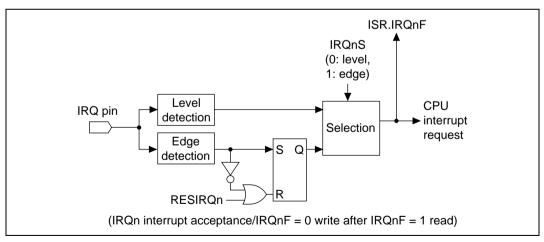

|       | 5.1.1   | Exception Handling Types and Priority                                 | 163 |

|       | 5.1.2   | Timing of Exception Source Detection and Start of Exception Handling  | 164 |

|       | 5.1.3   | Exception Vector Table                                                | 164 |

| 5.2   | Power-  | on Reset                                                              | 167 |

| 5.3   | Addres  | ss Errors                                                             | 168 |

|       | 5.3.1   | Address Error Sources                                                 | 168 |

|       | 5.3.2   | Address Error Exception Handling                                      | 169 |

| 5.4   | Interru | pts                                                                   | 169 |

|       | 5.4.1   | Interrupt Sources                                                     | 169 |

|       | 5.4.2   | Interrupt Priority                                                    | 170 |

|       | 5.4.3   | Interrupt Exception Handling                                          | 170 |

| 5.5   | Instruc | tion Exceptions                                                       | 171 |

|       | 5.5.1   | Types of Instruction Exception                                        | 171 |

|       | 5.5.2   | Trap Instruction                                                      | 171 |

|       | 5.5.3   | Slot Illegal Instructions                                             | 172 |

|       | 5.5.4   | General Illegal Instructions                                          | 172 |

| 5.6   | Cases i | in Which Exceptions Are Not Accepted                                  | 173 |

|       | 5.6.1   | After a Delayed Branch Instruction                                    | 173 |

|       | 5.6.2   | After an Instruction for Which Interruption Is Prohibited             | 173 |

|       | 5.6.3   | Instructions in Repeat Loops                                          | 174 |

| 5.7   | Stack S | Status after Exception Handling                                       | 175 |

| 5.8   | Usage   | Notes                                                                 | 176 |

|       | 5.8.1   | Stack Pointer (SP) Value                                              | 176 |

|       | 5.8.2   | Vector Base Register (VBR) Value                                      | 176 |

|       | 5.8.3   | Address Errors Occurring in Address Error Exception Handling Stacking | 176 |

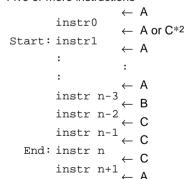

| Secti | ion 6   | Interrupt Controller (INTC)                                           | 177 |

| 6.1   | Overvi  | ew                                                                    | 177 |

|       | 6.1.1   | Features                                                              | 177 |

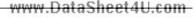

|       | 6.1.2   | Block Diagram                                                         | 178 |

|       | 6.1.3   | Pin Configuration                                                     | 179 |

|       | 6.1.4   | Register Configuration                                                | 179 |

| 6.2   | Interru           | pt Sources                                               | 180 |

|-------|-------------------|----------------------------------------------------------|-----|

|       | 6.2.1             | NMI Interrupt                                            | 180 |

| WWW.  | datashee<br>6.2.2 | User Break Interrupt                                     | 180 |

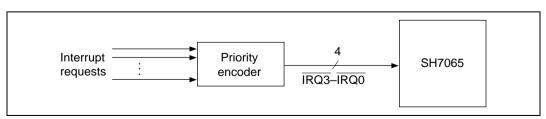

|       | 6.2.3             | External Interrupts                                      | 180 |

|       | 6.2.4             | On-Chip Peripheral Module Interrupts                     | 182 |

|       | 6.2.5             | Interrupt Exception Vectors and Priority Order           | 182 |

| 6.3   | Registe           | er Descriptions                                          | 188 |

|       | 6.3.1             | Interrupt Priority Registers A to L (IPRA to IPRL)       | 188 |

|       | 6.3.2             | Interrupt Control Register 1 (ICR1)                      | 190 |

|       | 6.3.3             | Interrupt Control Register 2 (ICR2)                      | 191 |

|       | 6.3.4             | IRQ Status Register (ISR)                                | 192 |

| 6.4   | Operat            | ion                                                      | 194 |

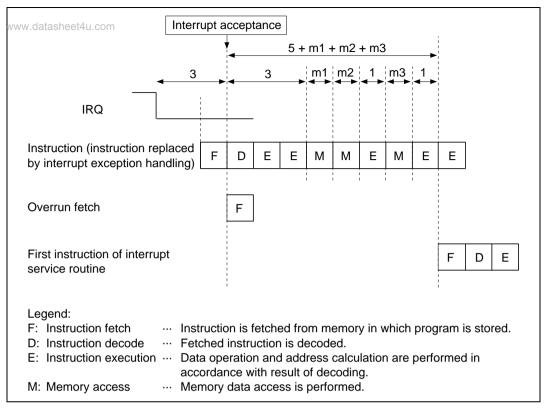

|       | 6.4.1             | Interrupt Operation Sequence                             | 194 |

|       | 6.4.2             | Interrupt Response Time                                  | 196 |

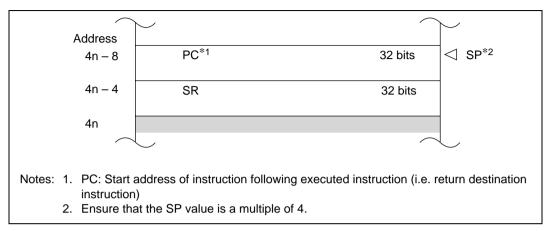

|       | 6.4.3             | Stack Status after Interrupt Exception Handling          | 198 |

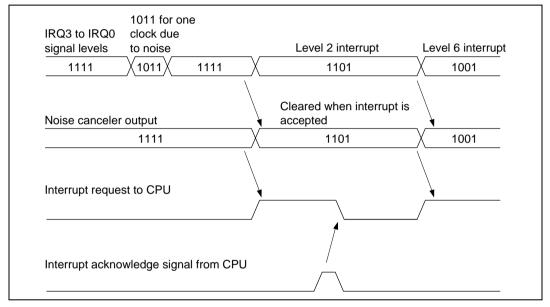

| 6.5   | Sampli            | ng of Signals IRQ3 to IRQ0 in IRL Mode                   | 198 |

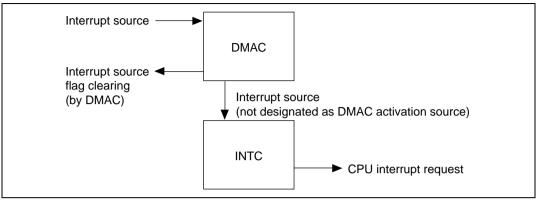

| 6.6   | Data T            | ransfer by Means of Interrupt Request Signal             | 199 |

|       | 6.6.1             | To Designate a Source as a DMAC Activation Source,       |     |

|       |                   | Not a CPU Interrupt Source                               | 200 |

|       | 6.6.2             | To Designate a Source as a CPU Interrupt Source,         |     |

|       |                   | Not a DMAC Activation Source                             | 200 |

| 6.7   | Usage             | Notes                                                    | 201 |

|       | 6.7.1             | IRQ3 to IRQ0 Sampling and Interrupt Source Determination |     |

|       |                   | in IRL Interrupt Mode                                    | 201 |

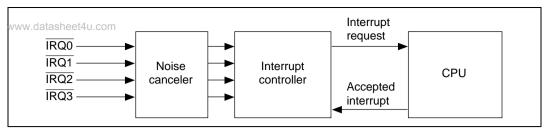

|       | 6.7.2             | IRQ Pin Noise Cancellation Function                      | 201 |

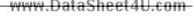

| Secti | on 7              | User Break Controller (UBC)                              | 203 |

| 7.1   | Overvi            | ew                                                       | 203 |

|       | 7.1.1             | Features                                                 | 203 |

|       | 7.1.2             | Block Diagram                                            | 204 |

|       | 7.1.3             | Register Configuration                                   | 205 |

| 7.2   | Registe           | er Descriptions                                          | 205 |

|       | 7.2.1             | User Break Address Register (UBAR)                       | 205 |

|       | 7.2.2             | User Break Address Mask Register (UBAMR)                 | 207 |

|       | 7.2.3             | User Break Bus Cycle Register (UBBR)                     | 208 |

| 7.3   | Operat            | ion                                                      | 211 |

|       | 7.3.1             | User Break Operation Sequence                            | 211 |

|       | 7.3.2             | Instruction Fetch Cycle Break                            | 212 |

|       | 7.3.3             | Data Access Cycle Break                                  | 212 |

|       | 7.3.4             | X Memory Bus or Y Memory Bus Cycle Break                 |     |

|       | 7.3.5             | Program Counter (PC) Value Saved                         | 213 |

|       |                   |                                                          |     |

| 7.4    | Examp             | ples of Use                                   | 214 |

|--------|-------------------|-----------------------------------------------|-----|

| 7.5    | Usage             | Notes                                         | 217 |

| www.da | atasheet<br>7.5.1 | Changes to UBC Register Settings              | 217 |

|        | 7.5.2             | Repeat Condition Breaks                       | 217 |

|        |                   |                                               |     |

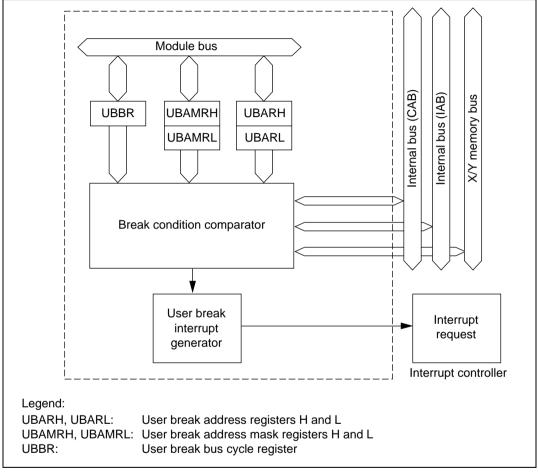

| Secti  | ion 8             | Bus State Controller (BSC)                    | 219 |

| 8.1    | Overv             | iew                                           | 219 |

|        | 8.1.1             | Features                                      | 219 |

|        | 8.1.2             | Block Diagram                                 | 221 |

|        | 8.1.3             | Pin Configuration                             | 222 |

|        | 8.1.4             | Register Configuration                        | 224 |

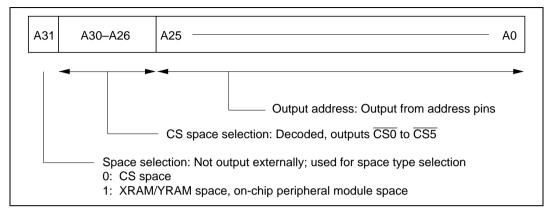

|        | 8.1.5             | Address Format                                | 225 |

| 8.2    | Regist            | er Descriptions                               | 228 |

|        | 8.2.1             | Bus Control Register (BCR)                    | 228 |

|        | 8.2.2             | Area Control Registers 1 (ACR1_0 to ACR1_5)   | 229 |

|        | 8.2.3             | Wait Control Registers (WCR_0 to WCR_3)       | 233 |

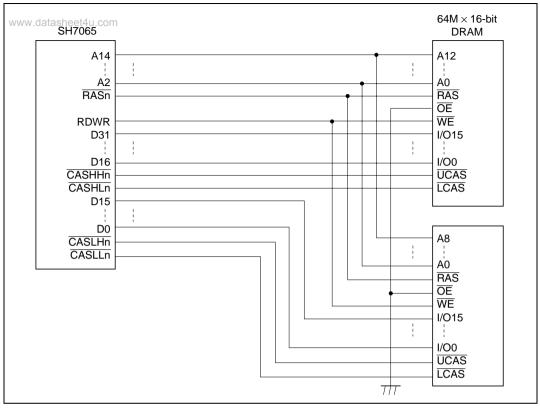

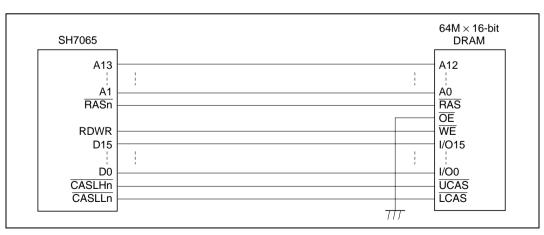

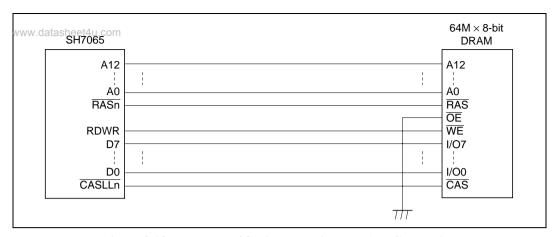

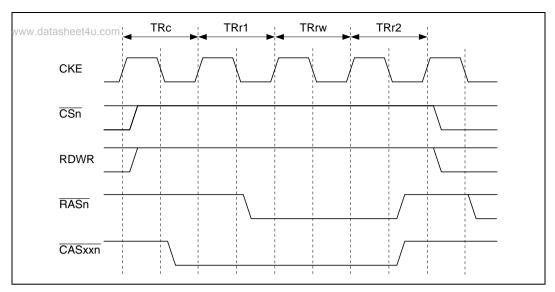

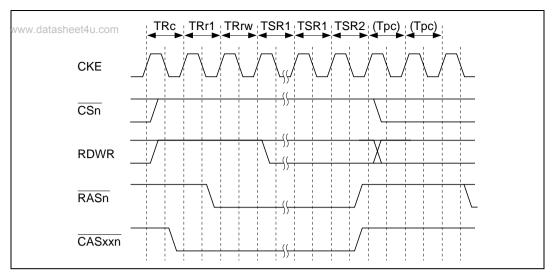

|        | 8.2.4             | DRAM Control Register 1 (DCR1)                | 235 |

|        | 8.2.5             | DRAM Control Register 2 (DCR2)                | 237 |

|        | 8.2.6             | DRAM Control Register 3 (DCR3)                | 240 |

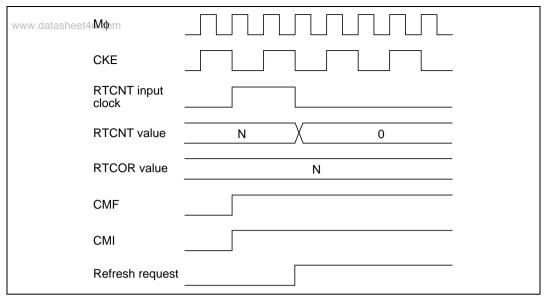

|        | 8.2.7             | Refresh Timer Control/Status Register (RTCSR) |     |

|        | 8.2.8             | Refresh Timer Counter (RTCNT)                 |     |

|        | 8.2.9             | Refresh Time Constant Register (RTCOR)        |     |

|        | 8.2.10            | - · · · · · · · · · · · · · · · · · · ·       |     |

| 8.3    | Opera             | tion                                          |     |

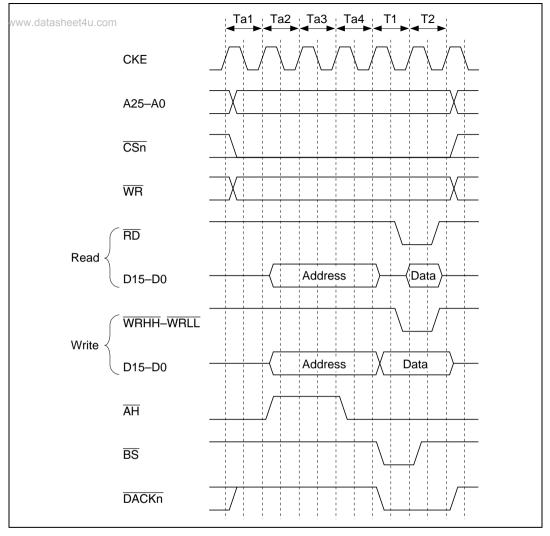

|        | 8.3.1             | Endian/Access Size and Data Alignment         |     |

|        | 8.3.2             | Areas                                         |     |

|        | 8.3.3             | Normal Space Access                           |     |

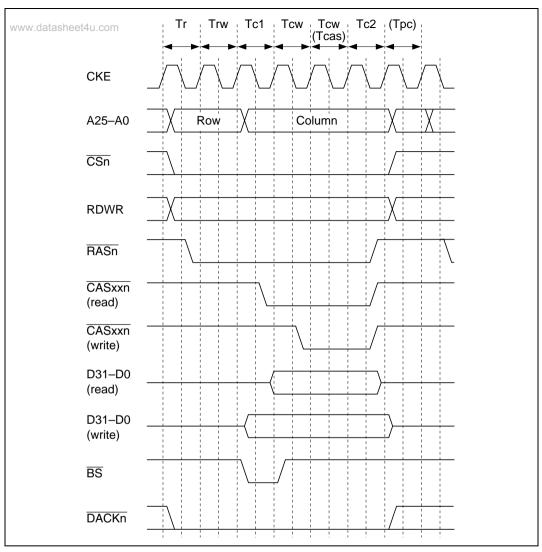

|        | 8.3.4             | DRAM Interface                                |     |

|        | 8.3.5             | Multiplexed Address/Data I/O Interface        |     |

|        | 8.3.6             | Waits between Access Cycles                   |     |

|        | 8.3.7             | Bus Arbitration.                              |     |

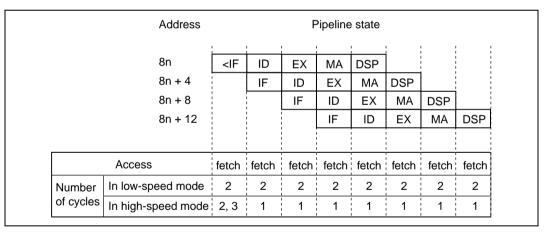

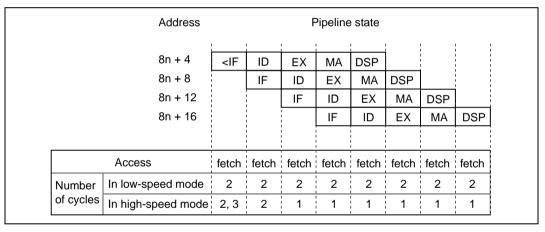

| 8.4    | Numb              | er of Access Cycles (SH7065A)                 |     |

| 8.5    |                   | Notes                                         |     |

|        | C                 |                                               |     |

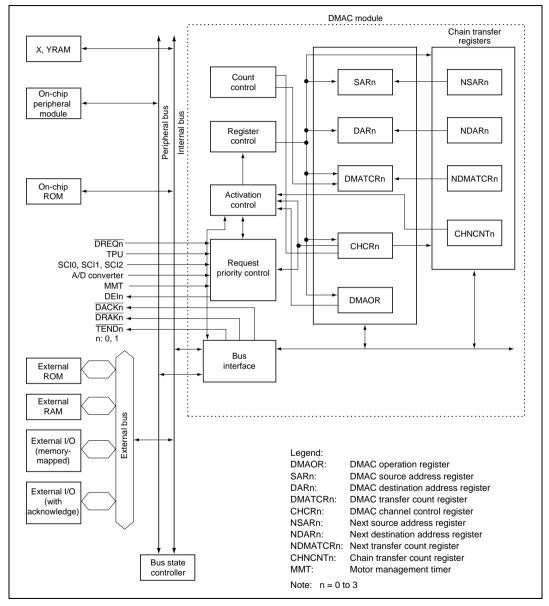

| Secti  | ion 9             | Direct Memory Access Controller (DMAC)        | 305 |

| 9.1    |                   | iew                                           |     |

|        | 9.1.1             | Features                                      |     |

|        | 9.1.2             | Block Diagram                                 |     |

|        | 9.1.3             | Pin Configuration                             |     |

|        | 9.1.4             | Register Configuration                        |     |

| 9.2    |                   | er Descriptions                               |     |

|        | - 0               | 1                                             |     |

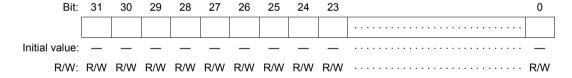

|      | 9.2.1             | DMA Source Address Registers 0 to 3 (SAR0 to SAR3)              | 311 |

|------|-------------------|-----------------------------------------------------------------|-----|

|      | 9.2.2             | DMA Destination Address Registers 0 to 3 (DAR0 to DAR3)         |     |

| www. | datashee<br>9.2.3 | DMA Transfer Count Registers 0 to 3 (DMATCR0 to DMATCR3)        | 312 |

|      | 9.2.4             | DMA Channel Control Registers 0 to 3 (CHCR0 to CHCR3)           | 313 |

|      | 9.2.5             | Next Source Address Registers 0 to 3 (NSAR0 to NSAR3)           | 320 |

|      | 9.2.6             | Next Destination Address Registers 0 to 3 (NDAR0 to NDAR3)      | 321 |

|      | 9.2.7             | Next Transfer Count Registers 0 to 3 (NDMATCR0 to NDMATCR3)     | 321 |

|      | 9.2.8             | Chain Transfer Count Registers 0 to 3 (CHNCNT0 to CHNCNT3)      | 322 |

|      | 9.2.9             | DMA Operation Register (DMAOR)                                  | 322 |

| 9.3  | Operat            | ion                                                             | 324 |

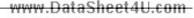

|      | 9.3.1             | DMA Transfer Procedure                                          | 325 |

|      | 9.3.2             | DMA Transfer Requests                                           | 327 |

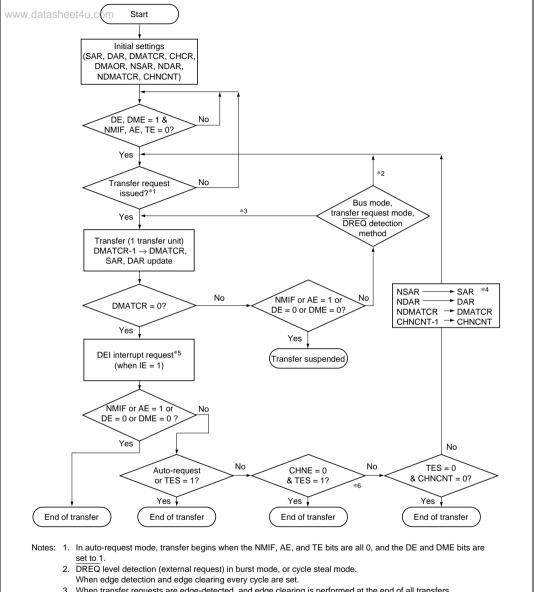

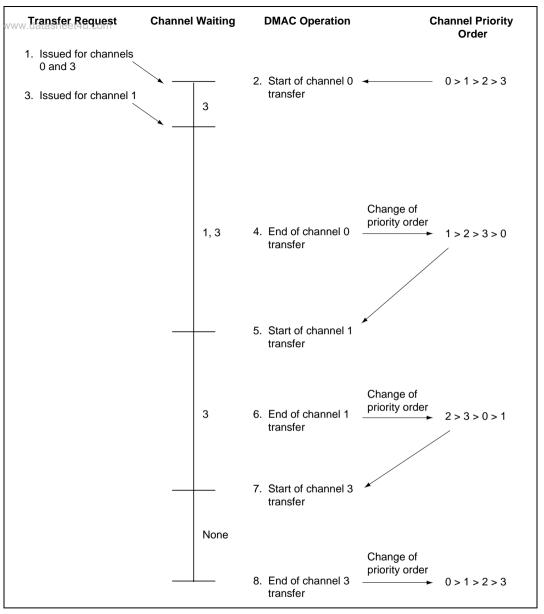

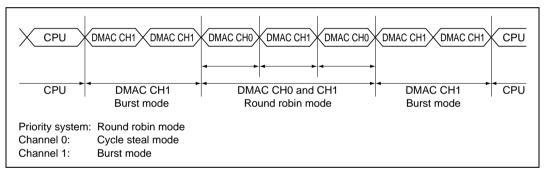

|      | 9.3.3             | Channel Priorities                                              | 330 |

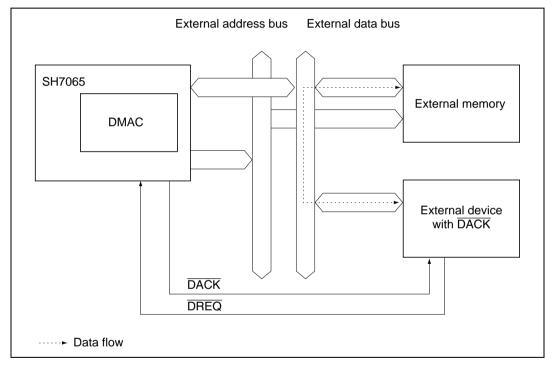

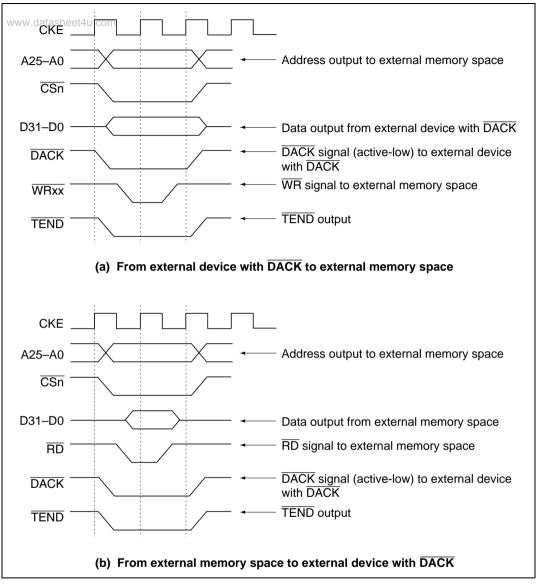

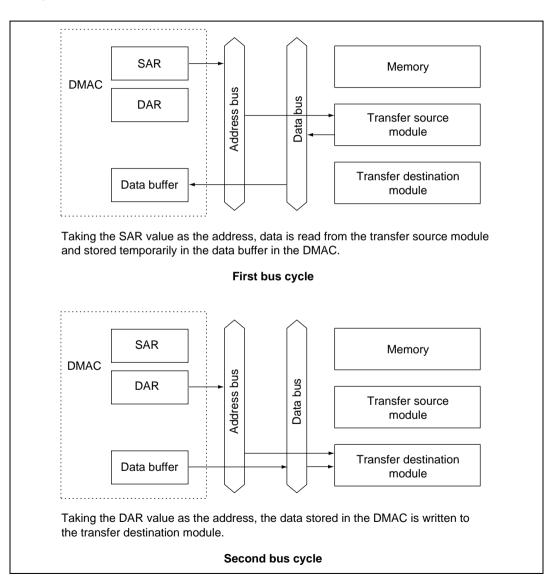

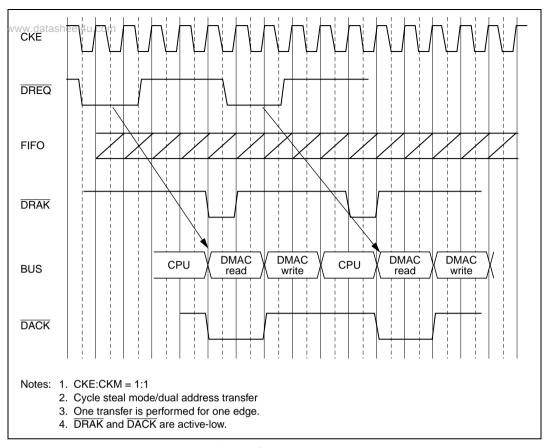

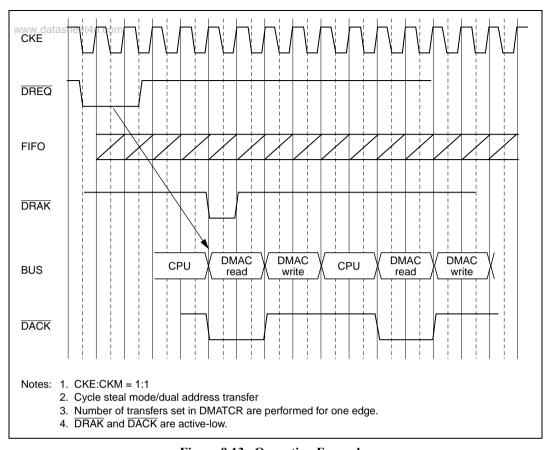

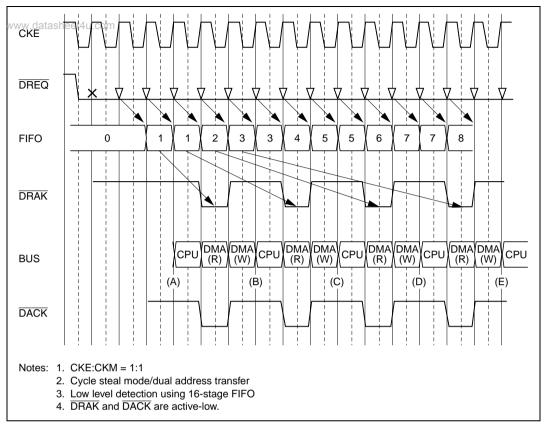

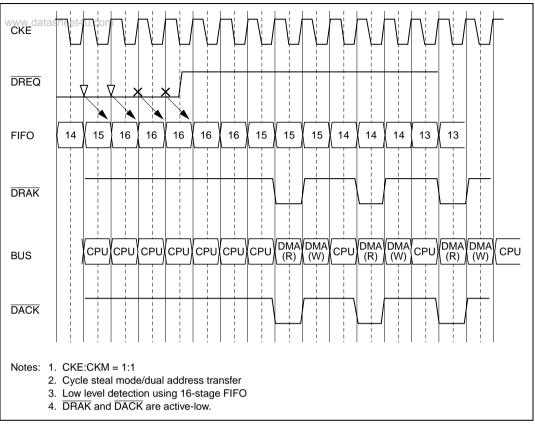

|      | 9.3.4             | Types of DMA Transfer                                           | 334 |

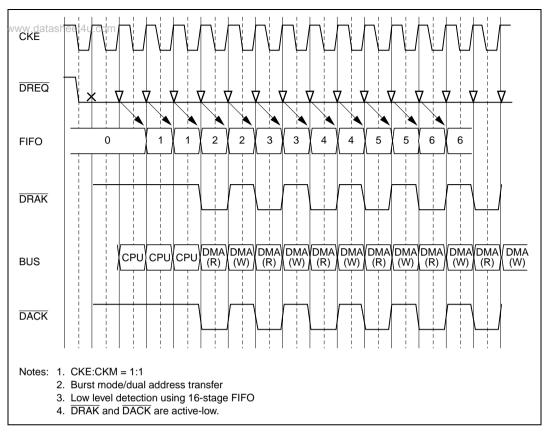

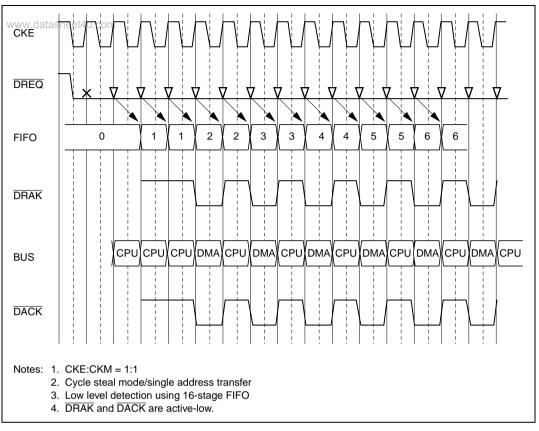

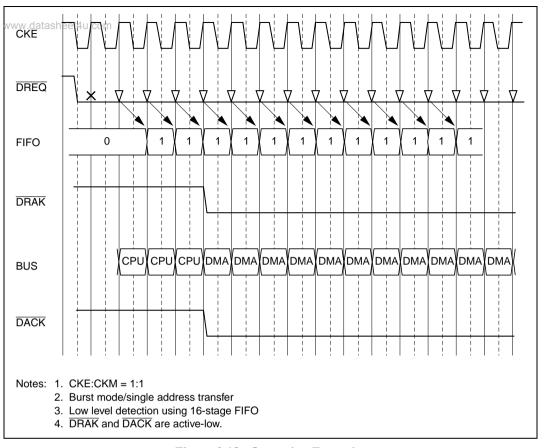

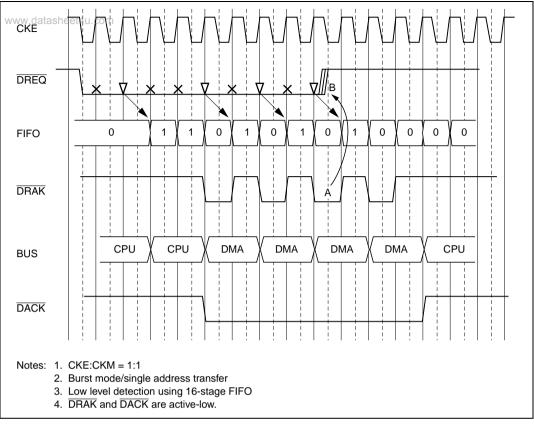

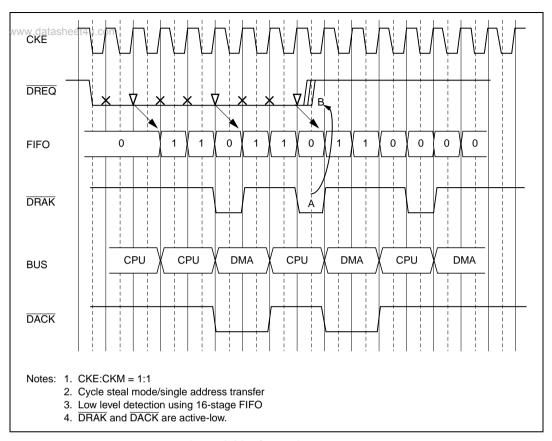

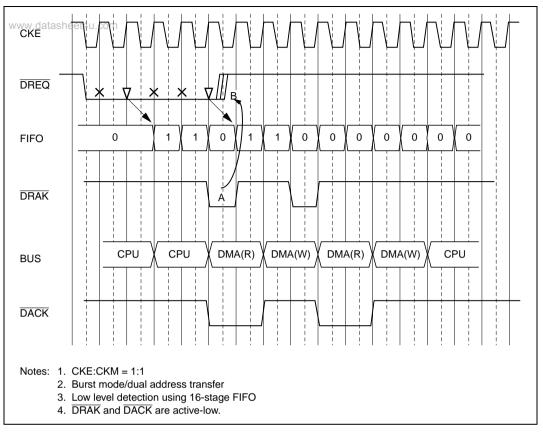

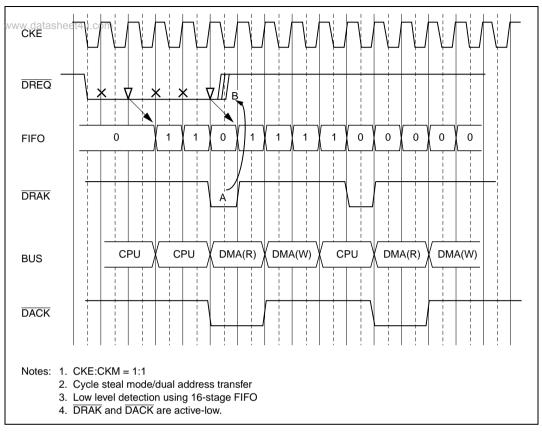

|      | 9.3.5             | Number of Bus Cycle States and DREQ Pin Sampling Timing         | 342 |

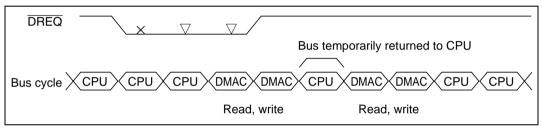

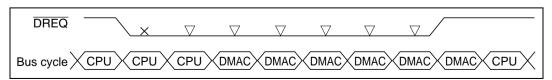

|      | 9.3.6             | Parallel Operation of DMA and CPU                               | 356 |

|      | 9.3.7             | DMA Transfer When External Bus Is Released                      | 356 |

|      | 9.3.8             | Chain Transfer                                                  | 358 |

| 9.4  | Examp             | le of Use                                                       | 360 |

|      | 9.4.1             | Example of DMA Transfer between On-Chip SCI and External Memory | 360 |

| 9.5  | Usage             | Notes                                                           | 360 |

| 9.6  | DMAC              | Restrictions                                                    | 362 |

|      | 9.6.1             | TEND Output                                                     | 362 |

|      | 9.6.2             | Notes on Suspension of Transfer                                 | 362 |

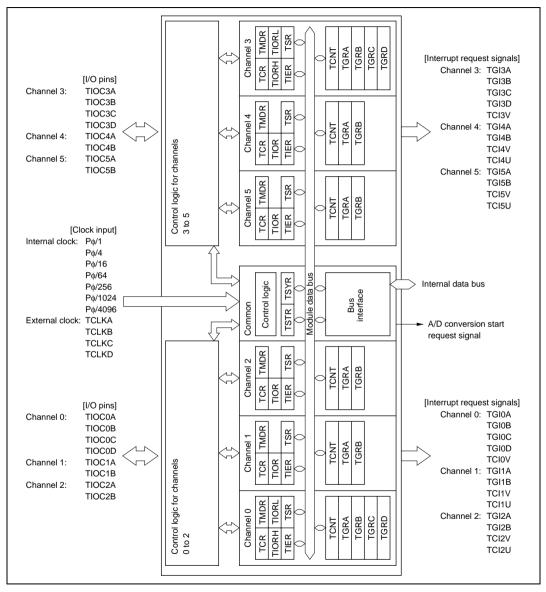

| Sect | ion 10            | 16-Bit Timer Pulse Unit (TPU)                                   | 365 |

| 10.1 |                   | ew                                                              |     |

|      | 10.1.1            | Features                                                        | 365 |

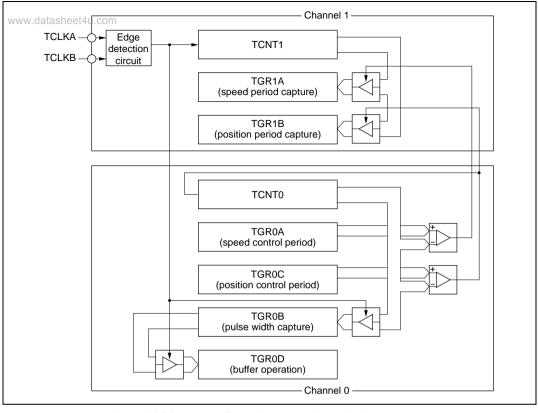

|      | 10.1.2            | Block Diagram                                                   | 369 |

|      | 10.1.3            | Pin Configuration                                               | 370 |

|      | 10.1.4            | Register Configuration                                          | 372 |

| 10.2 | Registe           | er Descriptions                                                 | 374 |

|      | 10.2.1            | Timer Control Registers (TCR)                                   | 374 |

|      | 10.2.2            | Timer Mode Registers (TMDR)                                     | 379 |

|      | 10.2.3            | Timer I/O Control Registers (TIOR)                              | 381 |

|      | 10.2.4            | Timer Interrupt Enable Registers (TIER)                         | 398 |

|      | 10.2.5            | Timer Status Registers (TSR)                                    | 400 |

|      | 10.2.6            | Timer Counters (TCNT)                                           |     |

|      | 10.2.7            | Timer General Registers (TGR)                                   |     |

|      | 10.2.8            | Timer Start Register (TSTR)                                     |     |

|      | 10.2.9            | Timer Sync Register (TSYR)                                      | 405 |

|      |                   |                                                                 |     |

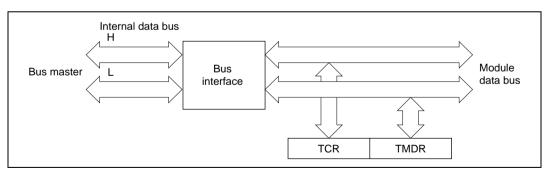

| 10.3  | Interfac | ce to Bus Master                     | . 406 |

|-------|----------|--------------------------------------|-------|

|       | 10.3.1   | 16-Bit Registers                     | . 406 |

| www.d | 10.3.2   | 8-Bit Registers                      | . 406 |

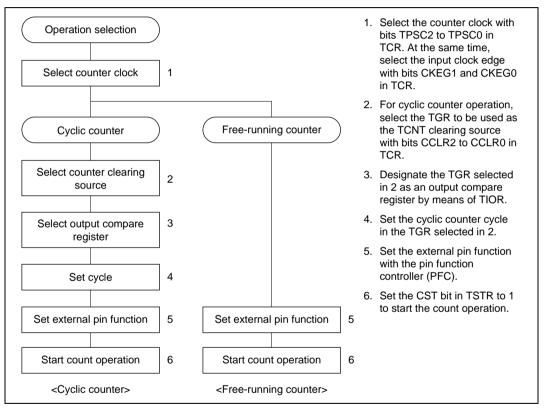

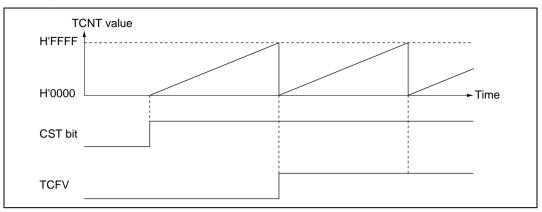

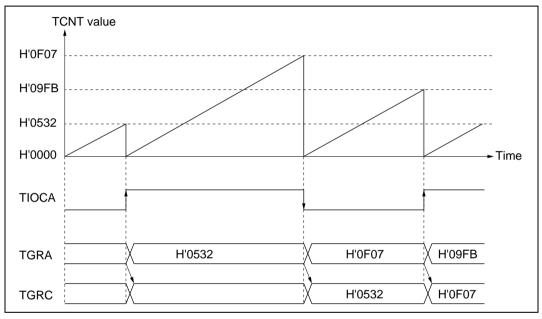

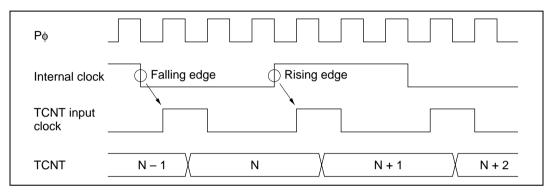

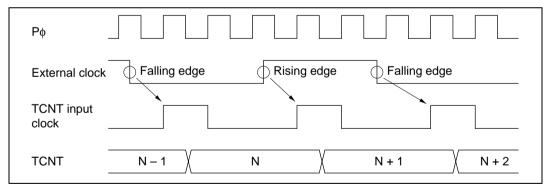

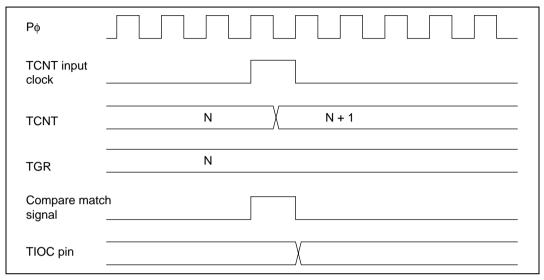

| 10.4  | Operat   | ion                                  | . 408 |

|       | 10.4.1   | Overview                             | . 408 |

|       | 10.4.2   | Basic Functions                      | . 409 |

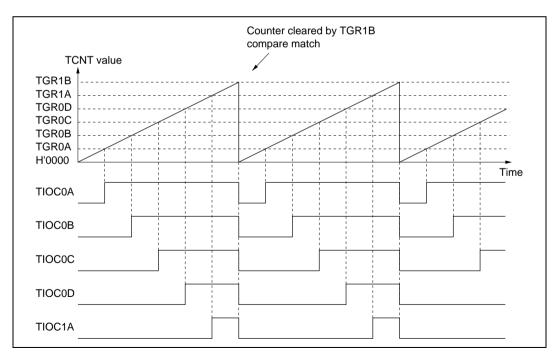

|       | 10.4.3   | Synchronous Operation                | . 414 |

|       | 10.4.4   | Buffer Operation                     | . 417 |

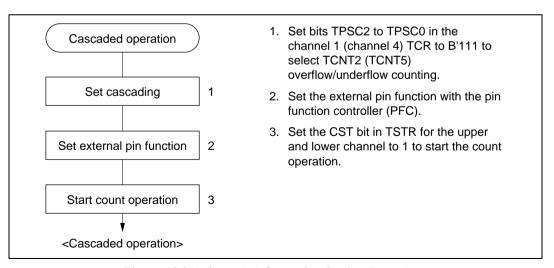

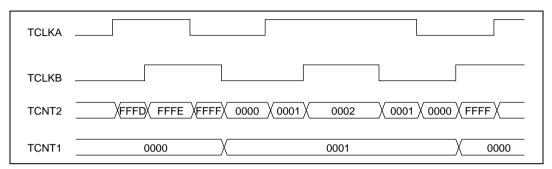

|       | 10.4.5   | Cascaded Operation                   | . 421 |

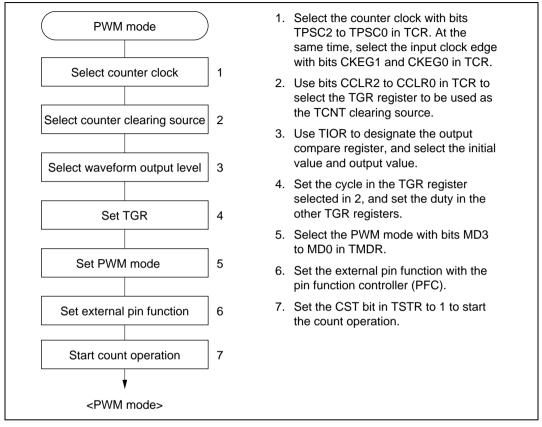

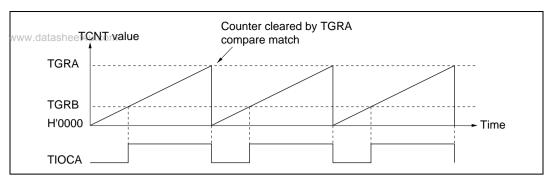

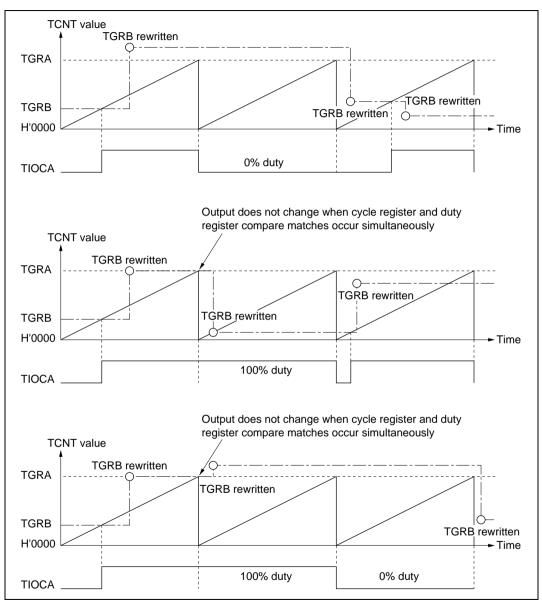

|       | 10.4.6   | PWM Modes                            | . 422 |

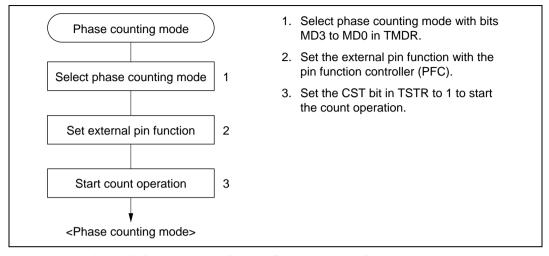

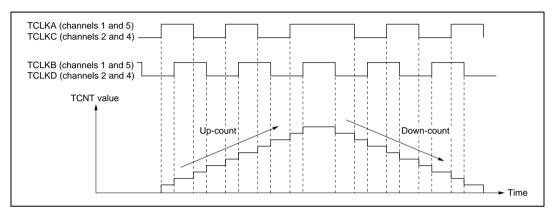

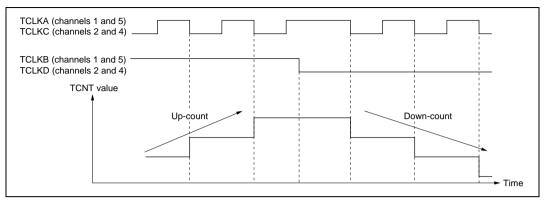

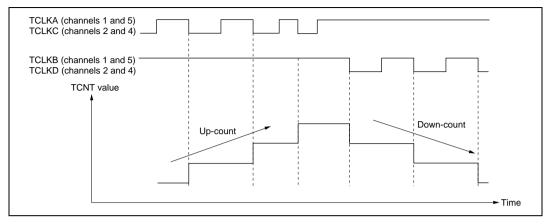

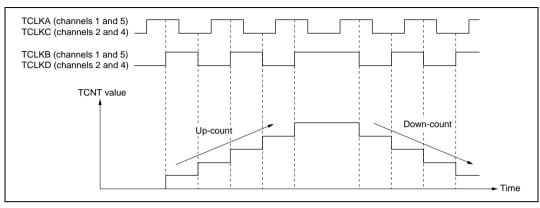

|       | 10.4.7   | Phase Counting Mode                  | . 427 |

| 10.5  | Interru  | pts                                  | . 434 |

|       | 10.5.1   | Interrupt Sources and Priorities     | . 434 |

|       | 10.5.2   | DMAC Activation                      | . 436 |

|       | 10.5.3   | A/D Converter Activation             | . 436 |

| 10.6  | Operat   | ion Timing                           | . 437 |

|       | 10.6.1   | Input/Output Timing                  | . 437 |

|       |          | Interrupt Signal Timing              |       |

| 10.7  | Usage    | Notes                                | . 445 |

| ~     |          |                                      |       |

|       |          | Motor Management Timer (MMT)         |       |

| 11.1  |          | ew                                   |       |

|       |          | Features                             |       |

|       |          | Block Diagram                        |       |

|       |          | Pin Configuration                    |       |

|       |          | Register Configuration               |       |

| 11.2  | _        | er Descriptions                      |       |

|       |          | Timer Mode Register (TMDR)           |       |

|       |          | Timer Control Register (TCNR)        |       |

|       |          | Timer Status Register (TSR)          |       |

|       | 11.2.4   | Timer Counter (TCNT)                 | . 463 |

|       | 11.2.5   | Timer Buffer Registers (TBR)         | . 463 |

|       | 11.2.6   | Timer General Registers (TGR)        | . 464 |

|       |          | Timer Dead Time Counters (TDCNT)     |       |

|       | 11.2.8   | Timer Dead Time Data Register (TDDR) | . 465 |

|       | 11.2.9   | Timer Period Buffer Register (TPBR)  | . 465 |

|       | 11.2.10  | Timer Period Data Register (TPDR)    | . 466 |

| 11.3  | Operat   | ion                                  | . 466 |

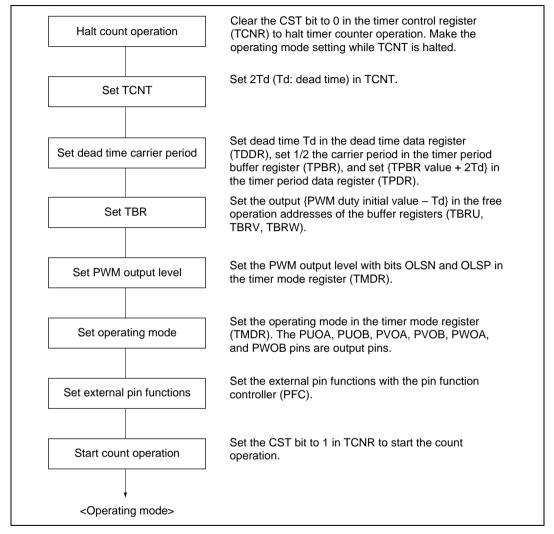

|       | 11.3.1   | Sample Setting Procedure             |       |

|       | 11.3.2   | Overview of Operation                | . 468 |

|       | 11.3.3   | Output Protection Functions          | . 476 |

|       |          |                                      |       |

| 11.4  | Interru            | pts                                                       | 476 |

|-------|--------------------|-----------------------------------------------------------|-----|

|       | 11.4.1             | Compare Match Interrupts                                  | 476 |

| WWW.  | datashee<br>11.4.2 | DMA Controller Activation                                 | 476 |

|       | 11.4.3             | A/D Converter Activation                                  | 477 |

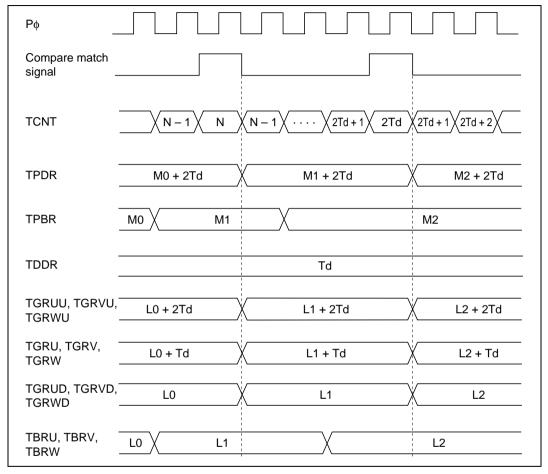

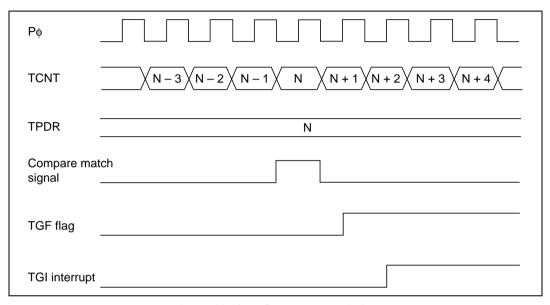

| 11.5  | Operat             | ion Timing                                                | 477 |

|       | _                  | Input/Output Timing                                       |     |

|       | 11.5.2             | Interrupt Signal Timing                                   | 480 |

| 11.6  | Usage              | Notes                                                     | 482 |

| 11.7  | Port O             | utput Enable (POE)                                        | 486 |

|       | 11.7.1             | Overview                                                  | 486 |

|       | 11.7.2             | Register Description                                      | 488 |

|       | 11.7.3             | Operation                                                 | 491 |

| Secti | ion 12             | Compare Match Timer (CMT)                                 | 493 |

| 12.1  |                    | ew                                                        |     |

|       | 12.1.1             | Features                                                  | 493 |

|       | 12.1.2             | Block Diagram                                             | 494 |

|       |                    | Register Configuration                                    |     |

| 12.2  | Registe            | er Descriptions                                           | 496 |

|       | 12.2.1             | Compare Match Timer Start Register (CMSTR)                | 496 |

|       | 12.2.2             | Compare Match Timer Control/Status Registers 0 and 1      |     |

|       |                    | (CMCSR0, CMCSR1)                                          | 497 |

|       | 12.2.3             | Compare Match Counters 0 and 1 (CMCNT0, CMCNT1)           | 498 |

|       | 12.2.4             | Compare Match Constant Registers 0 and 1 (CMCOR0, CMCOR1) | 499 |

| 12.3  | Operat             | ion                                                       | 499 |

|       | 12.3.1             | Cyclic Count Operation                                    | 499 |

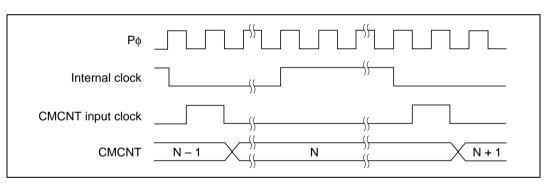

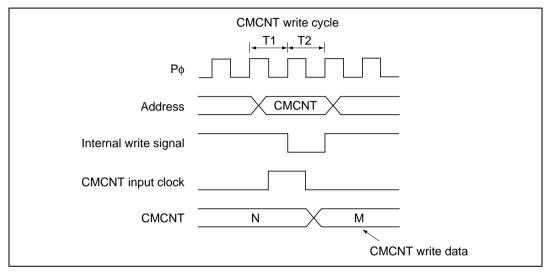

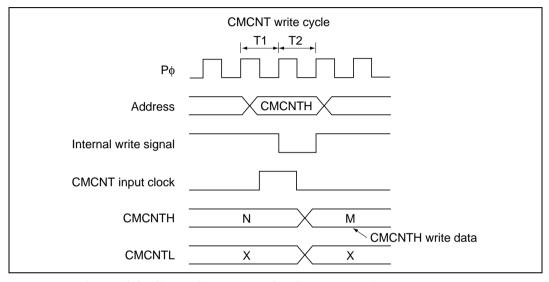

|       | 12.3.2             | CMCNT Count Timing                                        | 500 |

| 12.4  | Interru            | pts                                                       | 501 |

|       | 12.4.1             | Interrupt Sources                                         | 501 |

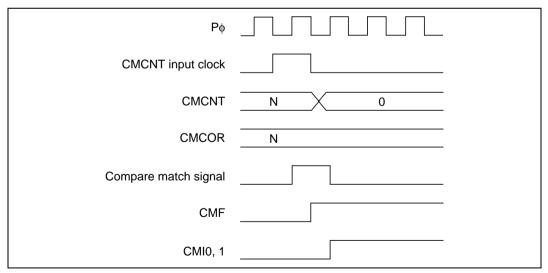

|       | 12.4.2             | Timing of Compare Match Flag Setting                      | 501 |

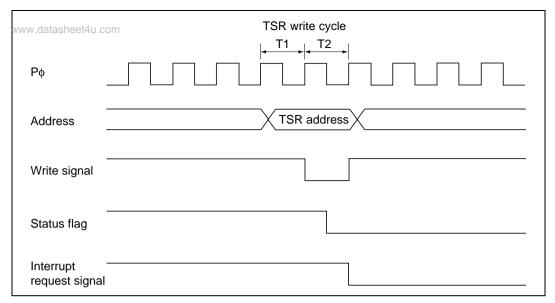

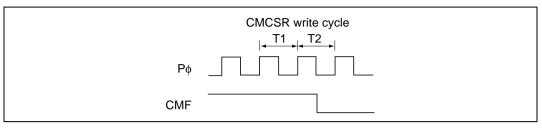

|       | 12.4.3             | Timing of Compare Match Flag Clearing                     | 502 |

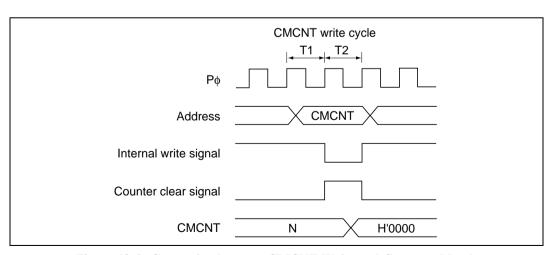

| 12.5  | Usage              | Notes                                                     | 502 |

| Secti | ion 13             | Watchdog Timer                                            | 505 |

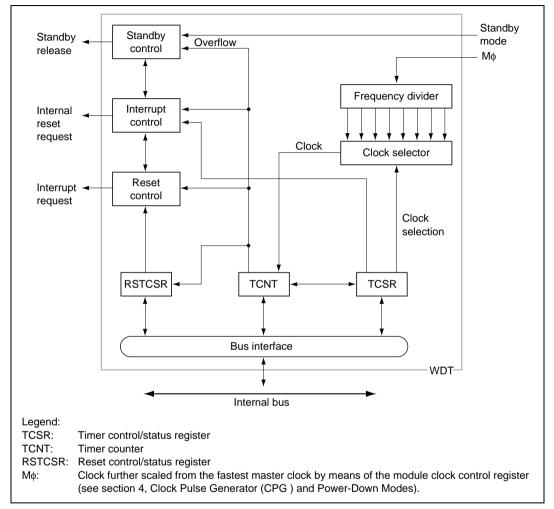

|       |                    | ew                                                        |     |

|       | 13.1.1             | Features                                                  | 505 |

|       | 13.1.2             | Block Diagram                                             | 506 |

|       | 13.1.3             | Pin Configuration                                         | 507 |

|       | 13.1.4             | Register Configuration                                    | 507 |

| 13.2  |                    | er Descriptions                                           |     |

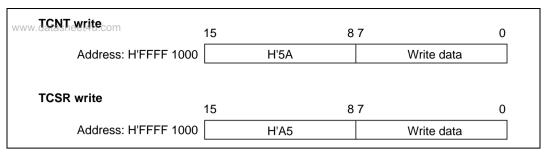

|       |                    | Timer Counter (TCNT)                                      |     |

|       |                    | Datachast                                                 | 411 |

|        | 13.2.2              | Timer Control/Status Register (TCSR)          | 508 |

|--------|---------------------|-----------------------------------------------|-----|

|        | 13.2.3              | Reset Control/Status Register (RSTCSR)        | 510 |

| www.da | atasheet4<br>13.2.4 | Notes on Register Access                      | 511 |

| 13.3   | Operati             | on                                            | 513 |

|        | 13.3.1              | Operation in Watchdog Timer Mode              | 513 |

|        |                     | Operation in Interval Timer Mode              |     |

|        | 13.3.3              | Operation When Clearing Software Standby Mode | 515 |

| Secti  | ion 14              | Serial Communication Interface (SCI)          | 517 |

| 14.1   | Overvi              | ew                                            | 517 |

|        | 14.1.1              | Features                                      | 517 |

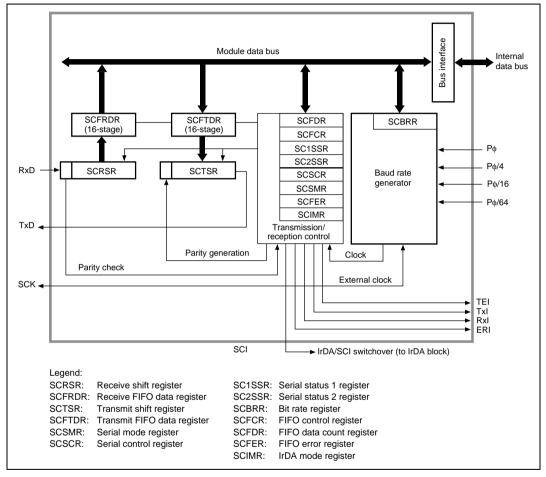

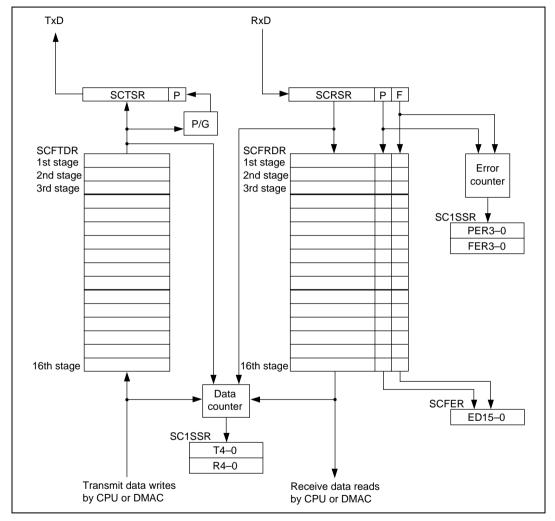

|        | 14.1.2              | Block Diagrams.                               | 519 |

|        | 14.1.3              | Pin Configuration                             | 520 |

|        | 14.1.4              | Register Configuration                        | 521 |

| 14.2   | Registe             | er Descriptions                               | 522 |

|        | 14.2.1              | Receive Shift Register (SCRSR)                | 522 |

|        | 14.2.2              | Receive FIFO Data Register (SCFRDR)           | 523 |

|        | 14.2.3              | Transmit Shift Register (SCTSR)               | 523 |

|        | 14.2.4              | Transmit FIFO Data Register (SCFTDR)          | 524 |

|        | 14.2.5              | Serial Mode Register (SCSMR)                  | 524 |

|        | 14.2.6              | Serial Control Register (SCSCR)               | 527 |

|        | 14.2.7              | Serial Status 1 Register (SC1SSR)             | 532 |

|        | 14.2.8              | Serial Status 2 Register (SC2SSR)             | 537 |

|        | 14.2.9              | Bit Rate Register (SCBRR)                     | 540 |

|        | 14.2.10             | FIFO Control Register (SCFCR)                 | 549 |

|        | 14.2.11             | FIFO Data Count Register (SCFDR)              | 551 |

|        | 14.2.12             | 2 FIFO Error Register (SCFER)                 | 552 |

|        | 14.2.13             | FIDA Mode Register (SCIMR)                    | 553 |

| 14.3   | Operati             | ion                                           | 554 |

|        | 14.3.1              | Overview                                      | 554 |

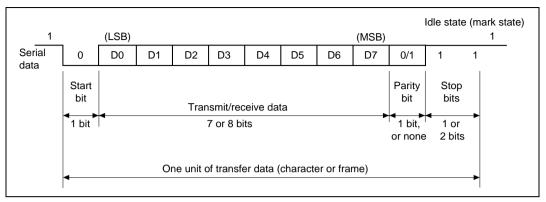

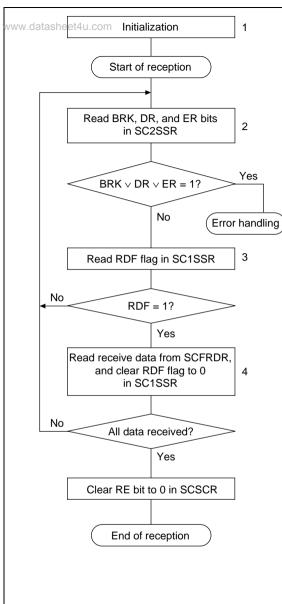

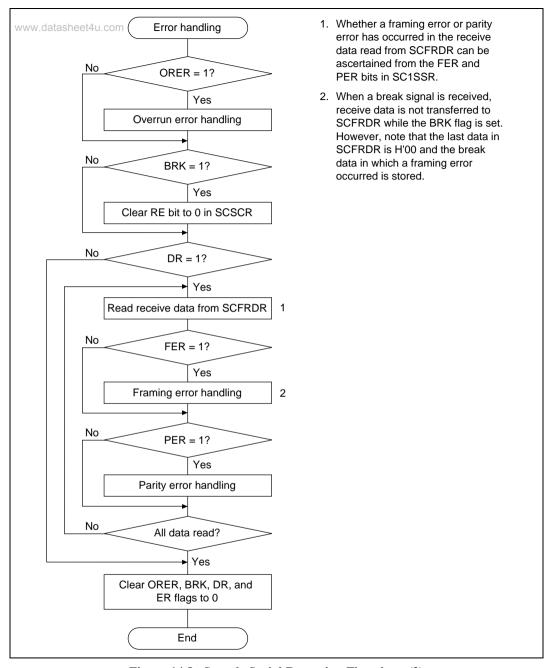

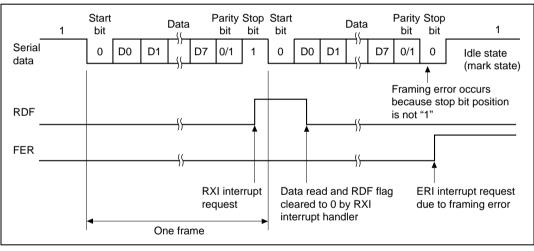

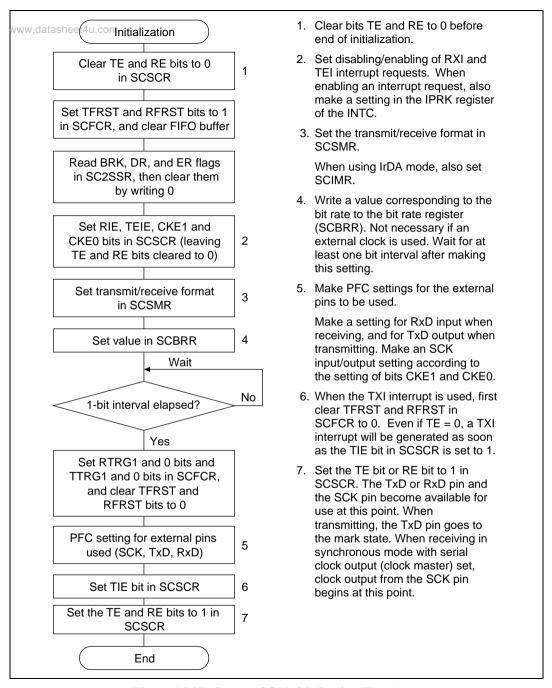

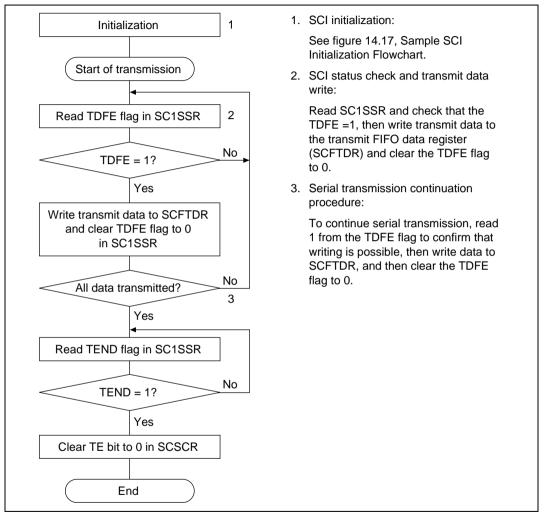

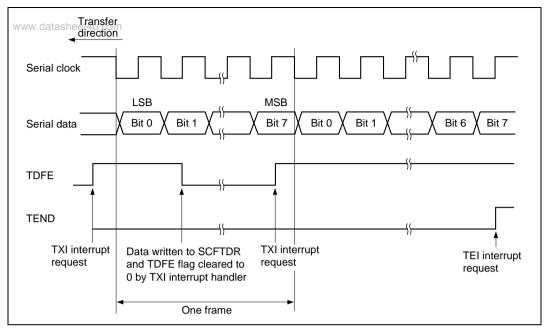

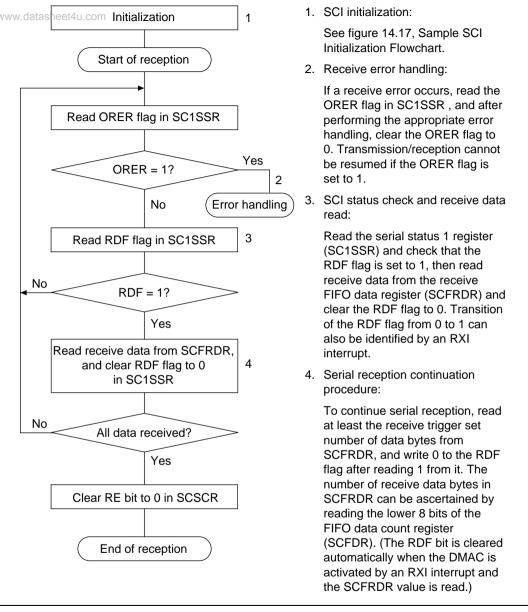

|        | 14.3.2              | Operation in Asynchronous Mode                | 557 |

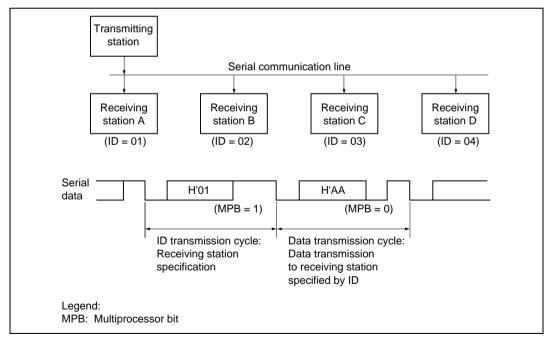

|        |                     | Multiprocessor Communication Function         |     |

|        |                     | Operation in Synchronous Mode                 |     |

|        | 14.3.5              | Use of Transmit/Receive FIFO Buffers          | 587 |

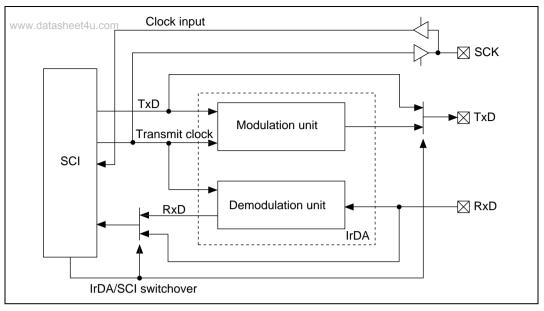

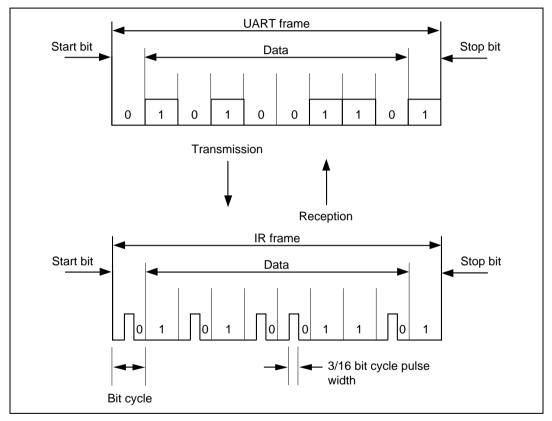

|        | 14.3.6              | Operation in IrDA Mode                        | 590 |

| 14.4   | SCI Int             | errupt Sources and the DMAC                   | 593 |

| 14.5   | Usage 1             | Notes                                         | 594 |

| Secti  | ion 15              | A/D Converter                                 | 601 |

| 15.1   | Overvi              | ew                                            | 601 |

|        | 15.1.1              | Features                                      | 601 |

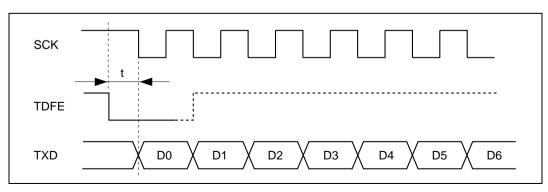

|      | 15.1.2             | Block Diagram                                                  | . 601 |

|------|--------------------|----------------------------------------------------------------|-------|

|      | 15.1.3             | Pin Configuration                                              | . 603 |

| WWW. | datashee<br>15.1.4 | Register Configuration                                         | . 604 |

| 15.2 | Registe            | er Descriptions                                                | . 605 |

|      | 15.2.1             | A/D Data Registers A to D (ADDRA0 to ADDRD0, ADDRA1 to ADDRD1) | . 605 |

|      | 15.2.2             | A/D Control/Status Registers (ADCSR0, ADCSR1)                  | . 606 |

|      | 15.2.3             | A/D Control Registers (ADCR0, ADCR1)                           | . 608 |

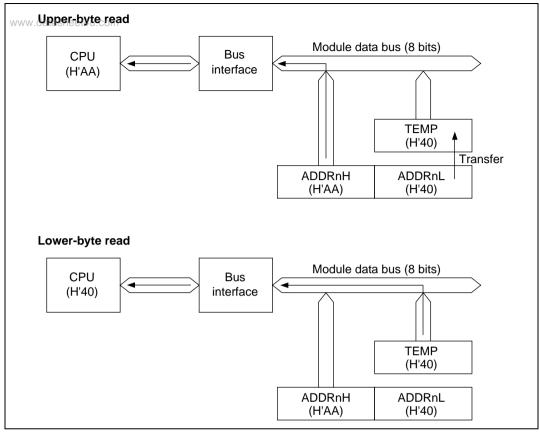

| 15.3 | CPU I              | nterface                                                       | . 609 |

| 15.4 | Operat             | ion                                                            | . 611 |

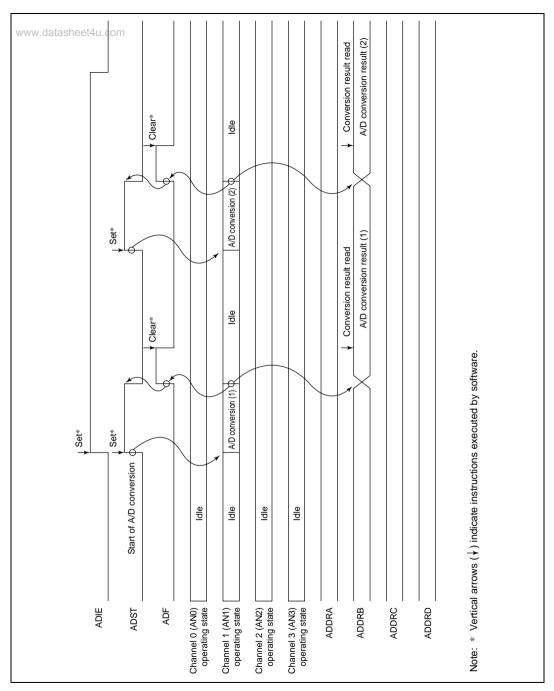

|      | 15.4.1             | Single Mode (MULTI = 0)                                        | . 611 |

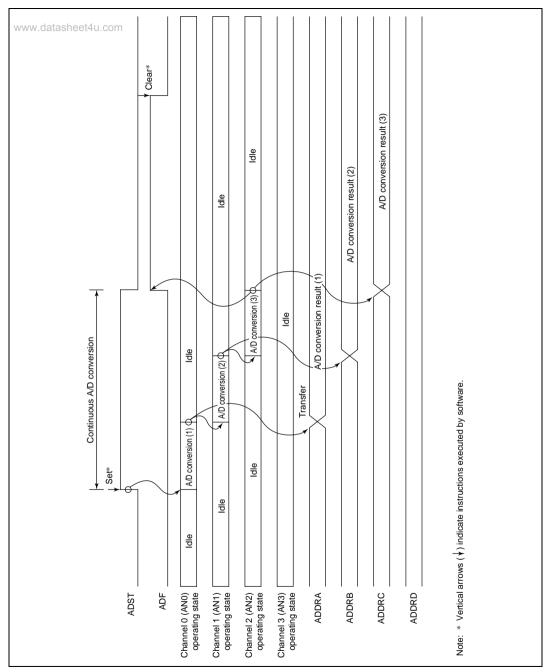

|      | 15.4.2             | Multi Mode                                                     | . 613 |

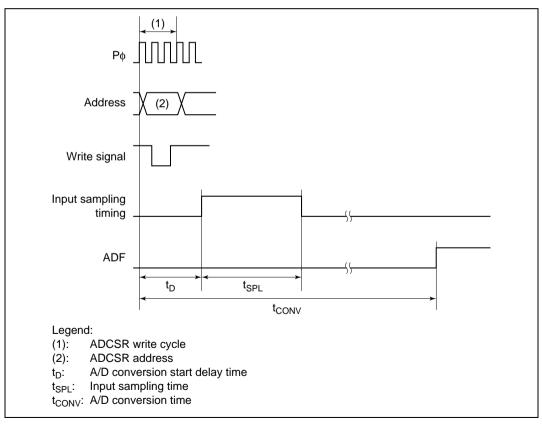

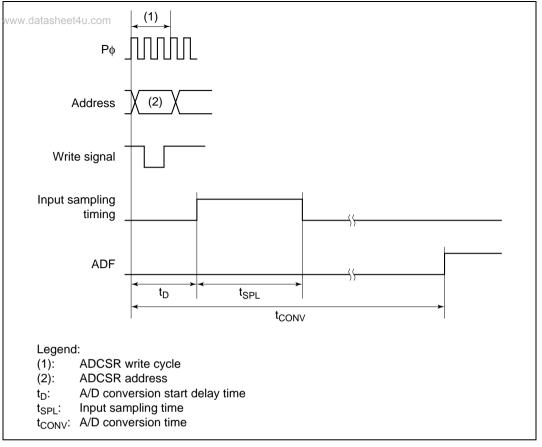

|      | 15.4.3             | Input Sampling and A/D Conversion Time                         | . 615 |

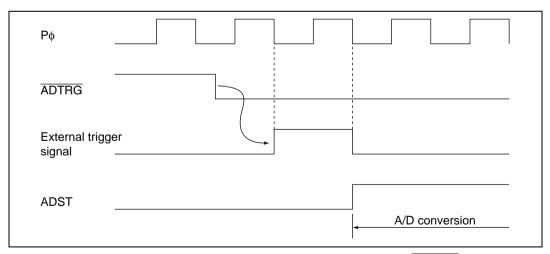

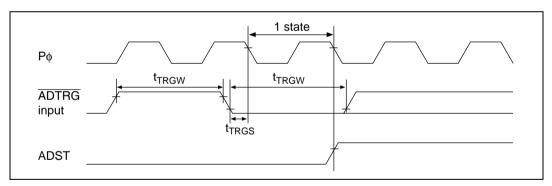

|      | 15.4.4             | External Trigger Input Timing                                  | . 616 |

| 15.5 | Interru            | pt Sources and DMA Transfer Requests                           | . 617 |

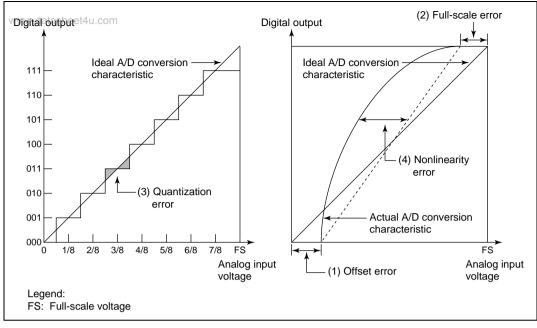

| 15.6 | A/D C              | onversion Accuracy Definitions                                 | . 617 |

| 15.7 | Usage              | Notes                                                          | . 618 |

|      | 15.7.1             | Analog Voltage Settings                                        | . 618 |

|      | 15.7.2             | Handling of Analog Input Pins                                  | . 619 |

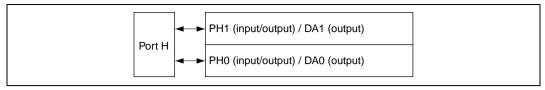

|      | 15.7.3             | Note on PH0 and PH1 Output                                     | . 620 |

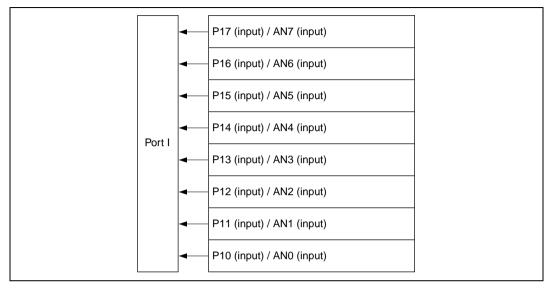

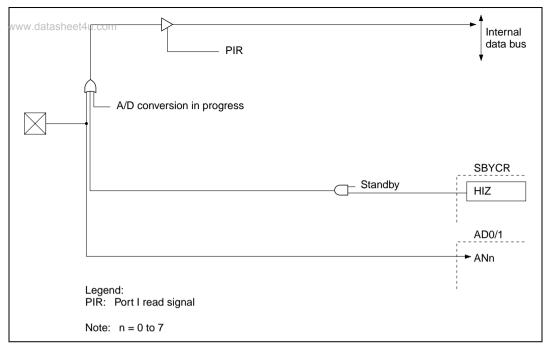

|      | 15.7.4             | Port I PFC Settings                                            | . 620 |

|      | 15.7.5             | Simultaneous A/D and D/A Conversion                            | . 621 |

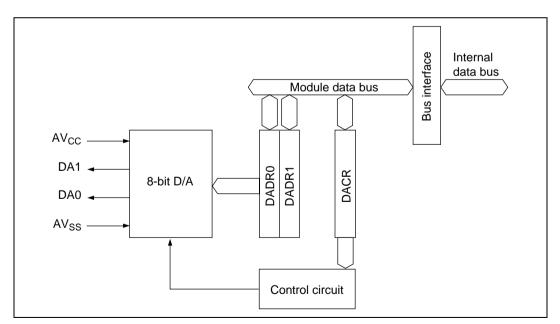

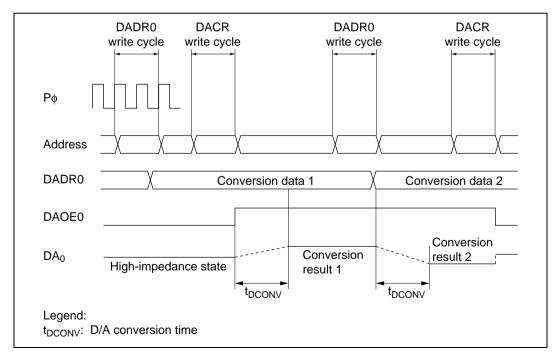

| Sect | ion 16             | D/A Converter                                                  | . 623 |

| 16.1 |                    | ew                                                             |       |

|      |                    | Features                                                       |       |

|      |                    | Block Diagram                                                  |       |

|      |                    | Pin Configuration                                              |       |

|      |                    | Register Configuration                                         |       |

| 16.2 |                    | er Descriptions                                                |       |

|      | _                  | D/A Data Registers 0 and 1 (DADR0, DADR1)                      |       |

|      |                    | D/A Control Register (DACR)                                    |       |

| 16.3 | Operat             | ion                                                            | . 627 |

| 16.4 | Usage              | Note                                                           | . 628 |

| Sect | ion 17             | Pin Function Controller (PFC)                                  | 629   |

| 17.1 |                    | ew                                                             |       |

| 17.2 |                    | er Configuration                                               |       |

| 17.3 | _                  | er Descriptions                                                |       |

| 1,.5 | _                  | Port A IO Register H (PAIORH)                                  |       |

|      |                    | Port A IO Register L (PAIORL)                                  |       |

|      |                    | Port A Control Registers H1 and H2 (PACRH1, PACRH2)            |       |

|      | 17.5.5             |                                                                |       |

| _    |                    | www.DataSheet4U.c                                              | mu.   |

|       | 17.3.4 Port A Control Registers L1 and L2 (PACRL1, PACRL2)  | 649 |

|-------|-------------------------------------------------------------|-----|

|       | 17.3.5 Port B IO Register H (PBIORH)                        | 653 |

| www.d | 17.3.6 Port B IO Register L (PBIORL)                        | 653 |

|       | 17.3.7 Port B Control Register H2 (PBCRH2)                  | 654 |

|       | 17.3.8 Port B Control Registers L1 and L2 (PBCRL1, PBCRL2)  | 657 |

|       | 17.3.9 Port C IO Register H (PCIORH)                        |     |

|       | 17.3.10 Port C IO Register L (PCIORL)                       | 659 |

|       | 17.3.11 Port C Control Registers H1 and H2 (PCCRH1, PCCRH2) | 660 |

|       | 17.3.12 Port C Control Registers L1 and L2 (PCCRL1, PCCRL2) | 664 |

|       | 17.3.13 Port D IO Register H (PDIORH)                       | 669 |

|       | 17.3.14 Port D IO Register L (PDIORL)                       | 670 |

|       | 17.3.15 Port D Control Registers H1 and H2 (PDCRH1, PDCRH2) | 671 |

|       | 17.3.16 Port D Control Registers L1 and L2 (PDCRL1, PDCRL2) | 677 |

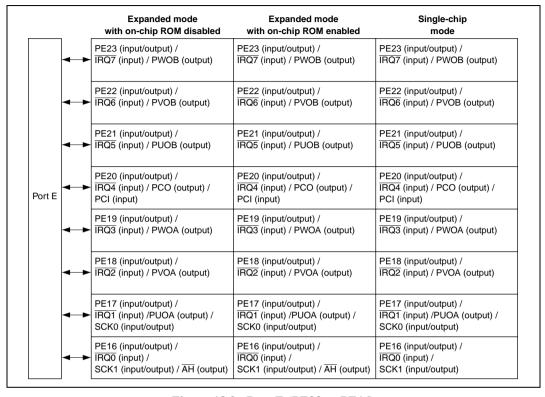

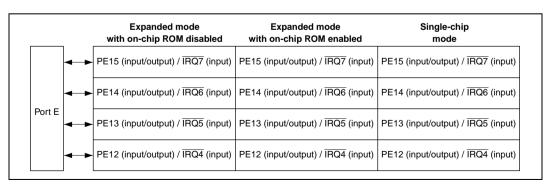

|       | 17.3.17 Port E IO Register H (PEIORH)                       | 683 |

|       | 17.3.18 Port E IO Register L (PEIORL)                       | 684 |

|       | 17.3.19 Port E Control Register H2 (PECRH2)                 | 684 |

|       | 17.3.20 Port E Control Register L (PECRL)                   | 687 |

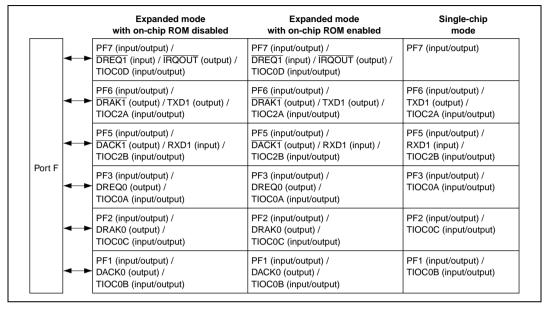

|       | 17.3.21 Port F IO Register L (PFIORL)                       | 688 |

|       | 17.3.22 Port F Control Register L2 (PFCRL2)                 | 689 |

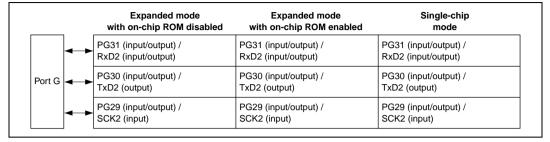

|       | 17.3.23 Port G IO Register (PGIOR)                          | 692 |

|       | 17.3.24 Port G Control Register H1 (PGCRH1)                 | 692 |

|       | 17.3.25 Port H IO Register (PHIOR)                          | 694 |

|       | 17.3.26 Port H Control Register (PHCR)                      | 694 |

|       | 17.3.27 Function Control Register (FCR)                     | 695 |

| 17.4  | PFC Restrictions                                            | 696 |

| Secti | ion 18 I/O Ports (I/O)                                      | 699 |

| 18.1  | Overview                                                    |     |

| 18.2  | Port A                                                      |     |

| 10.2  | 18.2.1 Register Configuration                               |     |

|       | 18.2.2 Port A Data Register H (PADRH)                       |     |

|       | 18.2.3 Port A Data Register L (PADRL)                       |     |

| 18.3  | Port B                                                      |     |

| 10.5  | 18.3.1 Register Configuration                               |     |

|       | 18.3.2 Port B Data Register H (PBDRH)                       |     |

|       | 18.3.3 Port B Data Register L (PBDRL)                       |     |

| 18.4  | Port C                                                      |     |

| 10.7  | 18.4.1 Register Configuration                               |     |

|       | 18.4.2 Port C Data Register H (PCDRH)                       |     |

|       | 18.4.3 Port C Data Register L (PCDRL)                       |     |

| 18.5  | Port D                                                      |     |

|       |                                                             |     |

|       | 18.5.1             | Register Configuration                              | . 712 |

|-------|--------------------|-----------------------------------------------------|-------|

|       | 18.5.2             | Port D Data Register H (PDDRH)                      | . 712 |

| www.c | datashee<br>18.5.3 | Port D Data Register L (PDDRL)                      | . 713 |

| 18.6  | Port E             |                                                     | . 714 |

|       | 18.6.1             | Register Configuration                              | . 715 |

|       | 18.6.2             | Port E Data Register H (PEDRH)                      | . 715 |

|       | 18.6.3             | Port E Data Register L (PEDRL)                      | . 716 |

| 18.7  | Port F.            |                                                     | . 717 |

|       | 18.7.1             | Register Configuration                              | . 717 |

|       | 18.7.2             | Port F Data Register L (PFDRL)                      | . 718 |

| 18.8  | Port G             |                                                     | . 719 |

|       | 18.8.1             | Register Configuration                              | . 719 |

|       | 18.8.2             | Port G Data Register H (PGDRH)                      | . 719 |

| 18.9  | Port H             |                                                     | . 721 |

|       | 18.9.1             | Register Configuration                              | . 721 |

|       | 18.9.2             | Port H Data Register (PHDR)                         | . 721 |

| 18.10 | Port I             |                                                     | . 723 |

|       | 18.10.1            | Register Configuration                              | . 723 |

|       | 18.10.2            | Port I Data Register (PIDR)                         | . 724 |

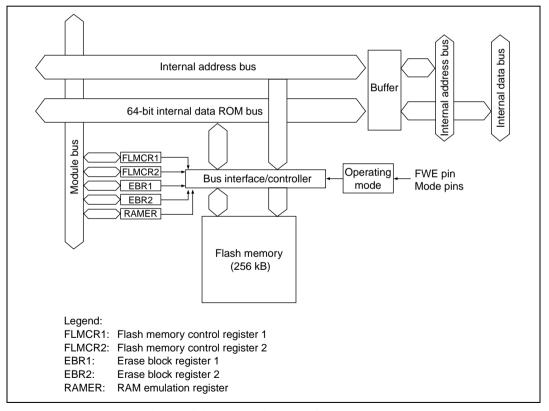

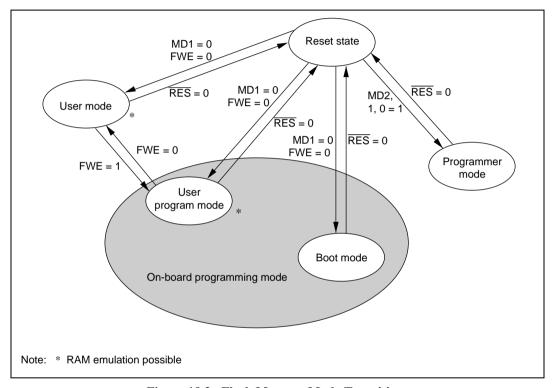

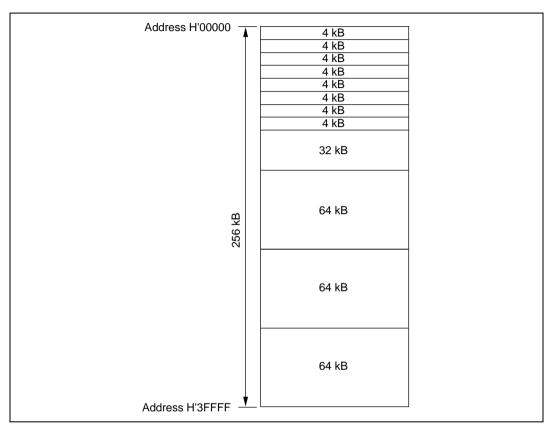

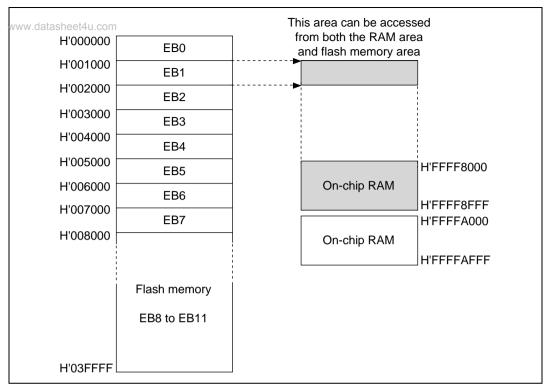

| Secti | on 19              | 256 kB Flash Memory (F-ZTAT)                        | . 725 |

| 19.1  |                    | es                                                  |       |

| 19.2  |                    | ew                                                  |       |

|       |                    | Block Diagram                                       |       |

|       |                    | Mode Transitions                                    |       |

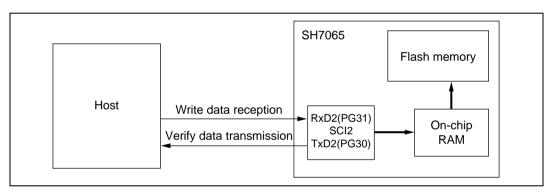

|       | 19.2.3             | On-Board Programming Modes                          | . 728 |

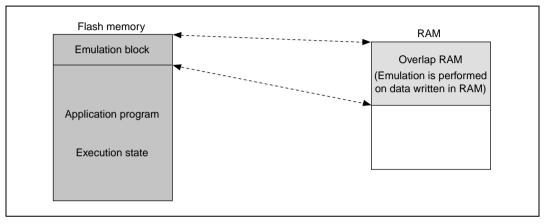

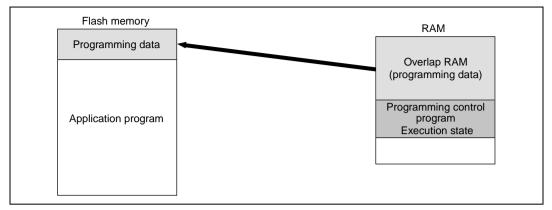

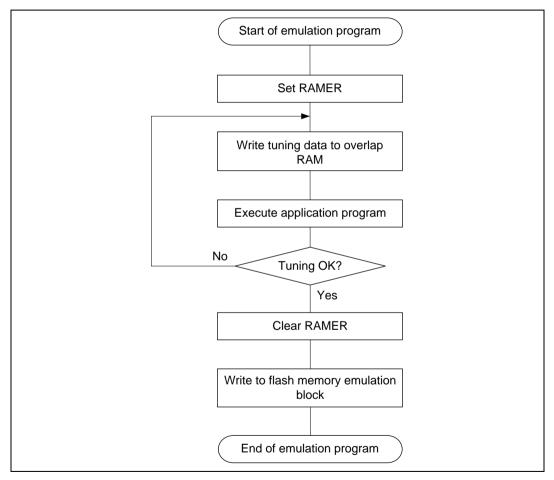

|       | 19.2.4             | Flash Memory Emulation in RAM                       | . 730 |

|       |                    | Differences between Boot Mode and User Program Mode |       |

|       |                    | Block Configuration                                 |       |

| 19.3  | Pin Co             | nfiguration                                         | . 733 |

| 19.4  | Registe            | er Configuration                                    | . 734 |

| 19.5  | Registe            | er Descriptions                                     | . 735 |

|       | 19.5.1             | Flash Memory Control Register 1 (FLMCR1)            | . 735 |

|       | 19.5.2             | Flash Memory Control Register 2 (FLMCR2)            | . 738 |

|       |                    | Erase Block Register 1 (EBR1)                       |       |

|       |                    | Erase Block Register 2 (EBR2)                       |       |

|       | 19.5.5             | RAM Emulation Register (RAMER)                      | . 740 |

| 19.6  |                    | ard Programming Modes                               |       |

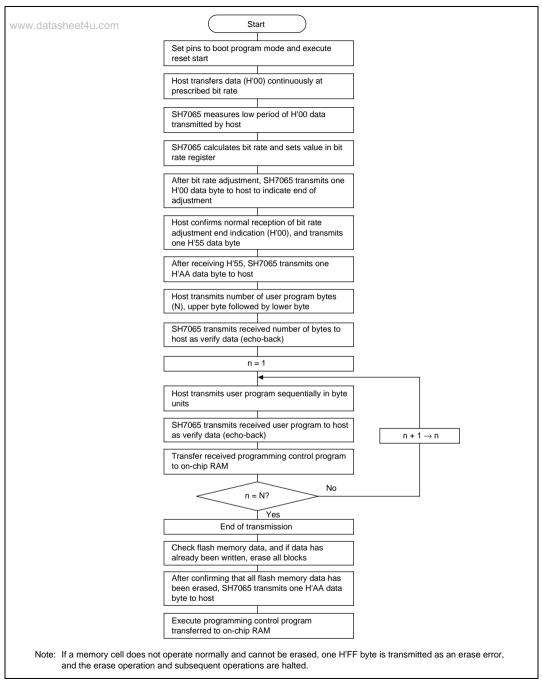

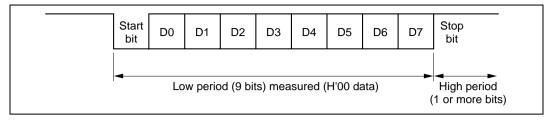

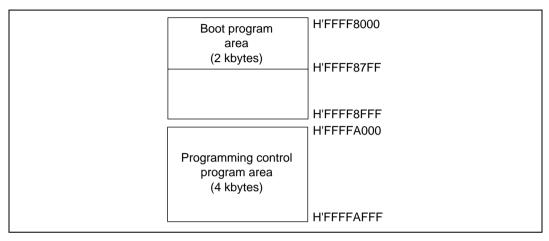

|       | 19.6.1             | Boot Mode                                           | . 743 |

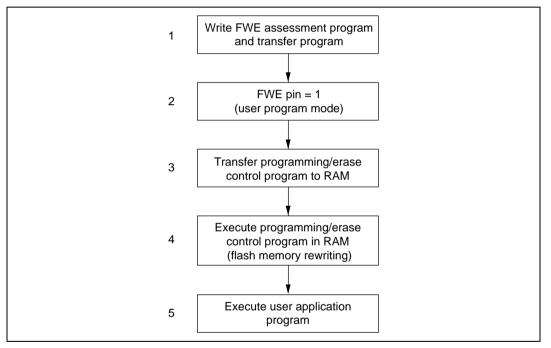

|       | 19.6.2             | User Program Mode                                   | . 747 |

| 19.7  |                    | mming/Erasing Flash Memory                          | . 748 |

| D .   | - 00 0             | www.DataSheet4U.c                                   | om    |

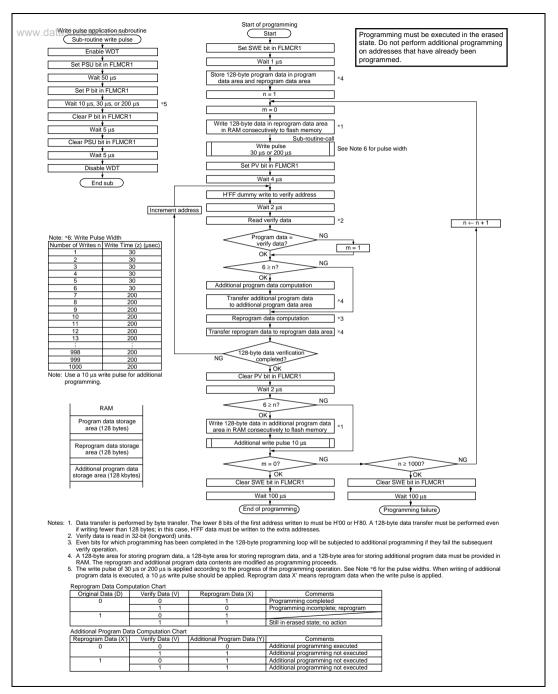

|       | 19.7.1  | Program Mode                                               | 748 |

|-------|---------|------------------------------------------------------------|-----|

|       | 19.7.2  | Program-Verify Mode                                        | 749 |

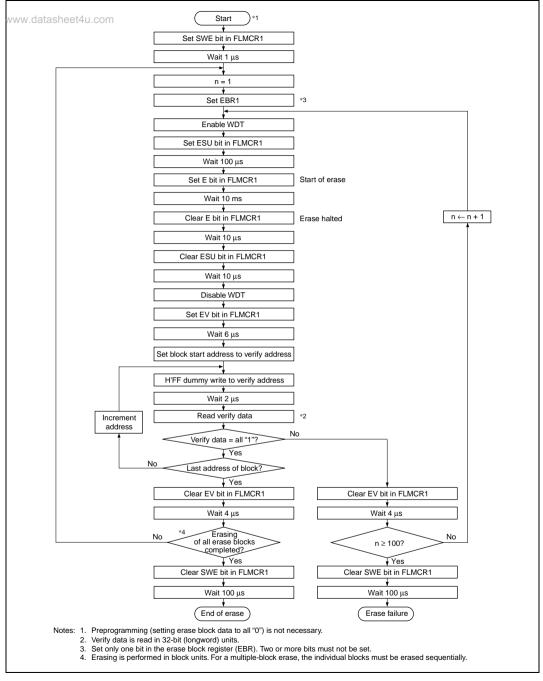

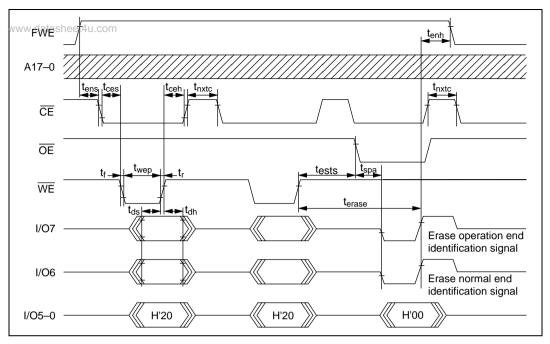

| www.d | 19.7.3  | Erase Mode (n = 1 for Addresses H'00000 to H'07FFF,        |     |

|       |         | n = 2 for Addresses H'08000 to H'3FFFF)                    | 757 |

|       | 19.7.4  | Erase-Verify Mode (n = 1 for Addresses H'00000 to H'07FFF, |     |

|       |         | n = 2 for Addresses H'08000 to H'3FFFF)                    | 758 |

|       | 19.7.5  | Wait Time Widths in Programming/Erasing                    | 764 |

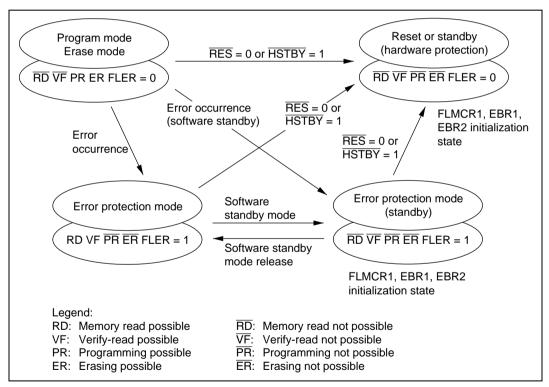

| 19.8  | Protect | ion                                                        | 765 |

|       | 19.8.1  | Hardware Protection                                        | 765 |

|       | 19.8.2  | Software Protection                                        | 766 |

|       | 19.8.3  | Error Protection                                           | 766 |

| 19.9  | Flash N | Memory Emulation in RAM                                    | 768 |

| 19.10 | Note of | n Flash Memory Programming/Erasing                         | 770 |

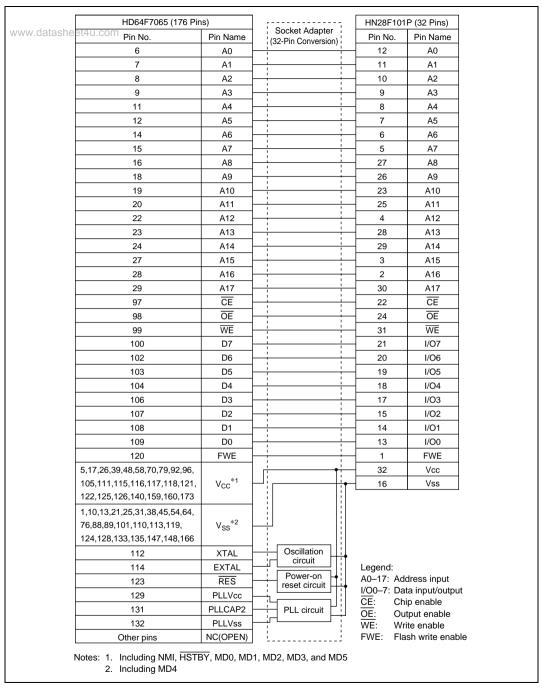

| 19.11 | Flash N | Memory Programmer Mode                                     | 770 |

|       | 19.11.1 | Socket Adapter Pin Correspondence Diagram                  | 771 |

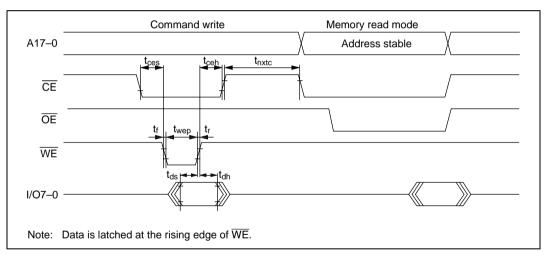

|       | 19.11.2 | 2 Operation in Programmer Mode                             | 773 |

|       | 19.11.3 | B Memory Read Mode                                         | 774 |

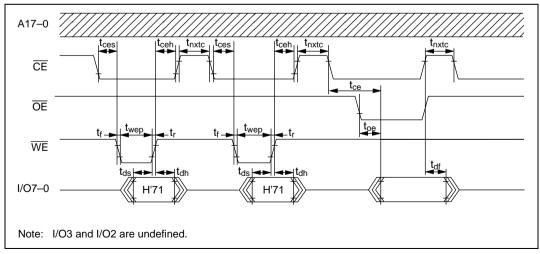

|       | 19.11.4 | Auto-Program Mode                                          | 778 |

|       |         | 5 Auto-Erase Mode                                          |     |

|       | 19.11.6 | Status Read Mode                                           | 782 |

|       | 19.11.7 | 7 Status Polling                                           | 783 |

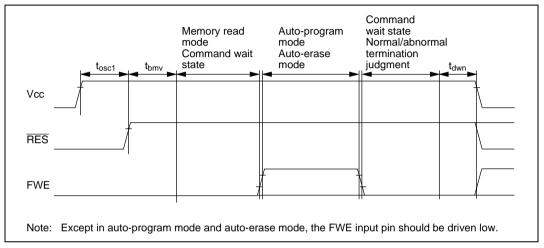

|       | 19.11.8 | Programmer Mode Transition Time                            | 783 |

|       | 19.11.9 | Cautions Concerning Memory Programming                     | 784 |

| 19.12 | . Usage | Notes                                                      | 785 |

| 19.13 | Caution | ns on Transition from F-ZTAT to Mask ROM Version           | 785 |

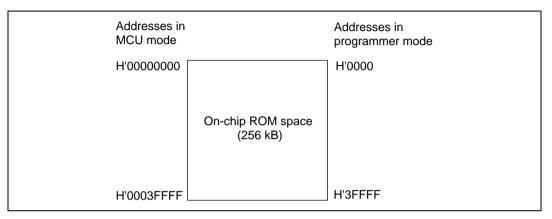

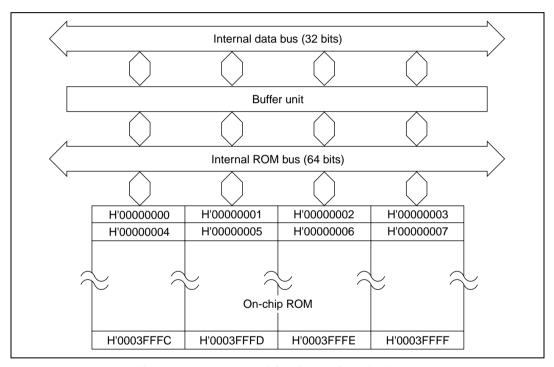

| Sect  | ion 20  | 256 kB Mask ROM                                            | 787 |

|       |         | ew                                                         |     |

|       |         |                                                            |     |

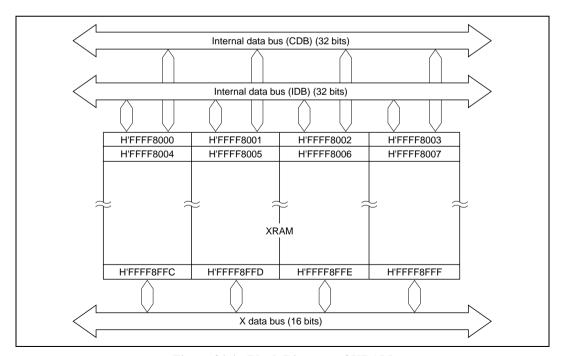

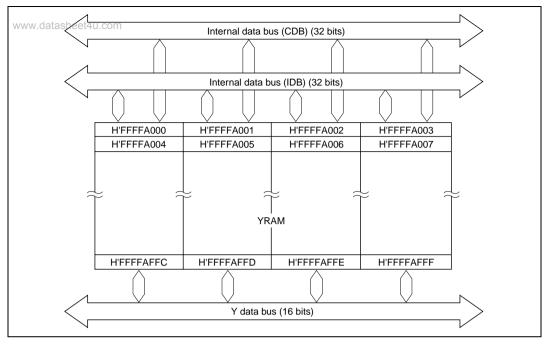

| Sect  | ion 21  | XRAM and YRAM                                              | 789 |

| 21.1  |         | ew                                                         |     |

| 21.2  | Operat  | ion                                                        | 790 |

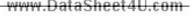

| Sect  | ion 22  | Electrical Characteristics                                 | 791 |

|       |         | te Maximum Ratings                                         |     |

| 22.2  |         | cal Characteristics                                        |     |

|       |         | DC Characteristics (1)                                     |     |

|       |         | DC Characteristics (2)                                     |     |

| 22.3  |         | aracteristics Test Conditions                              |     |

|       |         | Clock Timing                                               |     |

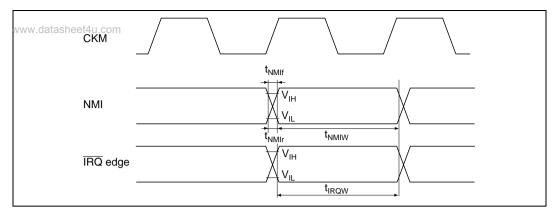

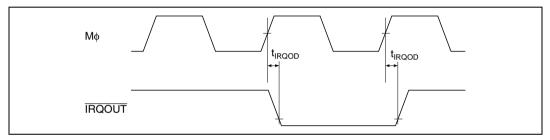

|       |         | Control Signal Timing                                      |     |

|       |         |                                                            |     |

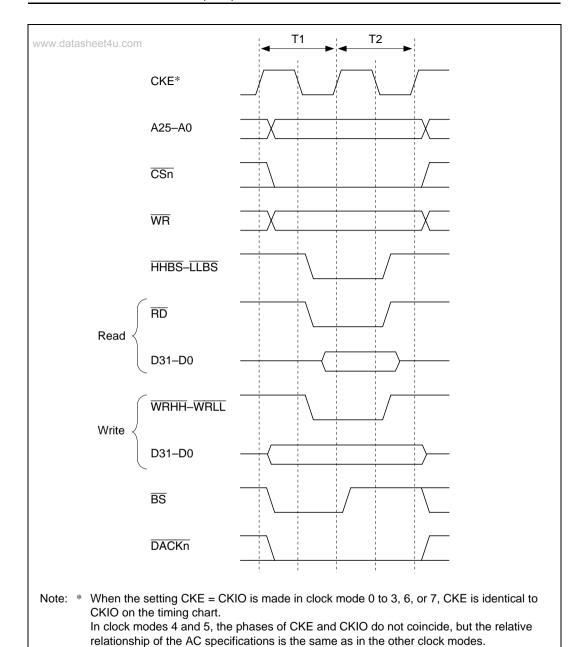

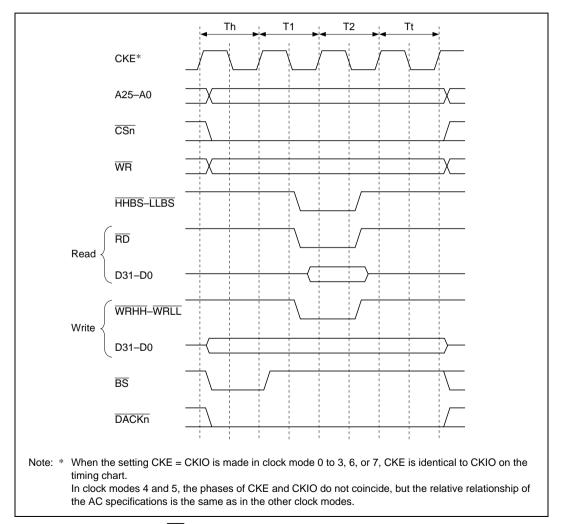

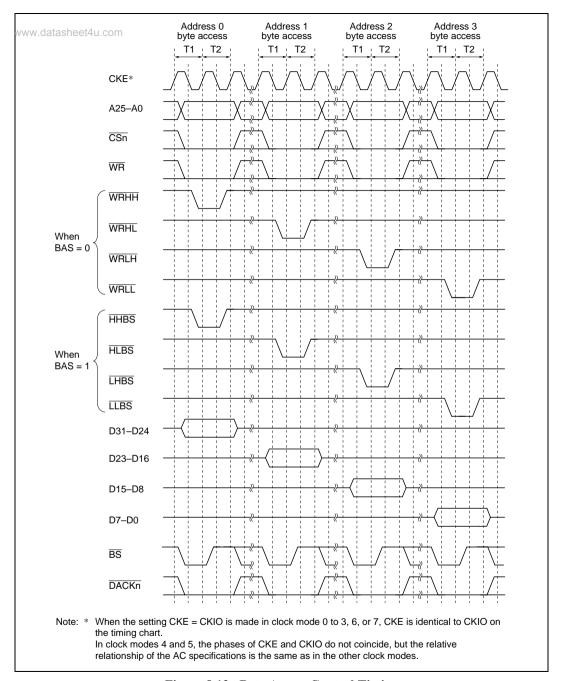

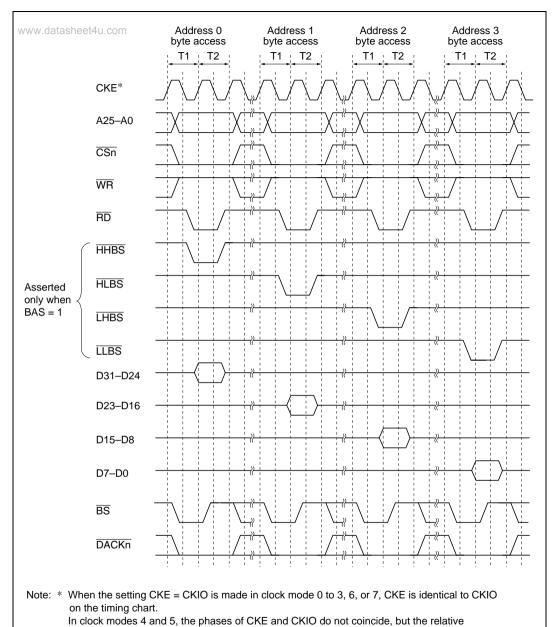

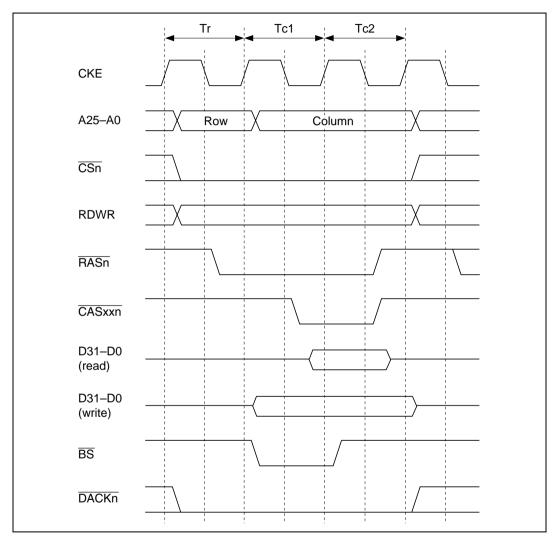

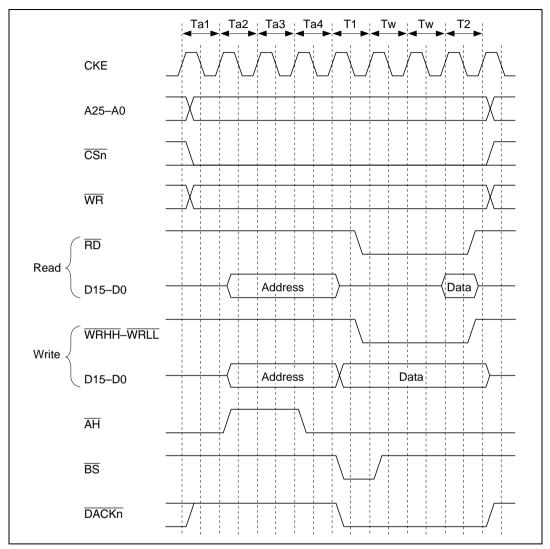

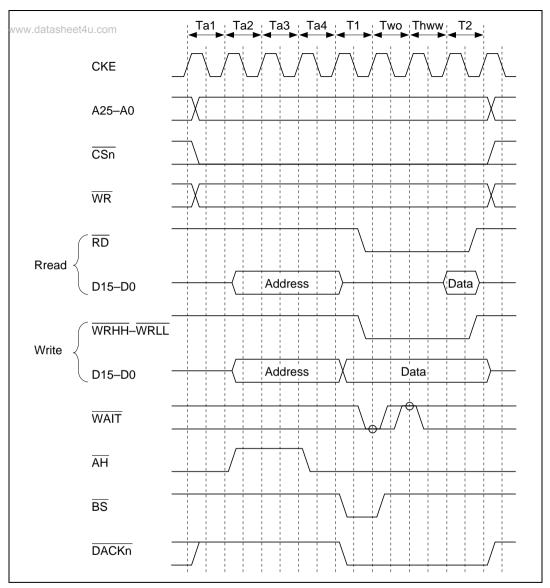

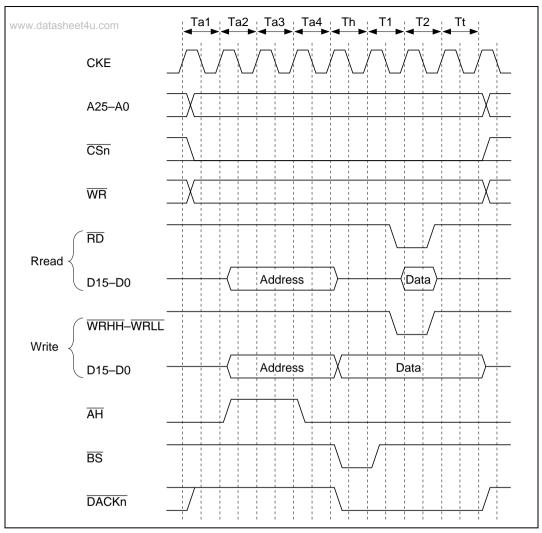

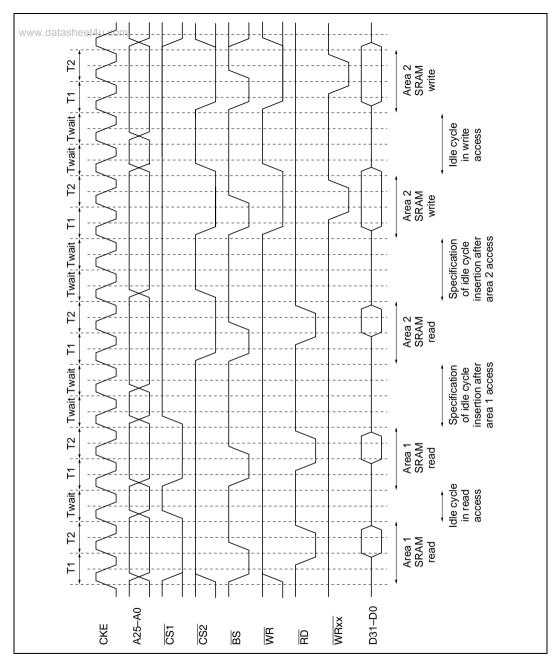

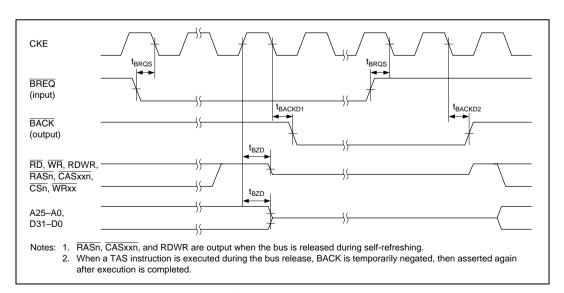

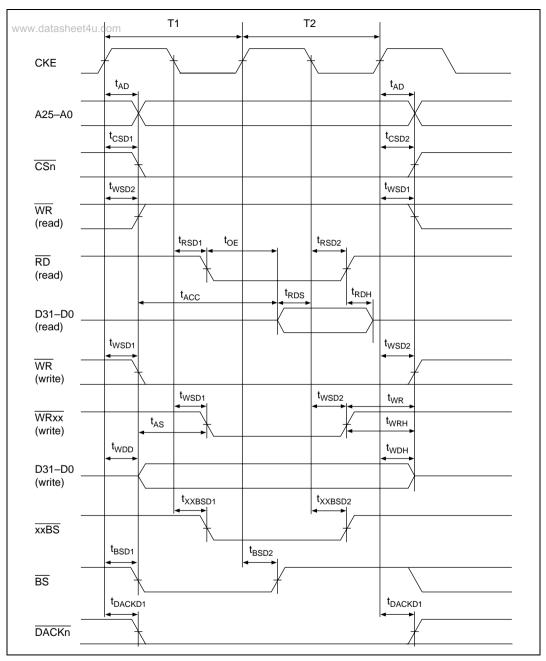

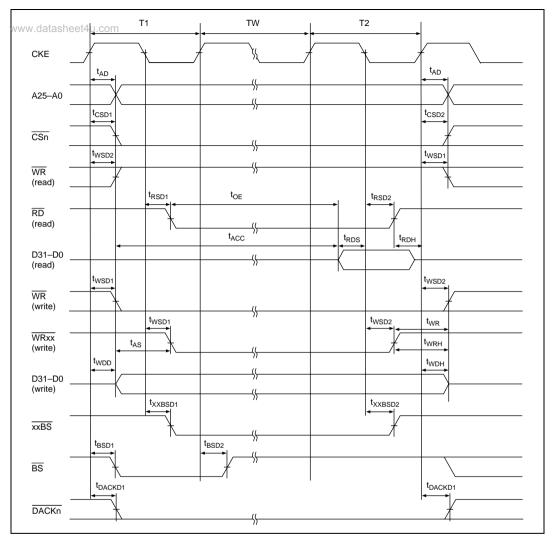

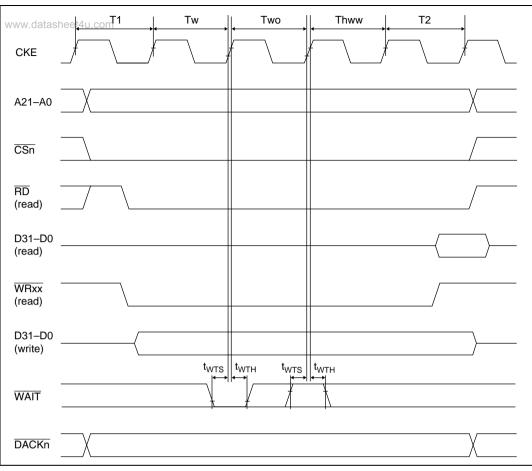

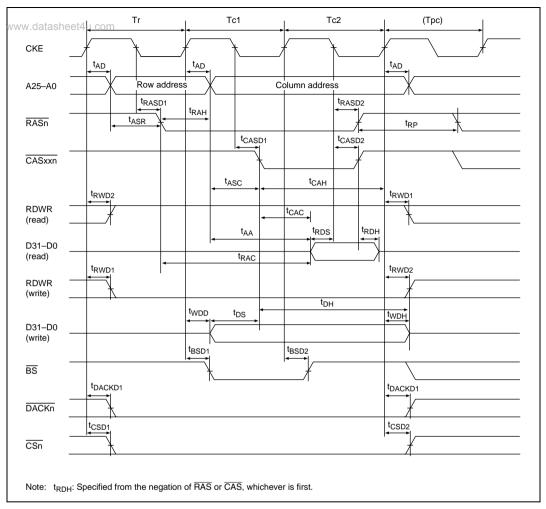

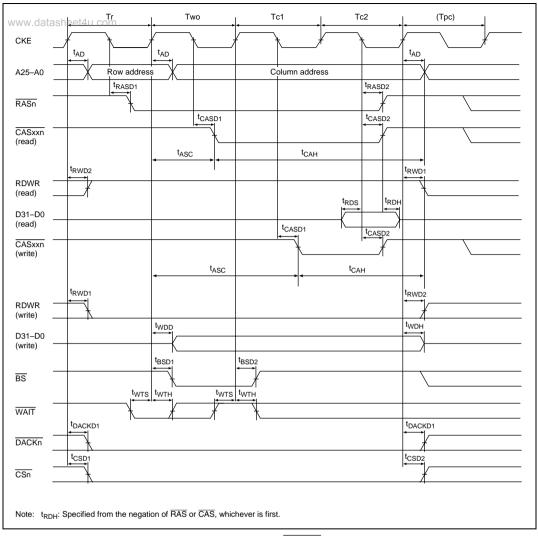

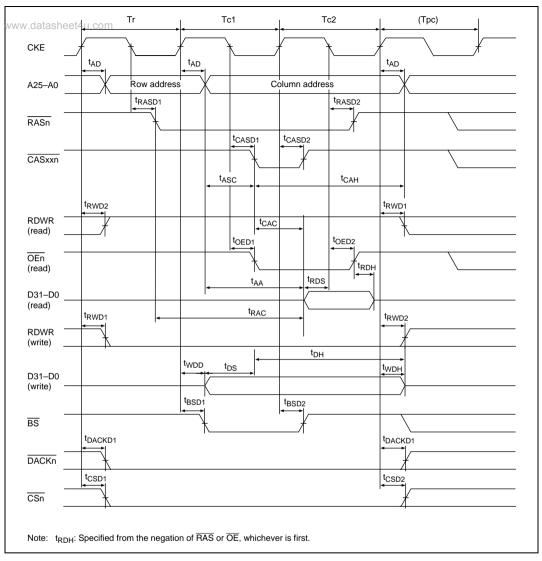

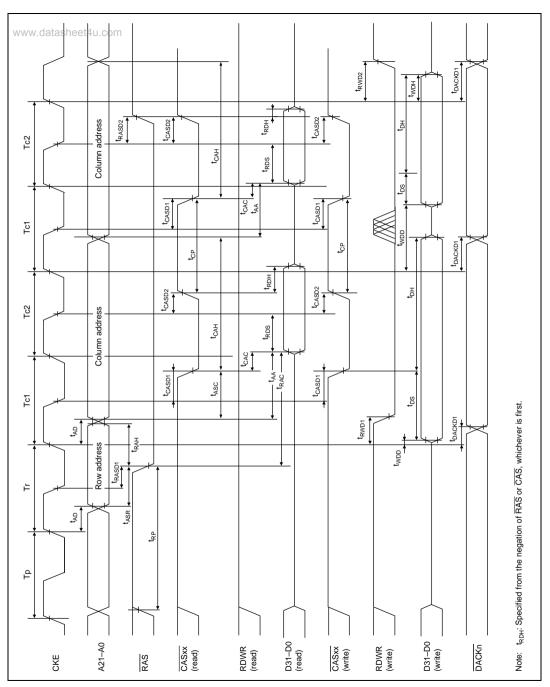

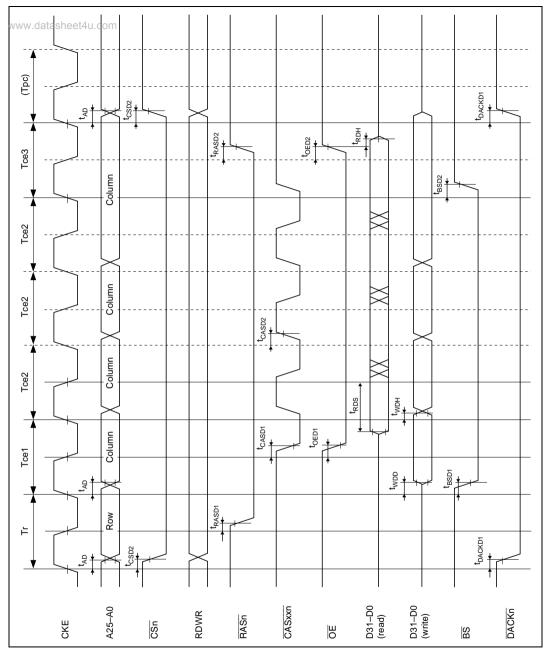

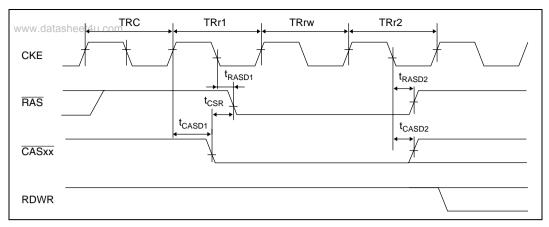

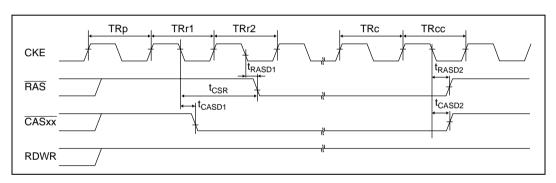

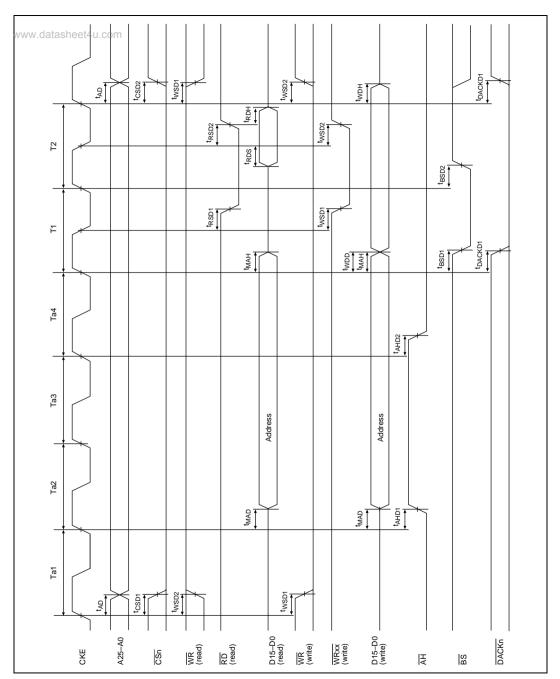

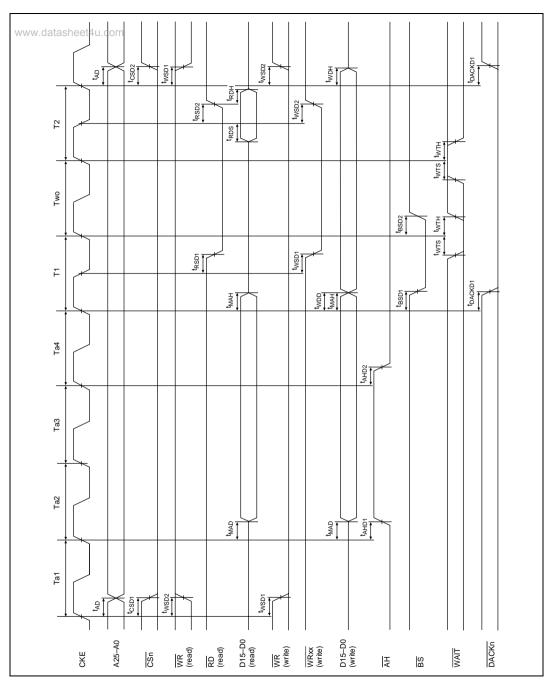

|      | 22.3.3    | Bus Timing                                                                                                             | 800 |

|------|-----------|------------------------------------------------------------------------------------------------------------------------|-----|

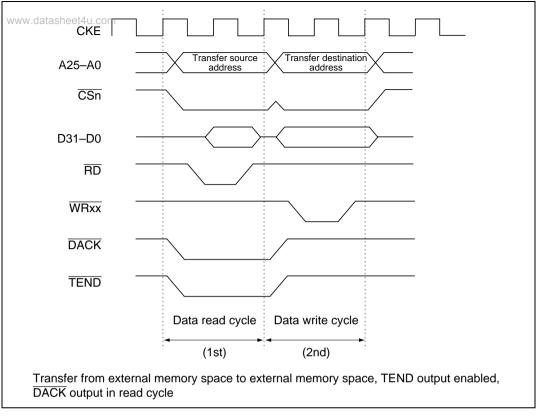

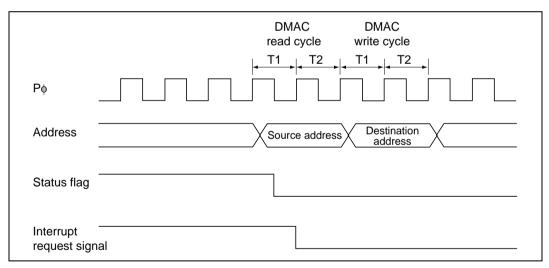

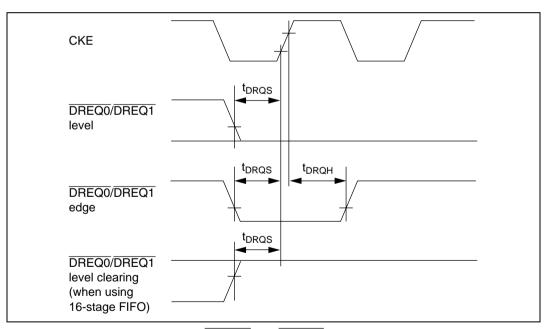

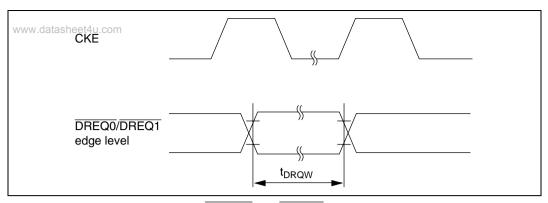

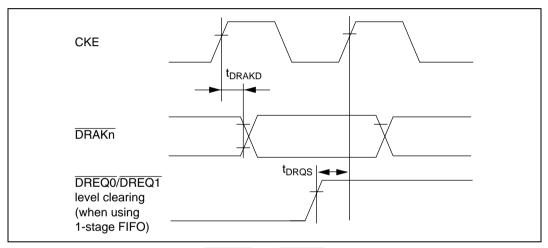

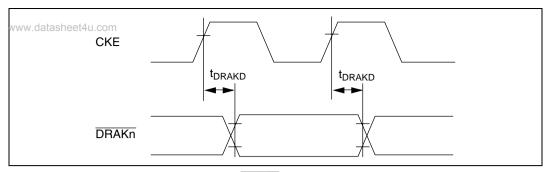

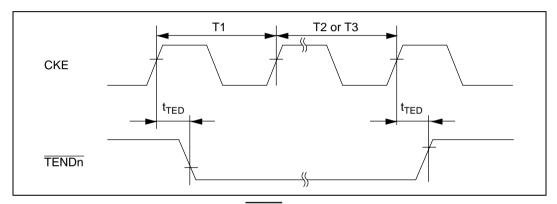

|      | 22.3.4    | Direct Memory Access Controller Timing                                                                                 | 815 |

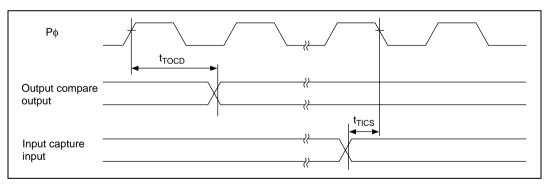

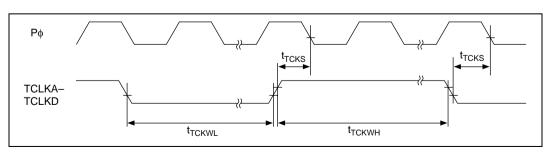

| WWW. | 22.3.5    | To-Bit Timer Pulse Unit (TPU) Timing                                                                                   | 818 |

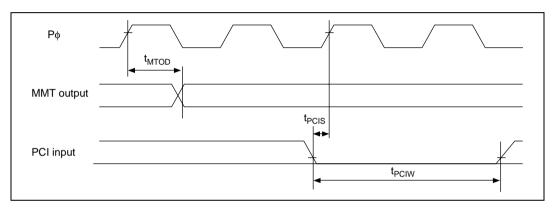

|      | 22.3.6    | Motor Management Timer (MMT) Timing                                                                                    | 819 |

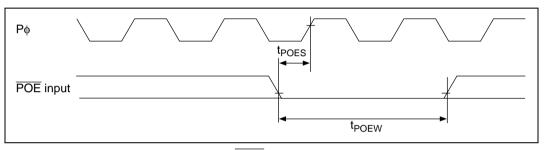

|      | 22.3.7    | Port Output Enable (POE) Timing                                                                                        | 820 |

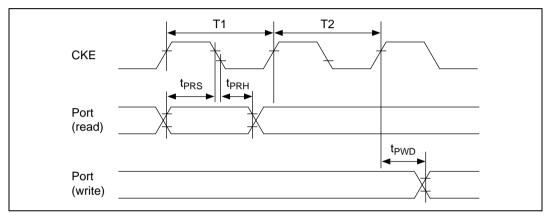

|      | 22.3.8    | I/O Port Timing                                                                                                        | 821 |

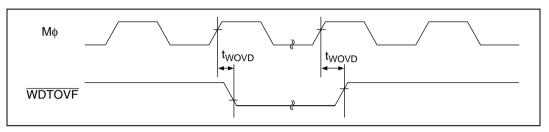

|      | 22.3.9    | Watchdog Timer Timing                                                                                                  | 822 |

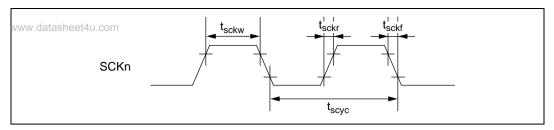

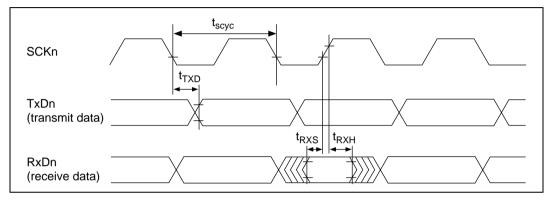

|      | 22.3.10   | Serial Communication Interface Timing                                                                                  | 822 |

|      |           | A/D Conversion Timing                                                                                                  |     |

|      | 22.3.12   | A/D Conversion Characteristics                                                                                         | 826 |

|      | 22.3.13   | D/A Conversion Characteristics                                                                                         | 827 |

| Appe | endix A   | On-Chip Peripheral Module Registers                                                                                    | 829 |

| Appe | endix B   | Pin States                                                                                                             | 849 |

| B.1  | Pin State | es in Reset, Power-Down State, and Bus-Released State                                                                  | 849 |

| B.2  | Bus-Rel   | ated Signal Pin States                                                                                                 | 853 |

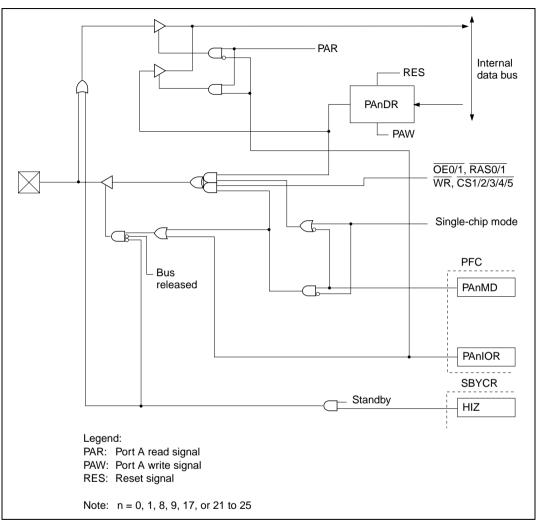

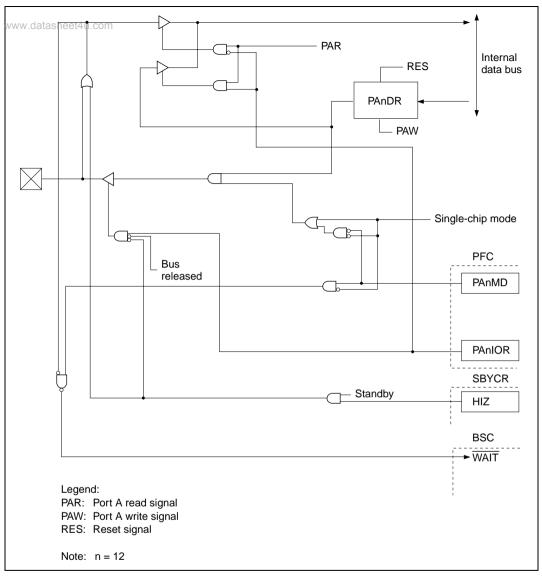

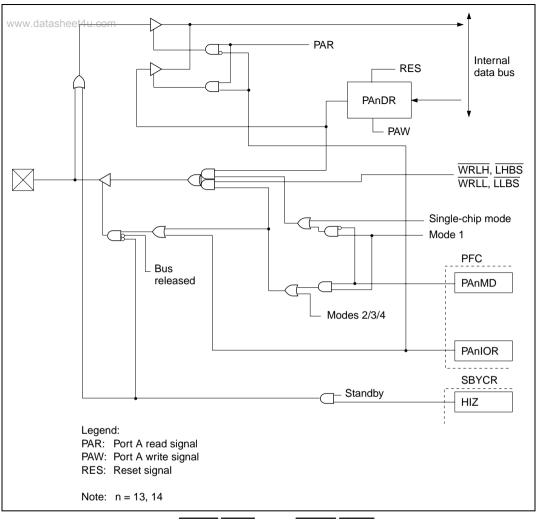

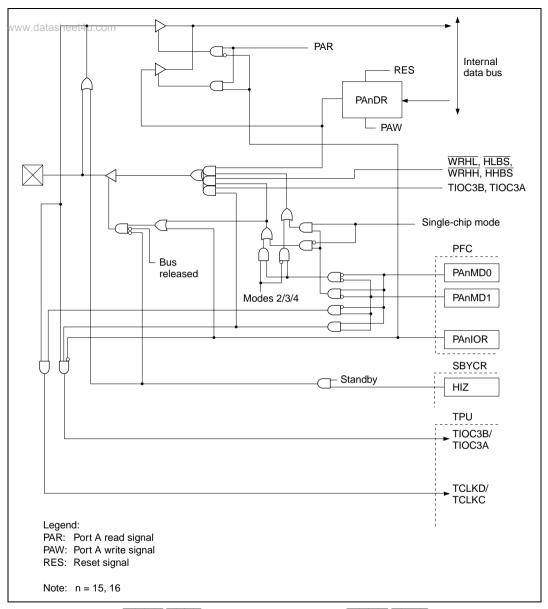

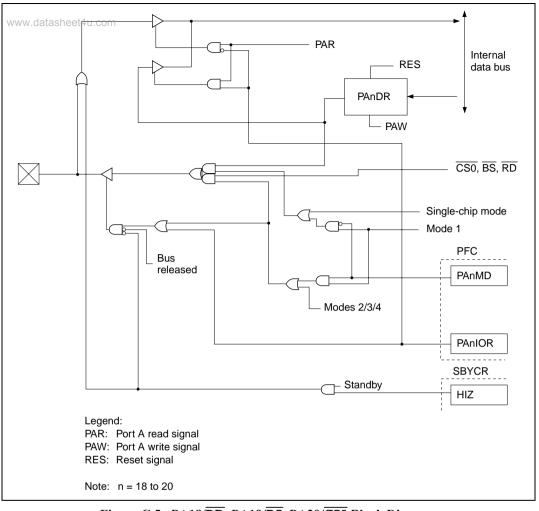

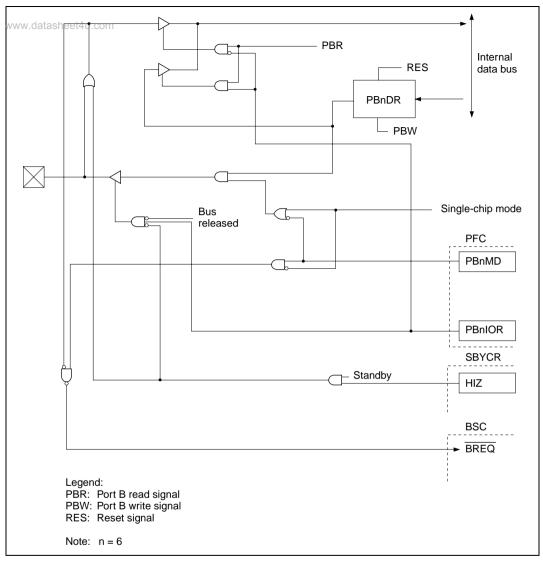

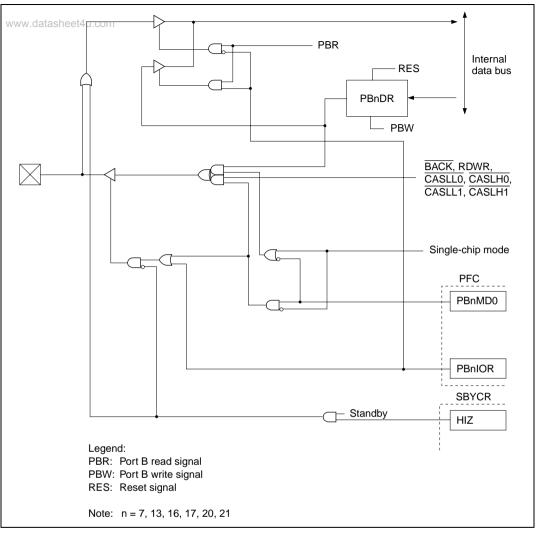

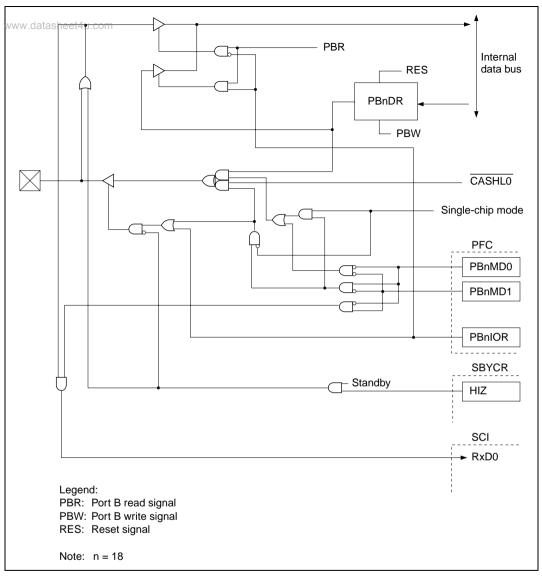

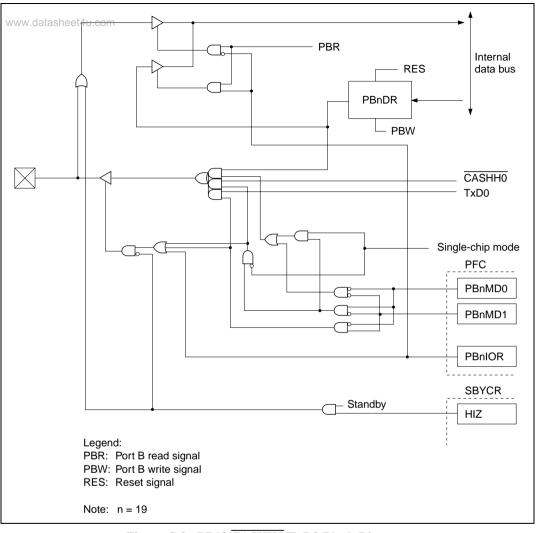

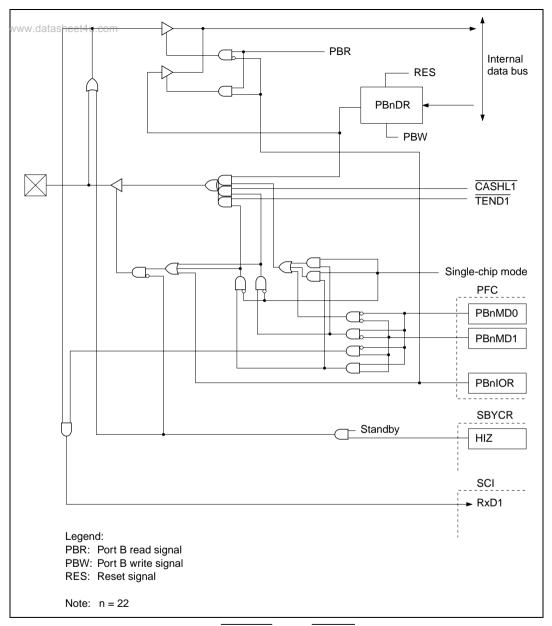

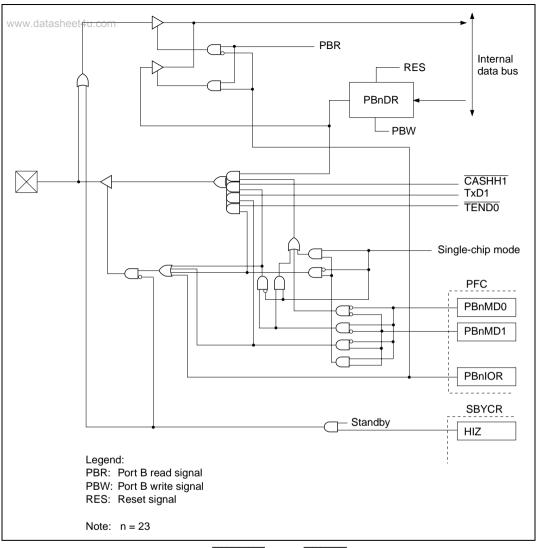

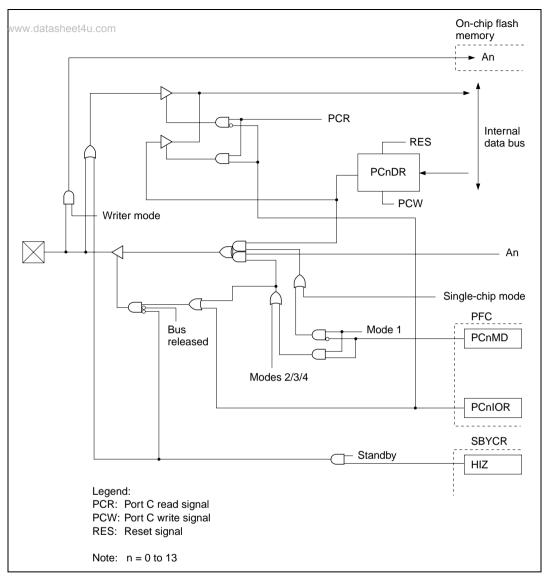

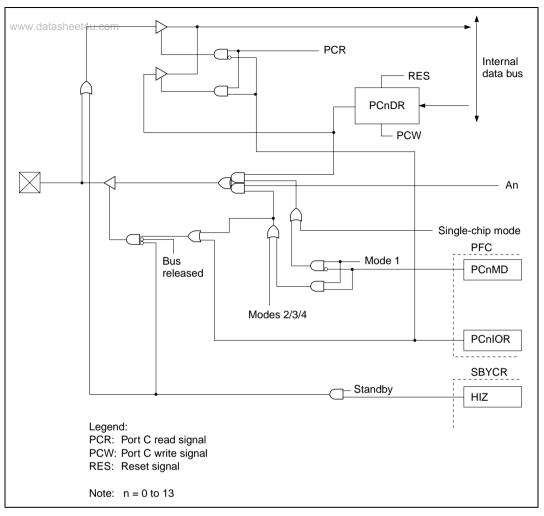

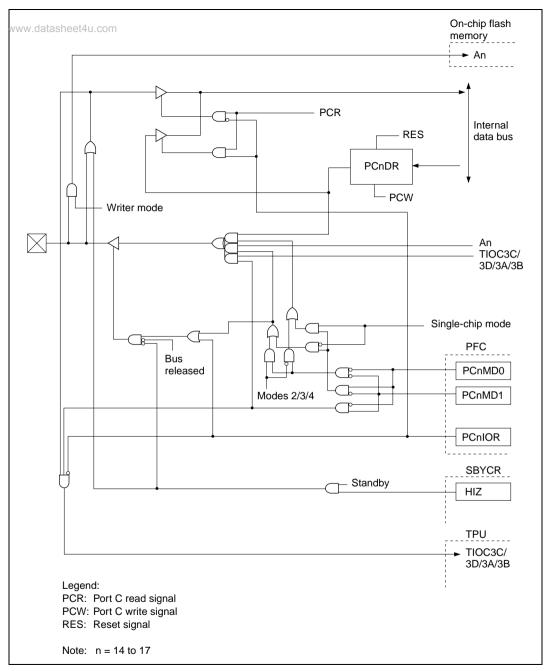

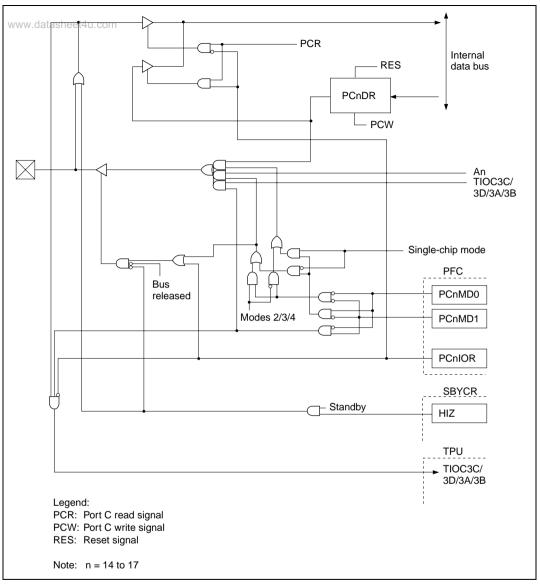

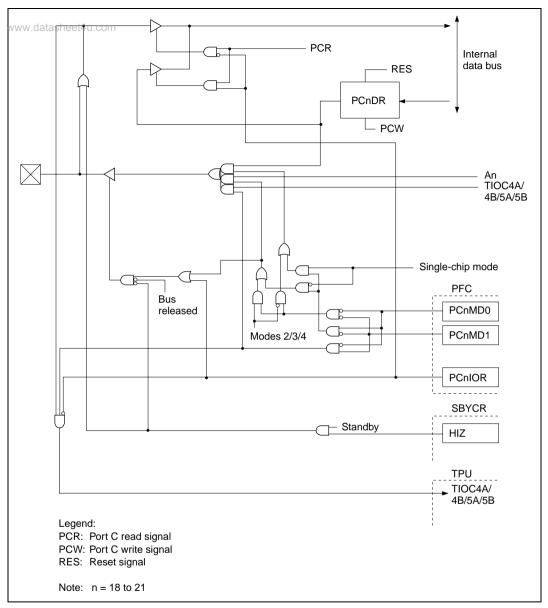

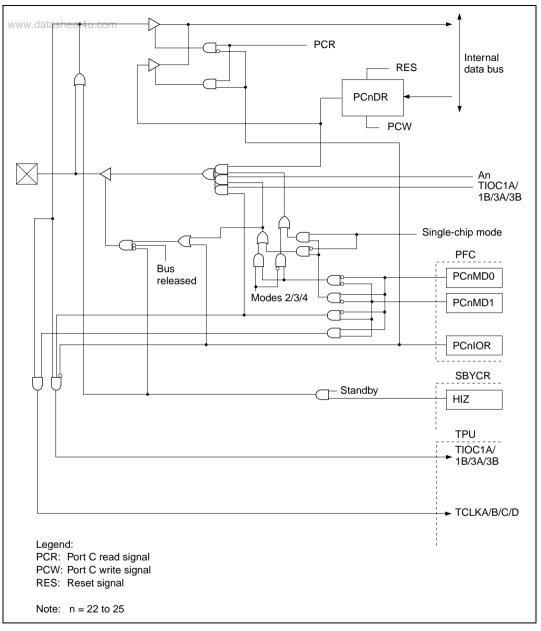

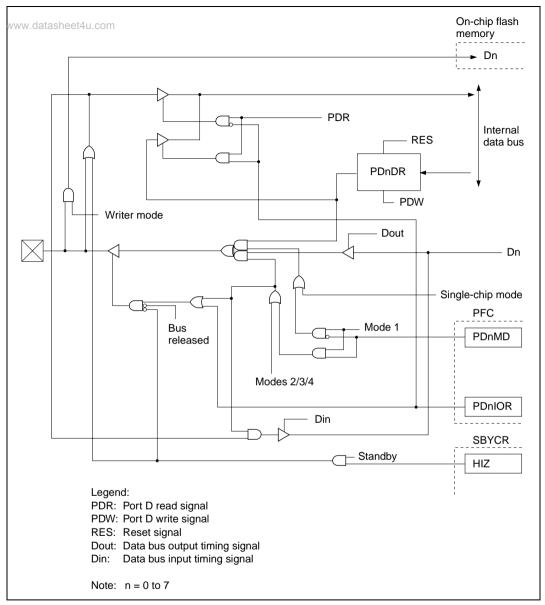

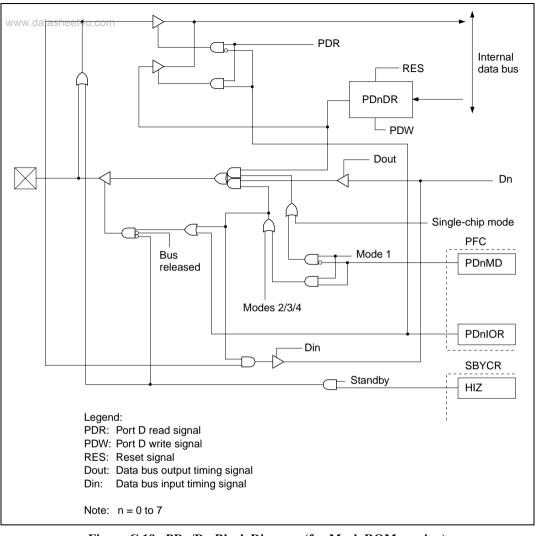

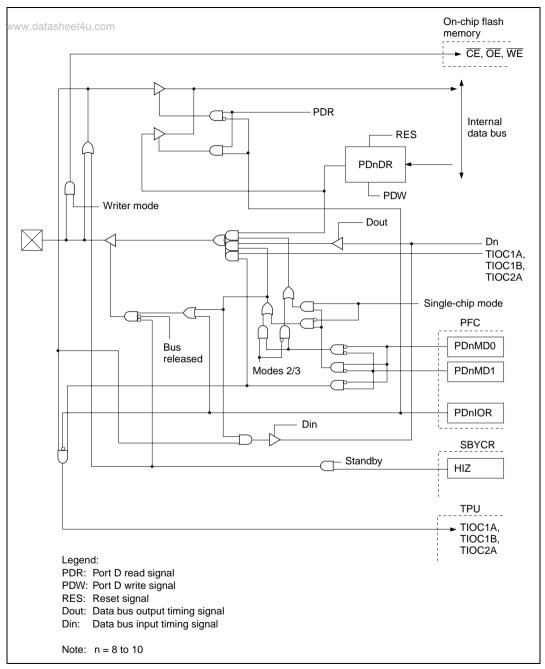

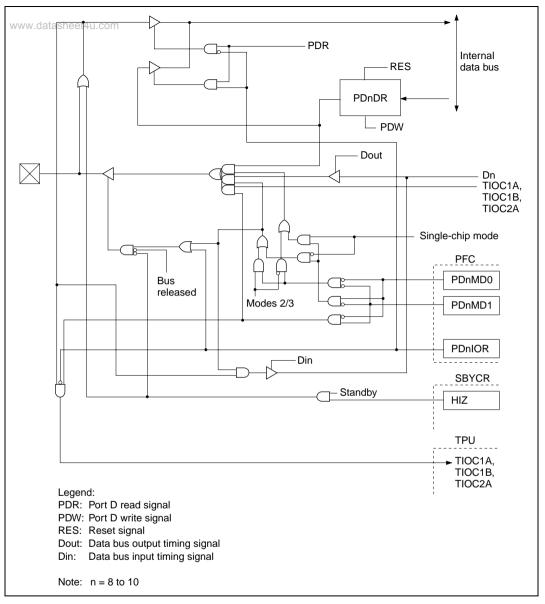

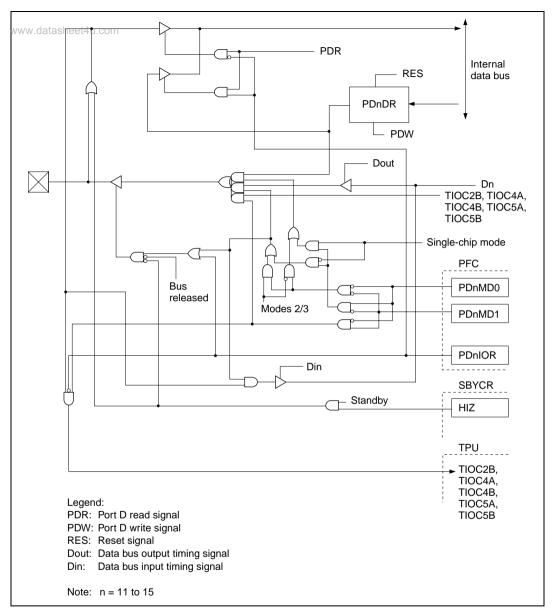

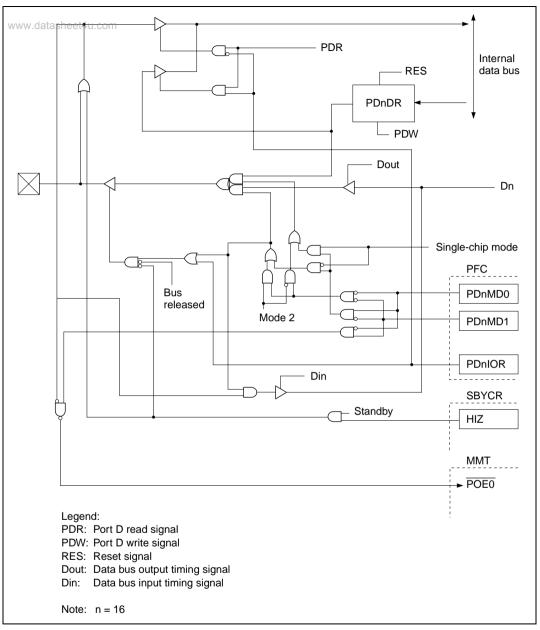

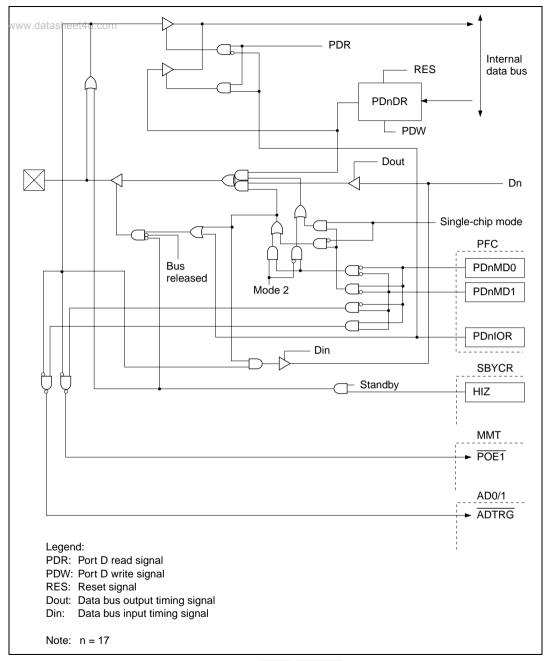

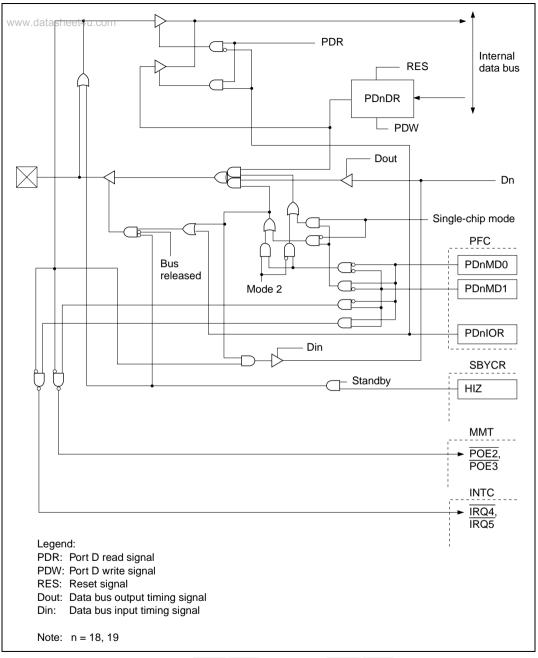

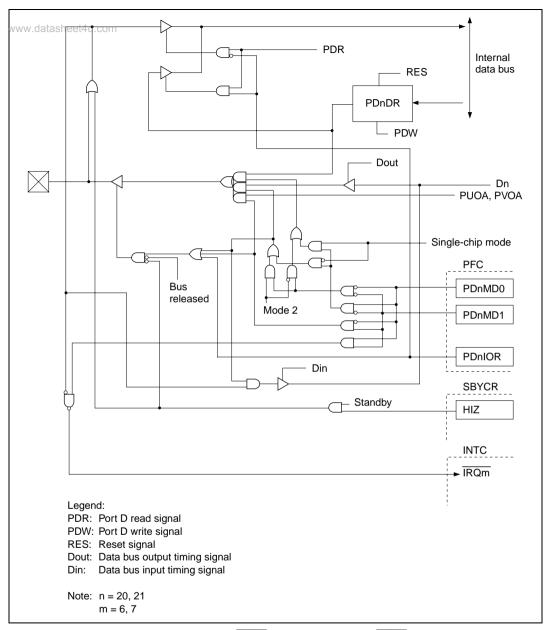

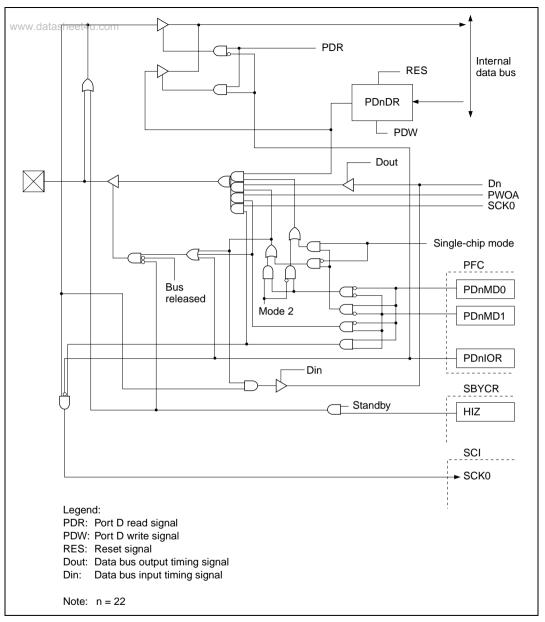

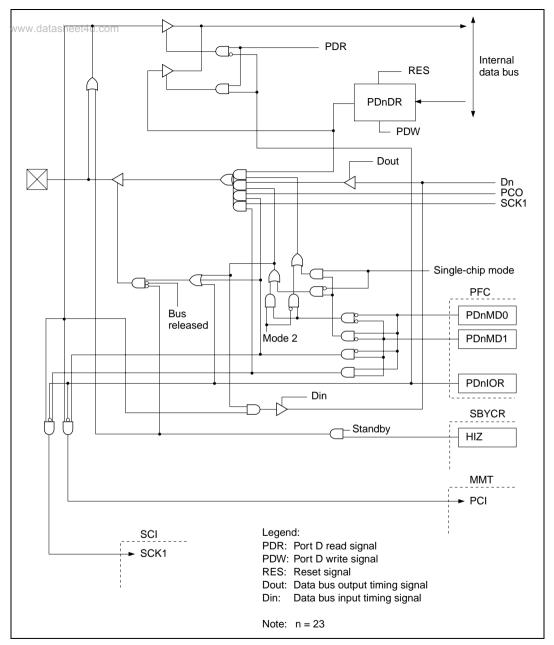

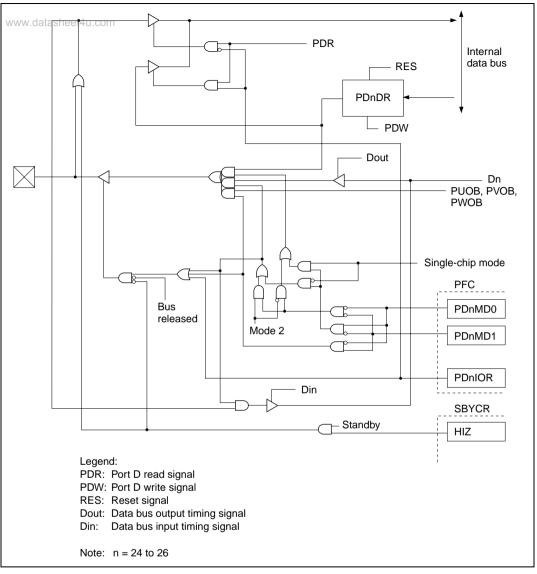

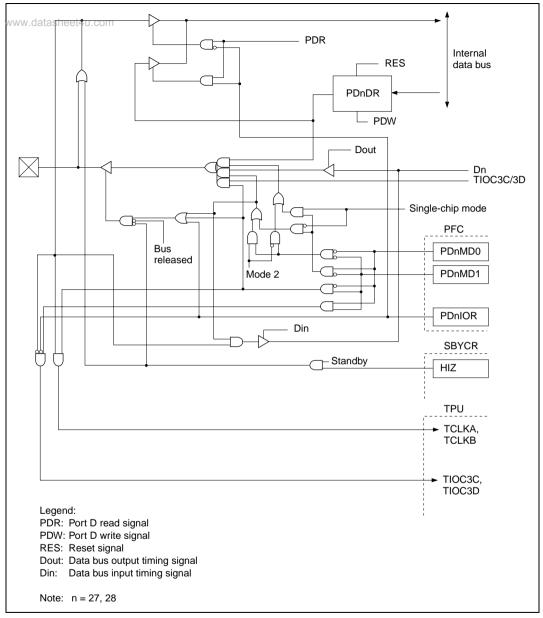

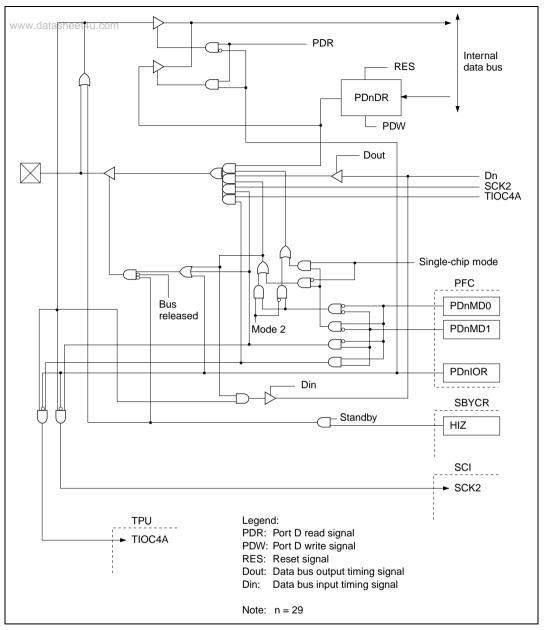

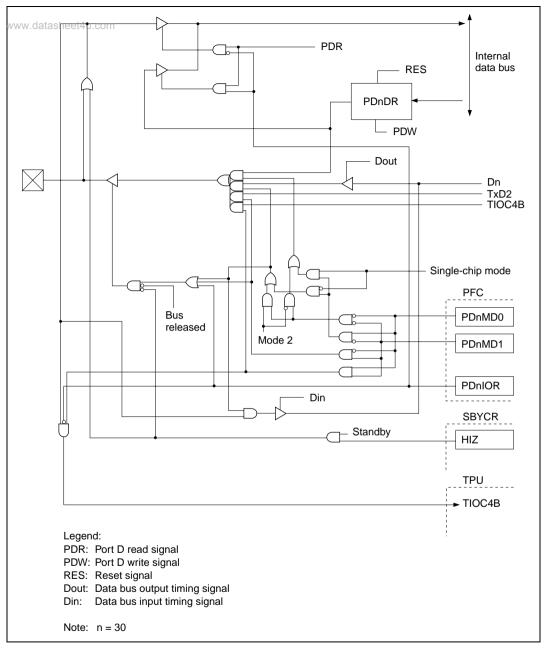

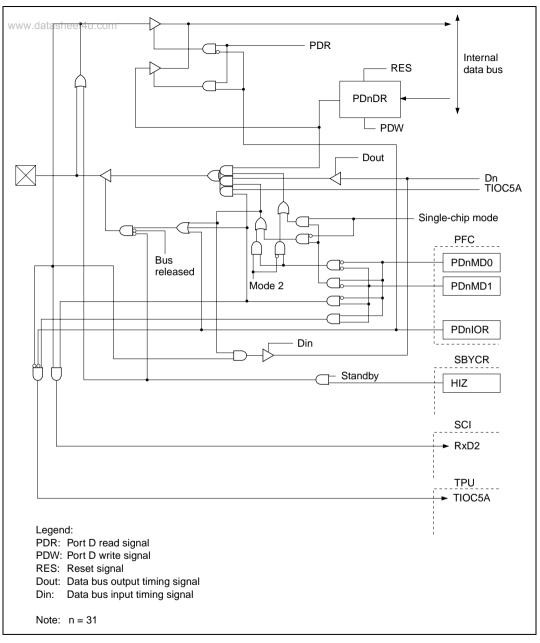

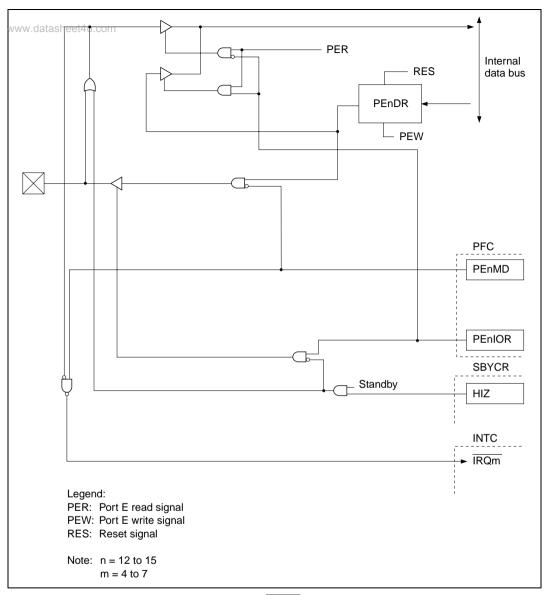

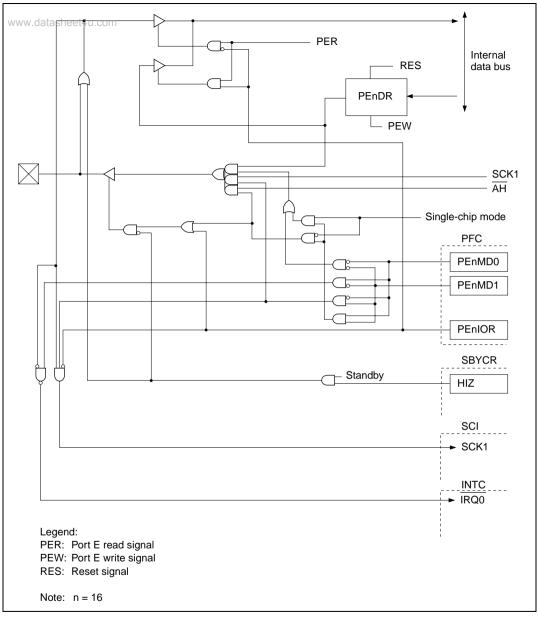

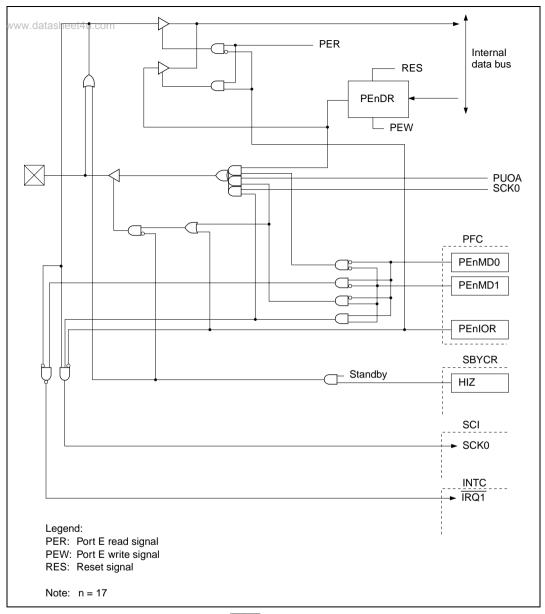

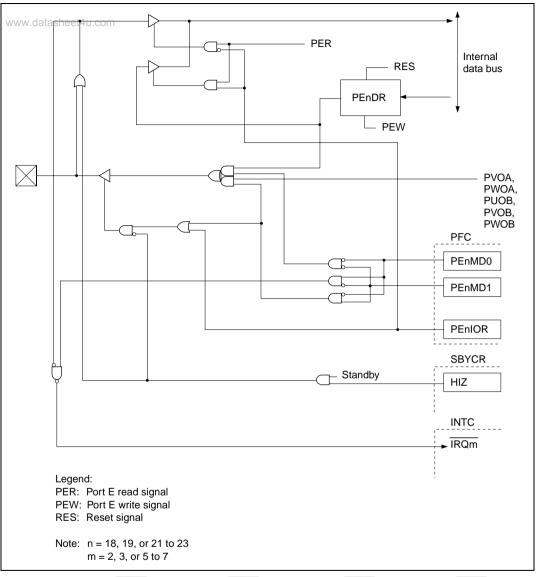

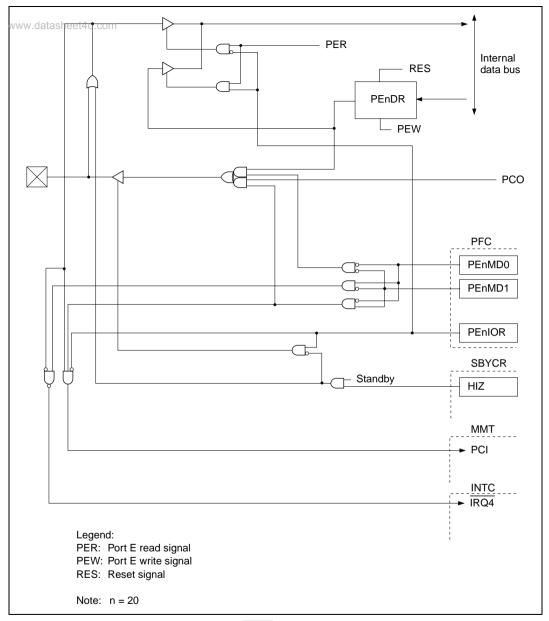

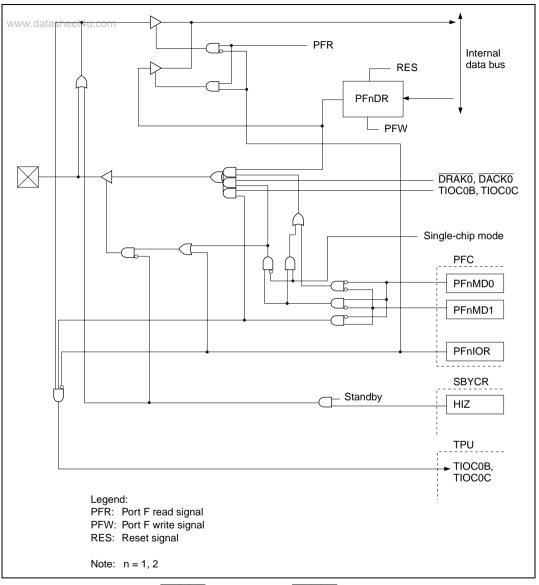

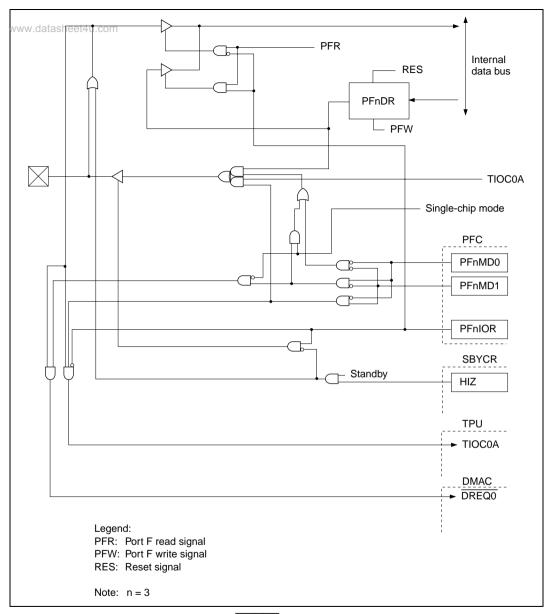

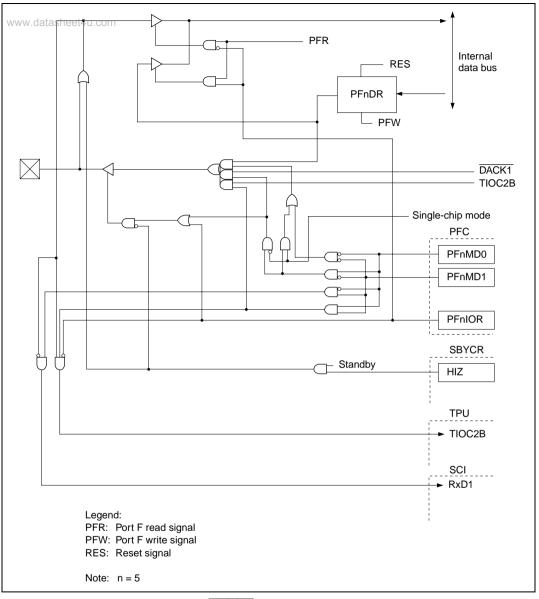

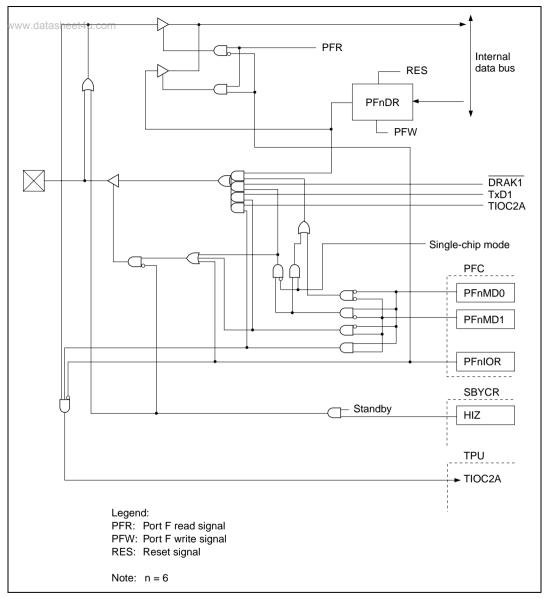

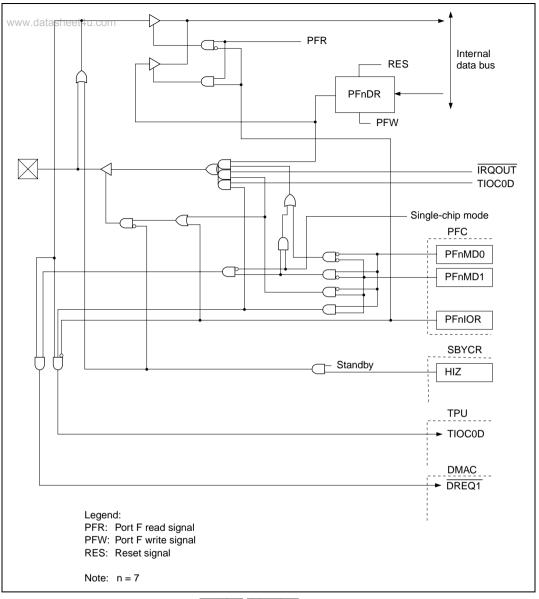

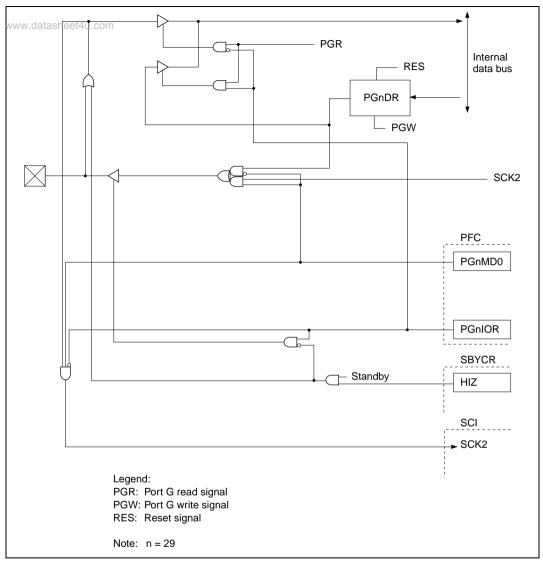

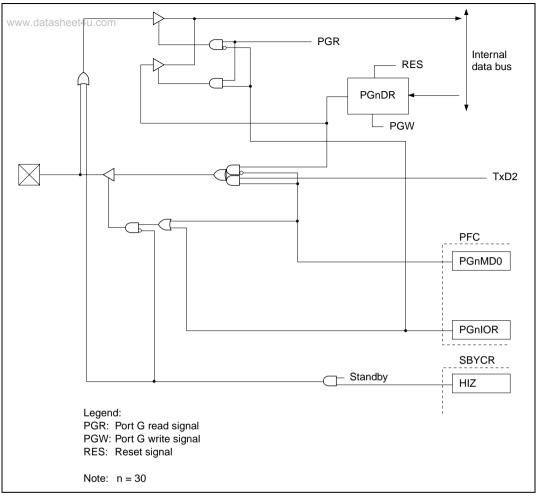

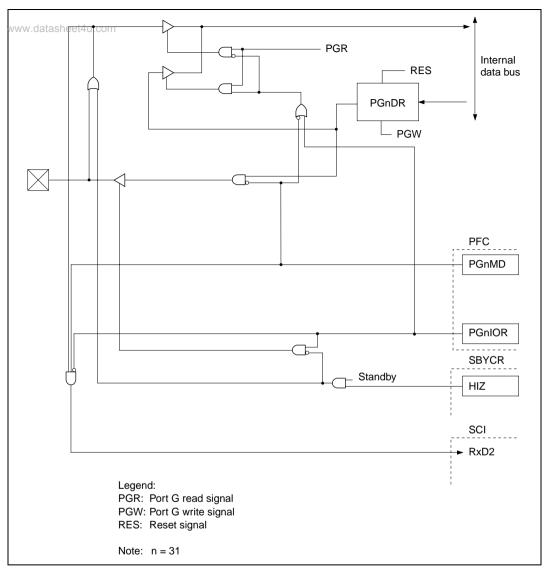

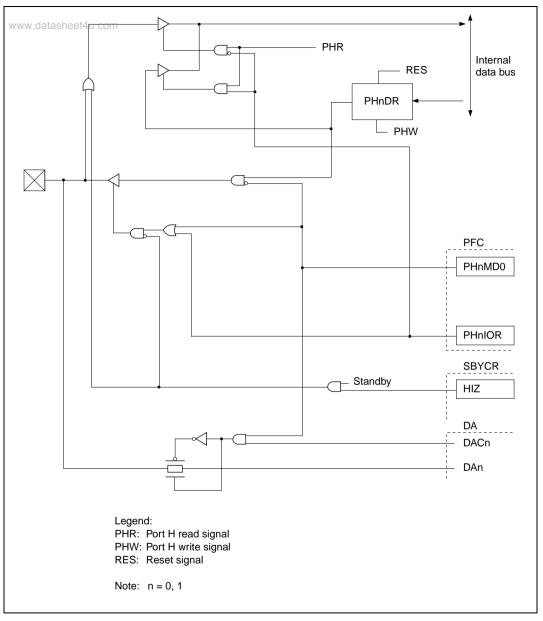

| Appe | endix C   | I/O Port Block Diagrams                                                                                                | 862 |

| Appe | endix D   | Restrictions and Caution on HD64F7065S                                                                                 |     |

|      |           | (and HD64F7065A Lots Prior to "1D5")                                                                                   | 910 |

| D.1  | BSC Re    | strictions                                                                                                             | 910 |

| D.2  | Restrict  | ons in Case of Contention between DSP Instruction and DMAC Transfer                                                    | 910 |

| D.3  | Pin State | e Related Restrictions                                                                                                 | 911 |

| D.4  | Caution   | Concerning Electrical Characteristics                                                                                  | 911 |

| D.5  | DMAC      | Restrictions                                                                                                           | 911 |

| D.6  |           | ons about Changing the Saturation Operation Mode during the Execution ply/Multiply and Accumulate, or DSP Instructions | 912 |

|      |           |                                                                                                                        |     |

| App  | endix E   | Product Lineup                                                                                                         | 914 |

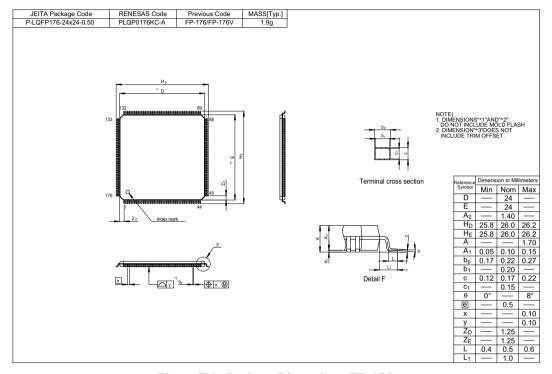

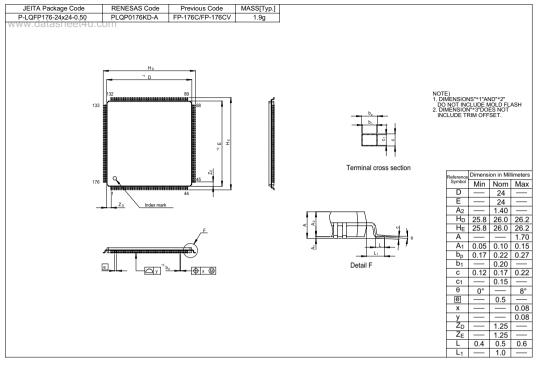

| Appe | endix F   | Package Dimensions                                                                                                     | 915 |

## Section 1 Overview

www.datasheet4u.com

### 1.1 Features of SH7065

The SH7065 is a CMOS single-chip microcomputer featuring an SH2-DSP core—a functionally enhanced version of the SuperH RISC engine using an original Renesas Technology architecture—with the same signal processing capability as a general-purpose digital signal processor (DSP), together with peripheral functions required for system configuration.

The SH2-DSP core offers enhancement of the DSP functions (multiply and multiply-and-accumulate) of the SuperH RISC engine, and provides full DSP type data bus functionality, enabling efficient execution of various kinds of signal processing and image processing. With this CPU, it has become possible to create low-cost, high-performance/high-functionality systems even for applications such as realtime control, which could not previously be handled by microcomputers because of their high-speed processing requirements.

In addition, the SH7065 includes on-chip peripheral functions necessary for system configuration, such as large-capacity ROM and RAM, timers, a serial communication interface (SCI), A/D converter, D/A converter, interrupt controller (INTC), and I/O ports. An external memory access support function allows efficient connection of memory and peripheral LSIs, greatly reducing system cost.

There are two versions of the SH7065, with different kinds of on-chip ROM: an F-ZTAT version with on-chip flash memory, and a mask ROM version. In the F-ZTAT version, programs can be written and rewritten with a Renesas-recommended ROM programmer, or on-board.

### Table 1.1 Features

www.datasheet4u.com

| ILEI | •• |  |

|------|----|--|

|      |    |  |

### **Specifications**

### CPU

- Original Renesas Technology architecture

- 32-bit internal configuration

- General register machine

- Sixteen 32-bit general registers

- Six 32-bit control registers (including three added for DSP use)

- Ten 32-bit system registers (including six added for DSP use)

- RISC (reduced instruction set computer) type instruction set

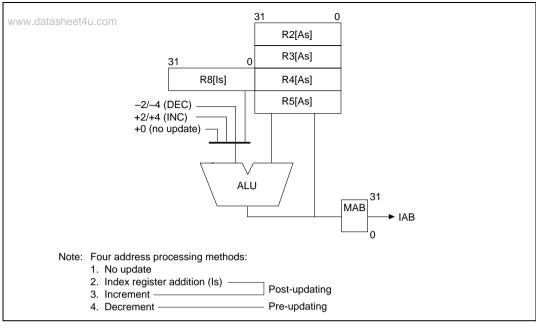

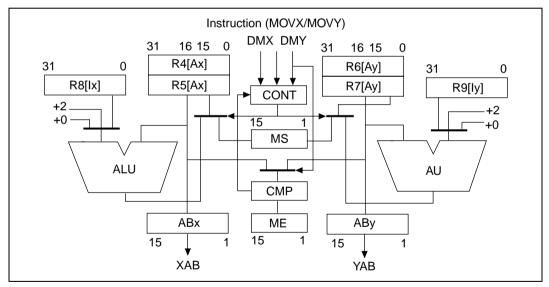

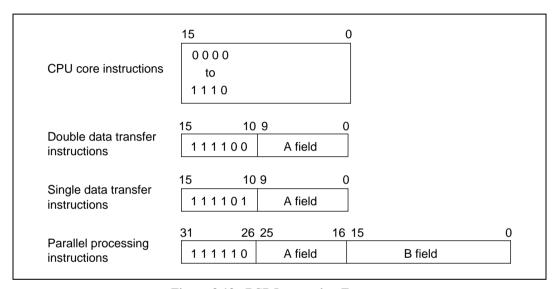

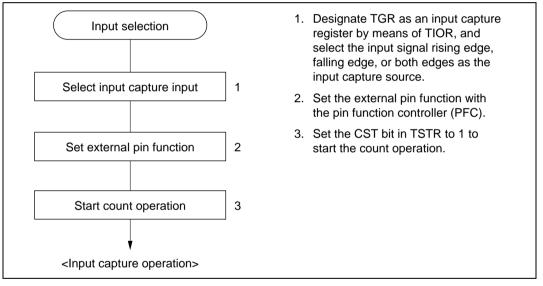

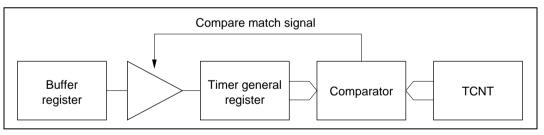

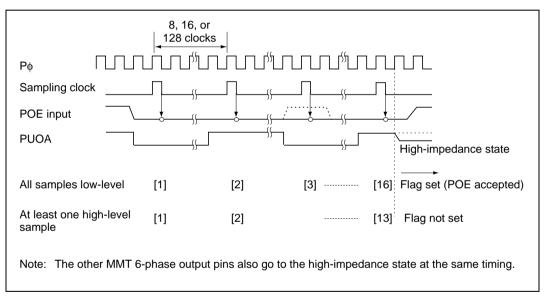

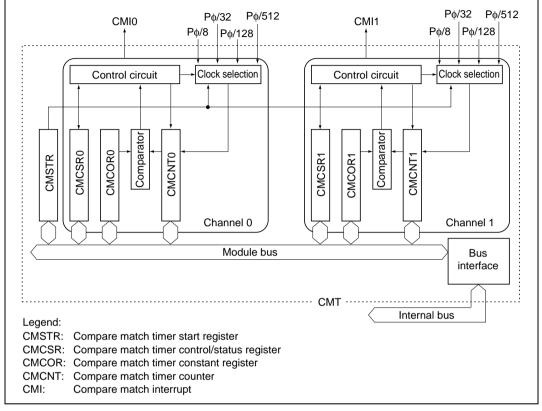

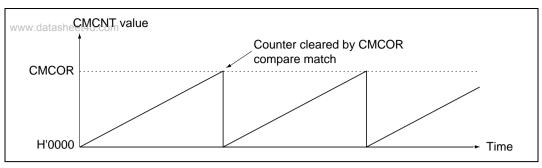

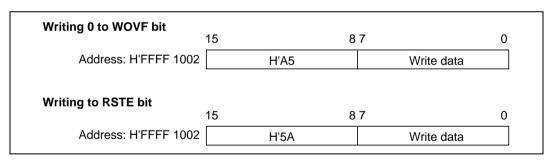

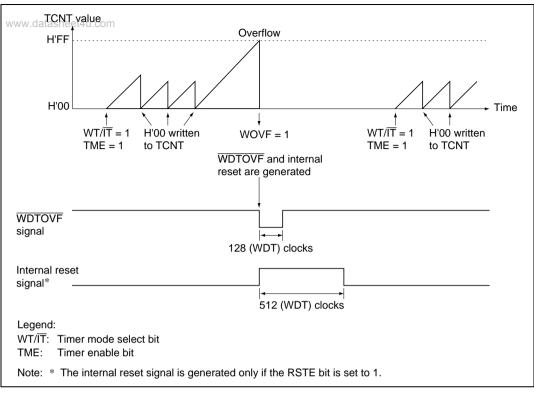

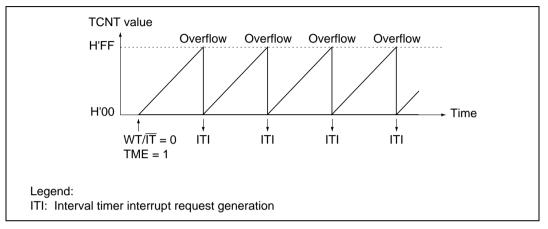

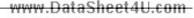

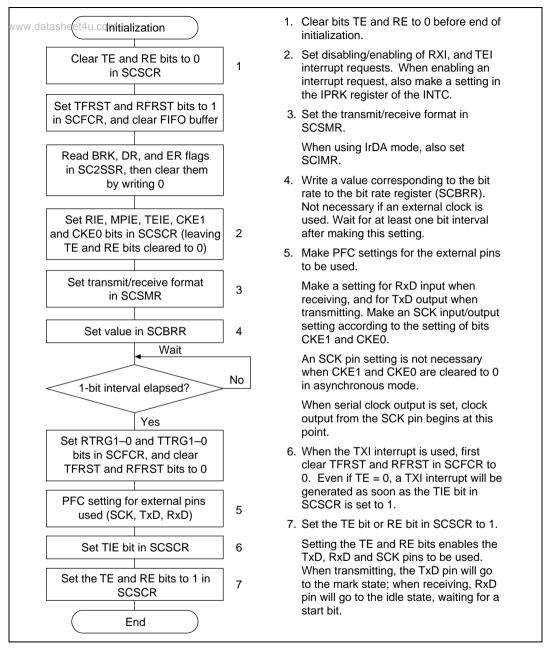

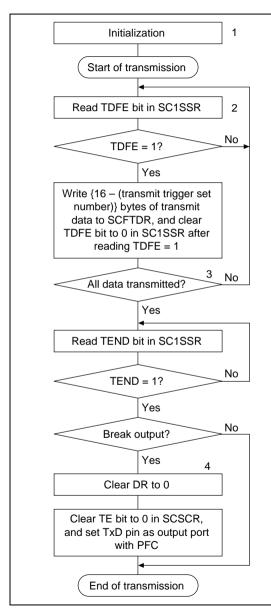

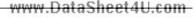

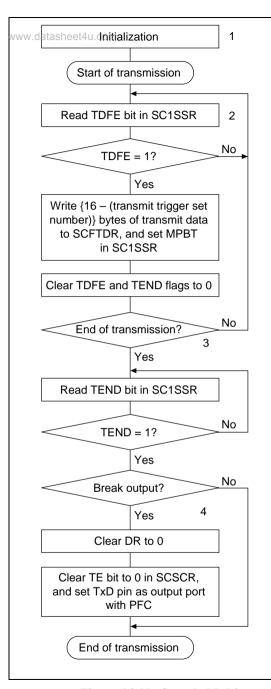

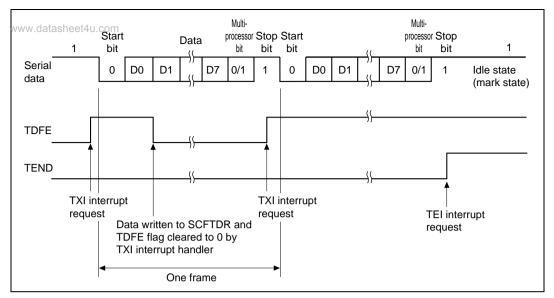

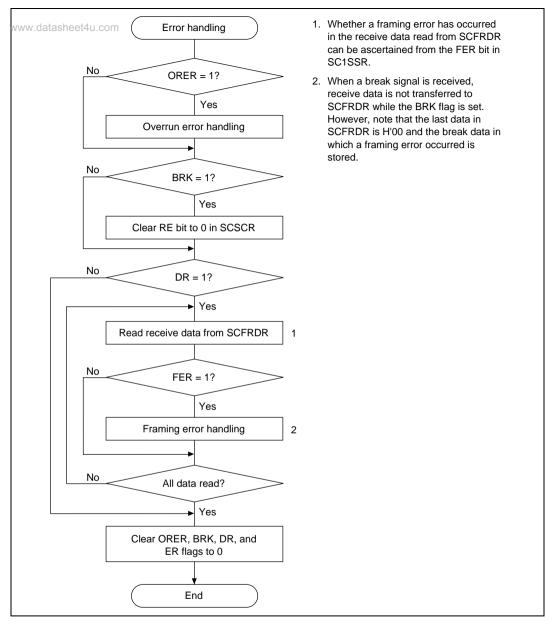

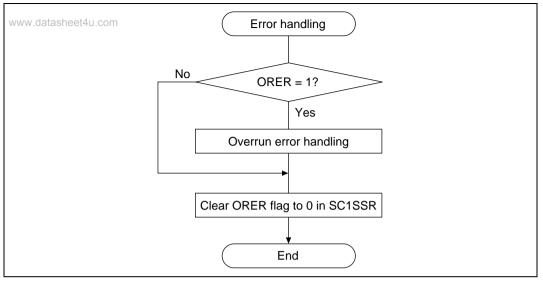

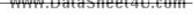

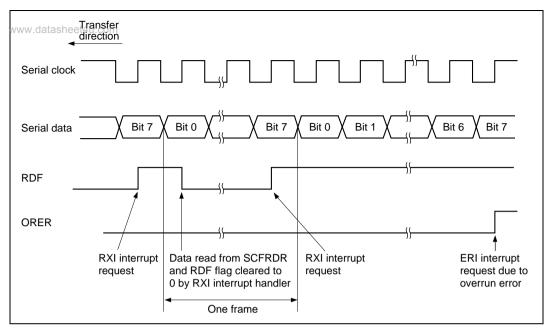

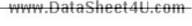

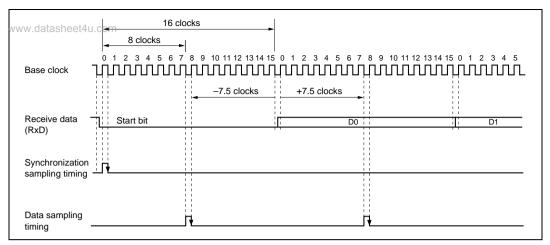

- Fixed 16-bit instruction length for improved code efficiency