# Windows<sup>®</sup> CE Intelligent Peripheral Controller HD64465

User's Manual

# HITACHI

# www.DataSheet4U.com

ADE-602-168B

Rev. 3.0 03/08/01 Hitachi Ltd.

#### Cautions

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- 2. Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# www.DataSheet4U.com

# Revisions and Additions in this Edition

| Page | Item                                                          | Description                                                                                           |

|------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| -    | Description of register address                               | <former edition=""> 0xh</former>                                                                      |

|      |                                                               | <this edition=""> H'</this>                                                                           |

| -    | Description of HD64465BQ                                      | Add the description of new product "HD64465BQ"                                                        |

| -    | HD64465BP Specifications<br>Changed                           | <former edition=""><br/>PLL used in bypass mode and 48 MHz clock input into<br/>UCK terminal</former> |

|      |                                                               | <this edition=""><br/>PLL used in bypass mode</this>                                                  |

| 16   | Table 4.1 HD64465BP Signal                                    | Add the description of M12 to M15 pins                                                                |

| 17   | Names (by pin numbers in<br>alphabetical order)               | Add the description of N12 to N15, P12 to P15, R12 to R15 pins                                        |

|      |                                                               | Signal name of R1 pin                                                                                 |

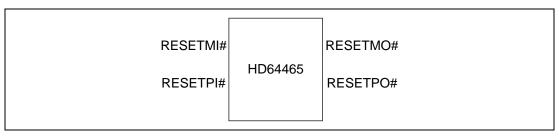

| 26   | Table 4.4 Pin Descriptions of<br>CPU Interface                | <pre> <former edition="">   RESET#</former></pre>                                                     |

|      |                                                               | <this edition=""></this>                                                                              |

|      |                                                               | RESETPI#                                                                                              |

| 39   | Table 4.24 Pin Descriptions of                                | Correct the table name                                                                                |

|      | No Connected Pins                                             | <former edition=""><br/>Pin Descriptions of LCD Interface</former>                                    |

|      |                                                               | <this edition=""></this>                                                                              |

|      |                                                               | Pin Descriptions of No Connected Pins                                                                 |

|      | Table 4.25 Pin Descriptions of                                | Pin description of AVSS3                                                                              |

|      | Power/Ground                                                  | <former edition=""><br/>Ground for analog circuit (can not connected)</former>                        |

|      |                                                               | <this edition=""></this>                                                                              |

|      |                                                               | NC (No Connected Pin)                                                                                 |

| 52   | 6.3 Register Dexcription                                      | <former edition=""></former>                                                                          |

|      | Table 6.1 The Register List Of<br>Power Management and System | Register Size = 2<br>Access Size = 2                                                                  |

|      | Configuration                                                 | <this edition=""><br/>Register Size = 16<br/>Access Size = 16</this>                                  |

| Page | Item                                                      | Description                                                                                                                                                                                        |

|------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54   | 6.3.2 System Configuration                                | Add the following description                                                                                                                                                                      |

|      | Register (SCONFR)<br>Description of Bits 11 - 8           | Note that the relationship between HW[3:0] and CPU programmed inserted wait states (IWS) is $2 \le 1 \text{ WS} \le 1 + \text{HW}[3:0]$ . Hence, the CPU default inserted wait states should be 2. |

| 58   | 6.3.4 System Peripheral Clock<br>Control Register (SPCCR) | <former edition=""><br/>Note: The parameter, Twkst, please refer the AC<br/>timing specification.</former>                                                                                         |

|      |                                                           | <this edition=""><br/>Note: The parameter, Twkst = 15 ms</this>                                                                                                                                    |

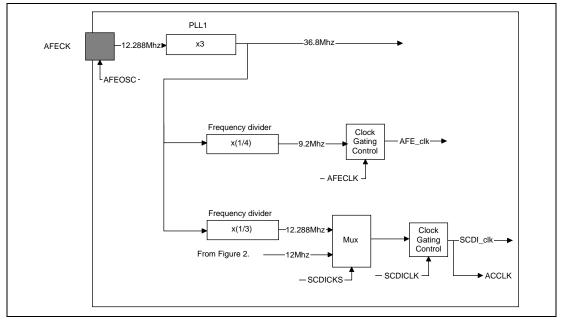

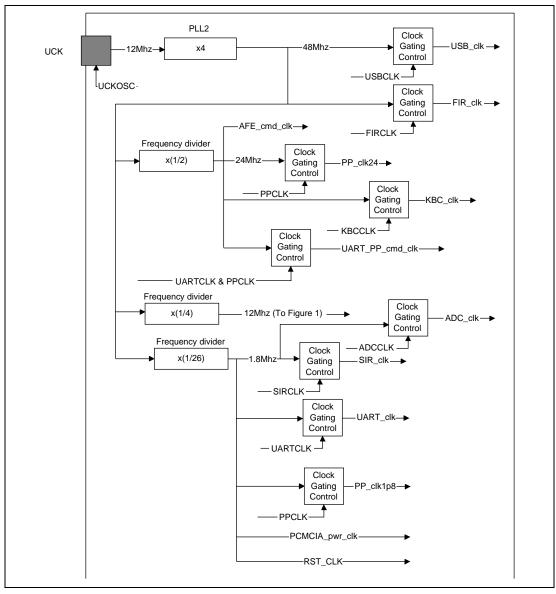

| 59   | Figure 6.1 AFECK & LCK<br>Related Clock Diagram           | Add the description of ACCLK pin                                                                                                                                                                   |

| 71   | 7.3.1 Port Data Register                                  | <former edition=""><br/>GPCDR Address: 100004018h</former>                                                                                                                                         |

|      |                                                           | <this edition=""><br/>GPEDR Address: H'100004018</this>                                                                                                                                            |

| 91   | Table 9.1 The Register List of<br>Timer Module            | <former edition=""><br/>Register Size = 2<br/>Access Size = 2</former>                                                                                                                             |

|      |                                                           | <this edition=""><br/>Register Size = 16<br/>Access Size = 16</this>                                                                                                                               |

| 93   | 9.2.3 TRVR1:Timer 1 Read Vlue<br>Register                 | <former edition=""> R/W value = R/O<br/><this edition=""> R/W value = R</this></former>                                                                                                            |

| 94   | 9.2.4 TRVR0:Timer 0 Read<br>Value Register                |                                                                                                                                                                                                    |

| 99   | 9.2.9 PWM1CS: PWM1 Clock<br>Scale Register                | Delete the default value                                                                                                                                                                           |

|      | Bits 5 - 0                                                |                                                                                                                                                                                                    |

| 102  | 9.2.12 PWM0CS: PWM0 Clock<br>Scale Register               | -                                                                                                                                                                                                  |

|      | Bits 5 - 0                                                |                                                                                                                                                                                                    |

| 121  | 10.4.8 PCC1 General Control                               | Description of bit 7                                                                                                                                                                               |

|      | Register (PCC1GCR)                                        | <former edition=""> PCC0</former>                                                                                                                                                                  |

|      |                                                           | <this edition=""> PCC1</this>                                                                                                                                                                      |

|      |                                                           | Description of bit 4                                                                                                                                                                               |

|      |                                                           | <former edition=""> VCC0SEL1</former>                                                                                                                                                              |

|      |                                                           | <this edition=""> VCC1SEL0</this>                                                                                                                                                                  |

| Page     | Item                                                                              | Description                  |         |                |

|----------|-----------------------------------------------------------------------------------|------------------------------|---------|----------------|

| 152      | (26) Timing control Register<br>(ITMCR)                                           | Delete the default           | value   |                |

|          | Bits 5 - 0                                                                        |                              |         |                |

| 176      | (2) ECP Address FIFO Register                                                     | Default value of bi          | its 2 - | 0              |

|          | (ECPAFifo)                                                                        | <former edition=""></former> | 111b    |                |

|          |                                                                                   | <this edition=""> 11</this>  | 1       |                |

|          | (4) Device Control Register (der)                                                 | Default value of bi          | its 2 - | 0              |

|          | (Address H'1000A004, Mode All)                                                    | <former edition=""></former> | 11b     |                |

|          |                                                                                   | <this edition=""> 11</this>  |         |                |

| 227      | Table 14.3 AC97 Timing                                                            | <former edition=""></former> | Unit :  | Us<br>Ns       |

|          |                                                                                   | <this edition=""> Un</this>  | it :    | μs<br>ns       |

| 336      | 19.2.1 A/D Data Registers A to D<br>(ADDRA to ADDRD, ADCAL)                       | <former edition=""></former> |         | : AD8<br>: AD9 |

|          |                                                                                   | <this edition=""></this>     |         | : AD9<br>: AD8 |

| 341      | 19.3.2 Acan Mode (SCAN = 1)                                                       | Add the ADCSR ta             | able    |                |

| 352, 353 | Table 20.13 AFECK clock input<br>AC Timing Spec. (PLL1:bypass)<br>(unit : ns)     | New tables added             | l       |                |

|          | Table 20.14 AFECK clock input<br>AC Timing Spec.<br>(PLL1:operatings) (unit : ns) |                              |         |                |

|          | Table 20.15 AFECK clock input<br>AC Timing Spec. (PLL2:bypass)<br>(unit : ns)     |                              |         |                |

|          | Table 20.16 AFECK clock input<br>AC Timing Spec.<br>(PLL2:operating) (unit : ns)  |                              |         |                |

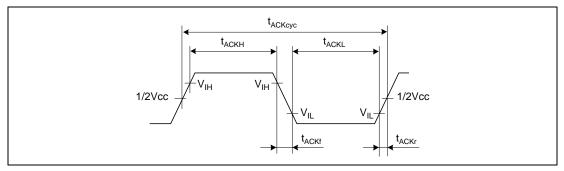

| 363, 364 | Figure 20.26 AFECK Clock Input<br>Timing                                          | New figures adde             | d       |                |

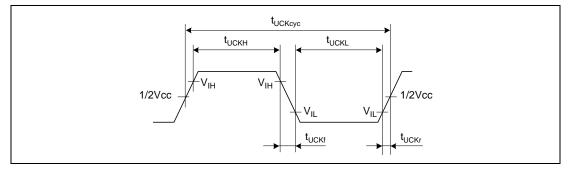

|          | Figure 20.27 UCK Clock Input<br>Timing                                            |                              |         |                |

# HD64465BP Specifications Changed

#### 1. Change in Specifications

| Item changed           | Guaranteed value before change | Guaranteed value after change |

|------------------------|--------------------------------|-------------------------------|

| PLL stabilization time | 5ms                            | Not guaranteed                |

2. Major Influences Due to Above Change in Specifications

| Preconditions                                           | Problems in usage                                                 |

|---------------------------------------------------------|-------------------------------------------------------------------|

| PLL used in bypass mode                                 | No problem (no standby time added)                                |

| Reset signal input after turning power on               | No problem (no standby time added)                                |

| PLL standby not used although oscillation stop used     | No problem (no standby time added)                                |

| Certain interval allowed between PLL standby and wakeup | Several seconds may be required for access by HD64465BP from CPU. |

- 3. Countermeasures

- Use the system in a state without any problem by referring to "2." above.

- Create your program in a way to prohibit access other than to the HD64465BP system configuration register (offset address: H'00000000 to H'00000ff0) for a certain period of time after returning from PLL standby.

- 4. Debugged Version

The cause of this problem has already been clarified, which can be solved by correcting the wiring layer. The new mask product (HD64465EBP) is available as the debugged version.

# Contents

| Sect | ion 1   | Features                       | 1  |

|------|---------|--------------------------------|----|

| 1.1  | CPU I   | nterface                       | 1  |

| 1.2  | PCMC    | CIA Controller                 | 1  |

| 1.3  | AFE I   | nterface                       | 1  |

| 1.4  | GPIO    | Function(Port Interrupt)       | 1  |

| 1.5  | Interru | pt Controller                  | 2  |

| 1.6  | Power   | Management                     | 2  |

| 1.7  | Timer   |                                | 2  |

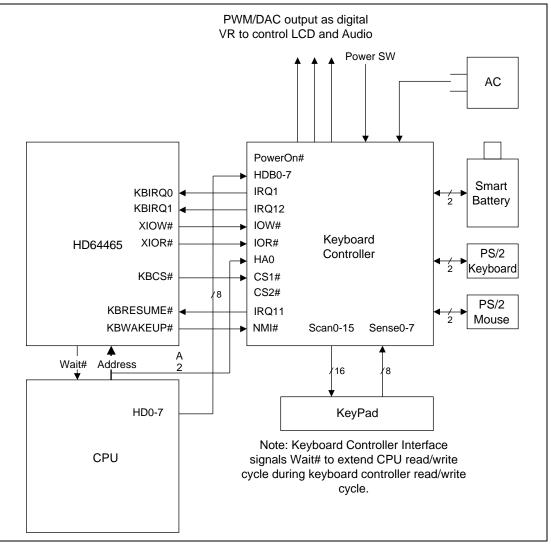

| 1.8  | Keybo   | ard Controller Interface       | 2  |

| 1.9  | UART    | ۰                              | 2  |

| 1.10 | Printer | r interface                    | 3  |

| 1.11 | Audio   | CODEC Interface                | 3  |

| 1.12 |         |                                |    |

| 1.13 | Clock   | Generator and PLL              | 3  |

| 1.14 | USB H   | Host Controller                | 4  |

| 1.15 | 10-bit  | ADC                            | 4  |

| 1.16 | Packag  | ge                             | 4  |

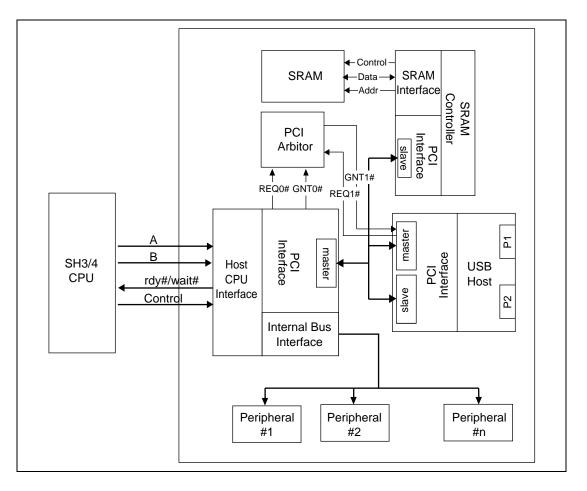

| Sect | ion 2   | General Description            | 5  |

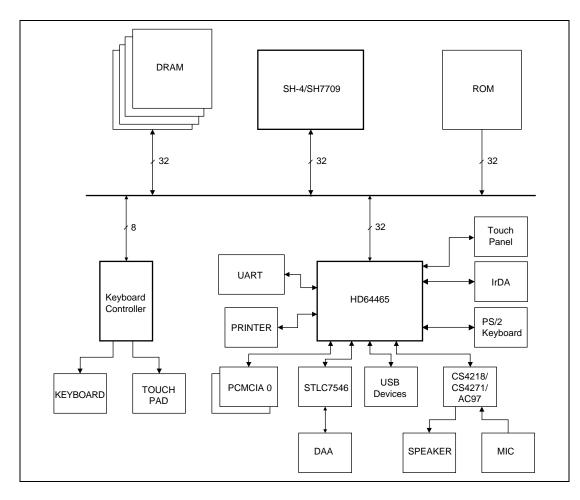

| Sect | ion 3   | System Block Diagram           | 7  |

| 3.1  | Applic  | cation Circuit                 | 7  |

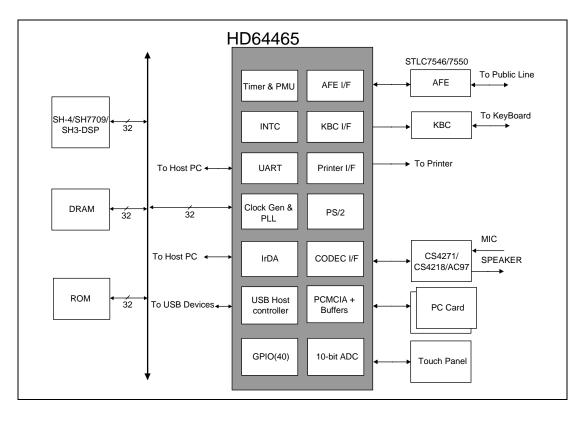

| 3.2  | Systen  | n Block Diagram                | 8  |

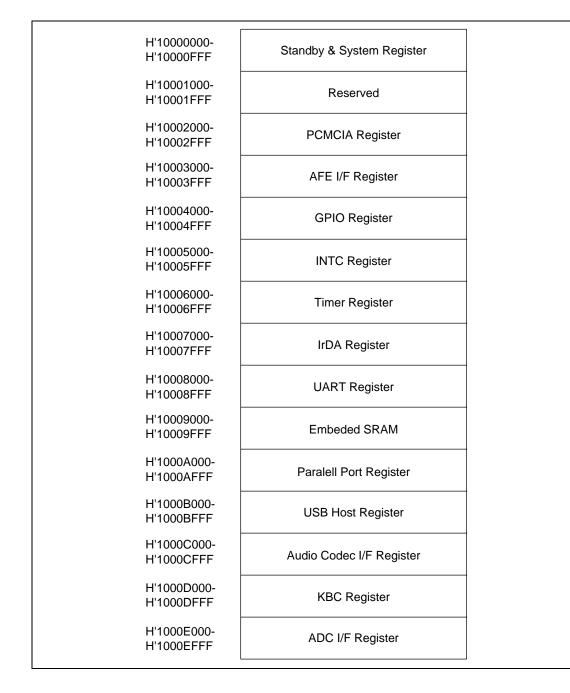

| 3.3  | Physic  | al Address Space               | 9  |

| 3.4  | HD64    | 465 Memory Address             | 10 |

| 3.5  | Pin Co  | onfiguration                   | 11 |

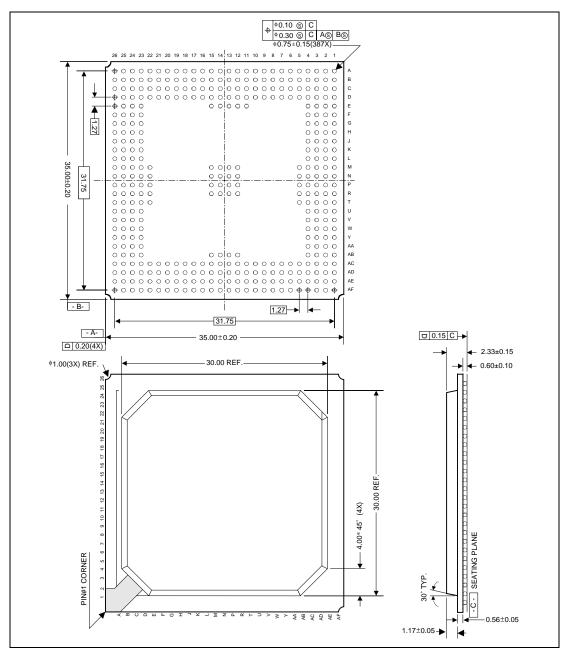

|      | 3.5.1   | HD64465BP Top View             | 11 |

|      | 3.5.2   | HD64465BP Bottom View          | 12 |

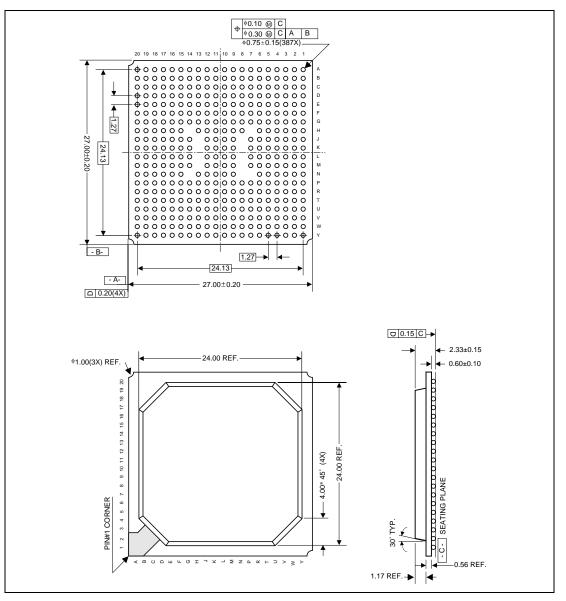

|      | 3.5.3   | HD64465BQ Top View             | 13 |

|      | 3.5.4   | HD64465BQ Bottom View          | 14 |

| Sect | ion 4   | Pin Description                | 15 |

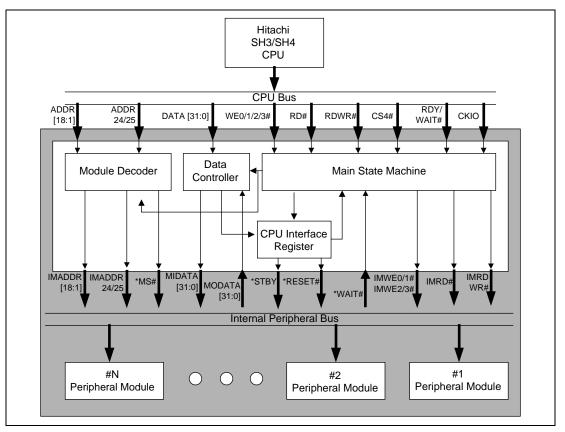

| Sect | ion 5   | Internal CPU Interface         | 41 |

| 5.1  | Introd  | uction                         |    |

| 5.2  |         | nterface Signal Description    |    |

|      | 5.2.1   | System Bus Interface Signals   |    |

|      | 5.2.2   | Internal Bus Interface Signals |    |

| 5.3  | Functi  | on Description                 |    |

|      |         |                                |    |

Rev. 3.0, 03/01, page i of xiii

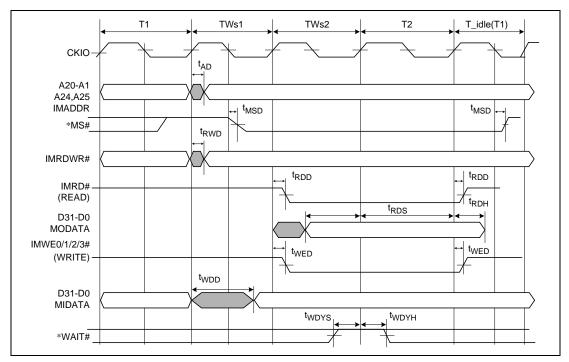

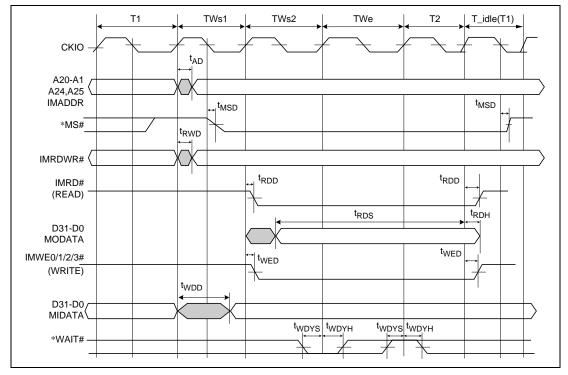

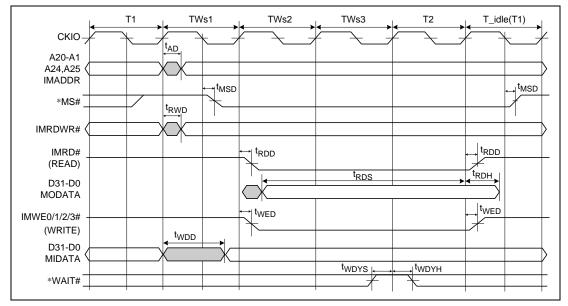

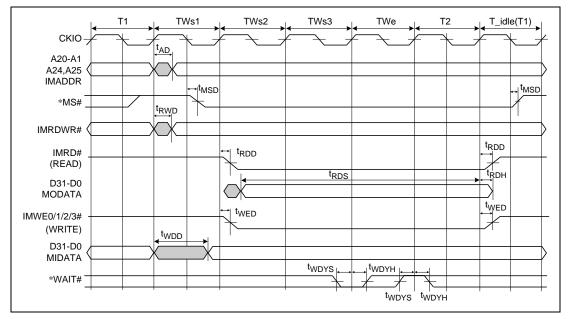

| 5.4                                           | Signal                                                                                                                                                                 | Timing Description                                                                                                                                                                                                                                                                                                                             | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               | 5.4.1                                                                                                                                                                  | Low Speed Timing                                                                                                                                                                                                                                                                                                                               | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               | 5.4.2                                                                                                                                                                  | High Speed Timing                                                                                                                                                                                                                                                                                                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.5                                           | Interna                                                                                                                                                                | l Bus Data Swap Rules                                                                                                                                                                                                                                                                                                                          | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.6                                           | Interna                                                                                                                                                                | l Peripheral Bus AC Timing Specification                                                                                                                                                                                                                                                                                                       | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Secti                                         | ion 6                                                                                                                                                                  | Power Management and System Configuration                                                                                                                                                                                                                                                                                                      | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.1                                           |                                                                                                                                                                        | ew                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.2                                           |                                                                                                                                                                        | 28                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.3                                           |                                                                                                                                                                        | er Description                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0.5                                           | 6.3.1                                                                                                                                                                  | System Module Standby Control Register (SMSCR)                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.2                                                                                                                                                                  | System Configuration Register (SCONFR)                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.3                                                                                                                                                                  | System Bus Control Register (SBCR)                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.4                                                                                                                                                                  | System Peripheral Clock Control Register (SPCCR)                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.5                                                                                                                                                                  | System Peripheral S/W Reset Control Register (SPSRCR)                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.6                                                                                                                                                                  | System PLL Control Register (SPLLCR)                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.7                                                                                                                                                                  | System Revision Register (SRR)                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.3.8                                                                                                                                                                  | System Device ID Register (SDID)                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

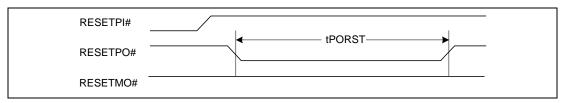

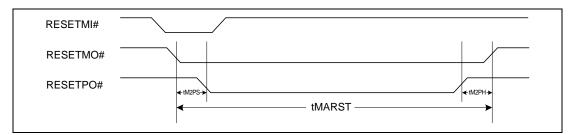

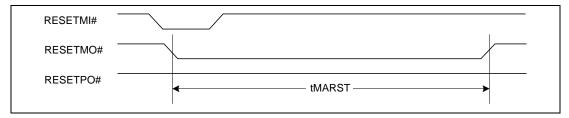

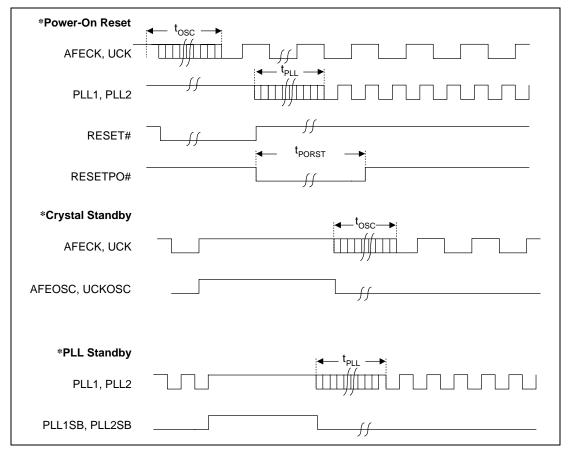

| 6.4                                           |                                                                                                                                                                        | h Hardware Reset Timing                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0.1                                           | 6.4.1                                                                                                                                                                  | Power-On Reset Output                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 6.4.2                                                                                                                                                                  | Manual Reset Output.                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               | 0.1.2                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                               |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

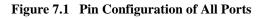

| Secti                                         | ion 7                                                                                                                                                                  | General Purpose I/O Port                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Secti<br>7.1                                  |                                                                                                                                                                        | ew                                                                                                                                                                                                                                                                                                                                             | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                               | Overvi<br>7.1.1                                                                                                                                                        | ew<br>Features                                                                                                                                                                                                                                                                                                                                 | 67<br>67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                               | Overvi<br>7.1.1                                                                                                                                                        | ew                                                                                                                                                                                                                                                                                                                                             | 67<br>67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.1                                           | Overvi<br>7.1.1<br>Registe                                                                                                                                             | ew<br>Features                                                                                                                                                                                                                                                                                                                                 | 67<br>67<br>69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.1<br>7.2                                    | Overvi<br>7.1.1<br>Registe                                                                                                                                             | ew<br>Features<br>er Configuration                                                                                                                                                                                                                                                                                                             | 67<br>67<br>69<br>70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7.1<br>7.2                                    | Overvi<br>7.1.1<br>Registe<br>Registe                                                                                                                                  | ew<br>Features<br>er Configuration<br>er Descriptions                                                                                                                                                                                                                                                                                          | 67<br>67<br>69<br>70<br>70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1<br>7.2                                    | Overvi<br>7.1.1<br>Registe<br>Registe<br>7.3.1                                                                                                                         | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register                                                                                                                                                                                                                                                                    | 67<br>67<br>70<br>70<br>72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1<br>7.2                                    | Overvi<br>7.1.1<br>Registe<br>7.3.1<br>7.3.2                                                                                                                           | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register                                                                                                                                                                                                                                           | 67<br>67<br>69<br>70<br>70<br>72<br>74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

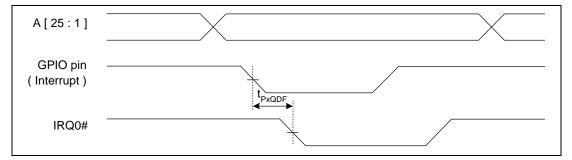

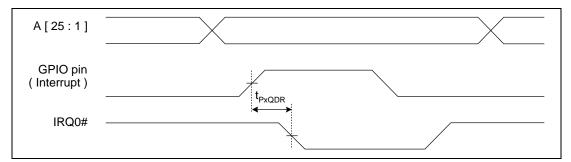

| <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Overvi<br>7.1.1<br>Registe<br>7.3.1<br>7.3.2<br>7.3.3                                                                                                                  | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register                                                                                                                                                                      | 67<br>67<br>70<br>70<br>70<br>72<br>74<br>76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.1<br>7.2<br>7.3                             | Overvi<br>7.1.1<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4                                                                                                         | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)                                                                                                                                       | 67<br>69<br>70<br>70<br>72<br>74<br>76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

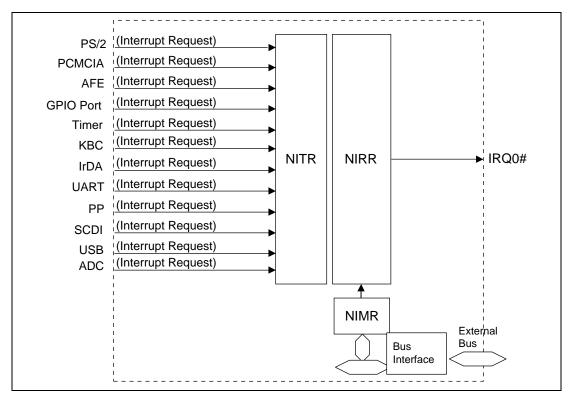

| <ul><li>7.1</li><li>7.2</li><li>7.3</li></ul> | Overvi<br>7.1.1<br>Registe<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4                                                                                                         | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew                                                                                                                                 | 67<br>69<br>70<br>70<br>70<br>70<br>71<br>74<br>76<br>79<br>79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.1<br>7.2<br>7.3                             | Overvi<br>7.1.1<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1                                                                             | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features                                                                                                                     | 67<br>67<br>70<br>70<br>72<br>74<br>76<br>79<br>79<br>79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7.1<br>7.2<br>7.3                             | Overvi<br>7.1.1<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2                                                                    | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram                                                                                                    | 67<br>67<br>70<br>70<br>72<br>74<br>76<br>79<br>79<br>79<br>80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.1<br>7.2<br>7.3                             | Overvi<br>7.1.1<br>Registe<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2<br>8.1.3                                                           | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram<br>Pin Configuration                                                                               | 67<br>69<br>70<br>70<br>72<br>74<br>74<br>76<br>79<br>79<br>79<br>79<br>80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1<br>7.2<br>7.3<br>Secti<br>8.1             | Overvi<br>7.1.1<br>Registe<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4                                                  | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration                                                     | 67<br>67<br>70<br>70<br>72<br>74<br>76<br>79<br>79<br>80<br>80<br>80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7.1<br>7.2<br>7.3                             | Overvi<br>7.1.1<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Interru                                       | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>pt Sources                                       | 67<br>67<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>74<br>76<br>70<br>70<br>74<br>76<br>78<br>78<br>78<br>78<br>78<br>78<br>79<br>78<br>78<br>79<br>79<br>79<br>78<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>79<br>80<br>80<br>80<br>80<br>80<br>80<br>80<br>                                                                                                         |

| 7.1<br>7.2<br>7.3<br>Secti<br>8.1             | Overvi<br>7.1.1<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Interru<br>8.2.1                              | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>pt Sources<br>On-Chip Module Interrupt           | 67<br>67<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>70<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71<br>71 |

| 7.1<br>7.2<br>7.3<br>Secti<br>8.1<br>8.2      | Overvi<br>7.1.1<br>Regista<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Interru<br>8.2.1<br>8.2.2          | ew<br>Features<br>er Configuration<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Pin Configuration<br>pt Sources<br>On-Chip Module Interrupt | 67<br>67<br>70<br>70<br>72<br>74<br>74<br>76<br>79<br>80<br>80<br>81<br>81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1<br>7.2<br>7.3<br>Secti<br>8.1             | Overvi<br>7.1.1<br>Regista<br>Regista<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.4<br>ion 8<br>Overvi<br>8.1.1<br>8.1.2<br>8.1.3<br>8.1.4<br>Interru<br>8.2.1<br>8.2.2<br>NIRR: | ew<br>Features<br>er Configuration<br>er Descriptions<br>Port Data Register<br>Port Control Register<br>Port Interrupt Control Register<br>Port Interrupt Status Register<br>Interrupt Controller (INTC)<br>ew<br>Features<br>Block Diagram<br>Pin Configuration<br>Register Configuration<br>pt Sources<br>On-Chip Module Interrupt           | 67<br>67<br>70<br>70<br>72<br>74<br>74<br>76<br>79<br>80<br>80<br>81<br>81<br>81<br>82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 8.5   | NITR:  | Interrupt Trigger Mode Register                                | 86  |

|-------|--------|----------------------------------------------------------------|-----|

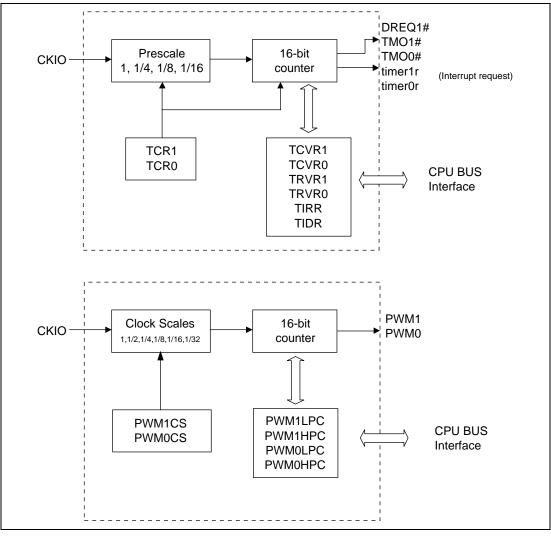

| Secti | ion 9  | Timer                                                          | 89  |

| 9.1   | Overvi | ew                                                             | 89  |

|       | 9.1.1  | Features                                                       | 89  |

|       | 9.1.2  | Block Diagram                                                  | 90  |

|       | 9.1.3  | Pin Configuration                                              | 91  |

|       | 9.1.4  | Register Configuration                                         | 91  |

| 9.2   | Timer  | Register                                                       |     |

|       | 9.2.1  | TCVR1: Timer 1 Constant Value Register                         | 92  |

|       | 9.2.2  | TCVR0: Timer 0 Constant Value Register                         |     |

|       | 9.2.3  | TRVR1: Timer 1 Read Value Register                             |     |

|       | 9.2.4  | TRVR0: Timer 0 Read Value Register                             |     |

|       | 9.2.5  | TCR1: Timer 1 Control Register                                 |     |

|       | 9.2.6  | TCR0: Timer 0 Control Register                                 |     |

|       | 9.2.7  | TIRR: Timer Interrupt Request Register                         |     |

|       | 9.2.8  | TIDR*: Timer Interrupt Disable Register                        |     |

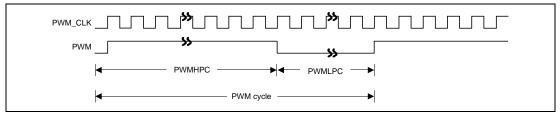

|       | 9.2.9  | PWM1CS: PWM 1 Clock Scale Register                             |     |

|       | 9.2.10 | PWM1LPC: PWM 1 Low Pulse Width Counter Register                |     |

|       | 9.2.11 | -                                                              |     |

|       | 9.2.12 | PWM0CS: PWM 0 Clock Scale Register                             |     |

|       |        | PWM0LPC: PWM 0 Low Pulse Width Counter Register                |     |

|       |        | PWM0HPC: PWM 0 High Pulse Width Counter Register               |     |

| 9.3   |        | Register Programming Sequence                                  |     |

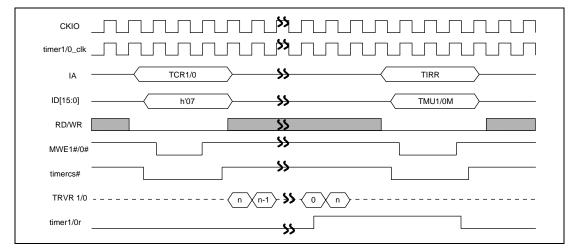

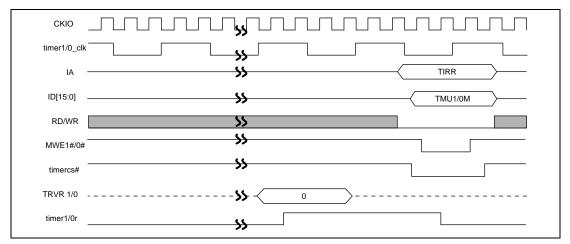

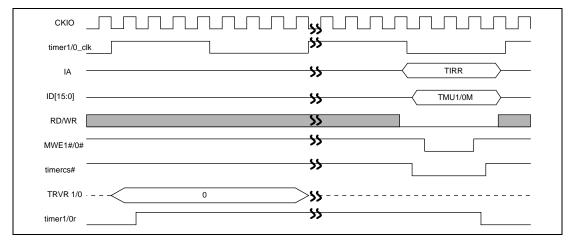

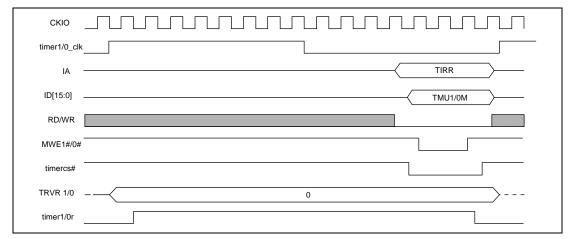

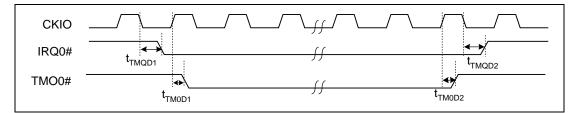

| 9.4   |        | pt Timing                                                      |     |

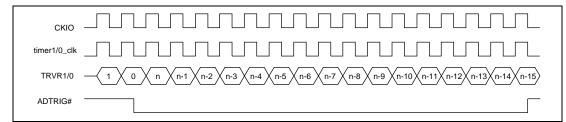

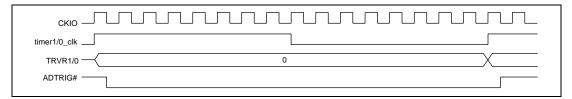

| 9.5   |        | igger Signal ADTRIG#                                           |     |

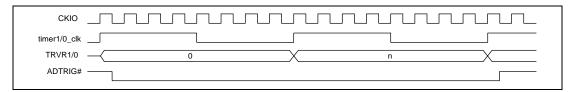

| 9.6   |        | Request Enable Function                                        |     |

| 9.7   |        | Operation                                                      |     |

| Saat  | ion 10 | PC Card Controller (PCC)                                       | 100 |

|       |        |                                                                |     |

| 10.1  |        | ew                                                             |     |

| 10.2  |        | 28                                                             |     |

| 10.3  | -      | er Configuration                                               |     |

| 10.4  | 0      | er Description                                                 |     |

|       |        | PCC0 Interface Status Register (PCC0ISR)                       |     |

|       |        | PCC0 General Control Register (PCC0GCR)                        |     |

|       | 10.4.3 |                                                                |     |

|       | 10.4.4 | PCC0 Card Status Change Interrupt Enable Register (PCC0CSCIER) |     |

|       | 10.4.5 | PCC0 Software Control Register (PCC0SCR)                       |     |

|       | 10.4.6 | PCC Serial Power Switch Control Register (PCCPSR)              |     |

|       | 10.4.7 | PCC1 Interface Status Register (PCC1ISR)                       |     |

|       | 10.4.8 | PCC1 General Control Register (PCC1GCR)                        |     |

|       | 10.4.9 | PCC1 Card Status Change Register (PCC1CSCR)                    | 123 |

Rev. 3.0, 03/01, page iii of xiii

|      | 10.4.10   | ) PCC1 Card Status Change Interrupt Enable Register (PCC1CSCIER) | 125 |

|------|-----------|------------------------------------------------------------------|-----|

|      | 10.4.1    | PCC1 Software Control Register (PCC1SCR)                         | 127 |

|      |           |                                                                  |     |

|      |           | FIR Module                                                       |     |

| 11.1 |           | ew                                                               |     |

|      |           | Features                                                         |     |

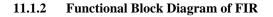

|      | 11.1.2    | Functional Block Diagram of FIR                                  | 130 |

| 11.2 |           | ontroller Register Description                                   |     |

|      | 11.2.1    | UART Register of FIR Portion                                     | 132 |

|      |           | FIR Controller Register                                          |     |

|      | 11.2.3    | Register Description                                             | 134 |

| 11.3 | FIR Tr    | ansmit Operation                                                 | 153 |

| 11.4 | FIR Re    | eceive Operation                                                 | 154 |

| 11.5 | Examp     | le of Initialization and Programming Procedure for HP-SIR        | 156 |

| Sect | ion 12    | UART                                                             | 157 |

| 12.1 | Overvi    | ew                                                               | 157 |

| 12.2 | Feature   | 28                                                               | 157 |

| 12.3 |           | Channel Register Description                                     |     |

|      |           | Data Register                                                    |     |

|      |           | Control Registers: UIER, UIIR, UFCR, UDLL, UDLM, ULCR, UMCR      |     |

|      |           | Status Register ULSR and UMSR                                    |     |

| 12.4 |           |                                                                  |     |

| 12.5 |           | mming                                                            |     |

| 12.0 | -         | Programming Sequence                                             |     |

| 12.6 |           | re Reset                                                         |     |

| 12.7 |           | Input Operation                                                  |     |

| 12.7 |           | nterrupt Mode Operation                                          |     |

| 12.9 |           | ION                                                              |     |

| Seat | ion 12    | Parallel Port                                                    | 171 |

|      |           |                                                                  |     |

| 13.1 |           | ew                                                               |     |

| 13.2 |           | 28                                                               |     |

| 13.3 |           | Port Register Description                                        |     |

|      |           | SPP and EPP Modes                                                |     |

|      | 13.3.2    | ECP Mode                                                         | 174 |

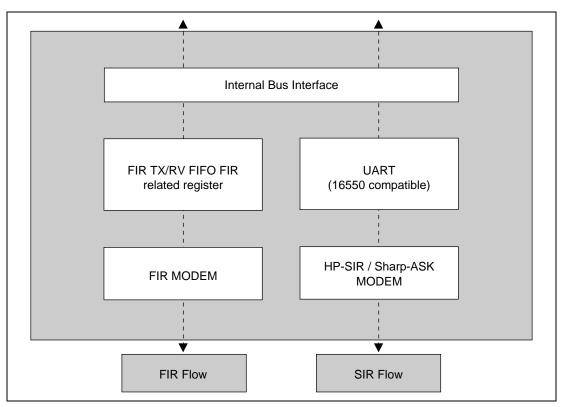

|      | ion 14    | Serial CODEC Interface                                           | 181 |

| 14.1 |           | ew                                                               |     |

|      |           | Features                                                         |     |

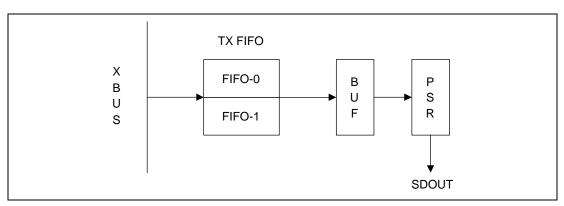

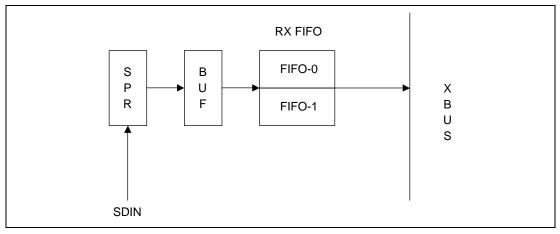

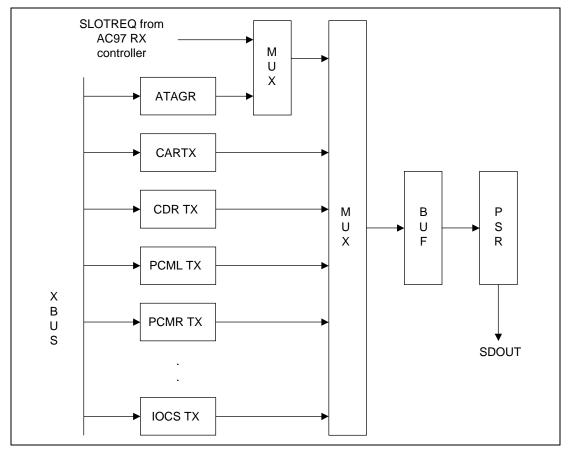

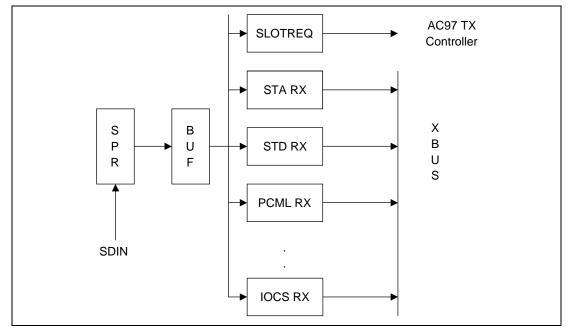

|      |           | Block Diagram                                                    |     |

| 14.2 | Registe   | er Description                                                   | 183 |

|      | 14.2.1    | Transmit Data Register (TDR)                                     | 184 |

| Rev. | 3.0, 03/0 | )1, page iv of xiii                                              |     |

|      | 14.2.2  | Receive Data Register (RDR)                      | 185  |

|------|---------|--------------------------------------------------|------|

|      | 14.2.3  | Control Register (CR)                            | 186  |

|      | 14.2.4  | Status Register (SR)                             | 187  |

|      | 14.2.5  | Frequency Select Register                        | .189 |

|      | 14.2.6  | Command/Status Address Register (CSAR)           | .190 |

|      | 14.2.7  | Command/Status Data Register (CSDR)              | .191 |

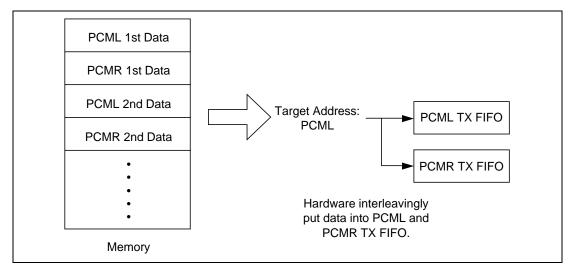

|      | 14.2.8  | PCM Playback/Record Left Channel (PCML)          | .192 |

|      |         | PCM Playback/Record Right Channel (PCMR)         |      |

|      | 14.2.10 | Line 1 Data Register (LINE1)                     | .194 |

|      | 14.2.11 | PCM Center Playback/MIC ADC Channel (PCMC)       | .195 |

|      | 14.2.12 | PCM Left Surround Channel Data Register (PCMLS)  | .196 |

|      | 14.2.13 | PCM Right Surround Channel Data Register (PCMRS) | .197 |

|      | 14.2.14 | PCMLFE Data Register (PCMLFE)                    | .198 |

|      | 14.2.15 | Line 2 Channel Data Register (LINE2)             | .199 |

|      | 14.2.16 | HSET Data Register (HSET)                        | .200 |

|      | 14.2.17 | IO Control/Status Data Register (IOCS)           | .201 |

|      |         | AC97 Transmit Interrupt Enable Register (ATIER)  |      |

|      |         | AC97 TX FIFO Status Register                     |      |

|      | 14.2.20 | AC97 RX FIFO Interrupt Enable Register (ARIER)   | .208 |

|      | 14.2.21 | AC97 RX Status Register (ARSR)                   | .211 |

|      | 14.2.22 | AC97 Control Register (ACR)                      | .213 |

|      | 14.2.23 | AC97 TAG Register (ATAGR)                        | .215 |

|      | 14.2.24 | Slot Request Active Register (SRAR)              | .216 |

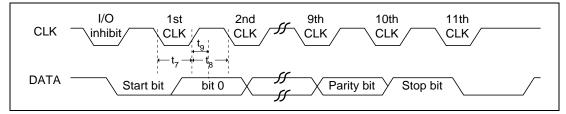

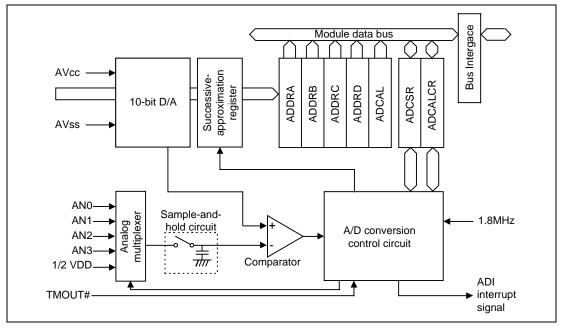

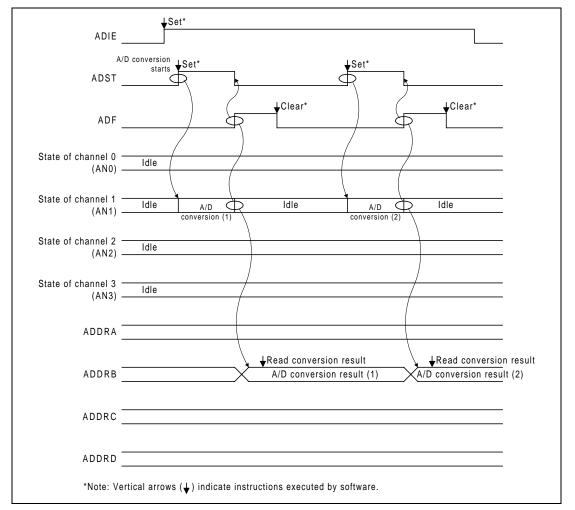

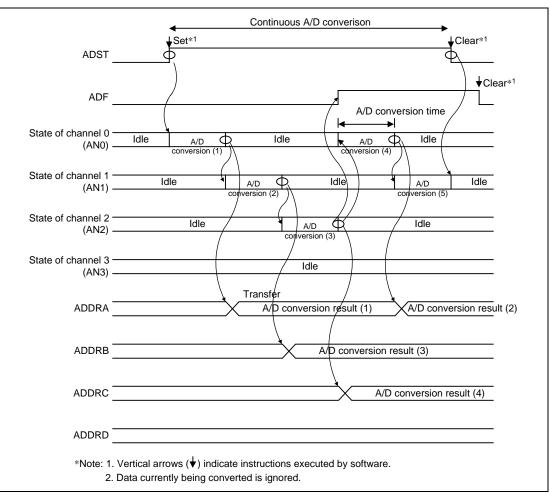

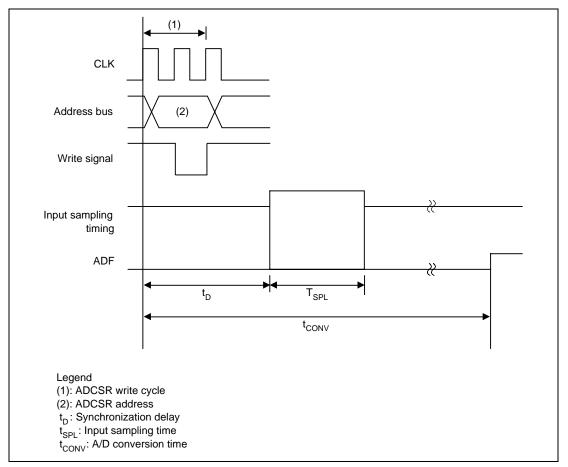

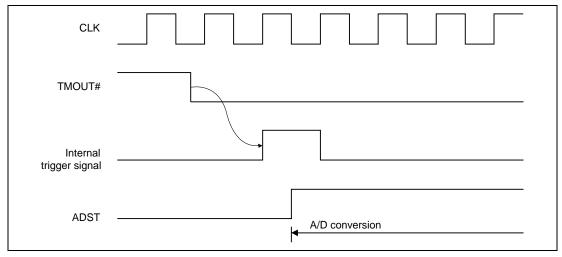

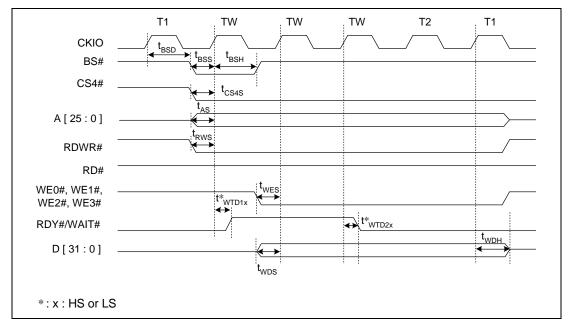

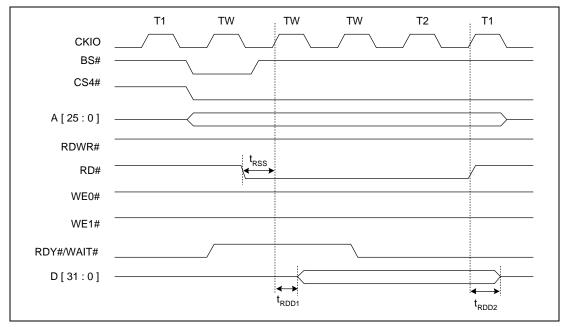

| 14.3 | Functio | n Description                                    | .217 |