# Information regarding change of names mentioned within this document, to Renesas Technology Corp.

On April 1<sup>st</sup> 2003 the following semiconductor operations were transferred to Renesas Technology Corporation: operations covering microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.).

Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have all been changed to Renesas Technology Corporation.

Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Thank you for your understanding.

Renesas Technology Home Page: www.renesas.com

Renesas Technology Corp. April 1, 2003

## SuperH<sup>TM</sup> RISC engine Peripheral LSI

# HD64404

Hardware Manual

# **HITACHI**

ADE-607-042

Rev. 1.0 09/13/02 Hitachi, Ltd.

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

### **General Precautions on Handling of Product**

#### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are they are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

#### 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

#### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

#### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

### Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3. Preface

- 4. Contents

- 5. Overview

- 6. Description of Functional Modules

System-Control Modules

On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. Electrical Characteristics

- 8. Appendix

- 9. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

10. Index

### **Preface**

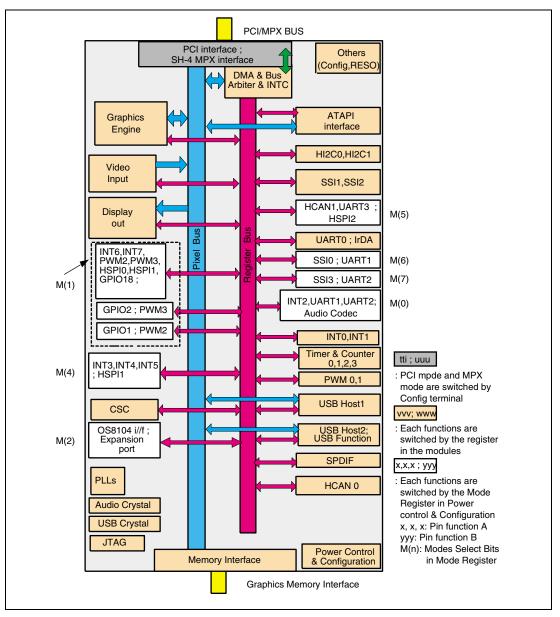

The HD64404 is a companion chip for the SuperH family SH-4 CPU core. It incorporates a graphic processing engine and an interface function with various network and multimedia devices that are required to configure Car Information Systems (CIS).

Target Users: This manual was written for users who will be using this LSI in the design of application systems. Users of this manual are expected to understand the fundamentals of electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical characteristics of this LSI to the above users.

Notes on reading this manual:

Product names

The following products are covered in this manual.

### Product Code HD64404BT

- In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts on system control functions, peripheral functions, and electrical characteristics.

- In order to understand the details of the CPU's functions of SH-4 Read the SH-4 Programming Manual.

Rules: Register name: The following notation is used for cases when the same or a

similar function, e.g. serial communication, is implemented

on more than one channel:

XXX\_N (XXX is the register name and N is the channel

number)

Bit order: The MSB (most significant bit) is on the left and the LSB

(least significant bit) is on the right.

Number notation: Binary is B'xxxx, hexadecimal is H'xxxx, decimal is xxxx.

Signal notation: An overbar is added to a low-active signal:  $\overline{xxxx}$

Related Manuals: The latest versions of all related manuals are available from our web site.

Please ensure you have the latest versions of all documents you require.

http://www.hitachisemiconductor.com/

#### HD64404 manuals:

| Manual Title            | ADE No.     |

|-------------------------|-------------|

| HD64404 Hardware Manual | This manual |

#### Users manuals for related LSI:

| Manual Title                  | ADE No.      |

|-------------------------------|--------------|

| SH7750 Series Hardware Manual | ADE-602-124E |

| SH7751 Series Hardware Manual | ADE-602-201B |

| SH-4 Programming Manual       | ADE-602-156D |

#### **Abbreviations**

ATA AT Attachiment

ATAPI AT Attachment Packet Interface

bpp bit per pixcel

bps bit per second

BMC biphase-mark-code

CPG Clock Pulse Generator

CPU Central Processing Unit

CRT Cathode Ray Tube

DMA Direct Memory Access

DMAC Direct Memory Access Controller

DRAM Dynamic Random Access Memory

DSP Digital Signal Processor

FIFO First-In First-Out

GE Graphic Engine

HCAN-2 Hitachi Control Area Network-2

Hi-Z High Impedance

HSPI Hitachi Serial Peripheral Interface

IEEE Institute Electronic and Electronics Engineers

I<sup>2</sup>C Inter IC bus

INTC Interrupt Controller

IrDA Infrared Data Association

ISO International Organization for Standardization

JTAG Joint Test Action Group LSB Least Significant Bit

MOST Media Oriented Systems Transport

MSB Most Significant Bit

PCIC Peripheral Component Interconnect Controller

PLL Phase Locked Loop

Q2SD Quick 2D Graphics Renderer with Synchronous DRAM Interface

RAM Random Access Memory

RGB Red Green Blue

SPDIF Sony Philips Digital Interface Format

SPI Serial Peripheral Interface

SSI Serial Sound Interface

SRAM Static Random Access Memory

T.B.D To Be Determined

UART Universal Asynchronous Receiver/Transmitter

USB Universal Serial Bus

VIO Video I/O

YUV Y-signal, U-signal, V-signal

### Contents

| Secti | on 1    | Overview                                   | 1  |

|-------|---------|--------------------------------------------|----|

| 1.1   | Genera  | l Description                              | 1  |

| 1.2   | Archite | ecture Overview                            | 1  |

|       | 1.2.1   | Mode Register Configuration.               | 3  |

|       | 1.2.2   | Peripheral Module Register Configuration   | 4  |

|       | 1.2.3   | Config Pin Configuration                   | 4  |

| 1.3   | Feature | PS                                         | 4  |

|       | 1.3.1   | System Interface                           | 4  |

|       | 1.3.2   | Pixel Bus                                  | 5  |

|       | 1.3.3   | Register Bus                               | 5  |

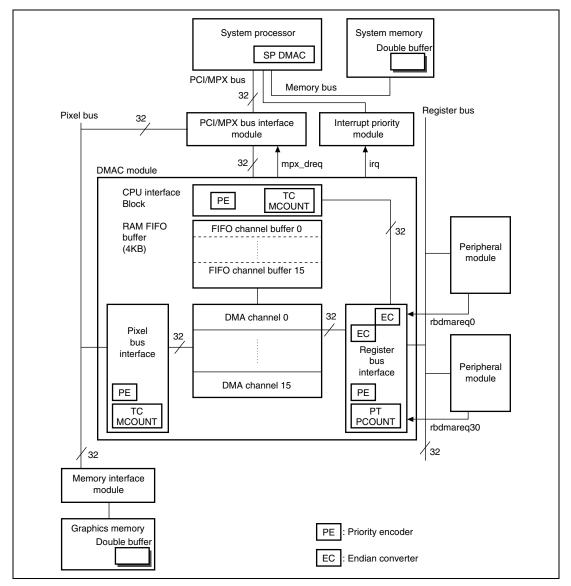

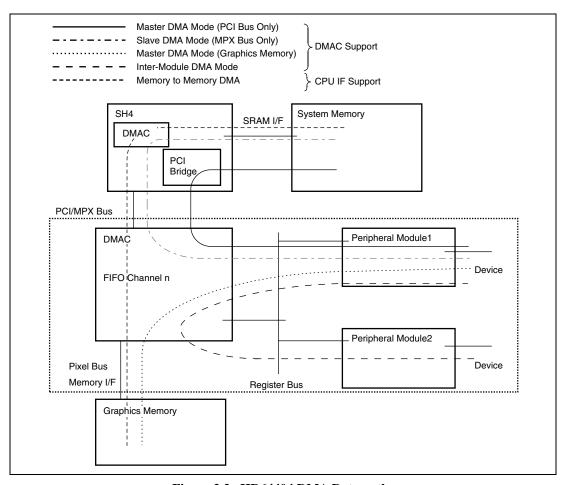

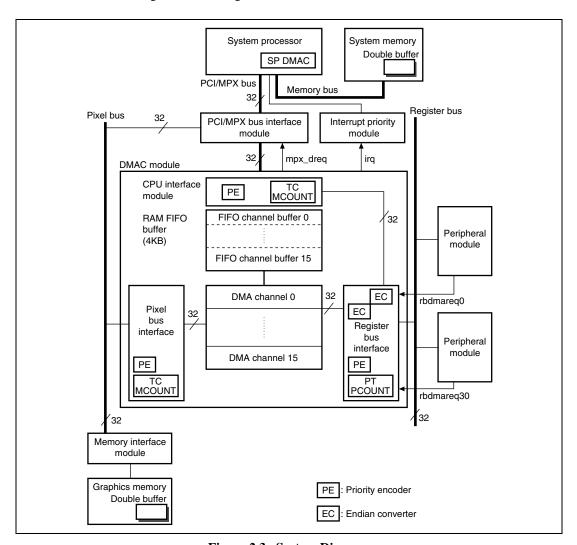

|       | 1.3.4   | DMAC                                       | 5  |

|       | 1.3.5   | Graphics Engine                            | 5  |

|       | 1.3.6   | Video Input                                | 6  |

|       | 1.3.7   | Display Output                             | 6  |

|       | 1.3.8   | CSC (Color Space Converter)                | 7  |

|       | 1.3.9   | SDRAM Interface                            | 7  |

|       | 1.3.10  | Interrupt Priority                         | 8  |

|       | 1.3.11  | Serial Sound Interface (SSI)               | 8  |

|       | 1.3.12  | Hitachi I <sup>2</sup> C Interface         | 8  |

|       | 1.3.13  | Hitachi Serial Peripheral Interface (HSPI) | 8  |

|       | 1.3.14  |                                            |    |

|       | 1.3.15  | Audio Codec                                | 9  |

|       | 1.3.16  | USB Host and Function Interface            | 9  |

|       | 1.3.17  | HCAN2                                      | 9  |

|       | 1.3.18  | UART                                       | 10 |

|       | 1.3.19  | IrDA                                       | 11 |

|       | 1.3.20  | OS8104 Interface or Expansion Bus          | 11 |

|       | 1.3.21  | ATAPI                                      | 11 |

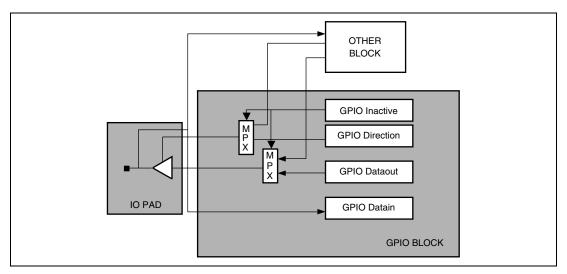

|       | 1.3.22  | GPIO                                       | 11 |

|       | 1.3.23  | Interrupt Input                            | 11 |

|       | 1.3.24  | Timer/Counter                              | 12 |

|       | 1.3.25  | PWM                                        | 12 |

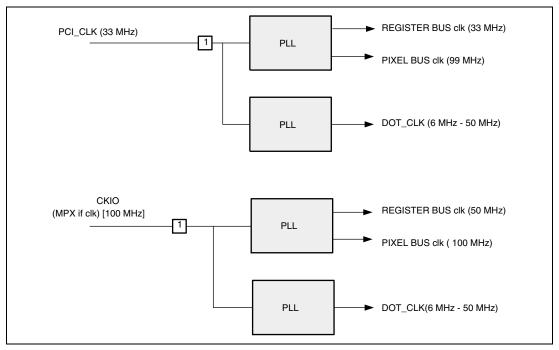

|       | 1.3.26  | PLL Clock Generation                       | 12 |

|       | 1.3.27  | Crystal Oscillators                        | 12 |

|       | 1.3.28  | Power Management                           | 12 |

| 1.4   | Pin Mo  | des                                        | 13 |

| 1.5   |         | scription                                  |    |

| 1.6   |         | ing Voltage                                |    |

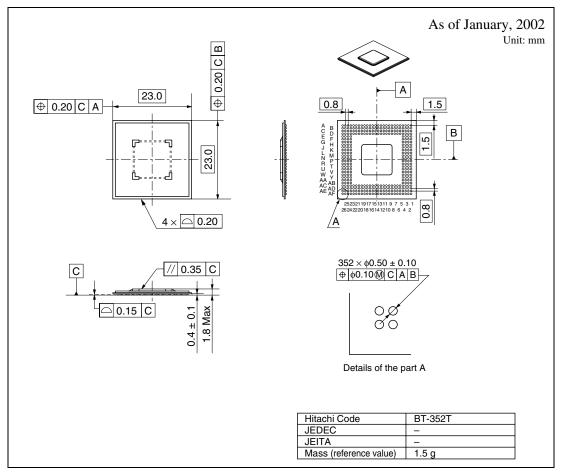

| 1.7   | Packag  | e                                          | 34 |

| 1.8  | Detaile   | d Architecture                                                      | 34  |

|------|-----------|---------------------------------------------------------------------|-----|

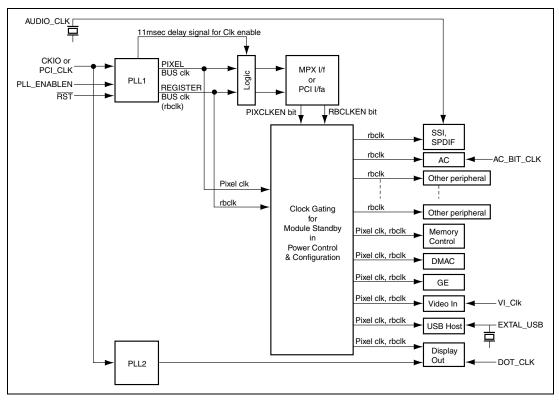

|      | 1.8.1     | Main Clocking                                                       | 34  |

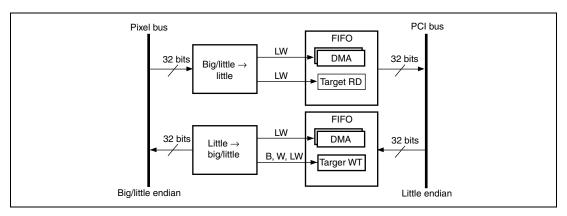

|      | 1.8.2     | Pixel Bus                                                           | 43  |

|      | 1.8.3     | Register Bus                                                        | 44  |

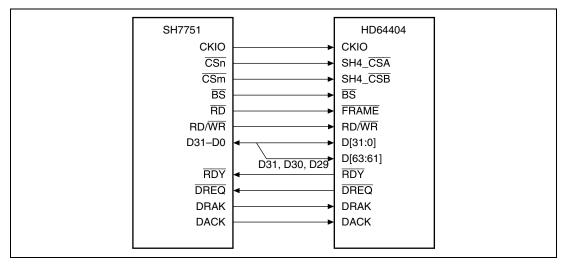

|      | 1.8.4     | System Interface                                                    | 45  |

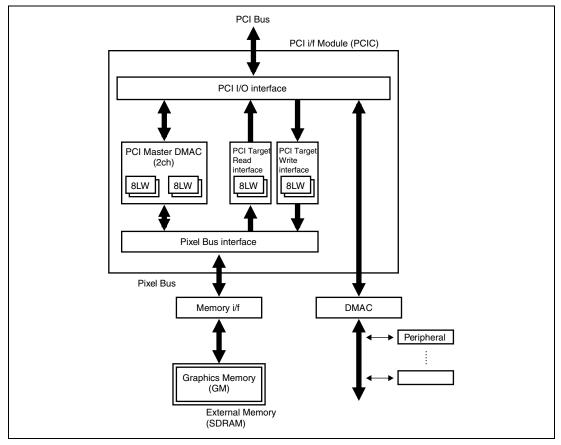

|      | 1.8.5     | PCI                                                                 | 46  |

|      | 1.8.6     | MPX                                                                 | 46  |

|      | 1.8.7     | Graphics Memory (SDRAM) Controller                                  | 46  |

|      | 1.8.8     | Interrupt Controller                                                |     |

|      | 1.8.9     | Power Saving                                                        |     |

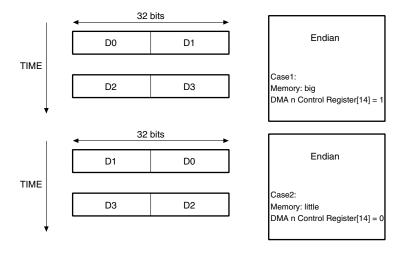

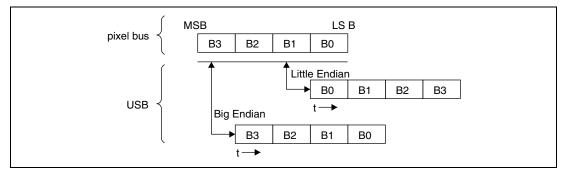

| 1.9  | Endian    | Support                                                             |     |

|      | 1.9.1     | Definitions                                                         |     |

|      | 1.9.2     | Description                                                         |     |

|      | 1.9.3     | Register Bus                                                        |     |

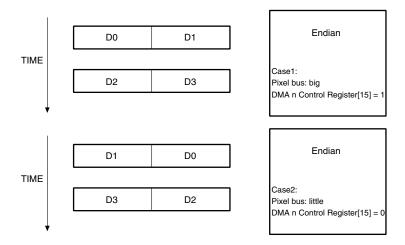

|      | 1.9.4     | Pixel Bus                                                           |     |

|      | 1.9.5     | System Types                                                        |     |

|      | 1.9.6     | Register Bus Summary                                                |     |

|      | 1.9.7     | Pixel Bus Summary                                                   |     |

| 1.10 |           | 104 Memory Map                                                      |     |

| 1.10 | 1.10.1    | MPX Mode                                                            |     |

|      |           | PCI Mode                                                            |     |

| 1.11 |           | Configuration Example                                               |     |

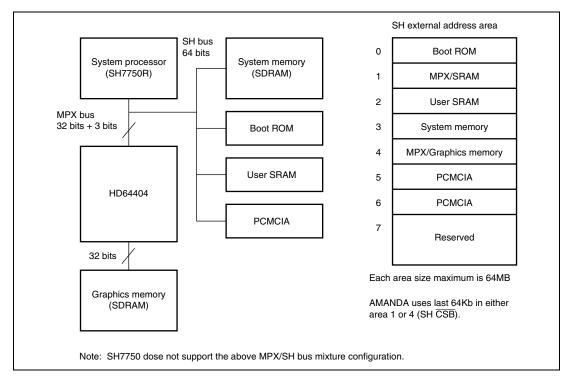

|      | •         | MPX System Example 1                                                |     |

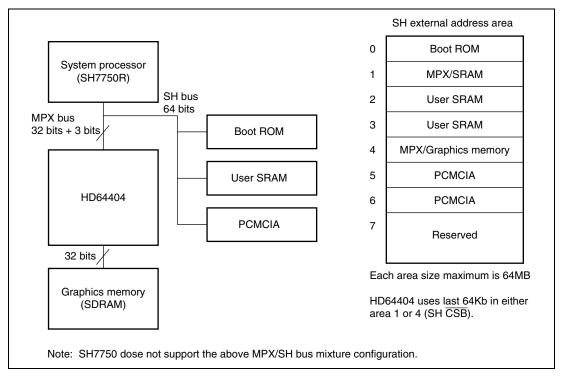

|      | 1.11.2    | MPX System Example 2—UMA (Unified Memory Architecture)              | 00  |

|      | 1.11.2    | Configuration                                                       | 61  |

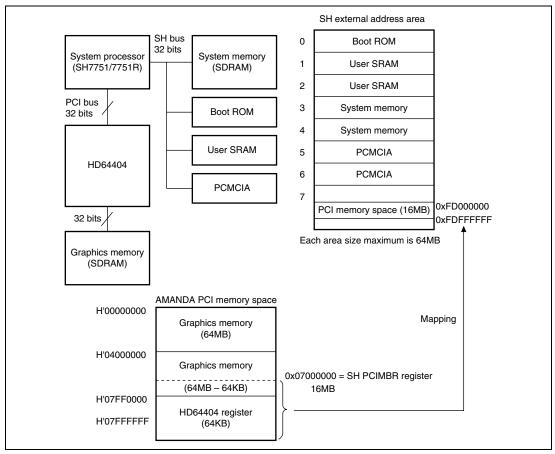

|      | 1 11 3    | PCI System Example                                                  |     |

|      | 1.11.5    | 1 Ci System Example                                                 | 02  |

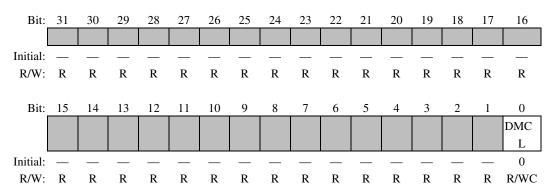

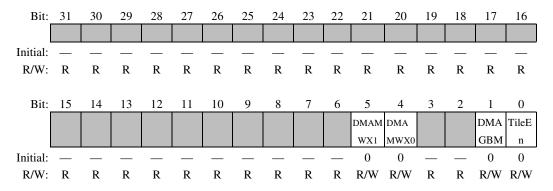

| Sect | ion 2     | DMAC                                                                | 65  |

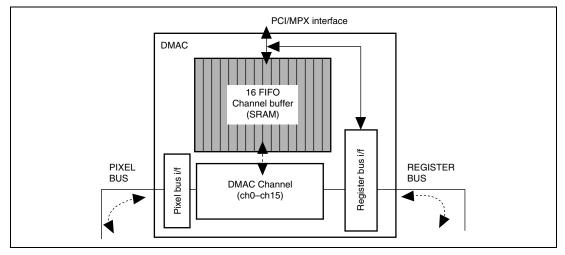

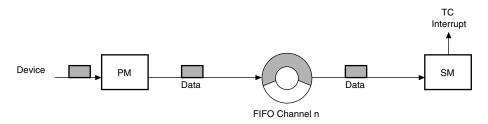

| 2.1  | Genera    | l Description                                                       | 65  |

| 2.2  |           | es                                                                  |     |

| 2.3  | Limita    | tions                                                               | 67  |

| 2.4  | Digital   | Inputs/Outputs                                                      | 70  |

| 2.5  | _         | ss Map                                                              |     |

|      |           | DMAC Registers                                                      |     |

|      |           | DMA Channel Registers                                               |     |

|      | 2.5.3     | DMA FIFO Channels                                                   |     |

|      | 2.5.4     | DMA Request Numbers                                                 |     |

| 2.6  |           | er Description                                                      |     |

|      | 2.6.1     | DMA Channel Registers (DMA Channel Number n = 0 to 15)              |     |

|      | 2.6.2     | DMA Peripheral Request Registers (DMA Request Number $q = 0$ to 30) |     |

|      | 2.6.3     | DMA Configuration and Status Registers                              |     |

| 2.7  |           | onal Description                                                    |     |

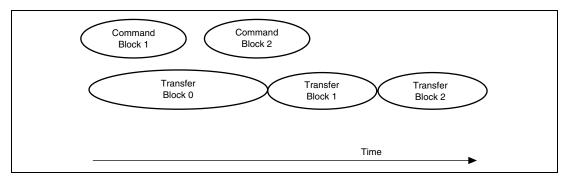

|      | 2.7.1     | DMA Data Transfer                                                   |     |

| Davi |           |                                                                     | 111 |

| Hev. | 1.0, 09/0 | 2, page x of xliv                                                   |     |

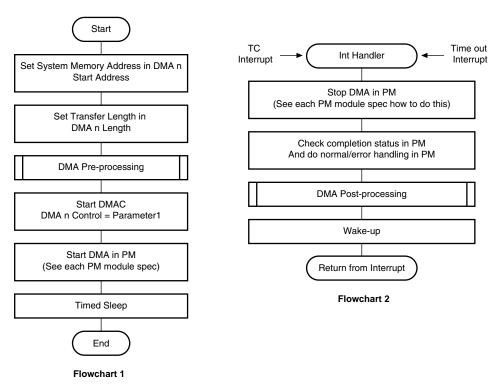

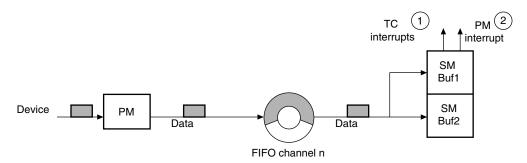

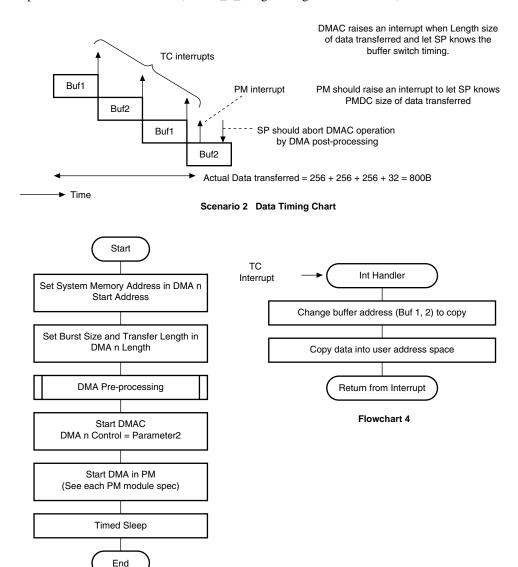

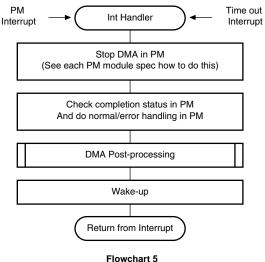

|       | 2.7.2    | Programming DMAC                                 | 112    |

|-------|----------|--------------------------------------------------|--------|

|       | 2.7.3    | DMA Channels                                     | 112    |

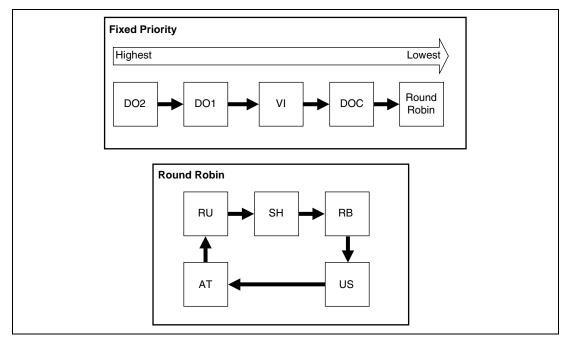

|       | 2.7.4    | Priority Encoders                                | 113    |

|       | 2.7.5    | RAM FIFO Buffer                                  | 113    |

|       | 2.7.6    | Direct Access to FIFO Channel Buffers            | 113    |

|       | 2.7.7    | Pixel Bus Interface                              | 114    |

|       | 2.7.8    | Register Bus                                     | 114    |

|       | 2.7.9    | External DMA                                     | 114    |

|       | 2.7.10   | Endian Conversion for PCI and MPX PIO Accesses   | 115    |

|       | 2.7.11   | PIO Bus Activity Monitor                         | 115    |

| 2.8   | Prograi  | nming the PIO Monitor                            | 116    |

|       | 2.8.1    | Monitoring Mode                                  | 116    |

|       | 2.8.2    | PIO Monitor Active Mode                          | 116    |

| 2.9   | Append   | lix 1 HD64404 Data Path                          | 120    |

| 2.10  | Append   | dix 2 DMA Modes in DMAC Module                   | 122    |

| 2.11  | Append   | lix 3 DMA Mode Parameters                        | 123    |

| 2.12  | HD644    | 04 DMA Driver Design Note                        | 127    |

|       | 2.12.1   | General Description                              | 127    |

|       | 2.12.2   | References                                       | 128    |

|       | 2.12.3   | Bus Configuration and Endian Support             | 128    |

|       | 2.12.4   | DMA Channel Allocation                           | 129    |

|       | 2.12.5   | DMA Channel Parameter Design                     | 130    |

|       | 2.12.6   | Consideration on External DMA mode and DMA modes |        |

|       |          | supported by CPU I/F Modules                     | 131    |

|       | 2.12.7   | Access Control of DMAC Registers                 | 132    |

|       |          | Data Transfer Procedure for Each DMA Scenario    |        |

|       | 2.12.9   | DMAC Initialisation Procedure                    | 151    |

|       | 2.12.10  | DMA Pre-, Post- and Abort processing             | 152    |

|       | 2.12.11  | Software Test Case: DMAC Flowchart for MIM       | 159    |

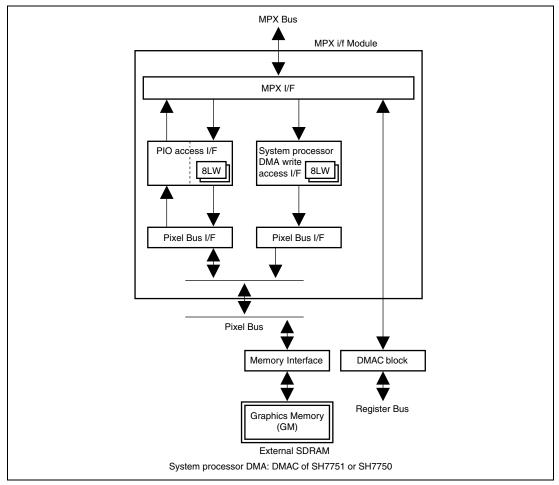

| Secti | ion 3    | MPX I/F                                          | . 163  |

| 3.1   | Genera   | l Description                                    | 163    |

| 3.2   | Feature  | S                                                | 163    |

| 3.3   | Externa  | al interface (MPX Bus)                           | 164    |

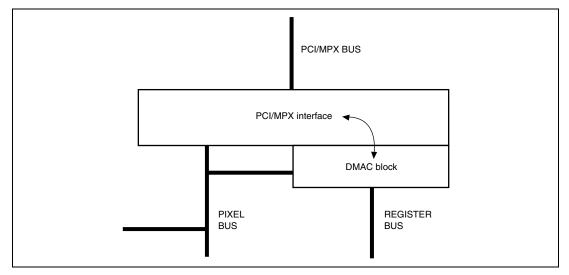

| 3.4   | Block l  | Diagram                                          | 165    |

| 3.5   | Registe  | r Description                                    | 166    |

|       | 3.5.1    | MPX interface registers                          | 166    |

| 3.6   | Function | onal Description                                 | 181    |

|       | 3.6.1    | General Functionality                            | 181    |

| Secti | on 4     | PCI I/F                                          | . 185  |

| 4.1   | Genera   | l Description                                    | 185    |

| 4.2   |          | ······································           |        |

|       |          | Rev. 1.0. 09/02 page xi                          | of xli |

| 4.3  |           | Diagram                                                         |     |

|------|-----------|-----------------------------------------------------------------|-----|

| 4.4  | Externa   | al interface                                                    | 187 |

| 4.5  | _         | er Configuration                                                |     |

| 4.6  | PCIC F    | Register Descriptions                                           |     |

|      | 4.6.1     | PCI Configuration Register 0 (PCICONF0)                         |     |

|      | 4.6.2     | PCI Configuration Register 1 (PCICONF1)                         |     |

|      | 4.6.3     | PCI Configuration Register 2 (PCICONF2)                         | 198 |

|      | 4.6.4     | PCI Configuration Register 3 (PCICONF3)                         | 201 |

|      | 4.6.5     | PCI Configuration Register 4 (PCICONF4)                         | 203 |

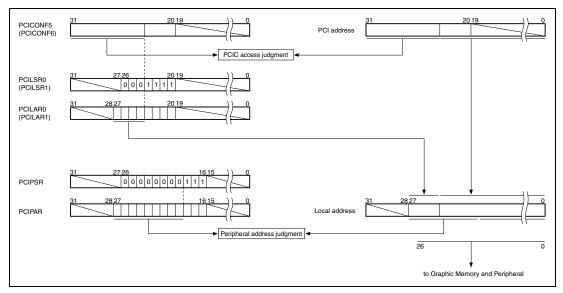

|      | 4.6.6     | PCI Configuration Register 5 (PCICONF5)                         | 205 |

|      | 4.6.7     | PCI Configuration Register 6 (PCICONF6)                         | 207 |

|      | 4.6.8     | PCI Configuration Register 7 (PCICONF7) to                      |     |

|      |           | PCI Configuration Register 10 (PCICONF10)                       | 210 |

|      | 4.6.9     | PCI Configuration Register 11 (PCICONF11)                       | 211 |

|      | 4.6.10    | PCI Configuration Register 12 (PCICONF12)                       | 213 |

|      |           | PCI Configuration Register 13 (PCICONF13)                       |     |

|      | 4.6.12    | PCI Configuration Register 14 (PCICONF14)                       | 214 |

|      |           | PCI Configuration Register 15 (PCICONF15)                       |     |

|      |           | PCI Configuration Register 16 (PCICONF16)                       |     |

|      |           | PCI Configuration Register 17 (PCICONF17)                       |     |

|      |           | Reserved Area                                                   |     |

|      |           | PCI Control Register (PCICR)                                    |     |

|      |           | PCI Local Space Register [26:20] (PCILSR [26:20])               |     |

|      |           | PCI Local Address Register [27:20] (PCILAR [27:20])             |     |

|      |           | PCI Interrupt Register (PCIINT)                                 |     |

|      |           | PCI Interrupt Mask Register (PCIINTM)                           |     |

|      |           | PCI Address Data Register at Error (PCIALR)                     |     |

|      |           | PCI Command Data Register at Error (PCICLR)                     |     |

|      |           | PCI DMA Transfer Arbitration Master (PCIDMABT)                  |     |

|      |           | PCI DMA Transfer PCI Address Register 0/1 (PCIDPA0/1)           |     |

|      |           | PCI DMA Transfer HD64404 Start Address Register 0/1 (PCIDLA0/1) |     |

|      |           | PCI DMA Transfer Counter Register 0/1 (PCIDTC0/1)               |     |

|      |           | PCI DMA Control Register 0/1 (PCIDCR0/1)                        |     |

|      |           | Reserved                                                        |     |

|      | 4.6.30    | PCI TRDY Enable Control (PCITRDYENB)                            |     |

|      | 4.6.31    | PCI Tile Mode Register (PCITILEMODE)                            |     |

|      | 4.6.32    | PCI Data Transfer Mode Register (PCIDTMR)                       |     |

|      |           | PCI Linear to Tile Convert Address Register (PCILTAD)           |     |

|      |           | PCI Linear to Tile Convert Address MASK (PCILTAM)               |     |

|      | 4.6.35    | PCI Peripheral Base Address Register (PCIPAR)                   |     |

|      |           |                                                                 |     |

|      | 4.6.37    |                                                                 |     |

|      |           | PCI PLL Control Register (PCIPLLCTL)                            |     |

|      |           |                                                                 | 231 |

| Rev. | 1.0, 09/0 | 2, page xii of xliv                                             |     |

|      | 4.6.39  | PCI TRDY Enable wait cycle counter (PCITRDYCNT) | 252                    |

|------|---------|-------------------------------------------------|------------------------|

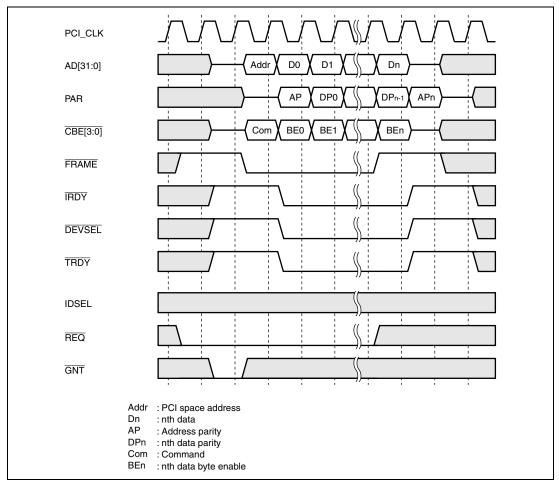

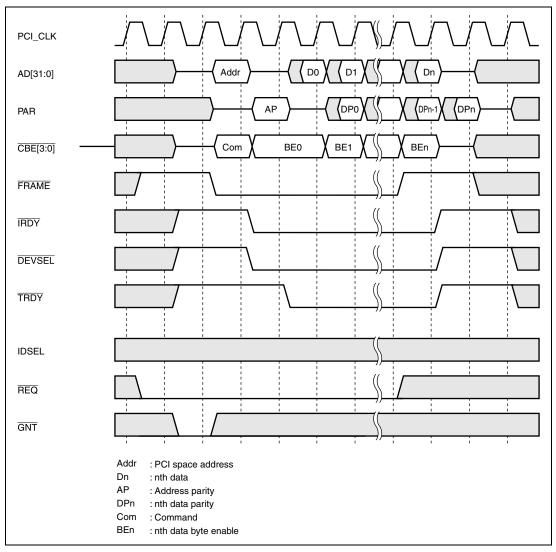

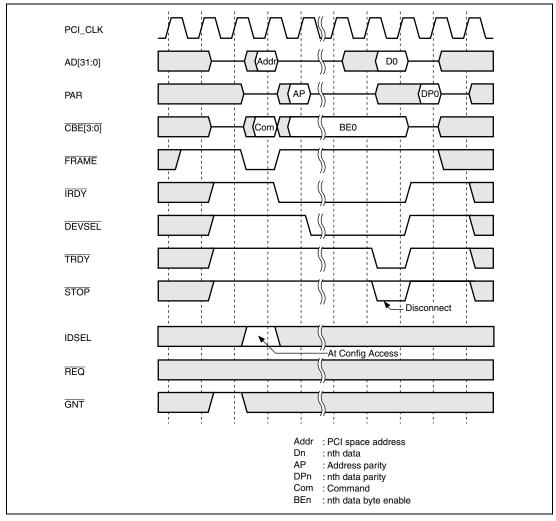

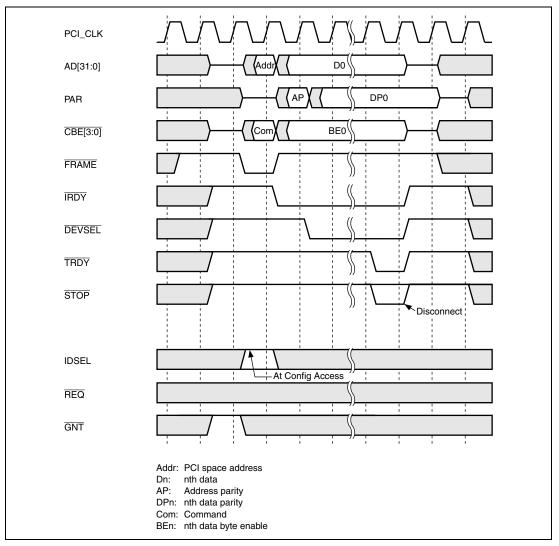

| 4.7  | Functi  | onal Description                                | 253                    |

|      | 4.7.1   | Operating Modes                                 |                        |

|      | 4.7.2   | PCI Commands                                    | 253                    |

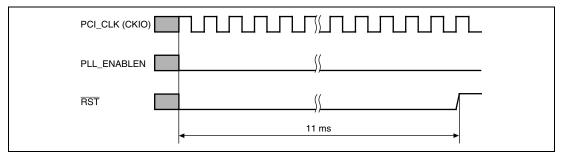

|      | 4.7.3   | PCIC Initialization                             | 254                    |

|      | 4.7.4   | Local Register Access                           | 254                    |

|      | 4.7.5   | Target Transfers                                | 254                    |

|      | 4.7.6   | DMA Transfers between External PCI Device       |                        |

|      |         | and Graphic Memory through Pixel Bus            | 257                    |

|      | 4.7.7   | Arbitration in PCIC                             | 259                    |

|      | 4.7.8   | PCI Bus Arbitration                             | 260                    |

|      | 4.7.9   | PCI Bus Basic Interface                         | 260                    |

| 4.8  | Endia   | ns                                              | 266                    |

|      | 4.8.1   | Endian Control on the pixel bus                 | 266                    |

|      | 4.8.2   | Endian Control in DMA Transfers                 | 266                    |

|      | 4.8.3   | Endian Control in Target Transfers              | 267                    |

| 4.9  | Resett  | ing                                             | 268                    |

| 4.10 | Interru | ıpts in PCIC                                    | 268                    |

| 4.11 | Error 1 | Detection                                       | 269                    |

| 4.12 | Refere  | ences                                           | 269                    |

| _    |         |                                                 |                        |

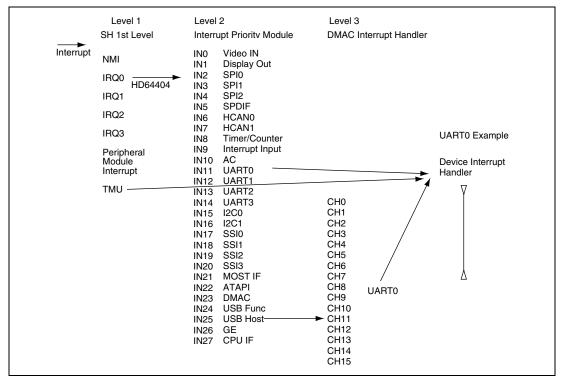

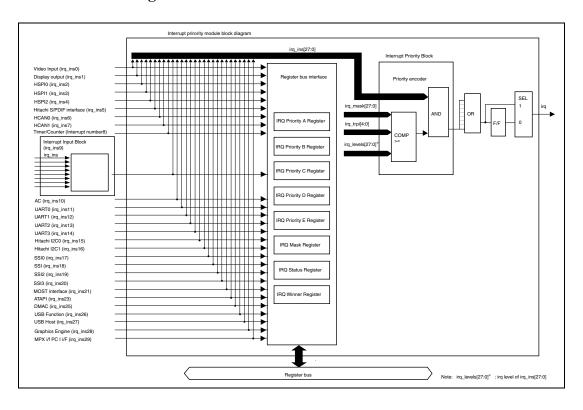

|      |         | Interrupt Priority Module                       |                        |

| 5.1  |         | uction                                          |                        |

| 5.2  |         | es                                              |                        |

| 5.3  |         | Diagram                                         |                        |

| 5.4  |         | aces                                            |                        |

|      | 5.4.1   | Digital Inputs/Outputs                          |                        |

|      | 5.4.2   | Software Interfaces                             |                        |

| 5.5  | _       | er Descriptions                                 |                        |

|      | 5.5.1   | IRQ PriorityA Register (IRQA)                   |                        |

|      | 5.5.2   | IRQ PriorityB Register (IRQB)                   |                        |

|      | 5.5.3   | IRQ PriorityC Register (IRQC)                   |                        |

|      | 5.5.4   | IRQ PriorityD Register (IRQD)                   |                        |

|      | 5.5.5   | IRQ PriorityE Register (IRQE)                   |                        |

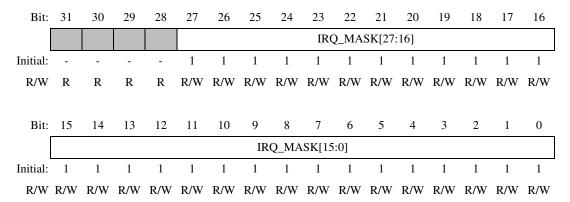

|      | 5.5.6   | IRQ Mask Register (IRQM)                        |                        |

|      | 5.5.7   | IRQ STATUS Register (IRQS)                      |                        |

|      | 5.5.8   | IRQ Winner Register (IRQW)                      |                        |

| 5.6  |         | onal Description                                |                        |

|      | 5.6.1   | General Functionality                           |                        |

|      | 5.6.2   | Reset Strategy                                  |                        |

|      | 5.6.3   | Power Saving and Clocking Strategy              |                        |

|      | 5.6.4   | Spurious Interrupt Handling                     |                        |

|      | 5.6.5   | Sample Interrupt Handler Pseudo Procedure       | 287                    |

|      |         | Rev. 1.0, 0                                     | 9/02, page xiii of xli |

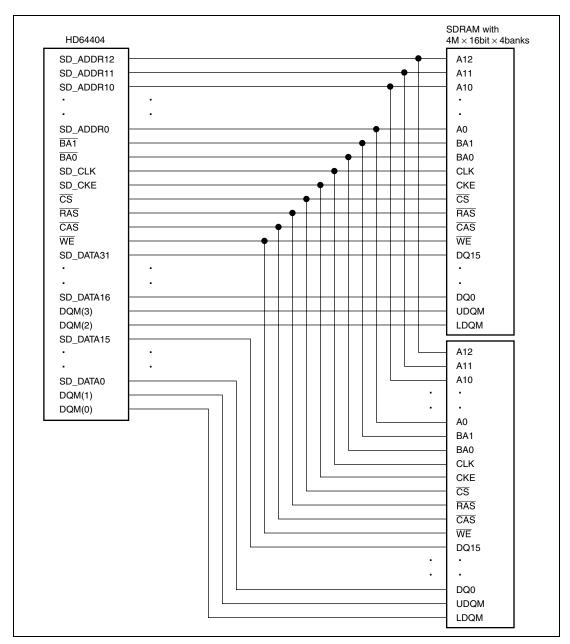

| Sect | ion 6 Memory Interface                                       | 289 |

|------|--------------------------------------------------------------|-----|

| 6.1  | General Description                                          | 289 |

| 6.2  | Features                                                     | 289 |

|      | 6.2.1 Digital Inputs/Outputs                                 | 289 |

|      | 6.2.2 Software Interfaces                                    | 290 |

|      | 6.2.3 Functional Description                                 | 290 |

| 6.3  | Register Descriptions                                        | 290 |

|      | 6.3.1 Memory Control Register (MCR)                          |     |

| 6.4  | Power saving                                                 |     |

|      | 6.4.1 Power-On sequence                                      |     |

|      | 6.4.2 Memory interface Power Down Sequence with Self Refresh |     |

|      | 6.4.3 Module Standby Mode                                    |     |

| 6.5  | SDRAM Mode Register setting                                  |     |

| 6.6  | SDRAM configuration for UM (unified memory)                  |     |

| 6.7  | Example of Synchronous DRAM Connection                       |     |

| 6.8  | Example of Setting Refresh Period (RP)                       |     |

| 0.0  | 2.map. 01.50mag 10.1100 (11.7)                               |     |

| Sect | ion 7 Memory Arbiter                                         | 301 |

| 7.1  | General Description                                          |     |

| 7.2  | Features                                                     |     |

| 7.3  | Register description                                         |     |

| 7.4  | Functional description.                                      |     |

|      | 7.4.1 Arbitration                                            |     |

|      | 7.4.2 Data transfers on the pixel bus                        |     |

|      | 1                                                            |     |

| Sect | ion 8 Power Control & Configuration                          | 303 |

| 8.1  | General Description                                          | 303 |

| 8.2  | Features                                                     | 303 |

| 8.3  | Digital Inputs/Outputs                                       | 304 |

| 8.4  | Software Interfaces                                          | 305 |

| 8.5  | Functional Description                                       | 305 |

| 8.6  | Register Descriptions                                        | 306 |

|      | 8.6.1 Mode Register (M)                                      | 307 |

|      | 8.6.2 Reso Register (RESO)                                   | 308 |

|      | 8.6.3 Clock Control 1 Register (CC1)                         | 309 |

|      | 8.6.4 Clock Control 2 Register (CC2)                         |     |

|      | 8.6.5 Xtal Control Register (XTC)                            |     |

|      | 8.6.6 Software Reset Register (SRST)                         |     |

|      | 8.6.7 Compare Match Register (CMR)                           |     |

| 8.7  | Power Saving and Clocking Strategy                           |     |

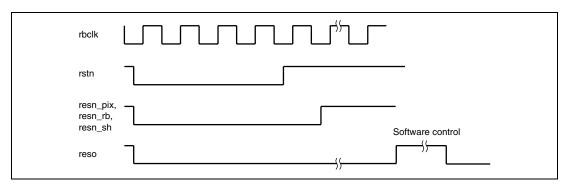

|      | 8.7.1 Procedure for Power On Sequence                        |     |

|      | 8.7.2 Procedure for Power Down and Wake Up                   |     |

| 8.8  | Clock Pulse Generator                                        |     |

|      |                                                              |     |

| Hev. | 1.0, 09/02, page xiv of xliv                                 |     |

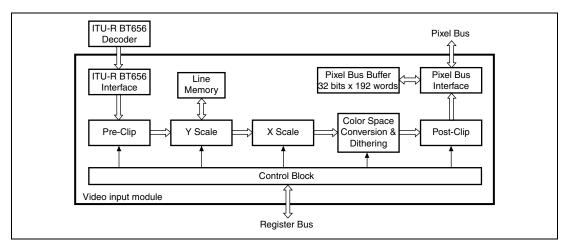

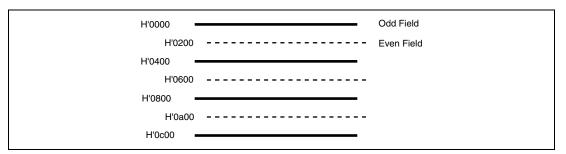

| Sect  | ion 9    | Video Input Module                                        | 32                   |

|-------|----------|-----------------------------------------------------------|----------------------|

| 9.1   | Overvi   | ew                                                        | 323                  |

|       | 9.1.1    | Features                                                  | 323                  |

|       | 9.1.2    | Block Diagram                                             | 323                  |

| 9.2   | Pin De   | scriptions                                                | 324                  |

| 9.3   | Registe  | er Description                                            | 324                  |

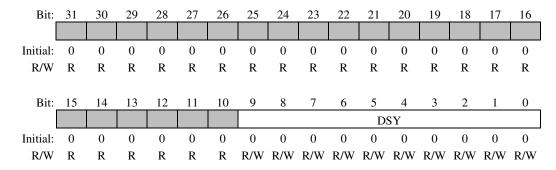

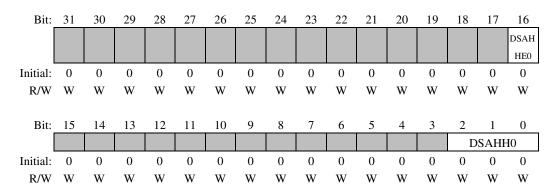

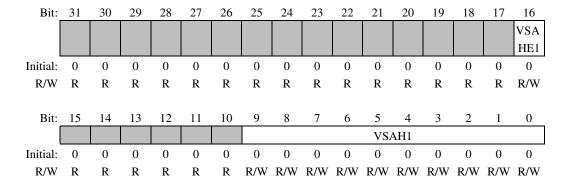

|       | 9.3.1    | Register Summary                                          | 324                  |

|       | 9.3.2    | Register Descriptions                                     | 320                  |

| 9.4   | Function | onal Description                                          | 340                  |

|       | 9.4.1    | ITU-R BT.656 Interface                                    | 340                  |

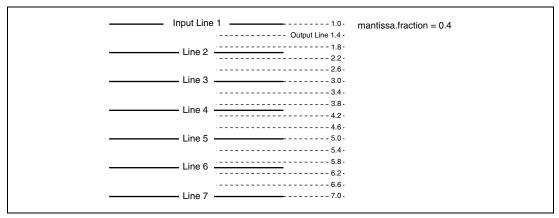

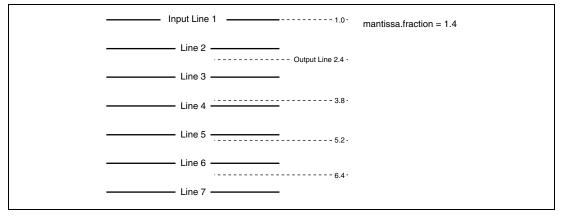

|       | 9.4.2    | Vertical Scaling                                          | 34                   |

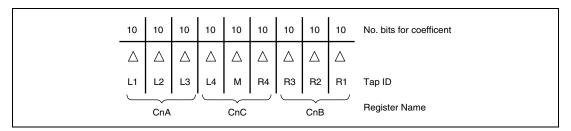

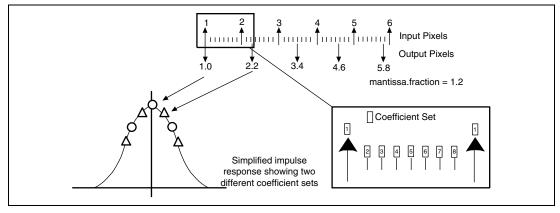

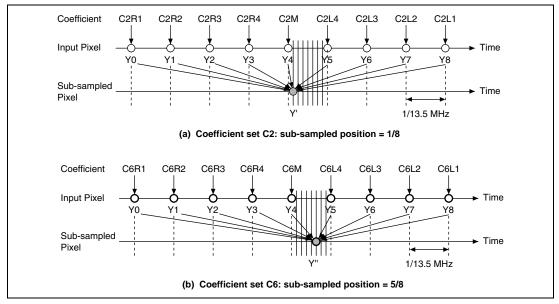

|       | 9.4.3    | Horizontal Scaling                                        | 348                  |

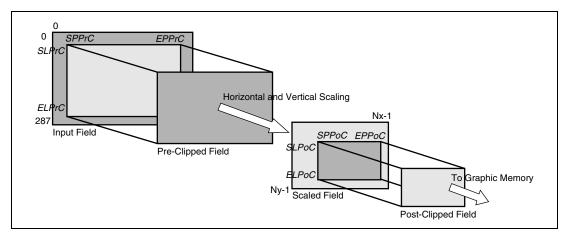

|       | 9.4.4    | Size Clipping before/after Vertical or Horizontal Scaling | 35                   |

|       | 9.4.5    | Color Space Conversion                                    | 352                  |

|       | 9.4.6    | Dithering                                                 | 352                  |

|       | 9.4.7    | Capture Mode                                              | 352                  |

|       | 9.4.8    | Module Standby Mode                                       | 352                  |

| 9.5   | Examp    | le of Sample Program                                      | 353                  |

|       | 9.5.1    | Example of Initial setting of Video Input registers       | 353                  |

|       | 9.5.2    | Function to Set the x Direction Filter Coefficient        | 355                  |

| Secti | ion 10   | Display Out Module                                        | 36                   |

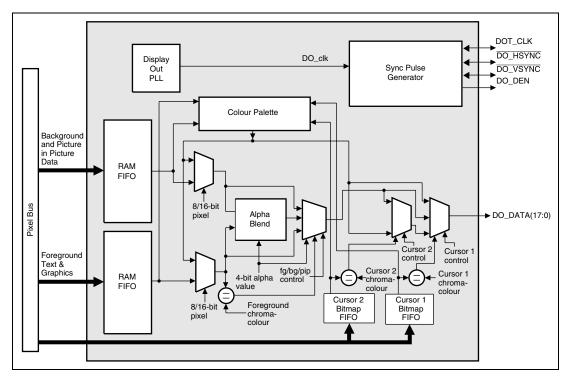

| 10.1  | Overvi   | ew                                                        | 36                   |

|       | 10.1.1   | Features                                                  | 36                   |

|       | 10.1.2   | Block Diagram                                             | 362                  |

| 10.2  | Interfa  | ces                                                       | 363                  |

|       | 10.2.1   | Digital Inputs/Outputs                                    | 363                  |

|       |          | Software Interfaces                                       |                      |

|       | 10.2.3   | Register Description                                      | 360                  |

| 10.3  |          | onal Description                                          |                      |

|       | 10.3.1   | General Functionality                                     |                      |

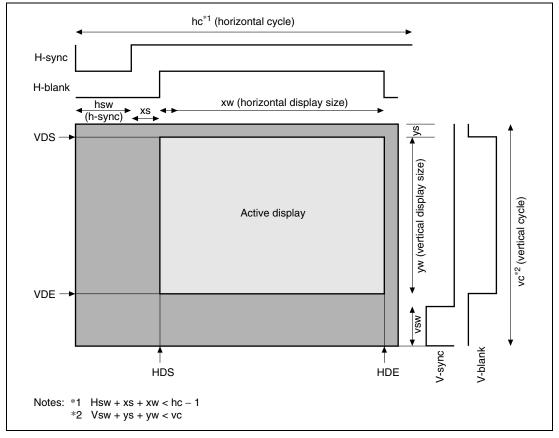

|       | 10.3.2   | Sync Pulse Generator                                      | 44                   |

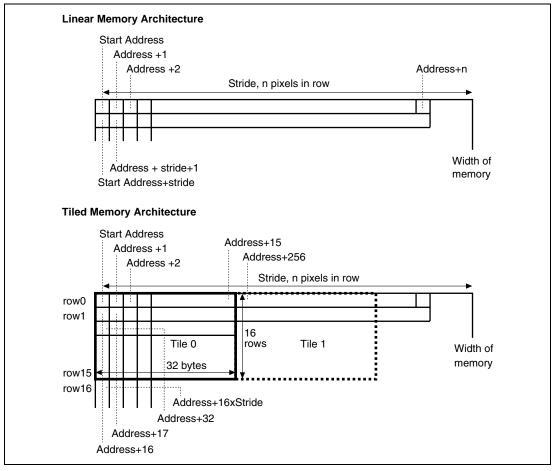

|       | 10.3.3   | Memory Architecture                                       | 443                  |

|       | 10.3.4   | Foreground                                                | 444                  |

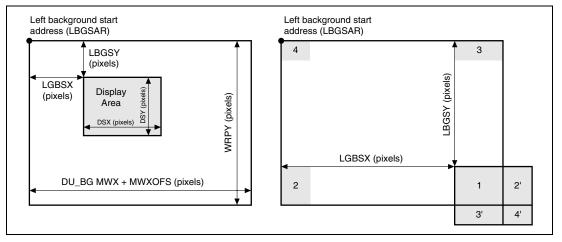

|       | 10.3.5   | Background and wrap function                              | 445                  |

|       | 10.3.6   | Picture in Picture                                        | 440                  |

|       | 10.3.7   | Alpha Blending                                            | 440                  |

|       | 10.3.8   | Chroma-Key                                                | 44′                  |

|       | 10.3.9   | Cursors                                                   | 44′                  |

|       |          | Q2SD Compatibility                                        |                      |

|       |          | PLL                                                       |                      |

|       | 10.3.12  | 2 Reset Strategy                                          | 452                  |

|       |          | B Power Saving and Clocking Strategy                      |                      |

|       |          | Rev. 1.0, (                                               | 09/02, page xv of xl |

| Sect | ion 11 GE for HD64404           | 453 |

|------|---------------------------------|-----|

| 11.1 | Overview                        | 453 |

|      | 11.1.1 Overview                 |     |

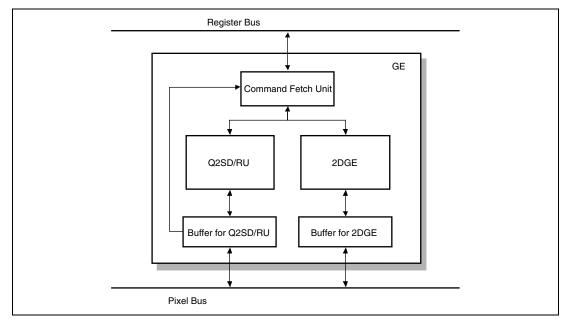

|      | 11.1.2 Block Diagram            |     |

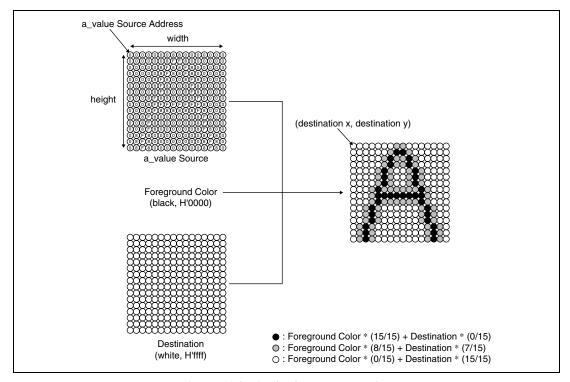

|      | 11.1.3 Drawing Functions        |     |

|      | 11.1.4 Module Standby Mode      |     |

| 11.2 | Basic Functions                 |     |

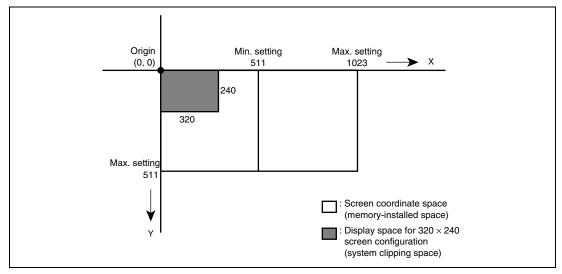

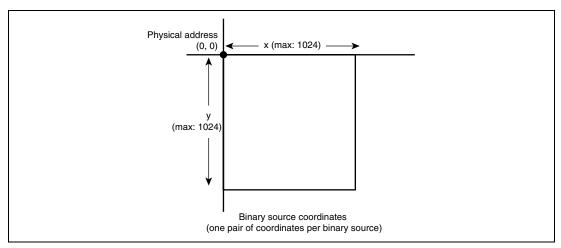

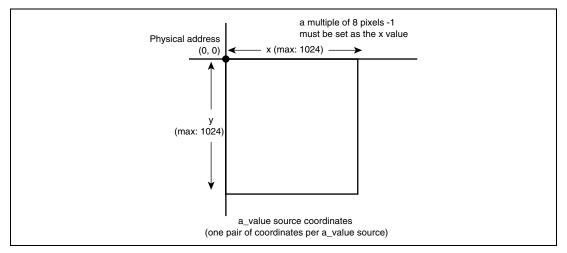

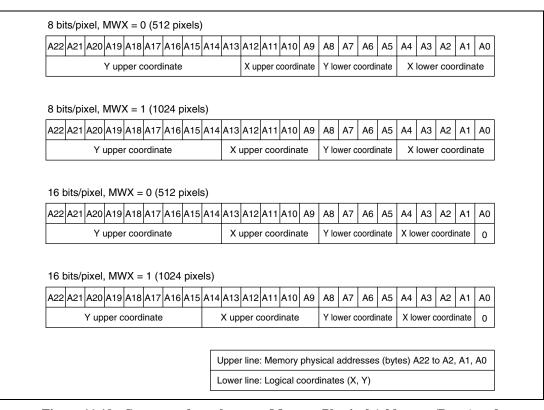

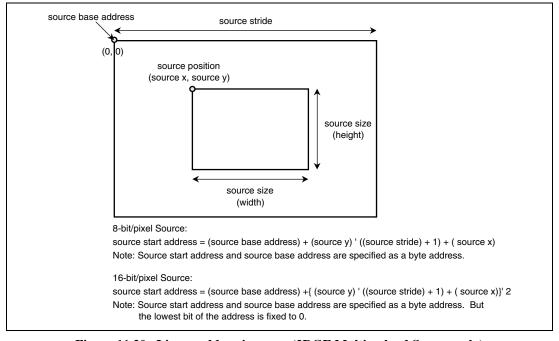

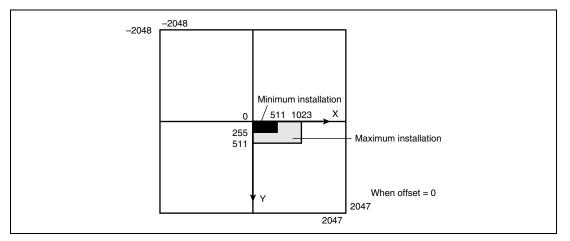

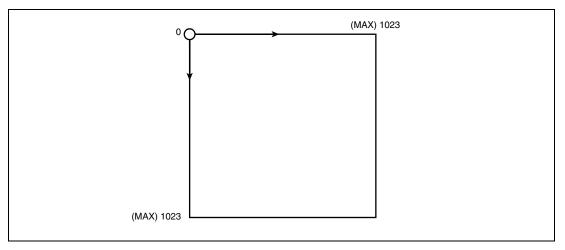

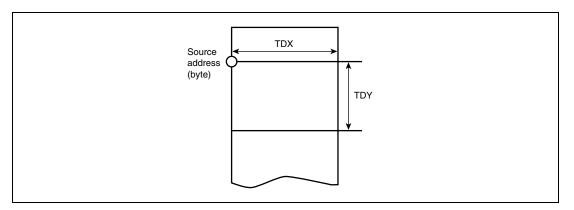

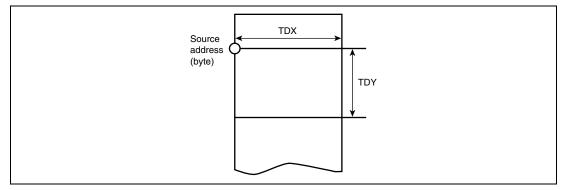

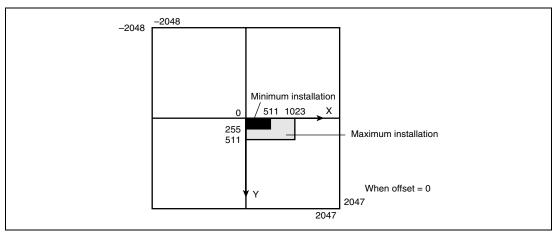

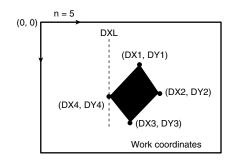

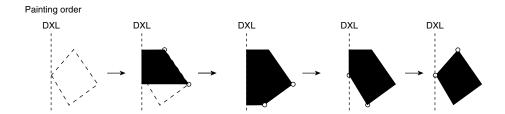

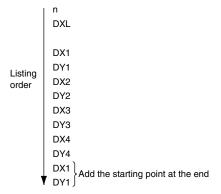

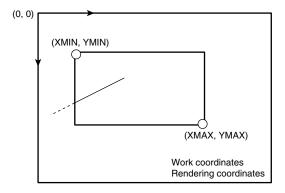

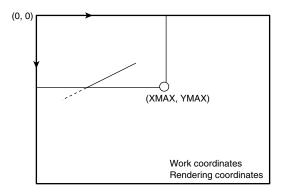

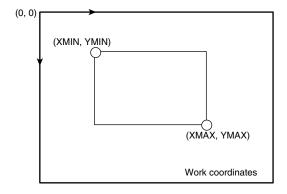

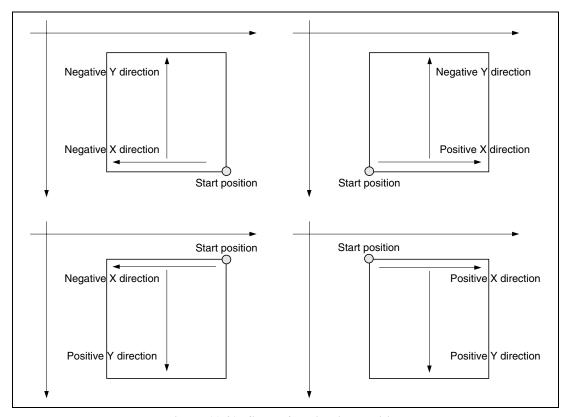

|      | 11.2.1 Coordinate Systems       |     |

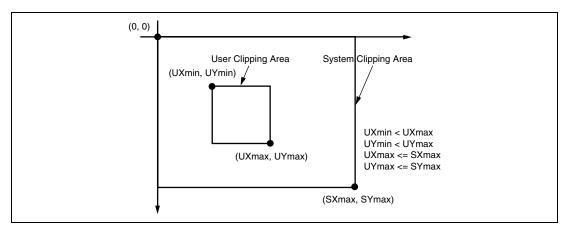

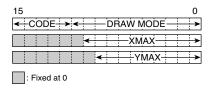

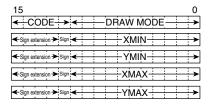

|      | 11.2.2 Clipping Area            |     |

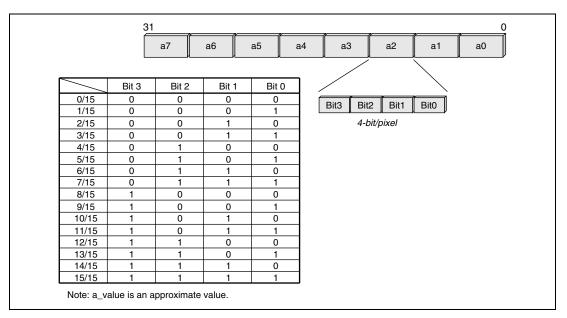

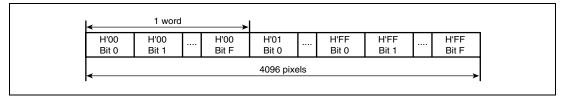

|      | 11.2.3 Pixel Data Format        |     |

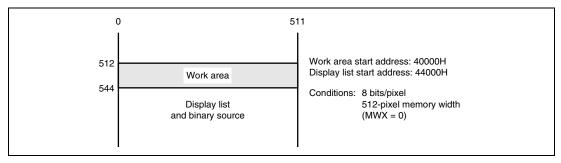

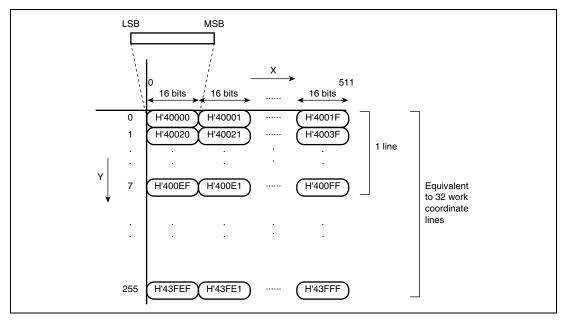

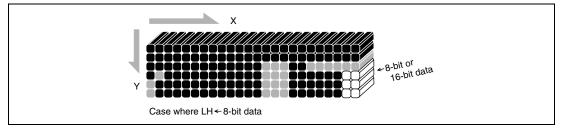

|      | 11.2.4 Memory Map               |     |

| 11.3 | • •                             |     |

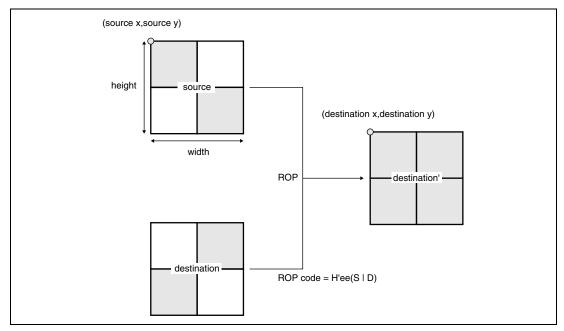

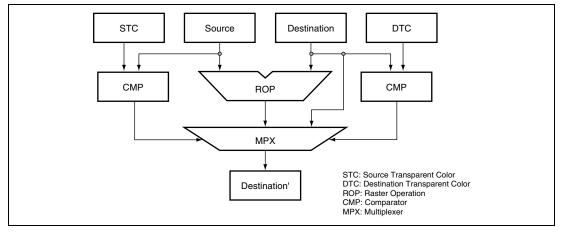

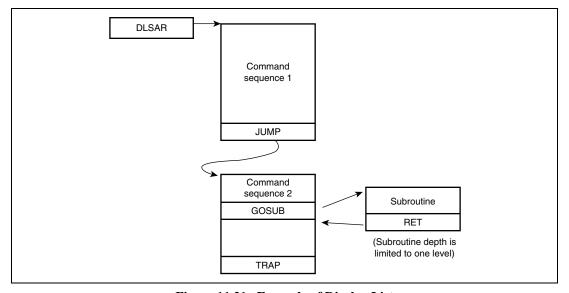

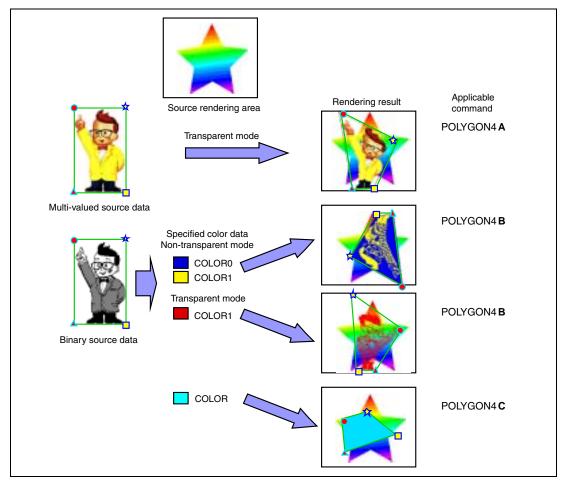

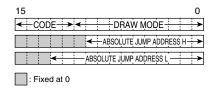

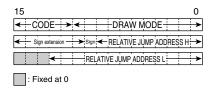

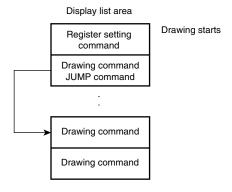

|      | 11.3.1 Overview                 |     |

|      | 11.3.2 Command Fetching         | 472 |

|      | 11.3.3 Q2SD/RU Basic Functions  |     |

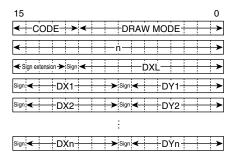

|      | 11.3.4 Q2SD/RU Drawing Commands |     |

|      | 11.3.5 2DGE Drawing Commands    |     |

| 11.4 | Register Description            |     |

|      | 11.4.1 Overview                 |     |

|      | 11.4.2 System Control Registers |     |

|      | 11.4.3 Q2SD/RU Registers        |     |

|      | 11.4.4 2DGE Registers           |     |

|      |                                 |     |

| Sect | ion 12 Color Space Converter    |     |

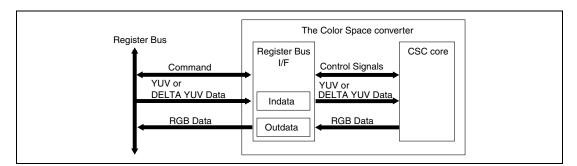

| 12.1 | General Description             | 581 |

| 12.2 | Features                        | 581 |

| 12.3 | Block Diagram                   | 581 |

| 12.4 | Data formats                    | 582 |

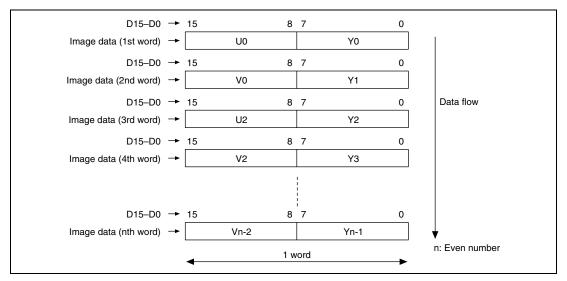

|      | 12.4.1 YUV data                 | 582 |

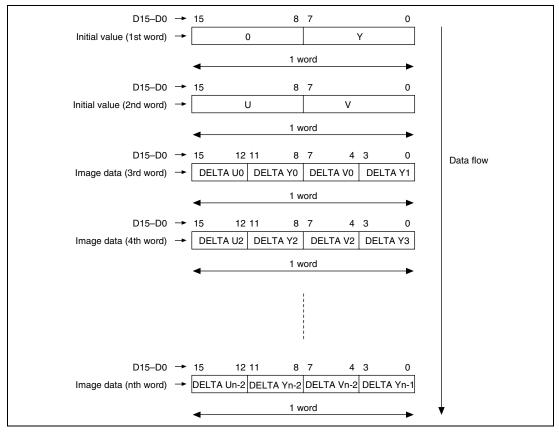

|      | 12.4.2 DELTA YUV data           | 583 |

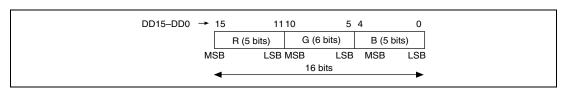

|      | 12.4.3 RGB data                 | 583 |

| 12.5 | Register Description            | 584 |

|      | 12.5.1 CSC Module Registers     | 584 |

|      | 12.5.2 Stadma Register          | 585 |

|      | 12.5.3 Indata Register          | 586 |

|      | 12.5.4 Outdata Register         | 587 |

|      | 12.5.5 Yuvmod Register          | 588 |

|      | 12.5.6 Start End Register       | 589 |

|      | 12.5.7 Transcount Register      | 590 |

|      | 12.5.8 Interrupt Register       | 591 |

| 12.6 | Functional Description          | 592 |

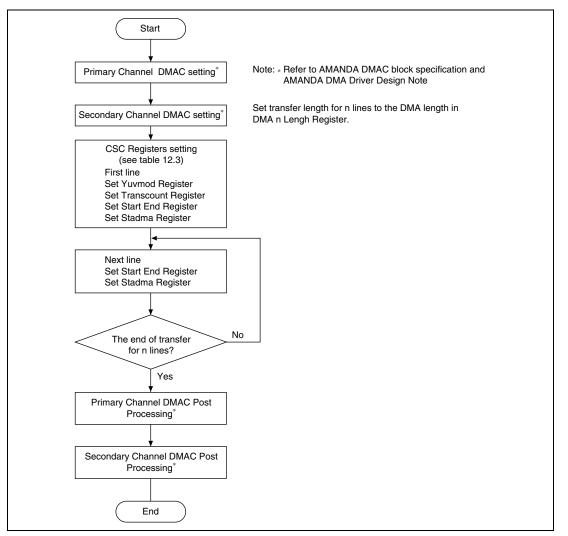

|      | 12.6.1 Utilization Flow         |     |

|      | 12.6.2 Endian setting           | 596 |

| Rev. | 1.0, 09/02, page xvi of xliv    |     |

|      | 12.6.3   | Module Standby Mode                         | 598     |

|------|----------|---------------------------------------------|---------|

| Sect | ion 13   | Audio Codec Interface                       | . 599   |

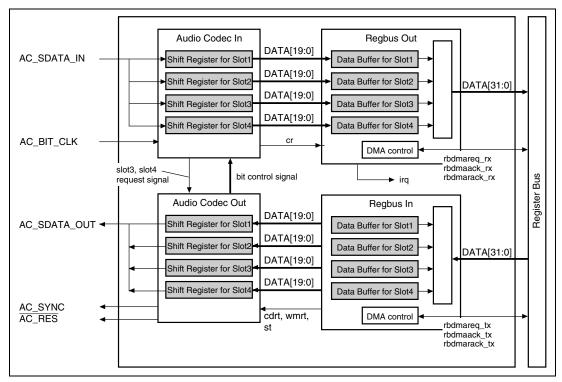

| 13.1 | Genera   | l Description                               | 599     |

| 13.2 | Feature  | 28                                          | 599     |

| 13.3 | Block    | Diagram                                     | 600     |

| 13.4 | Pin De   | scription                                   | 601     |

| 13.5 | Registe  | er Description                              | 602     |

|      | 13.5.1   | Control and Status Register (CR)            | 603     |

|      | 13.5.2   | Command/Status Address Register (CSAR)      | 604     |

|      | 13.5.3   | Command/Status Data Register (CSDR)         | 606     |

|      | 13.5.4   | PCM Playback/Record Left Channel (PCML)     | 607     |

|      | 13.5.5   | PCM Playback/Record Right Channel (PCMR)    | 610     |

|      | 13.5.6   | Transmit Interrupt Enable Register (TIER)   | 612     |

|      | 13.5.7   | TX Status Register (TSR)                    | 613     |

|      | 13.5.8   | Receive Interrupt Enable Register (RIER)    | 615     |

|      | 13.5.9   | RX Status Register (RSR)                    | 617     |

|      | 13.5.10  | Audio Codec Control Register (ACR)          | 618     |

|      | 13.5.11  | TX DMA Register (TXDMA)                     | 620     |

|      | 13.5.12  | 2 RX DMA Register (RXDMA)                   | 620     |

| 13.6 | Function | onal Description                            | 620     |

|      | 13.6.1   | Receiver                                    | 620     |

|      | 13.6.2   | Transmitter                                 | 621     |

|      | 13.6.3   | DMA                                         | 621     |

|      | 13.6.4   | Interrupts                                  | 621     |

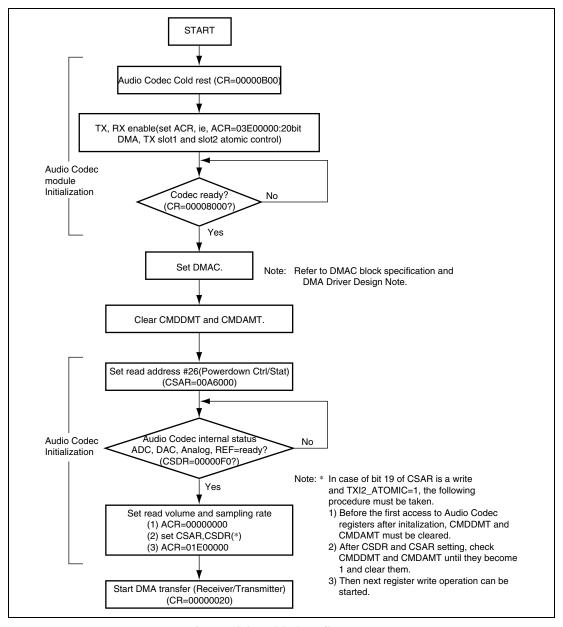

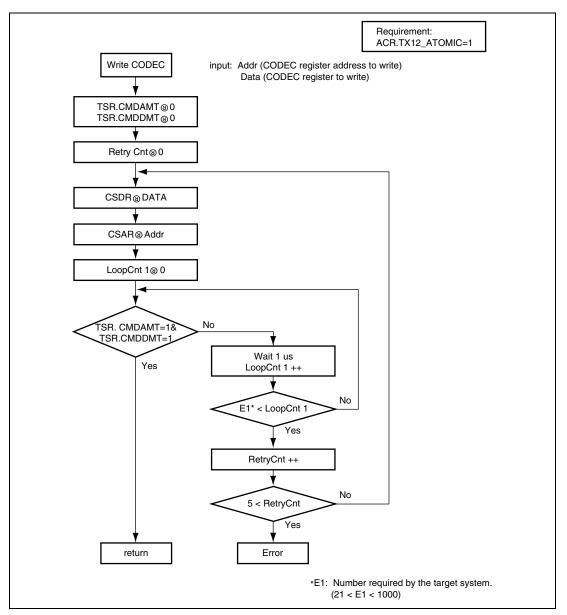

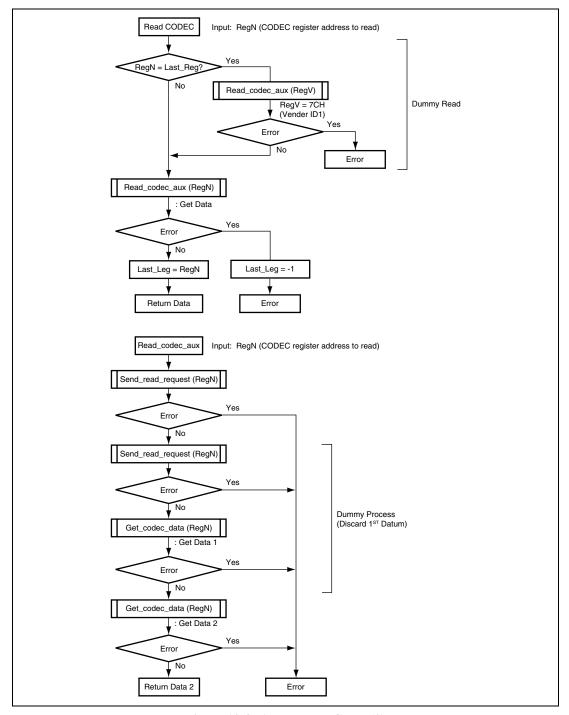

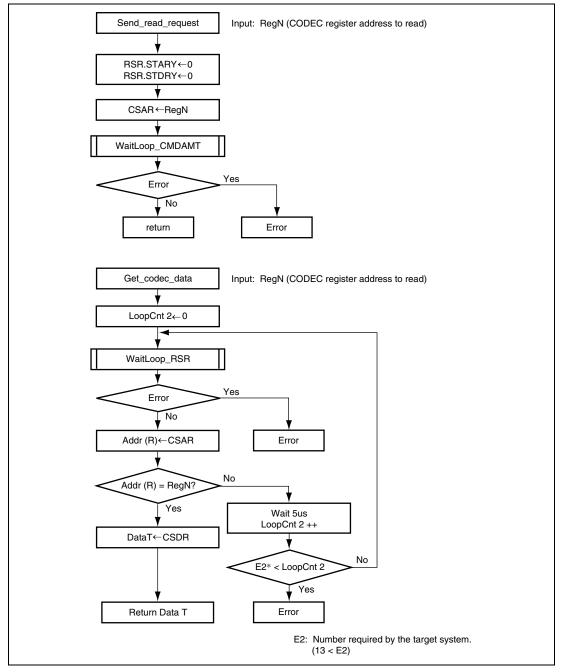

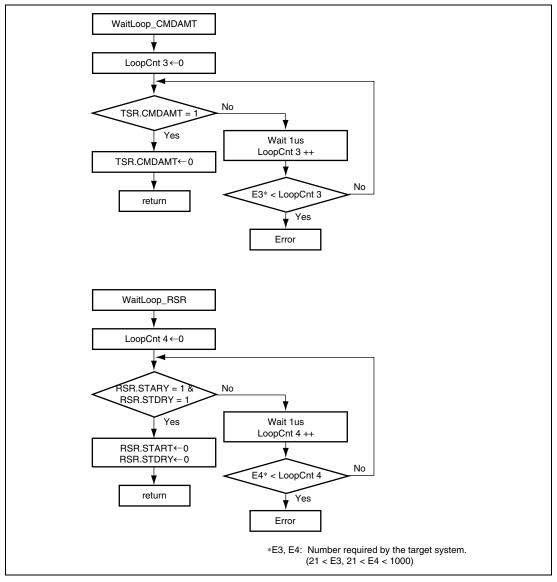

|      | 13.6.5   | Initialized sequence                        | 622     |

|      | 13.6.6   | Module Standby                              | 627     |

|      | 13.6.7   | General                                     | 627     |

| 13.7 | Refere   | nces                                        | 627     |

|      |          |                                             |         |

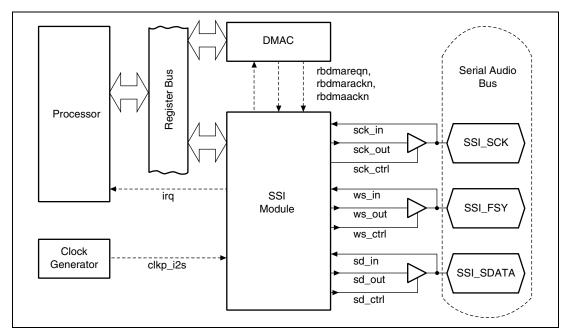

| Sect | ion 14   | Serial Sound Interface (SSI) Module         | . 629   |

| 14.1 | Genera   | l Description                               | 629     |

| 14.2 | Interfa  | ces                                         | 629     |

|      | 14.2.1   | Digital Inputs/Outputs                      | 630     |

|      | 14.2.2   | Software Interfaces                         | 631     |

| 14.3 |          | ers                                         |         |

|      | 14.3.1   | Control Register n (CR n) (n = 0 to 3)      | 632     |

|      | 14.3.2   |                                             |         |

|      | 14.3.3   | Transmit Data Register n (TDR n ) (n = 0-3) | 644     |

|      | 14.3.4   | Receive Data Register (RDR) (n = 0-3)       | 645     |

| 14.4 | SSI Mo   | odule Operation                             | 646     |

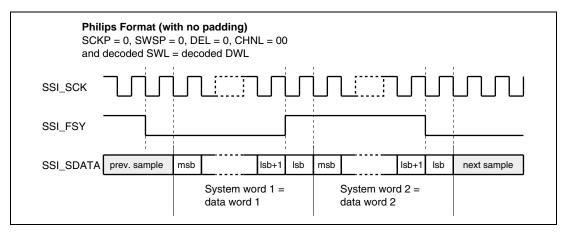

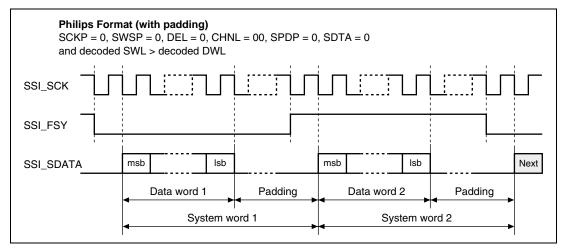

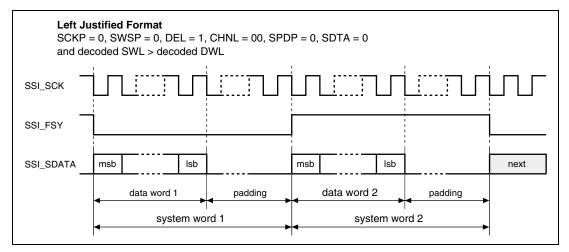

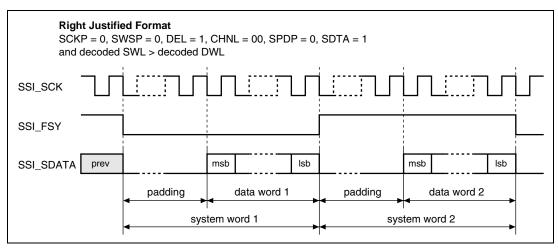

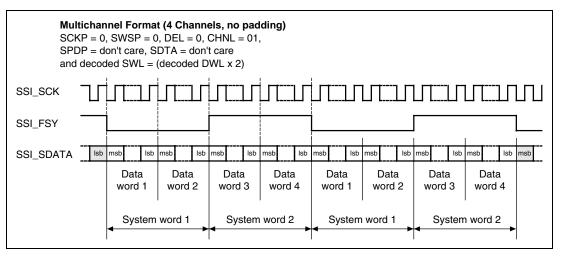

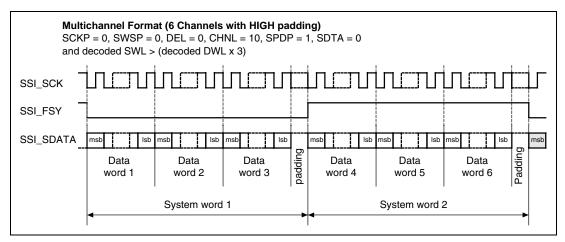

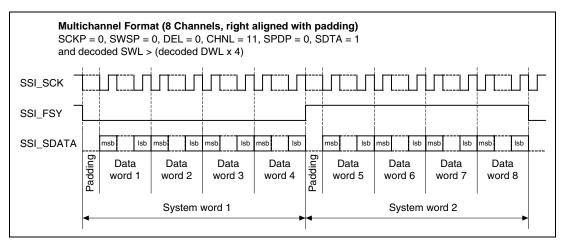

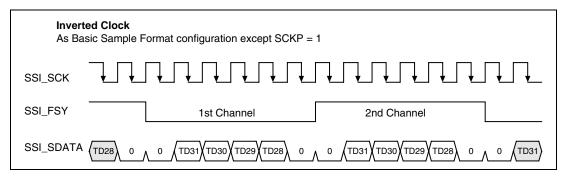

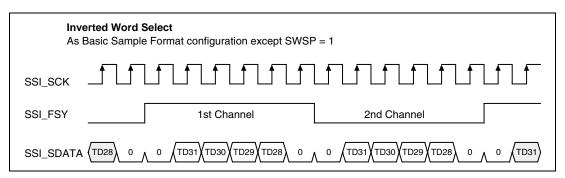

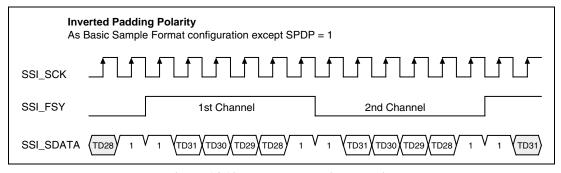

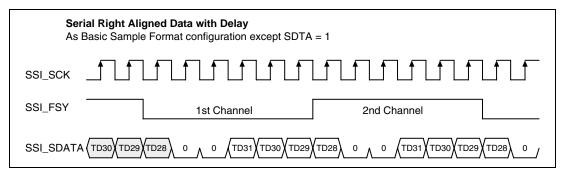

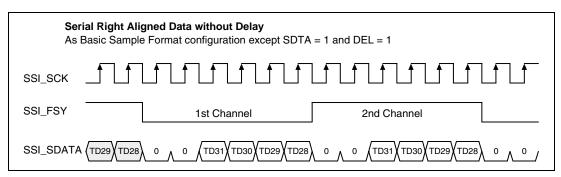

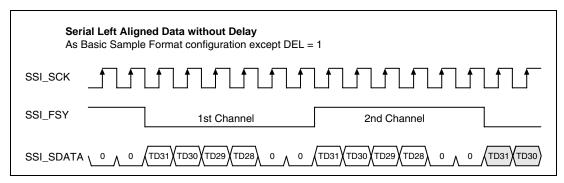

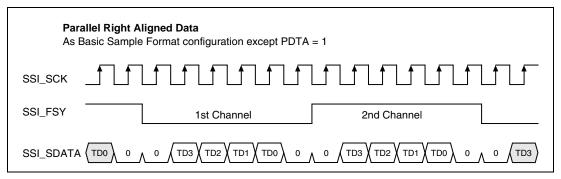

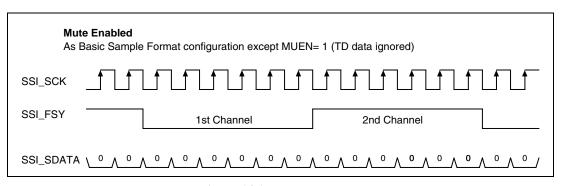

|      | 14.4.1   | Non-Compressed Modes                        | 647     |

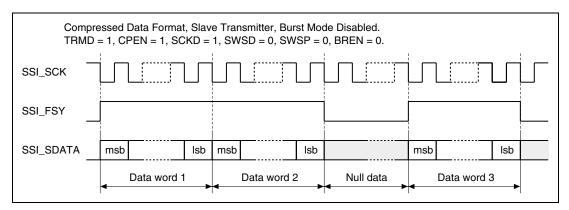

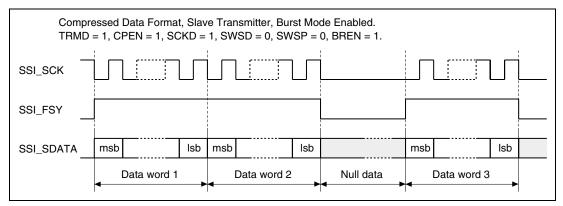

|      | 14.4.2   | Compressed Modes                            | 658     |

|      |          | Pov. 1.0. 00/02. pogo vvii                  | of vliv |

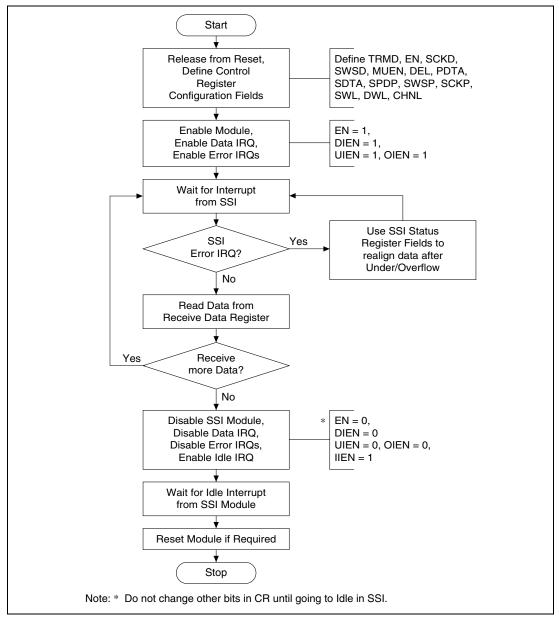

| 14.5 | Module    | e Operation                                      | 662 |

|------|-----------|--------------------------------------------------|-----|

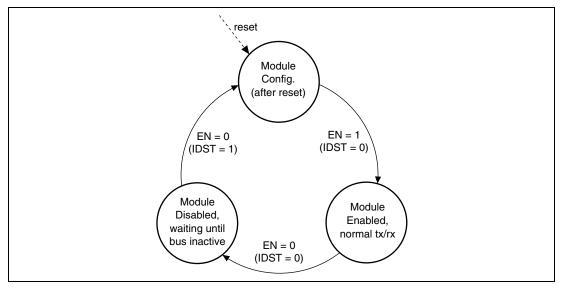

|      | 14.5.1    | Operation Modes                                  | 662 |

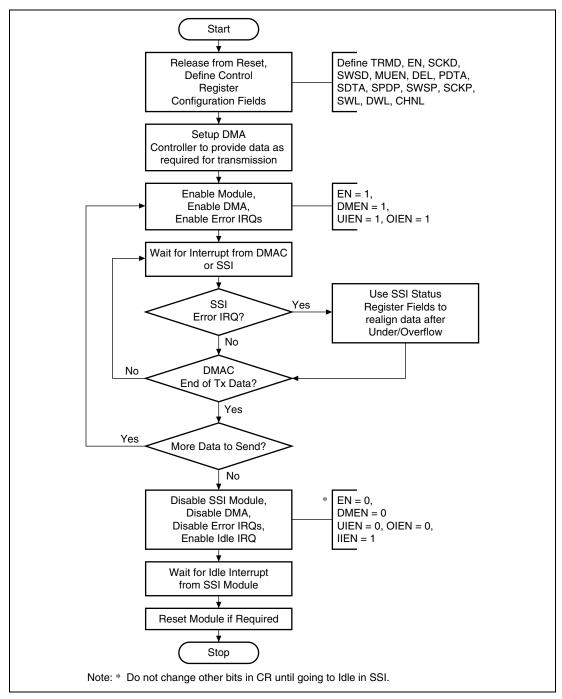

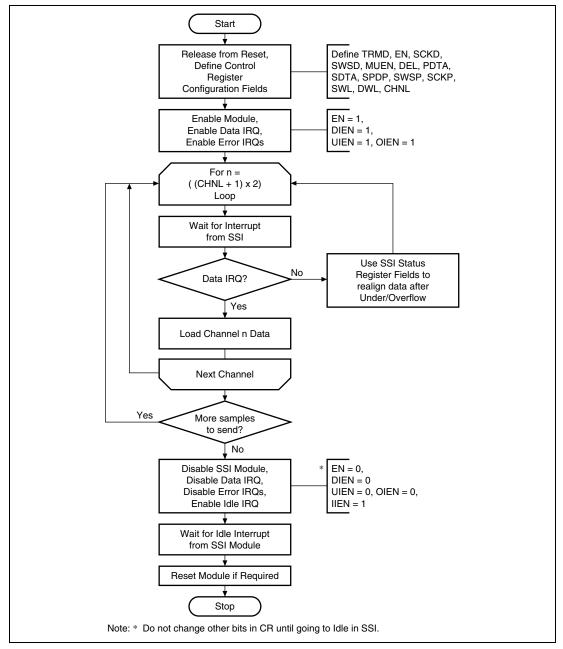

|      | 14.5.2    | Transmit Operation                               | 663 |

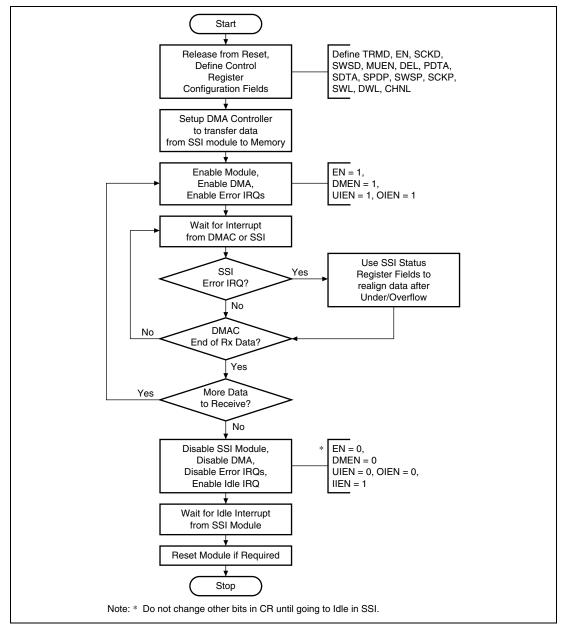

|      | 14.5.3    | Receive Operation                                | 666 |

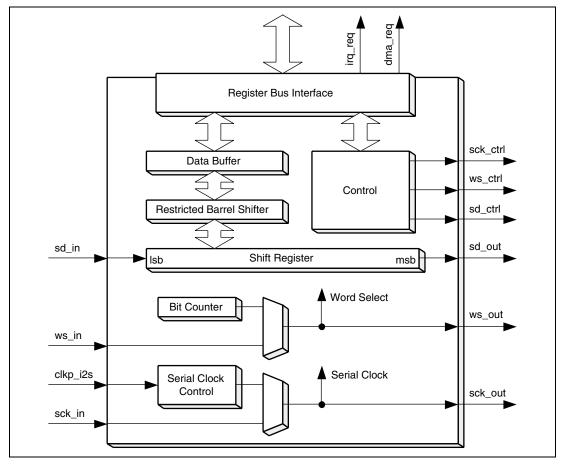

| 14.6 | Function  | onal Description                                 | 669 |

|      | 14.6.1    | Register Bus Interface and Control               | 670 |

|      | 14.6.2    | Buffer and Shift Register                        | 670 |

|      | 14.6.3    | Control (including Bit Counter)                  | 671 |

|      | 14.6.4    | Serial Clock Control                             | 671 |

| 14.7 | Power     | Saving and Clocking Strategy                     | 671 |

| 14.8 | Refere    | nces                                             | 672 |

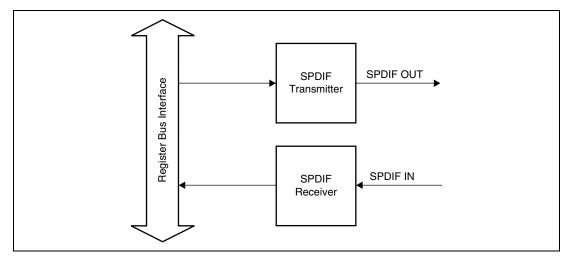

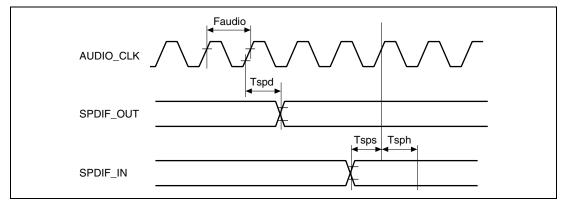

| Sect | ion 15    | Hitachi SPDIF Interface                          | 673 |

| 15.1 | Overvi    | ew                                               | 673 |

| 15.2 | Feature   | es                                               | 673 |

| 15.3 | Function  | onal Block Diagram                               | 674 |

| 15.4 | Pin De    | scription                                        | 674 |

|      | 15.4.1    | Processor Interface Pins                         | 674 |

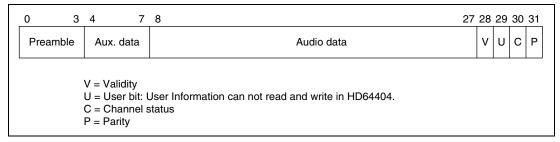

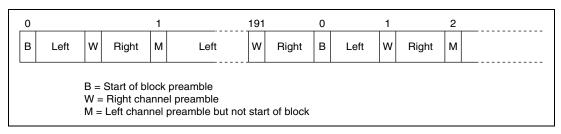

| 15.5 | SPDIF     | (IEC60958) Block Format                          | 675 |

| 15.6 | Registe   | er Map                                           | 676 |

| 15.7 | Registe   | er Descriptions                                  | 677 |

|      | 15.7.1    | Control Register (CTRL)                          | 677 |

|      | 15.7.2    | Status Register (STAT)                           | 681 |

|      | 15.7.3    | Transmitter Left Channel Audio Register (TLCA)   | 685 |

|      | 15.7.4    | Transmitter Right Channel Audio Register (TRCA)  | 686 |

|      | 15.7.5    | Transmitter DMA Audio Data Register (TDAD)       | 686 |

|      | 15.7.6    | Reseve Register                                  | 687 |

|      | 15.7.7    | Transmitter Left Channel Status Register (TLCS)  | 687 |

|      | 15.7.8    | Transmitter Right Channel Status Register (TRCS) | 689 |

|      | 15.7.9    | Receiver Left Channel Audio Register (RLCA)      | 690 |

|      | 15.7.10   | Receiver Right Channel Audio Register (RRCA)     | 690 |

|      | 15.7.11   | 1 Receiver DMA Audio Data (RDAD)                 | 691 |

|      | 15.7.12   | 2 Reserve Register                               | 691 |

|      | 15.7.13   | Receiver Left Channel Status Register (RLCS)     | 692 |

|      | 15.7.14   | 4 Receiver Right Channel Status Register (RRCS)  | 693 |

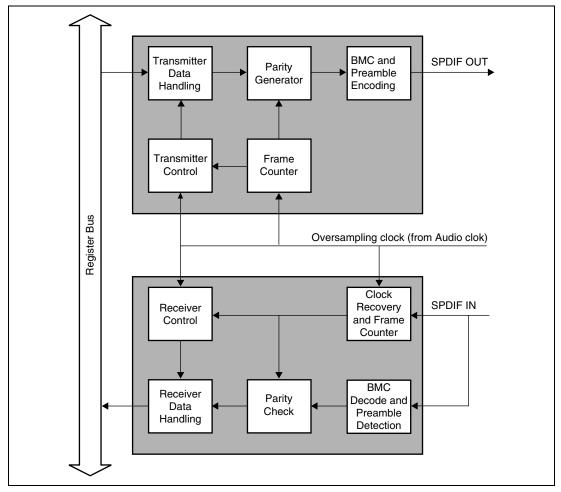

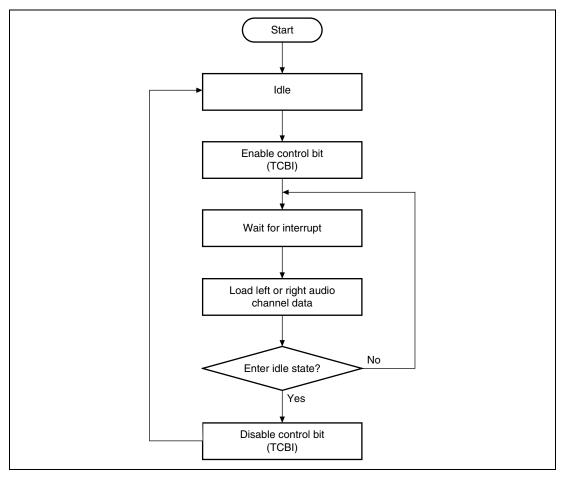

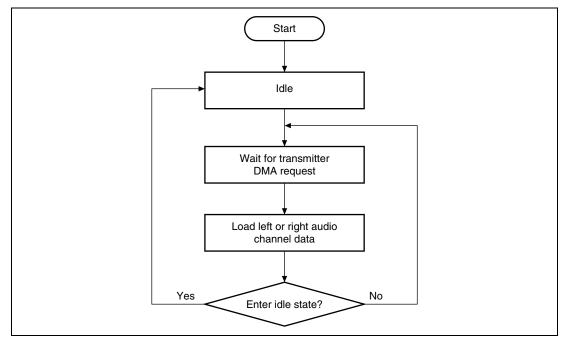

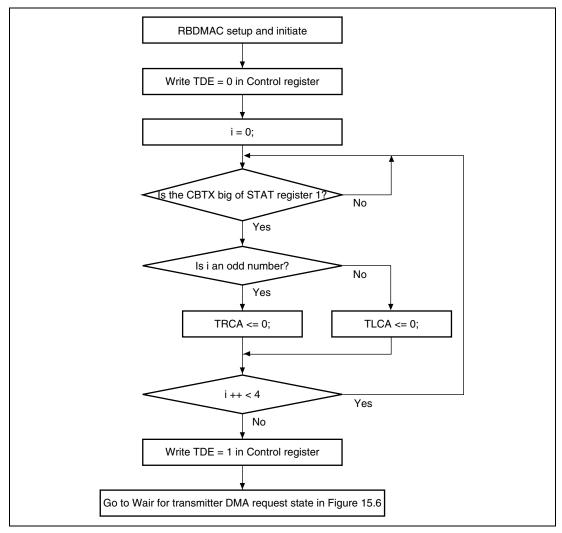

| 15.8 | Function  | onal Description—Transmitter                     | 695 |

|      | 15.8.1    | Module Interface                                 | 695 |

|      | 15.8.2    | Transmitter Module                               | 695 |

|      | 15.8.3    | Transmitter Module Initialisation                | 696 |

|      | 15.8.4    | Transmitter Module Data Transfer                 | 696 |

| 15.9 | Function  | onal Description—Receiver                        | 699 |

|      | 15.9.1    | Module Interface                                 | 699 |

|      | 15.9.2    | Receiver Module                                  | 699 |

| Rev. | 1.0, 09/0 | 02, page xviii of xliv                           |     |

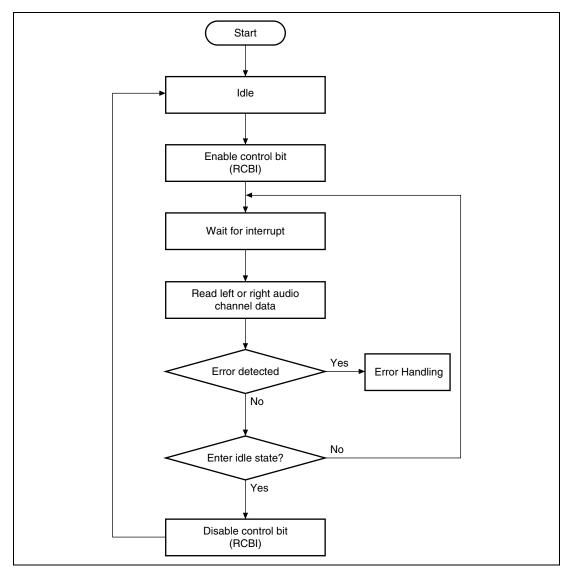

| ]       | 15.9.3 Receiver Module Initialisation                      | 700                       |

|---------|------------------------------------------------------------|---------------------------|

| 1       | 15.9.4 Receiver Module Data Transfer                       | 700                       |

| 15.10 I | Disabling the Module                                       | 704                       |

| 1       | 15.10.1 Transmitter and Receiver Idle                      | 704                       |

| 1       | 15.10.2 Power Down Mode                                    | 704                       |

| 15.11   | Compressed Mode Data                                       | 704                       |

| 15.12 I | References                                                 | 704                       |

| 15.13   | Glossary                                                   | 704                       |

|         | 2                                                          |                           |

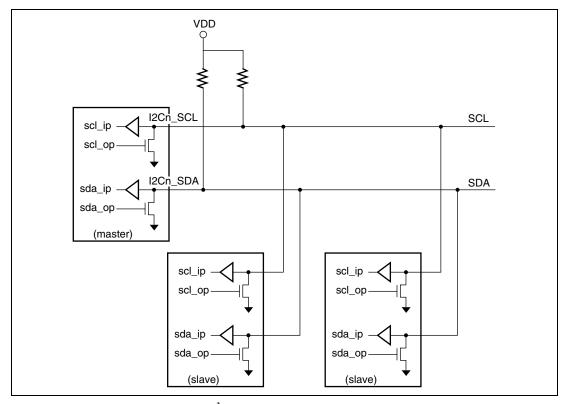

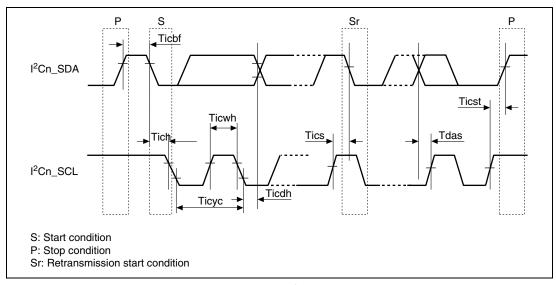

| Sectio  | on 16 Hitachi I <sup>2</sup> C Interface                   | 705                       |

| 16.1    | General Description                                        | 705                       |

| 16.2 I  | Features                                                   | 706                       |

| 16.3 I  | Pin Descriptions                                           | 707                       |

| 16.4 I  | Register Map                                               | 708                       |

| 16.5 I  | Register Descriptions                                      | 709                       |

| 1       | 16.5.1 Slave Control Register (SCR n) $(n = 0,1)$          | 709                       |

| 1       | 16.5.2 Slave Status Register (SSR n) (n = 0,1)             | 711                       |

| 1       | 16.5.3 Slave Interrupt Enable Register (SIER n) (n = 0,1)  | 713                       |

| 1       | 16.5.4 Slave Address Register (SAR n) (n = 0,1)            | 713                       |

| 1       | 16.5.5 Master Control Register (MCR n) (n = 0,1)           | 714                       |

| 1       | 16.5.6 Master Status Register (MSR n) (n = 0,1)            | 717                       |

| 1       | 16.5.7 Master Interrupt Enable Register (MIER n) (n = 0,1) | 719                       |

| 1       | 16.5.8 Master Address Register (MAR n) (n = 0,1)           | 720                       |

| 1       | 16.5.9 Clock Control Register (CCR n) (n = 0,1)            | 721                       |

| 1       | 16.5.10 Receive/Transmit Data (RXD n/TXD n) (n = 0, 1)     | 722                       |

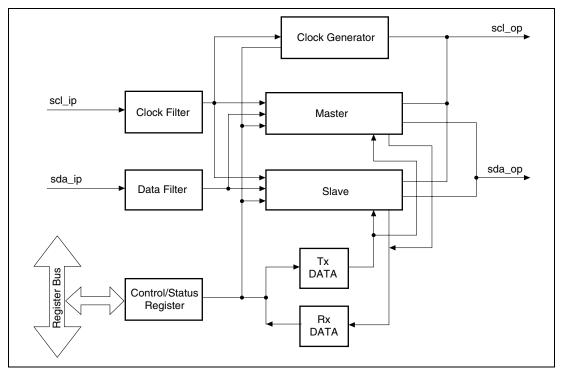

| 16.6 I  | Functional Description                                     | 723                       |

| 1       | 16.6.1 Data and Clock Filters                              | 723                       |

| 1       | 16.6.2 Clock Generator                                     | 723                       |

| 1       | 16.6.3 Master/Slave Interfaces                             | 724                       |

| 1       | 16.6.4 Software Interface                                  | 724                       |

| 1       | 16.6.5 Software Status Interlocking                        | 724                       |

|         | Operation                                                  |                           |

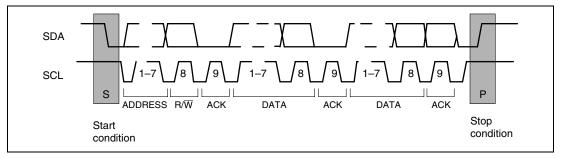

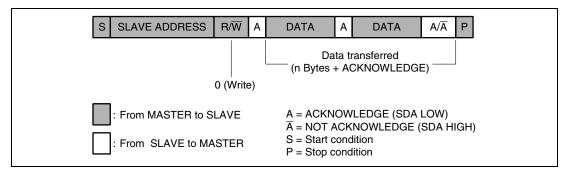

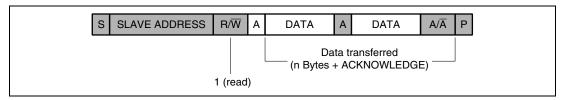

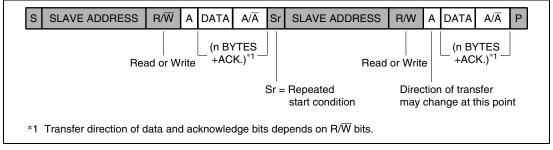

| 16.8 I  | r <sup>2</sup> C Bus Data Format                           | 727                       |

| 1       | 16.8.1 7-Bit Address Format                                | 727                       |

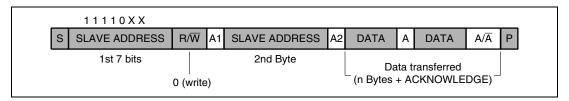

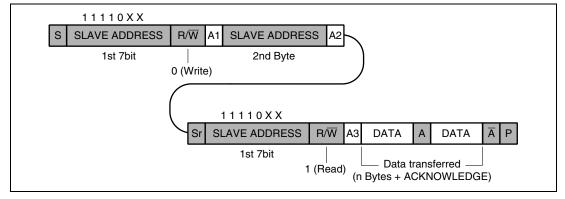

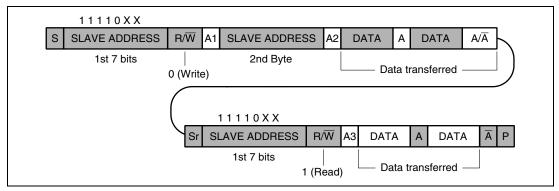

| 1       | 16.8.2 10-Bit Address Format                               | 728                       |

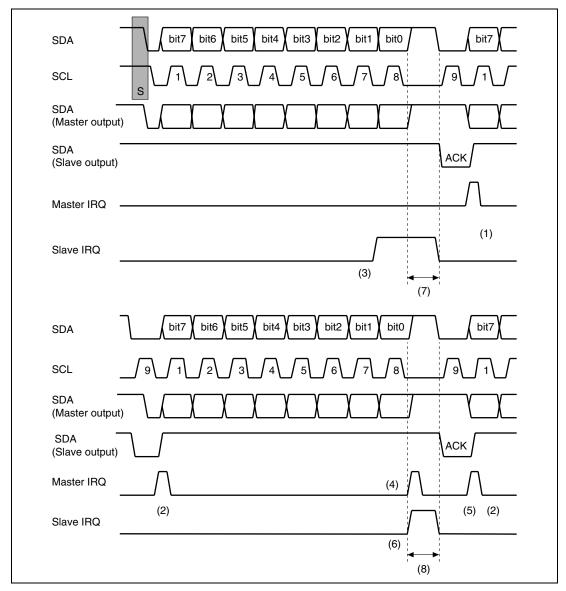

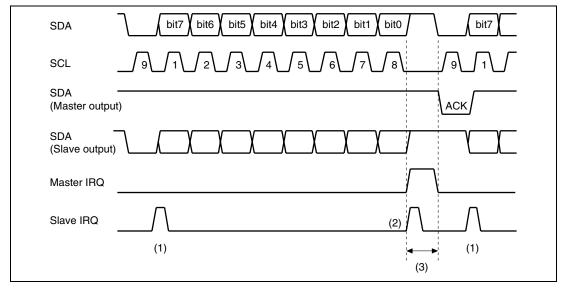

| 1       | 16.8.3 Master Transmit Operation                           | 730                       |

| 1       | 16.8.4 Master Receive Operation                            |                           |

| 1       | 16.8.5 Procedure for Entering Standby Mode                 |                           |

|         | Programming Examples                                       |                           |

|         | 16.9.1 Master Transmitter                                  |                           |

| 1       | 16.9.2 Master Receiver                                     |                           |

| 1       | 16.9.3 Master Transmitter—Restart—Master Receiver          |                           |

|         | Notice                                                     |                           |

|         |                                                            |                           |

|         | Rev. 1.0                                                   | ), 09/02, page xix of xli |

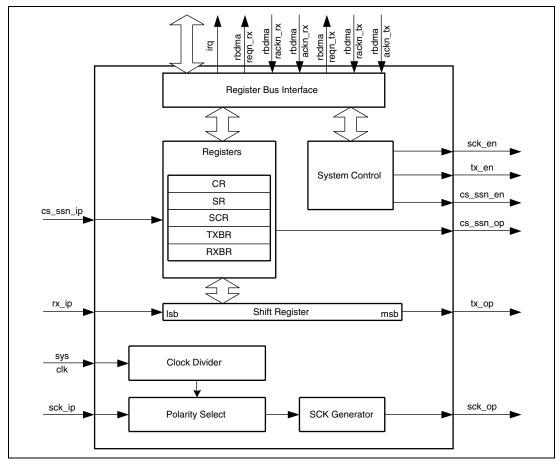

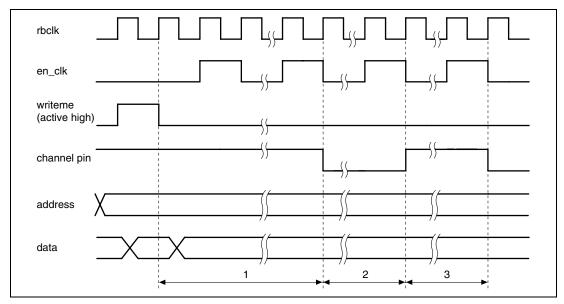

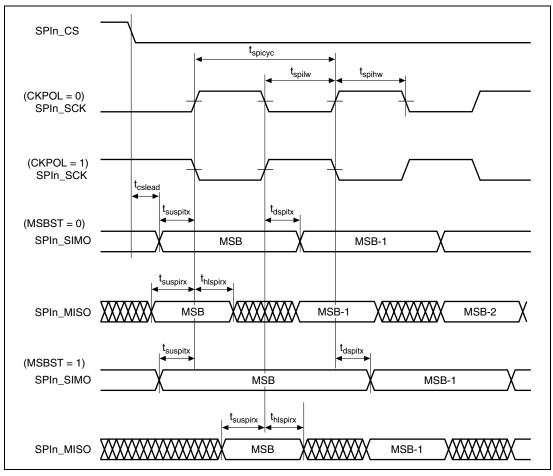

| Secti | ion 17   | Hitachi Serial Peripheral Interface                 | 739 |

|-------|----------|-----------------------------------------------------|-----|

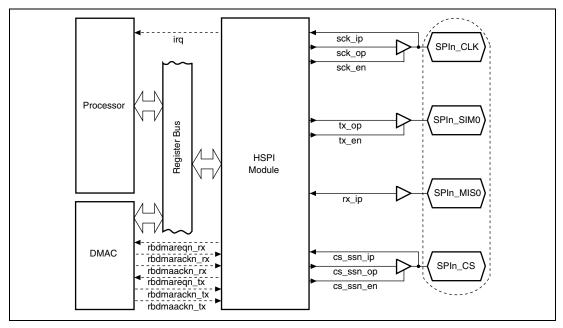

| 17.1  |          | l Description                                       |     |

| 17.2  |          | ces                                                 |     |

|       | 17.2.1   | Digital Inputs/Outputs                              | 741 |

|       | 17.2.2   | Software Interfaces                                 | 742 |

| 17.3  | Registe  | er Description                                      | 742 |

|       | 17.3.1   | Control Register n (CR n) (n = 0 to 2)              | 743 |

|       |          | Status Register n (SRn ) (n = 0 to 2)               |     |

|       | 17.3.3   |                                                     |     |

|       | 17.3.4   | Transmit Buffer Register n (TXBR n) (n = 0 to 2)    | 750 |

|       | 17.3.5   | Receive Buffer Register n (RXBR n) (n = 0 to 2)     | 750 |

| 17.4  |          | Module Operation                                    |     |

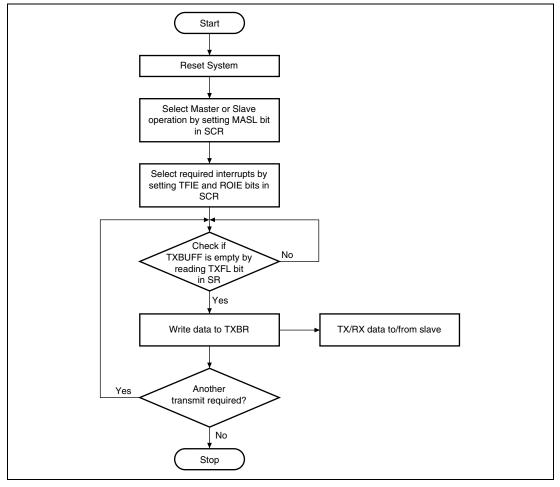

|       | 17.4.1   | Operation Overview without DMA (Fifo Mode Disabled) |     |

|       | 17.4.2   | _                                                   |     |

|       | 17.4.3   | =                                                   |     |

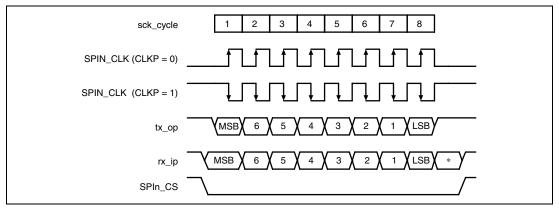

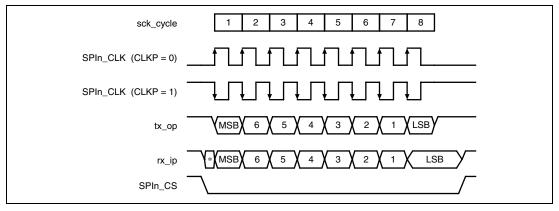

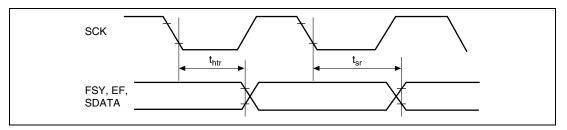

|       | 17.4.4   | Timing Diagrams                                     |     |

|       |          | Error Handling                                      |     |

|       |          | Soft Reset                                          |     |

| 17.5  |          | onal Description                                    |     |

|       | 17.5.1   | •                                                   |     |

|       | 17.5.2   | Clock Polarity and Transmit Control                 |     |

|       |          | Transmit and Receive Routines                       |     |

| 17.6  |          | Saving and Clocking Strategy                        |     |

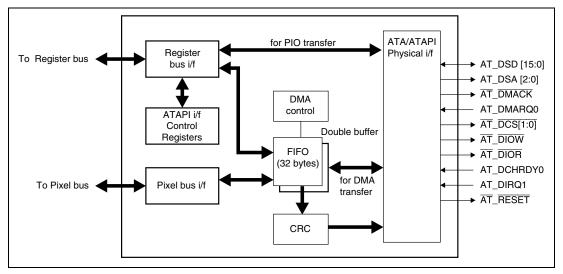

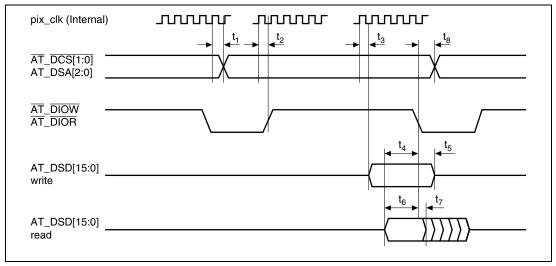

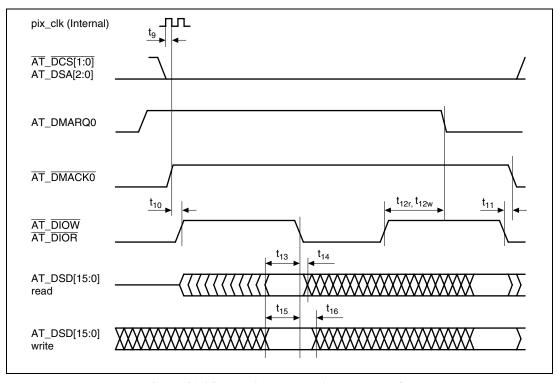

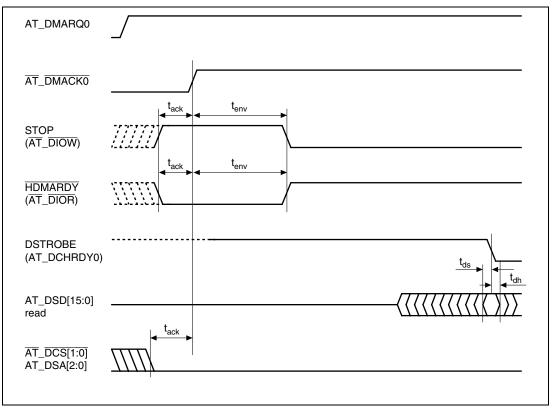

| Secti | ion 18   | ATAPI                                               | 759 |

| 18.1  |          | l Description                                       |     |

| 18.2  |          | es                                                  |     |

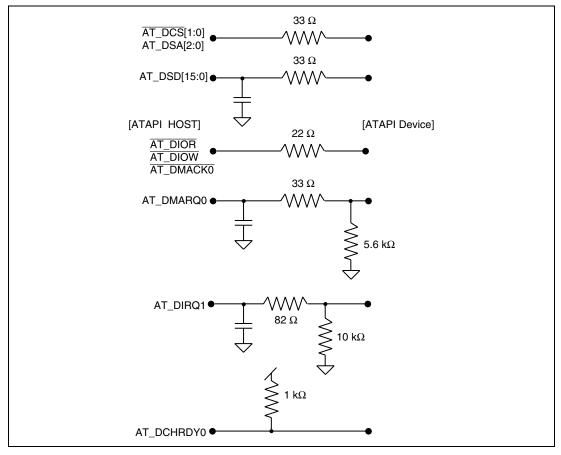

| 18.3  |          | al Interface                                        |     |

| 18.4  |          | Diagram                                             |     |

| 18.5  |          | er Description                                      |     |

|       | _        | ATAPI Interface Registers                           |     |

|       |          | ATA Task File Register                              |     |

|       |          | ATAPI Packet Command Task File Register             |     |

|       |          | ATAPI I/F Control Register Map                      |     |

| 18.6  |          | onal Description                                    |     |

| 18.7  |          | ed Termination                                      |     |

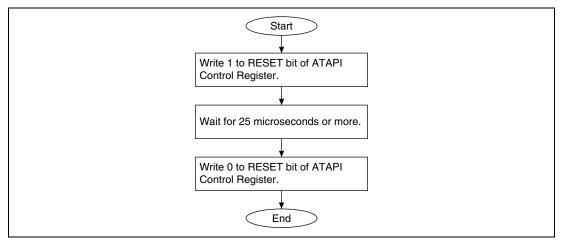

| 18.8  | -        | ing Procedure                                       |     |

| 10.0  |          | Initialization                                      |     |

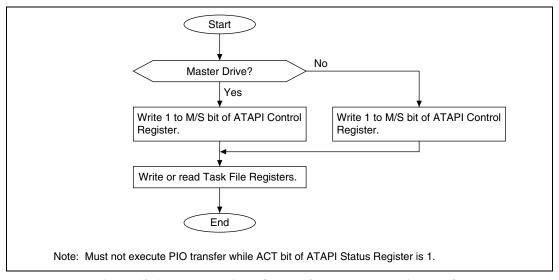

|       |          | Procedure in PIO Transfer Mode                      |     |

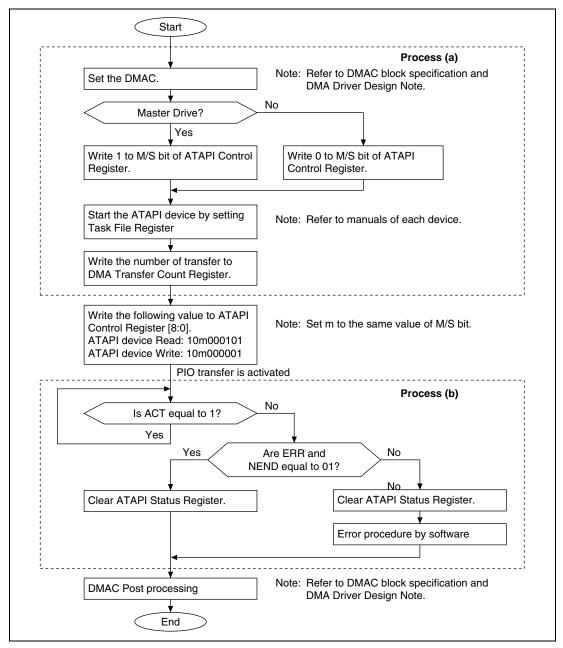

|       |          | Procedure in Multi Word DMA Transfer Mode           |     |

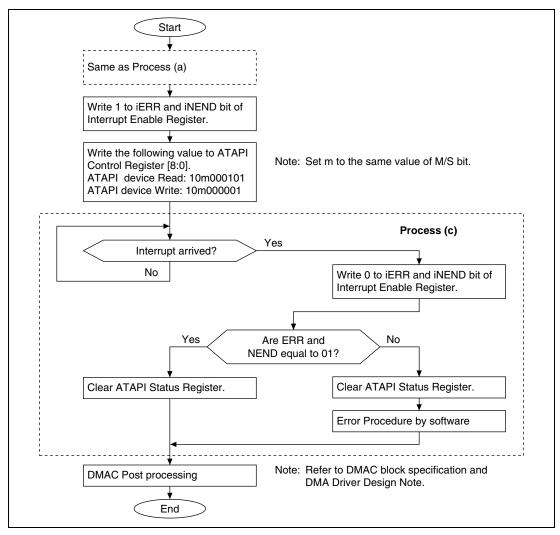

|       |          | Procedure in Ultra DMA Transfer Mode                |     |

|       |          | Procedure in Hardware Reset for ATAPI Device        |     |

|       | 10.0.3   | Troopers in Hardware Reset for ATTAI I Device       |     |

| Davis | 4 0 00/0 | O management of the                                 |     |

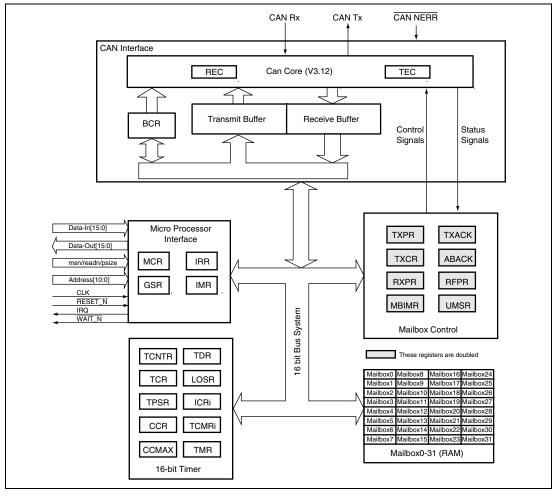

| Sect | ion 19  | HCAN-2 Module                                                | 80  |

|------|---------|--------------------------------------------------------------|-----|

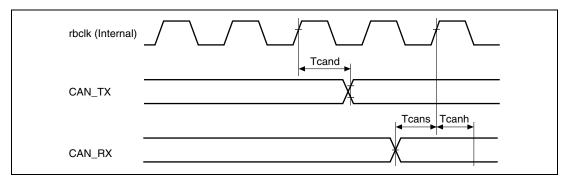

| 19.1 | Summa   | ıry                                                          | 801 |

|      | 19.1.1  | Overview                                                     | 801 |

|      | 19.1.2  | Scope                                                        | 801 |

|      | 19.1.3  | Audience                                                     | 801 |

|      | 19.1.4  | References                                                   | 802 |

|      | 19.1.5  | Features                                                     | 802 |

|      | 19.1.6  | HCAN-2 Differences from HCAN-1                               | 803 |

| 19.2 |         | ecture                                                       |     |

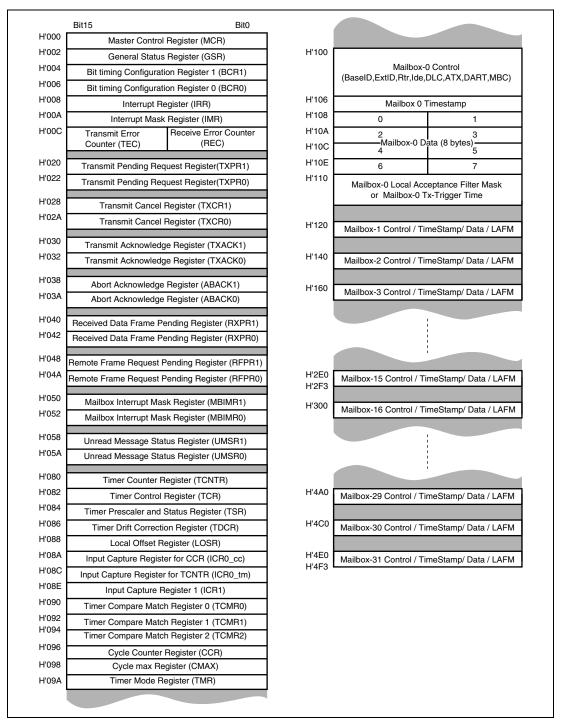

| 19.3 | Program | mming Model - Overview                                       | 806 |

|      | 19.3.1  | Memory Map                                                   | 806 |

|      | 19.3.2  | Mailbox Structure                                            | 808 |

|      | 19.3.3  | HCAN Control Registers                                       | 817 |

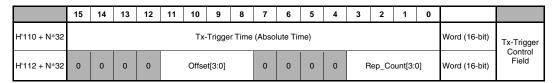

|      | 19.3.4  | HCAN Mailbox Registers                                       | 839 |

|      |         | Timer Registers                                              |     |

| 19.4 |         | ation Note                                                   |     |

|      | 19.4.1  | Test Mode Settings                                           | 870 |

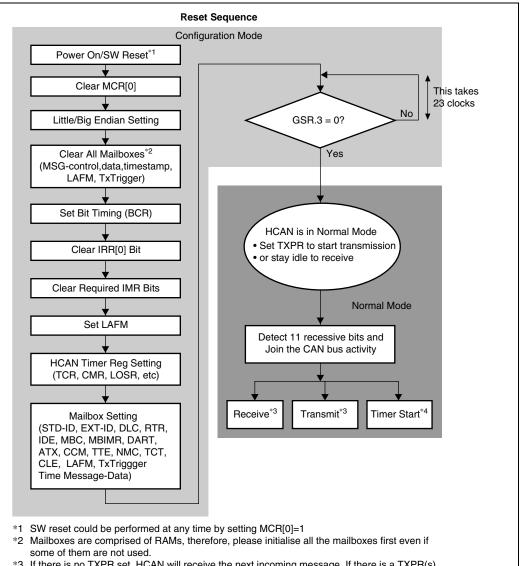

|      | 19.4.2  | Configuration of HCAN                                        |     |

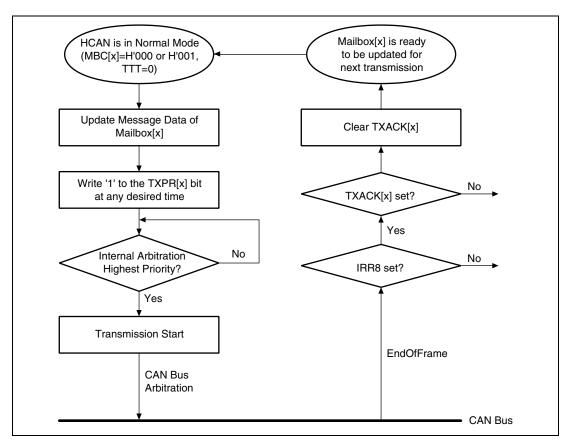

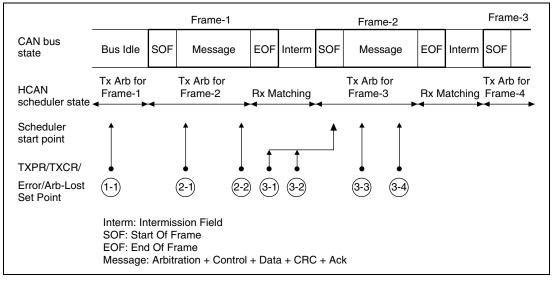

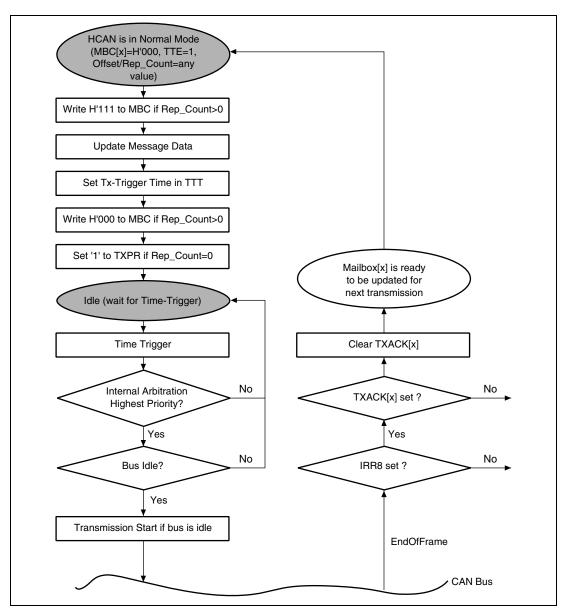

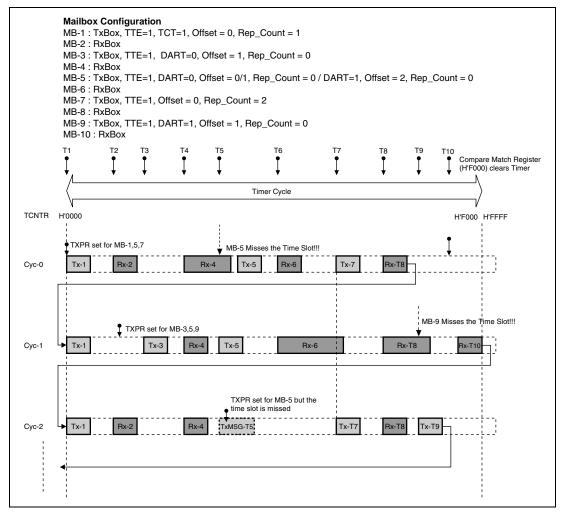

|      |         | Message Transmission Sequence                                |     |

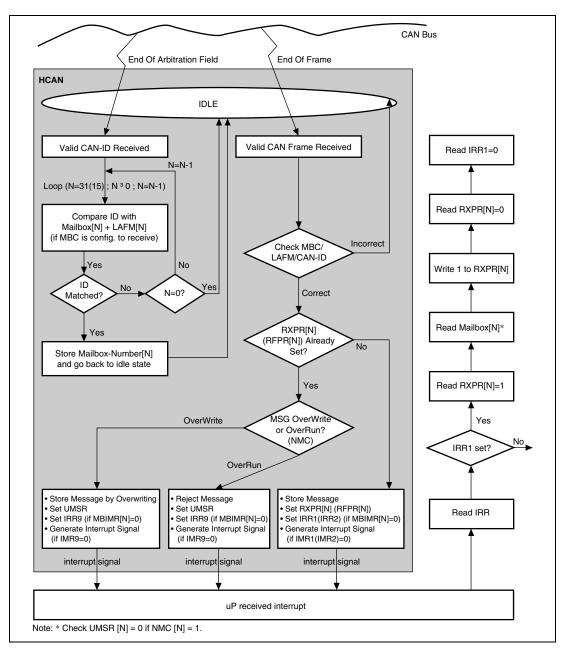

|      |         | Message Receive Sequence                                     |     |

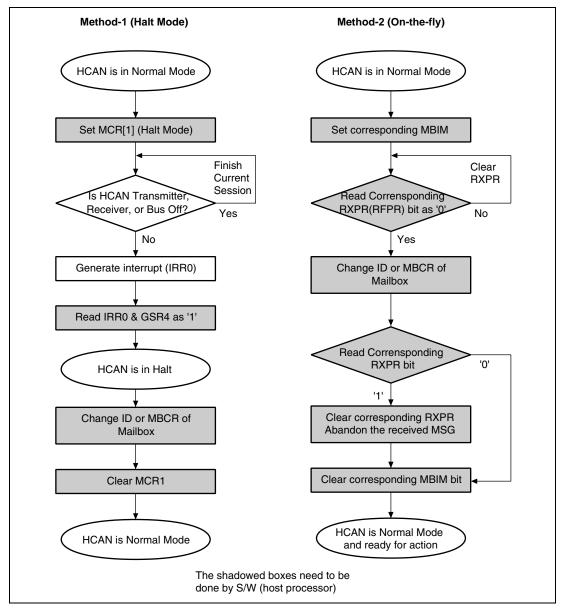

|      |         | Reconfiguration of Mailbox                                   |     |

|      |         | Global Synchronization                                       |     |

|      |         | HCAN module Standby-mode                                     |     |

|      |         | Registers Index                                              |     |

| Sect | ion 20  | Most Interface Module                                        | 889 |

| 20.1 | Genera  | l Description                                                | 889 |

|      |         | Features                                                     |     |

|      |         | Terminology                                                  |     |

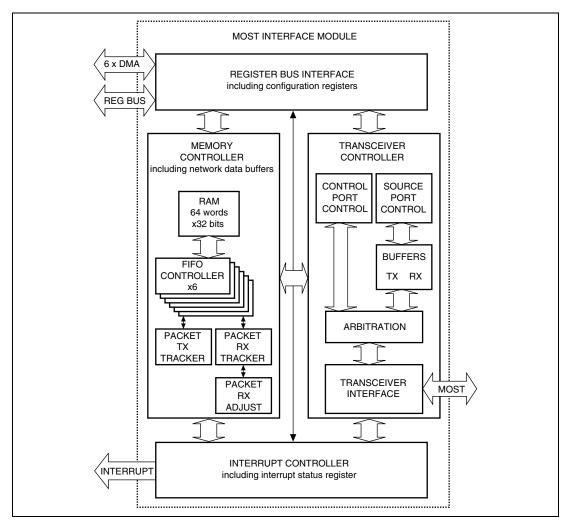

| 20.2 |         | ectural Overview                                             |     |

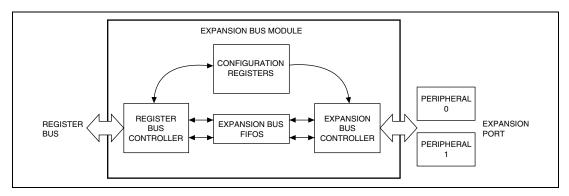

|      |         | Block Diagram                                                |     |

| 20.3 |         | scriptions                                                   |     |

| 20.4 |         | er Description                                               |     |

|      | _       | Data Registers                                               |     |

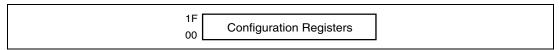

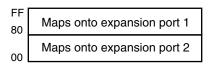

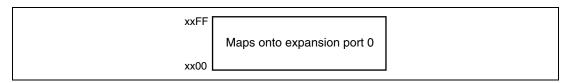

|      |         | Configuration Registers                                      |     |

| 20.5 |         | e Register Descriptions                                      |     |

|      | 20.5.1  | MIM Stream1, MIM Stream2, MIM Stream3, MIM Stream4 Registers |     |

|      |         | MIM_Stream1_Config, MIM_Stream2_Config, MIM_Stream3_Config,  |     |

|      |         | MIM_Stream4_Config Registers                                 | 895 |

|      | 20.5.3  | MIM_PacketTx (W)                                             |     |

|      | 20.5.4  |                                                              |     |

|      | 20.5.5  | _ , ,                                                        |     |

|      |         | MIM Control Config Register                                  |     |

|      |         | Rev. 1.0, 09/02, page >                                      |     |

|      |         | 1.01. 1.0, 00/02, page /                                     |     |

|         |          | MIM Interrupt Status Register                                    |      |

|---------|----------|------------------------------------------------------------------|------|

|         |          | MIM Interrupt Enable Register                                    |      |

|         |          | MIM Buffer Ready Register                                        |      |

|         |          | MIM PacketRx Config Register                                     |      |

|         |          | MIM PacketTx Config Register                                     |      |

|         |          | MIM Module Config Register                                       |      |

|         |          | MIM MOST Reg Wr Register                                         |      |

|         |          | MIM MOST Reg Rd Register                                         |      |

|         |          | MIM_Status                                                       |      |

| 20.6    | Functio  | nal overview                                                     | .918 |

|         | 20.6.1   | General Functionality                                            | .918 |

| 20.7    | Data Ha  | andling Methods                                                  | .919 |

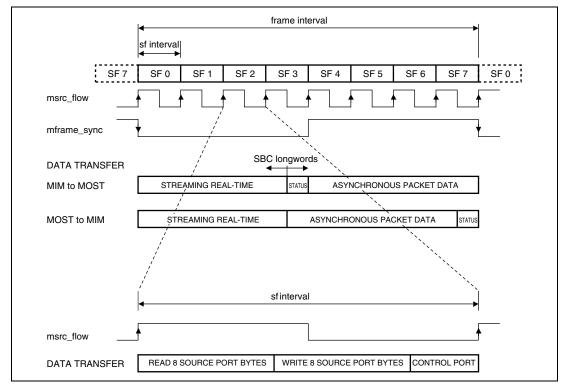

|         | 20.7.1   | Streaming real-time data                                         | .919 |

|         | 20.7.2   | High Bandwidth packet data                                       | .920 |

|         | 20.7.3   | Control Messages                                                 | .921 |

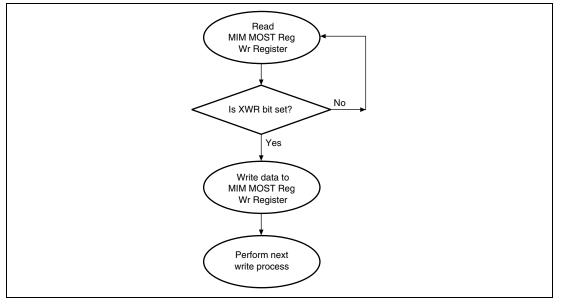

|         | 20.7.4   | Automatically Sending Control Messages to the MOST transceiver   | .922 |

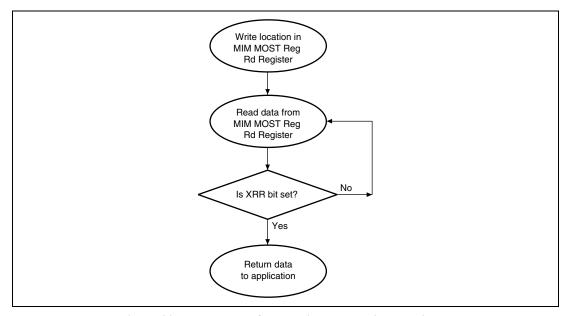

|         | 20.7.5   | Automatically Reading Control Messages from the MOST Transceiver | .923 |

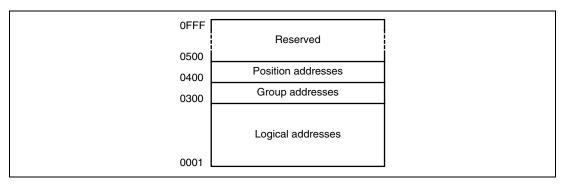

|         |          | Addressing formats                                               |      |

| 20.8    |          | uration of the MOST transceiver                                  |      |

|         | _        | Canceling a stream currently in use                              |      |

|         |          | Setting up a new data stream                                     |      |

|         |          | Programming MIM Module Config'                                   |      |

|         |          | Example streaming application                                    |      |

| 20.9    |          | ng Transceiver Registers                                         |      |

|         |          | eiver Power Up Procedure                                         |      |

|         |          | atic polling of transceiver registers                            |      |

|         |          | ot sources                                                       |      |

|         | _        | eiver loss of lock procedure                                     |      |

|         |          | es to the MOST transceiver                                       |      |

|         |          | Interface Module Standby Mode                                    |      |

|         |          | ices                                                             |      |

| 20.10   | referen  |                                                                  |      |

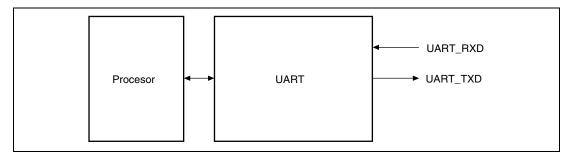

| Section | on 21    | UART                                                             | 943  |

|         |          | Description                                                      |      |

|         |          | S                                                                |      |

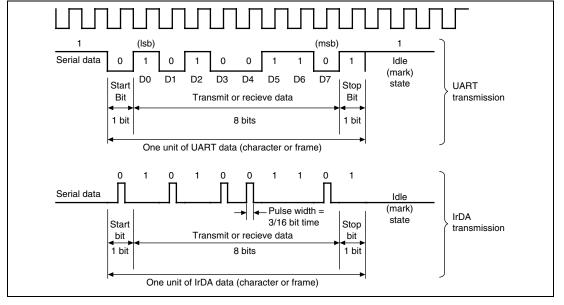

| 21.2    |          | Asynchronous Mode                                                |      |

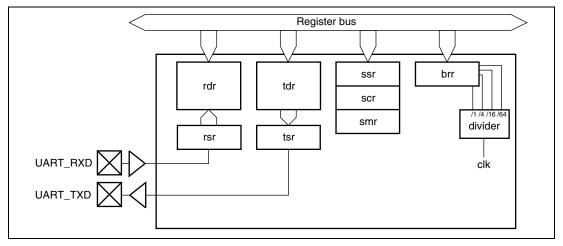

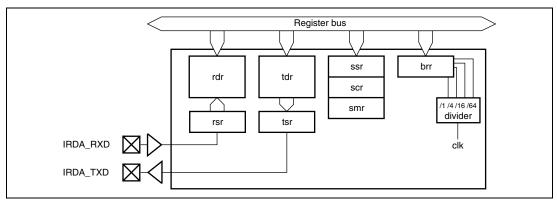

| 21.3    |          | Diagram                                                          |      |

|         |          | res                                                              |      |

| 21.4    |          | Digital Inputs/Outputs                                           |      |

|         |          | Software Interfaces                                              |      |

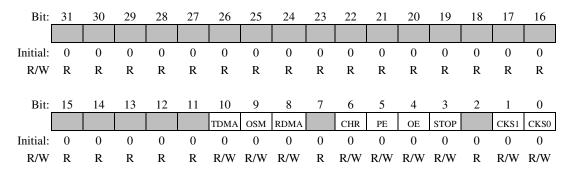

| 21.5    |          |                                                                  |      |

| 21.5    |          | nal Description  Overview                                        |      |

|         |          |                                                                  |      |

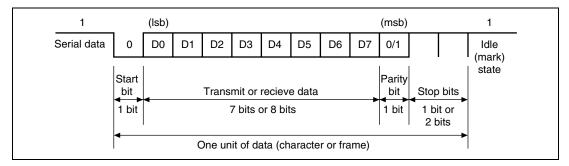

|         | 21.5.2   | Asynchronous Mode                                                | .939 |

| Rev. 1  | .0, 09/0 | 2, page xxii of xliv                                             |      |

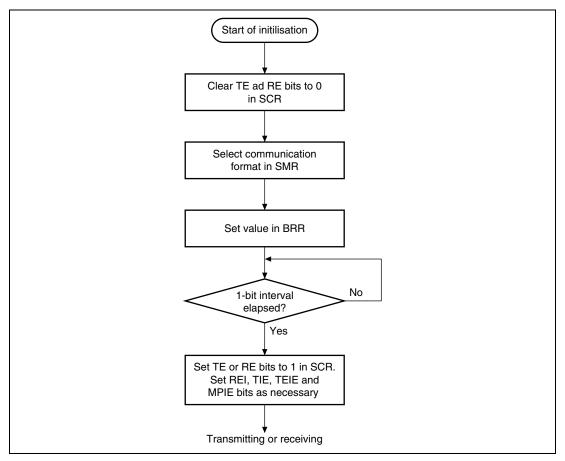

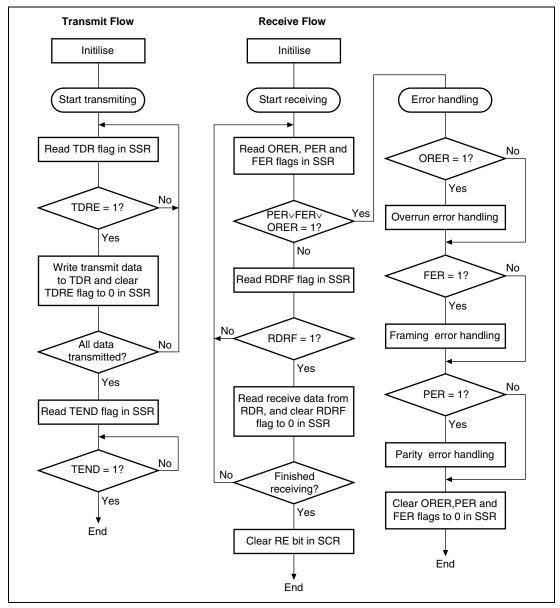

|      | 21.5.3   | Operation                                   | 960                        |

|------|----------|---------------------------------------------|----------------------------|

|      | 21.5.4   | Transmitting and Receiving Data             | 961                        |

|      | 21.5.5   | Reset Strategy                              | 966                        |

|      | 21.5.6   | Standby mode                                | 967                        |

| Sect | ion 22   | IrDA                                        | 969                        |

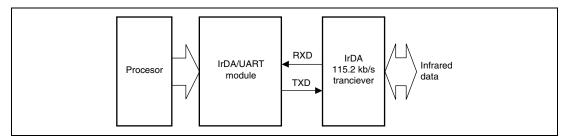

| 22.1 | Genera   | l Description                               | 969                        |

| 22.2 | Feature  | es                                          | 969                        |

| 22.3 | Block l  | Diagram                                     | 969                        |

| 22.4 | Interfac | ces                                         | 970                        |

|      | 22.4.1   | Digital Inputs/Outputs                      | 970                        |

|      |          | Software Interfaces                         |                            |

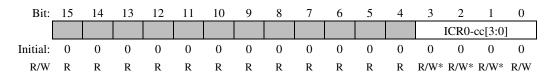

|      | 22.4.3   | IrDA Control Register 0 (ICR0)              | 971                        |

| 22.5 | Function | onal Description                            | 972                        |

|      | 22.5.1   | Overview                                    | 972                        |

|      | 22.5.2   | IrDA Mode Register Settings                 | 972                        |

|      | 22.5.3   | BRR Setting                                 | 973                        |

|      |          | Reset Strategy                              |                            |

|      | 22.5.5   | Standby mode                                | 977                        |

| Sect | ion 23   | USB Function                                | 979                        |

| 23.1 |          | es                                          |                            |

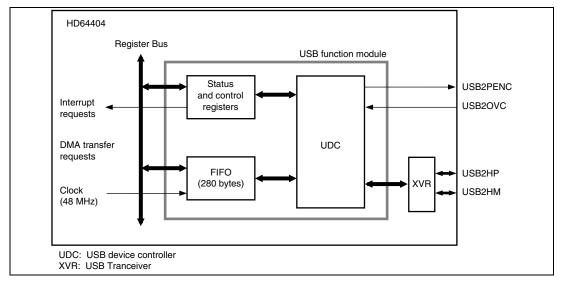

| 23.2 |          | Diagram                                     |                            |

| 23.3 |          | scription                                   |                            |

| 23.4 |          | er Configuration                            |                            |

| 23.5 | _        | er Descriptions                             |                            |

|      | _        | EP0i Data Register (USBEPDR0I)              |                            |

|      |          | EP0o Data Register (USBEPDR0O)              |                            |

|      |          | EP0s Data Register (USBEPDR0S)              |                            |

|      |          | EP1 Data Register (USBEPDR1)                |                            |

|      |          | EP2 Data Register (USBEPDR2)                |                            |

|      |          | EP3 Data Register (USBEPDR3)                |                            |

|      | 23.5.7   | Interrupt Flag Register 0 (USBIFR0)         | 988                        |

|      | 23.5.8   | Interrupt Flag Register 1 (USBIFR1)         | 990                        |

|      | 23.5.9   | Trigger Register (USBTRG)                   | 991                        |

|      |          | ) FIFO Clear Register (USBFCLR)             |                            |

|      | 23.5.11  | EP0o Receive Data Size Register (USBEPSZ0O) | 993                        |

|      |          | 2 Data Status Register (USBDASTS)           |                            |

|      |          | B Endpoint Stall Register (USBEPSTL)        |                            |

|      |          | Interrupt Enable Register 0 (USBIER0)       |                            |

|      |          | 5 Interrupt Enable Register 1 (USBIER1)     |                            |

|      |          | 6 EP1 Receive Data Size Register (USBEPSZ1) |                            |

|      |          | DMA Setting Register (USBDMAR)              |                            |

|      |          |                                             | , 09/02, page xxiii of xli |

| 23.6  | Operation                                                     | 1001 |

|-------|---------------------------------------------------------------|------|

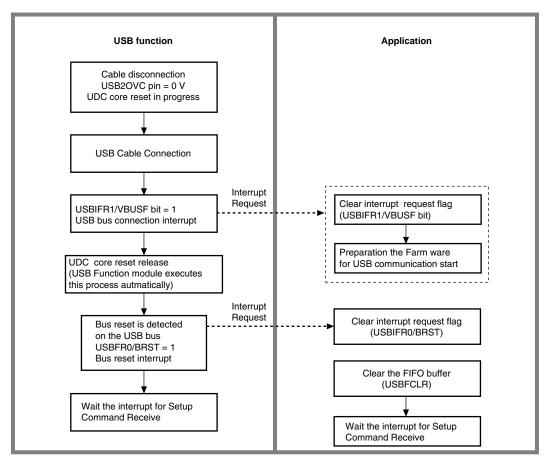

|       | 23.6.1 Cable Connection                                       |      |

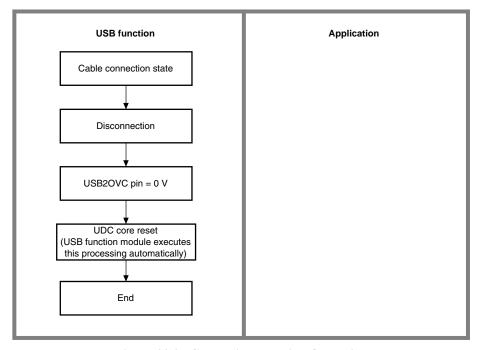

|       | 23.6.2 Cable Disconnection                                    |      |

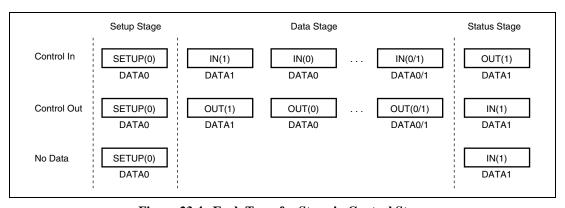

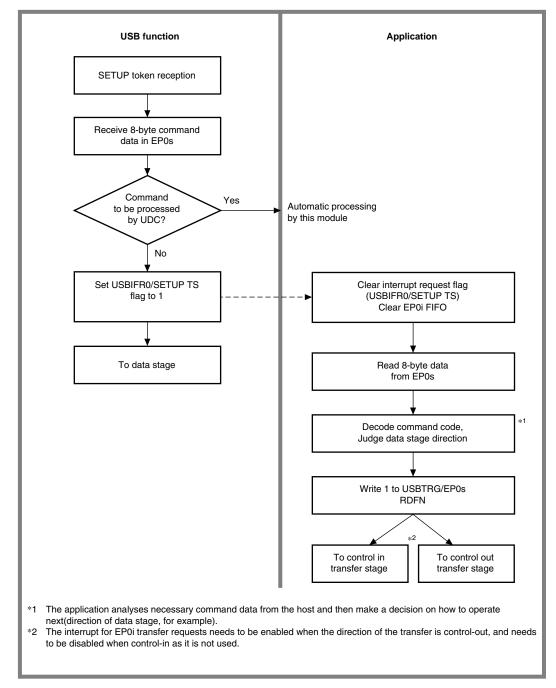

|       | 23.6.3 Control Transfer                                       |      |

|       | 23.6.4 Setup Stage                                            |      |

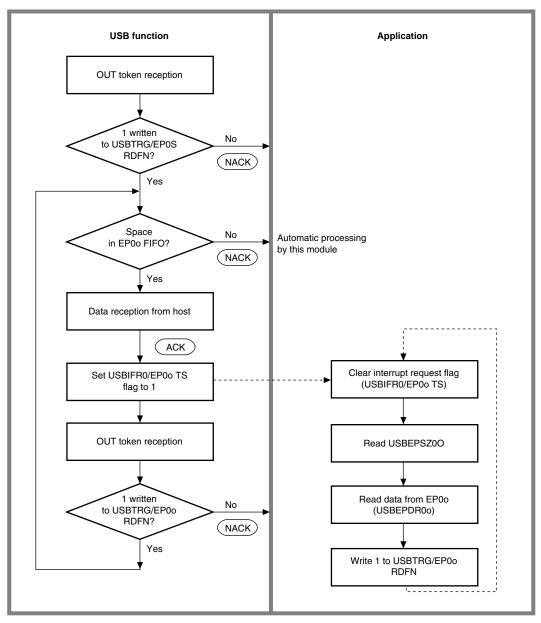

|       | 23.6.5 Data Stage (Control-Out Transfer)                      |      |

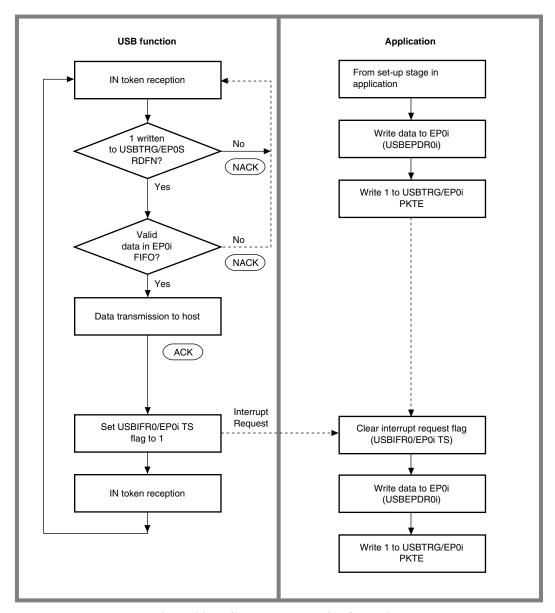

|       | 23.6.6 Data Stage (Control-In Transfer)                       |      |

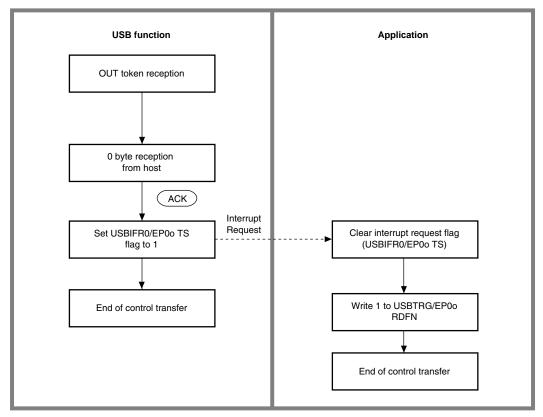

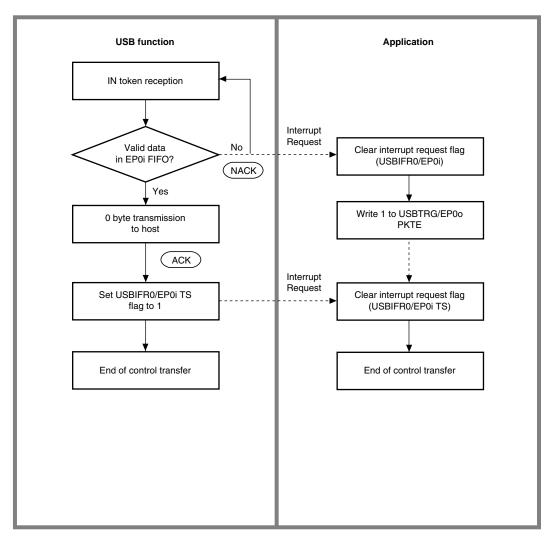

|       | 23.6.7 Status Stage(Control-In Transfer)                      |      |

|       | 23.6.8 Status Stage (Control-Out Transfer)                    |      |

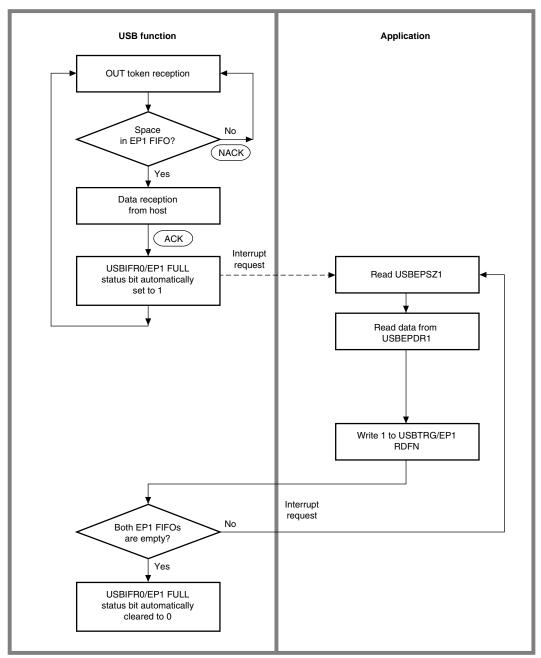

|       | 23.6.9 EP1 Bulk-Out Transfer (Dual FIFOs)                     |      |

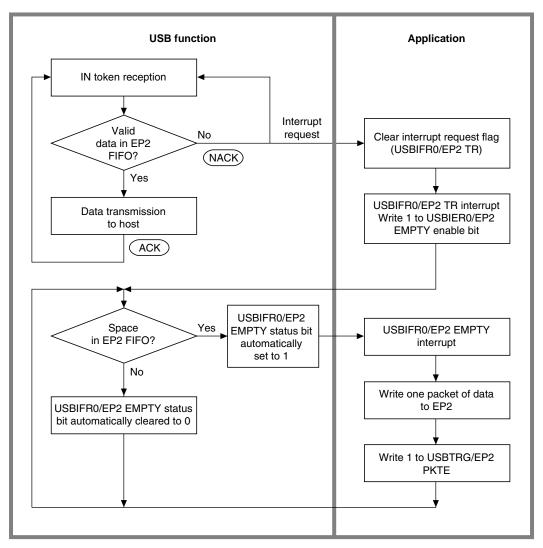

|       | 23.6.10 EP2 Bulk-In Transfer (Dual FIFOs)                     |      |

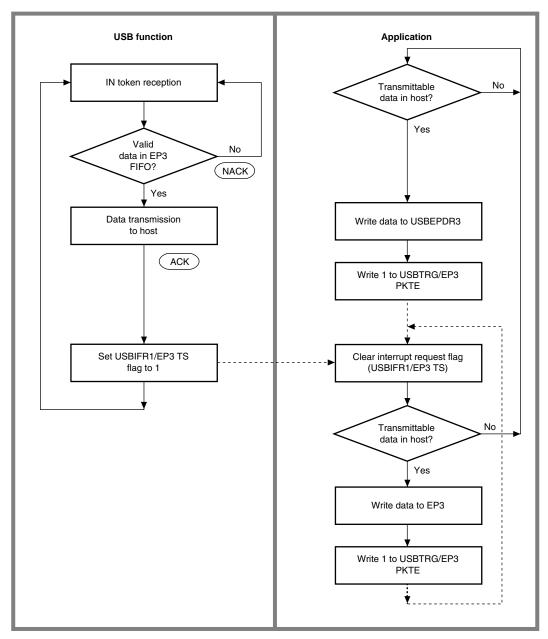

|       | 23.6.11 EP3 Interrupt-In Transfer                             |      |

| 23.7  | Processing of USB Standard Commands and Class/Vendor Commands |      |

|       | 23.7.1 Processing of Commands Transmitted by Control Transfer |      |

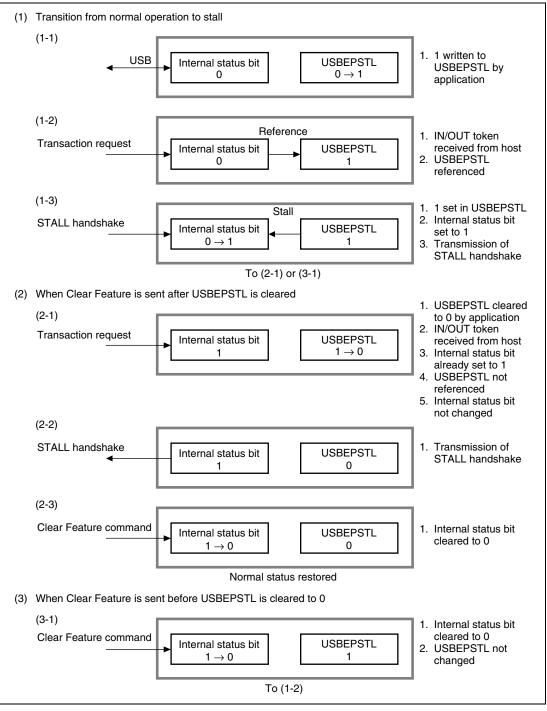

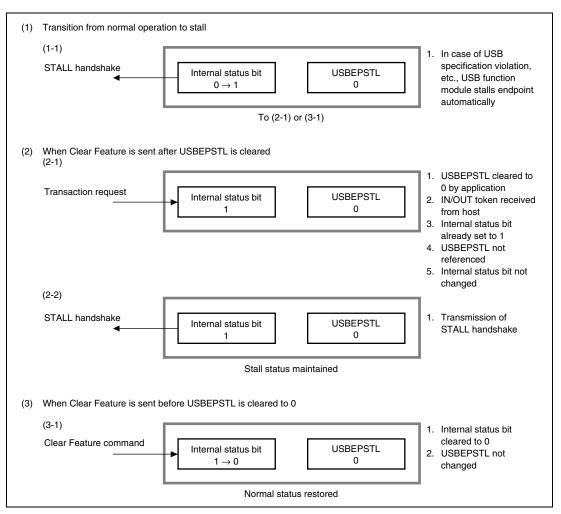

| 23.8  | Stall Operations.                                             |      |

|       | 23.8.1 Overview                                               |      |

|       | 23.8.2 Forcible Stall by Application                          | 1014 |

|       | 23.8.3 Automatic Stall by USB Function Module                 |      |

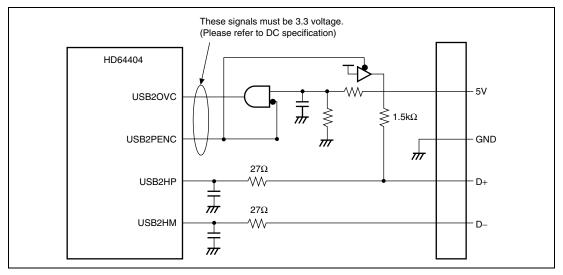

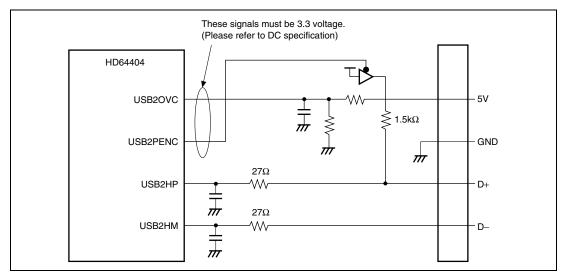

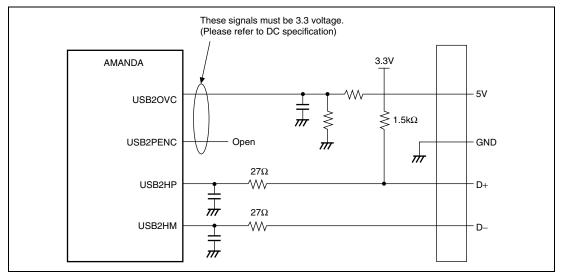

| 23.9  | Connection example of an external circuit                     |      |

|       | 23.9.1 Example 1 (When Using USB2PENC)                        |      |

|       | 23.9.2 Example 2 (When Using USB2PENC)                        |      |

|       | 23.9.3 Example 3 (When Not Using USB2PENC)                    |      |

| 23.10 | Module Standby Mode                                           |      |

|       |                                                               |      |

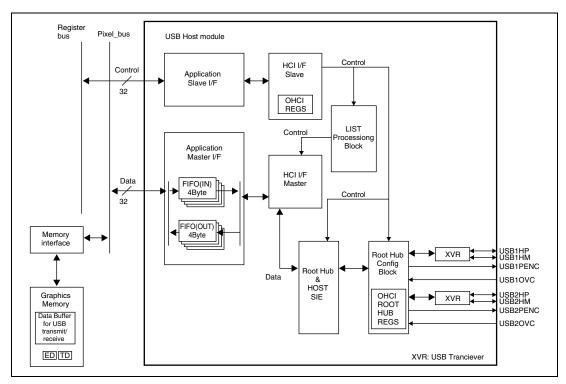

| Secti | ion 24 USB HOST                                               | 1021 |

| 24.1  | General Description                                           | 1021 |

| 24.2  | Features                                                      | 1021 |

| 24.3  | Block Diagram                                                 | 1022 |

| 24.4  | Register Description                                          | 1023 |

|       | 24.4.1 OpenHCI Registers                                      |      |

| 24.5  | Functional Description                                        | 1050 |

|       | 24.5.1 General Functionality                                  | 1050 |

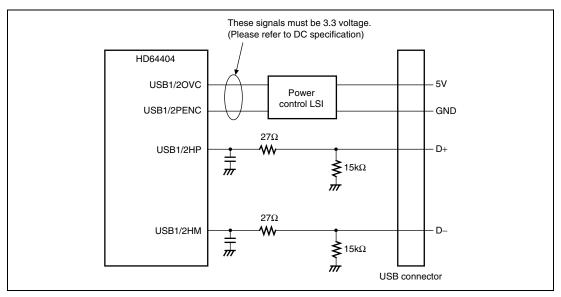

| 24.6  | Connection Example of an External Circuit                     | 1052 |

| C4    | 25 Intermed Insert                                            | 1052 |

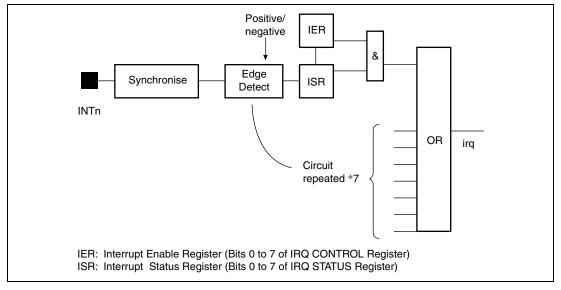

|       | ion 25 Interrupt Input                                        |      |

| 25.1  | General Description                                           |      |

| 25.2  | Features                                                      |      |

| 25.3  | Interface                                                     |      |

| 25.4  | Block Diagram                                                 |      |

| 25.5  | Register Description                                          |      |

|       | 25.5.1 IRQ Status Register                                    |      |

| 27.   | 25.5.2 IRQ Control                                            |      |

| 25.6  | Functional Description                                        | 1057 |

| Rev.  | 1.0, 09/02, page xxiv of xliv                                 |      |

|       | 25.6.1  | General Functionality                                          | 1057          |

|-------|---------|----------------------------------------------------------------|---------------|

|       | 25.6.2  | Register Bus                                                   | 1057          |

|       | 25.6.3  | Standby mode                                                   | 1058          |

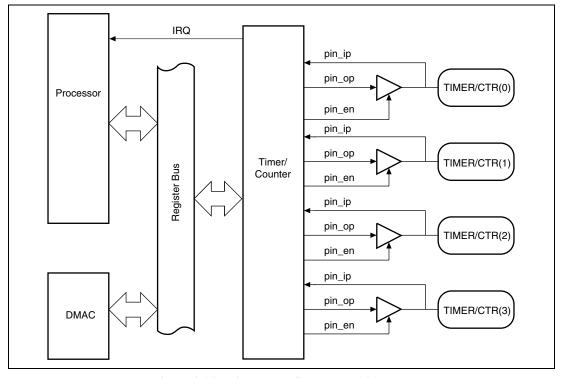

| Secti | ion 26  | Timer/Counter                                                  | 1059          |

| 26.1  |         | l Description                                                  |               |

| 26.2  |         | 28                                                             |               |

| 26.3  |         | Counter Interface                                              |               |

| 26.4  | Addres  | s Map                                                          | 1060          |

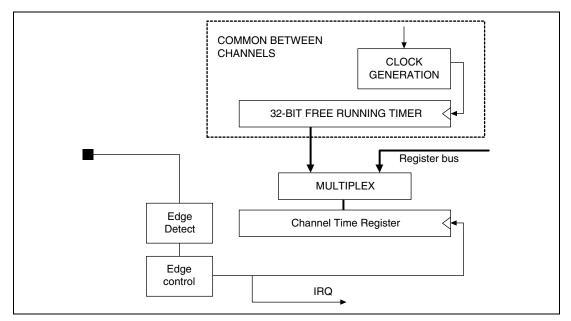

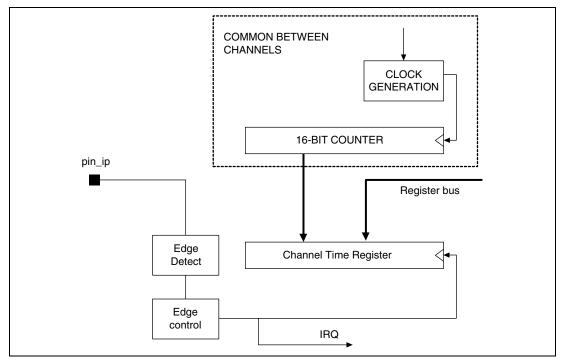

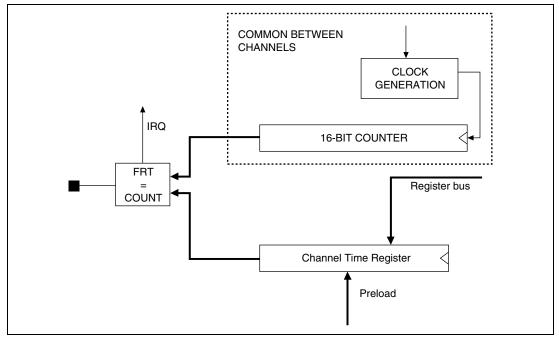

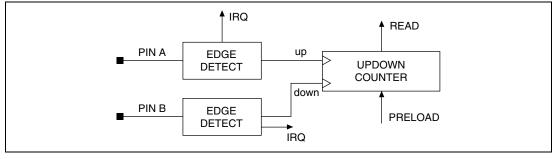

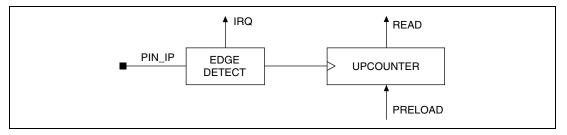

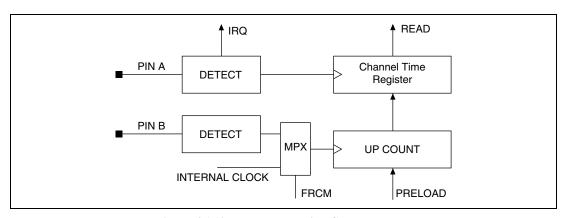

| 26.5  | Block   | Diagram                                                        | 106           |

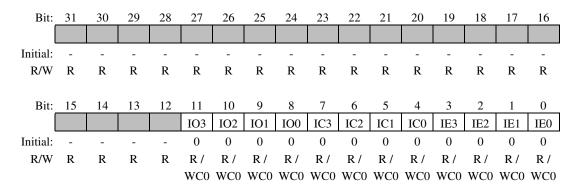

| 26.6  | Registe | er Description                                                 | 1061          |

|       | 26.6.1  | Config Register                                                | 1062          |

|       | 26.6.2  | Free Running Timer                                             | 1066          |

|       | 26.6.3  | Control Register                                               | 1066          |

|       | 26.6.4  | IRQ Status Register                                            | 1069          |

|       | 26.6.5  | Channel 0 Time, Channel 1 Time, Channel 2 Time,                |               |

|       |         | Channel 3 Time Registers                                       | 1070          |

|       | 26.6.6  | Channel 0 Stop Time, Channel 1 Stop Time, Channel 2 Stop Time, |               |

|       |         | Channel 3 Stop Time Registers                                  | 107           |

|       | 26.6.7  | , , , , , , , , , ,                                            |               |

|       |         | Channel 3 Counter                                              | 1072          |

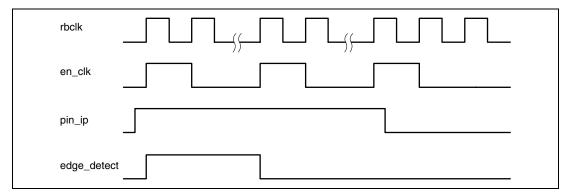

| 26.7  |         | onal Description                                               |               |

|       |         | General Functionality                                          |               |

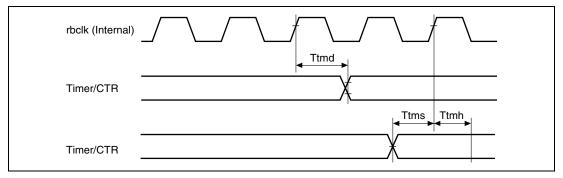

|       | 26.7.2  | Edge Detection                                                 |               |

|       | 26.7.3  | r                                                              |               |

|       | 26.7.4  | · · · · · · · · · · · · · · · · ·                              |               |

|       | 26.7.5  | <u></u>                                                        |               |

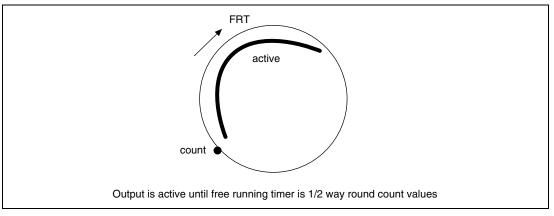

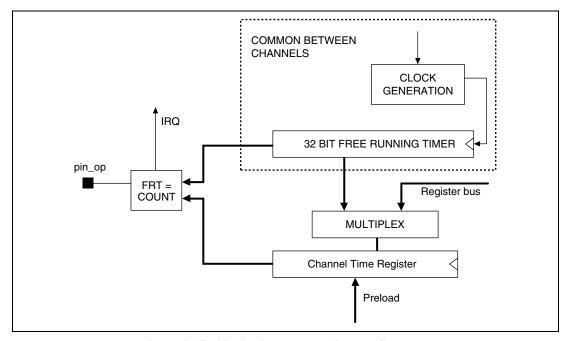

|       |         | Timer 16 bit: Output Compare                                   |               |

|       |         | Counter: Up/Updown Counter                                     |               |

|       |         | Counter: Upcounter with Capture                                |               |

|       |         | Interrupts                                                     |               |

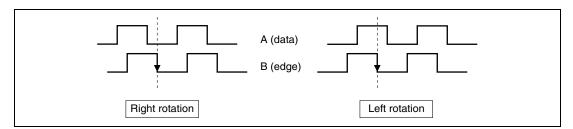

|       |         | Rotary mode                                                    |               |

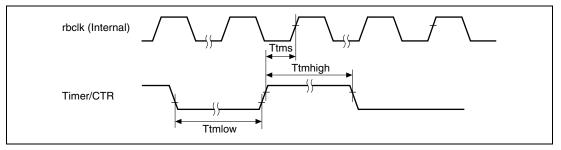

|       |         | Timer Frequency                                                |               |

|       |         | 2 Power Saving                                                 |               |

|       |         | S Standby Mode                                                 |               |

|       | 26.7.14 | Register Bus                                                   | 1080          |

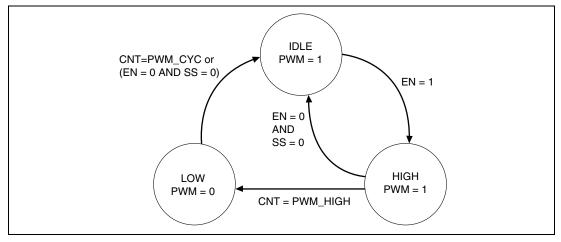

| Secti |         | Pulse Width Modulation                                         |               |

| 27.1  |         | l Description                                                  |               |

| 27.2  |         | 28                                                             |               |

| 27.3  |         | ce                                                             |               |

| 27.4  |         | s Map                                                          |               |

| 27.5  | Registe | er Description                                                 | 1082          |

|       |         | Rev. 1.0, 09/02, pag                                           | ne xxv of xli |

|      | 27.5.1    | DURACO LA LIDA CA            | 1000  |

|------|-----------|------------------------------|-------|

|      |           | PWM Control Register         |       |

|      |           | PWM01 Counts Register        |       |

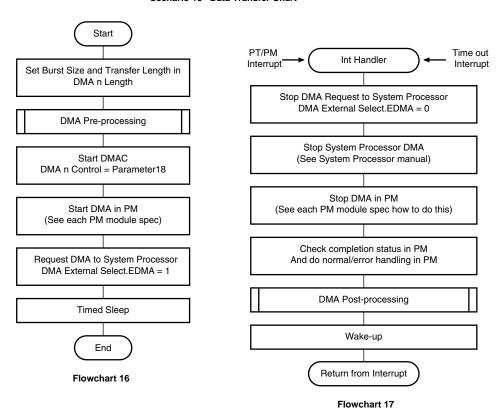

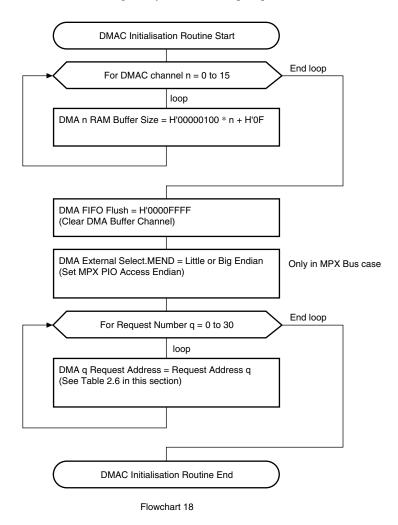

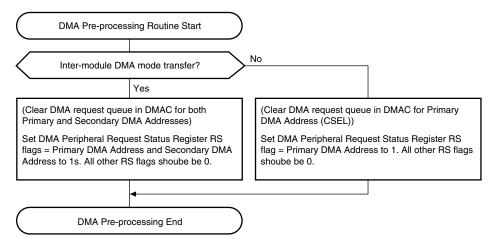

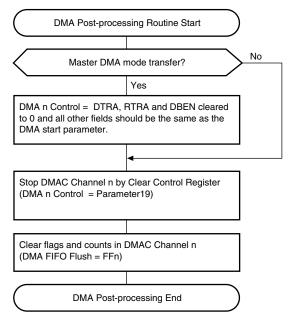

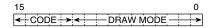

|      |           | PWM23 Counts Register        |       |