The revision list can be viewed directly by clicking the title page. The revision list summarizes the locations of revisions and additions. Details should always be checked by referring to the relevant text.

16

# H8S/2194 Group, H8S/2194C Group, H8S/2194F-ZTAT™, H8S/2194C F-ZTAT™ Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8S Family/H8S/2100 Series

| H8S/2194  | HD6432194  |

|-----------|------------|

|           | HD64F2194  |

| H8S/2193  | HD6432193  |

| H8S/2192  | HD6432192  |

| H8S/2191  | HD6432191  |

| H8S/2194C | HD6432194C |

|           | HD64F2194C |

| H8S/2194B | HD6432194B |

| H8S/2194A | HD6432194A |

|           |            |

Hardware Manua

Rev.3.00

Revision Date: Jan. 10, 2007

Renesas Technology www.renesas.com

#### Notes regarding these materials

- 1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- 2. Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below:

- (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

- Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

### **General Precautions in the Handling of MPU/MCU Products**

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions may occur due to the false recognition of the pin state as an input signal. Unused pins should be handled as described under Handling of Unused Pins in the manual.

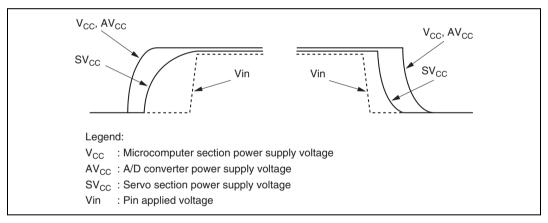

#### 2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

- In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

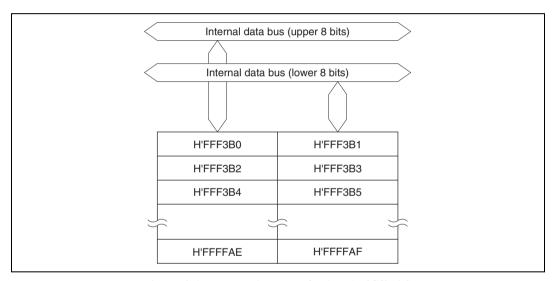

#### 3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

The reserved addresses are provided for the possible future expansion of functions. Do not access these addresses; the correct operation of LSI is not guaranteed if they are accessed.

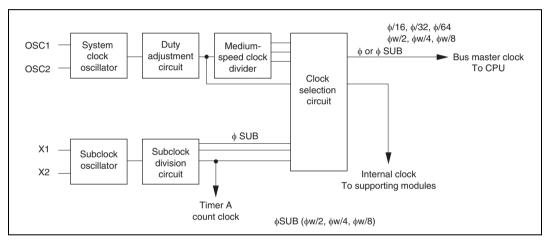

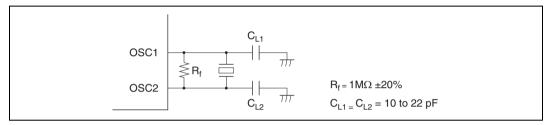

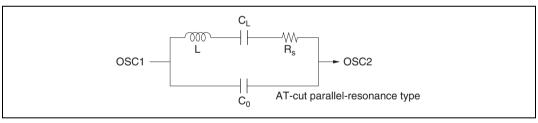

#### 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

# Main Revisions for This Edition

| Item                                | Page | Revision (See Manual for Details)                                                    |

|-------------------------------------|------|--------------------------------------------------------------------------------------|

| All www.DataSheet4U                 | com  | Notification of change in company name amended                                       |

|                                     |      | (Before) Hitachi, Ltd. $\rightarrow$ (After) Renesas Technology Corp.                |

|                                     |      | Product naming convention amended                                                    |

|                                     |      | (Before) H8S/2194 Series → (After) H8S/2194 Group                                    |

|                                     |      | (Before) H8S/2194C Series $\rightarrow$ (After) H8S/2194C Group                      |

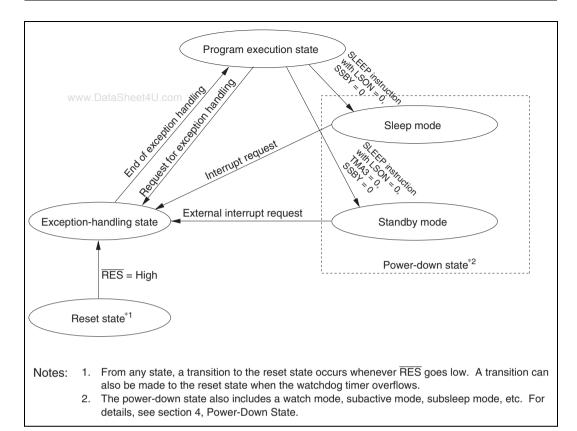

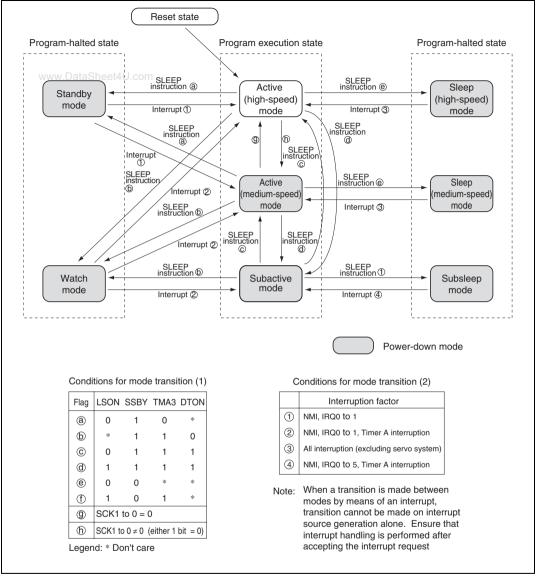

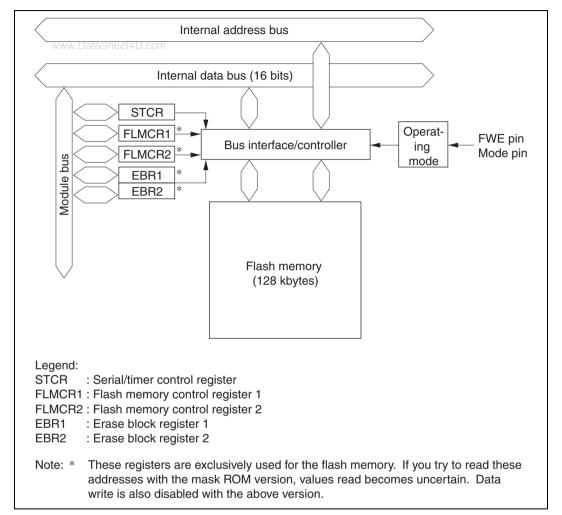

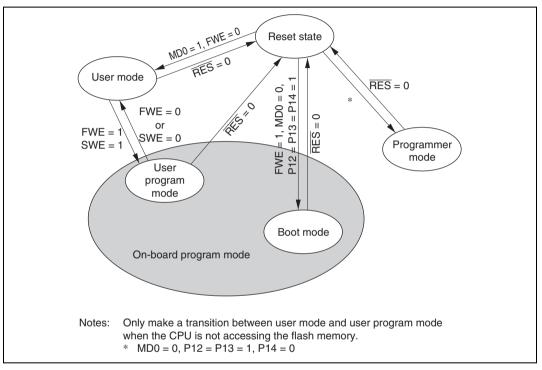

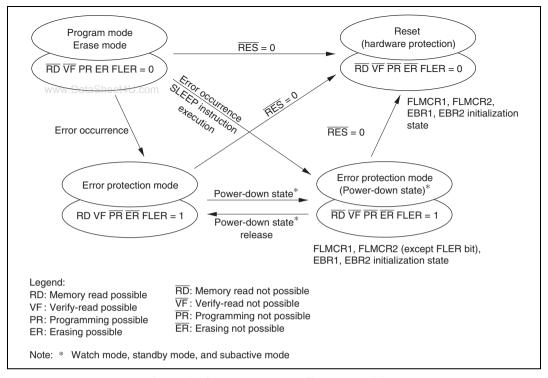

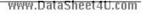

| 2.8.1 Overview                      | 54   | Figure 2.15 amended                                                                  |

| Figure 2.15 State                   |      | RES = High                                                                           |

| Transitions                         |      | SLEEP instruction with LSON = 0, TMA3 = 0, SSBY = 0                                  |

| 4.2.3 Timer Register                | 79   | Table amended                                                                        |

| A (TMA)                             |      | <ul> <li>Timer A counts φ-based prescalar (PSS) divided clock pulses</li> </ul>      |

|                                     |      | <ul> <li>Timer A counts φw-based prescalar (PSW) divided clock<br/>pulses</li> </ul> |

| 4.6.1 Standby Mode                  | 83   | Description amended                                                                  |

|                                     |      | RAM as well as functions of the SCI1, timer X1                                       |

| 4.6.2 Clearing                      | 83   | (1) Clearing with an Interrupt                                                       |

| Standby Mode                        |      | in bits STS2 to STS0 in SBYCR, stable clocks are supplied                            |

|                                     |      |                                                                                      |

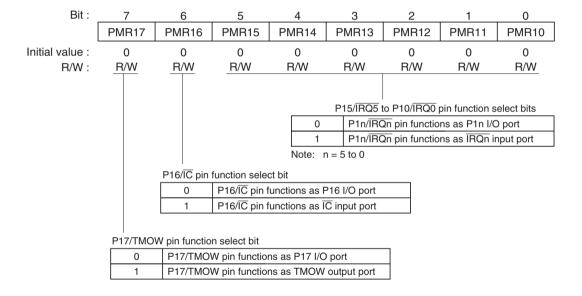

| 6.2.6 Port Mode<br>Register (PMR1)  | 106  | Table amended                                                                        |

| -                                   |      | P1n/IRQn pin functions as the IRQn input pin                                         |

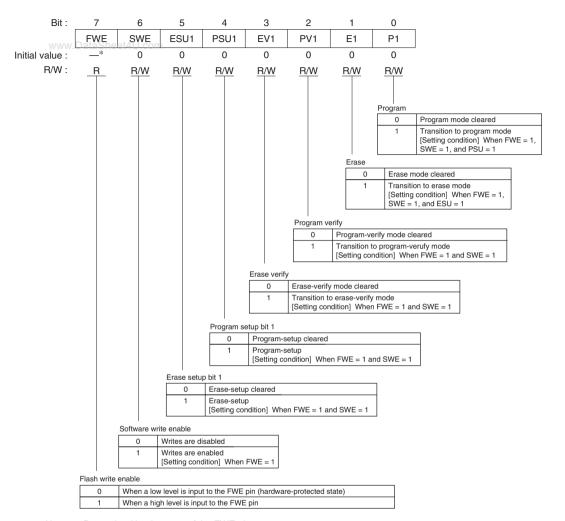

| 7.2.5 Register Configuration        | 132  | Access size description deleted from table 7.3                                       |

| Table 7.3 Flash<br>Memory Registers |      |                                                                                      |

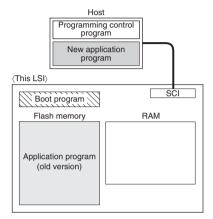

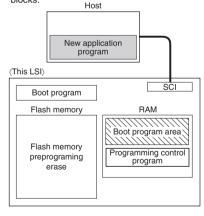

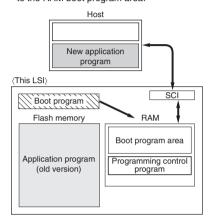

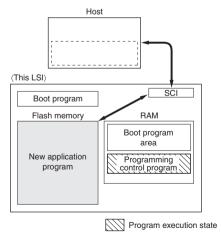

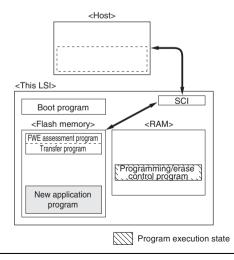

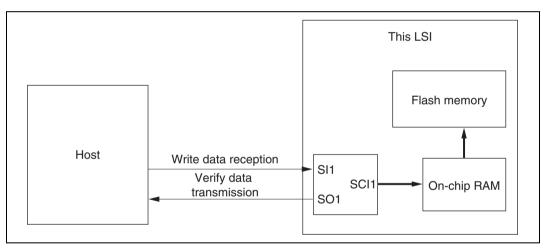

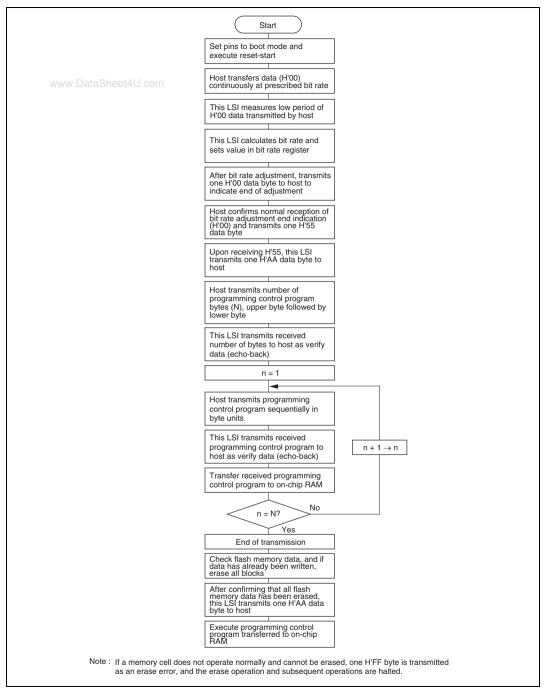

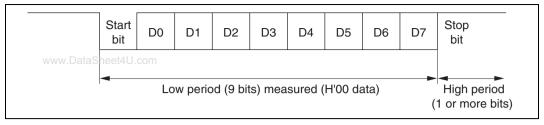

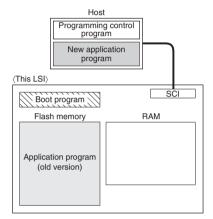

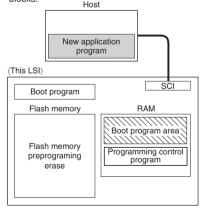

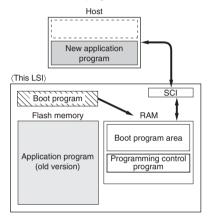

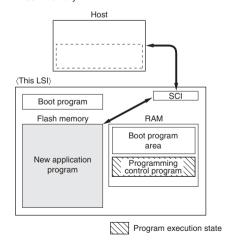

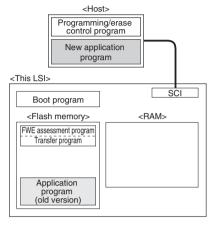

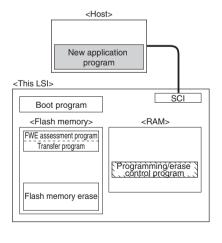

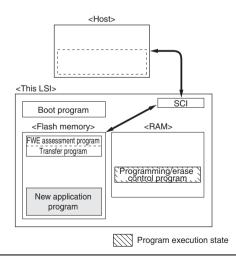

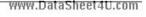

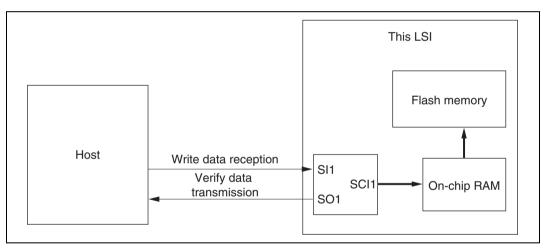

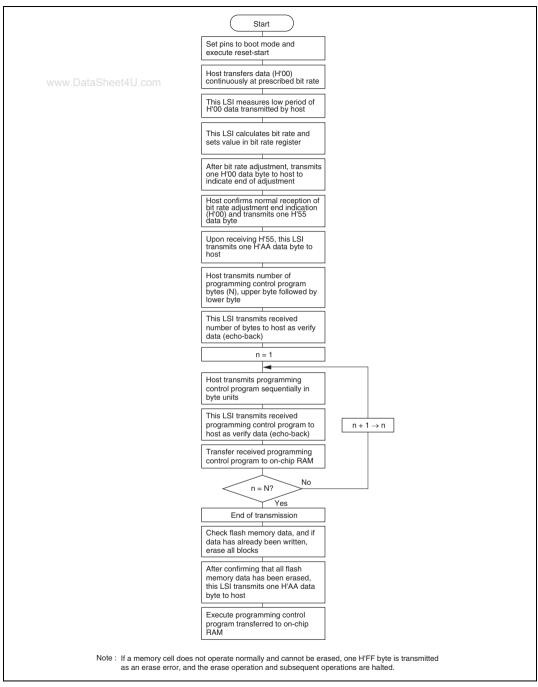

| 7.4.1 Boot Mode                     | 143  | (1) Automatic SCI Bit Rate Adjustment                                                |

|                                     |      | Description amended                                                                  |

|                                     |      | bit rate should be set to (4800, or 9600) bps                                        |

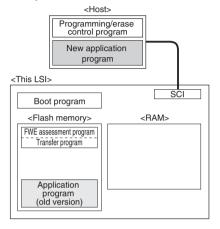

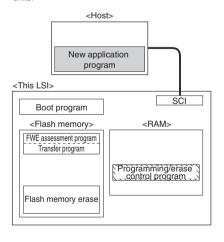

| 8.4.1 Boot Mode                     | 191  | (1) Automatic SCI Bit Rate Adjustment                                                |

|                                     |      | Description amended                                                                  |

|                                     |      | bit rate should be set to (4800, or 9600) bps                                        |

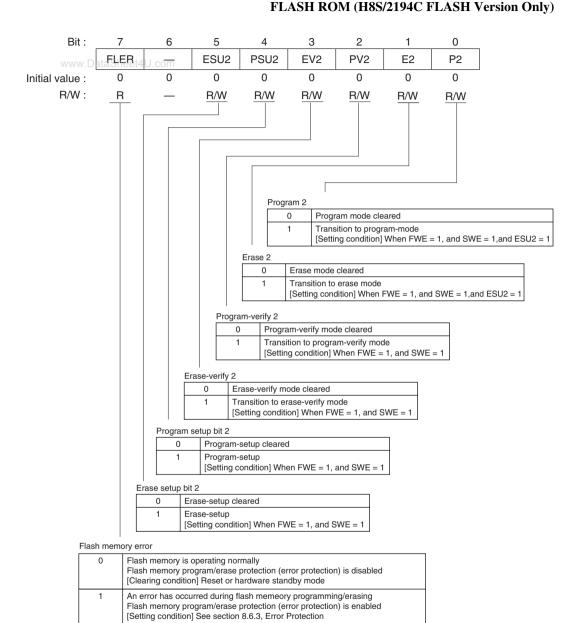

| 8.5                                 | 195  | Description amended                                                                  |

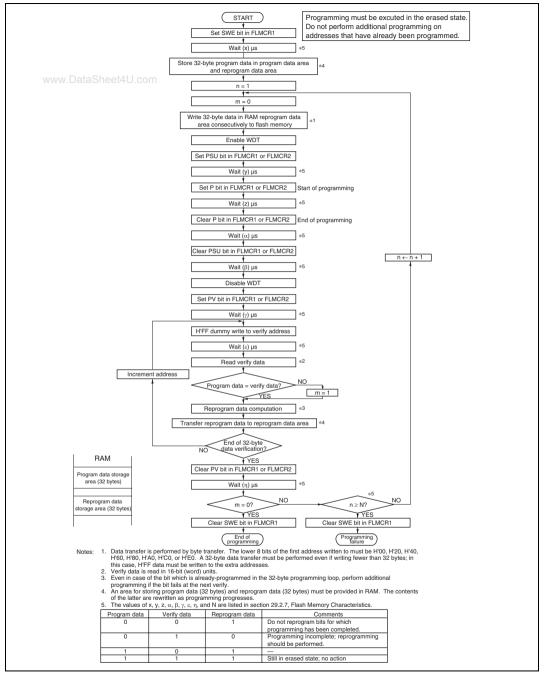

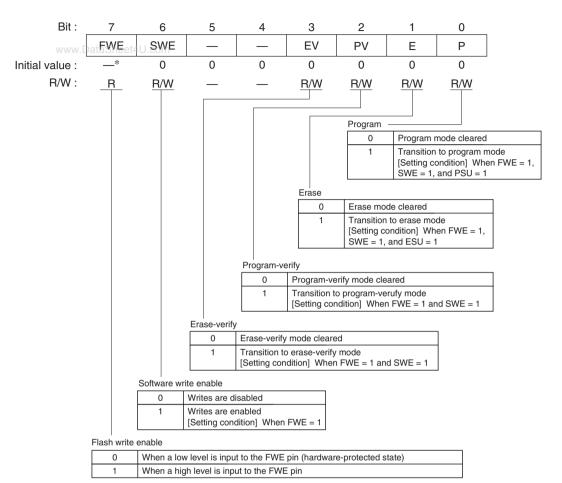

| Programming/Erasing Flash Memory    |      | PSU2, ESU2, P2, E2, PV2, and EV2 bits in FLMCR2                                      |

| Item                                                                                                              | Page         | Revision (See Manual for Details)                                                                  |

|-------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------|

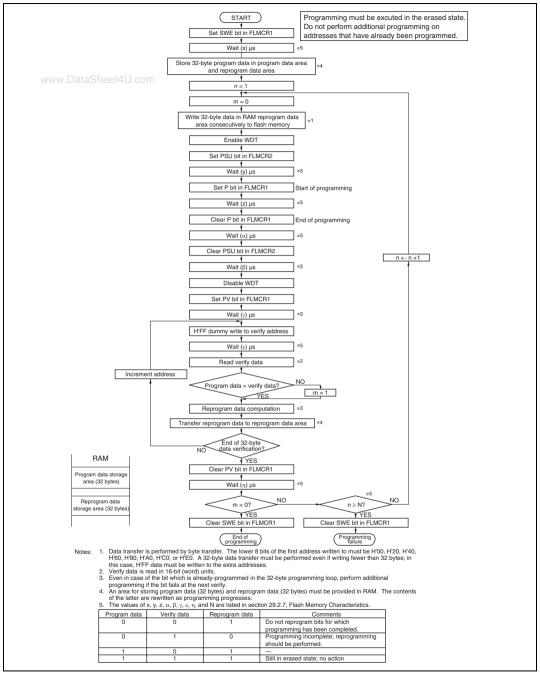

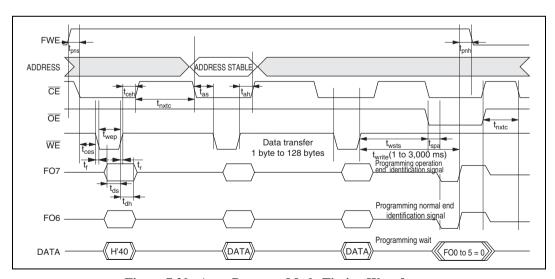

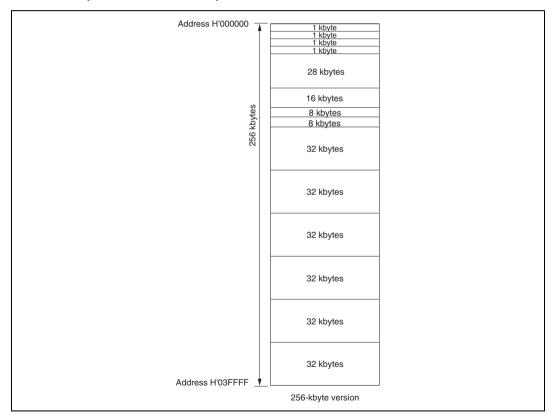

| 8.5.1 Program Mode<br>(n = 1 for addresses<br>H'00000 to H'1FFFF<br>and n= 2 for addresses<br>H'20000 to H'3FFFF) | 195<br>J.com | Section 8.5.1 title amended                                                                        |

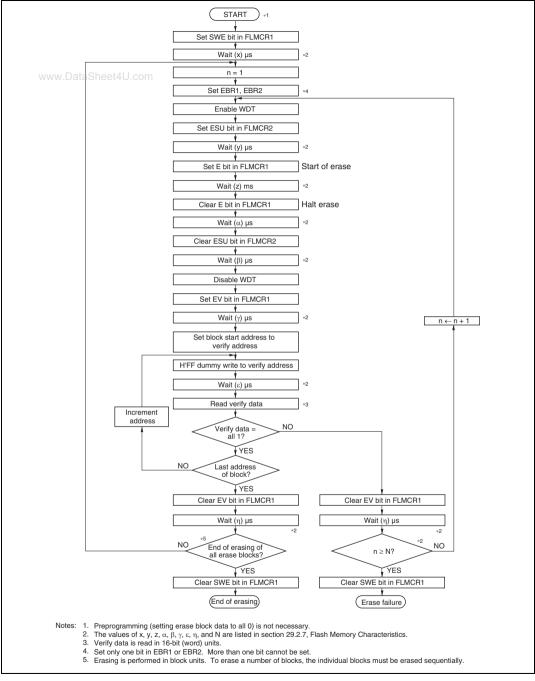

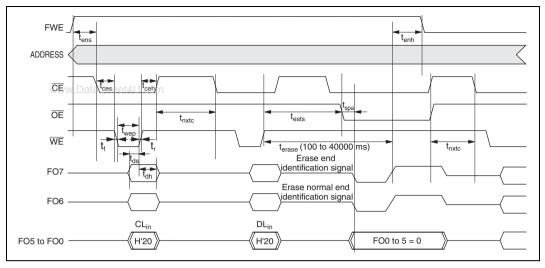

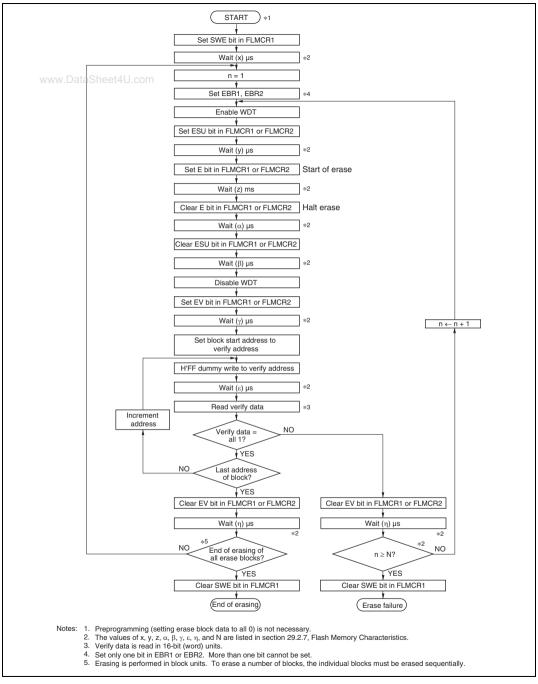

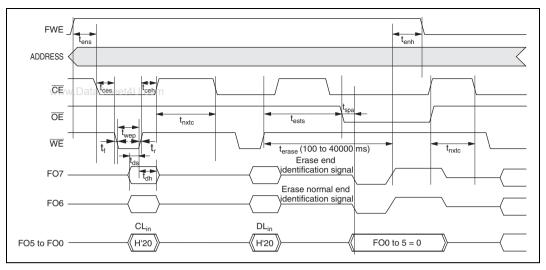

| 8.5.3 Erase Mode (n =                                                                                             | 198          | Description amended                                                                                |

| 1 for Addresses<br>H'00000 to H'1FFFF<br>and N = 2 for<br>Addresses H'20000 to<br>H'3FFFF)                        |              | is switched to erase mode by setting the En bit in FLMCRn. The time during                         |

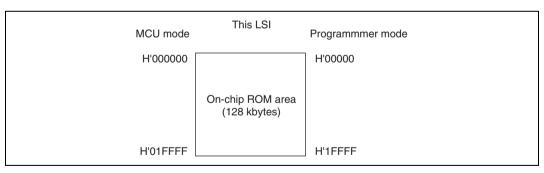

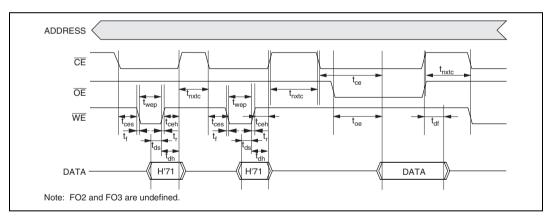

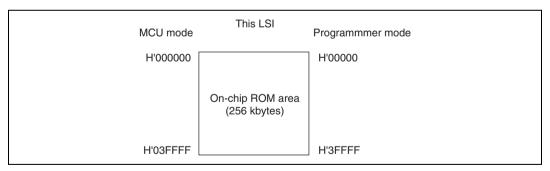

| 8.8.1 Program Mode                                                                                                | 205          | Description amended                                                                                |

| Setting                                                                                                           |              | Renesas Technology microcomputer device type with 256-kbyte on-chip flash memory                   |

| 8.8.3 Programmer                                                                                                  | 206          | Table 8.10 amended                                                                                 |

| Mode Operation                                                                                                    |              | Pin Names                                                                                          |

| Table 8.10 Settings for Each Operating                                                                            |              | Read H or L L H Data output Ain                                                                    |

| Mode in Programmer                                                                                                |              | Output disable H or L L H H Hi-Z X                                                                 |

| Mode                                                                                                              |              |                                                                                                    |

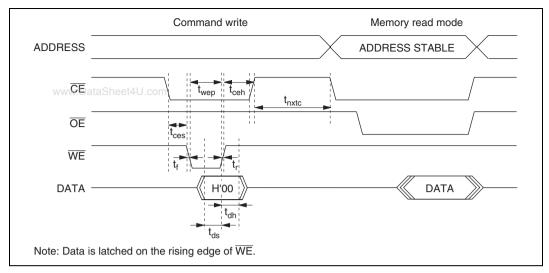

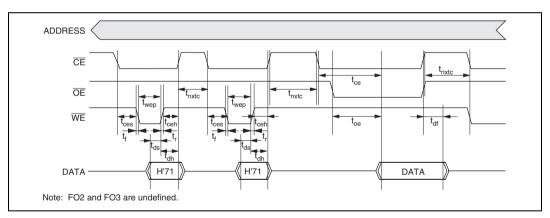

| 8.8.5 Auto-Program<br>Mode                                                                                        | 211          | Description amended (d) Do not perform transfer after the third cycle.                             |

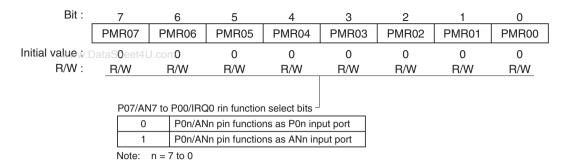

| 11.1.2 Port Input                                                                                                 | 236          | Pin description for port 0 in table 11.1 amended                                                   |

| Table 11.1 Port Functions                                                                                         |              | P07/AN7 to P00/AN0                                                                                 |

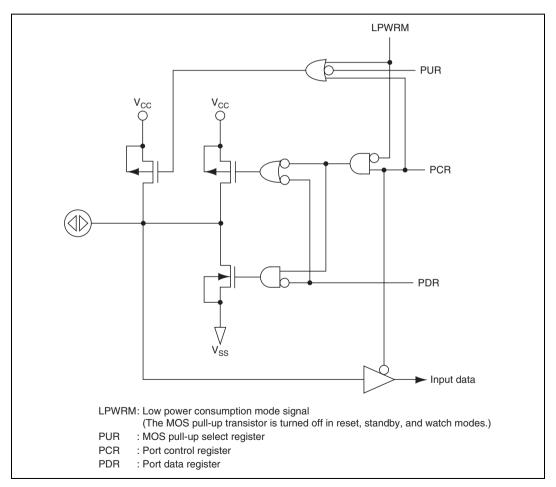

| 11.1.3 MOS Pull-Up<br>Transistors                                                                                 | 237          | Figure 11.1 amended                                                                                |

| Figure 11.1 Circuit<br>Configuration of Pin<br>with MOS Pull-Up<br>Transistor                                     |              | Input data                                                                                         |

| 11.2.4 Pin States                                                                                                 | 240          | Table 11.4 amended                                                                                 |

| Table 11.4 Port 0 Pin<br>States                                                                                   |              | P07/AN7 to P00/AN0                                                                                 |

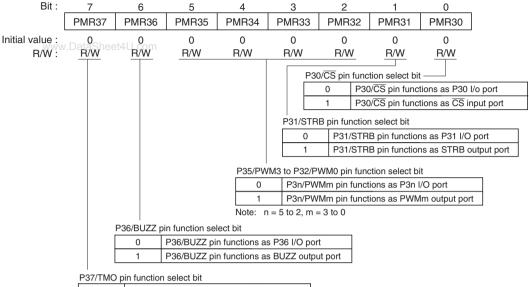

| 11.4.1 Overview                                                                                                   | 248          | (1) Port Mode Register 2 (PMR2)                                                                    |

|                                                                                                                   |              | Description amended                                                                                |

|                                                                                                                   |              | Port mode register 2 (PMR2) controls switching If the SCK1, SCK2, SI1, and SI2 input pins are set, |

| 11.10.2 Register<br>Configuration                            | 284 | (1) Port                                                  | Mode F                          |            |                |            |                                      |               |

|--------------------------------------------------------------|-----|-----------------------------------------------------------|---------------------------------|------------|----------------|------------|--------------------------------------|---------------|

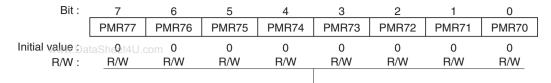

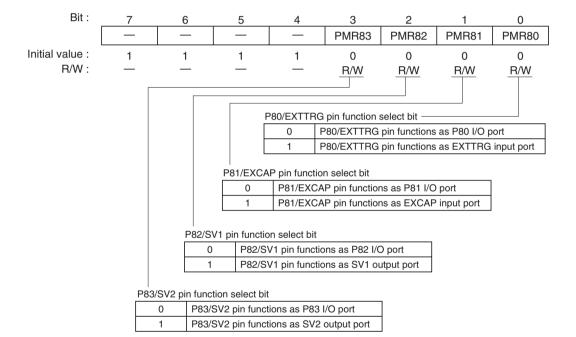

| Configuration                                                |     |                                                           | (1) Port Mode Register 8 (PMR8) |            |                |            |                                      |               |

|                                                              |     | Description amended                                       |                                 |            |                |            |                                      |               |

| www.DataSheet4U.co                                           |     | whether                                                   | the P8                          | 1/EXCA     | P pin is u     | sed as a   | 1): PMR81<br>P81 I/O p<br>hronous si |               |

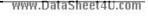

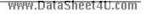

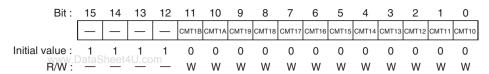

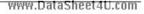

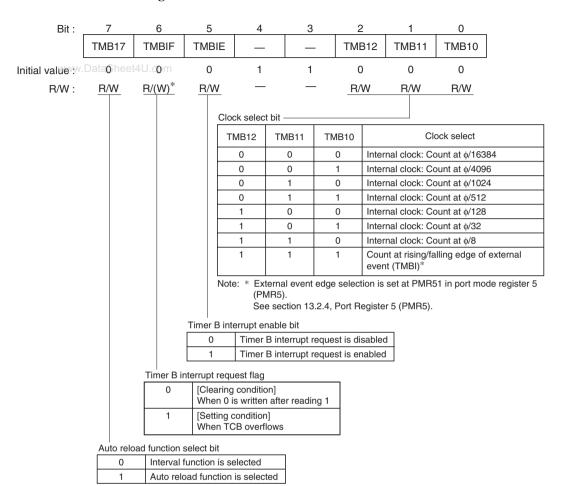

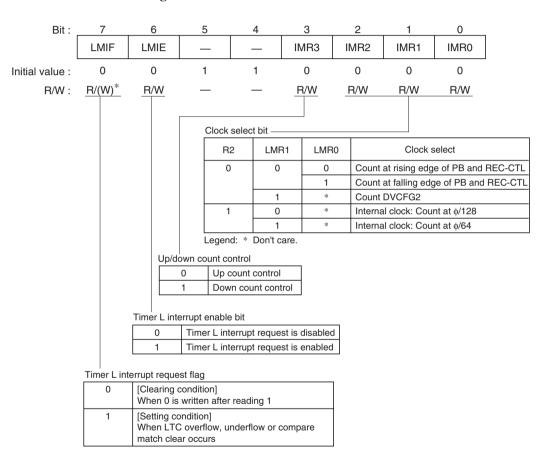

|                                                              | 324 | Bit figure                                                | e amen                          | ded        |                |            |                                      |               |

| Register (LMR)                                               |     | Bits 3 to                                                 | 0 (Befo                         | ore) IMR   | → (After       | r) LMR     |                                      |               |

| -                                                            | 325 | Bits 2 to                                                 | 0—Clo                           | ck Selec   | ction          |            |                                      |               |

|                                                              |     | Bit table                                                 | amend                           | led        |                |            |                                      |               |

|                                                              |     | (Before)                                                  | $R2 \rightarrow 0$              | (After) L  | MR2            |            |                                      |               |

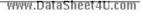

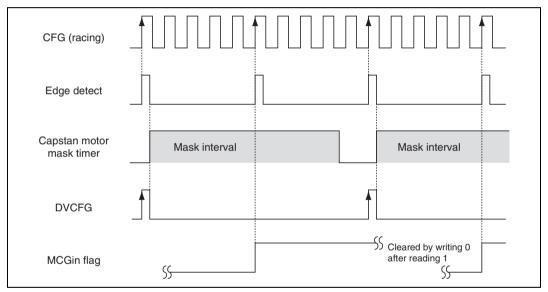

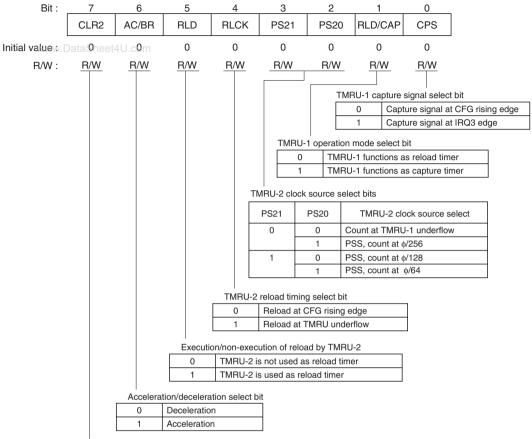

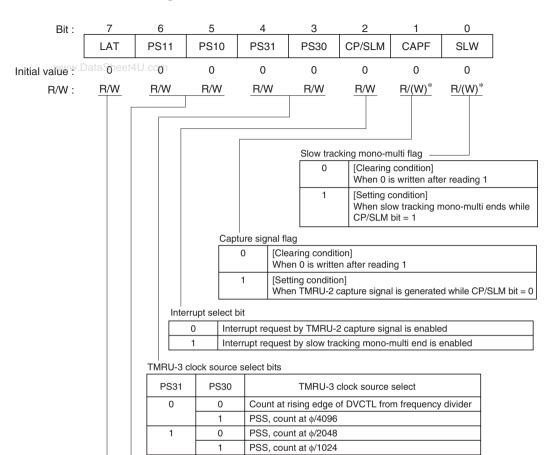

| 16.2.2 Timer R Mode                                          | 335 | Bit 7—S                                                   | election                        | of Cap     | ture Sign      | als of the | TMRU-2                               | (LAT)         |

| Register 2 (TMRM2)                                           |     | Bit table                                                 | amend                           | led        |                |            |                                      |               |

|                                                              |     | Capture                                                   | s at the                        | rising e   | dge of th      | e CFG      |                                      |               |

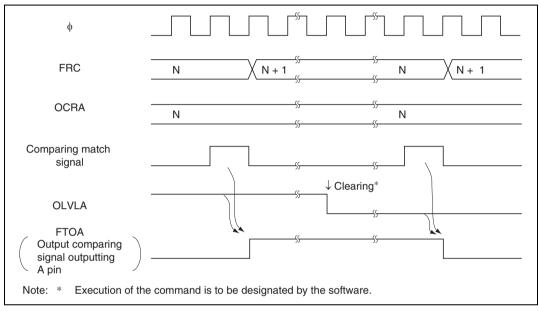

| 17.6 Exemplary Uses                                          | 379 | Descript                                                  | ion ame                         | ended      |                |            |                                      |               |

| of the Timer X1                                              |     | (2) Each time a comparing match occurs, the OLVLA bit and |                                 |            |                |            |                                      | A bit and     |

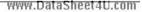

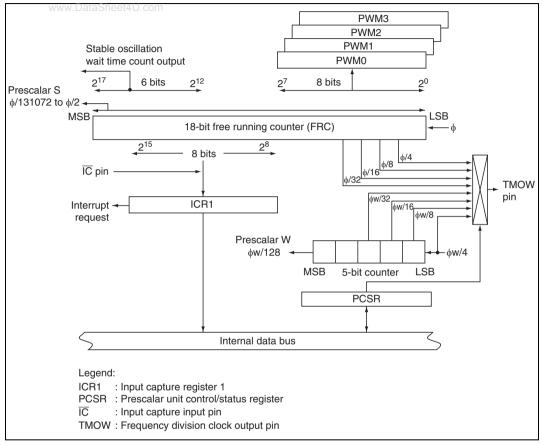

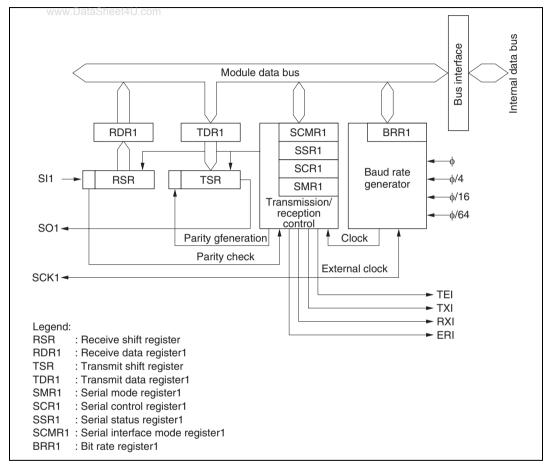

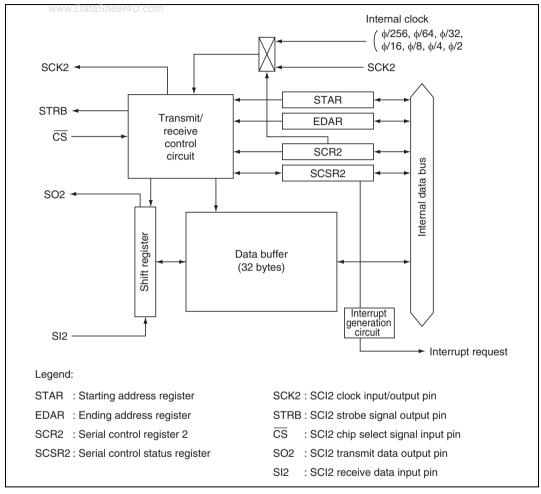

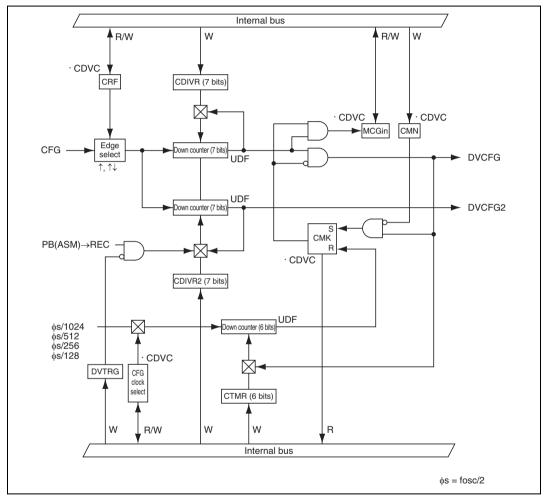

| 22.1.2 Block Diagram                                         | 424 | Figure 2                                                  | 2.1 am                          | ended      |                |            |                                      |               |

| Figure 22.1 Block<br>Diagram of Prescalar<br>Unit            |     | (Before)                                                  | $2^8 \rightarrow (R$            | After) 2º  |                |            |                                      |               |

| 23.2.5 Serial Mode                                           | 440 | Bit 4—P                                                   | arity Mo                        | ode (O/Ē   | Ē)             |            |                                      |               |

| Register (SMR1)                                              |     | Bit table amended                                         |                                 |            |                |            |                                      |               |

|                                                              |     | Odd par                                                   | ity*²                           |            |                |            |                                      |               |

| 23.2.7 Serial Status                                         | 448 | Bit 4—P                                                   | arity Er                        | ror (PEF   | R)             |            |                                      |               |

| Register (SSR1)                                              |     | Bit table amended                                         |                                 |            |                |            |                                      |               |

|                                                              |     | (Before)                                                  | Bit 4                           | (After)    | Bit 3          |            |                                      |               |

| 23.2.8 Bit Rate                                              | 452 | Table 23                                                  | 3.4 ame                         | nded       |                |            |                                      |               |

| Register (BRR1)                                              |     |                                                           | Opera                           | ting Freq  | uency φ (N     | /IHz)      |                                      |               |

| Table 23.4 BRR1 Settings for Various Bit                     |     | Bit Rate                                                  | 2                               |            | 4              |            | 8                                    |               |

| Rates (Clock                                                 |     | (bits/s)                                                  | n                               | N          | n              | N          | n                                    | N             |

| Synchronous Mode)                                            |     | 110                                                       | 3                               | 70         |                |            | 2                                    | 104           |

|                                                              |     | 250<br>500                                                | 1                               | 124<br>249 | 2              | 249<br>124 | 3                                    | 124<br>249    |

|                                                              |     |                                                           |                                 |            |                |            |                                      |               |

|                                                              | 455 | Table 23                                                  | 3.6 ame                         |            |                |            |                                      |               |

| Bit Rate with External<br>Clock Input<br>(Asynchronous Mode) |     | φ (MHz)<br>6 1.500                                        |                                 | Extern     | nal Input Cloc | k (MHz)    | Maximum Bit<br>93750                 | Rate (bits/s) |

| Item                                | Page | Revision (See Manual for Details)                                                                            |

|-------------------------------------|------|--------------------------------------------------------------------------------------------------------------|

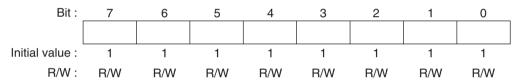

| 23.2.9 Serial Interface             | 457  | Bit 0—Serial Communication Interface Mode Select (SMIF)                                                      |

| Mode Register (SCMR1)               | )    | Bit table amended                                                                                            |

|                                     |      | Normal SCI1 mode                                                                                             |

| 23.3.4 Operation in                 | 478  | (2) Clock                                                                                                    |

| Clock Synchronous<br>Mode           |      | Description amended                                                                                          |

| Widde                               |      | For details on SCI1 clock source selection,                                                                  |

| 23.5 Usage Notes                    | 488  | (1) Relation between Writes to TDR1 and the TDRE Flag                                                        |

|                                     |      | Description amended                                                                                          |

|                                     |      | $\dots$ TDR1 to TSR. When the SCI1 transfers data from TDR1 to TSR, $\dots$                                  |

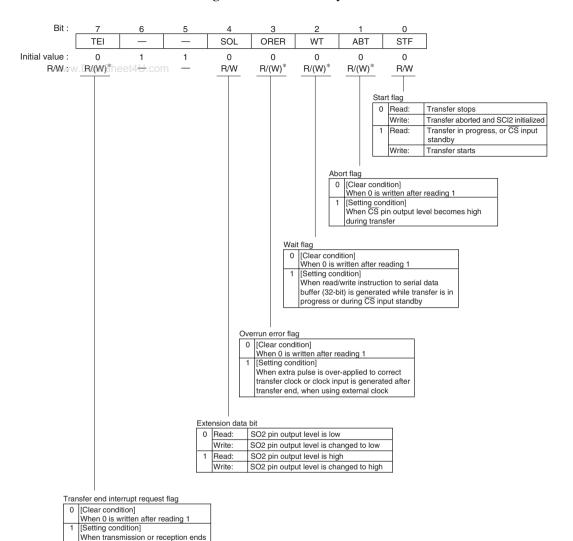

| 24.2.4 Serial Control               | 499  | Bit 1—Abort Flag (ABT)                                                                                       |

| Status Register 2 (SCSR2)           |      | Description amended                                                                                          |

| (303112)                            |      | $\dots$ while this bit is set to 1. Resume transfer after clearing to 0.                                     |

|                                     |      | Bit 0—Start Flag (STF)                                                                                       |

|                                     |      | Description amended                                                                                          |

|                                     |      | other than the SCSR2 and serial data buffer (32 bytes) are retained.                                         |

| 24.3.3 Data Transfer                | 504  | (1) SCI2 Initialization                                                                                      |

| Operations                          |      | Description amended                                                                                          |

|                                     |      | (2) The SCI2 pin is also used as a port. Switching of a port is performed on PMR3.                           |

|                                     | 505  | Description amended                                                                                          |

|                                     |      | While PMR30 of PMR3 is set to 1, transmission is                                                             |

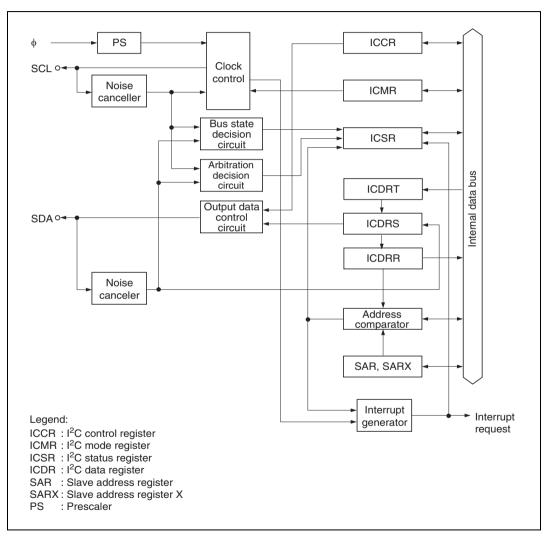

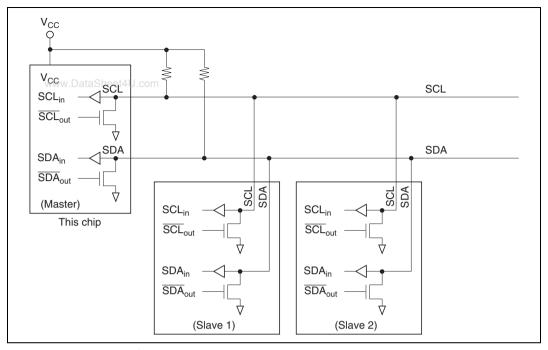

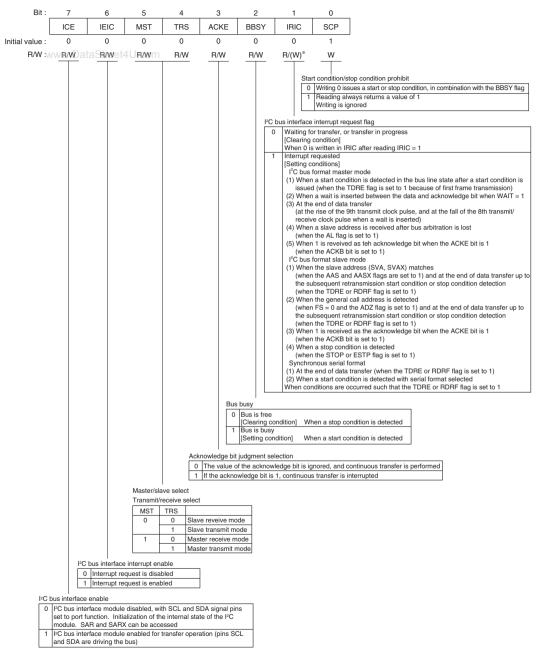

| 25.2.5 I <sup>2</sup> C Bus Control | 521  | Bit 7—I <sup>2</sup> C Bus Interface Enable (ICE)                                                            |

| Register (ICCR)                     |      | Description amended                                                                                          |

|                                     |      | I <sup>2</sup> C Bus interface module enabled for transfer operations (pins SCL and SDA are driving the bus) |

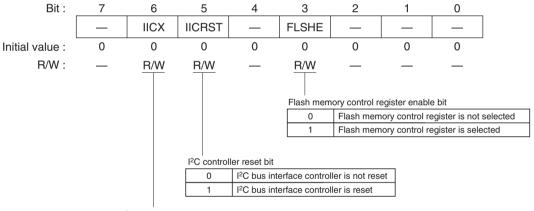

| 25.2.7 Serial/Timer                 | 533  | Bit 5—I <sup>2</sup> C Controller Reset (IICRST)                                                             |

| Control Register (STCR)             |      | Description amended                                                                                          |

| (STON)                              |      | Therefore, be sure to clear the IICRST bit after setting it.                                                 |

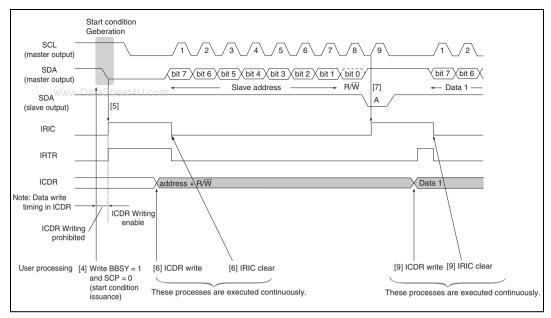

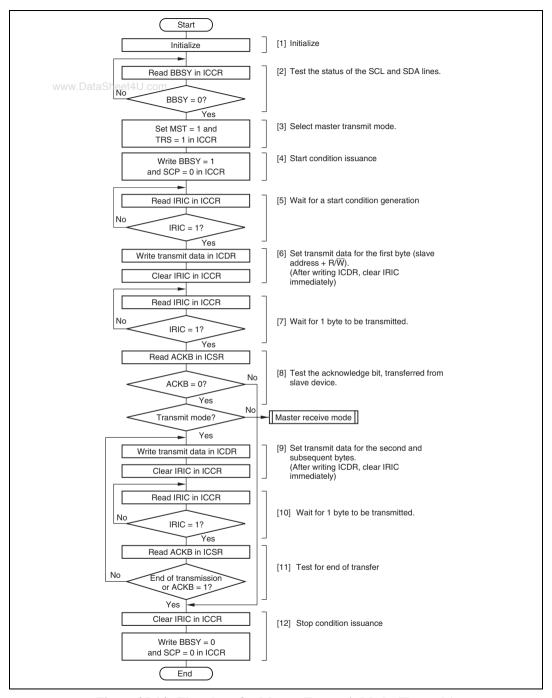

| 25.3.2 Master                       | 537  | Description amended                                                                                          |

| Transmit Operation                  |      | [11]When there is data to be transmitted, go to the step [9] to continue next transmission                   |

RENESAS

| Item                                                                                   | Page   | Revision (See Manual for Details)                                                                                                                                                           |

|----------------------------------------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

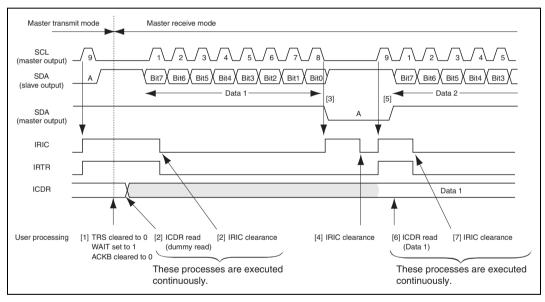

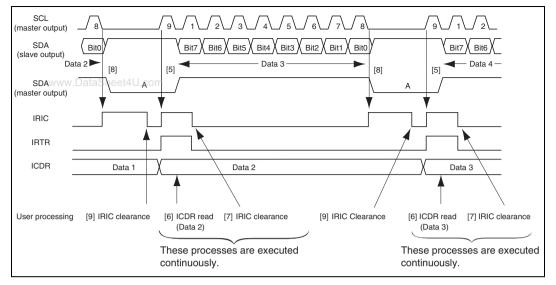

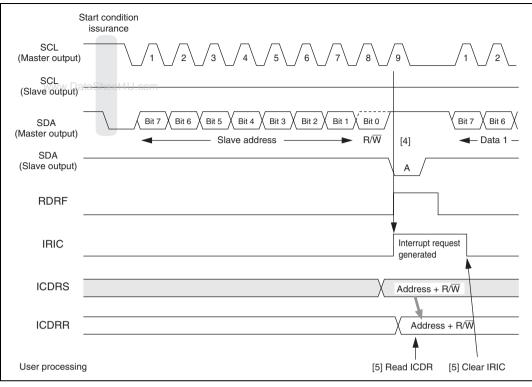

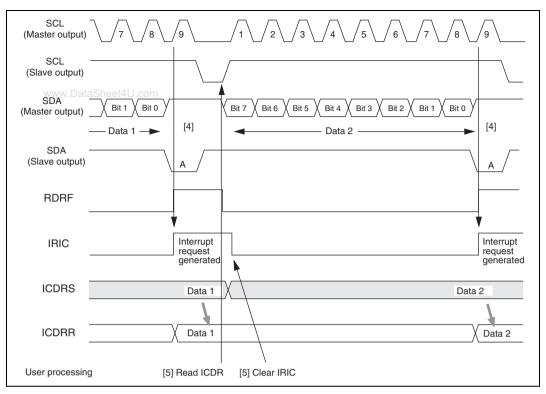

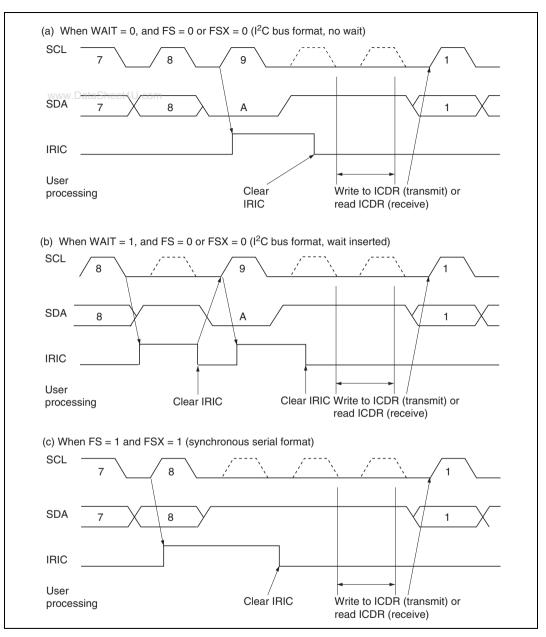

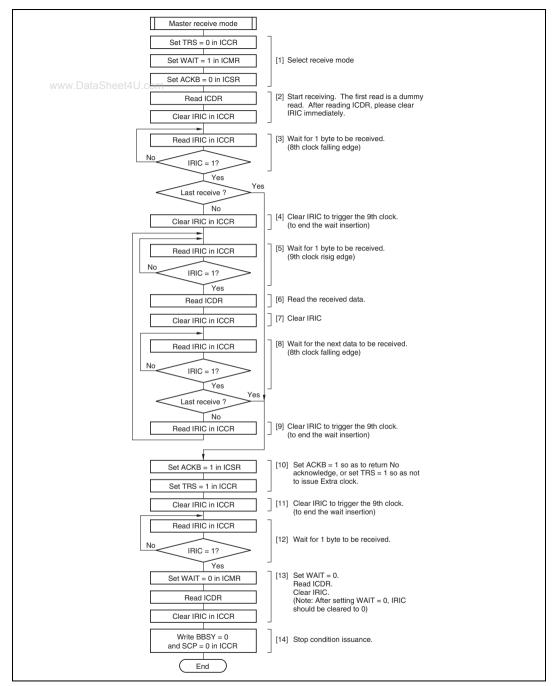

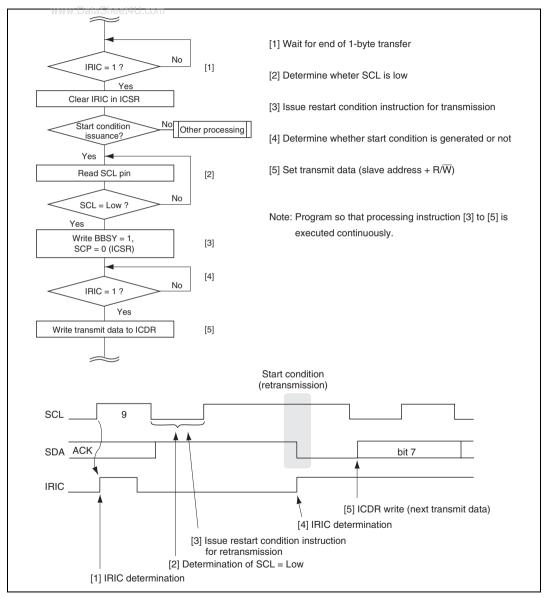

| 25.3.3 Master                                                                          | 540    | Figure 25.7 amended                                                                                                                                                                         |

| Receive Operation                                                                      |        | [4] IRIC clearance                                                                                                                                                                          |

| Figure 25.7 Example of Master Receive Mode Operation Timing (MLS = ACKB = 0, WAIT = 1) |        |                                                                                                                                                                                             |

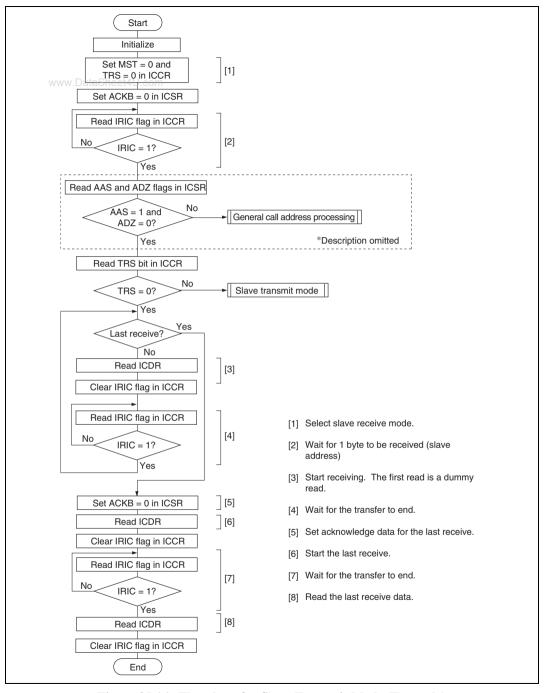

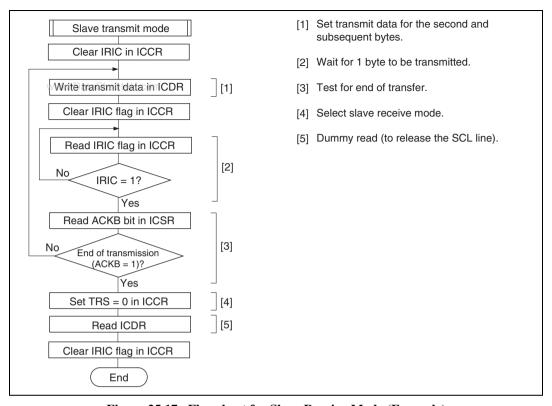

| 25.3.8 Sample<br>Flowcharts                                                            | 548    | Figure 25.14 amended                                                                                                                                                                        |

| Figure 25.14<br>Flowchart for Master                                                   |        | Read IRIC in ICCR  [5] Wait for a start condition generation  No  IRIC = 1?                                                                                                                 |

| Transmit Mode<br>(Example)                                                             |        | Write transmit data in ICDR  Write transmit data in ICDR  Clear IRIC in ICCR  [6] Set transmit data for the first byte (slave address + R/W).  (After writing ICDR, clear IRIC immediately) |

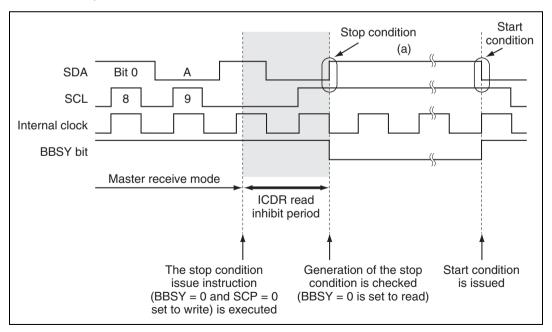

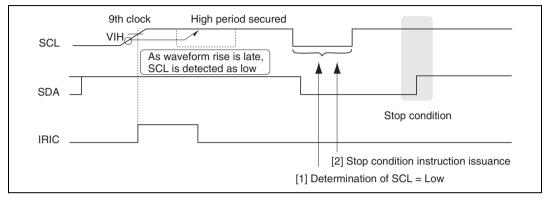

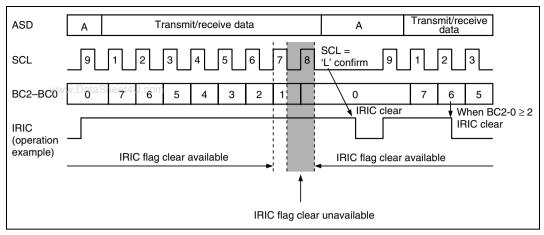

| 25.4 Usage Notes                                                                       | 554    | Description amended                                                                                                                                                                         |

|                                                                                        |        | (1) then issue the instruction that generates the stop condition. Note that the SCL may briefly remain at a high level immediately after BBSY is cleared to 0.                              |

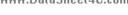

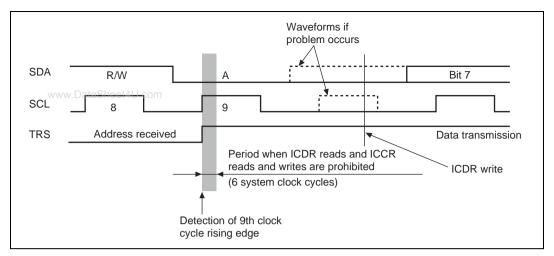

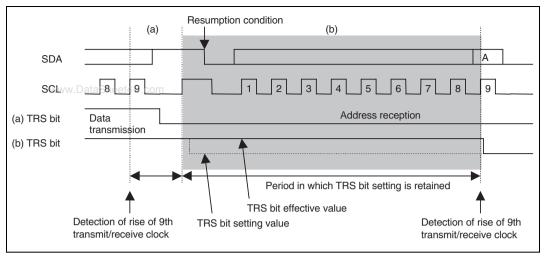

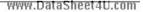

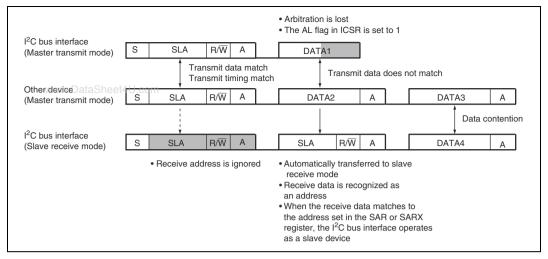

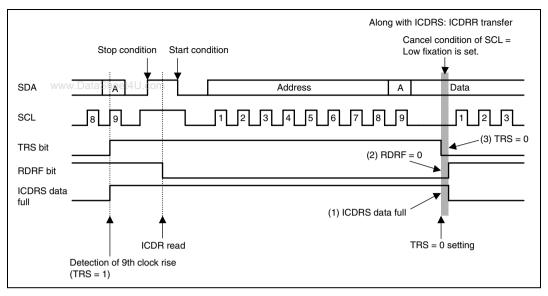

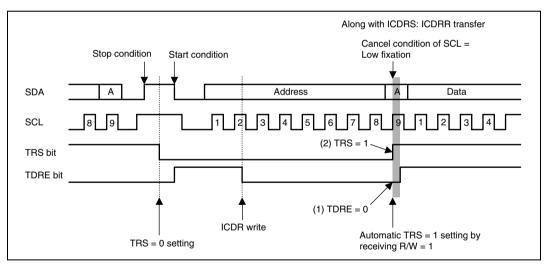

|                                                                                        | 559 to | (10) Notes on WAIT Function                                                                                                                                                                 |

|                                                                                        | 566    | (11) Notes on ICDR Reads and ICCR Access in Slave<br>Transmit Mode                                                                                                                          |

|                                                                                        |        | (12) Notes on TRS Bit Setting in Slave Mode                                                                                                                                                 |

|                                                                                        |        | (13) Notes on Arbitration Lost in Master Mode                                                                                                                                               |

|                                                                                        |        | (14) Notes on Interrupt Occurrence after ACKB Reception                                                                                                                                     |

|                                                                                        |        | (15) Notes on TRS Bit Setting and ICDR Register Access                                                                                                                                      |

|                                                                                        |        | Description added                                                                                                                                                                           |

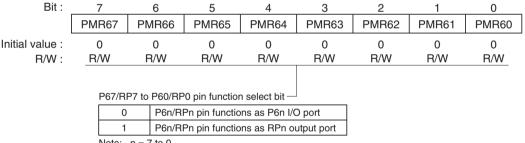

| 28.2.3 Pin                                                                             | 610    | Description amended                                                                                                                                                                         |

| Configuration                                                                          |        | P6n, P7n, P80 to P83, and PS1 to PS4 are general-purpose ports                                                                                                                              |

| 28.3.4 Register                                                                        | 626    | (5) Reference Period Mode Register 2 (RFM2)                                                                                                                                                 |

| Descriptions                                                                           |        | Description amended                                                                                                                                                                         |

|                                                                                        |        | signal generators. Bits 6 to 1 are reserved                                                                                                                                                 |

| Item                                                                                   | Page         | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

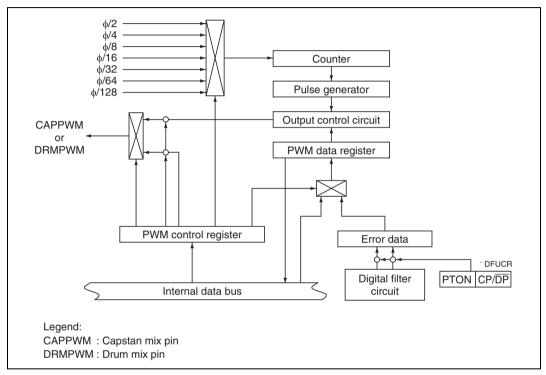

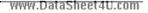

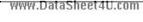

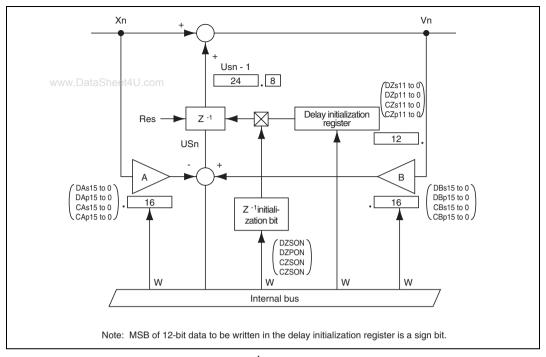

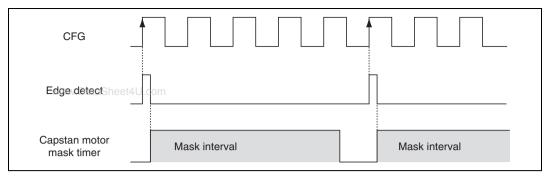

| 28.11.2 Block<br>Diagram<br>Figure 28.38 Block<br>Diagram of Digital Filter<br>Circuit | 713<br>J.com | Figure 28.38 amended  A, B, G, etc.  Logistical transfer of the property of th |

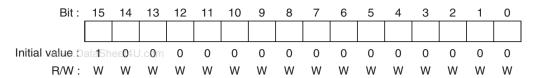

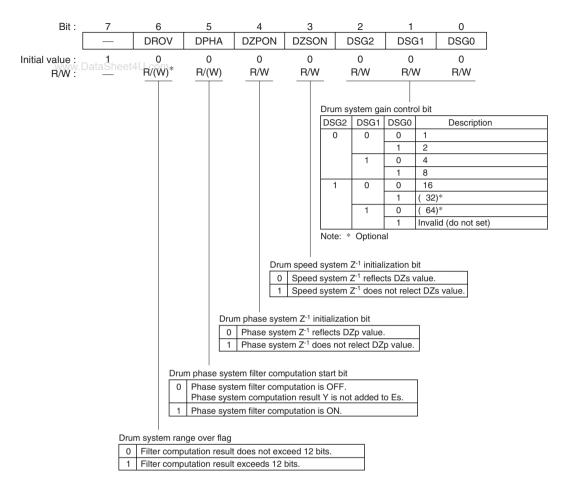

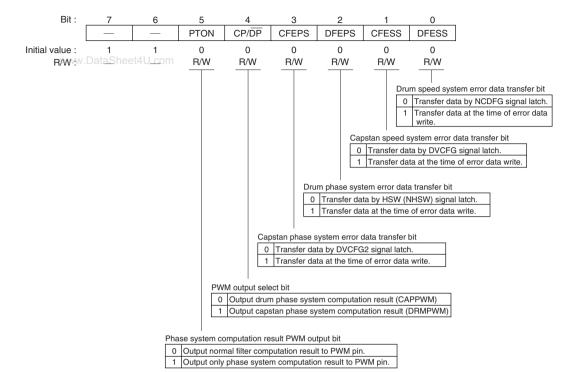

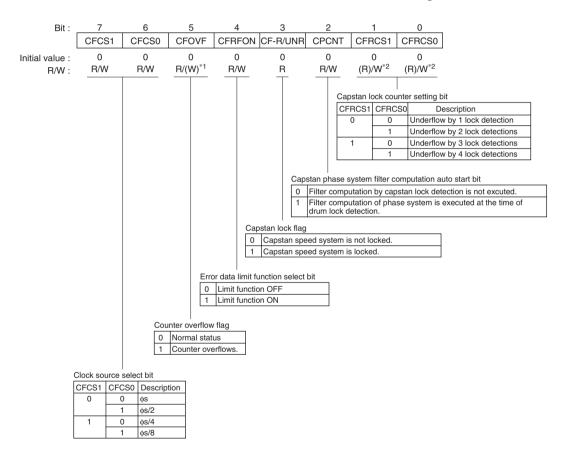

| 28.11.5 Register<br>Descriptions                                                       | 721          | (6) Capstan System Digital Filter Control Register (CFIC)  Bit figure amended    Bit: 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

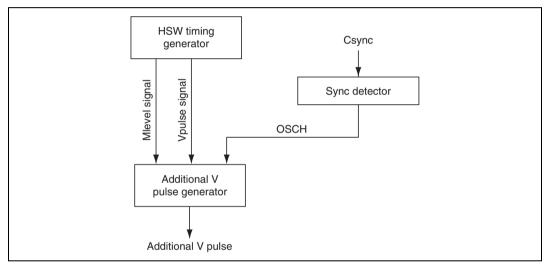

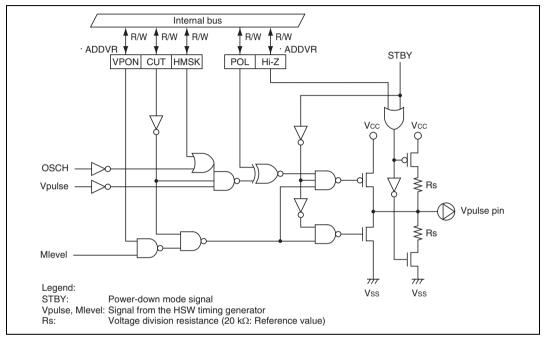

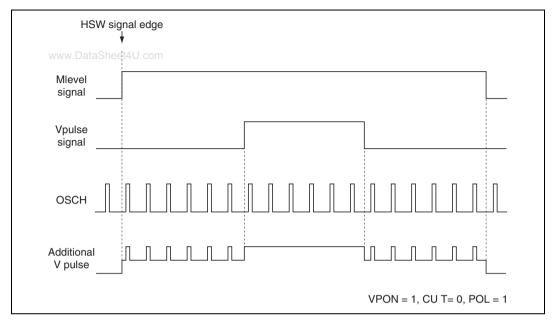

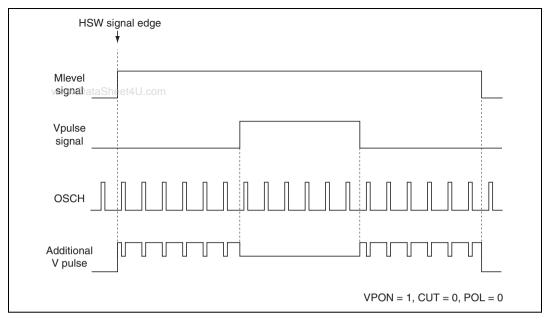

| 28.12.5 Additional V<br>Pulse Signal                                                   | 732          | Description amended  Additional V Pulses when Sync Signal Is Not Detected: depending on the HRTR and HPWR setting, with resultant discontinuity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

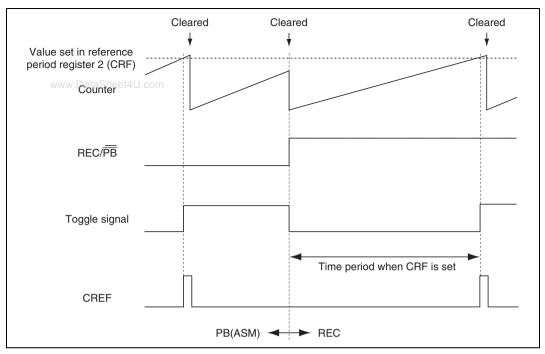

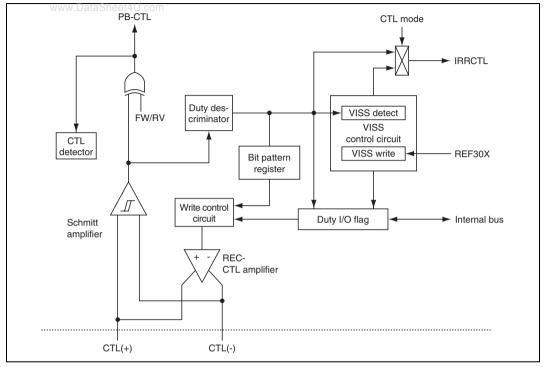

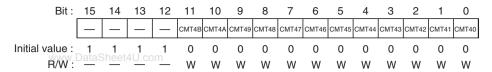

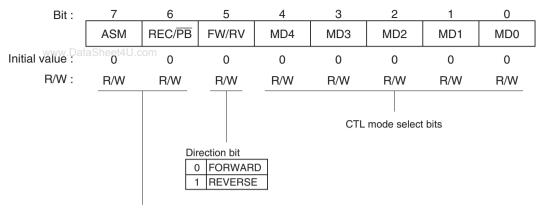

| 28.13.5 Register<br>Descriptions                                                       | 740          | (2) CTL Mode Register (CTLM)  Description amended  Bits 7 and 6: Record/Playback Mode Bits (ASM, REC/PB):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

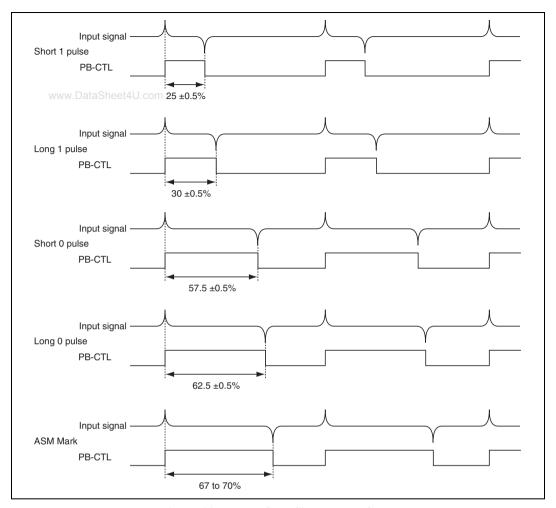

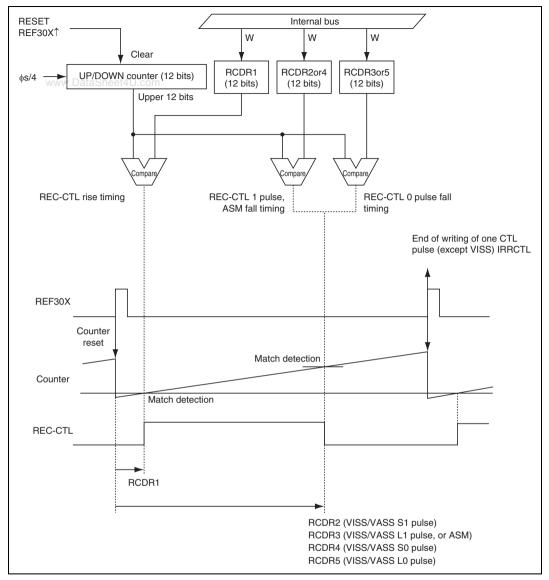

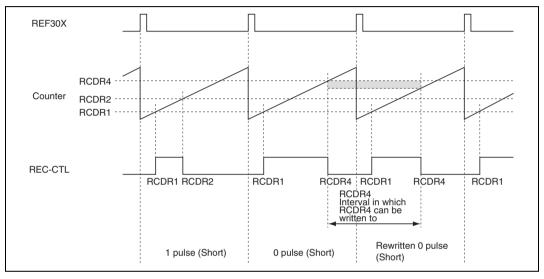

|                                                                                        | 745          | (6) REC-CTL Duty Data Register 4 (RCDR4)  Description amended  RCDR4 = T4 × $\phi$ s/64 $\phi$ s is the servo clock frequency (= $f_{osc}/2$ ) in Hz, and T4 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                        | 746          | (7) REC-CTL Duty Data Register 5 (RCDR5)  Description amended RCDR5 = T5 × φ s/64 φs is the servo clock frequency (= f <sub>osc</sub> /2) in Hz, and T5 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

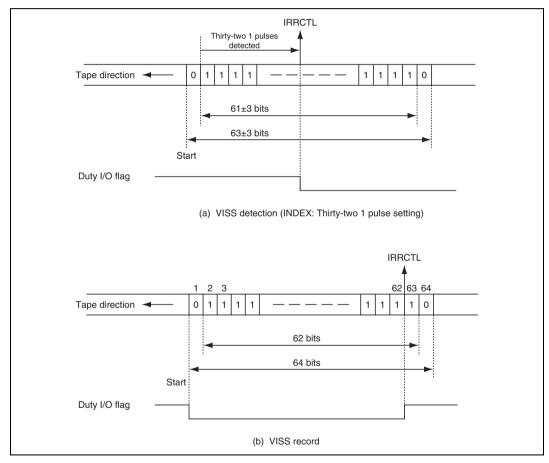

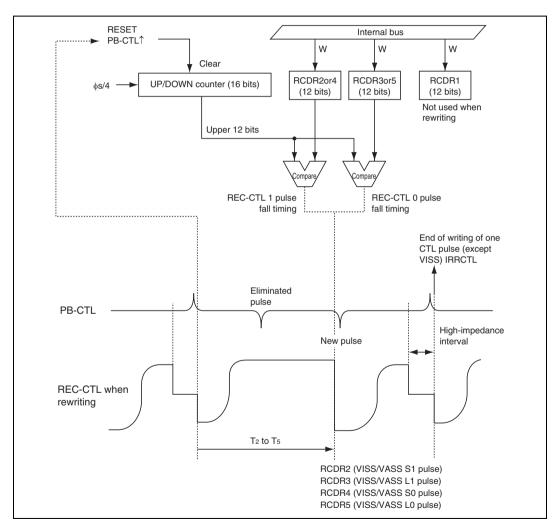

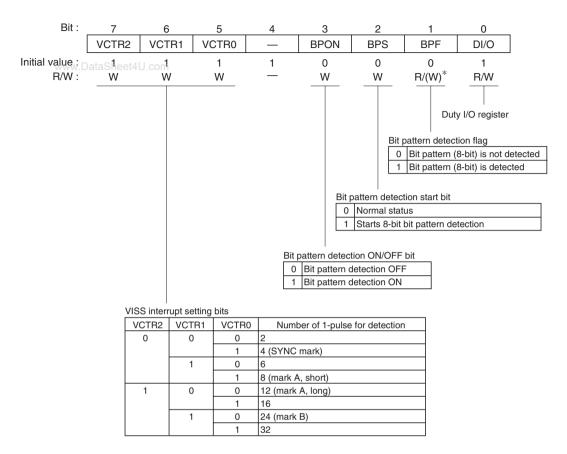

|                                                                                        | 747          | Bit 0—Duty I/O Register (DI/O)  Description amended  the VISS control circuit. In VISS record or rewrite mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

RENESAS

| Item                                                                                                              | Page | Revision (See Manual for Details)                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

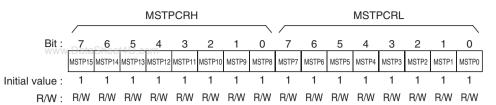

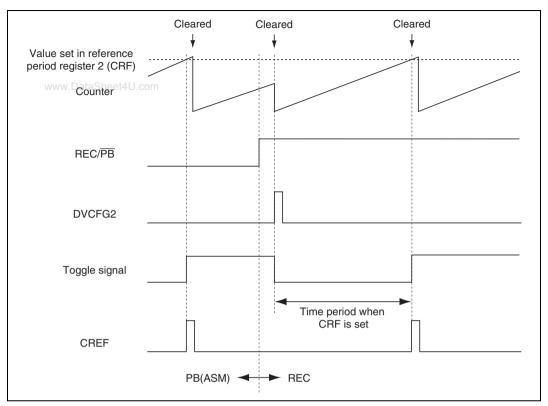

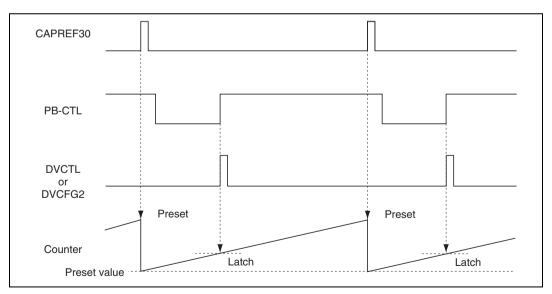

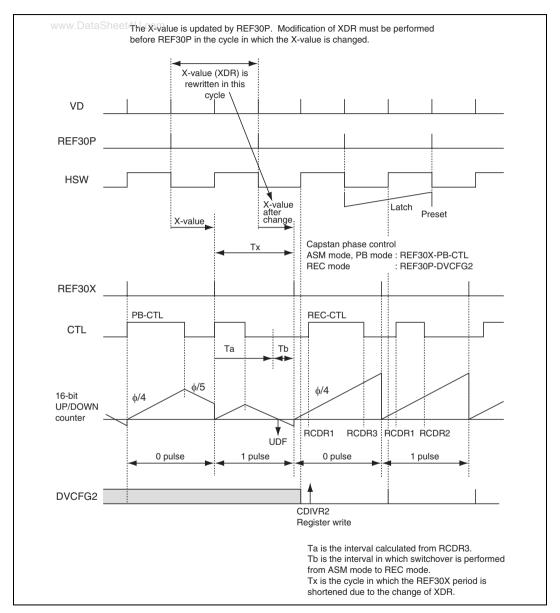

| 28.13.6 Operation                                                                                                 | 751  | Figure 28.50 amended                                                                                                                         |

| Figure 28.50 Example of CTLM Switchover Timing (When Phase Control Is Performed by REF30P and DVCFG2 in REC Mode) |      | (Before) PDCR3 → (After) PCDR3                                                                                                               |

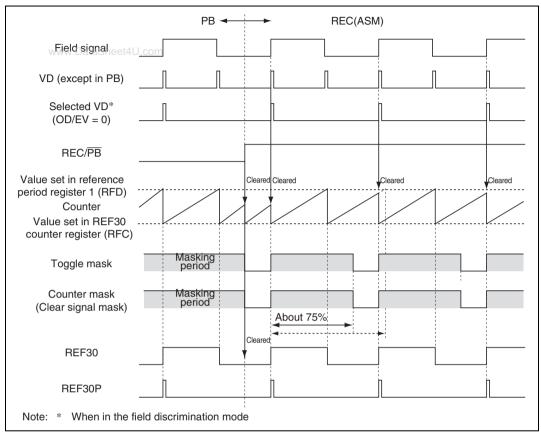

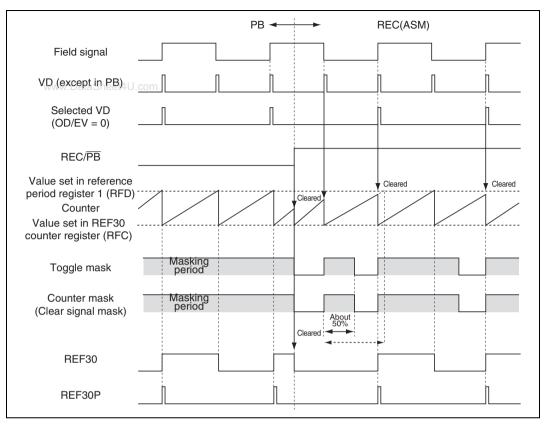

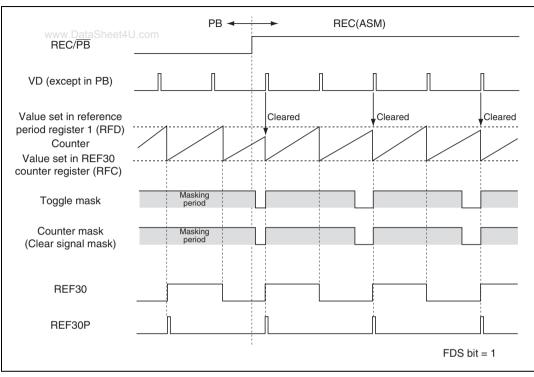

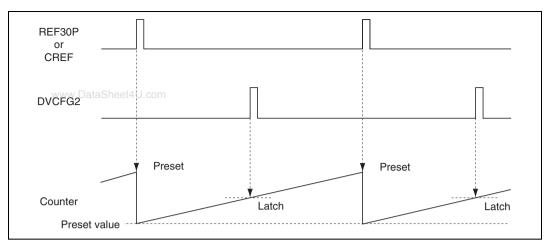

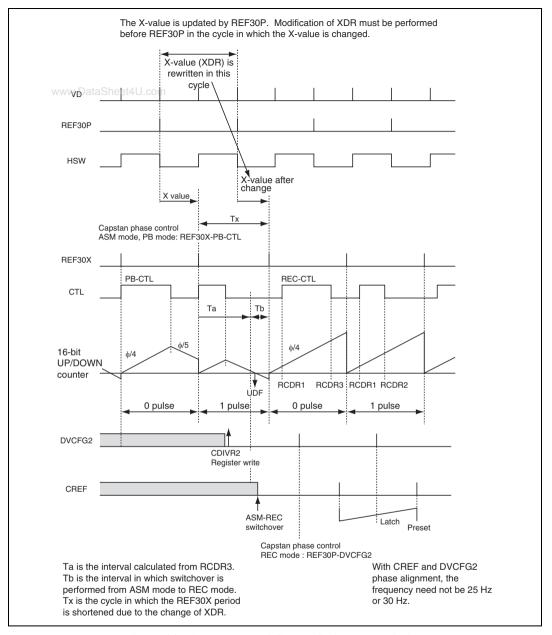

| Figure 28.51 Example                                                                                              | 752  | Figure 28.51 amended                                                                                                                         |

| of CTLM Switchover<br>Timing (When Phase<br>Control Is Performed<br>by CREF and DVCFG2<br>in REC Mode)            |      | Ta is the interval calculated from RCDR3                                                                                                     |

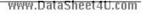

| 28.18.9 CTL Output                                                                                                | 762  | Table 28.21 amended                                                                                                                          |

| Section                                                                                                           |      | (Before) 65.5 $\pm 0.5\% \rightarrow$ (After) 62.5 $\pm 0.5\%$                                                                               |

| Table 28.21 REC-CTL Duty Register and CTL Outputs                                                                 |      |                                                                                                                                              |

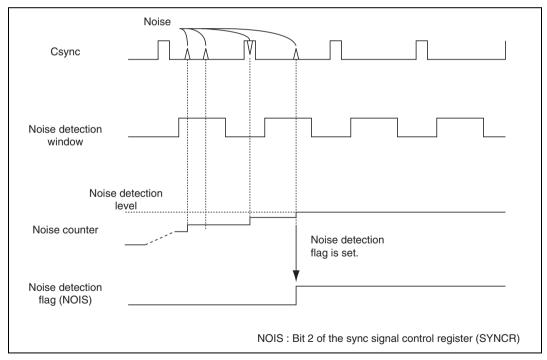

| 28.15.6 Noise                                                                                                     | 790  | (1) Example of Setting                                                                                                                       |

| Detection                                                                                                         |      | Description amended                                                                                                                          |

|                                                                                                                   |      | ∴HPWR3 - 0 = H'B                                                                                                                             |

| 29.2.7 Flash Memory Characteristics                                                                               | 824  | Table 29.12 amended                                                                                                                          |

| Table 29.12 Flash                                                                                                 |      | Test<br>Item Symbol Min Typ Max Unit Conditions                                                                                              |

| Memory Characteristics                                                                                            |      | Erasing time*1*3*5 te 100 1200 ms/<br>block                                                                                                  |

| (Preliminary)                                                                                                     |      | Reprogramming count NwEc 100 10000 — Times                                                                                                   |

|                                                                                                                   |      | Data retention time <sup>*0</sup> t <sub>DRP</sub> 10 — Years  At Wait time after SWE-bit setting <sup>*1</sup> χ 10 — μs                    |

|                                                                                                                   |      | Programming                                                                                                                                  |

|                                                                                                                   | 825  | Notes 7 to 9 added                                                                                                                           |

|                                                                                                                   |      | Notes: 7. Minimum number of times for which all characteristics are guaranteed after rewriting (Guarantee range is 1 to minimum value).      |

|                                                                                                                   |      | 8. Reference value for 25°C (as a guideline, rewriting should normally function up to this value).                                           |

|                                                                                                                   |      | <ol><li>Data retention characteristic when rewriting is performed<br/>within the specification range, including the minimum value.</li></ol> |

| lk                                                                         | D    | Participa (One Manual for Patella)                                                                                                                    |

|----------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| A 1 Instructions                                                           | Page | Revision (See Manual for Details)                                                                                                                     |

| A.1 Instructions Table A.1 List of Instruction Set  www.DataSheet4         |      | (7) System Control Instructions in table A.1 amended    No of Execution                                                                               |

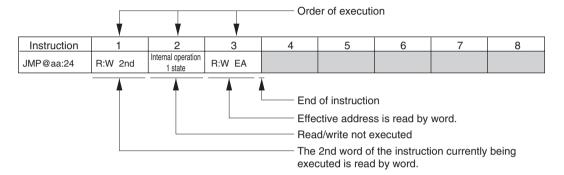

| A.4 Number of<br>Execution States                                          | 872  | Description amended for each instruction of the H8S/2000 CPU. Table A.5                                                                               |

| Table A.4 Number of States Required for                                    | 873  | Table A.4 amended  Target of Access                                                                                                                   |

| Each Execution Status                                                      |      | On-Chip Supporting Module                                                                                                                             |

| (Cycle)                                                                    |      | Execution Status (Cycle) On-Chip Memory 8-Bit Bus 16-Bit Bus                                                                                          |

|                                                                            |      | Byte data access S <sub>L</sub> 2 2                                                                                                                   |

|                                                                            |      | Word data access S <sub>M</sub> 4 2                                                                                                                   |

|                                                                            |      | Internal operation $S_N \hspace{1cm} 1 \hspace{1cm} 1 \hspace{1cm} 1$                                                                                 |

| A.6 Change of<br>Condition Codes<br>Table A.7 Change of<br>Condition Codes | 902  | Table A.7 amended (Before) C=D0 (In case of 1 bit), C=D-1 (In case of 2 bits) $\rightarrow$ (After) C=D0 (In case of 1 bit), C=D1 (In case of 2 bits) |

| em  | l             | Page | Revision (See Manual for Details)                                                                                                 |

|-----|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

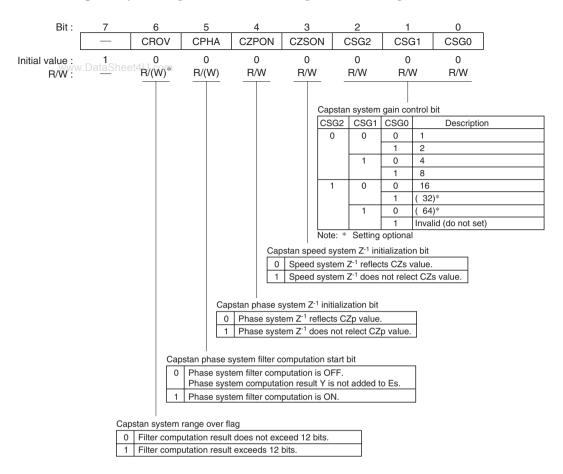

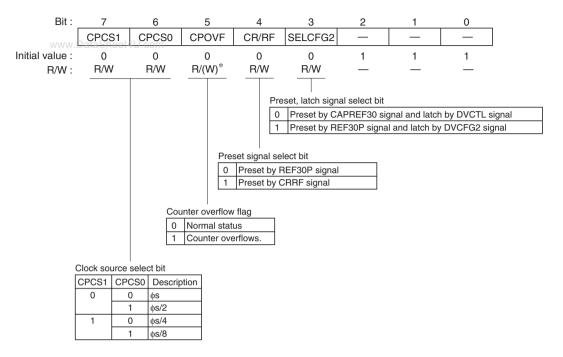

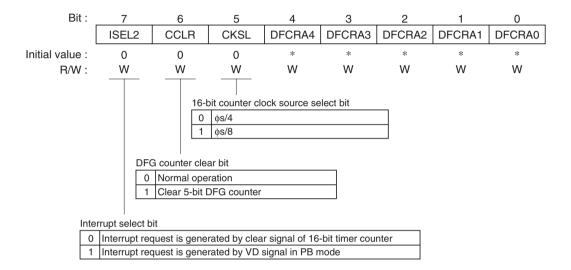

| 3.2 | Function List | 918  | H'D029: CFIC: Digital Filter                                                                                                      |

|     |               |      | Figure amended                                                                                                                    |

|     |               |      | 2 1 0 CSG2 CSG1 CSG0 0 0 0 0 R/W R/W R/W  Capstan system gain control bit CSG2 CSG1 CSG0 Description 0 0 0 ×1 1 ×2                |

|     |               |      | 1 0 ×4 1 ×8 1 0 0 ×16 1 (×32)* 1 0 (×64)* 1 Invalid (do not set)  Note: * Setting optional                                        |

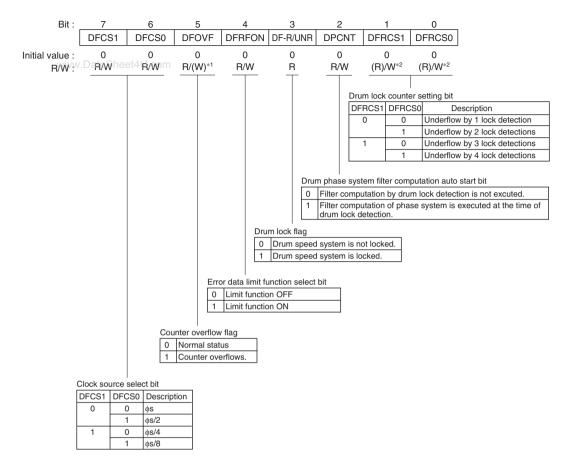

|     |               | 919  | H'D031: DFPR: Drum Error Detector                                                                                                 |

|     |               |      | H'D033: DFER: Drum Error Detector                                                                                                 |

|     |               |      | Subheading deleted                                                                                                                |

|     |               | 919  | H'D032: DFER: Drum Error Detector                                                                                                 |

|     |               |      | Note * added                                                                                                                      |

|     |               |      | Note: * Note that only detected error data can be read.                                                                           |

|     |               | 920  | H'D035: DFRUDR: Drum Error Detector                                                                                               |

|     |               |      | H'D037: DFRLDR: Drum Error Detector                                                                                               |

|     |               |      | Subheading deleted                                                                                                                |

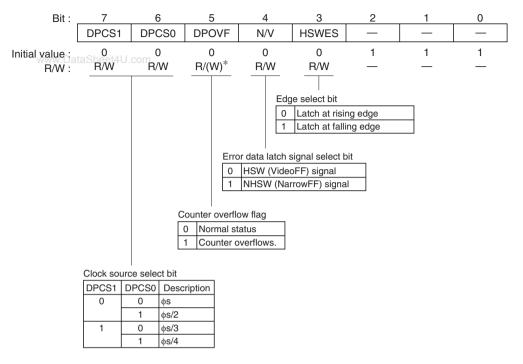

|     |               | 927  | H'D060: HSM1: HSW Timing Generator                                                                                                |

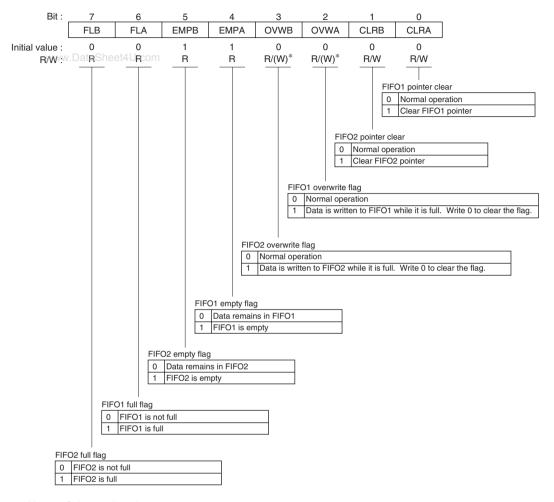

|     |               |      | Figure amended  FIFO1 overwrite flag  O Normal operation  1 Data is written to FIFO2 while it is full. Write 0 to clear the flag. |

|     |               | 941  | Table amended                                                                                                                     |

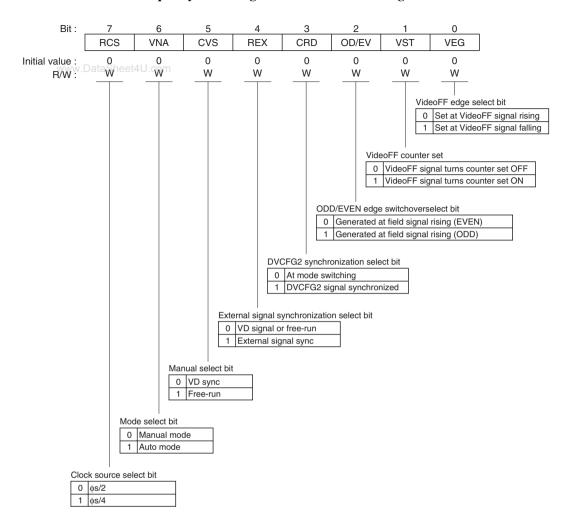

Video FF signal turns counter set ON

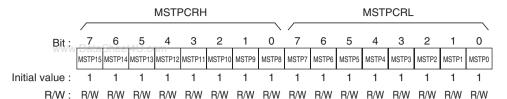

#### Item Page **Revision (See Manual for Details)** B.2 Function List 954 H'D0E2: SCR2: 32-byte Buffer SCI2 Figure amended Transfer clock select bits CKS2 CKS1 CKS0 SCK2 pin Clock source Prescaler frequency Transfer clock frequency division rate φ = 10 MHz φ = 5 MHz SCK2 φ/256 25.6 μs 51.2 μs Ω 0 0 Sprescaler S 0 6.4 μs 12.8 µs 0 1 φ/64 1 3.2 µs 0 0 o/32 6.4 µs 0 1 1 φ/16 1.6 µs 3.2 µs 0 0 φ/8 0.8 μs 1.6 µs 0 1 6/4 0.4 μs 0.8 μs 1 0 ġ/2 0.4 μs 1 SCK2 External clock Transfer data interval select bits Transfer data interval GAP1 GAP0 0 0 No interval 0 1 8-clock interval 0 24-clock interval 1 56-clock interval 956 H'D100: ITER: Timer X1 Figure amended Output compare interrupt enable bit OFV interrupt request (FOVI) is disabled **OFV** interrupt request (FOVI) is enabled H'D100: TMB: Timer B 962 Figure amended Clock select bit Count at rising/falling edge of external event (TMBI)\* H'D14C: SSR1: SCI1 984 Figure amended Parity error (Before) (even or odd) specified by the O/E bit in SMR1\*2 → (After) (even or odd) specified by the O/E bit in SMR1\*2 H'D158: ICCR: IIC Bus Interface 986 Figure amended I<sup>2</sup>C bus interface enable I<sup>2</sup>C bus interface module enabled for transfer operation (pins

SCL and SDA are driving the bus)

RENESAS

| Item                                    | Page    | Revision (See Manual for Details)                                                                                                                                                                                                                                                                                 |

|-----------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

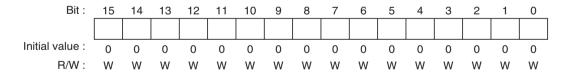

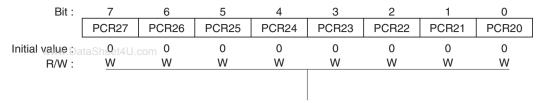

| B.2 Function List                       | 1000    | H'FFD4: PCR4: I/O Port                                                                                                                                                                                                                                                                                            |

|                                         |         | Figure amended                                                                                                                                                                                                                                                                                                    |

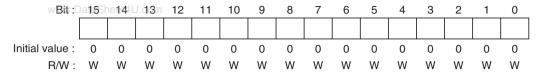

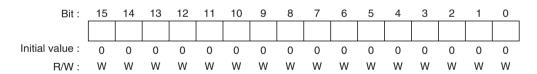

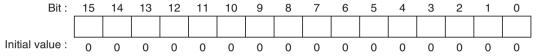

| www.DataSheet4U                         |         | Bit: 7 6 5 4 3 2 1 0    PCR47   PCR46   PCR45   PCR44   PCR43   PCR42   PCR41   PCR40     Initial value: 0 0 0 0 0 0 0 0 0 0 0 0 0     R/W: W W W W W W W W W W W W W W W W W W                                                                                                                                   |

|                                         |         | Note: n = 7 to 0                                                                                                                                                                                                                                                                                                  |

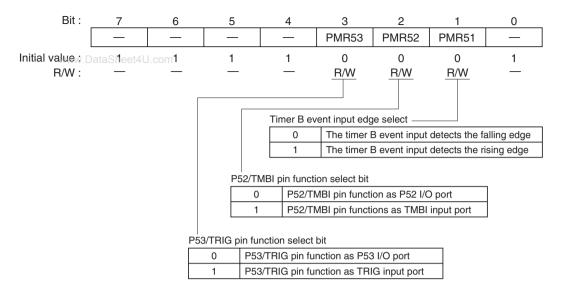

|                                         | 1002    | H'FFDC: PMR5: I/O Port                                                                                                                                                                                                                                                                                            |

|                                         |         | Figure amended                                                                                                                                                                                                                                                                                                    |

|                                         |         | P52/TRIG pin function select bit                                                                                                                                                                                                                                                                                  |

|                                         | ·       | P52/TMBI pin functions as TMBI input port                                                                                                                                                                                                                                                                         |

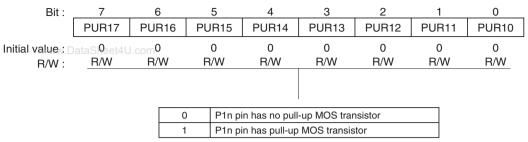

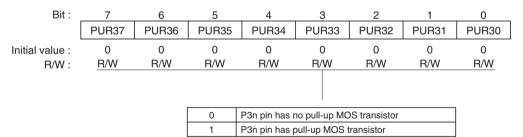

|                                         | 1004    | H'FFE3: PUR3: I/O Port                                                                                                                                                                                                                                                                                            |

|                                         |         | Figure amended                                                                                                                                                                                                                                                                                                    |

|                                         |         | 0 P3n pin has no pull-up MOS transistor 1 P3n pin has pull-up MOS transistor Note: n = 7 to 0                                                                                                                                                                                                                     |

|                                         | 1010    | Table amended                                                                                                                                                                                                                                                                                                     |

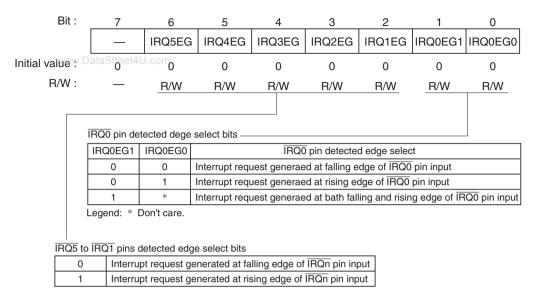

|                                         |         | (Before) IRQ0EG2 $\rightarrow$ (After) IRQ0EG0                                                                                                                                                                                                                                                                    |

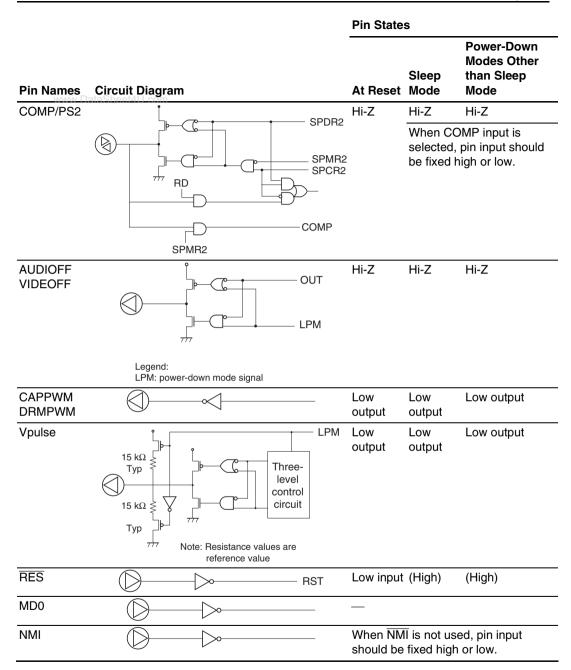

| C.1 Pin Circuit                         | 1019 to | Circuit diagram description amended                                                                                                                                                                                                                                                                               |

| Diagrams Table C.1 Pin Circuit Diagrams | 1024    | PUR1n         PCR1n         PUR17         PCR17         PUR20         PCR20           PUR21         PCR21         PUR22         PCR22         PUR2n         PCR2n           PUR26         PCR26         PUR25         PCR25         PUR27         PCR27           PUR30         PCR30         PUR3n         PCR3n |

|                                         | 1024    | Circuit diagram description amended                                                                                                                                                                                                                                                                               |

|                                         |         | (Before) OUR: $\rightarrow$ (After) OUT:                                                                                                                                                                                                                                                                          |

|                                         | 1025    | Pin name description amended                                                                                                                                                                                                                                                                                      |

|                                         |         | P42/FTIB                                                                                                                                                                                                                                                                                                          |

|                                         |         | P46/FTOB                                                                                                                                                                                                                                                                                                          |

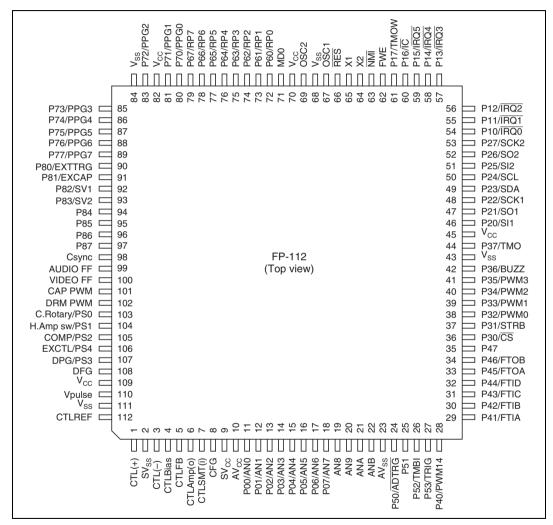

| G. External<br>Dimensions               | 1037    | Figure G.1 replaced                                                                                                                                                                                                                                                                                               |

| Figure G.1 External Dimensions (FP-112) |         |                                                                                                                                                                                                                                                                                                                   |

Rev.3.00 Jan. 10, 2007 page xvi of xxxvi REJ09B0328-0300

www.DataSheet4U.com

All trademarks and registered trademarks are the property of their respective owners.

### Contents

| Sect | ion 1                         | Overview                                          | 1  |  |  |  |  |  |

|------|-------------------------------|---------------------------------------------------|----|--|--|--|--|--|

| 1.1  | Overv                         | ataSheet4U.com<br>lew                             | 1  |  |  |  |  |  |

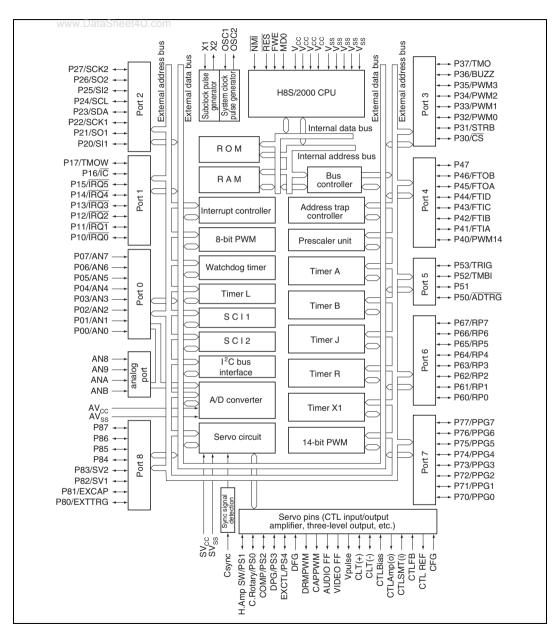

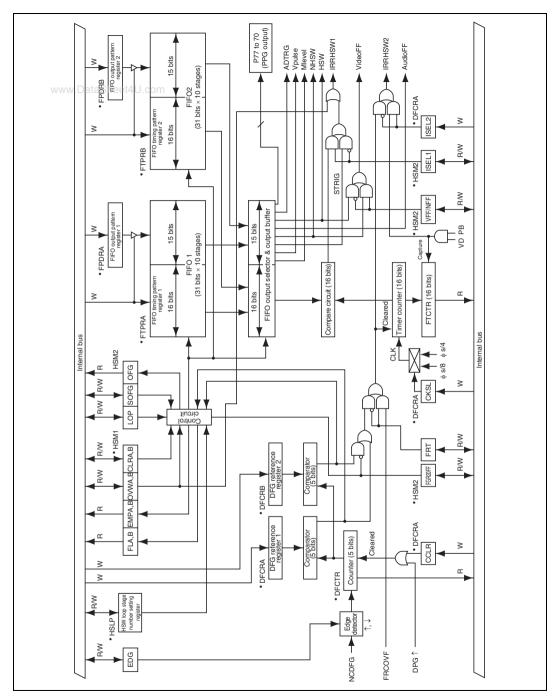

| 1.2  | Interna                       | al Block Diagram                                  | 6  |  |  |  |  |  |