# **Crystal Clock Oscillators**

T.50-23

## ENABLE/DISABLE 3-STATE COMPATIBLE

HS-1200/1210 Series (TTL) HS-1370/1380 Series (CMOS) 500 kHz-36.0 MHz

HS-1200/1300 Series

HA-1200/1300 Series (See Options)

The HS-1200/1210 and HS-1370/1380 Series of quartz crystal clock oscillators provide enable/disable 3-state TTL/CMOS compatible signals for bus connected systems. Supplying Pin 1 of the HS-1200/1370 units with a logic "0" enables the output on Pin 8. Alternatively, supplying Pin 1 of the HS-1210/1380 units with a logic "1" enables its Pin 8 output. In the disabled mode, Pin 8 presents a high impedance to the load.

The HS-1370/1380 oscillator does not have an internal pull-up resistor. Pin 1 should not be left floating.

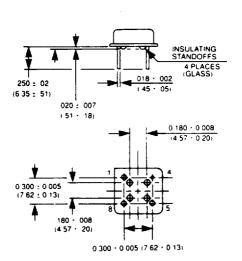

All units are resistance welded in an all metal package, offering RFI shielding, and are designed to survive standard wave soldering operations without damage. Insulated standoffs to enhance board cleaning are standard.

# Enable/Disable vs. 3-State

An oscillator is termed enable/disable when its output can be disabled in some manner.

Some manufacturers choose to supply this oscillator as a standard product with a constant Logic "1" state when disabled. If these oscillators are used in an application where another signal needs to be injected on the same bus, such as automatic test equipment, the output must be shorted to ground off and on to create the new clock signal. In some cases, this overdrives the output device causing permanent damage. This may be either immediate or latent oscillator damage. Because of this possible damage, **NEL Frequency Controls has elected** to design the enable/disable product line using a 3-state device. A threestate oscillator is one in which the oscillator, when disabled, is in the high impedance state. The 3-state has

been established for signal multiplexing applications, making it ideal for automatic test equipment use.

Employing the 3-state design, when the oscillator output is disabled, another standard digital signal can be applied without damage to the output device. It can also be used for applications as a second source for other enable/disable oscillators, if the use does not depend on the output being a particular voltage level when disabled.

### **Suggested Applications**

HS-1200/1210 and HS-1370/1380 Series oscillators are ideally suited for applications involving more than one clock or source on the same bus. The high impedance state allows ATE (Automatic Test Equipment) board testing without having to remove the oscillator. In multiplexing applications, multiplex clock signals can be made available to a system using the enable/disable 3-state feature.

#### **Features**

- ☐ Wide frequency range— 500 kHz to 36.0 MHz (consult factory for higher frequency requirements)

- ☐ User specified tolerance from ± 0.0025%

- □ Low power consumption

- ☐ All metal, resistance weld, hermetically sealed package

- ☐ High shock resistance, to 3,000 G's

(Cont. on next page)

# **Crystal Clock Oscillators**

**ENABLE/DISABLE**

# **Specifications**

| PARAMETER                                           | CONDITIONS                                         | MINIMUM                                      | MAXIMUM             | 3-STATE                                               |

|-----------------------------------------------------|----------------------------------------------------|----------------------------------------------|---------------------|-------------------------------------------------------|

| <b>General Characteristics</b>                      | · · · · · · · · · · · · · · · · · · ·              | <del></del>                                  | <del></del>         | COMPATIBLE                                            |

| Supply voltage (V <sub>CC</sub> , V <sub>DD</sub> ) | Supply                                             | 4.5 V                                        | 5.5 V               | HS-1200/1210                                          |

| u ( 00, bb/                                         | Breakdown                                          | - 0.5 V                                      | 7.0 V¹              | Series (TTL)                                          |

| Supply current (I <sub>CC.</sub> I <sub>DD</sub> )  |                                                    | 0.0 mA                                       | 55mA                |                                                       |

| Output current (IO)                                 |                                                    | 0.0 mA                                       | 16.0 mA             | HS-1370/1380                                          |

| Operating temperature (T <sub>A</sub> )             | gradus <del>and</del> gradus state of the state of | 0° C                                         | 70° C               | Series (CMOS)                                         |

| Storage temperature (T <sub>S</sub> )               |                                                    | – 65° C                                      | +125° C             | 500 kHz-36.0 MHz                                      |

| Power dissipation (PD)                              |                                                    | _                                            | 400 mW              |                                                       |

| Lead temperature (T <sub>L</sub> )                  | Soldering, 10 s                                    |                                              | 300° C              | (Continued)                                           |

| Output Characteristics                              |                                                    |                                              |                     |                                                       |

| Frequency                                           |                                                    | 500 kHz                                      | 36.0 MHz            | SQUARE CORNER 1.45 04 ± 0.005 PIN #7 CONNECTED        |

| Tolerance                                           | User specified                                     | ±0.0025%                                     |                     | SQUARE CORNER (15.24 ± 0.13) PIN #7 CONNECTED TO CASE |

| Symmetry                                            | TTL, @ 1.4 V                                       | 40/60%                                       | 60/40%              |                                                       |

|                                                     | CMOS, @ 0.5 V <sub>DD</sub>                        | 40/60%                                       | 60/40%              | •                                                     |

| Logic 0 (V <sub>OL</sub> )                          | TTL, driving equiv. load                           |                                              | 0.4 V               | 0.300 ± 0.005                                         |

| 3 (.OE)                                             | CMOS, driving                                      | ·                                            | 0.2 V               | 0.180 ± 0.008 (7.62 ± 0.13)                           |

|                                                     | equiv. load                                        |                                              |                     | (4.58 ± 0.20)                                         |

| Logic 1 (V <sub>OH</sub> )                          | TTL, driving equiv. load                           | 1 2.4 V                                      | -                   | DN 152                                                |

|                                                     | CMOS, driving                                      | V <sub>DD</sub> -0.2 V                       | 1. <del>1.</del> 1. | PIN #14                                               |

| Logio O / Logista                                   | equiv. load                                        |                                              | 40-4                | (12.20 ± 0.20)                                        |

| Logic 0 (I <sub>OL</sub> sink)                      | TTL, driving equiv. load CMOS, driving             | · <del>-</del>                               | 16 mA               |                                                       |

|                                                     | equiv. load                                        |                                              | 600 μα              | Pin Connection                                        |

| Logic 1 (I <sub>OH</sub> source)                    | TTL, driving equiv. load                           | <del></del>                                  | 400 μa              | 1 enable/disable input                                |

| -0 (.01//                                           | CMOS, driving                                      |                                              | 600 μa              | 7 grd and case                                        |

|                                                     | equiv. load                                        | 5 1 1 1<br>1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                     | 8 Output                                              |

| Logic 0 (V <sub>IL</sub> )                          | ŢŢĹ                                                | and <del>all</del> the signal                | 0.4 V               | $V_{CC}$ , $V_{DD}$                                   |

| 1 - 1 - 4 01 - 5                                    | CMOS                                               |                                              | 0.4 V               |                                                       |

| Logic 1 (V <sub>IIH</sub> )                         | TTL                                                | 2.4 V                                        | -                   |                                                       |

| Rise & fall time (t <sub>r</sub> , t <sub>f</sub> ) | CMOS<br>TTL,                                       | 3.0 V                                        |                     | 이는 일이 이렇게 이번 약을 이번                                    |

| 1 1100 a rail time (tf. tf)                         | @ 0.4 V to 2.4V                                    | _                                            | 10 ns               |                                                       |

|                                                     | CMOS,                                              |                                              | 10110               |                                                       |

|                                                     | @ 10% to 90% of V <sub>DD</sub>                    | <u></u> -                                    | 10 ns               |                                                       |

| 3-state                                             | 50                                                 |                                              | particular de la Co |                                                       |

| enable/disable time (t <sub>pz</sub> )              |                                                    | <del></del> .                                | 25 ns               |                                                       |

<sup>&</sup>lt;sup>1</sup>Overvoltage causes the oscillator to draw extreme current, and damage occurs.

- Options

☐ Gull wing surface mount package available on all enable/disable 3-state compatible oscillators.

☐ Metal Half Pack HA/SA Series

- 500 kHz to 36.0 MHz (Dimensions-see page 35)

**Enclosure Dimensions, Output Waveform** & Equivalent Load see pages 16 to 19.

### **NEW PRODUCTS**

In our continued effort to provide quality products to meet the needs of the changing electronics market, NEL is in the process of developing several new products.

Among these are:

#### TTL/CMOS Oscillator

Frequency range 70 to100 MHz. User tolerance available from ± .005%.

#### 3-State CMOS/TTL

Frequency range extended to 80MHz. User tolerance available from ± .005%.

#### Z80/8000/80A/80B Oscillator

Frequency range on HS-380/2890 Series extended to 40.0MHz. User tolerance available from ± .0025%.

### Programmable Video Clock Generator

For use in the computer graphics, disk drive (zone locator) and fiber optics markets.

This product simplifies operations by using phase-locked loop techniques to generate, from the crystal oscillator, all the necessary clocks used in a typical graphics system.

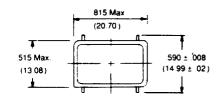

# OSCILLATOR METAL HALF PACK AND SURFACE MOUNT DIMENSIONS

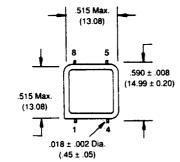

### **HA Series**

# 0 515 Max (13.08)0 515 Max (13.08)

Pin number 4 connected to case.

The metal half pack oscillator is available in TTL, CMOS, and Z80 logics. See options on pages 17, 20, 29, and 33 for details.

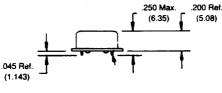

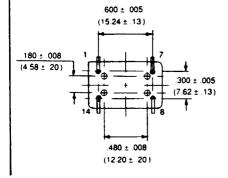

# **SA Series**

Pin number 4 connected to case. Seating plane = .005 Max. (.127) Wire leads to be formed to a 90° angle.

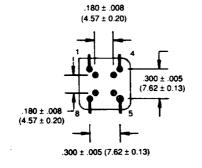

# **SM Series**

Pin number 7 connected to case. Seating plane = .005 Max. (.127) Wire leads to be formed to a 90° angle.

Dimensions are for reference only, inches (mm).