# Hitachi 16-Bit Single-Chip Microcomputer

H8S/2319, H8S/2318 Series, H8S/2319 F-ZTAT<sup>TM</sup>, H8S/2318 F-ZTAT<sup>TM</sup>, H8S/2315 F-ZTAT<sup>TM</sup>

H8S/2319 HD64F2319 H8S/2318 HD6432318, HD64F2318 H8S/2317 HD6432317 H8S/2316 HD6432316 H8S/2315 HD64F2315 H8S/2313 HD6432313 H8S/2312 HD6412312 H8S/2310 HD6412310

Reference Manual

— Individual Product Specifications —

# **HITACHI**

ADE-602-188A Rev. 2.0 8/24/00 Hitachi, Ltd.

www.DataSheet4U.com

#### Cautions

- Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's

patent, copyright, trademark, or other intellectual property rights for information contained in

this document. Hitachi bears no responsibility for problems that may arise with third party's

rights, including intellectual property rights, in connection with use of the information

contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

# Main Revisions and Additions in this Edition

| Page            | Item                                                    | Revisions (See Manual for Details)                                                                                                                                                            |

|-----------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| All             | Whole sections                                          | Amendment due to the addition of the H8S/2319 F-ZTAT, H8S/2315 F-ZTAT, H8S/2316, and H8S/2313 to the product lineup.                                                                          |

| 5               | 1.1 Overview                                            | Table 1.1 Overview The product lineup added.                                                                                                                                                  |

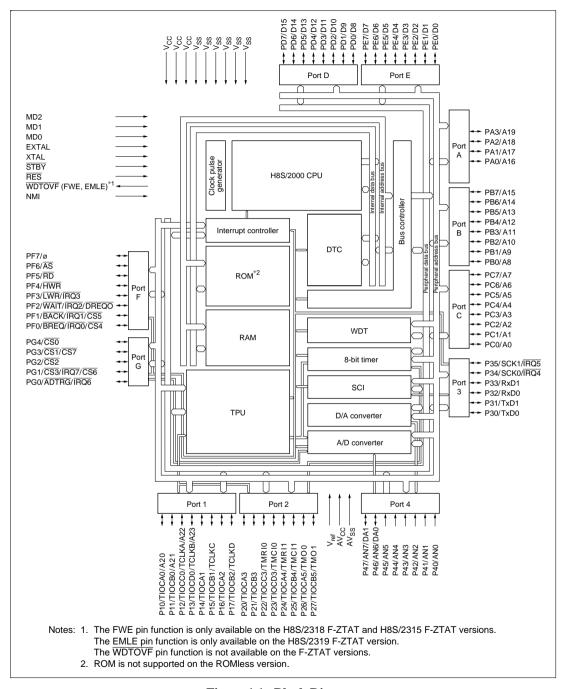

| 6               | 1.2 Block Diagram                                       | Figure 1.1 Block Diagram  Note 1 amended due to the addition of WDTOVF (FWE, EMLE).                                                                                                           |

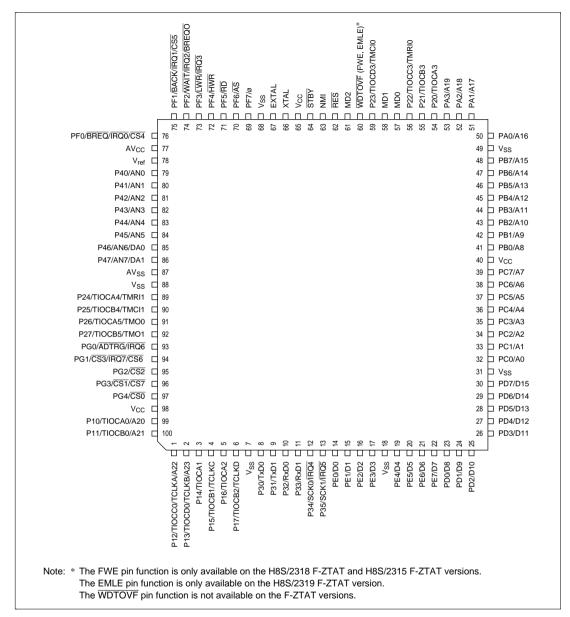

| 7               | 1.3 Pin Arrangement                                     | Figure 1.2 Pin Arrangement  Note amended due to the addition of WDTOVF  (FWE, EMLE).                                                                                                          |

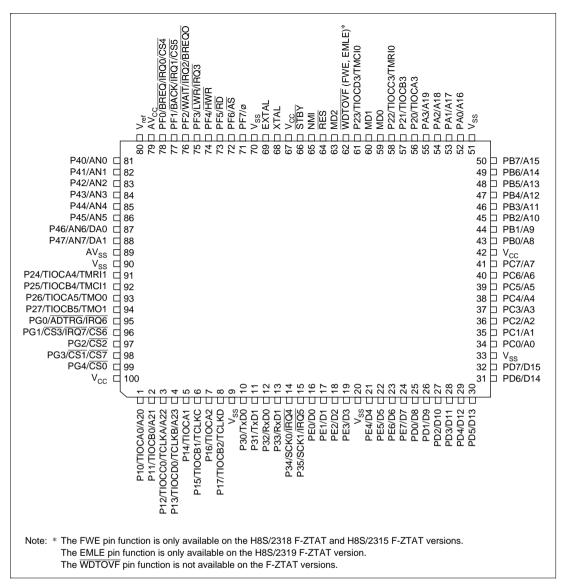

| 8               |                                                         | Figure 1.3 Pin Arrangement  Note amended due to the addition of WDTOVF  (FWE, EMLE).                                                                                                          |

| 10              | 1.4 Pin Functions in Each<br>Operating Mode             | Table 1.2 Pin Functions in Each Operating Mode Functions for pins 32 to 39, 41 to 48, and 50 to 52 (TFP-100B) in flash memory programmer mode amended. Function for pin 60 (TFP-100B) amended |

| 12              |                                                         | Note 3 amended.                                                                                                                                                                               |

| 15              | 1.5 Pin Functions                                       | Table 1.3 Pin Functions EMLE pin added.                                                                                                                                                       |

| 19              |                                                         | Note 4 added.                                                                                                                                                                                 |

| 20              | 1.6 Product Lineup                                      | Note 2 added.                                                                                                                                                                                 |

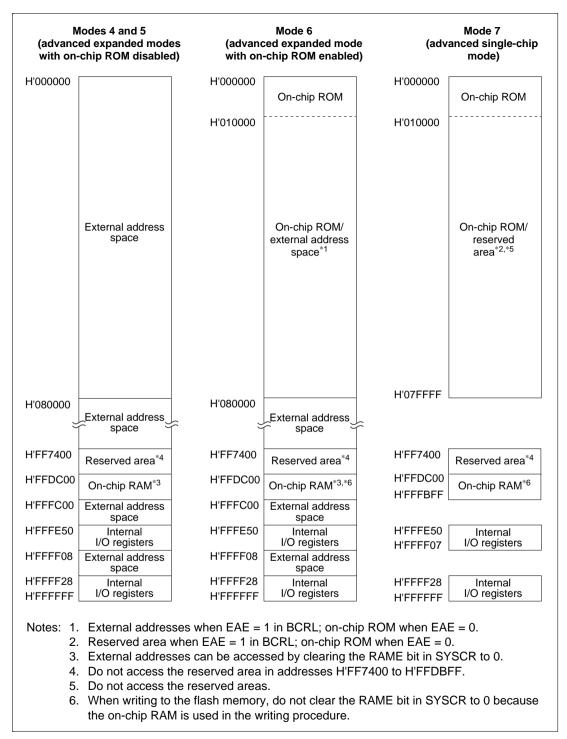

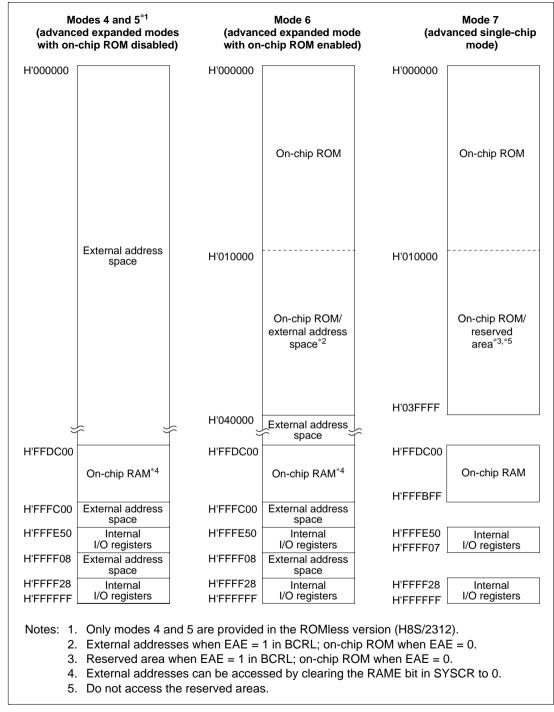

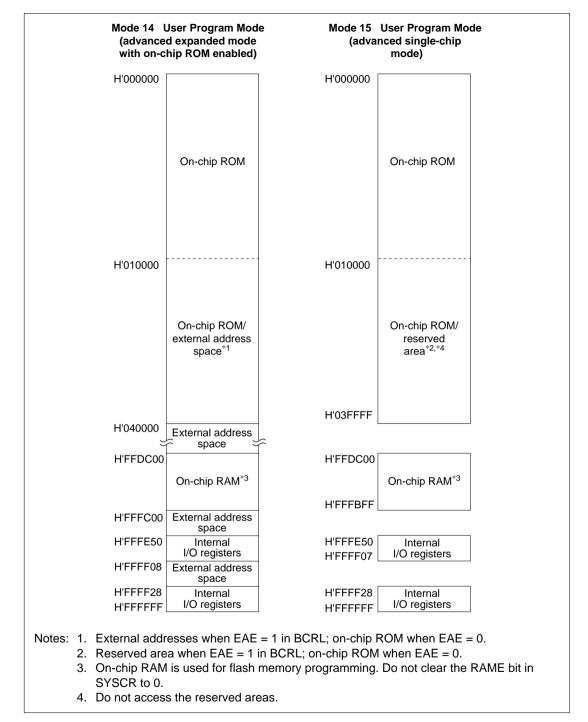

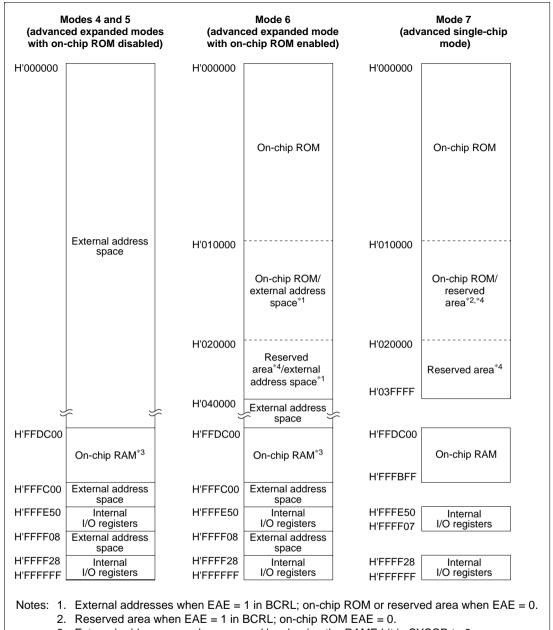

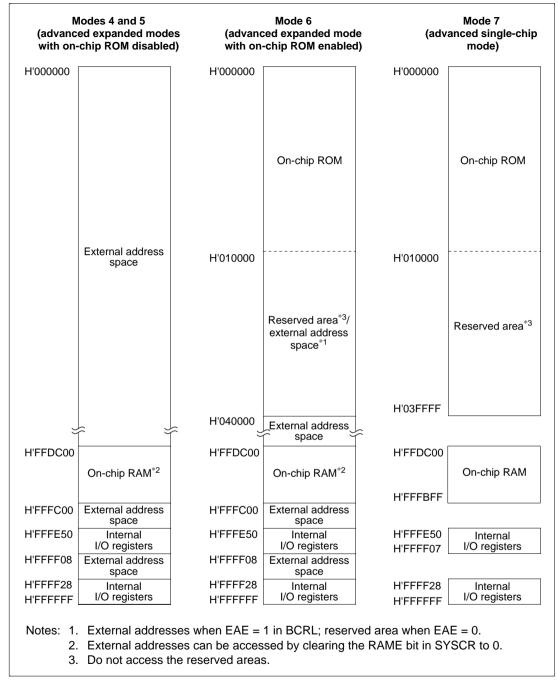

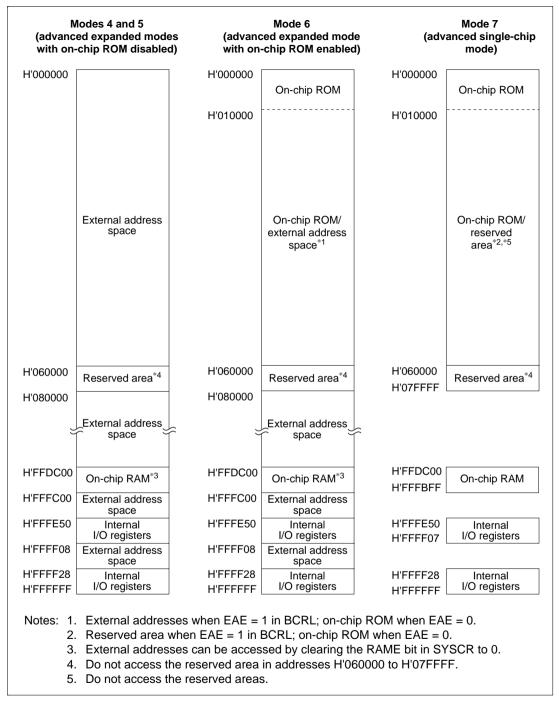

| 32              | 2.5 Memory Map in Each Operating Mode                   | Figure 2.1 H8S/2319 F-ZTAT Memory Map in Each Operating Mode added.                                                                                                                           |

| 33 to 36,<br>42 |                                                         | Figures 2.2, 2.3, and 2.7 Memory Map in Each Operating Mode Note on reserved area added.                                                                                                      |

| 37              |                                                         | Figure 2.4 H8S/2316 Memory Map in Each Operating Mode added.                                                                                                                                  |

| 38 to 40        |                                                         | Figure 2.5 H8S/2315 F-ZTAT Memory Map in Each Operating Mode added.                                                                                                                           |

| 41              |                                                         | Figure 2.6 H8S/2313 Memory Map in Each Operating Mode added.                                                                                                                                  |

| _               | 2.6 H8S/2318 Series Operating<br>Modes (F-ZTAT Version) | Deleted (see the hardware manual).                                                                                                                                                            |

| Page          | Item                                                                                                      | Revisions (See Manual for Details)                                                                                                                                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 51            | 3.3.3 Interrupt Exception Vector Table                                                                    | Table 3.3 Interrupt Sources, Vector Addresses, and Interrupt Priorities Names for SCI interrupts RXI0 and RXI1 amended.                                                                                                                                                                        |

| 54            | 3.5 Interrupt Response Times                                                                              | Table 3.8 Interrupt Response Times Number of wait states until execution instruction ends amended.                                                                                                                                                                                             |

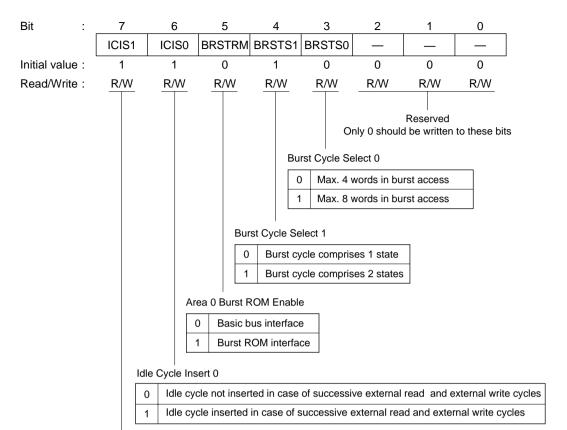

| 73            | 4.2.5 Bus Control Register L (BCRL)                                                                       | Description of bit 5<br>H8S/2319, H8S/2316, H8S/2315, and H8S/2313<br>added                                                                                                                                                                                                                    |

| 177           | 5.13 Pin States                                                                                           | Table 5.23 I/O Port States in Each Processing State LWROD and DAOEn added to Legend.                                                                                                                                                                                                           |

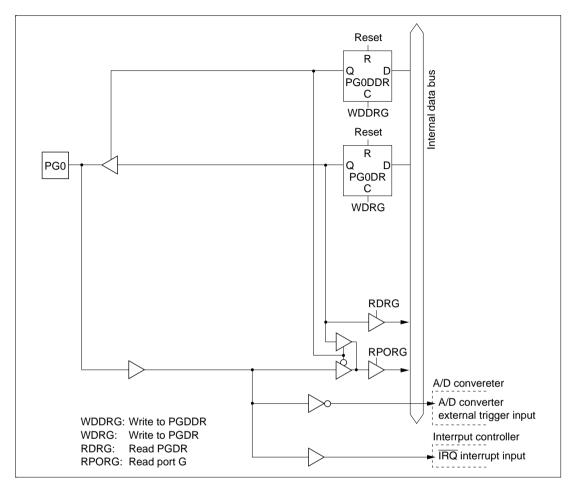

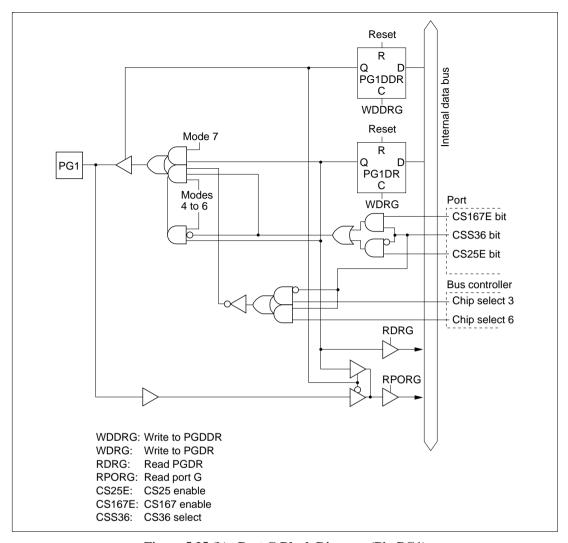

| 200           | 5.14.11 Port G                                                                                            | Figure 5.35(a) Port G Block Diagram (Pin PG0) Amended.                                                                                                                                                                                                                                         |

| 225           | 6.11 ROM                                                                                                  | Amended due to the addition of the H8S/2319 F-ZTAT to the product lineup.                                                                                                                                                                                                                      |

| 252           | 7.1.4 A/D Conversion<br>Characteristics                                                                   | Table 7.8 A/D Conversion Characteristics<br>Nonlinearity error, offset error, full-scale error,<br>quantization error, and absolute accuracy<br>amended.                                                                                                                                       |

| 254 to<br>262 | 7.2 Electrical Characteristics of<br>Mask ROM Version (H8S/2318,<br>H8S/2317) in Low-Voltage<br>Operation | Added.                                                                                                                                                                                                                                                                                         |

| 263           | 7.3 Electrical Characteristics of F-ZTAT Version (H8S/2318)                                               | Table 7.19 Absolute Maximum Ratings Conditions A and B added. Note amended.                                                                                                                                                                                                                    |

| 264 to<br>267 | 7.3.2 DC Characteristics                                                                                  | Tables 7.20 (a) and (b) DC Characteristics Maximum value of input leakage current, typical and maximum values of current dissipation, typical and maximum values of analog power supply voltage, typical and maximum values of reference power supply voltage, and equation in note 4 amended. |

| _             | 7.3.3 AC Characteristics                                                                                  | Table 7.25 Timing of On-Chip Supporting Modules WDT overflow output delay time deleted.                                                                                                                                                                                                        |

| 275           | 7.3.4 A/D Conversion<br>Characteristics                                                                   | Table 7.26 A/D Conversion Characteristics<br>Nonlinearity error, offset error, full-scale error,<br>quantization error, and absolute accuracy<br>amended.                                                                                                                                      |

### **HITACHI**

| Page          | Item                                                        | Revisions (See Manual for Details)                                                                                                           |

|---------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 277 to<br>280 | 7.3.6 Flash Memory<br>Characteristics                       | Tables 7.28 (a) and (b) Flash Memory Characteristics Completely replaced.                                                                    |

| 281 to<br>298 | 7.4 Electrical Characteristics of F-ZTAT Version (H8S/2315) | Added.                                                                                                                                       |

| _             |                                                             | 7.3.1 Notes when Converting the F-ZTAT Application Software to the Mask-ROM Versions (in the 1st Edition) Deleted (see the hardware manual). |

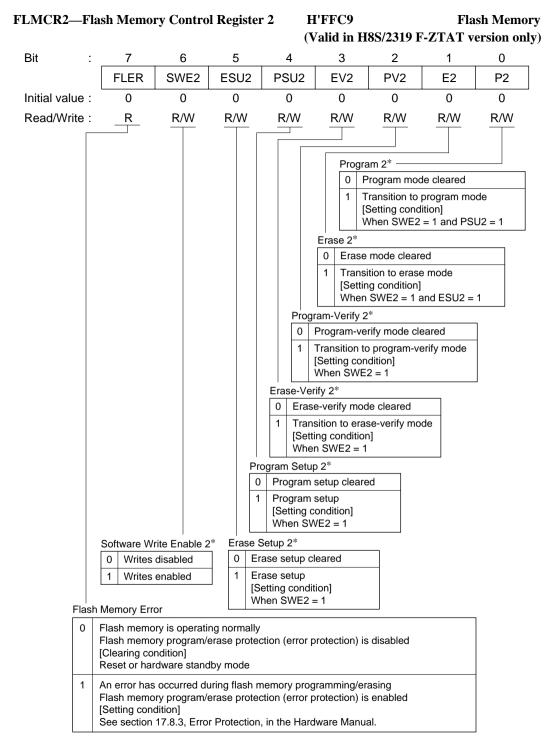

| 305           | 8.1 List of Registers (Address Order)                       | H'FFC8: FLMCR1<br>H'FFC9: FLMCR2<br>H'FFCB: EBR2<br>Amended.                                                                                 |

| 345           | 8.3 Functions                                               | H'FED5: BCRL Description of bit 5 amended.                                                                                                   |

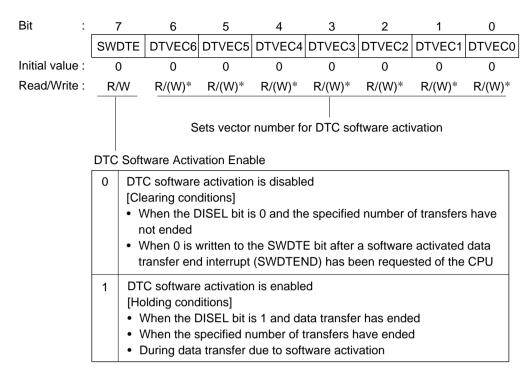

| 351           |                                                             | H'FF37: DTVECR Description of bit 7 amended.                                                                                                 |

| 402, 403      |                                                             | H'FFC8: FLMCR1<br>Amended.                                                                                                                   |

| 404, 405      |                                                             | H'FFC9: FLMCR2<br>Amended.                                                                                                                   |

| 406           |                                                             | H'FFCB: EBR2<br>Amended.                                                                                                                     |

# Organization of H8S/2319, H8S/2318 Series Reference Manual

The following manuals are available for H8S/2319, H8S/2318 Series.

Table 1 Manuals

| Title                                                                                                                | Document Code                    |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------|

| H8S/2600 Series, H8S/2000 Series Programming Manual                                                                  | ADE-602-083A                     |

| H8S/2339 Series, H8S/2338 Series, H8S/2329 Series, H8S/2328 Series, H8S/2319 Series, H8S/2318 Series Hardware Manual | ADE-602-171A<br>(in preparation) |

| H8S/2319, H8S/2318 Series, H8S/2319 F-ZTAT™, H8S/2318 F-ZTAT™, H8S/2315 F-ZTAT™ Reference Manual                     | ADE-602-188A                     |

The H8S/2600 Series, H8S/2000 Series Programming Manual gives a detailed description of the architecture and instruction set of the H8S/2000 CPU.

The H8S/2339 Series, H8S/2338 Series, H8S/2329 Series, H8S/2328 Series, H8S/2319 Series, H8S/2318 Series Hardware Manual describes the operation of on-chip functions, and gives a detailed description of the related registers.

The H8S/2319, H8S/2318 Series, H8S/2319 F-ZTAT<sup>TM</sup>, H8S/2318 F-ZTAT<sup>TM</sup>, H8S/2315 F-ZTAT<sup>TM</sup> Reference Manual mainly covers information specific to H8S/2319, H8S/2318 Series and H8S/2318 F-ZTAT<sup>TM</sup> products, including pin arrangement, I/O ports, MCU operating modes (address maps), interrupt vectors, bus control, and electrical characteristics, and also includes a brief description of all I/O registers for the convenience of the user.

The contents of H8S/2339 Series, H8S/2338 Series, H8S/2329 Series, H8S/2328 Series, H8S/2319 Series, H8S/2318 Series Hardware Manual and the H8S/2319, H8S/2318 Series, H8S/2319 F-ZTAT<sup>TM</sup>, H8S/2318 F-ZTAT<sup>TM</sup>, H8S/2315 F-ZTAT<sup>TM</sup> Reference Manual are summarized in table 2.

Table 2 Contents of Hardware Manual and Reference Manual

| No. | Item                                                               | Hardware<br>Manual | Reference<br>Manual                           |

|-----|--------------------------------------------------------------------|--------------------|-----------------------------------------------|

| 1   | Overview                                                           | 0                  | <ul><li>(including pin arrangement)</li></ul> |

| 2   | MCU operating modes (including address maps)                       | <del></del>        | 0                                             |

| 3   | Exception handling                                                 | 0                  | 0                                             |

| 4   | Interrupt controller                                               | 0                  | 0                                             |

| 5   | Bus controller                                                     | 0                  | 0                                             |

| 6   | DMA controller (DMAC)                                              | 0                  | <del></del>                                   |

| 7   | Data transfer controller (DTC)                                     | 0                  |                                               |

| 8   | 16-bit timer pulse unit (TPU)                                      | 0                  |                                               |

| 9   | Programmable pulse generator (PPG)                                 | 0                  | <del>_</del>                                  |

| 10  | 8-bit timers                                                       | 0                  | <u> </u>                                      |

| 11  | Watchdog timer                                                     | 0                  | <del></del>                                   |

| 12  | Serial communication interface (SCI)                               | 0                  | _                                             |

| 13  | Smart card interface                                               | 0                  |                                               |

| 14  | A/D converter                                                      | 0                  | <del></del>                                   |

| 15  | D/A converter                                                      | 0                  | _                                             |

| 16  | RAM                                                                | 0                  | <del></del>                                   |

| 17  | ROM (flash memory)                                                 | 0                  | <del></del>                                   |

| 18  | Clock pulse generator                                              | 0                  | _                                             |

| 19  | Power-down modes                                                   | 0                  |                                               |

| 20  | I/O ports (including port block diagrams)                          | <del></del>        | 0                                             |

| 21  | Electrical characteristics                                         | _                  | 0                                             |

| 22  | Register reference chart (in address order, with function summary) | _                  | 0                                             |

| 23  | Instruction set                                                    | 0                  |                                               |

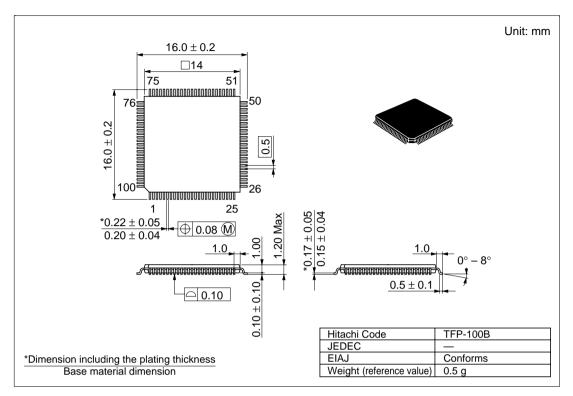

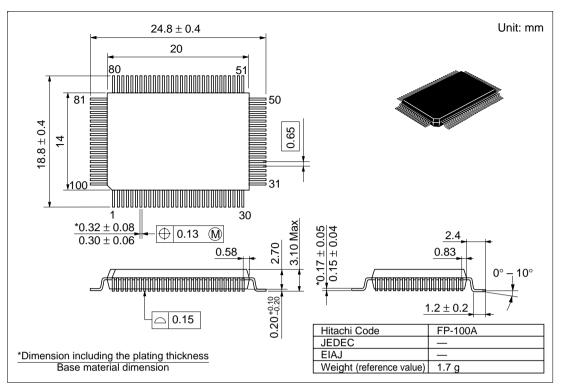

| 24  | Package dimension diagrams                                         | _                  | 0                                             |

O: Included

©: Included (with detailed register descriptions)

-: Not included

The following chart shows where to find various kinds of information for different purposes.

For product evaluation information, or comparative specification information for current users of Hitachi products

| For product specifications         |                                      |

|------------------------------------|--------------------------------------|

| Overview                           | 1.1 Overview                         |

| Pin arrangement diagram            | 1.3 Pin Arrangement                  |

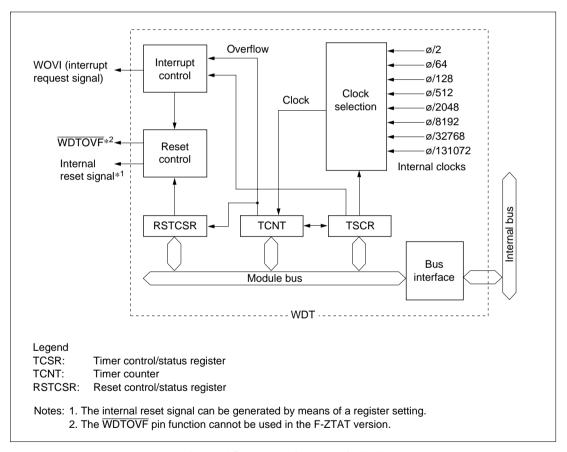

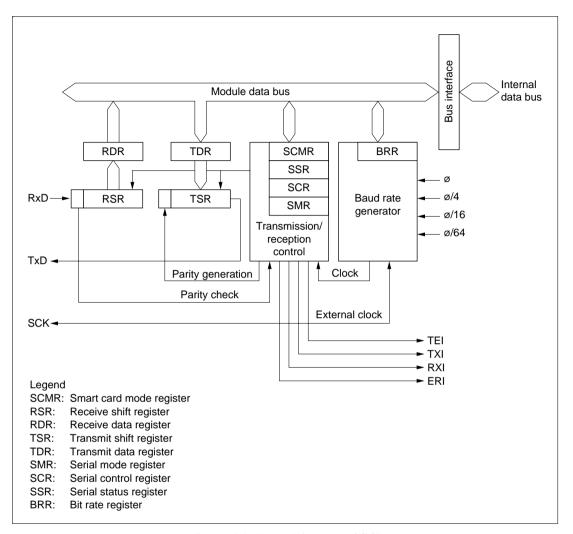

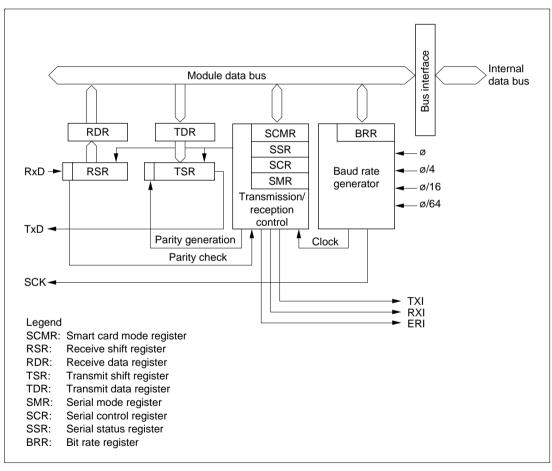

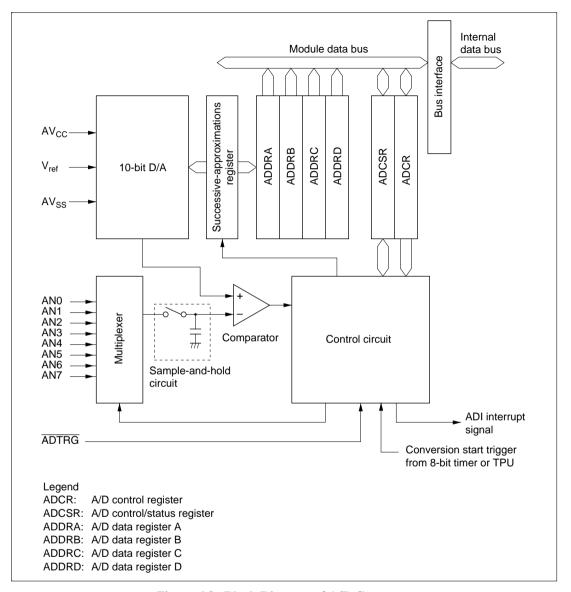

| Block diagrams of function modules | Section 6 Peripheral Block Diagrams  |

| Pin functions                      | 1.5 Pin Functions                    |

| Electrical characteristics         | Section 7 Electrical Characteristics |

For detailed information on functions

| I/O port information              |                           | Section 5 I/O Ports                                                                                                           |

|-----------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Interrupts and exception handling | _                         | Section 3 Exception Handling and Interrupt Controller                                                                         |

| Information on other modules      | _ <b>_</b> [\$\frac{1}{2} | H8S/2339 Series, H8S/2338 Series,<br>H8S/2329 Series, H8S/2328 Series,<br>H8S/2319 Series, H8S/2318 Series<br>Hardware Manual |

| Pin functions                     |                           | 1.5 Pin Functions                                                                                                             |

For use as design material

| List                                     | _ <b> </b> \$\frac{1}{2} | 1.4 Pin Functions in Each Operating Mode                            |

|------------------------------------------|--------------------------|---------------------------------------------------------------------|

| Detailed descriptions                    | <b>J</b>                 | Section 2 MCU Operating Modes                                       |

|                                          |                          |                                                                     |

| For information on registers             |                          |                                                                     |

| List                                     | <b>_</b>                 | Section 8 registers                                                 |

| To find a register from its address      | J\$                      | 8.1 List of Registers (Address Order)                               |

| To find register information by function | JS .                     | 8.2 List of Registers (By Module)                                   |

| Setting procedure and notes              | <b>_</b>                 | H8S/2339 Series, H8S/2338 Series, H8S/2329 Series, H8S/2328 Series, |

|                                          |                          | H8S/2319 Series, H8S/2318 Series                                    |

|                                          |                          | Hardware Manual                                                     |

| For information on instructions          |                          |                                                                     |

| List                                     | <b>_</b>                 |                                                                     |

| Operation description and notes          | _ <b>_</b>               | H8S/2600 Series, H8S/2000 Series<br>Programming Manual              |

| Program examples                         | <b>1</b>                 |                                                                     |

|                                          |                          |                                                                     |

#### **HITACHI**

The H8S/2339 Series, H8S/2338 Series, H8S/2329 Series, H8S/2328 Series, H8S/2319 Series, and H8S/2318 Series have the on-chip modules shown below

Table 3 H8S/2339, H8S/2338, H8S/2329, H8S/2328, H8S/2319, and H8S/2318 Series On-Chip Modules

| On-Chip Module                       | H8S/2339<br>H8S/2338 |                 |                 | H8S/2329 :      |                 |                 | H8S/2319<br>H8S/2318 |                 |                 |  |

|--------------------------------------|----------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------------|-----------------|-----------------|--|

| CPU                                  | 0                    |                 |                 | 0               |                 |                 | 0                    |                 |                 |  |

| Bus controller<br>(BUSC)             | 0                    |                 |                 | 0               | 0               |                 |                      | 0               |                 |  |

| DRAM controller                      | 0                    |                 |                 | 0               |                 |                 | ×                    |                 |                 |  |

| DMA controller<br>(DMAC)             | 0                    |                 |                 | 0               |                 |                 | ×                    |                 |                 |  |

| Data transfer controller (DTC)       | 0                    |                 |                 | 0               |                 |                 | 0                    |                 |                 |  |

| 16-bit timer pulse unit (TPU)        | O (6 chan            | inels)          |                 | O (6 chan       | nels)           |                 | ○ (6 char            | inels)          |                 |  |

| Programable pulse generator (PPG)    | 0                    |                 |                 | 0               |                 |                 | ×                    |                 |                 |  |

| 8-bit timer                          | O (2 char            | nnels)          |                 | O (2 chan       | (2 channels)    |                 |                      | (2 channels)    |                 |  |

| Watchdog timer                       | 0                    |                 |                 | 0               |                 |                 | 0                    |                 |                 |  |

| Serial communication interface (SCI) | ○ (3 char            | nnels)          |                 | (3 chan         | nels)           |                 | O (2 char            | nnels)          |                 |  |

| A/D converter                        | (12 cha              | annels)         |                 | (8 chan         | (8 channels)    |                 |                      | nels)           |                 |  |

| D/A converter                        | O (4 chan            | inels)          |                 | (2 channels)    |                 |                 | O (2 channels)       |                 |                 |  |

| Interrupt controller (INTC)          | 0                    |                 |                 | 0               |                 |                 | 0                    |                 |                 |  |

| Memory*                              | Product<br>Code      | ROM<br>(kbytes) | RAM<br>(kbytes) | Product<br>Code | ROM<br>(kbytes) | RAM<br>(kbytes) | Product<br>Code      | ROM<br>(kbytes) | RAM<br>(kbytes) |  |

|                                      | H8S/2339             | 384             | 32              | H8S/2329        | 384             | 32              | H8S/2319             | 512             | 8               |  |

|                                      | H8S/2338             | 256             | 8               | H8S/2328        | 256             | 8               | H8S/2318             | 256             | 8               |  |

|                                      | H8S/2337             | 128             | 8               | H8s/2327        | 128             | 8               | H8S/2317             | 128             | 8               |  |

|                                      | H8S/2332             | _               | 8               | H8S/2324        | _               | 32              | H8S/2316             | 64              | 8               |  |

|                                      |                      |                 |                 | H8S/2323        | 32              | 8               | H8S/2315             | 384             | 8               |  |

|                                      |                      |                 |                 | H8S/2322R       |                 | 8               | H8S/2313             | 64              | 2               |  |

|                                      |                      |                 |                 | H8S/2320        | _               | 4               | H8S/2312             |                 | 8               |  |

|                                      |                      |                 |                 |                 |                 |                 | H8S/2311             | 32              | 2               |  |

|                                      |                      |                 |                 |                 |                 |                 | H8S/2310             | _               | 2               |  |

O: On-chip

x: Not on-chip

Note: \* See the reference manual of each series for details.

## Contents

| Secti | on 1     | Overview                                                             | 1  |

|-------|----------|----------------------------------------------------------------------|----|

| 1.1   | Overvie  | 2W                                                                   | 1  |

| 1.2   | Block I  | Diagram                                                              | 6  |

| 1.3   | Pin Arr  | angement                                                             | 7  |

| 1.4   | Pin Fun  | actions in Each Operating Mode                                       | 9  |

| 1.5   | Pin Fun  | actions                                                              | 13 |

| 1.6   | Product  | Lineup                                                               | 20 |

| 1.7   | Package  | e Dimensions                                                         | 21 |

| Secti | on 2     | MCU Operating Modes                                                  | 23 |

| 2.1   |          | PW                                                                   | 23 |

|       | 2.1.1    | Operating Mode Selection                                             |    |

|       |          | (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions)                       | 23 |

|       | 2.1.2    | Operating Mode Selection                                             |    |

|       |          | (Mask ROM, ROMless, and H8S/2319 F-ZTAT Versions)                    | 24 |

|       | 2.1.3 R  | egister Configuration                                                | 25 |

| 2.2   |          | r Descriptions                                                       | 26 |

|       | 2.2.1    | Mode Control Register (MDCR)                                         | 26 |

|       | 2.2.2    | System Control Register (SYSCR)                                      | 26 |

|       | 2.2.3    | System Control Register 2 (SYSCR2) (F-ZTAT Version Only)             | 28 |

| 2.3   | Operati  | ng Mode Descriptions                                                 | 28 |

|       | 2.3.1    | Modes 1 to 3                                                         | 28 |

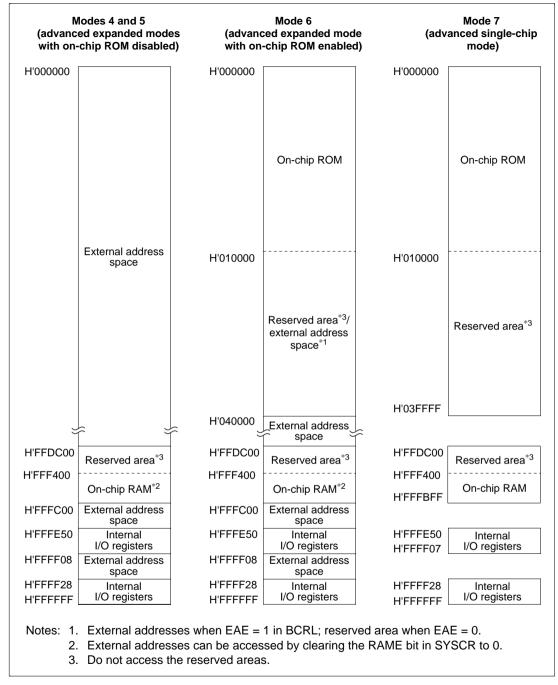

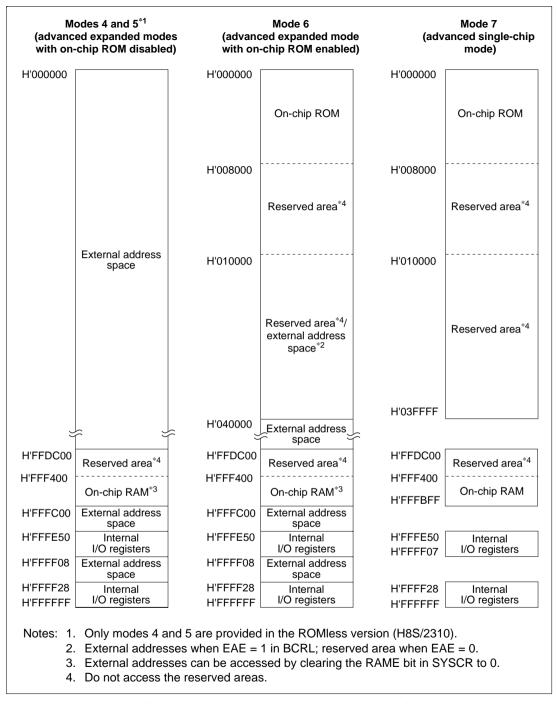

|       | 2.3.2    | Mode 4 (Expanded Mode with On-Chip ROM Disabled)                     | 28 |

|       | 2.3.3    | Mode 5 (Expanded Mode with On-Chip ROM Disabled)                     | 29 |

|       | 2.3.4    | Mode 6 (Expanded Mode with On-Chip ROM Enabled)                      | 29 |

|       | 2.3.5    | Mode 7 (Single-Chip Mode)                                            | 29 |

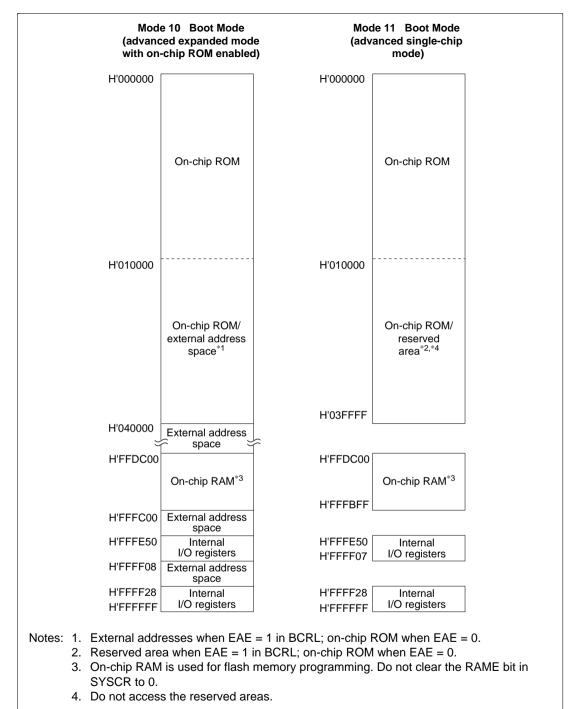

|       | 2.3.6    | Modes 8 and 9 (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions Only)    | 29 |

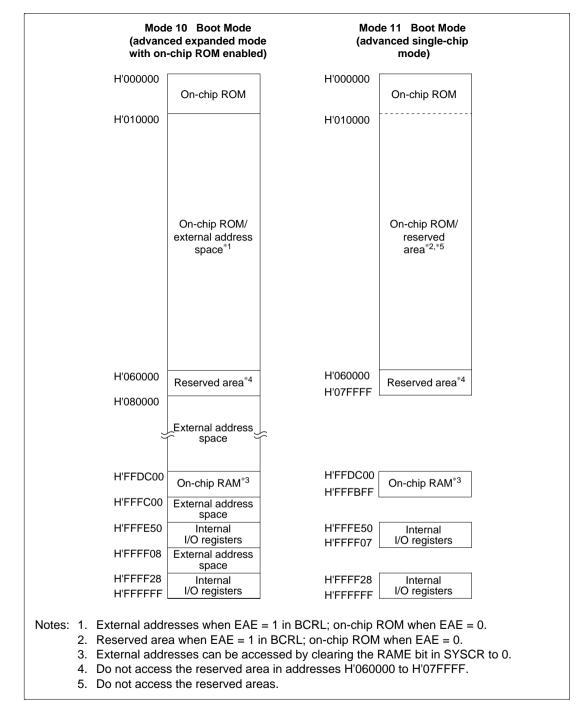

|       | 2.3.7    | Mode 10 (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions Only)          | 30 |

|       | 2.3.8    | Mode 11 (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions Only)          | 30 |

|       | 2.3.9    | Modes 12 and 13 (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions Only). | 30 |

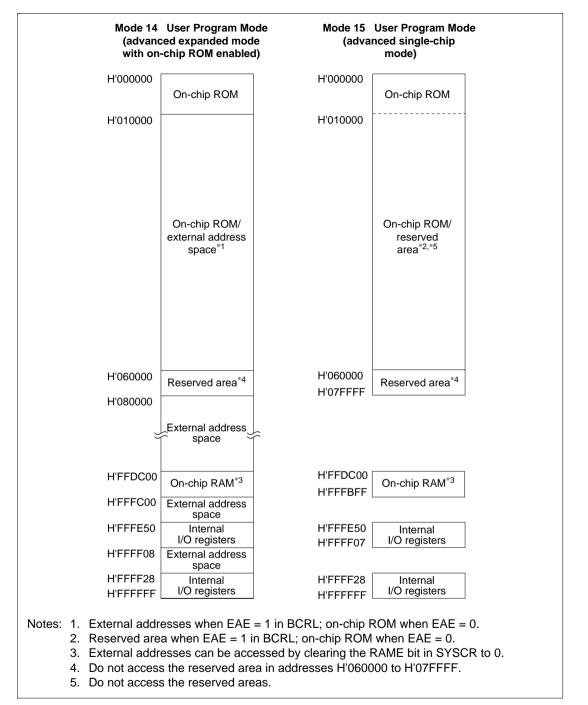

|       | 2.3.10   | Mode 14 (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions Only)          | 30 |

|       | 2.3.11   | Mode 15 (H8S/2318 F-ZTAT and H8S/2315 F-ZTAT Versions Only)          | 30 |

| 2.4   | Pin Fun  | actions in Each Operating Mode                                       | 31 |

| 2.5   | Memor    | y Map in Each Operating Mode                                         | 31 |

| Secti | on 3     | Exception Handling and Interrupt Controller                          | 43 |

| 3.1   |          | ew                                                                   | 43 |

|       | 3.1.1    | Exception Handling Types and Priority                                | 43 |

| 3.2   | Interrup | ot Controller                                                        | 44 |

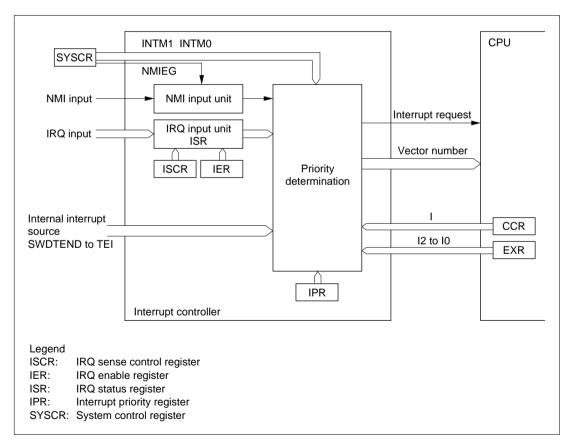

|       | 3.2.1   | Interrupt Controller Features               | 4  |

|-------|---------|---------------------------------------------|----|

|       | 3.2.2   | Pin Configuration                           | 4  |

| 3.3   | Interru | pt Sources                                  | 4  |

|       | 3.3.1   | External Interrupts                         | 4: |

|       | 3.3.2   | Internal Interrupts                         | 4  |

|       | 3.3.3   | Interrupt Exception Vector Table            | 4  |

| 3.4   | Interru | pt Control Modes and Interrupt Operation    | 5  |

| 3.5   |         | pt Response Times                           | 54 |

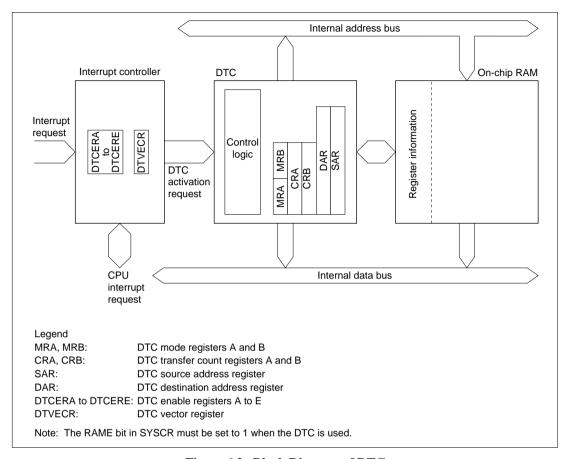

| 3.6   | DTC A   | ctivation by Interrupt                      | 5: |

|       | 3.6.1   | Overview                                    | 5: |

|       | 3.6.2   | Block Diagram                               | 5: |

|       | 3.6.3   | Operation                                   | 5  |

|       |         |                                             |    |

| Secti | on 4    | Bus Controller                              | 6  |

| 4.1   | Overvi  | ew                                          | 6  |

|       | 4.1.1   | Features                                    | 6  |

|       | 4.1.2   | Block Diagram                               | 6  |

|       | 4.1.3   | Pin Configuration                           | 6. |

|       | 4.1.4   | Register Configuration                      | 6  |

| 4.2   | Registe | er Descriptions                             | 6  |

|       | 4.2.1   | Bus Width Control Register (ABWCR)          | 6  |

|       | 4.2.2   | Access State Control Register (ASTCR)       | 6  |

|       | 4.2.3   | Wait Control Registers H and L (WCRH, WCRL) | 6  |

|       | 4.2.4   | Bus Control Register H (BCRH)               | 7  |

|       | 4.2.5   | Bus Control Register L (BCRL)               | 7  |

| 4.3   | Overvi  | ew of Bus Control                           | 7  |

|       | 4.3.1   | Area Partitioning                           | 7  |

|       | 4.3.2   | Bus Specifications                          | 7  |

|       | 4.3.3   | Memory Interfaces                           | 7  |

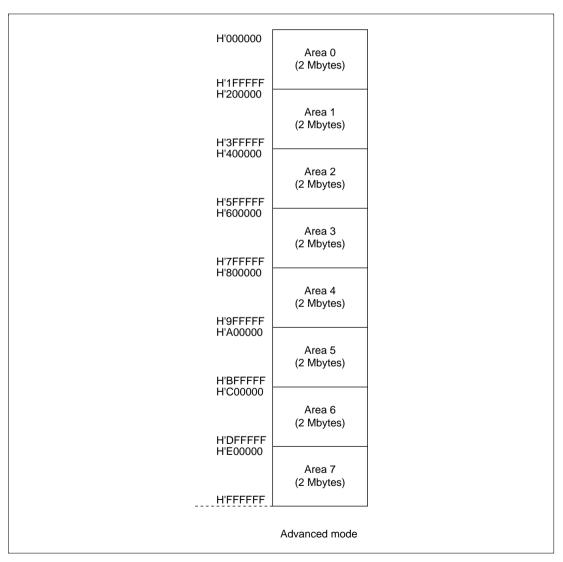

|       | 4.3.4   | Advanced Mode                               | 7  |

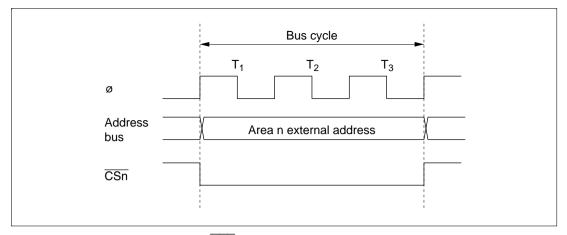

|       | 4.3.5   | Chip Select Signals                         | 7  |

| 4.4   | Basic E | Bus Interface                               | 7  |

|       | 4.4.1   | Overview                                    | 7  |

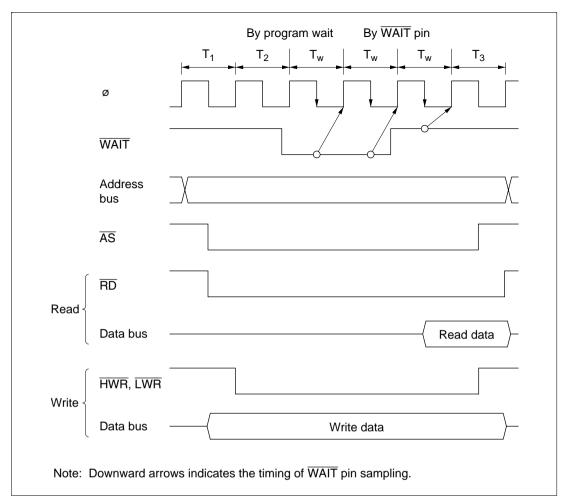

|       | 4.4.2   | Wait Control                                | 79 |

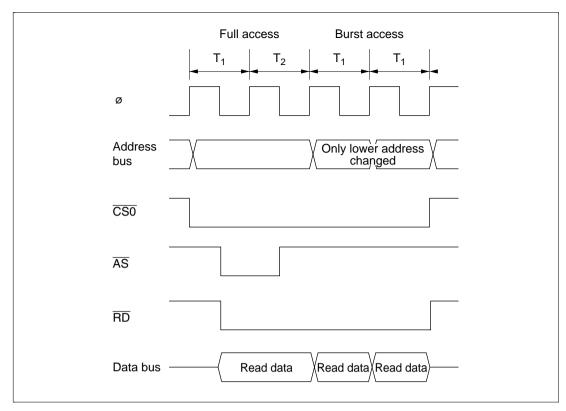

| 4.5   | Burst R | COM Interface                               | 8  |

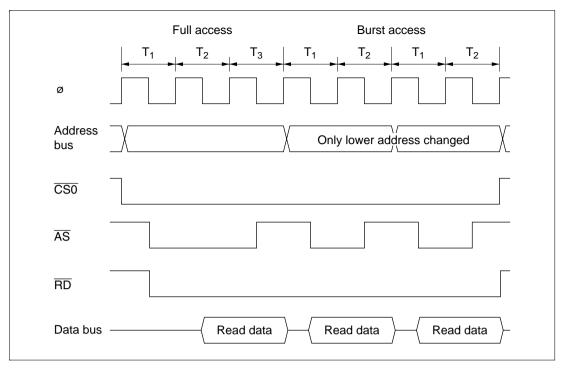

|       | 4.5.1   | Overview                                    | 8  |

|       | 4.5.2   | Basic Timing                                | 8  |

|       | 4.5.3   | Wait Control                                | 8. |

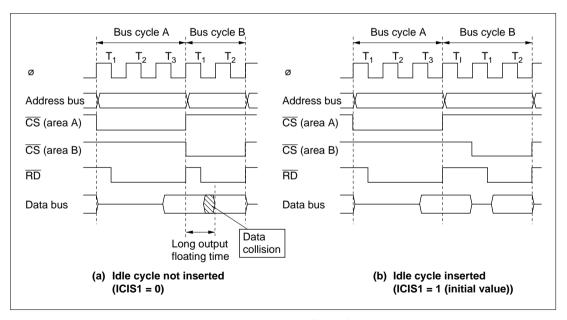

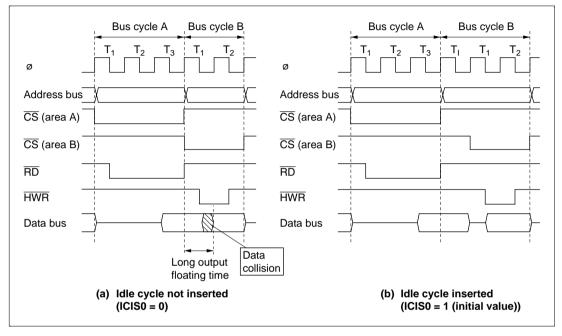

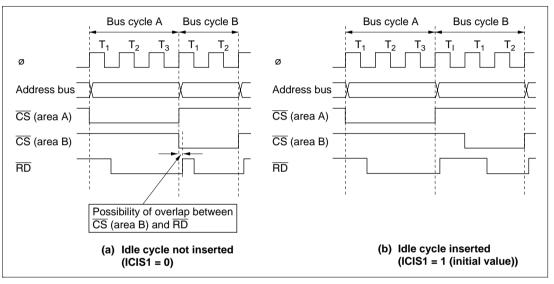

| 4.6   | Idle Cy | rcle                                        | 84 |

|       | 4.6.1   | Operation                                   | 8  |

|       | 4.6.2   | Pin States in Idle Cycle                    | 8  |

| 4.7   | Bus Re  | lease                                       | 8  |

|       | 4.7.1   | Overview                                    | 8  |

| ii    |         |                                             |    |

|       |         |                                             |    |

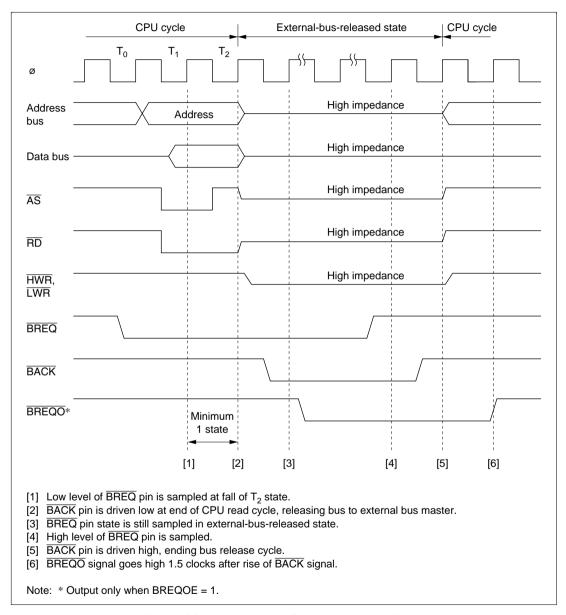

|      | 4.7.2   | Operation                                 | 87   |

|------|---------|-------------------------------------------|------|

|      | 4.7.3   | Pin States in External-Bus-Released State | 88   |

|      | 4.7.4   | Transition Timing                         | 89   |

|      | 4.7.5   | Usage Note                                | 90   |

| 4.8  | Bus Ar  | bitration                                 | 90   |

|      | 4.8.1   | Overview                                  | 90   |

|      | 4.8.2   | Operation                                 | 90   |

|      | 4.8.3   | Bus Transfer Timing                       | 90   |

|      | 4.8.4   | Note on Use of External Bus Release       | 91   |

| 4.9  | Bus Co  | ontroller Operation in a Reset            | 91   |

|      |         |                                           |      |

| Sect | ion 5   | I/O Ports                                 | 93   |

| 5.1  | Overvi  | ew                                        | 93   |

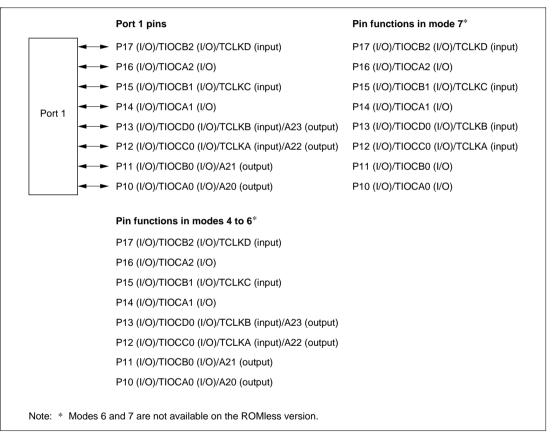

| 5.2  | Port 1. |                                           | 98   |

|      | 5.2.1   | Overview                                  | 98   |

|      | 5.2.2   | Register Configuration                    | 99   |

|      | 5.2.3   | Pin Functions.                            | 101  |

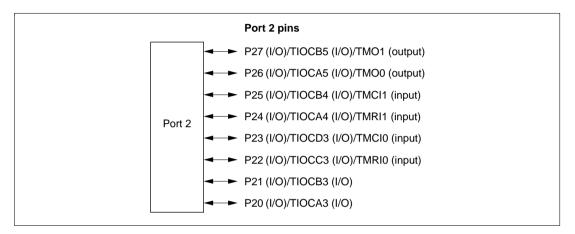

| 5.3  | Port 2. |                                           | 110  |

|      | 5.3.1   | Overview                                  | 110  |

|      | 5.3.2   | Register Configuration                    | 110  |

|      | 5.3.3   | Pin Functions.                            | 112  |

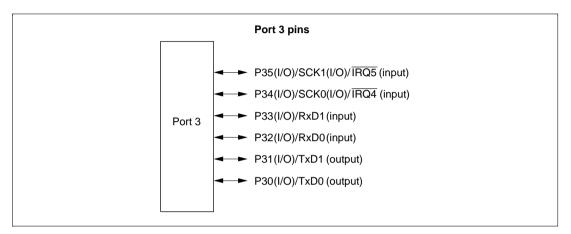

| 5.4  | Port 3. |                                           | 120  |

|      | 5.4.1   | Overview                                  | 120  |

|      | 5.4.2   | Register Configuration                    |      |

|      | 5.4.3   | Pin Functions.                            |      |

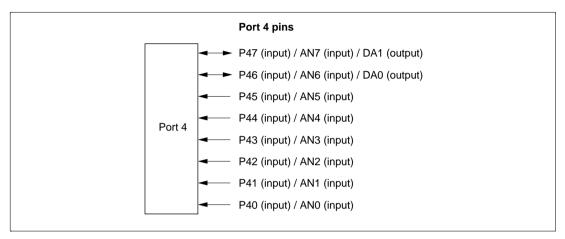

| 5.5  | Port 4. |                                           | 125  |

|      | 5.5.1   | Overview                                  | 125  |

|      | 5.5.2   | Register Configuration                    | 125  |

|      | 5.5.3   | Pin Functions.                            |      |

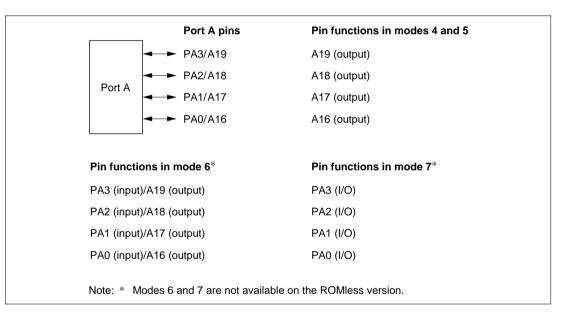

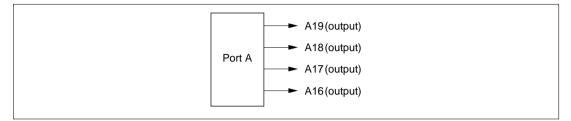

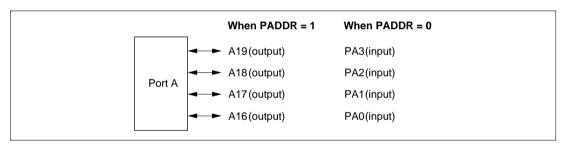

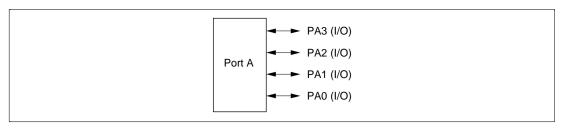

| 5.6  | Port A  |                                           |      |

|      | 5.6.1   | Overview                                  | 126  |

|      | 5.6.2   | Register Configuration                    |      |

|      | 5.6.3   | Pin Functions.                            |      |

|      | 5.6.4   | MOS Input Pull-Up Function                |      |

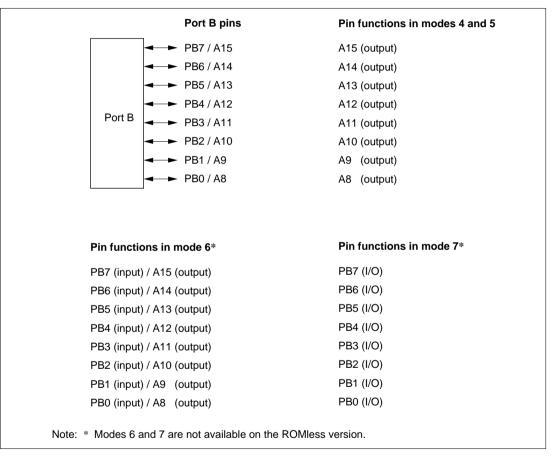

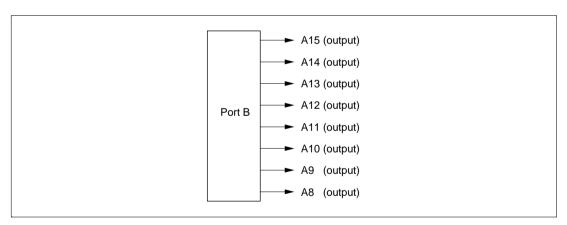

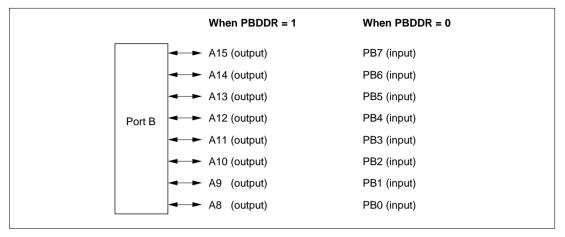

| 5.7  | Port B  | •                                         |      |

|      | 5.7.1   | Overview                                  |      |

|      | 5.7.2   | Register Configuration                    |      |

|      | 5.7.3   | Pin Functions                             |      |

|      | 5.7.4   | MOS Input Pull-Up Function                |      |

| 5.8  |         | 1 1                                       |      |

|      | 5.8.1   | Overview                                  |      |

|      | 5.8.2   | Register Configuration                    |      |

|      | 5.8.3   | Pin Functions.                            |      |

|      |         |                                           | ii   |

|      |         |                                           | - 11 |

| 5.9       Port D.       144         5.9.1       Overview.       144         5.9.2       Register Configuration       145         5.9.3       Pin Functions.       147         5.9.4       MOS Input Pull-Up Function       148         5.10       Port E.       150         5.10.1       Overview.       150         5.10.2       Register Configuration       151         5.10.3       Pin Functions.       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F.       156         5.11.1       Overview.       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions.       162         5.12.1       Overview.       165         5.12.1       Overview.       165         5.12.1       Port G.       165         5.12.1       Port G.       165         5.12.1       Port States in Each Mode       172         5.13.1       Port States in Each Mode       172         5.14.1       Port 1       178         5.14.2       Port 2       182         5.14.3       Port 3       183                                                                                                              |      | 5.8.4   | MOS Input Pull-Up Function       | . 143 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|----------------------------------|-------|

| 5.9.2       Register Configuration       145         5.9.3       Pin Functions       147         5.9.4       MOS Input Pull-Up Function       148         5.10       Port E       150         5.10.1       Overview       150         5.10.2       Register Configuration       151         5.10.3       Pin Functions       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview       156         5.11.2       Register Configuration       165         5.11.3       Pin Functions       162         5.12.1       Overview       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.3       Pin Functions       170         5.13       Port States       172         5.13.1       Port States in Each Mode       172         5.13       Port Block Diagrams       178         5.14.1       Port 1       178         5.14.2       Port 2       182         5.14.3       Port 3       183         5.14.4       Port 4       18                                                                                                       | 5.9  | Port D  |                                  | 144   |

| 5.9.3       Pin Functions.       147         5.9.4       MOS Input Pull-Up Function       148         5.10       Port E       150         5.10.1       Overview       150         5.10.2       Register Configuration       151         5.10.3       Pin Functions.       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions.       165         5.12.1       Overview       165         5.12.1       Overview       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.1       Port G       165         5.12.2       Register Configuration       166         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.1       Overview       165         5.12.2       Register Configurat                                                                                              |      | 5.9.1   | Overview                         | 144   |

| 5.9.3       Pin Functions.       147         5.9.4       MOS Input Pull-Up Function       148         5.10       Port E       150         5.10.1       Overview       150         5.10.2       Register Configuration       151         5.10.3       Pin Functions.       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions.       165         5.12.1       Overview       165         5.12.1       Overview       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.1       Port G       165         5.12.2       Register Configuration       166         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.1       Overview       165         5.12.2       Register Configurat                                                                                              |      | 5.9.2   | Register Configuration           | . 145 |

| 5.10       Port E       150         5.10.1       Overview.       150         5.10.2       Register Configuration       151         5.10.3       Pin Functions.       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview.       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions.       165         5.12.1       Poverview.       165         5.12.2       Register Configuration       166         5.12.3       Pin Functions.       170         5.13       Pin States.       172         5.14.1       Port States in Each Mode       172         5.14.1       Port States in Each Mode       172         5.14.1       Port Block Diagrams       178         5.14.2       Port 2       182         5.14.3       Port 2       182         5.14.4       Port 4       186         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190 <td></td> <td>5.9.3</td> <td></td> <td></td>                                                                        |      | 5.9.3   |                                  |       |

| 5.10.1       Overview       150         5.10.2       Register Configuration       151         5.10.3       Pin Functions       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.3       Pin Functions       170         5.13       Pin Functions       170         5.14       I/O Port Block Diagrams       172         5.14.1       Port States in Each Mode       172         5.14.1       Port I       178         5.14.2       Port 2       182         5.14.3       Port 1       178         5.14.4       Port 2       182         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190         5.14.9       Port E       191 <t< td=""><td></td><td>5.9.4</td><td>MOS Input Pull-Up Function</td><td>. 148</td></t<>                                                |      | 5.9.4   | MOS Input Pull-Up Function       | . 148 |

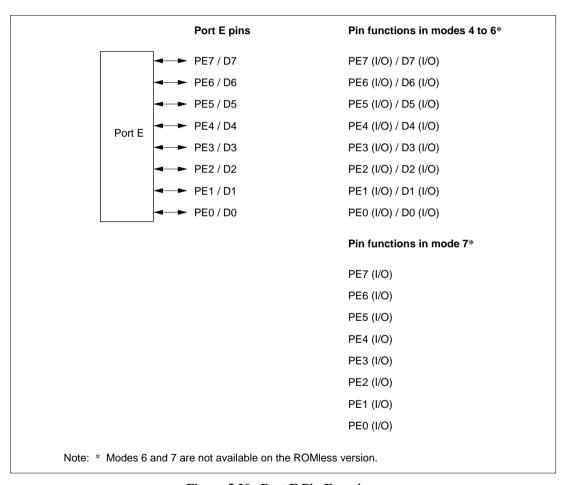

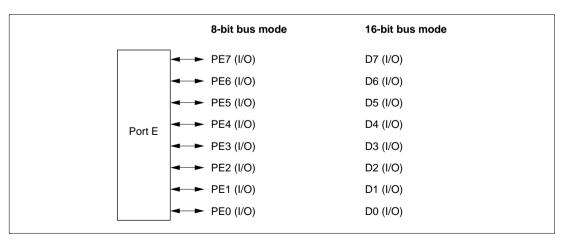

| 5.10.2       Register Configuration       151         5.10.3       Pin Functions       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.3       Pin Functions       170         5.13       Pin States       172         5.13.1       Port States in Each Mode       172         5.14.1       Port Block Diagrams       178         5.14.2       Port 1       178         5.14.2       Port 2       182         5.14.3       Port 3       183         5.14.4       Port 4       186         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190         5.14.9       Port E       191         5.14.10 Port F       192         5.14.11 Port G                                                                                                                             | 5.10 | Port E. |                                  | . 150 |

| 5.10.3       Pin Functions       153         5.10.4       MOS Input Pull-Up Function       154         5.11       Port F       156         5.11.1       Overview       156         5.11.2       Register Configuration       157         5.11.3       Pin Functions       162         5.12.1       Port G       165         5.12.2       Register Configuration       165         5.12.3       Pin Functions       170         5.13       Pin States       172         5.13.1       Port States in Each Mode       172         5.14.1       Port I       178         5.14.1       Port I       178         5.14.2       Port 2       182         5.14.3       Port 3       183         5.14.4       Port 4       186         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190         5.14.9       Port E       191         5.14.10       Port F       192         5.14.11       Port G       200         6.1.1       Features                                                                                                                                               |      | 5.10.1  | Overview                         | 150   |

| 5.10.4 MOS Input Pull-Up Function.       154         5.11 Port F.       156         5.11.2 Register Configuration.       157         5.11.3 Pin Functions       162         5.12 Port G.       165         5.12.1 Overview       165         5.12.2 Register Configuration       166         5.12.3 Pin Functions.       170         5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207 <td></td> <td>5.10.2</td> <td>Register Configuration</td> <td>. 151</td> |      | 5.10.2  | Register Configuration           | . 151 |

| 5.11 Port F       156         5.11.1 Overview       156         5.11.2 Register Configuration       157         5.11.3 Pin Functions       162         5.12 Port G       165         5.12.1 Overview       165         5.12.2 Register Configuration       166         5.12.3 Pin Functions       170         5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14.1 Port Block Diagrams       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       206         6.2 Data Transfer Controller       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208     <                                                                            |      | 5.10.3  | Pin Functions.                   | 153   |

| 5.11.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      | 5.10.4  | MOS Input Pull-Up Function       | . 154 |

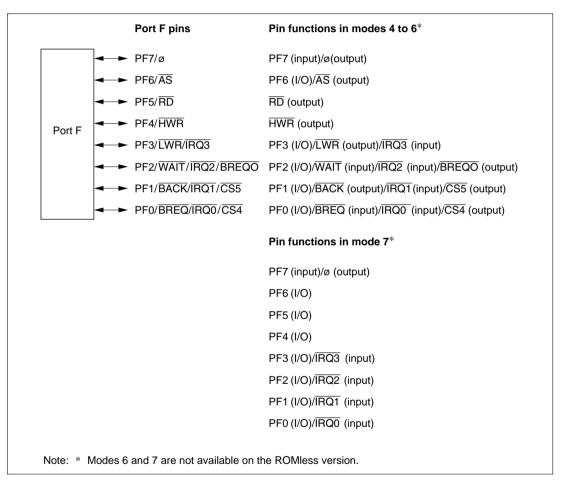

| 5.11.2       Register Configuration       157         5.11.3       Pin Functions       162         5.12       Port G       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.3       Pin Functions       170         5.13       Pin States       172         5.13.1       Port States in Each Mode       172         5.13.1       Port States in Each Mode       178         5.14.1       Port Port I       178         5.14.2       Port 2       182         5.14.3       Port 3       183         5.14.4       Port 3       183         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190         5.14.9       Port E       191         5.14.10       Port F       192         5.14.11       Port G       200         Section 6       Supporting Module Block Diagrams       205         6.1       Interrupt Controller       205         6.1.1       Features       205         <                                                                                                                             | 5.11 | Port F  |                                  | . 156 |

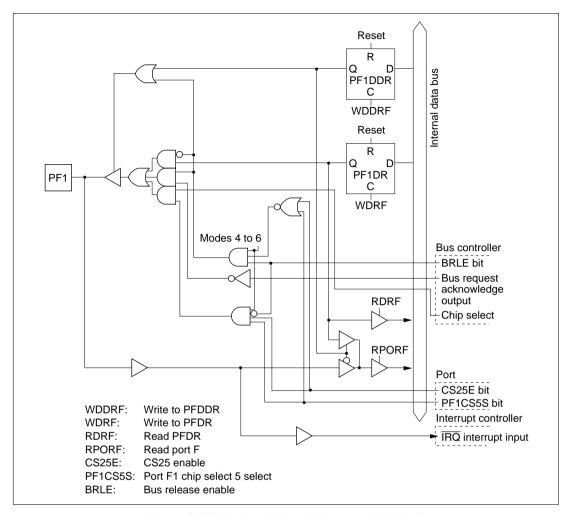

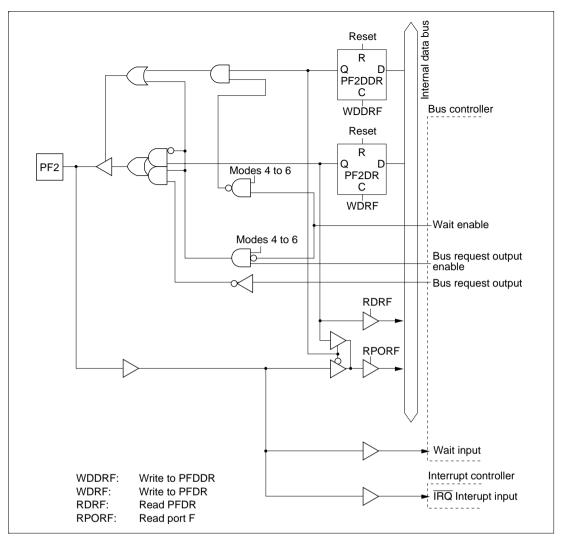

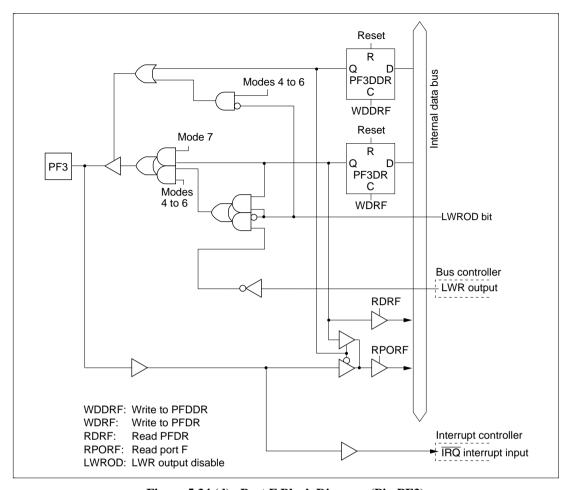

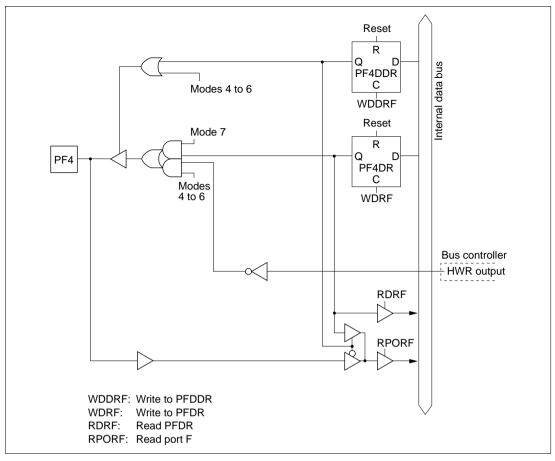

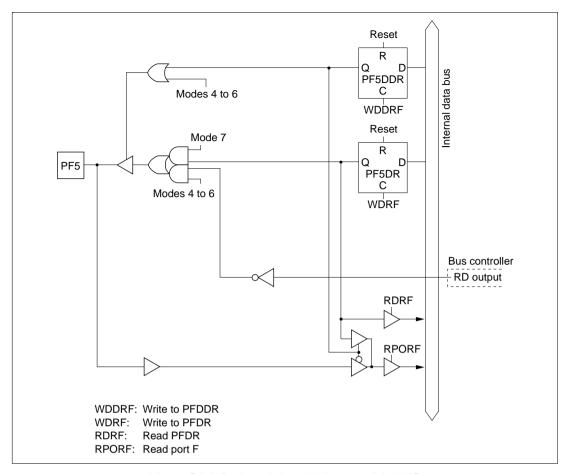

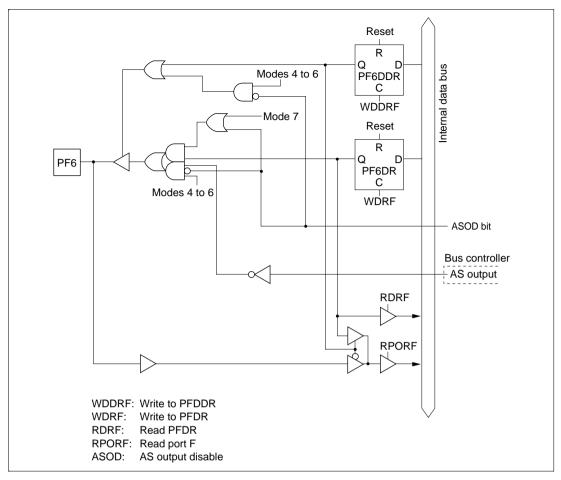

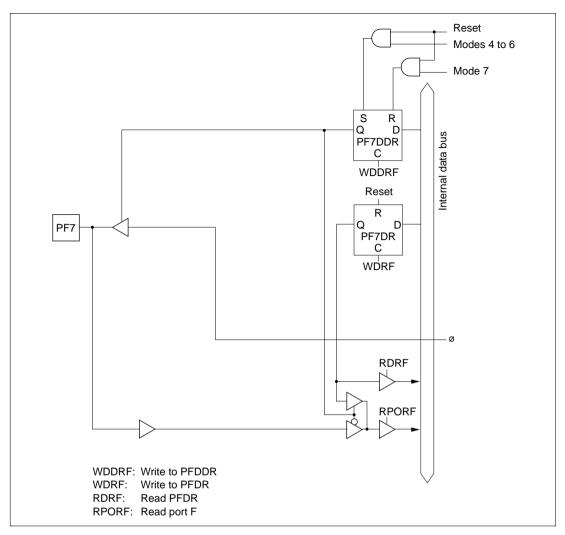

| 5.11.3 Pin Functions       162         5.12 Port G       165         5.12.1 Overview       165         5.12.2 Register Configuration       166         5.12.3 Pin Functions       170         5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208                                                                                                                               |      | 5.11.1  | Overview                         | 156   |

| 5.12       Port G       165         5.12.1       Overview       165         5.12.2       Register Configuration       166         5.12.3       Pin Functions       170         5.13       Pin States       172         5.13.1       Port States in Each Mode       172         5.14       I/O Port Block Diagrams       178         5.14.1       Port 1       178         5.14.2       Port 2       182         5.14.3       Port 3       183         5.14.4       Port 4       186         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190         5.14.9       Port E       191         5.14.10       Port F       192         5.14.11       Port G       200         Section 6       Supporting Module Block Diagrams       205         6.1       Interrupt Controller       205         6.1.1       Features       205         6.1.2       Block Diagram       205         6.2       Data Transfer Controller       206                                                                                                                                                 |      | 5.11.2  | Register Configuration           | . 157 |

| 5.12.1 Overview       165         5.12.2 Register Configuration       166         5.12.3 Pin Functions       170         5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                        |      | 5.11.3  | Pin Functions.                   | 162   |

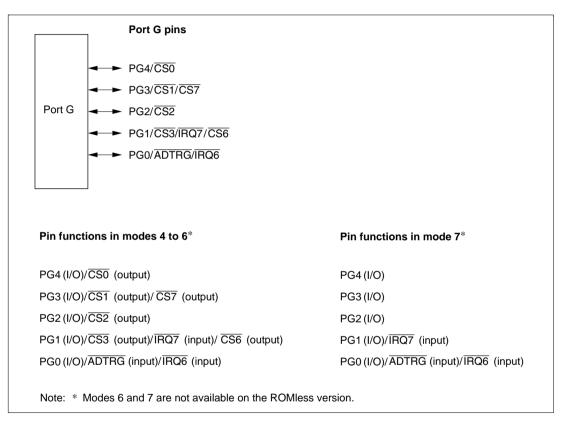

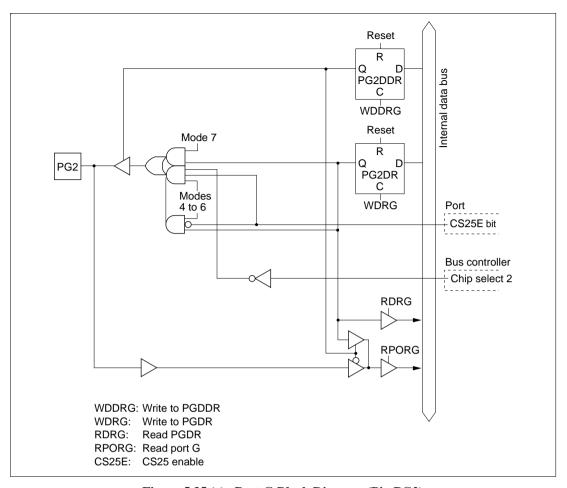

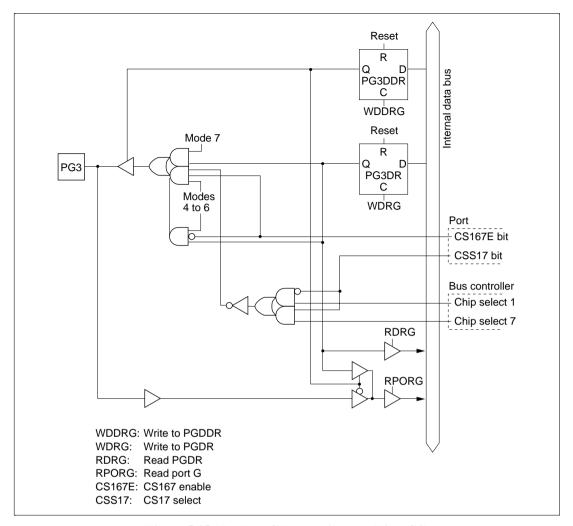

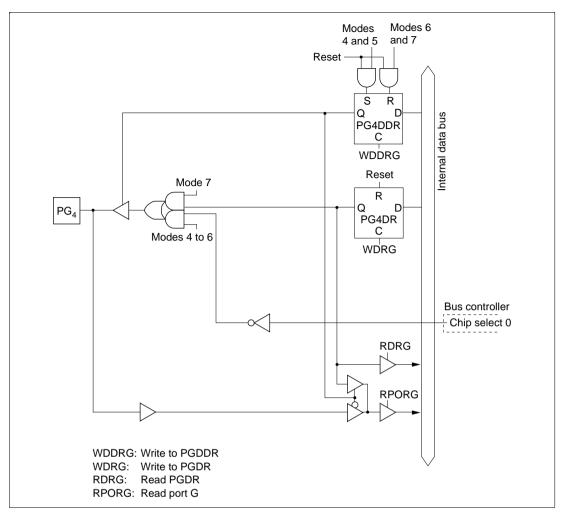

| 5.12.2 Register Configuration       166         5.12.3 Pin Functions.       170         5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                             | 5.12 | Port G  |                                  | 165   |

| 5.12.3 Pin Functions.       170         5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                                                                             |      | 5.12.1  | Overview                         | 165   |

| 5.13 Pin States       172         5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                                                                                                                     |      | 5.12.2  | Register Configuration           | . 166 |

| 5.13.1 Port States in Each Mode       172         5.14 I/O Port Block Diagrams       178         5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                                                                                                                                                   |      | 5.12.3  | Pin Functions.                   | 170   |

| 5.14       I/O Port Block Diagrams       178         5.14.1       Port 1       178         5.14.2       Port 2       182         5.14.3       Port 3       183         5.14.4       Port 4       186         5.14.5       Port A       187         5.14.6       Port B       188         5.14.7       Port C       189         5.14.8       Port D       190         5.14.9       Port E       191         5.14.10       Port F       192         5.14.11       Port G       200         Section 6       Supporting Module Block Diagrams       205         6.1       Interrupt Controller       205         6.1.1       Features       205         6.1.2       Block Diagram       205         6.1.3       Pins       206         6.2       Data Transfer Controller       206         6.2.1       Features       206         6.2.2       Block Diagram       207         6.3       16-Bit Timer Pulse Unit       208                                                                                                                                                                                                                                                      | 5.13 | Pin Sta | ites                             | . 172 |

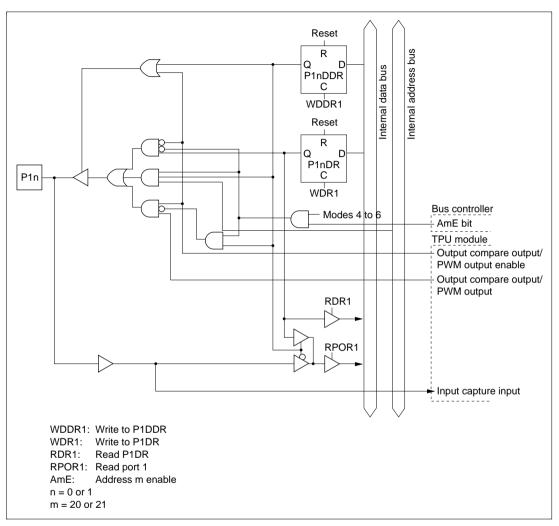

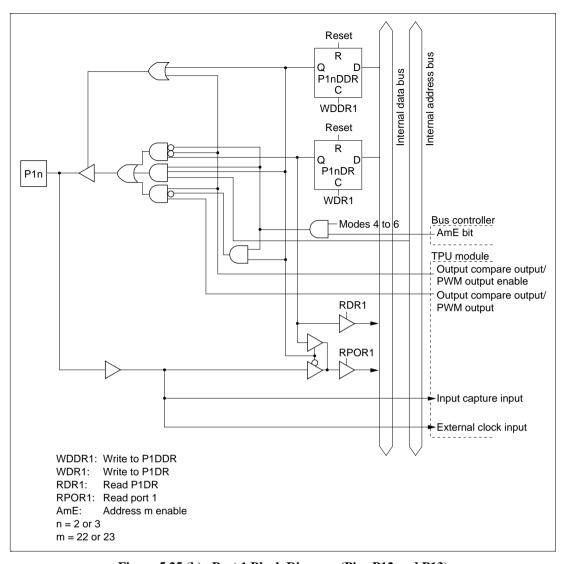

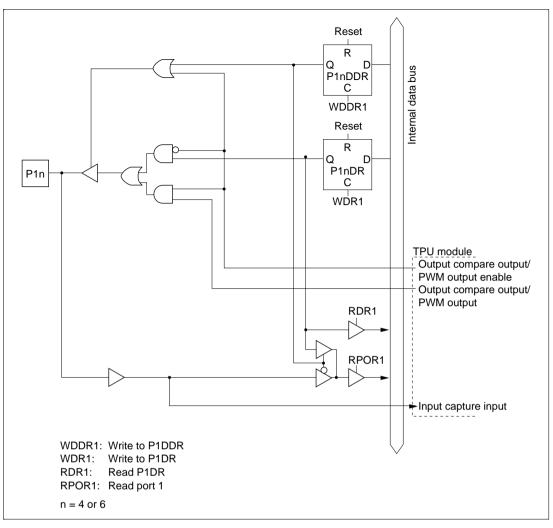

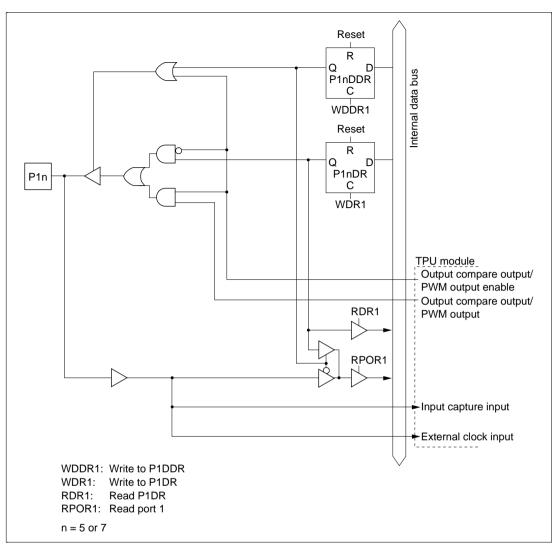

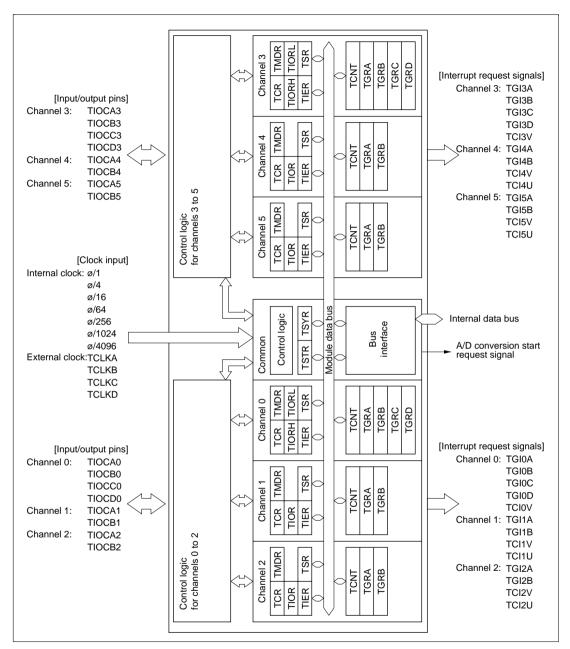

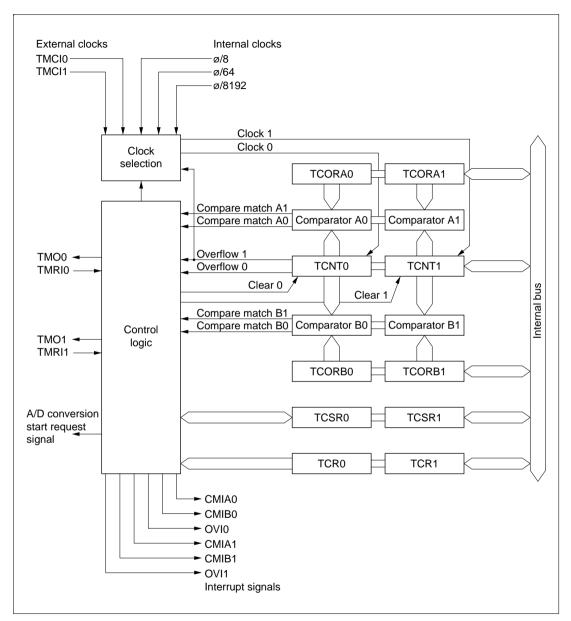

| 5.14.1 Port 1       178         5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 5.13.1  | Port States in Each Mode         | . 172 |

| 5.14.2 Port 2       182         5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.14 | I/O Po  | rt Block Diagrams                | . 178 |

| 5.14.3 Port 3       183         5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208          iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      | 5.14.1  | Port 1                           | 178   |

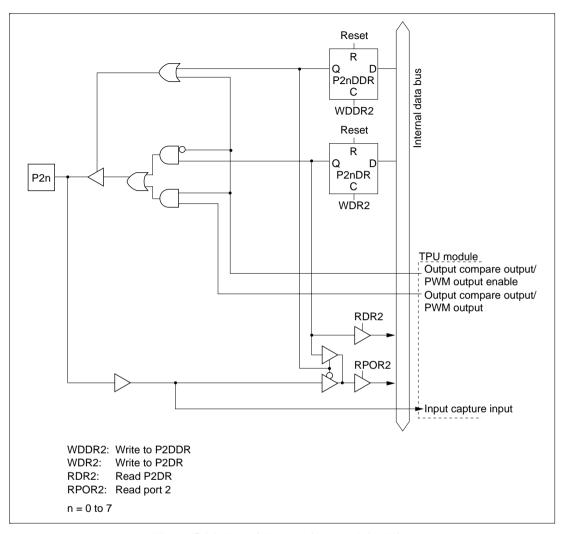

| 5.14.4 Port 4       186         5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208         iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 5.14.2  | Port 2                           | 182   |

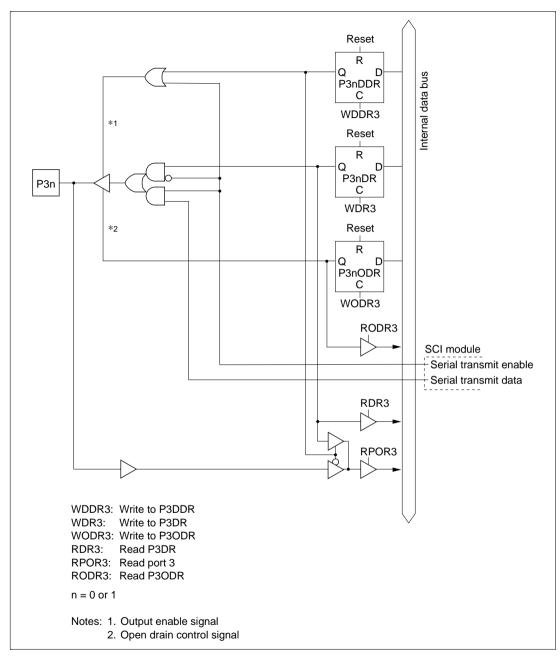

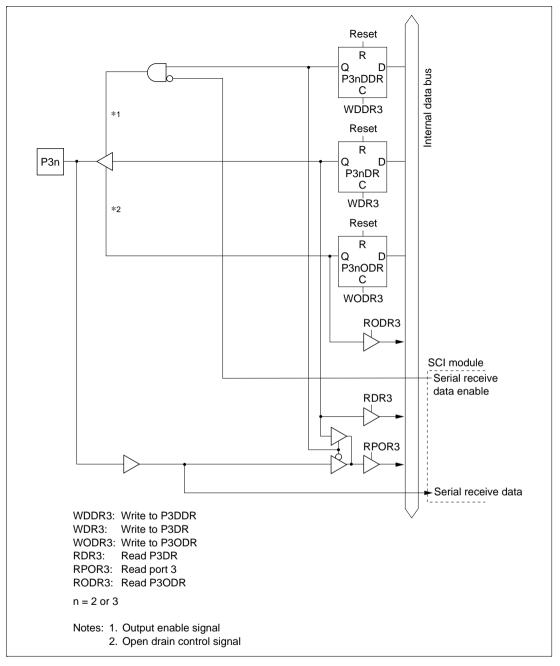

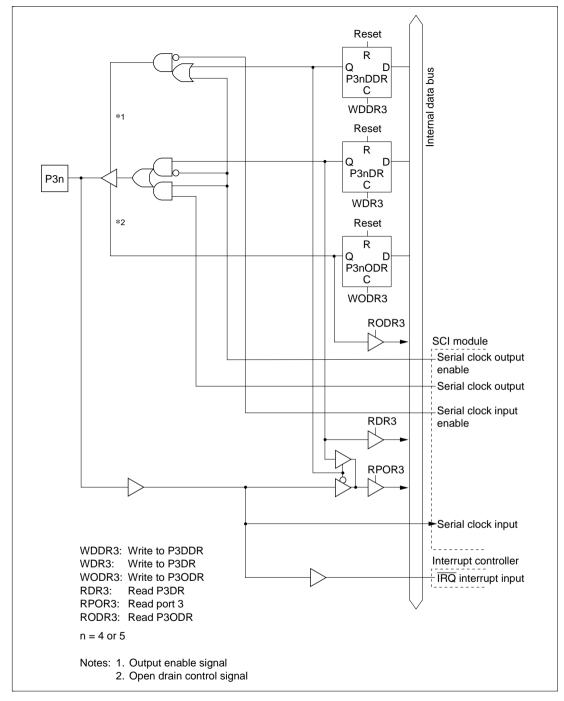

| 5.14.5 Port A       187         5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208         iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 5.14.3  | Port 3                           | 183   |

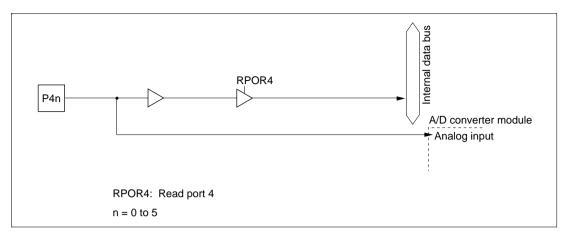

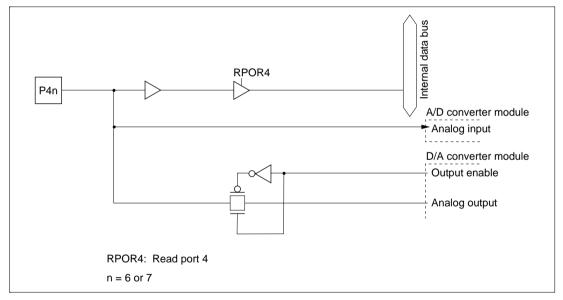

| 5.14.6 Port B       188         5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208         iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 5.14.4  | Port 4                           | 186   |

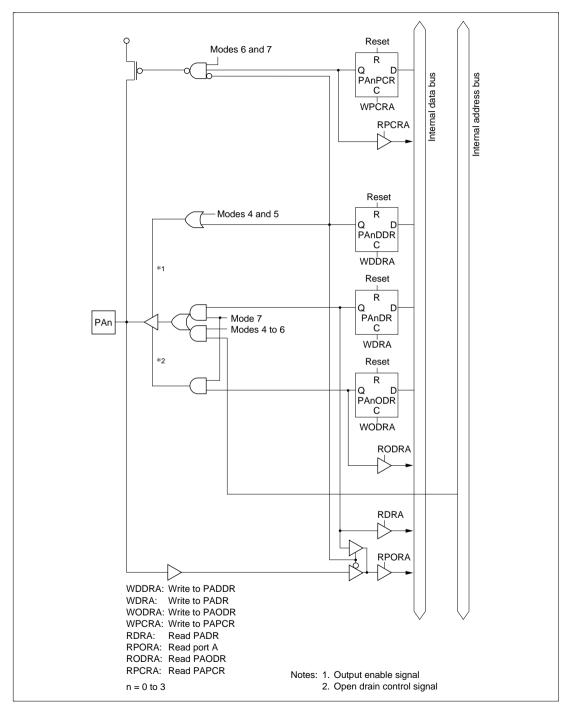

| 5.14.7 Port C       189         5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208         iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 5.14.5  | Port A                           | . 187 |

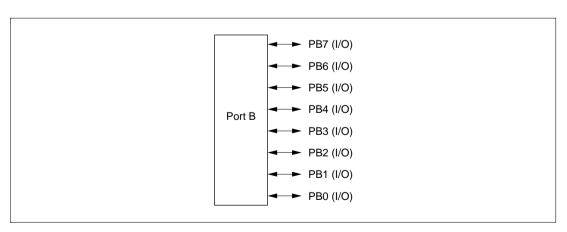

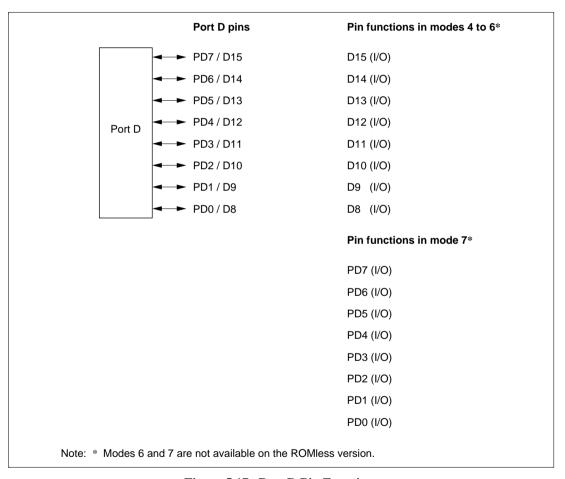

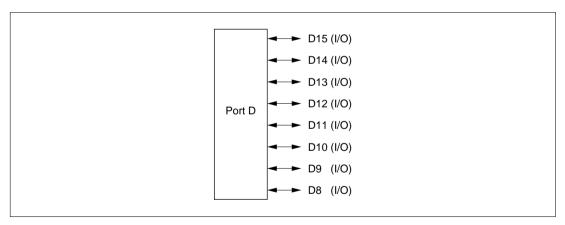

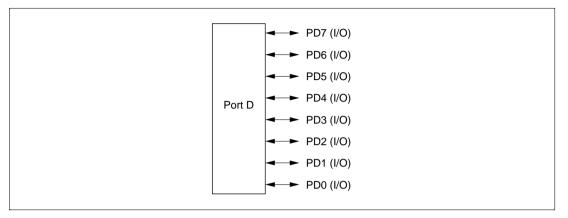

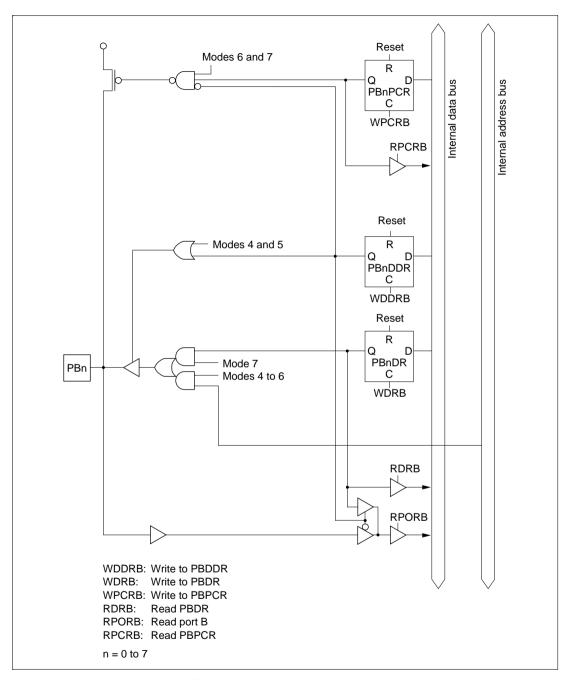

| 5.14.8 Port D       190         5.14.9 Port E       191         5.14.10 Port F       192         5.14.11 Port G       200         Section 6 Supporting Module Block Diagrams       205         6.1 Interrupt Controller       205         6.1.1 Features       205         6.1.2 Block Diagram       205         6.1.3 Pins       206         6.2 Data Transfer Controller       206         6.2.1 Features       206         6.2.2 Block Diagram       207         6.3 16-Bit Timer Pulse Unit       208         iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      | 5.14.6  | Port B                           | . 188 |

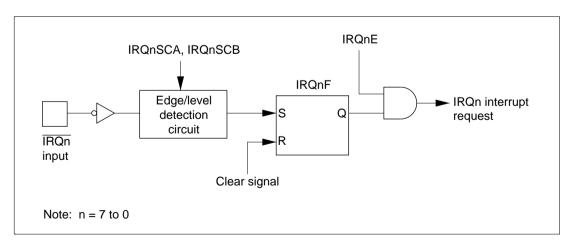

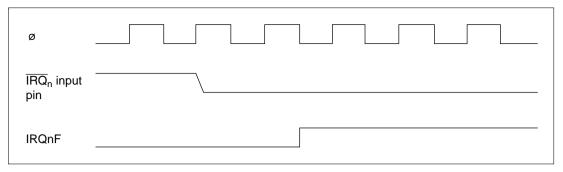

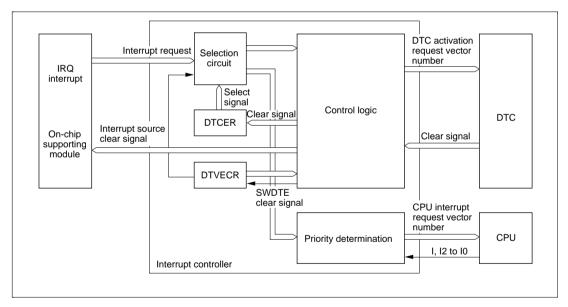

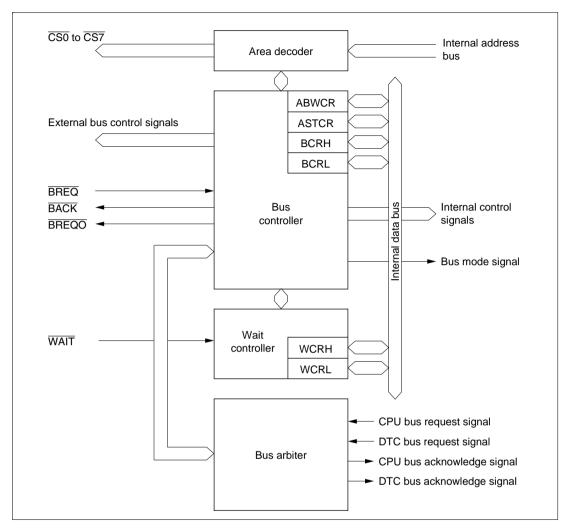

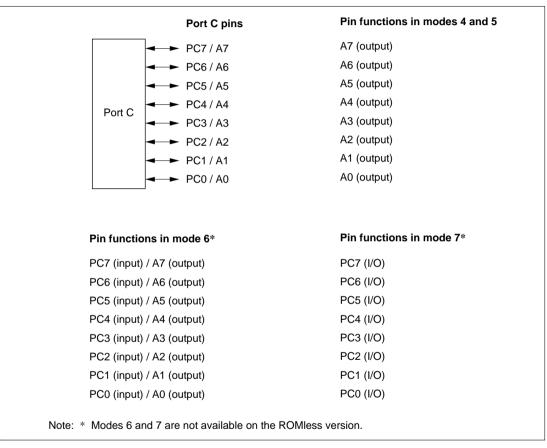

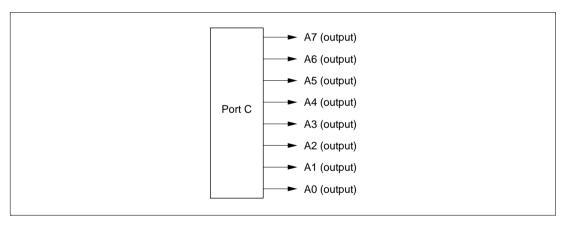

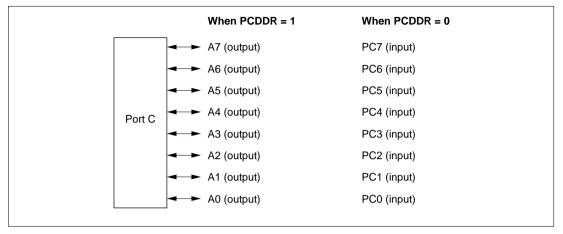

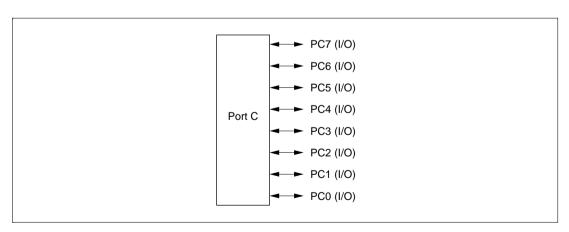

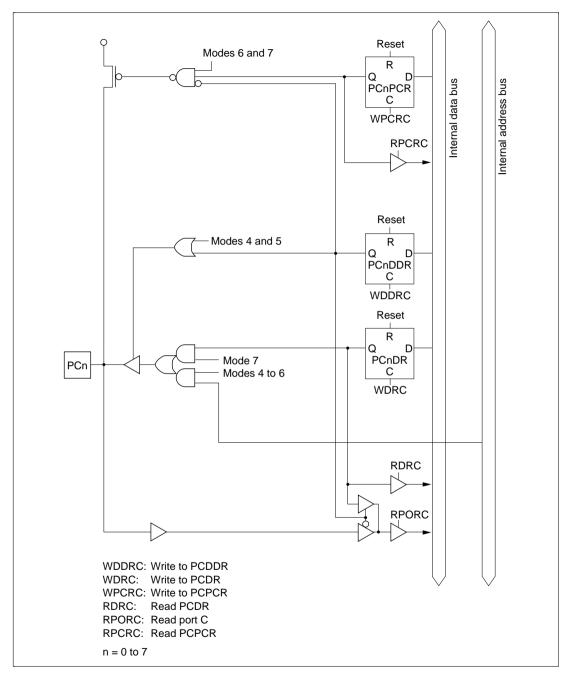

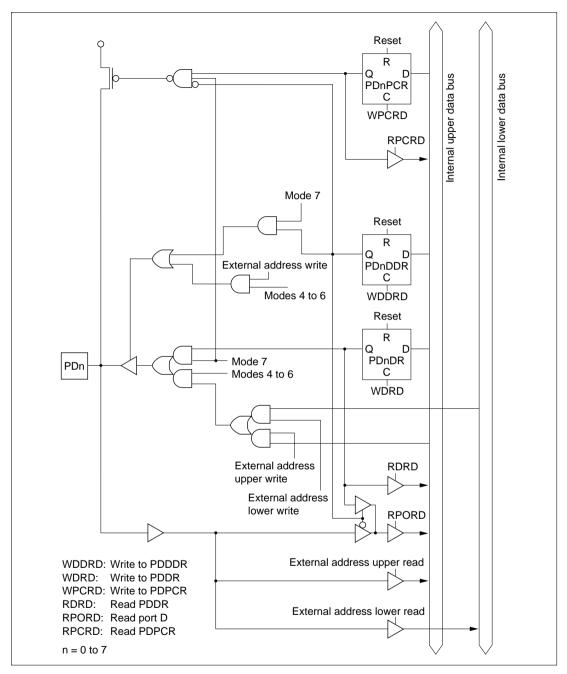

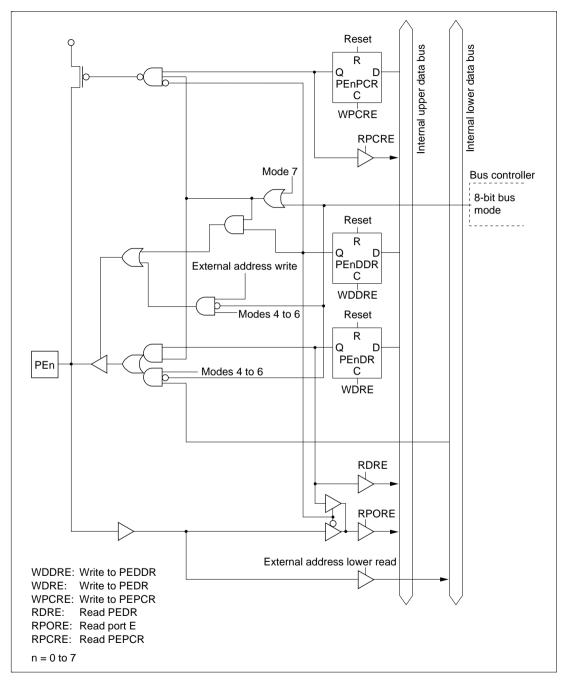

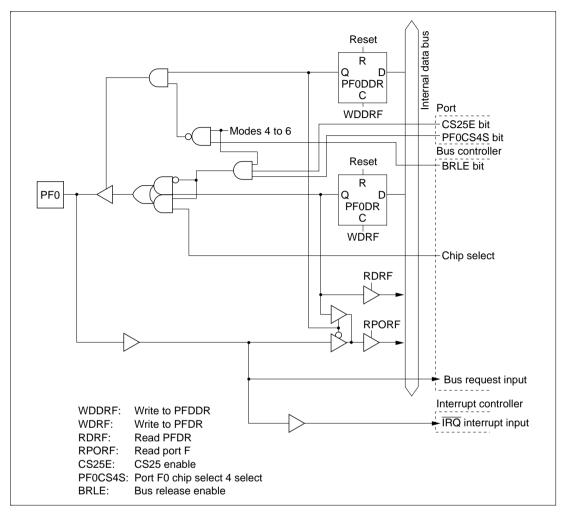

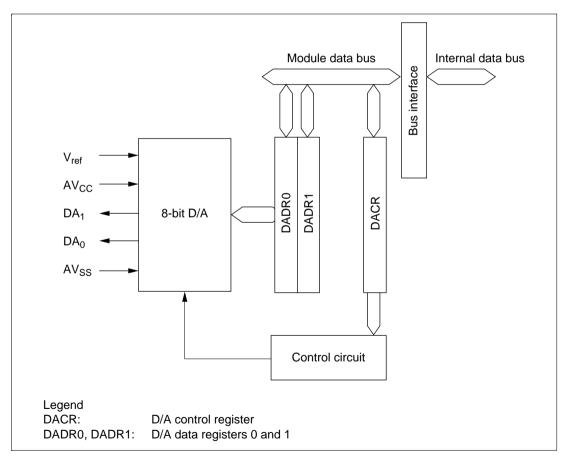

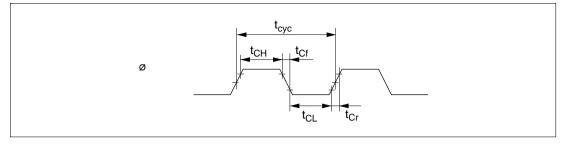

| 5.14.9 Port E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 5.14.7  | Port C                           | . 189 |