## **HD-VLC™ Transmitter**

### **Key Features**

- Serial digital video transmitter for HD and 3G video surveillance and HDcctv applications

- Quad rate operation: 270Mb/s, 540Mb/s, 1.485Gb/s, and 2.97Gb/s

- Supports HDcctv 1.0, HD-SDI (ST 292), 3G-SDI (ST 424), and SD-SDI (ST 259)<sup>1</sup>

- Integrated High Definition Visually Lossless CODEC (HD-VLC™) for extended cable reach:

- HD over 550m of Belden 543945 CCTV coax at 270Mb/s

- Full HD over 300m of Belden 543945 CCTV coax at 540Mb/s

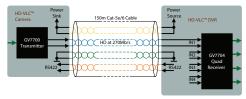

- HD over 150m of Cat-5e/6 UTP cable at 270Mb/s

- Configurable  $50/75\Omega$  cable driver output, for both coaxial and twisted pair cable transmission

- Integrated audio embedder with support for up to 4 channels of I<sup>2</sup>S serial digital audio at 32kHz, 44.1kHz and 48kHz sample rates

- Downstream ancillary data insertion

- Supports both 720p and 1080p HD formats:

- Full HD: 1080p50/59.94/60fps

- HD: 1080p25/29.97/30fps

- HD: 720p25/29.97/30/50/59.94/60fps

- Support for both 8/10-bit and 16/20-bit BT.1120 compliant video interfaces, with embedded TRS or external HVF timing

- 4-wire Gennum Serial Peripheral Interface (GSPI 2.0) for external host command and control

- Dedicated JTAG test interface

- 1.8V core power supply and 1.8V or 3.3V digital I/O supply

- Small-footprint 84-pin dual-row QFN (7mm x 7mm)

- Low power operation, typically 180mW

- Wide operating temperature range: -20°C to + 85°C

- Pb-free and RoHS compliant

### **Applications**

- HD/3G security cameras

- Industrial cameras

- · HD-SDI, 3G-SDI, and HDcctv peripherals

- Media converters

- Video multiplexers

### Description

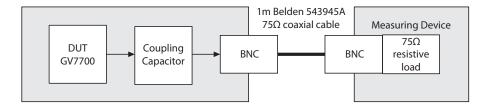

The GV7700 is a serial digital video transmitter for High Definition component video. With integrated cable driving technology, the GV7700 is capable of transmitting compressed video at 270Mb/s or 540Mb/s, or uncompressed video at 1.485Gb/s or 2.97Gb/s, over  $75\Omega$  coaxial cable, or differentially over  $100\Omega$  twisted pair cable.

The GV7700 integrates the High Definition Visually Lossless CODEC (HD-VLC™) technology, which has been developed specifically to reduce the transmission data rate of HD video over both coaxial and unshielded twisted pair (UTP) cable. This is achieved by encoding the HD video, normally transmitted at a serial data rate of 1.485Gb/s, to the same rate as Standard Definition (SD) video, at 270Mb/s serial data rate.

At 270Mb/s, the effect of cable loss is greatly reduced, resulting in much longer cable transmission. For  $75\Omega$  coaxial cable, HD-VLC allows a 1.485Gb/s HD signal to be transmitted up to 3x the normal reach. In typical video over coaxial installations, when paired with Semtech's GV7704 HD-VLC receiver, cable distances over 550m are possible.

Similarly, a 2.97Gb/s 3G signal can be transmitted at 540Mb/s using HD-VLC.

The GV7700 can also be configured to transmit HD and 3G video over UTP cable, such as Cat-5e and Cat-6 cable, when HD-VLC encoded at 270Mb/s and 540Mb/s, respectively.

The device supports both 8-bit and 10-bit per pixel YCbCr 4:2:2 BT.1120 component digital video. A configurable 20-bit or 10-bit wide parallel digital video input bus is provided, with associated pixel clock and timing signal inputs. The GV7700 supports direct interfacing of HD video formats conforming to ITU-R BT.709 and BT.1120-6 for 1125-line formats, and SMPTE ST 296 for 750-line formats.

The GV7700 features an audio embedding core, which supports up to 4 channels of I<sup>2</sup>S serial digital audio within the ancillary data space of the video data stream. The audio embedding core supports 32kHz, 44.1kHz, and 48kHz sample rates.

The GV7700 supports the insertion of ancillary data into the horizontal blanking of the video data stream. User data can be programmed via the GSPI, allowing downstream communication from the video source to sink device. The ancillary data packing format is compliant with HDcctv 2.0 communications protocol.

Packaged in a space-saving 84-pin dual-row QFN, the GV7700 is ideal for single PCB security cameras, where high-density component placement is required. Typically requiring only 180mW of power, the device does not require any special heat sinking or air flow, reducing the over-cost of HD security camera designs.

<sup>1</sup>Frame structure with encoded HD only. Does not support SD/D1 video.

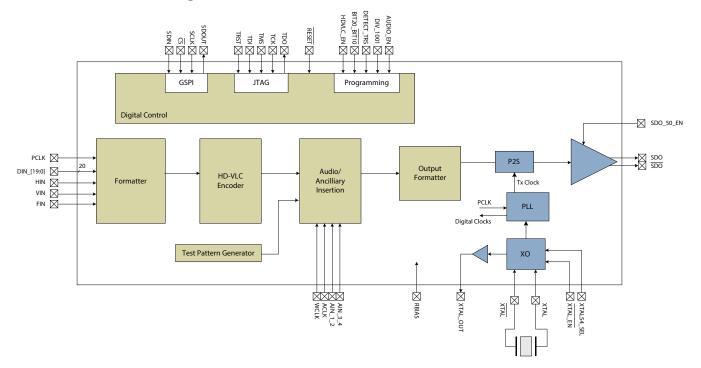

### **Functional Block Diagram**

**GV7700 Functional Block Diagram**

# **Revision History**

| Version | ECO    | PCN | Date              | Description                                                                                                                                                                      |

|---------|--------|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8       | 029991 | _   | March 2016        | Addition of Figure 3-3: XTAL_N, XTAL_P, XTAL_EN. Updates to values in Table 4-6: Cable Reach for Various Cable Types (In Meters).                                                |

| 7       | 029012 | _   | December<br>2015  | Updated values in Table 2-3: AC Electrical Characteristics.                                                                                                                      |

| 6       | 028866 | _   | December<br>2015  | Updated to Final Data Sheet from Preliminary Data Sheet.                                                                                                                         |

| 5       | 027517 | _   | September<br>2015 | Removed Proprietary and Confidential from footer.<br>Updated Table 1-1, Table 2-3, Section 4.4,<br>Section 4.11, Section 4.14, Figure 4-18, and<br>Figure 6-1. Added Figure 6-2. |

| 4       | 027026 | _   | July 2015         | Updated cable reach values. Updated Table 2-2 and Table 2-3.                                                                                                                     |

| 3       | 025836 | _   | May 2015          | Updated to Preliminary Data Sheet from Draft Data<br>Sheet                                                                                                                       |

| 2       | 025126 | _   | April 2015        | Updated GV7700 Functional Block Diagram,<br>Figure 1-1, Figure 6-1. Updated Table 2-2 and<br>Table 2-3. Various updates throughout document.                                     |

| 1       | 024223 | _   | February 2015     | Updated Table 1-1, Table 2-2, Section 4.1                                                                                                                                        |

| 0       | 020611 | _   | August 2014       | New Document                                                                                                                                                                     |

### **Contents**

| 1. Pin Out                                |    |

|-------------------------------------------|----|

| 1.1 GV7700 Pin Assignment                 | 5  |

| 1.2 Pin Descriptions                      | 6  |

| 2. Electrical Characteristics             | 10 |

| 2.1 Absolute Maximum Ratings              | 10 |

| 2.2 DC Electrical Characteristics         |    |

| 2.3 AC Electrical Characteristics         | 11 |

| 3. Input/Output Circuits                  | 13 |

| 4. Detailed Description                   |    |

| 4.1 Functional Overview                   |    |

| 4.2 Parallel Video Data Inputs DIN_[19:0] | 15 |

| 4.2.1 Parallel Input In Video Mode        | 15 |

| 4.3 Video Processing                      | 21 |

| 4.3.1 H:V:F Timing                        |    |

| 4.4 HD-VLC™ Encoder                       |    |

| 4.5 Stream ID Packet Insertion            | 24 |

| 4.6 Audio Embedding                       | 25 |

|                                           |    |

| 4.6.1 Serial Audio Data Inputs                 | 25 |

|------------------------------------------------|----|

| 4.6.2 Serial I2S Audio Data Format             | 26 |

| 4.6.3 Audio Mute                               | 26 |

| 4.6.4 ECC Error Detection and Correction       | 27 |

| 4.7 Ancillary Data Insertion                   | 27 |

| 4.8 Additional Processing Functions            | 29 |

| 4.8.1 Test Pattern Generation                  | 29 |

| 4.8.2 TRS Generation and Insertion             | 32 |

| 4.8.3 HD Line Number Calculation and Insertion | 32 |

| 4.8.4 Line Based CRC Generation and Insertion  | 32 |

| 4.8.5 Illegal Code Re-Mapping                  | 32 |

| 4.9 Parallel to Serial Conversion              | 32 |

| 4.10 PLL                                       | 33 |

| 4.10.1 Frequency Reference                     | 33 |

| 4.11 Serial Data Output                        | 34 |

| 4.11.1 Output Signal Interface Levels          | 35 |

| 4.11.2 Serial Data Output Signal               | 35 |

| 4.12 GSPI Host Interface                       | 35 |

| 4.12.1 CS Pin                                  | 35 |

| 4.12.2 SDIN Pin                                | 36 |

| 4.12.3 SDOUT Pin                               | 36 |

| 4.12.4 SCLK Pin                                | 36 |

| 4.12.5 Command Word Description                | 36 |

| 4.12.6 Data Word Description                   | 37 |

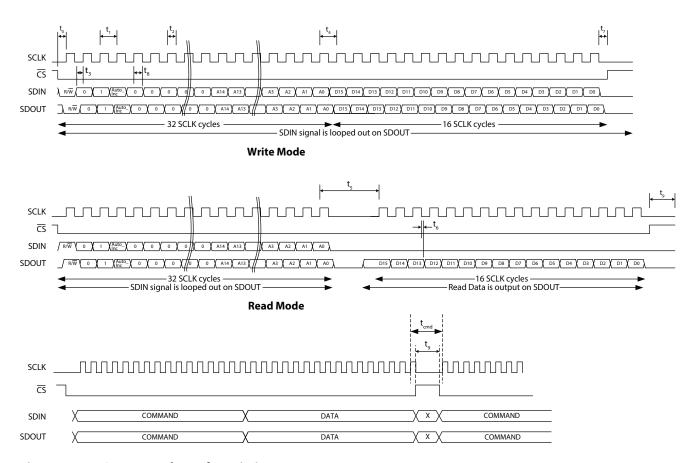

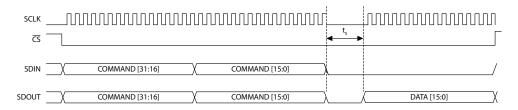

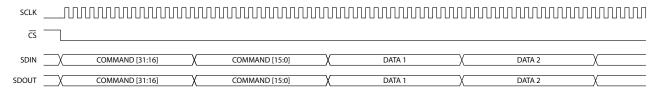

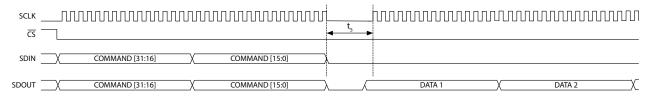

| 4.12.7 GSPI Transaction Timing                 | 38 |

| 4.12.8 Single Read/Write Access                | 39 |

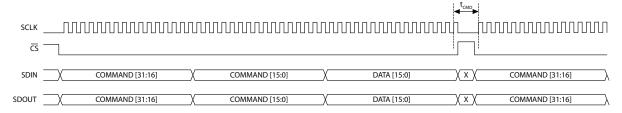

| 4.12.9 Auto-increment Read/Write Access        | 40 |

| 4.13 JTAG                                      | 40 |

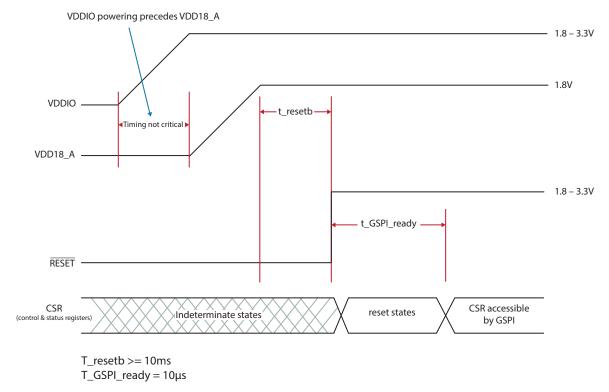

| 4.14 Power Supply and Reset Timing             | 41 |

| 5. Register Map                                | 42 |

| 6. Typical Application Circuit                 | 45 |

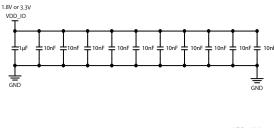

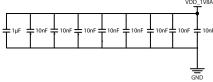

| 6.1 Power Supply Decoupling and Filtering      | 46 |

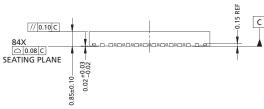

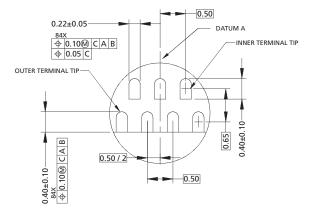

| 7. Packaging Information                       | 47 |

| 7.1 Package Dimensions                         | 47 |

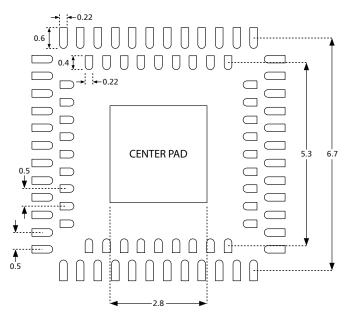

| 7.2 Recommended PCB Footprint                  | 48 |

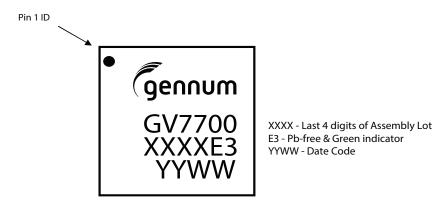

| 7.3 Marking Diagram                            | 48 |

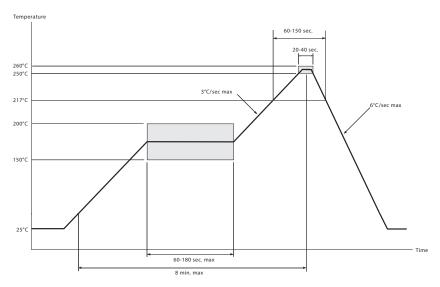

| 7.4 Solder Reflow Profile                      | 49 |

| 7.5 Packaging Data                             | 49 |

| 7.6 Ordering Information                       | 49 |

GV7700

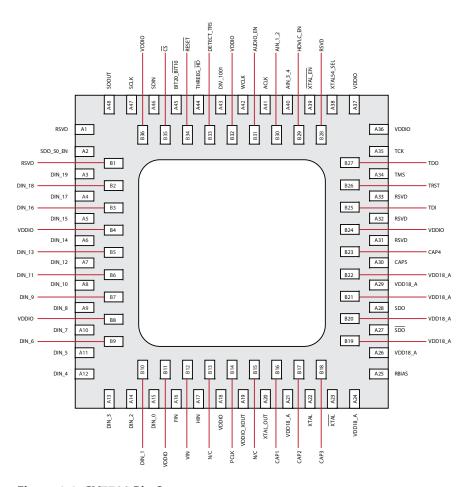

# 1. Pin Out

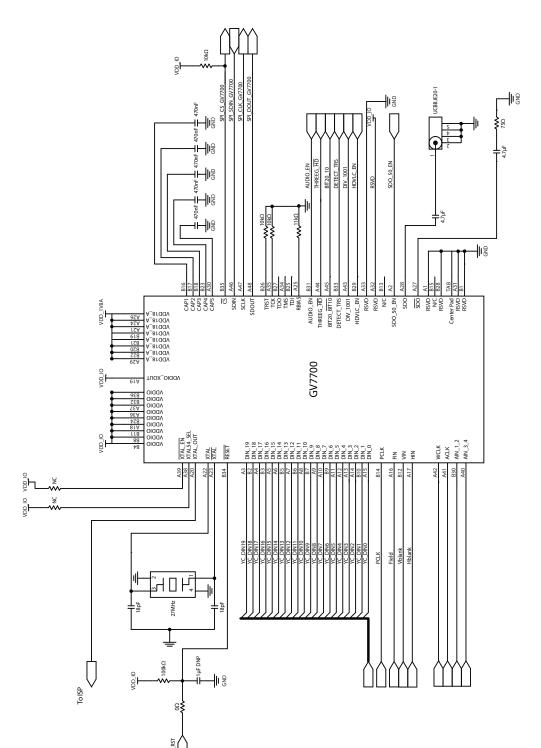

# 1.1 GV7700 Pin Assignment

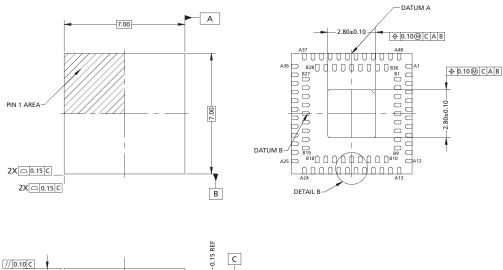

Figure 1-1: GV7700 Pin Out

# **1.2 Pin Descriptions**

**Table 1-1: GV7700 Pin Descriptions**

| Pin Number                                            | Name        | Туре                   | Description                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------|-------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                                                    | RSVD        | _                      | Connect to ground.                                                                                                                                                                                                                                                              |

| A2                                                    | SDO_50_EN   | Input                  | HIGH = device outputs a $100\Omega$ differential signal.<br>LOW = device outputs a $75\Omega$ single-ended output signal, with both complementary outputs ON by default.<br>Each output can be manually disabled via GSPI.<br>Schmitt Trigger Input with Pull-Down.             |

| B1                                                    | RSVD        | _                      | Connect to ground.                                                                                                                                                                                                                                                              |

| A3, B2, A4, B3,<br>A5, A6, B5, A7,<br>B6, A8          | DIN_[19:10] | Input                  | Parallel data bus inputs [19:10].  If BIT20_BIT10 = HIGH, the input data format must be word aligned, demultiplexed Luma and Chroma data. DIN_[19:10] are the input pins for Luma data.  If BIT20_BIT10 = LOW, the multiplexed Luma and Chroma data is presented on these pins. |

| B7, A9, A10,<br>B9, A11 A12,<br>A13, A14, B10,<br>A15 | DIN_[9:0]   | Input                  | Parallel data bus inputs [9:0].  If BIT20_BIT10 = HIGH, the input data format must be word aligned, demultiplexed Luma and Chroma data. DIN_[9:0] are the input pins for Chroma data.  If BIT20_BIT10 = LOW, these pins are unused and should be tied to ground.                |

| B4, B8, B11,<br>A18, B24, A36,<br>A37, B32, B36       | VDDIO       | Power                  | Connect to 1.8V or 3.3V.                                                                                                                                                                                                                                                        |

| A16                                                   | FIN         | Input                  | Field identification. Used in interlaced mode.                                                                                                                                                                                                                                  |

| B12                                                   | VIN         | Input                  | Vertical blanking.                                                                                                                                                                                                                                                              |

| A17                                                   | HIN         | Input                  | Horizontal blanking.                                                                                                                                                                                                                                                            |

| B13                                                   | N/C         | _                      | Do not connect.                                                                                                                                                                                                                                                                 |

| B14                                                   | PCLK        | Input                  | 148.5MHz/74.25MHz input clock representing the time allocated to one 10 or 20-bit pixel.                                                                                                                                                                                        |

| A19                                                   | VDDIO_XOUT  | Power                  | Connect to 1.8V or 3.3V <sup>1</sup> .                                                                                                                                                                                                                                          |

| B15                                                   | N/C         | _                      | Do not connect.                                                                                                                                                                                                                                                                 |

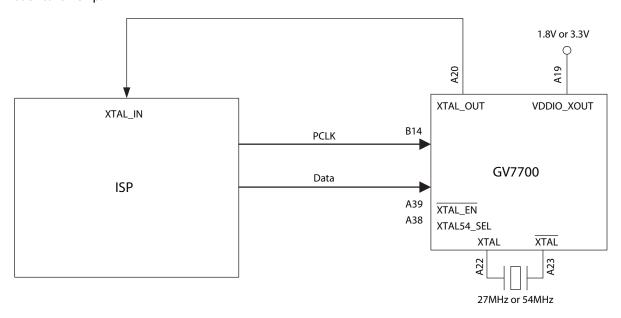

| A20                                                   | XTAL_OUT    | Analog<br>Output       | Output capable of driving ISP clock input.                                                                                                                                                                                                                                      |

| A21, A24, A26,<br>B19, B20, B21,<br>A29, B22          | VDD18_A     | Power                  | Connect to 1.8V.                                                                                                                                                                                                                                                                |

| B16                                                   | CAP1        | Analog<br>Input/Output | Must connect to external decoupling filter. Refer to Figure 6-1: GV7700 Typical Application Circuit.                                                                                                                                                                            |

Table 1-1: GV7700 Pin Descriptions (Continued)

| Pin Number | Name     | Туре                           | Description                                                                                                                                                                                  |

|------------|----------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B17        | CAP2     | Analog<br>Input/Output         | Must connect to external decoupling filter.<br>Refer to Figure 6-1: GV7700 Typical Application Circuit.                                                                                      |

| A22        | XTAL     | Analog<br>Input/Output         | Pin to external 27MHz or 54MHz crystal.  When not using a crystal reference (XTAL_EN = HIGH), connect XTAL to ground.                                                                        |

| B18        | CAP3     | Analog<br>Input/Output         | Must connect to external decoupling filter.<br>Refer to Figure 6-1: GV7700 Typical Application Circuit.                                                                                      |

| A23        | XTAL     | Analog<br>Input/Output         | Pin to external 27MHz or 54MHz crystal.  When not using a crystal reference (XTAL_EN = HIGH), XTAL can be left floating.                                                                     |

| A25        | RBIAS    | Analog<br>Input/Output         | External 11k $\Omega$ resistor for bias reference. Connect the resistor to ground.                                                                                                           |

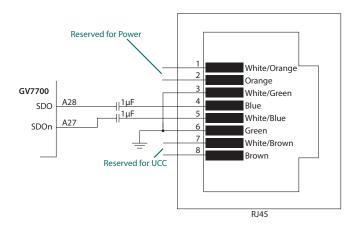

| A27, A28   | SDO, SDO | Analog<br>High-Speed<br>Output | Serial differential output signal.  Single-ended operation at data rates of 2.97Gb/s, 2.97/1.001Gb/s, 1.485Gb/s, 1.485/1.001Gb/s, 540Mb/s, or 270Mb/s.                                       |

| B23        | CAP4     | Analog<br>Input/Output         | Must connect to external decoupling filter.<br>Refer to Figure 6-1: GV7700 Typical Application Circuit.                                                                                      |

| A30        | CAP5     | Analog<br>Input/Output         | Must connect to external decoupling filter.<br>Refer to Figure 6-1: GV7700 Typical Application Circuit.                                                                                      |

| A31        | RSVD     | _                              | Connect to ground.                                                                                                                                                                           |

| A32        | RSVD     | _                              | This pin must be set HIGH.                                                                                                                                                                   |

| B25        | TDI      | Input                          | Dedicated JTAG pin – Test data input.  This pin is used to shift JTAG test data into the device.  Schmitt Trigger Input with Pull-Up.  If JTAG is not used this pin may be left floating.    |

| A33        | RSVD     | _                              | Connect to ground.                                                                                                                                                                           |

| B26        | TRST     | Input                          | Dedicated JTAG pin – Test Reset.  When set LOW, the JTAG logic will be reset.  Schmitt Trigger Input with Pull-Up.  If JTAG is not used this pin must be pulled LOW.                         |

| A34        | TMS      | Input                          | Dedicated JTAG pin – Test Mode Select.  This pin is used to control the operation of the JTAG test.  Schmitt Trigger Input with Pull-Up.  If JTAG is not used this pin may be left floating. |

| B27        | TDO      | Output                         | Dedicated JTAG pin – Test data output. This pin is used to shift results from the device.                                                                                                    |

Table 1-1: GV7700 Pin Descriptions (Continued)

| Pin Number | Name       | Type  | Description                                                                                                                                                                                                                                                                   |

|------------|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A35        | TCK        | Input | Dedicated JTAG pin – Serial data clock signal. This pin is the JTAG clock. Schmitt Trigger Input. If JTAG is not used this pin must be pulled LOW.                                                                                                                            |

| A38        | XTAL54_SEL | Input | HIGH = for use with a 54MHz crystal.  LOW = for use with a 27MHz crystal (default).  Schmitt Trigger Input with Pull-Down.                                                                                                                                                    |

| B28        | RSVD       | _     | Connect to ground                                                                                                                                                                                                                                                             |

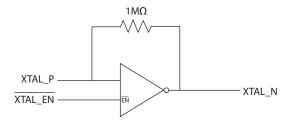

| A39        | XTAL_EN    | Input | HIGH = when using the PCLK input as a frequency reference. LOW = when using an external XTAL as a frequency reference. Schmitt Trigger Input with Pull-Down.                                                                                                                  |

| B29        | HDVLC_EN   | Input | HIGH = Enables HD-VLC compression for extended cable reach.  LOW = Disables HD-VLC compression.                                                                                                                                                                               |

| A40        | AIN_3_4    | Input | I <sup>2</sup> S Serial Audio Input; Channels 3 and 4.<br>Schmitt Trigger Input.                                                                                                                                                                                              |

| B30        | AIN_1_2    | Input | I <sup>2</sup> S Serial Audio Input; Channels 1 and 2.<br>Schmitt Trigger Input.                                                                                                                                                                                              |

| A41        | ACLK       | Input | Serial Audio Input bit clock.  Serial bit clock for audio data from pins AIN_1_2 and AIN_3_4.  Schmitt Trigger Input.                                                                                                                                                         |

| B31        | AUDIO_EN   | Input | HIGH = Enables the device to support the insertion of 4 audio channels.  LOW = Disables device audio support.                                                                                                                                                                 |

| A42        | WCLK       | Input | Serial Audio Left/Right Clock.  Word rate clock for the audio data from pins AIN_1_2 and AIN_3_4.  Supports sampling frequencies of 32KHz, 44.1kHz, and 48kHz.  Schmitt Trigger Input.                                                                                        |

| A43        | DIV_1001   | Input | HIGH = Enable device support for when the incoming frame rate is 60/1.001 or 30/1.001 frames per second.  LOW = When the incoming frame rate is 60, 50, 30, or 25 frames per second.                                                                                          |

| A44        | THREEG_HD  | Input | HIGH = 3G video input.  LOW = HD video input.                                                                                                                                                                                                                                 |

| B33        | DETECT_TRS | Input | Control Signal Input.  Used to select external HVF timing mode or TRS extraction timing mode.  LOW = the device extracts all internal timing from the supplied H:V:F.  HIGH = the device extracts all internal timing from TRS signals embedded in the supplied video stream. |

Table 1-1: GV7700 Pin Descriptions (Continued)

| Pin Number | Name        | Туре   | Description                                                                                                                                                                                                                                   |

|------------|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B34        | RESET       | Input  | Digital active-low reset input. Used to reset the internal operating conditions to default settings. Minimum reset duration of 10ms. See Section 4.14. Device configuration pins should be set prior to device reset.  Schmitt Trigger Input. |

| A45        | BIT20_BIT10 | Input  | HIGH = Selects 20-bit wide input interface. LOW = Selects 10-bit wide input interface.                                                                                                                                                        |

| B35        | <u>cs</u>   | Input  | Chip select input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.  Active-low input.                                                                                                                              |

| A46        | SDIN        | Input  | Serial data input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                                                                                                                                 |

| A47        | SCLK        | Input  | Burst-mode clock input for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                                                                                                                            |

| A48        | SDOUT       | Output | Serial data output for the Gennum Serial Peripheral Interface (GSPI) host control/status port.                                                                                                                                                |

| _          | Center Pad  | Power  | Common analog and digital ground connection, and main thermal path for device.                                                                                                                                                                |

#### Notes:

<sup>1.</sup> Serial output jitter increases by 10ps at 3.3V.

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

**Table 2-1: Absolute Maximum Ratings**

| Parameter                                             | Value                   |

|-------------------------------------------------------|-------------------------|

| Supply Voltage, Digital I/O (VDDIO)                   | -0.5V to +3.6V          |

| Supply Voltage, Analog (VDD18_A)                      | -0.5V to +2.5V          |

| DC Input Voltage, V <sub>IN</sub> (except I/O pins)   | -0.5V to (VDDIO + 0.5V) |

| DC Output Voltage, V <sub>OUT</sub> (except I/O pins) | -0.5V to (VDDIO + 0.5V) |

| Input ESD Voltage (HBM)                               | 2.5kV                   |

| Input ESD Voltage (CDM)                               | 1kV                     |

| Storage Temperature Range (T <sub>S</sub> )           | -50°C to 125°C          |

| Operating Temperature Range (T <sub>A</sub> )         | -40°C to 85°C           |

| Solder Reflow Temperature (4s)                        | 260°C                   |

**Note:** Absolute Maximum Ratings are those values beyond which damage may occur. Functional operation outside of the ranges shown in the AC and DC Electrical Characteristics is not guaranteed.

# 2.2 DC Electrical Characteristics

**Table 2-2: DC Electrical Characteristics**

VDD18\_A =  $1.8V\pm5\%$  and TA =  $-20^{\circ}$ C to  $+85^{\circ}$ C unless otherwise stated

| Parameter                   | Symbol              | Conditions | Min  | Тур  | Max  | Units | Notes |

|-----------------------------|---------------------|------------|------|------|------|-------|-------|

| Supply Voltage Digital I/O  | VDDIO               | 1.8V mode  | 1.71 | 1.8  | 1.89 | V     | _     |

| Supply Voltage, Digital I/O | VDDIO               | 3.3V mode  | 3.13 | 3.3  | 3.47 | V     | _     |

| Supply Voltage, Analog      | VDD18_A             |            | 1.71 | 1.8  | 1.89 | V     | _     |

| Supply Current Digital I/O  | 1 .                 | 1.8V mode  | _    | 0.25 | 0.5  | mA    | _     |

| Supply Current, Digital I/O | IDDIO               | 3.3V mode  | _    | 3.5  | 4.75 | mA    | _     |

| Supply Current, Analog      | I <sub>DD18_A</sub> |            | _    | 100  | 115  | mA    | 1     |

### **Table 2-2: DC Electrical Characteristics (Continued)**

VDD18\_A = 1.8V $\pm$ 5% and TA = -20°C to +85°C unless otherwise stated

| Parameter               | Symbol             | Conditions  | Min                                                   | Тур | Max                                                                                                                           | Units            | Notes |

|-------------------------|--------------------|-------------|-------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------|------------------|-------|

| HD mode                 |                    | HD mode     | _                                                     | 140 | 170                                                                                                                           | mW               | 2     |

|                         | mW                 | 2           |                                                       |     |                                                                                                                               |                  |       |

| total Power Consumption | <sup>r</sup> total | 270 mode    | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |     |                                                                                                                               |                  |       |

|                         |                    | 540 mode    | _                                                     | 240 | 275                                                                                                                           | mW               | 2     |

| External RBIAS Resistor |                    |             | 10.89                                                 | 11  | 11.1                                                                                                                          | kΩ               | _     |

| Power Supply Noise Mask |                    | 0Hz-1.5GHz  | _                                                     | _   | 20                                                                                                                            | mV <sub>pp</sub> | 3     |

| Digital Lagis Input     | V <sub>IL</sub>    | Input LOW   | -0.3                                                  | _   | 0.63                                                                                                                          | V                | _     |

| Digital Logic Input     | V <sub>IH</sub>    | Input HIGH  | 1.17                                                  | _   | 170 mW $2$ $180$ mW $2$ $2$ $215$ mW $2$ $275$ mW $2$ $211.1$ kΩ $ 20$ mV <sub>pp</sub> $3$ $0.63$ V $ 3.465$ V $ 0.45$ V $-$ | _                |       |

| Digital Logic Output    | V <sub>OL</sub>    | Output LOW  | _                                                     | _   | 0.45                                                                                                                          | V                | _     |

| Digital Logic Output    | V <sub>OH</sub>    | Output HIGH | 1.35                                                  | _   | _                                                                                                                             | V                | _     |

#### Notes:

- 1. SD mode.

- 2. Max = 85°C, VDD18\_A = 1.89V.

- 3. Using recommended power supply decoupling. See Figure 6-1: GV7700 Typical Application Circuit.

# 2.3 AC Electrical Characteristics

### **Table 2-3: AC Electrical Characteristics**

VDD18\_A =  $1.8V\pm5\%$  and TA =  $-20^{\circ}$ C to  $+85^{\circ}$ C unless otherwise stated

| Parameter                   | Symbol             | Conditions                | Min | Тур   | Max | Units | Notes |

|-----------------------------|--------------------|---------------------------|-----|-------|-----|-------|-------|

| Input Conditions            |                    |                           |     |       |     |       |       |

| Input DCL K clark fraguancy |                    | 10-bit mode               | _   | 148.5 | _   | MHz   | 1     |

| Input PCLK clock frequency  |                    | 20-bit mode               | _   | 74.25 | _   | MHz   | 1,3   |

| PCLK Duty Cycle             | DC <sub>PCLK</sub> |                           | 40  | _     | 60  | %     | _     |

| Input Data Setup Time       | t <sub>SU</sub>    |                           | 1.2 | _     | _   | ns    | _     |

| Input Data Hold Time        | t <sub>HOLD</sub>  |                           | 0.8 | _     | _   | ns    | _     |

| Output Driver               |                    |                           |     |       |     |       |       |

| Impodance                   |                    | 75 $\Omega$ single-ended  | 66  | 75    | 84  | Ω     | _     |

| Impedance                   |                    | 100 $\Omega$ differential | 88  | 100   | 112 | Ω     | _     |

### **Table 2-3: AC Electrical Characteristics (Continued)**

VDD18\_A =  $1.8V\pm5\%$  and TA =  $-20^{\circ}$ C to  $+85^{\circ}$ C unless otherwise stated

| Parameter                               | Symbol | Conditions                     | Min  | Тур      | Max  | Units            | Notes |

|-----------------------------------------|--------|--------------------------------|------|----------|------|------------------|-------|

|                                         |        | 1MHz - 5MHz                    | _    | _        | 17.9 | dB               | _     |

| Return loss                             |        | 5MHz - 1.485GHz                | _    | _        | 6.7  | dB               | _     |

|                                         |        | 1.485GHz - 2.25GHz             | _    | _        | 4    | dB               | _     |

| A                                       |        | 75 $\Omega$ single-ended       | 0.36 | 0.8      | 0.9  | $V_{pp}$         | _     |

| Amplitude                               |        | 100Ω differential              | 0.36 | 0.8      | 0.9  | $V_{ppd}$        | _     |

| D: (F.H.T.                              |        | 100Ω differential<br>20% - 80% | _    | 85       | 95   | ps               | _     |

| Rise/Fall Time                          |        | 75Ω single-ended<br>20% - 80%  | _    | 102      | 150  | ps               | _     |

| Rise/Fall Time Mismatch                 |        | 20% - 80%                      | _    | _        | 50   | ps               | _     |

| Overshoot                               |        |                                | _    | _        | 10   | %                | _     |

| Output Total Jitter -  De-emphasis      |        | Data rate = 270Mb/s            | _    | 0.021    | _    | Ul <sub>pp</sub> | 2     |

|                                         |        | Data rate = 540Mb/s            | _    | 0.04     | _    | Ul <sub>pp</sub> | 2     |

|                                         |        | Data rate = 1.485Gb/s          | _    | 0.115    | _    | Ul <sub>pp</sub> | 2     |

|                                         |        | Data rate = 2.97Gb/s           | _    | 0.2      | _    | Ul <sub>pp</sub> | 2     |

| De-emphasis                             |        | Post-Cursor                    | 0    | 1        | _    | dB               | _     |

| Crystal Oscillator                      |        |                                |      |          |      |                  |       |

| External Crystal Reference<br>Frequency |        |                                | _    | 27 or 54 | _    | MHz              | _     |

| Load Capacitance                        |        |                                | 8    | _        | 9    | pF               | _     |

| Start-up time                           |        |                                | _    | 100      | _    | ms               | _     |

| Accuracy                                |        |                                | _    | ±20      | ±100 | ppm              | _     |

| GSPI Digital Control                    |        |                                |      |          |      |                  |       |

| GSPI Read/Write Clock<br>Frequency      |        |                                | _    | _        | 40   | MHz              | _     |

| Reset Time                              |        |                                | 10   | _        | _    | ms               | _     |

| Register Access Time                    |        |                                | _    | _        | 300  | ns               | _     |

#### Notes:

- 1. If DIV\_1001 = HIGH, divide the listed PCLK frequency by 1.001.

- 2. Jitter performance is only guaranteed when using a crystal (27/54MHz) as the clock reference for the device. Jitter performance is not guaranteed when using the PCLK clock generated by the ISP as the reference for the device.

- 3. In 3G 20-bit mode, the PCLK is 148.5MHz.

# 3. Input/Output Circuits

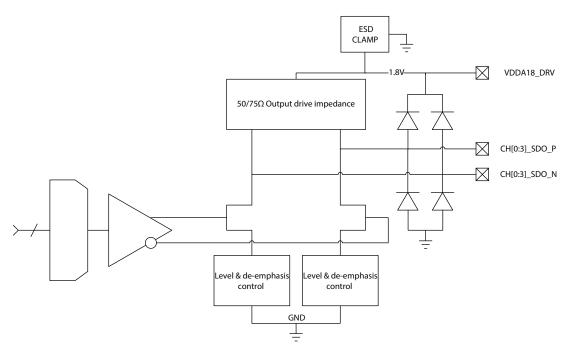

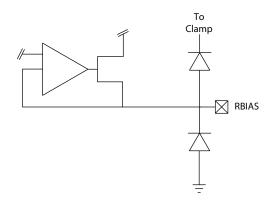

Figure 3-1: Serial Output Driver

Figure 3-2: RBIAS

Figure 3-3: XTAL\_N, XTAL\_P, XTAL\_EN

# 4. Detailed Description

### 4.1 Functional Overview

The GV7700 is a low cost, dual-rate HDcctv transmitter with integrated HD-VLC encoding. With integrated cable driving technology, the GV7700 is capable of transmitting compressed video at 270Mb/s or 540Mb/s, or uncompressed video at 1.485Gb/s or 2.97Gb/s, over 75 $\Omega$  coaxial cable. Compressed signals can also be transmitted differentially over 100 $\Omega$  twisted pair cable.

The High Definition Visually Lossless CODEC (HD-VLC™) technology is integrated in order to reduce the transmission data rate of HD video over both coaxial and unshielded twisted pair (UTP) cable. This is achieved by encoding the HD-SDI video, normally transmitted at a serial data rate of 1.485Gb/s, to the same rate as Standard Definition (SD-SDI) video, at 270Mb/s serial data rate. This provides extended cable reach for HD video up to 550m over Belden 543945 CCTV coax or 150m over Cat-5e/6 UTP cable. Similarly, 3G-SDI normally transmitted at 2.97Gb/s can be encoded down to 540Mb/s.

The GV7700 features an audio embedding core, which supports up to 4 channels of I<sup>2</sup>S serial digital audio within the ancillary data space of the video data stream. The audio embedding core supports 32kHz, 44.1kHz, and 48kHz sample rates.

The device allows for both 8-bit and 10-bit per pixel YCbCr 4:2:2 BT.1120 component digital video. A configurable 20-bit wide parallel digital video input bus is provided, with associated pixel clock and H/V/F timing signal inputs.

The GV7700 supports the insertion of ancillary data into the horizontal blanking of the video data stream. User data can be programmed via the GSPI, allowing downstream communication from the video source to sink device. The ancillary data packing format is compliant with HDcctv 2.0 communications protocol.

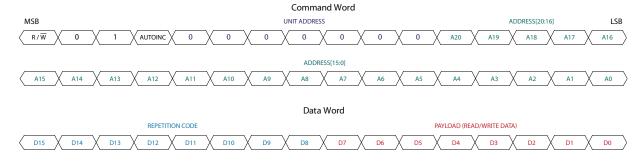

The device includes a 4-wire Gennum Serial Peripheral Interface (GSPI 2.0) for external host command and control. All read or write access to the GV7700 is initiated and terminated by the application host processor. The host interface is provided to allow optional configuration of some of the functions and operating modes of the GV7700.

It is recommended to use the integrated low-noise crystal oscillator and an external crystal as the primary reference clock for the GV7700. This configuration will yield the optimal jitter performance. Degraded performance will likely occur when using a PCLK input from the ISP which typically has much more jitter. A derived clock must be used as the clock reference by the Image Signal Processing (ISP) IC to avoid any frequency mismatch. In this case, connect the GV7700's XTAL\_OUT pin to the ISP's reference frequency input. Crystal values of 27MHz or 54MHz may be used, depending on the ISP requirement. XTAL54\_SEL must be HIGH when using a 54MHz crystal and LOW when using a 27MHz crystal.

Jitter performance is only guaranteed when using a crystal (27/54MHz) as the clock reference for the device. Jitter performance is not guaranteed when using the PCLK clock generated by the ISP as the reference for the device.

# 4.2 Parallel Video Data Inputs DIN\_[19:0]

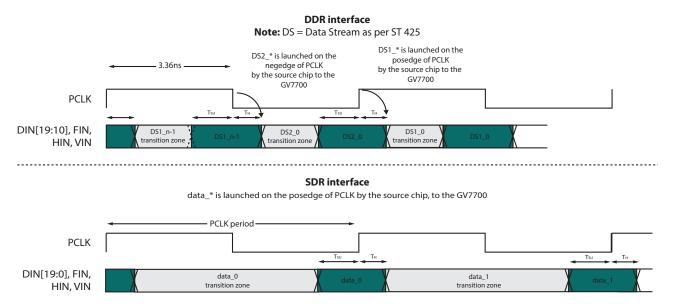

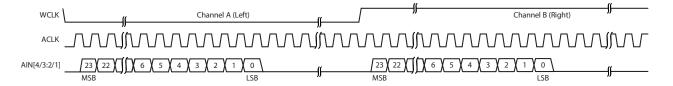

Data signal inputs enter the device on the rising edge of PCLK, as shown in Figure 4-1.

Figure 4-1: GV7700 Video Interface Timing Diagram

**Table 4-1: GV7700 Parallel Input AC Electrical Characteristics**

| Parameter              | Symbol         | Conditions     | Min | Тур | Max | Units |

|------------------------|----------------|----------------|-----|-----|-----|-------|

| Input data set-up time | $T_{SU}$       | 50% levels;    | 1.2 | _   | _   | ns    |

| Input data hold time   | T <sub>H</sub> | 1.8V operation | 0.8 | _   | _   | ns    |

The GV7700 is a high performance serial digital video and audio transmitter. Source series termination resistors should be used to minimize reflections on the parallel video data inputs, PCLK, audio inputs, and H, V, F timing input signals. This will ensure that signals are received correctly by the GV7700. Resistors must be placed at the signal source away from the GV7700 inputs.

# 4.2.1 Parallel Input In Video Mode

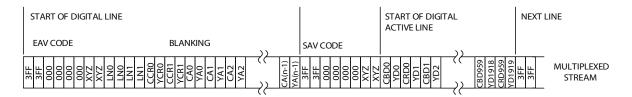

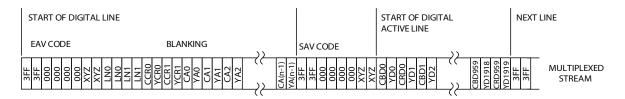

Data must be presented to the input bus in either multiplexed or demultiplexed form, depending on the setting of the BIT20\_BIT10 pin.

When operating in 20-bit mode (BIT20\_BIT10 = HIGH), the input data format must be word aligned, demultiplexed Luma and Chroma data. The Luma (Y) data must be presented on the DIN[19:10] pins, and the Chroma (Cb/Cr) data must be presented on the DIN[9:0] pins.

When operating in 10-bit mode (BIT20\_BIT10 = LOW), the input data format must be word aligned, multiplexed Luma and Chroma data. In this mode, the data must be presented on the DIN[19:10] pins. The DIN[9:0] inputs are ignored and should be tied to ground.

When operating in 10-bit mode (BIT20\_BIT10 = LOW) with 3G video (THREEG\_ $\overline{\text{HD}}$  = HIGH), the PCLK input is DDR 148.5MHz.

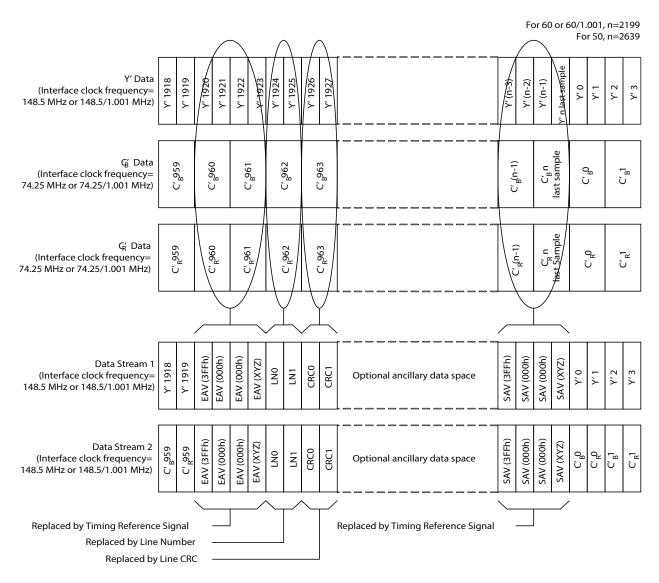

### 4.2.1.1 High Definition Video Input Formats

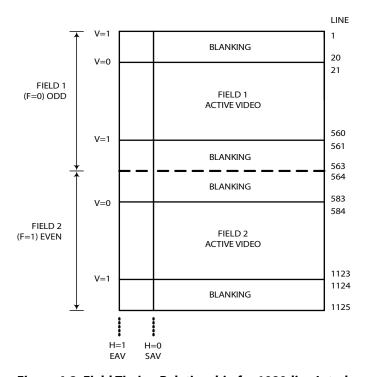

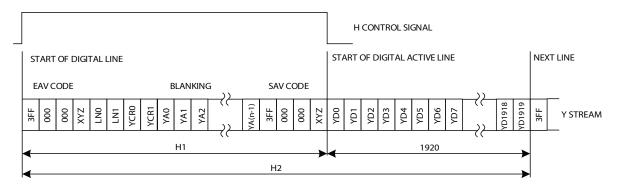

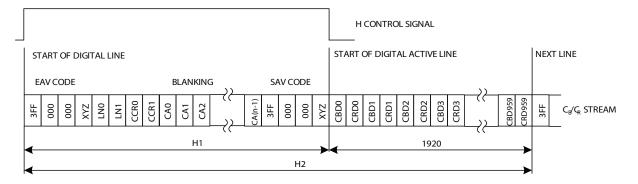

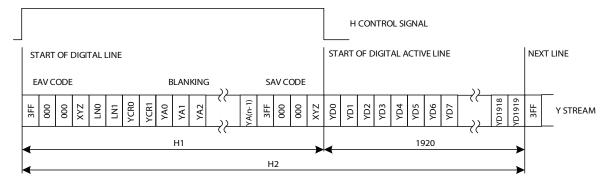

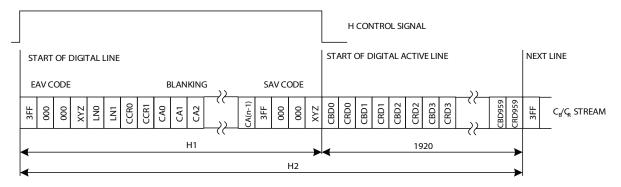

ITU-R BT.1120 describes the serial and parallel format for 1080-line interlaced and progressive digital video. The field/frame blanking period (V), the line blanking period (H), and the field identification (F), are embedded as digital timing codes (TRS) within the video. Data is transmitted over two 10-bit buses, one for Luma (Y') and one for colour difference ( $C'_BC'_R$ ), operating at a clock rate of 74.25MHz or 74.25/1.001MHz.

The following figures show horizontal and vertical timing for 1080-line interlaced systems.

Figure 4-2: Field Timing Relationship for 1080-line Interlaced Systems

Figure 4-3: Luma Stream Over One Video Line - 1080i

Rev.8

March 2016

Figure 4-4: Chroma Stream Over One Video Line - 1080i

Figure 4-5: Multiplexed Luma and Chroma Over One Video Line - 1080i

**Table 4-2: 1080-line Interlaced Horizontal Timing**

| Interlaced | 60Hz or 60/1.001Hz | 50Hz |

|------------|--------------------|------|

| H1         | 280                | 720  |

| H2         | 2200               | 2640 |

### 4.2.1.2 High Definition 1080p Input Formats

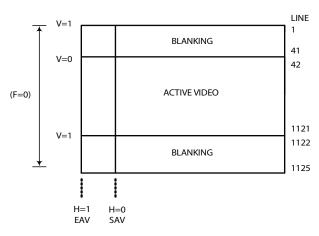

ITU-R BT.1120 also includes progressive scan formats with 1080 active lines, with Y'C' $_B$ C' $_R$ 4:2:2 sampling at pixel rates of 74.25MHz or 74.25/1.001MHz. The following diagrams show horizontal and vertical timing for 1080-line progressive systems.

Figure 4-6: Frame Timing Relationship For 1080-line Progressive Systems

Figure 4-7: Luma Stream Over One Video Line - 1080p

Figure 4-8: Chroma Stream Over One Video Line - 1080p

Figure 4-9: Multiplexed Luma and Chroma Over One Video Line - 1080p

**Table 4-3: 1080-line Progressive Horizontal Timing**

| Progressive | 30Hz, 30/1.001Hz,<br>60Hz, 60/1.001Hz | 25Hz or 50Hz | 24Hz or<br>24/1.001Hz |

|-------------|---------------------------------------|--------------|-----------------------|

| H1          | 280                                   | 720          | 830                   |

| H2          | 2200                                  | 2640         | 2750                  |

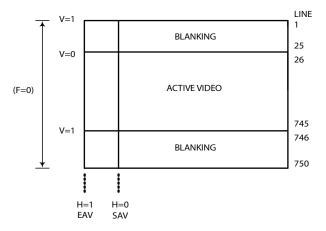

### 4.2.1.3 High Definition 720p Input Formats

The Society of Motion Picture and Television Engineers (SMPTE) defines the standard for progressive scan 720-line HD image formats. SMPTE ST 296-2001 specifies the representation for 720p digital Y'C' $_B$ C' $_R$  4:2:2 signals at pixel rates of 74.25MHz or 74.25/1.001MHz.

Figure 4-10: 720p Digital Vertical Timing

The frame rate determines the horizontal timing, which is shown in Table 4-4.

**Table 4-4: 720p Horizontal Timing**

| Frame Rate     | H = 1 Sample Number | H = 0 Sample Number | Total Samples Per Line |

|----------------|---------------------|---------------------|------------------------|

| 25             | 1280                | 0                   | 3960                   |

| 30 or 30/1.001 | 1280                | 0                   | 3300                   |

| 50             | 1280                | 0                   | 1980                   |

| 60 or 60/1.001 | 1280                | 0                   | 1650                   |

### 4.2.1.4 3G-SDI 1080p Input Formats

The Society of Motion Picture and Television Engineers (SMPTE) defines the standard for 3G-SDI image formats in ST 425. The GV7700 supports 1080p50/60 Y'C' $_B$ C' $_R$  4:2:2 8/10-bit.

Figure 4-11: 20-bit Mapping Structure for 1920 x 1080 50/60Hz Progressive 4:2:2 (Y'C'BC'R) 8/10-bit Signals

Table 4-5: 1080p Y'C'<sub>B</sub>C'<sub>R</sub> 4:2:0 & 4:2:2 10-bit Bit Structure Mapping

| Data Stream |   | Bit Number                            |   |   |   |   |   |   |   |   |

|-------------|---|---------------------------------------|---|---|---|---|---|---|---|---|

| Data Stream | 9 | 8                                     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| DS1         |   | Y'[9:0]                               |   |   |   |   |   |   |   |   |

| DS2         |   | C' <sub>B</sub> C' <sub>R</sub> [9:0] |   |   |   |   |   |   |   |   |

**Note:** For 8-bit systems, the data should be justified to the most significant bit (Y'9 and  $C'_BC'_B9$ ), with the two least significant bits (Y'[1:0] and  $C'_BC'_R[1:0]$ ) set to zero.

# 4.3 Video Processing

The GV7700 is designed to carry out data scrambling according to ITU-R BT.1120, and to carry out NRZ to NRZI encoding prior to presentation to the parallel to serial converter.

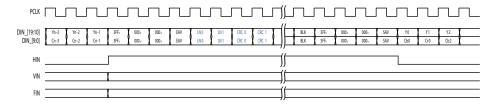

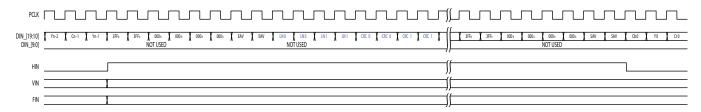

### 4.3.1 H:V:F Timing

The GV7700 can automatically detect the video standard and generate all internal timing signals. The total line length, active line length, total number of lines per field/frame and total active lines per field/frame are calculated for the received parallel video.

When DETECT\_TRS is LOW, the video standard and timing signals are based on the externally supplied horizontal blanking, vertical blanking, and field identification signals. These signals go to the HIN, VIN, and FIN pins respectively. When DETECT\_TRS is HIGH, the video standard timing signals are extracted from the embedded TRS ID words in the parallel input data. Both 8-bit and 10-bit TRS code words are identified by the device.

The GV7700 determines the video standard by timing the horizontal and vertical reference information supplied at the HIN, VIN, and FIN input pins, or contained in the TRS ID words of the received video data. Therefore, full synchronization to the received video standard requires at least one complete video frame.

Once synchronization has been achieved, the GV7700 continues to monitor the received TRS timing or the supplied H, V, and F timing information to maintain synchronization. The GV7700 loses all timing information immediately following loss of H, V, and F.

The timing of these signals is shown in Figure 4-12 to Figure 4-13 below.

Figure 4-12: H:V:F Input Timing — HD 20-bit Input Mode

Figure 4-13: H:V:F Input Timing — HD 10-bit Input Mode

## 4.4 HD-VLC™ Encoder

The GV7700 integrates the High Definition Visually Lossless CODEC (HD-VLC) encoder for extended reach video transmission. When used in conjunction with the GV7704 HD-VLC Quad Receiver, HD video transmission can be extended significantly over existing HD serial digital video systems. HD-VLC is based on a simple visually lossless implementation of the Dirac compression tool kit. The visually lossless encoder is used to reduce the video bandwidth, using a very low latency mode, from a transmission rate of 1.485Gb/s (HD-SDI) to 270Mb/s (SD-SDI).

At a data rate of 270Mb/s, the serial digital encoded HD video can be transmitted over longer runs of coaxial cable. Table 4-6 below shows a comparison of cable distances between HD video transmission at 1.485Gb/s and HD-VLC encoded at 270Mb/s for various common coaxial cable types.

**Table 4-6: Cable Reach for Various Cable Types (In Meters)**

| Cable Type                     | HD-VLC:<br>270Mb/s (m) | HD-VLC:<br>540Mb/s (m) | HD-SDI:<br>1.485Gb/s (m) | 3G-SDI:<br>2.97Gb/s (m) |

|--------------------------------|------------------------|------------------------|--------------------------|-------------------------|

| Belden 1694A / Canare L-4.5CHD | 710                    | 400                    | 230                      | 80                      |

| Belden 543945                  | 550                    | 300                    | 150                      | 50                      |

| KW-Link SYV 75-5               | 500                    | 275                    | 140                      | 50                      |

| Canare L-3C2V                  | 300                    | 160                    | 95                       | 30                      |

| KW-Link SYV 75-3               | 300                    | 160                    | 80                       | 30                      |

Note: These values apply for new, properly terminated cables. Actual performance may vary.

**Note:** Longer cable reach performance at both 3G and 540M is possible; up to 100m at 3G and 400m at 540M can be achieved using Belden 543945. However, GV7704 lock times can increase significantly at these cable ranges, and may exceed the lock time requirements of the intended application.

After transmission over the coaxial cable, the 270Mb/s serial data is recovered using the GV7704 HD-VLC Quad Receiver and the data decoded back to the native HD format. The encoding and decoding process has a total latency of 12-14 HD lines, which makes the CODEC ideal for low latency real-time applications. Table 4-7 below shows the total encode/decode latency through the GV7700 and the GV7704.

Table 4-7: Encode and Decode Total Latency (GV7700 + GV7704)

| Video Format | Delay (μs) | Delay (HD/3G Lines) |

|--------------|------------|---------------------|

| 1080p25      | 422.2      | 11.9                |

| 1080p29.97   | 368.8      | 12.4                |

| 1080p30      | 368.4      | 12.4                |

| 720p25       | 635.1      | 11.9                |

| 720p29.97    | 546.6      | 12.2                |

| 720p30       | 546.6      | 12.2                |

| 720p50       | 368.6      | 13.8                |

| 720p59.94    | 324.2      | 14.5                |

| 720p60       | 324.2      | 14.5                |

| 1080p60      | 184.2      | 12.4                |

| 1080p59.94   | 184.4      | 12.4                |

| 1080p50      | 211.1      | 11.9                |

The HD-VLC encoder can be enabled by setting the HDVLC\_EN input pin HIGH. When this pin is set HIGH, the GV7700 will output HD encoded video at 270Mb/s and 3G encoded video at 540Mb/s. Configuration pins should be set prior to device reset. The 270Mb/s data stream uses the same timing and frame structure as Standard Definition SDI (SD-SDI), and can be monitored using standard SD-SDI test equipment to check signal integrity. However, the data contained within the active picture area of the SD-SDI stream contains only encoded HD packets. The HD video content can only be viewed after the HD-VLC decoding process.

When the GV7700 is HD-VLC encoding video formats at "true" 30 or 60 frames per second, the 270Mb/s (540Mb/s) serial data output will actually operate at 270x1.001Mb/s (540x1.001Mb/s). This multiplication factor is to account for the fractional increase in the original HD video frame rate. For all other HD frame rates, the GV7700 serial data output will be exactly 270Mb/s (540Mb/s).

# 4.5 Stream ID Packet Insertion

The GV7700 will always insert Stream ID packets immediately after the CRC1 word of the Y channel if the chip is in Reclocker mode (HDVLC\_EN = 0) or immediately after the CRC1 word of the YCbCr multiplexed data if the chip is in HD-VLC compression mode (HDVLC\_EN = 1).

The chip will insert the Stream ID packet on the following lines shown in Table 4-8 below.

**Table 4-8: Stream ID Line Insertion for Video Standards**

| Input Video<br>Standard | HDVLC_EN | Output Video<br>Standard | Line Number for Insertion |

|-------------------------|----------|--------------------------|---------------------------|

| 720-25                  | 0        | 720p25                   | 8                         |

| 720p25                  | 1        | 625i50                   | 7, 320                    |

| 720~20.07               | 0        | 720p29.97                | 8                         |

| 720p29.97               | 1        | 525i59.94                | 11, 274                   |

| 720m20                  | 0        | 720p30                   | 8                         |

| 720p30                  | 1        | 525i60                   | 11, 274                   |

| 720550                  | 0        | 720p50                   | 8                         |

| 720p50                  | 1        | 625i25                   | 7, 320                    |

| 720mE0.04               | 0        | 720p59.94                | 8                         |

| 720p59.94               | 1        | 525i29.97                | 11, 274                   |

| 720-60                  | 0        | 720p60                   | 8                         |

| 720p60                  | 1        | 525i30                   | 11, 274                   |

| 1000 25                 | 0        | 1080p25                  | 8                         |

| 1080p25                 | 1        | 625i25                   | 7, 320                    |

| 1000-20 07              | 0        | 1080p29.97               | 8                         |

| 1080p29.97              | 1        | 525i29.97                | 11, 274                   |

| 1000 20                 | 0        | 1080p30                  | 8                         |

| 1080p30                 | 1        | 525i30                   | 11, 274                   |

| 1000:50                 | 0        | 1080i50                  | 8, 570                    |

| 1080i50 -               | 1        | 625i25                   | 7, 320                    |

| 1000:50.04              | 0        | 1080i59.94               | 8, 570                    |

| 1080i59.94              | 1        | 525i29.97                | 11, 274                   |

| 1000 60                 | 0        | 1080p60                  | 8                         |

| 1080p60                 | 1        | 525i69                   | 11, 274                   |

Table 4-8: Stream ID Line Insertion for Video Standards (Continued)

| Input Video<br>Standard | HDVLC_EN | Output Video<br>Standard | Line Number for Insertion |

|-------------------------|----------|--------------------------|---------------------------|

| 1080p59.94              | 0        | 1080p59.94               | 8                         |

| 1080p39.94 -            | 1        | 525i59.94                | 11, 274                   |

| 100050                  | 0        | 1080p50                  | 8                         |

| 1080p50                 | 1        | 625i50                   | 7, 320                    |

# 4.6 Audio Embedding

The GV7700 includes an Audio Multiplexer, which is enabled by setting the AUDIO\_EN pin HIGH. The device will embed audio in both HD and HD-VLC encoding modes.

The GV7700 can embed up to four channels of serial digital audio at an audio sampling rate of 32kHz, 44.1kHz, or 48kHz.

### 4.6.1 Serial Audio Data Inputs

The GV7700 supports the insertion of up to 4 channels of embedded audio, in one audio group according to SMPTE ST 299. When in HD-VLC mode (HDVLC\_EN = 1), the audio data packets will be inserted in the YCbCr multiplexed data. When HD-VLC encoding is disabled (HDVLC\_EN = 0), the audio data packets will be inserted in the C channel of the HD signal as per SMPTE ST 299.

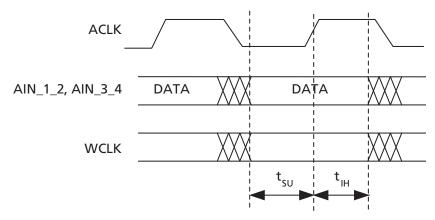

The four audio channels must be input as 2-channel pairs, timed to a serial bit clock (ACLK) at a frequency of  $64*f_s$ , and a word clock (WCLK) at a frequency of  $f_s$ , where  $f_s$  can be 32kHz, 44.1kHz, or 48kHz. The serial audio input format must conform to  $I^2$ S.

The serial audio input signals and WCLK input signals enter the device on the rising edge of ACLK as shown in Figure 4-14.

The audio sampling frequency can be programmed from the host interface by writing to the AUDIO\_SAMPLING\_FREQ bits in register 109. See Table 4-9 below.

Table 4-9: Audio Sampling Frequency Selection

| AUDIO_SAMPLING_FREQ | Input Audio Sampling<br>Rate |

|---------------------|------------------------------|

| 00                  | 48kHz                        |

| 01                  | 44.1kHz                      |

| 10                  | 32kHz                        |

Figure 4-14: ACLK to Audio Data and WCLK Signal Input Timing

Table 4-10: GV7700 Serial Audio Data Inputs - AC Electrical Characteristics

| Parameter              | Symbol          | Conditions                 | Min | Тур | Max | Units |

|------------------------|-----------------|----------------------------|-----|-----|-----|-------|

| Input data set-up time | t <sub>SU</sub> | 50% levels; 1.8V operation | 1.3 | _   | _   | ns    |

| Input data hold time   | t <sub>IH</sub> | 30% levels, 1.8v operation | 45  | _   | _   | ns    |

### 4.6.2 Serial I<sup>2</sup>S Audio Data Format

The GV7700 supports the I<sup>2</sup>S serial audio data format, as shown in Figure 4-15 below.

Figure 4-15: I<sup>2</sup>S Audio Input Format

### 4.6.3 Audio Mute

The GV7700 can mute either pair of input audio channels using 2 host interface control bits. The bits can mute channels 1 & 2 or channels 3 & 4. Channels 1 & 2 can be muted by asserting the MUTE\_1\_2 bit in the AUD\_INS\_CTRL\_REG register. Channels 3 & 4 can be muted by asserting the MUTE\_3\_4 bit in the AUD\_INS\_CTRL\_REG register. See Table 4-11.

By default, the 4 channels will not be muted.

**Table 4-11: Audio Mute Controls**

| Address                 | Parameter | Description                                                           |

|-------------------------|-----------|-----------------------------------------------------------------------|

| 486F <sub>h</sub> [1:1] | MUTE_3_4  | HIGH = Channels 3 & 4 are muted<br>LOW = Channels 3 & 4 are not muted |

| 486F <sub>h</sub> [0:0] | MUTE_1_2  | HIGH = Channels 1 & 2 are muted<br>LOW = Channels 1 & 2 are not muted |

### 4.6.4 ECC Error Detection and Correction

For audio embedding in HD video formats, the packeted audio sample data is protected from bit errors using error correction codes (ECC). The error correction codes are carried in the same packet as the audio sample data for error detection and correction in the GV7704 receiver. The GV7700 uses BCH(31,25) code for ECC.

The GV7700 automatically generates the error detection and correction fields in the audio data packets.

# 4.7 Ancillary Data Insertion

The horizontal blanking region of a digital video signal may be used to carry ancillary data packets. The vertical blanking region is used by the HD-VLC encoder which inserts compression coefficients which cannot be overwritten. The payload of the ancillary data packet can be used to carry user-defined or proprietary data, which can be sent between an Aviia transmitter and receiver.

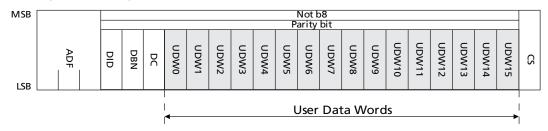

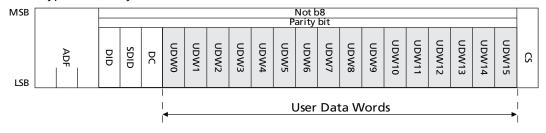

The ancillary data packet is formatted according to the Figure 4-16 below. The packet must always begin with the Ancillary Data Flag (ADF), defined as the following 10-bit word sequence: 000<sub>h</sub>, 3FF<sub>h</sub>, 3FF<sub>h</sub>.

The next data word is the 8-bit Data ID (DID), used to define the contents of the packet. For example, a unique DID can be used to denote alarm data, with another DID to denote status data. The 8-bit DID is written to the ANC\_INS\_DID bits of the ANC\_INS\_DID\_REG register.

After the DID insertion, there are two possible options, as shown in Figure 4-16.

#### Type 1 Ancillary Data Packet

Type 2 Ancillary Data Packet

Figure 4-16: Ancillary Data Packets

A Type 1 packet defines an 8-bit Data Block Number (DBN) sequence, used to distinguish successive packets with the same DID. The DBN simply increments with each packet of the same DID, between 0 and 15.

For a Type 2 packet, an 8-bit Secondary Data ID (SDID) word is defined, which can be used to denote variants of payloads with the same DID. For example, packets with a DID to denote error data may distinguish different error types using unique SDID's. The SDID or DBN word is written to the ANC\_INS\_SDID bits of the ANC\_INS\_SDID\_REG register.

After the DBN or SDID, the next data word is the 8-bit Data Count (DC). This word must be set to the number of user data words (UDW) that follow the DC, and must not exceed 16 (maximum payload size). The Data Count (DC) word is written to the ANC\_INS\_DC bits of the ANC\_INS\_DC\_REG register. The valid range for this word is 00000001<sub>b</sub> to 00010000<sub>b</sub>.

The final word of the ancillary data packet is the 9-bit Checksum (CS). The CS value must be equal to the nine least significant bits of the sum of the nine least significant bits of the DID, the DBN or the SDID, the DC and all user data words (UDW) in the packet. The CS value is automatically calculated by the GV7700, so no user configuration is required.

For HD video formats, the GV7700 only inserts ancillary data packets in the Luma channel.

Data words may be inserted on any line in the horizontal blanking region by writing the line number to the two bit slices ANC\_INS\_LINE\_NUMBER\_10\_8 and ANC\_INS\_LINE\_NUMBER\_7\_0.

The three most significant bits of the line number (bits 10:8) are written to ANC\_INS\_LINE\_NUMBER\_10\_8, and the remaining eight bits (bits 7:0) are written to ANC\_INS\_LINE\_NUMBER\_7\_0. An example is illustrated in Table 4-12 below.

**Table 4-12: Examples of Ancillary Data Insertion Line Number Selection**

| ANC_INS_LINE_NUMBER_10_8 | ANC_INS_LINE_NUMBER_7_0 | Horizontal Line Number Insertion |  |

|--------------------------|-------------------------|----------------------------------|--|

| 000                      | 0000001                 | 1                                |  |

| 100                      | 01100101                | 1125                             |  |

Up to 23 Data Words may be inserted per frame with all Data Words — including the ancillary packet ADF, DID, SDID/DBN, DC, and CSUM words — being provided by the user via host interface configuration.

User configuration of the ancillary data insertion function includes the following information:

- Line Number for Insertion any line in the Horizontal blanking region may be programmed for ancillary data insertion

- Total number of words to insert includes all data words for all ancillary packets to be inserted on each line

- Ancillary data up to 23 user data words may be inserted

- Operating Mode two modes of operation can be selected:

- Continuous Mode (ANC\_INS\_SELECT = 0) the data packet will be inserted

continuously each time the current line number equals the line number

specified through the ANC\_INS\_LINE\_NUMBER\_10\_8 and

ANC\_INS\_LINE\_NUMBER\_7:0 bits in the host interface.

- One-time Mode (ANC\_INS\_SELECT = 1) the data packet will be inserted once, and then it will not be inserted again until the host resets the ANC\_INS\_ENABLE signal LOW, and then sets it HIGH.

# 4.8 Additional Processing Functions

#### 4.8.1 Test Pattern Generation

The GV7700 supports test pattern generation through CSR configuration. Two types of patterns are supported:

- Flat-field pattern (a single programmable colour for the whole active picture)

- Pathological pattern

Test pattern generation is enabled via the INSERT\_TEST\_PAT\_ENABLE bit of the TPG\_CTRL\_REG register. When this bit is HIGH, test patterns are inserted into the active picture region of the incoming video data.

The type of test pattern is determined by the PATTERN\_SEL bit of the TPG\_CTRL\_REG register, shown in Table 4-13 below.

**Table 4-13: Test Pattern Type Selection**

| PATTERN_SEL | Output Test Pattern |

|-------------|---------------------|

| 0           | Pathological        |

| 1           | Flat-field          |

The following is an example of how to program a Flat-field Red test pattern (PATTERN\_SEL = 1). The pixel setting registers, and the required values to write to the registers, are shown in Table 4-14 below.

Note that when HD-VLC encoding is enabled, the pixel registers are programmed with the same values as when HD-VLC encoding is disabled.

**Table 4-14: Flat-Field Red Test Pattern**

| Parameter      | Bit Value        | Pixel Value         | Channel Outputs<br>(HDVLC_EN = 0)                                                                                                   | Channel Outputs<br>(HDVLC_EN = 1)                                                                                                                                                 |  |

|----------------|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIXELO_YO_9_8  | 0 <sub>d</sub>   | – 0FC <sub>h</sub>  |                                                                                                                                     |                                                                                                                                                                                   |  |

| PIXEL0_Y0_7_0  | 252 <sub>d</sub> | - or c <sub>h</sub> | Y Channel:<br>- 0FC <sub>h</sub> - 0FC <sub>h</sub> - 0FC <sub>h</sub> - 0FC <sub>h</sub> -                                         | <b>YCbCr Channel:</b><br>198 <sub>h</sub> – 0FC <sub>h</sub> – 3C0 <sub>h</sub> – 0FC <sub>h</sub> – 198 <sub>h</sub> –<br>0FC <sub>h</sub> – 3C0 <sub>h</sub> – 0FC <sub>h</sub> |  |

| PIXEL0_Y1_9_8  | 0 <sub>d</sub>   | – 0FC <sub>h</sub>  | $0FC_h - 0FC_h - 0FC_h$                                                                                                             |                                                                                                                                                                                   |  |

| PIXEL0_Y1_7_0  | 252 <sub>d</sub> | - or c <sub>h</sub> |                                                                                                                                     |                                                                                                                                                                                   |  |

| PIXELO_CBO_9_8 | 1 <sub>d</sub>   | – 198 <sub>h</sub>  |                                                                                                                                     |                                                                                                                                                                                   |  |

| PIXELO_CBO_7_0 | 152 <sub>d</sub> | – 150 <sub>h</sub>  | <b>C Channel:</b> - 198 <sub>h</sub> - 3C0 <sub>h</sub> - 198 <sub>h</sub> - 3C0 <sub>h</sub> - 198 <sub>h</sub> - 3C0 <sub>h</sub> |                                                                                                                                                                                   |  |

| PIXELO_CRO_9_8 | 3 <sub>d</sub>   | - 3C0 <sub>h</sub>  |                                                                                                                                     |                                                                                                                                                                                   |  |

| PIXELO_CRO_7_0 | 192 <sub>d</sub> | – 3co <sub>h</sub>  |                                                                                                                                     |                                                                                                                                                                                   |  |

**Note:** All "PIXEL1" registers, from register address  $48A0_h$  to  $48A7_h$ , are not required for programming Flat-field test patterns. They may all be set to "0000h"

In order to generate a pathological test pattern as per SMPTE recommended practice RP 198, the GV7700 should be configured as shown in Table 4-15 below.

Table 4-15: Pathological Test Pattern (SMPTE RP 198 Recommended)

| Parameter               | Bit Value        | Pixel Value        | Channel Outputs                                                                                                                                                           |  |

|-------------------------|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Equalizer Test Signal   |                  |                    |                                                                                                                                                                           |  |

| PIXELO_YO_9_8           | 1 <sub>d</sub>   | - 198 <sub>b</sub> |                                                                                                                                                                           |  |

| PIXELO_YO_7_0           | 152 <sub>d</sub> | - 150h             | <b>Y Channel:</b><br>198 <sub>h</sub> – 198 <sub>h</sub> – 198 <sub>h</sub> –                                                                                             |  |

| PIXEL0_Y1_9_8           | 1 <sub>d</sub>   | - 198 <sub>h</sub> | 198 <sub>h</sub> - 198 <sub>h</sub> - 198 <sub>h</sub> -<br>198 <sub>h</sub> - 198 <sub>h</sub>                                                                           |  |

| PIXELO_Y1_7_0           | 152 <sub>d</sub> | - 190h             | 150 <sub>h</sub> 150 <sub>h</sub>                                                                                                                                         |  |

| PIXELO_CBO_9_8          | 3 <sub>d</sub>   | - 300 <sub>h</sub> |                                                                                                                                                                           |  |

| PIXELO_CBO_7_0          | 0 <sub>d</sub>   | - 300 <sub>h</sub> | C Channel:<br>300 <sub>h</sub> - 300 <sub>h</sub> - 300 <sub>h</sub> -<br>300 <sub>h</sub> - 300 <sub>h</sub> - 300 <sub>h</sub> -<br>300 <sub>h</sub> - 300 <sub>h</sub> |  |

| PIXELO_CRO_9_8          | 3 <sub>d</sub>   | - 300 <sub>h</sub> |                                                                                                                                                                           |  |

| PIXEL0_CR0_7_0          | 0 <sub>d</sub>   | - 300 <sub>h</sub> | 1111                                                                                                                                                                      |  |

| PLL Test Signal (See No | te 1 <b>)</b>    |                    |                                                                                                                                                                           |  |

| PIXEL1_Y0_9_8           | 1 <sub>d</sub>   | - 110 <sub>h</sub> | y el l                                                                                                                                                                    |  |

| PIXEL1_Y0_7_0           | 16 <sub>d</sub>  | - ITOn             | Y Channel: $ 110_{h} - 110_{h} $                                                                    |  |

| PIXEL1_Y1_9_8           | 1 <sub>d</sub>   | - 110 <sub>h</sub> |                                                                                                                                                                           |  |

| PIXEL1_Y1_7_0           | 16 <sub>d</sub>  | - ITOh             | anan                                                                                                                                                                      |  |

| PIXEL1_CB0_9_8          | 2 <sub>d</sub>   | - 200 <sub>h</sub> | c cl .                                                                                                                                                                    |  |

| PIXEL1_CB0_7_0          | 0 <sub>d</sub>   | - 200 <sub>h</sub> | <b>C Channel:</b> 200 <sub>h</sub> – 200 <sub>h</sub> –                                                                                                                   |  |

| PIXEL1_CR0_9_8          | 2 <sub>d</sub>   | 200 <sub>h</sub>   | 200 <sub>h</sub> - 200 <sub>h</sub>                                                           |  |

| PIXEL1_CR0_7_0          | 0 <sub>d</sub>   | - 200 <sub>h</sub> |                                                                                                                                                                           |  |