# **GPCE512A**

## SOUND CONTROLLER WITH 256 K x 16 MASK ROM

OCT. 02, 2013 Version 1.7

GENERALPLUS TECHNOLOGY INC. reserves the right to change this documentation without prior notice. Information provided by GENERALPLUS TECHNOLOGY INC. is believed to be accurate and reliable. However, GENERALPLUS TECHNOLOGY INC. makes no warranty for any errors which may appear in this document. Contact GENERALPLUS TECHNOLOGY INC. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by GENERALPLUS TECHNOLOGY INC. for any infringement of patent or other rights of third parties which may result from its use. In addition, GENERALPLUS products are not authorized for use as critical components in life support devices/systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Generalplus.

### **Table of Contents**

#### **PAGE**

| 1.  | GENERAL DESCRIPTION                                                       | 3    |

|-----|---------------------------------------------------------------------------|------|

| 2.  | APPLICATION FIELD                                                         | 3    |

| 3.  | FEATURES                                                                  | 3    |

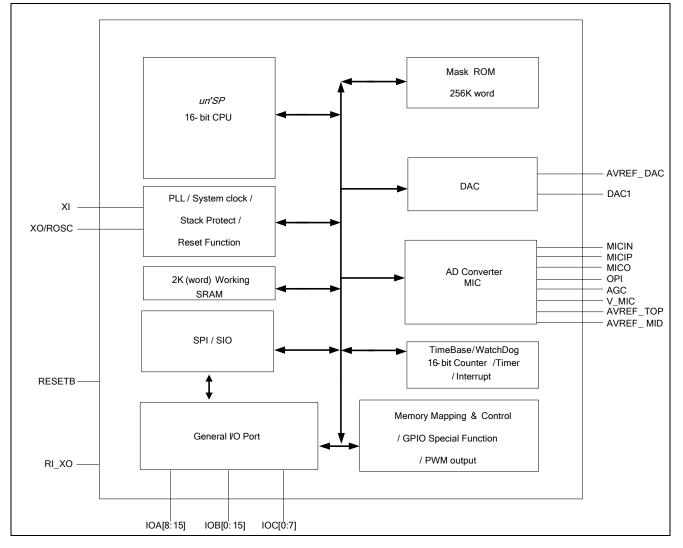

| 4.  | BLOCK DIAGRAM                                                             | 4    |

| 5.  | SIGNAL DESCRIPTIONS                                                       | 5    |

|     | 5.1. PAD Assignment                                                       | 6    |

| 6.  | FUNCTIONAL DESCRIPTION                                                    | 7    |

|     | 6.1. CPU                                                                  | 7    |

|     | 6.2. MEMORY                                                               | 7    |

|     | 6.3. PLL, CLOCK, POWER SAVING MODE                                        | 7    |

|     | 6.4. Power Saving Mode                                                    | 7    |

|     | 6.5. CPU HALT MODE                                                        | 8    |

|     | 6.6. Low Voltage Detection and Low Voltage Reset                          | 8    |

|     | 6.7. INTERRUPT                                                            | 8    |

|     | 6.8. I/O                                                                  | 9    |

|     | 6.9. TIMER/COUNTER                                                        | 11   |

|     | 6.10.SLEEP MODE, WAKEUP, HALT MODE, AND WATCHDOG                          | . 12 |

|     | 6.11. ADC (Analog to Digital Converter)                                   | . 12 |

|     | 6.12.16 Bits DAC Audio Driver                                             | . 12 |

|     | 6.13. Serial interface I/O (SIO)                                          | . 12 |

|     | 6.14.SPI                                                                  | . 13 |

|     | 6.15.Audio Algorithm                                                      | . 13 |

| 7.  | ELECTRICAL SPECIFICATIONS                                                 | . 14 |

|     | 7.1. Absolute Maximum Ratings                                             | . 14 |

|     | 7.2. DC CHARACTERISTICS (VDD = 3.3V, VDDIO = 5V, $T_A$ = 25 $^{\circ}$ C) | . 14 |

|     | 7.3. ADC CHARACTERISTICS (AVDD = 3.3V, $T_A = 25^{\circ}C$ )              | . 15 |

|     | 7.4. DAC CHARACTERISTICS (AVDD = 3.3V, $T_A$ = 25°C)                      | . 15 |

| 8.  | APPLICATION CIRCUITS                                                      | . 17 |

|     | 8.1. APPLICATION CIRCUIT 1 (WITH CRYSTAL, DAC OUTPUT)                     | . 17 |

|     | 8.2. APPLICATION CIRCUIT (WITH R-OSCILLATOR, DAC OUTPUT)                  | . 18 |

| 9.  | PACKAGE/PAD LOCATIONS                                                     | . 19 |

|     | 9.1. ORDERING INFORMATION                                                 | . 19 |

| 10  | DISCLAIMER                                                                | . 20 |

| 11. | REVISION HISTORY                                                          | . 21 |

### SOUND CONTROLLER WITH 256 K x 16 MASK ROM

#### **1. GENERAL DESCRIPTION**

The GPCE512A is equipped with the newest 16-bit CPU µ'nSP® (read as "micro-n-SP") designed by SUNPLUS. It's high processing speed empowered the  $\mu$ 'nSP<sup>TM</sup> ISA 1.3 capable of handling sophisticated digital signal processes (DSP) computation easily. The wide range of CPU speed, from 0.1875MHz to 48MHz, makes the GPCE512A to be easily applied in different kinds of applications. The built-in memory contains 256K-word mask ROM and 2K-word working SRAM. Other features including 32 programmable multi-functional I/Os, three 16-bit timers/counters, 32768Hz Real Time Clock, Low Voltage Reset/Detection, eight channels of 12-bit ADC (one channel built-in MIC amplifier with Auto Gain Controller). One very important feature is GPCE512A built-in very high quality, one 16-bit DACs, this provides GPCE512A being able to output very high quality sound and music. Another two IO PWM outputs provide the convenience of generating some duty-cycle wave form signals. A power saving mode, halt mode, is designed to only stop CPU clock but reserve others. To save even more power, a sleep mode is available to stop all clocks. These two modes can be awakened from the I/O or interrupt source triggers.

#### 2. APPLICATION FIELD

- Intelligent interactive talking toys

- Advanced educational toys

- General speech synthesizer

- Long duration audio products

#### 3. FEATURES

- 16-bit µ'nSP<sup>™</sup> ISA 1.3 microprocessor

- CPU clock: 0.1875MHz 48MHz@6MHz crystal

- 256K-word mask ROM

- 2K-word CPU working SRAM

- Chip operating voltage: 2.7V 3.6V

- IO operating voltage: 2.7V 5.5V

- Total of 32 programmable IOs including IOA(8 pins), IOB(16 pins) and IOC(8 pins)

- Crystal Resonator & R-oscillator

- Standby mode (Clock Stop mode) for power savings

- Halt mode (only stops CPU clock) for power savings

- Three 16-bit timers/counters and One RTC

- One 16-bit DAC output

- Eight channels of 12-bit AD converter

- Wakeup source from IOA key, TIMER/RTC

- 32768Hz Real Time Clock (RTC)

- ADC external top reference voltage

- One Generalplus Serial interface I/O (SIO)

- One SPI serial interface I/O

- Built-in microphone amplifier and AGC function

- Low voltage reset and low voltage detection

- Watchdog function

#### 4. BLOCK DIAGRAM

#### 5. SIGNAL DESCRIPTIONS

| Mnemonic        | PIN No.            | Туре     | Description                                                                                   |  |  |

|-----------------|--------------------|----------|-----------------------------------------------------------------------------------------------|--|--|

| Port A, Port B, | Port C & Port D    |          |                                                                                               |  |  |

| IOA [15:8]      | 52 – 53, 55 - 60   | I/O      | IOA [15:8]: bi-directional I/O ports. It can be programmed as wakeup I/O pins.                |  |  |

| IOB [15:0]      | 61 - 76            | I/O      | IOB [15:0]: bi-directional I/O ports.                                                         |  |  |

| IOC [7:0]       | 31 - 38            | I/O      | IOC [7:0]: bi-directional I/O ports.                                                          |  |  |

| Power & GND     |                    |          |                                                                                               |  |  |

| VDDIO_1         | 39                 | Р        | Positive power supply for IOC [7:0].                                                          |  |  |

| VSSIO_1         | 40                 | G        | Ground reference for IOC [7:0].                                                               |  |  |

| VSSIO_2         | 41                 | G        | Positive power supply                                                                         |  |  |

| VDDIO_2         | 42                 | Р        | Ground reference                                                                              |  |  |

| VDDIO_3         | 77                 | Р        | Positive power supply for IOA [15:8], IOB [15:0].                                             |  |  |

| VSSIO_3         | 78                 | G        | Ground reference for IOA [15:8], IOB [15:0].                                                  |  |  |

| AVDD_1          | 22                 | Р        | Positive power supply for analog circuit including ADC & MIC.                                 |  |  |

| AVSS_1          | 21                 | G        | Ground reference for analog circuit including ADC & MIC.                                      |  |  |

| AVDD_2          | 18                 | Р        | Positive power supply for analog circuit including DAC.                                       |  |  |

| AVSS_2          | 20                 | G        | Ground reference for analog circuit including DAC.                                            |  |  |

| AVDD_3          | 4                  | Р        | Positive power supply for analog circuit including PLL, ROSC and OSC.                         |  |  |

| AVSS_3          | 2                  | G        | Ground reference for analog circuit including PLL, ROSC and OSC.                              |  |  |

| VDD             | 3                  | Р        | Positive power supply for digital circuit.                                                    |  |  |

| VSS             | 1                  | G        | Ground reference for digital circuit.                                                         |  |  |

| CLK System/ I   | CE Interface       |          |                                                                                               |  |  |

| XI              | 10                 | Ι        | Oscillator crystal input.                                                                     |  |  |

| XO / ROSC       | 9                  | 0        | Oscillator crystal output / ROSC-input at ROSC mode.                                          |  |  |

| Option          |                    | ·        |                                                                                               |  |  |

| TEST            | 8                  | Ι        | TEST Mode selection pin, high is test mode and low is normal mode (Pad internal pull low).    |  |  |

| RI_XO           | 43                 | I        | ROSC/Crystal selection pin, high is Crystal and low is R-oscillator (Pad internal pull high). |  |  |

| DAC             |                    |          |                                                                                               |  |  |

| DAC1            | 16                 | 0        | Audio DAC1 output.                                                                            |  |  |

| AVREF_DAC       | 19                 | 0        | DAC reference pin.                                                                            |  |  |

| DAC_EN          | 44                 | I        | DAC enable signal with pull high. We strongly recommend connecting it with power (ex. VDDIO)  |  |  |

| ADC             |                    |          |                                                                                               |  |  |

| MICIP           | 29                 | I        | MIC amplifier input positive (Internal Floating).                                             |  |  |

| MICIN           | 28                 | I        | MIC amplifier input negative (refer to application circuit).                                  |  |  |

| MICO            | 27                 | 0        | MIC amplifier output (refer to application circuit).                                          |  |  |

| OPI             | 26                 | I        | Audio amplifier negative input (refer to application circuit).                                |  |  |

| AGC             | 25                 | 10       | AGC by pass filter (refer to application circuit).                                            |  |  |

| V_MIC           | 24                 | 0        | Microphone power supply.                                                                      |  |  |

| AVREF_TOP       | 23                 | I        | AVREF_TOP input (ADC maximum value voltage) (refer to application circuit).                   |  |  |

| AVREF_MID       | 30                 | 0        | AVREF_TOP/2 output with buffer (~ ADC middle value voltage) (refer to application circuit).   |  |  |

| Other Signal    |                    |          |                                                                                               |  |  |

| RESETB          | 7                  | I        | System reset pin (active low) (internal 47Kohm pull high resistor).                           |  |  |

| NC              | 5-6 , 11-14 , 15 , | 17, 45-5 | 1 , 54 , 79-81                                                                                |  |  |

| Total: 81 pads  |                    |          |                                                                                               |  |  |

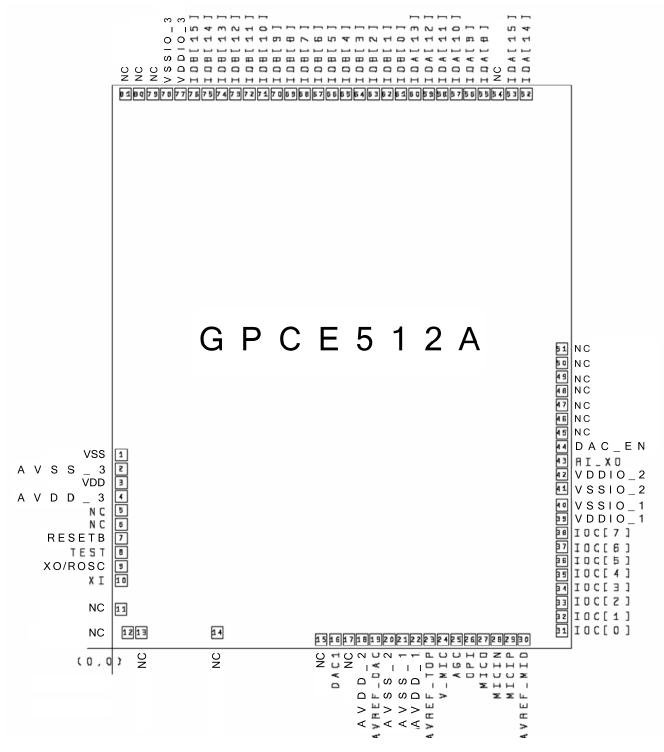

#### 5.1. PAD Assignment

This IC substrate should be connected to VSS

#### 6. FUNCTIONAL DESCRIPTION

#### 6.1. CPU

The GPCE512A is equipped with the newest 16-bit CPU  $\mu'nSP^{\circ}$  (read as "micro-n-SP") designed by SUNPLUS. Thirteen registers are available in  $\mu'nSP^{\circ}$ : R1 ~ R4 (General-purpose registers), SR1 ~ SR4 (Secondary Bank Registers), PC (Program Counter), SP (Stack Pointer), Base Pointer (BP), SR (Segment Register) and FR (Flag Register). It provides interrupts, including thirteen FIQs (Fast Interrupt Request) and fourteen IRQs (Interrupt Request), plus one software-interrupt, BREAK.

Moreover, a high performance hardware multiplier with the capability of FIR filter calculation is also built-in to reduce the software multiplication loading.

#### 6.2. Memory

#### 6.2.1. SRAM

The amount of SRAM is 2K-word (including Stack) ranged from \$0000 through \$07FF with two CPU-clock cycles access speed.

#### 6.2.2. Mask ROM

Mask ROM size is 256K words and its address is mapped from \$004000 to \$043FFF. This mask ROM is a high-speed memory, with 60ns access time. The mask option on GPCE512A is described below.

OPTION\_WDOG\_EN: enable or disable watchdog reset.

#### 6.3. PLL, Clock, Power Saving Mode

#### 6.3.1. PLL (Phase Lock Loop)

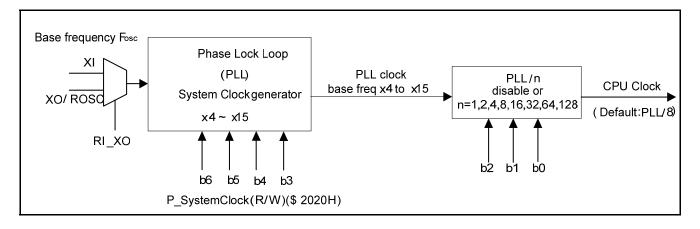

The purpose of PLL is to provide stable output frequency which reference a base frequency (from crystal). The PLL frequency gain (output frequency / input frequency) ranges from 4 to 15. Suppose base frequency is 6MHz and PLL frequency gain selects 8, the output frequency of PLL is 48MHz.

#### 6.3.1.1. System clock

Basically, the system clock is provided by PLL and determined by programming the P\_SystemClock. The default PLL clock (PLL) pumps to  $6*F_{OSC}$ , that is 36MHz using 6MHz crystal and CPU clock will also be 36MHz if PLL/8 not specified.

#### 6.3.1.2. 32768Hz RTC

The Real Time Clock (RTC) is normally used in watch, clock or other timing-based applications. A 2Hz-RTC (0.5 seconds) function is available in GPCE512A. The RTC counts the time as well as to wake CPU up whenever RTC occurs. Time can be traced by the numbers of RTC occurrence. In addition,

GPCE512A supports 32768Hz oscillator in strong mode and weak mode for power savings. In strong mode, 32768Hz OSC circuit in GPCE512A always runs at the highest power consumption. On the other hand, 32768Hz OSC in GPCE512A circuit run less power consumption in weak mode, but it must use a high-standard 32768Hz external crystal such as SEIKO SSP\_T6 or Microcrystal CC5V-T1A.

#### 6.4. Power Saving Mode

The GPCE512A features a power savings mode (or called standby mode) for low power applications. To enter standby mode, the desired key wakeup port(IOA[15:8]) must be configured to input first. And read the P\_IOA\_Data to latch the IOA state before entering the standby mode. Also remember to enable the corresponding interrupt source(s) for wakeup. After that, stop the CPU clock by writing \$5555 into P\_SystemSleep(W) to enter standby mode. In such mode, SRAM and I/Os remain in the previous states until CPU being awakened. The wakeup sources in GPCE512A include KEY wakeup (IOA[15:8]), RTC wakeup, and IRQ1 – IRQ7. After GPCE512A is awakened, CPU will continue to execute the program from the location it slept. Programmer

can also enable or disable the 32768Hz RTC when CPU is in standby mode.

#### 6.5. CPU Halt Mode

The GPCE512A features a CPU halt mode for power savings. In this mode, the CPU clock is turned off.

#### 6.6. Low Voltage Detection and Low Voltage Reset

#### 6.6.1. Low Voltage Detection (LVD)

The Low Voltage Detect (LVD) reports the circumstance of present voltage. There are four LVD levels to be selected: 2.6V, 2.8V, 3.0v and 3.2V. Those levels can be programmed via P\_LVD\_Ctrl. As an example, suppose LVD is given to 2.8V. When the voltage drops below 2.8V, the b12 of P\_LVD\_Ctrl is read as HIGH. In such state, program can be designed to react this condition.

#### 6.6.2. Low Voltage Reset (LVR)

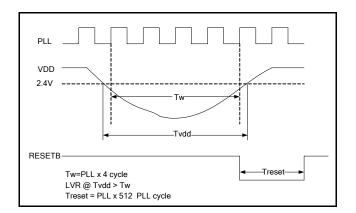

In addition to the LVD, the GPCE512A provides another important feature, Low Voltage Reset (LVR). With the LVR function, a reset signal is generated to reset system when the operating voltage drops below 2.4V for 4 consecutive PLL system clock cycles. Without LVR, the CPU becomes unstable and malfunctions when the operating voltage drops below 2.4V. Using LVR, it will reset all functions to the initial operational (stable) states when the voltage drops below 2.4V. The LVR function is always on in GPCE512A. A LVR timing diagram is given as follows:

#### 6.6.3. Watchdog reset

The GPCE512A provides another important feature, watchdog reset. With the watchdog function, a reset signal is generated to reset system when watchdog counter is overflow and the mask option of OPTION\_WDOG\_EN is enabled.

The purpose of watchdog is to monitor whether the system operates normally. Within a certain period, watchdog register must be cleared. If it is not cleared, CPU assumes the program

has been running in an abnormal condition. As a result, the CPU will reset the system to the initial state and start running the program all over again.

#### 6.6.4. Soft reset protection

Software reset. Writes \$5555 into P\_System\_Reset will reset the whole system like hardware reset (pull low RESETB pin), except a flag will set on in P\_System\_LVD\_Ctrl(R/W).

#### 6.6.5. Stack access protection

GPCE512A will reset when stack operation (example push or pop) of CPU accesses the SRAM that is not in the defined range. The defined stack range uses stack top (P\_Stack\_Top) and bottom (P\_Stack\_Bottom) control register.

#### 6.7. Interrupt

The GPCE512A has 14 interrupt sources, grouped into two types, FIQ (Fast Interrupt Request) and IRQ (Interrupt request). The priority of FIQ is higher than IRQ. An IRQ can be interrupted by a FIQ, but not by another IRQ. A FIQ cannot be interrupted by any other interrupt sources.

| Interrupt Source | Interrupt Name / FIQ Name | IRQ Priority |

|------------------|---------------------------|--------------|

| Timer A          | IRQ0_TMA/FIQ_TMA          | 1(High)      |

| Timer B          | IRQ1_TMB/FIQ_TMB          | 2            |

| Timer C          | IRQ2_TMC/FIQ_TMC          | 3            |

| SPI              | IRQ3_SPI/FIQ_SPI          | 4            |

| SIO              | IRQ3_SIO                  | 5            |

| Key wakeup       | IRQ5_KEY/FIQ_KEY          | 6            |

| EXT1             | IRQ5_EXT1/FIQ_EXT1        | 7            |

| EXT2             | IRQ5_EXT2/FIQ_EXT2        | 8            |

| 4096Hz           | IRQ6_4KHz/FIQ_4KHz        | 9            |

| 2048Hz           | IRQ6_2KHz/FIQ_2KHz        | 10           |

| 512Hz            | IRQ6_512Hz/FIQ_512Hz      | 11           |

| 64Hz             | IRQ7_64Hz/FIQ_64Hz        | 12           |

| 16Hz             | IRQ7_16Hz_FIQ_16Hz        | 13           |

| 2Hz              | IRQ7_2Hz/FIQ_2Hz          | 14(Low)      |

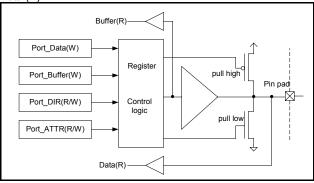

#### 6.8. I/O

Three I/O ports are built in GPCE512A - PortA, PortB and PortC, total has 32 bit-programmable I/Os. The PortA is a general purpose I/O with programmable wakeup capability, i.e. IOA [15:8] is the key wakeup port. To activate key wakeup function, latch data on P\_IOA\_Data and enable the key wakeup function. Wakeup is triggered when the PortA state is different from at the time latched. Furthermore, the I/O ports can be operated at 5V level, higher than the CPU core which is a 3V level system. Suppose system operating voltage is running at 3.3V, and then VDDIO (power for I/O) operates from 3.3V to 5.5V. In such condition, the I/O pad is capable of operating from 0V through VDDIO. The following diagram is an I/O schematic. Although data can be written into the same register through Port\_Data and Port\_Buffer, they can be read from different places, Buffer (R) and

#### Data (R).

In addition to a general purpose I/O port function, PortA/B/C also shares/carries some special functions. A summary of PortA/B/C special functions is listed as follows:

| Port    | Special Function | Function Description                                                                 |

|---------|------------------|--------------------------------------------------------------------------------------|

| IOA8    | APWMO1           | TimerA PWM output                                                                    |

| 10.40   | BPWMO1           | TimerB PWM output                                                                    |

| IOA9    | IROUT            | IR Output                                                                            |

| IOA10   | Feedback Output2 | Work with IOA11 by adding a RC circuit between them to get an OSC to EXT2 interrupts |

| 10.4.11 | Feedback Input2  | -                                                                                    |

| IOA11   | EXT2             | External interrupt source 2                                                          |

| IOA12   | Feedback Output1 | Work with IOA13 by adding a RC circuit between them to get an OSC to EXT1 interrupt  |

| 10.4.40 | Feedback Input1  | -                                                                                    |

| IOA13   | EXT1             | External interrupt source 1                                                          |

| IOA14   | RTCO             | Real time clock output                                                               |

| IOA15   | RTCI             | Real time clock input                                                                |

| IOB6    | APWMO2           | TimerA PWM output                                                                    |

| IOB7    | BPWMO2           | TimerB PWM output                                                                    |

| IOB10   | SDA              | Serial interface data                                                                |

| IOB11   | SCK              | Serial interface clock                                                               |

| IOB12   | CS               | SPI chip select                                                                      |

| IOB13   | СК               | SPI clock                                                                            |

| IOB14   | DI               | SPI data input                                                                       |

| IOB15   | DO               | SPI data output                                                                      |

| IOC0    | AN0              | ADC Channel 0                                                                        |

| IOC1    | AN1              | ADC Channel 1                                                                        |

| IOC2    | AN2              | ADC Channel 2                                                                        |

| IOC3    | AN3              | ADC Channel 3                                                                        |

| IOC4    | AN4              | ADC Channel 4                                                                        |

| IOC5    | AN5              | ADC Channel 5                                                                        |

| IOC6    | AN6              | ADC Channel 6                                                                        |

| IOC7    | AN7              | ADC Channel 7                                                                        |

### GPCE512A

Refer to the above table, the configuration of IOA10, IOA11, IOA12, and IOA13 involves feedback function that an OSC frequency can be obtained from EXT1 (EXT2) by simply adding a RC circuit between IOA10 (IOA12) and IOA11 (IOA13).

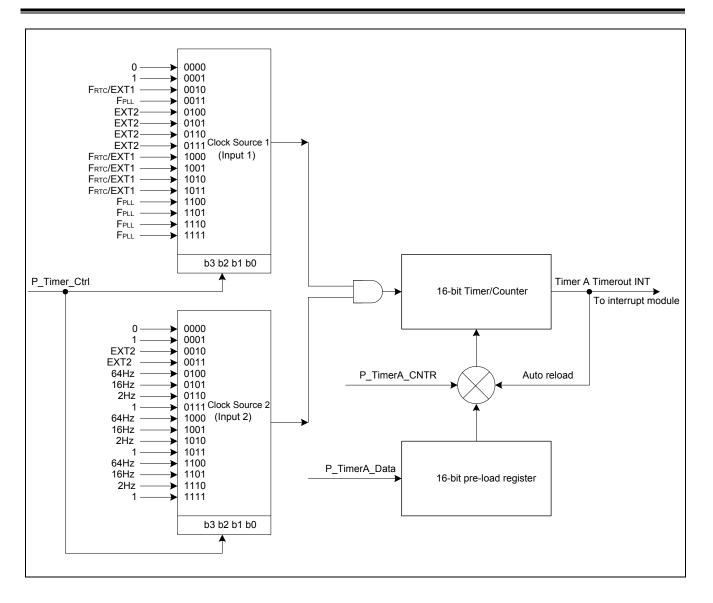

#### 6.9. Timer/Counter

GPCE512A provides three 16-bit timers/counters - TimerA, TimerB and TimerC, or so called universal counters. The clock source of Timer A/B/C are from clock source Input 1 and clock source Input 2 (see below table) which perform AND operation to form the varieties of combinations. When timer overflows, a timeout signal (TAOUT) is sent to CPU interrupt module to generate a timer interrupt signal. In addition, Timer A/ B/ C hardware interrupt events can be used to latch the DAC audio output and trigger ADC conversion.

Example to Timer A, sending a write signal into TMA\_CNT, the value of TMA\_DATA (value=N) will reload into TMA\_CNT and set an appropriated clock source. Timer up-counts from N, N+1, N+2... 0XFFFF. An INT signal is generated at the moment of timer rolling over from "0xFFFF" to "0x0000", and an INT signal is processed by INT controller immediately. At the same time, N will be reloaded into TMA\_CNT and start counting again.

In Timer A, the clock Input 1 is a high frequency source and clock Input 2 is a low frequency clock source. The combination of clock Input 1 and 2 provides varieties of speeds to TimerA/ CounterA - "1" representing pass signal (not gating), and "0" meaning timer deactivated. For instance, if Input 1="1", the clock is depending on Input 2. If Input 1="0", the TimerA is deactivated. The EXT1/ETX2 is the external clock source 1 and external clock source 2.

| TMXSEL | Input 1                 | Input 2 |

|--------|-------------------------|---------|

| 0000   | ʻ0'                     | ʻ0'     |

| 0001   | '1'                     | '1'     |

| 0010   | F <sub>RTC</sub> / EXT1 | EXT2    |

| 0011   | F <sub>PLL</sub>        | EXT2    |

| 0100   | EXT2                    | 64Hz    |

| 0101   | EXT2                    | 16Hz    |

| 0110   | EXT2                    | 2Hz     |

| 0111   | EXT2                    | '1'     |

| 1000   | F <sub>RTC</sub> / EXT1 | 64Hz    |

| 1001   | F <sub>RTC</sub> / EXT1 | 16Hz    |

| 1010   | F <sub>RTC</sub> / EXT1 | 2Hz     |

| 1011   | F <sub>RTC</sub> / EXT1 | '1'     |

| 1100   | F <sub>PLL</sub>        | 64Hz    |

| 1101   | F <sub>PLL</sub>        | 16Hz    |

| 1110   | F <sub>PLL</sub>        | 2Hz     |

| 1111   | F <sub>PLL</sub>        | '1'     |

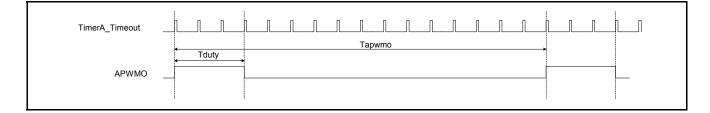

Two IO PWMs which duty is selected from 1/16 to 14/16. Example the above figure is a 3/16-duration cycle. The APWMO waveform is made by selecting a pulse width through P\_APWM\_Ctrl. As a result, each 16 cycles will generate a pulse width defined in control port. These PWM signals can be applied for controlling the speed of motor or other devices.

#### 6.9.2. Timebase

Timebase, generated by 32768Hz crystal oscillator, is a combination of frequency selection. Furthermore, timebase generates 4KHz, 2KHz, 512Hz, 64Hz, 16Hz and 2Hz interrupt sources (FIQ6/IRQ6, FIQ7/IRQ7) for Real-Time-Clock.

#### 6.10. Sleep Mode, Wakeup, Halt Mode, and Watchdog

#### 6.10.1. Sleep and Wakeup modes

- Sleep: After power-on reset, IC starts running until a sleep command is issued. When a sleep command is accepted, IC will turn the system clock (PLL) off. After all, it enters sleep mode.

- 2) Wakeup: CPU awaking from sleep mode requires a wakeup signal to turn the system clock (PLL) on. The FIQ/IRQ signal makes CPU complete the wakeup process and initialization. The CPU wakeup source is given in the following table.

| Wakeup Source     |

|-------------------|

| Timer A interrupt |

| Timer B interrupt |

| Timer C interrupt |

| EXT1/EXT2/KEY     |

| RTC               |

Halt mode: Halt mode for power saving. In this mode, CPU clock is turned off.

#### 6.11. ADC (Analog to Digital Converter)

The GPCE512A has eight channels of 12-bit A/D (Analog to Digital Converter). The function of an A/D converter is to convert analog quality signal, e.g. a voltage into a digital word or input source, can be eight channels line-in from IOC [7:0] or one channel microphone input through amplifier and AGC controller. The MIC amplifier circuit is capable of reducing common mode noise by transmitting signals through MIC fully differential Input. Moreover, an external resistor can be applied to adjust microphone gain and time of AGC operating. The AD needs to select source of line-in before converting. The ADC is able to choose the external or internal (=AVDD) top reference voltage.

#### 6.12. 16 Bits DAC Audio Driver

The GPCE512A provides one 16-bit DAC for audio outputs; the pin name is DAC1.

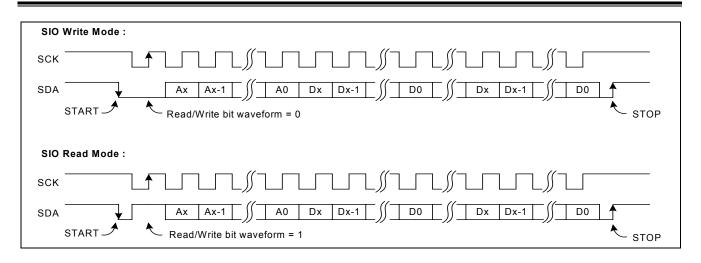

#### 6.13. Serial interface I/O (SIO)

Serial interface I/O offers a one-bit serial interface that communicates with other devices. This serial interface is capable of transmitting or receiving data via two I/O pins, IOB11 (SCK) and IOB10 (SDA).

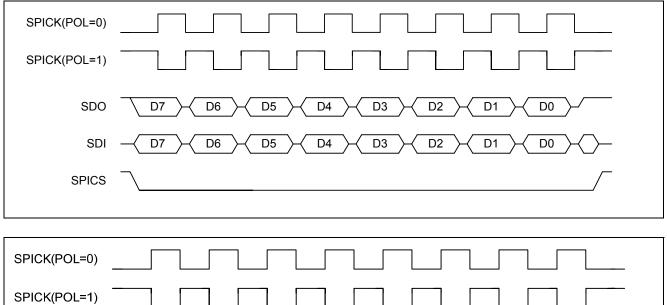

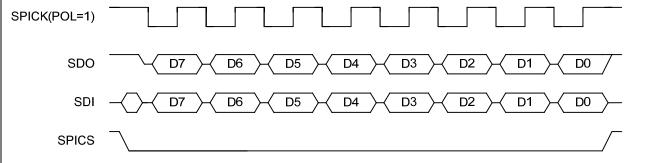

#### 6.14. SPI

A Serial Peripheral Interface (SPI) controller is built in GPCE512A to facilitate communicating with other devices and components.

There are four control signals on SPI - SPICS (IOB12), SPICK (IOB13), SDI (IOB14), and SDO (IOB15).

#### 6.15. Audio Algorithm

The following speech types can be used in GPCE512A: PCM,LOGPCM,SACM\_S200,SACM\_S480,SACM\_S530,SACM\_S720,SACM\_A1600,SACM\_A1601,SACM\_A3200,

SACM\_A3600, SACM\_DVR1600 (Digital Voice Recorder), and SACM\_DVR4800.

#### 7. ELECTRICAL SPECIFICATIONS

#### 7.1. Absolute Maximum Ratings

| Characteristics             | Symbol           | Min. | Max.        | Unit |

|-----------------------------|------------------|------|-------------|------|

| IO PAD Supply Voltage       | VDDIO            | -0.3 | 6.0         | V    |

| Analog Supply Voltage       | AVDD             | -0.3 | 4.0         | V    |

| Core Supply Voltage         | VDD              | -0.3 | 4.0         | V    |

| Input Voltage Range         | V <sub>IN</sub>  | -0.3 | VDDIO + 0.5 | V    |

| ESD Protection(HBM)         | V <sub>ESD</sub> | 2К   | -           | V    |

| Operating Temperature Range | T <sub>A</sub>   | 0    | +60         | °C   |

| Storage Temperature Range   | T <sub>STO</sub> | -50  | +150        | °C   |

Note: Stresses beyond those given in the Absolute Maximum Rating table may cause operational errors or damage to the device. For normal operational conditions see DC Electrical Characteristics.

#### 7.2. DC Characteristics (VDD = 3.3V, VDDIO = 5V, $T_A = 25^{\circ}C$ )

| Oh ann a ta miadia a                       | 0. material      | Limit     |      |           | 11-14 | <b>T</b> ( <b>0</b> ) ""                                                |  |

|--------------------------------------------|------------------|-----------|------|-----------|-------|-------------------------------------------------------------------------|--|

| Characteristics                            | Symbol           | Min.      | Тур. | Max.      | Unit  | Test Condition                                                          |  |

| Operating Voltage (IO)                     | VDDIO            | VDD       | 5.0  | 5.5       | V     | IO VDD                                                                  |  |

| Operating Voltage (Analog)                 | AVDD             | 2.7       | 3.3  | 3.6       | V     | 3.3V for analog power                                                   |  |

| Operating Voltage (Core)                   | VDD              | 2.7       | 3.3  | 3.6       | V     | 3.3V for core power                                                     |  |

| Operating Current                          | I <sub>OP</sub>  | -         | 55   | -         | mA    | PLL = 48MHz,<br>AD, DAC disable, no loading ;<br>VDD = 3.3v; VDDIO=5.0v |  |

| Standby Current                            | I <sub>STB</sub> | -         | -    | 4         | μA    | Disable 32KHz crystal                                                   |  |

| Input High Level                           | VIH              | 0.7 VDDIO | -    | -         | V     | -                                                                       |  |

| Input Low Level                            | VIL              | -         | -    | 0.3 VDDIO | V     | -                                                                       |  |

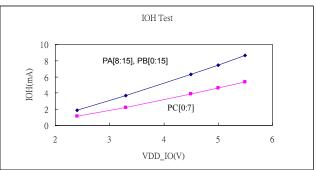

| IO Output High Current                     | I <sub>он</sub>  | -         | -7.4 | -         | mA    | $V_{OH} = 0.9 \times VDDIO$                                             |  |

| IO Output Low Current                      | I <sub>OL</sub>  | -         | 12.4 | -         | mA    | $V_{OL} = 0.1 \times VDDIO$                                             |  |

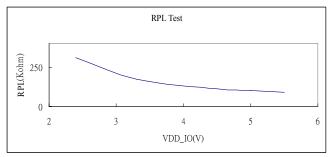

| Input Pull-Low Resistor<br>(IOA, IOB, IOC) | R <sub>PL</sub>  | -         | 100  | -         | KΩ    | V <sub>IN</sub> = VDDIO                                                 |  |

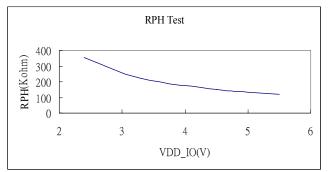

| Input Pull-High Resistor<br>(IOA, IOB,IOC) | $R_{PH}$         | -         | 130  | -         | KΩ    | V <sub>IN</sub> = VSS                                                   |  |

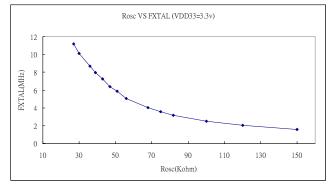

#### 7.2.1. R-OSC frequency vs. resistor

#### 7.2.1.1. VDD = 3.3V, VDDIO = 5V, $T_A = 25^{\circ}C$

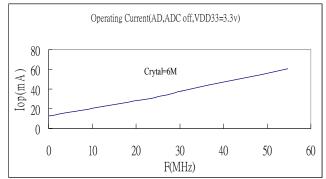

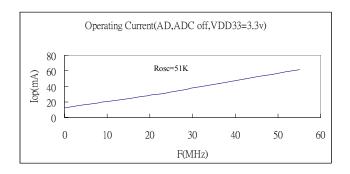

## 7.2.1.2. Operation current (VDD = 3.3V, VDDIO = 5V, $T_{\rm A}$ = 25 $^\circ\!{\rm C}$ )

#### 7.3. ADC Characteristics (AVDD = 3.3V, $T_A = 25^{\circ}C$ )

| 2h ann stariathar                                   | 0hal              | Unit    |      |          |              |

|-----------------------------------------------------|-------------------|---------|------|----------|--------------|

| Characteristics                                     | Symbol            | Min.    | Тур. | Max.     | Unit         |

| ADC Line_In Input Voltage Range from<br>IOC[7:0]    | VINL (Note 1)     | VSS-0.3 | -    | AVDD+0.3 | V            |

| ADC Microphone Input Voltage Range                  | VINM              | VSS-0.3 | -    | AVDD+0.3 | V            |

| External ADC Top Voltage                            | VEXTREF (Note 2)  | 2.0     | -    | AVDD+0.3 | V            |

| Resolution of ADC                                   | RESO              | -       | -    | 12       | bits         |

| Signal-to-Noise Plus Distortion of ADC from Line in | SINAD (Note 4)    | -       | 60   | -        | dB           |

| Effective Number of Bit                             | ENOB (Note 5)     | -       | 9.6  | -        | bits         |

| Integral Non-Linearity of ADC                       | INL               | -       | ±3.0 | -        | LSB (Note 3) |

| Differential Non-Linearity of ADC                   | DNL (Note 6)      | -       | ±1.0 | -        | LSB          |

| No Missing Code                                     |                   | -       | 12   | -        | Bits         |

| MAX ADC Clock                                       |                   | -       | -    | 3        | MHz          |

| AD Conversion Rate                                  | F <sub>CONV</sub> | -       | -    | 150K     | Hz           |

Note1: Internal protection diodes clamp the analog input to AVDD and VSS. These diodes allow the analog input to swing from (VSS-0.3V) to (AVDD+0.3V) without causing damage to the devices.

**Note2:** The ADC performance is limited by the system's noise level, so the GPCE512A just guarantee with the 8-bit accuracy when AVREF\_TOP is 2V. **Note3:** LSB means Least Significant Bit. With VINL=3V, 1LSB=3V/2^12= 0.732 mV.

Note4: The SINAD testing condition at VINLp-p=3.1V, F\_CONV = 48KHz, Fin=1KHz Sine waves at AVDD=3.3V from the IOC [7:0] input.

Note5: ENOB= (SINAD-1.76)/6.02.

Note6: The ADC of GPCE512A can guarantee no missing code.

#### 7.4. DAC Characteristics (AVDD = 3.3V, $T_A = 25^{\circ}C$ )

| Characteristics              | 0k.a.l                     | Unit |      |      |      |

|------------------------------|----------------------------|------|------|------|------|

| Characteristics              | Symbol                     | Min. | Тур. | Max. | Unit |

| Resolution of DAC            | RESO                       | -    | 16   | -    | bit  |

| Signal to Noise Ratio of DAC | SNR                        | -    | 90   | -    | dB   |

| Dynamic Range                | DR                         | -    | 85   | -    | dB   |

| Sample Rate                  | Fs                         | -    | 200K | -    | Hz   |

| THD+N at FS (Note 1)         | F <sub>оит</sub> =0.997KHz | -    | -60  | -    | db   |

| Output Loading               | RL                         | 125  | -    | -    | ohm  |

| Output Range                 | Input=Full Scale           | -    | 60%  | -    | AVDD |

Note1: The THD+N testing condition at AVDD=3.3, Fs=48KHz, Fin=0.997KHz input at RL=125 ohm.

#### 7.4.1. Pull high resister and VDDIO

#### 7.4.2. Pull low resister and VDDIO

#### 7.4.3. I/O output high current $I_{\text{OH}}$ and $V_{\text{OH}}$

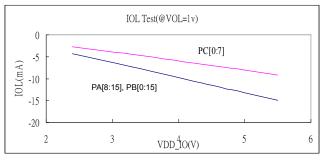

#### 7.4.4. I/O output low current $I_{\text{OL}}$ and $V_{\text{OL}}$

#### 8. APPLICATION CIRCUITS

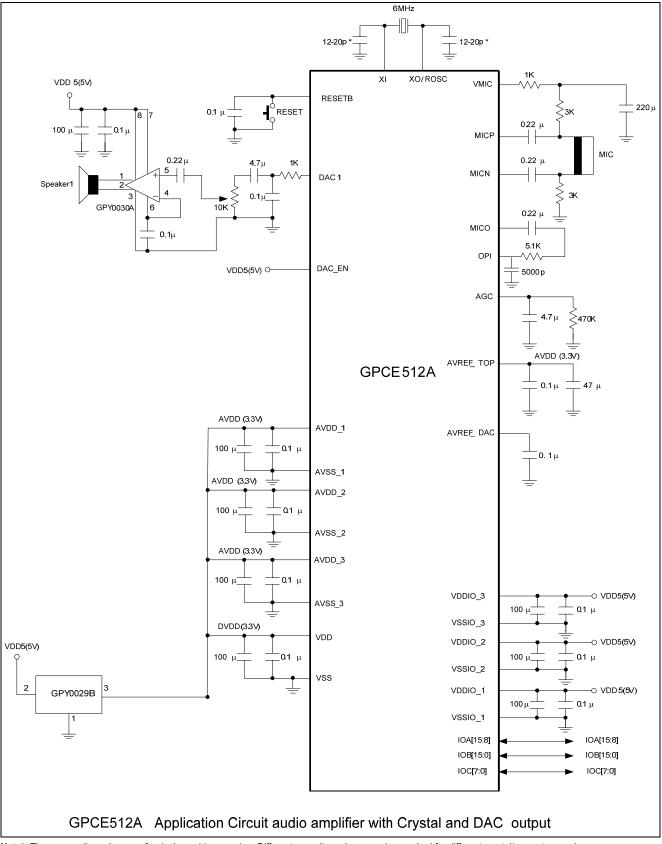

#### 8.1. Application Circuit 1 (with Crystal, DAC Output)

Note\*: These capacitor values are for design guidance only. Different capacitor values may be required for different crystal/resonator used.

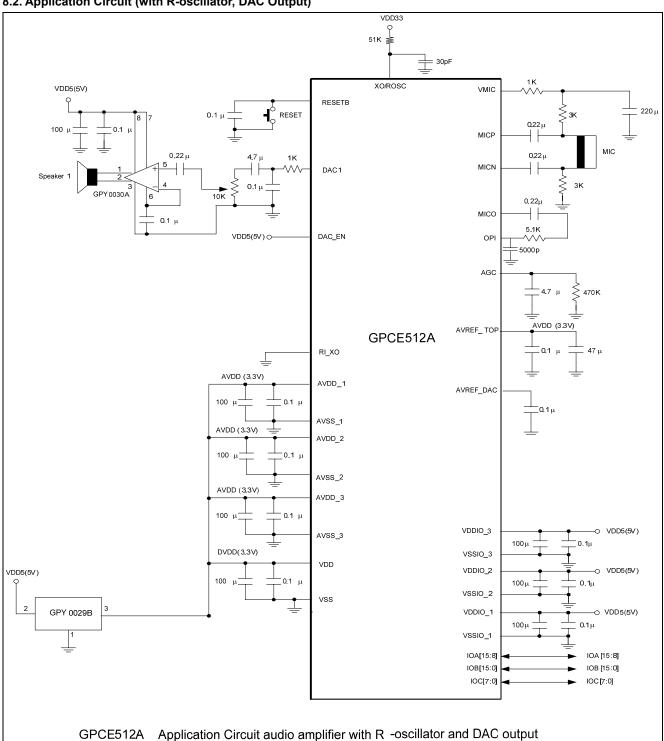

#### 8.2. Application Circuit (with R-oscillator, DAC Output)

#### 9. PACKAGE/PAD LOCATIONS

#### 9.1. Ordering Information

| Product Number  | Package Type |

|-----------------|--------------|

| GPCE512A-NnnV-C | Chip form    |

Note1: Code number is assigned for customer.

Note2: Code number (N = A - Z or 0 - 9, nn = 00 - 99); version (V = A - Z).

#### **10. DISCLAIMER**

The information appearing in this publication is believed to be accurate.

Integrated circuits sold by Generalplus Technology are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. GENERALPLUS makes no warranty, express, statutory implied or by description regarding the information in this publication or regarding the freedom of the described chip(s) from patent infringement. FURTHERMORE, GENERALPLUS MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. GENERALPLUS reserves the right to halt production or alter the specifications and prices at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by GENERALPLUS for such applications. Please note that application circuits illustrated in this document are for reference purposes only.

#### **11. REVISION HISTORY**

| Date          | Revision # | Description                                                                                    | Page      |

|---------------|------------|------------------------------------------------------------------------------------------------|-----------|

| OCT. 02, 2013 | 1.7        | Add COMAIR logo to the cover page                                                              |           |

| May 06, 2011  | 1.6        | Modify name of one NC pin to DAC_EN and add it in application circuit.                         | 5,6,17,18 |

| Sep 15, 2009  | 1.5        | 1. Modify 3. FEATURES.                                                                         | 3         |

|               |            | 2. Modify 7.2 DC Characteristics.                                                              | 14        |

| May 14, 2008  | 1.4        | Modify the "DC Characteristics (VDD = 3.3V, VDDIO = 5V, $T_A = 25^{\circ}C$ )" in section 7.2. | 14        |

| JUL. 13, 2007 | 1.3        | 1. Modify the "Application Circuit 1" in section 8.1.                                          | 16        |

|               |            | 2. Modify the "Application Circuit" in section 8.2.                                            | 17        |

| FEB. 16, 2007 | 1.2        | 1. Modify the "FEATURES" in section 3.                                                         | 3         |

|               |            | 2. Modify the "Absolute Maximum Ratings" in section 7.1.                                       | 13        |

|               |            | 3. Modify the "DC Characteristics" in section 7.2.                                             | 13        |

| DEC. 05, 2006 | 1.1        | 1. Delete SPU clock feature.                                                                   |           |

|               |            | 2. Delete Audio PWM feature.                                                                   |           |

|               |            | 3. The operating voltage was changed form 2.4V to 2.7V.                                        |           |

|               |            | 4. The AVREF_DAC's pin description was moved from ADC to DAC.                                  |           |

|               |            | 5. Modify the "ADC Characteristics" in section 7.3.                                            | 14        |

|               |            | 6. Modify the "Pad Assignment" in section 9.1.                                                 | 18        |

| OCT. 05, 2006 | 1.0        | Original.                                                                                      | 20        |