# GC4130A Low Distortion AGC Amplifier

DATA SHEET

#### **FEATURES**

- · high stability of output level

- · 40 dB AGC operating range

- · adjustable AGC threshold

- · adjustable release time

- · levels adjustable with external components

- · maximum frequency 200 kHz

- · operates from standard 5V power supply

#### INTRODUCTION

www.DataSheet.ir

The GC4130A is a low cost, high performance, easy to use AGC amplifier. In the minimum component configuration it only requires four external capacitors. The output level is maintained constant over 40 dB variation of input signal. The GC4130A can drive a 600  $\Omega$  load and can be operated with a power supply voltage of 4.6 to 20 volts. No adjustments are necessary.

Some potential applications are:

intercoms hands-free telephones

hands-free telephones P.A. systems

voice recognition systems ultrasonic remote controls

answering machines modems voice operated devices infrared security controls

ultrasonic radars & proximity switches

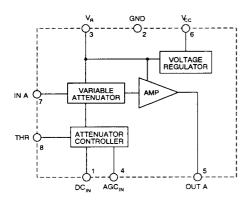

## **FUNCTIONAL BLOCK DIAGRAM**

## CIRCUIT DESCRIPTION

The GC4130A contains four functional blocks:

- 1. Variable Attenuator

- 2. Linear Amplifier

- 3. Attenuator Control

- 4. Voltage Regulator

A variable attenuator is placed at the input and is controlled by a DC voltage. With no DC input it has an initial attenuation of 1 to 4 dB; in AGC mode (for input signals larger than the threshold) it maintains a constant level at the input of the amplifier. The DC voltage at pin 7 is 1.9 V.

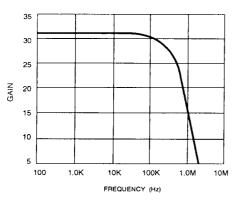

The amplifier has a gain of 33 dB and together with the attenuator (for input signals lower than the threshold), the gain is approximately 31 dB. The non-inverting amplifier has a class AB output stage, and the phase shift of the output signal is level independent. The minimum bandwidth (-3 dB) is 200 kHz.

The attenuator control is a window comparator followed by a constant current output stage. The window is set by the chip voltage regulator and the comparator responds to both negative and positive cycles. The input signal to the comparator (pin 4) must be coupled through an external capacitor. The peak-to-peak voltage of the output signal is maintained constant within 0.2 dB over the AGC operating range. To smooth the DC control signal an external filter capacitor is required. An on-chip current source, together with this capacitor, determines the release time and connecting a resistor in parallel to the capacitor will reduce the release time.

The voltage regulator powers all the functional blocks except the output stage of the amplifier. The 3.2 V nominal regulated voltage is referenced to a temperature-stable bandgap reference. The regulator voltage is brought out at pin 3 for filtering and external use.

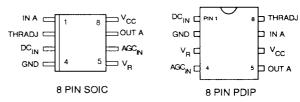

## PIN CONNECTIONS

NOTE: PIN-OUTS DIFFER SOIC TO PDIP

Document No. 510 - 92 - 4

# **ABSOLUTE MAXIMUM RATING**

| PARAMETER                   | VALUE / UNIT |  |  |

|-----------------------------|--------------|--|--|

| Power Supply                | 20 V DC      |  |  |

| Power Dissipation           | 300 mW       |  |  |

| Operating Temperature Range | -40 to +85 ℃ |  |  |

## **ORDERING INFORMATION**

| Part Number | Package Type | Temperature Range |

|-------------|--------------|-------------------|

| GC4130AEDA  | 8 Pin PDIP   | -40 to + 85°C     |

| GC4130AEKA  | 8 Pin SOIC   | -40 to + 85°C     |

## **ELECTRICAL CHARACTERISTICS**

Limits apply over -25°C  $\leq$  T<sub>A</sub>  $\leq$  85°C  $V_{cc}$  = 4.5 to 20V. Typical values are at T<sub>A</sub>  $\leq$ 25°C. The test circuit is shown in Figure 6.

| Parameter / Symbol                   |                   | Conditions / Notes                                                                       | Min.   | Тур. | Max. | Units    |

|--------------------------------------|-------------------|------------------------------------------------------------------------------------------|--------|------|------|----------|

| Supply Voltage                       | v <sub>cc</sub>   |                                                                                          | 4.5    | 5.0  | 20   | V DC     |

| Supply Current                       | I <sub>CC</sub>   | no signal                                                                                | 2      | 3    | 4.7  | mA       |

| Reg. Voltage                         | V <sub>REG</sub>  |                                                                                          | 3.00   | 3.2  | 3.5  | V        |

| Temp. Coeff. of V <sub>REG</sub>     |                   |                                                                                          | -      | 100  | -    | ppm/°C   |

| Max. O/P Current                     | I <sub>REG</sub>  | for V <sub>REG</sub>                                                                     | -      | -    | 1    | mA       |

| Decoupling Capacitor                 | C <sub>REG</sub>  | for V <sub>REG</sub>                                                                     |        | 4.7  | -    | μF       |

| Power Supply<br>Decoupling Capacitor | C <sub>s</sub>    | optional                                                                                 | -      | 10   | -    | μF       |

| Signal-to-Noise Ratio                |                   | at amplifier O/P<br>(V <sub>IN</sub> = 100 -1000 mVp-p at 1 kHz)                         | -      | 60   | -    | dB       |

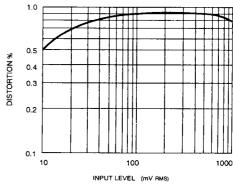

| Total Harmonic Distortion            | THD               | at amplifier O/P<br>(V <sub>IN</sub> = 100-1000 mVp-p at 1 kHz,V <sub>OUT</sub> =1 Vp-p) | -      | 0.5  | 2    | %        |

| Input Signal Level                   | >2                |                                                                                          | -      | 0.1  | 4    | Vp-p     |

| Output Signal Level                  | V <sub>OUT</sub>  | in AGC mode                                                                              | 0.8    | 0.95 | 1.15 | Vp-p     |

| Gain                                 | Α                 | in linear mode                                                                           | -      | 31   | -    | dB       |

| Atten. Input Impedance               | Z <sub>IN</sub>   | at 1 kHz                                                                                 | 6      | 10   | •    | kΩ       |

| Output Impedance                     | Z <sub>OUT</sub>  | at 1 kHz                                                                                 | -      | 20   | -    | Ω        |

| Clipping Voltage                     | V <sub>OUTM</sub> |                                                                                          | -      | 2.5  | -    | V        |

| Slew Rate                            |                   |                                                                                          |        | 1.5  | -    | V/µs     |

| O/P DC Bias Level                    |                   | no signal                                                                                | -      | 1.9  | -    | v        |

| Source Impedance                     | R <sub>S</sub>    | for V <sub>IN</sub>                                                                      | -      | -    | 5    | kΩ       |

| Attenuation Range                    |                   |                                                                                          | -      | 40   | -    | dB       |

| O/P Current                          | I <sub>L</sub>    | Source<br>Sink                                                                           | 3<br>3 | -    |      | mA<br>mA |

| O/P Voltage Change                   |                   | I/P Level Change V <sub>IN</sub> = 20 to 1000 mV <sub>RMS</sub>                          | -      | 0.2  | -    | dB       |

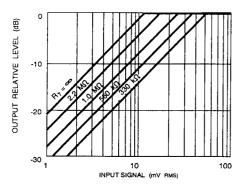

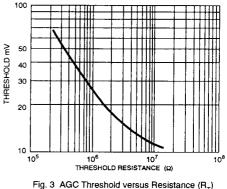

Fig. 2 AGC Characteristics

Fig. 4 Amplifier Gain versus Frequency

Fig. 5 Distortion Function of Input Level (AGC Mode)

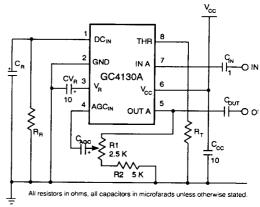

## **TEST CIRCUIT**

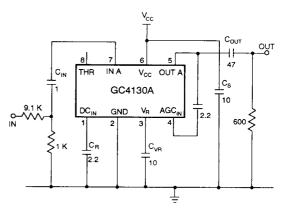

The test circuit is shown in Figure 6. The 20 dB attenuator at the input facilitates measurements at low input levels. The input (pin 1) must be capacitively coupled. Any direct coupling of the input will prevent proper operation.

The output is loaded by a 600  $\Omega$  resistor through a capacitor. The resistor is present for test purposes only. Output loading is not necessary for normal operation. The amplifier output is coupled with the attenuator control (AGC<sub>IN</sub> pin 4) through a capacitor. Both inputs (IN A and  $AGC_{IN}$ ) are internally biased and should not be loaded with a DC current. Frequency response should be measured at input levels lower than the threshold. A value of  $8\,\mathrm{mV}_\mathrm{RMS}$  (80 mV before the attenuator) is recommended.

All resistors in ohms, all capacitors in microfarads unless otherwise stated

Fig. 6 Test Circuit

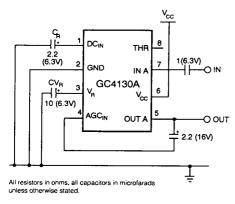

Fig. 7 Minimum Components Circuit

## **APPLICATIONS**

Figure 7 shows a minimum component configuration. This should be adequate for most applications. With a 1  $\mu\text{F}$  input capacitor coupling, the 3 dB cut-off frequency (highpass) is approximately 150 Hz. The AGC filter capacitor,  $C_{\text{R}}$ , sets the attack and release time.  $C_{\text{R}}$  also affects the distortion performance at low frequencies. For operation down to 300 Hz,  $C_{\text{R}}$  should be a minimum of 2.2  $\mu\text{F}$ .

Figure 8 shows a maximum component configuration. An optional capacitor,  $C_{\rm CC}$ , has been added for filtering the power supply line. It is not necessary to have it close to the IC. If there is a capacitor already on the supply line, another one is not necessary. The threshold resistor,  $R_{\rm Tr}$  is to be used if a higher threshold is desired. The relationship between the threshold voltage and this resistor is shown in Figures 2 and 3.

The release time resistor,  $R_R$  connected in parallel to  $C_R$ , will reduce the release time. The <u>same</u> effect can be obtained by reducing the value of  $C_R$ . However, using a resistor ensures a better control of the release time.

Finally a potentiometer, R1, and a resistor, R2, are added in order to control the output level, which can only be increased; it cannot be decreased. The potentiometer can be replaced by two or three resistors in parallel. The output level can be adjusted by cutting one or two of these. In order to avoid clipping, care should be exercised not to exceed 1.5 V p-p output level.

Fig. 8 Maximum Components Circuit

## **AVAILABLE PACKAGING**

8 Pin Molded SOIC 8 Pin DIP

CAUTION

ELECTROSTATIC

SENSITIVE DEVICES

DO NOT OPEN PACKAGES OR HANDLE

#### REVISION NOTES:

- -3 Product No. is changed to GC4130A

- -4 SOIC pin-out added

Gennum Corporation assumes no responsibility for the use of any circuits described herein and makes no representations that they are free from patent infringement, O Copyright February 1989 Gennum Corporation. Revision Date: December 1991 All rights reserved. Printed in Canada