# **Continuous Conduction Mode PFC IC** FA5614N / FA5615N

**Datasheet**

#### 1. Overview

FA5614/15 is control IC for power factor correction converter. It realizes low power consumption by using high voltage CMOS process. Thanks to a average current control, a stable operation is obtained, whereby a power factor of 99% or more is easily available. DC output voltage is controlled under a wide range of load from rated to no load. Further, a unique switching frequency diffusion function incorporated simplifies the line filter.

# 2. Features

- · Unique switching frequency diffusion function incorporated

- · Selectable switching frequency: Diffuse or Fix (120 kHz, 130 kHz)

- High-precision over current protection: 0.5V ± 5%

- · No audible noise at startup by dynamic OVP circuit

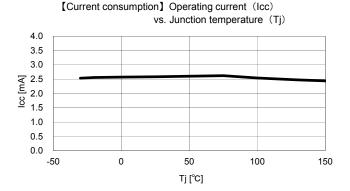

- · Low current consumption by high voltage CMOS process

- Operating: 2mA (typ.)

- · Enabled to drive power MOSFET directly. Output peak current, source: 1.5A, sink: 1.5A.

- · Open/short protection at feedback (FB) pin

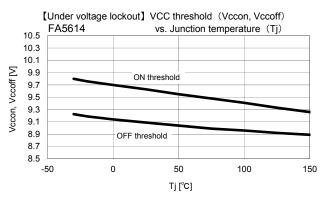

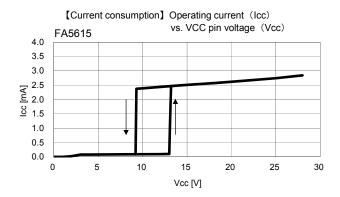

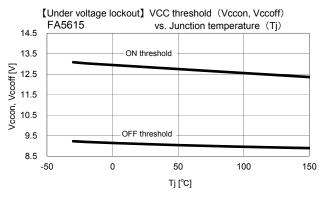

- · Under-voltage lockout

FA5614: 9.6V ON / 9V OFF FA5615: 13V ON / 9V OFF

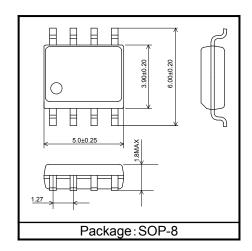

· 8-pin package: SOP-8,

## 3. Function list by types

| Туре    | Startup Threshold | Frequency              |

|---------|-------------------|------------------------|

| FA5614N | 9.6V(typ.)        | Diffuse or             |

| FA5615N | 13V(typ.)         | Fix (120 kHz, 130 kHz) |

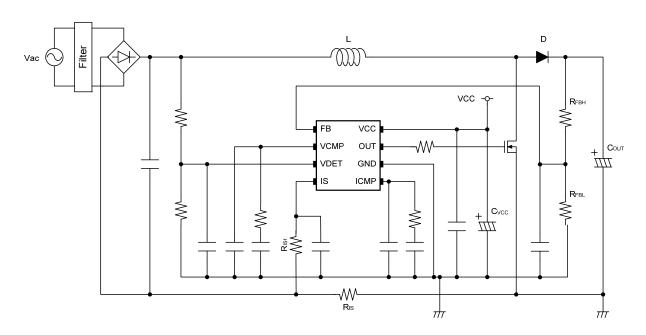

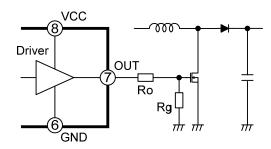

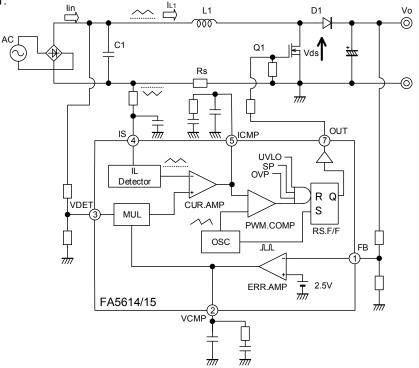

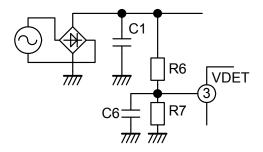

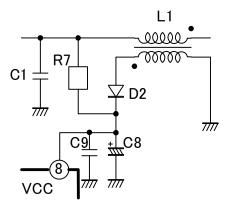

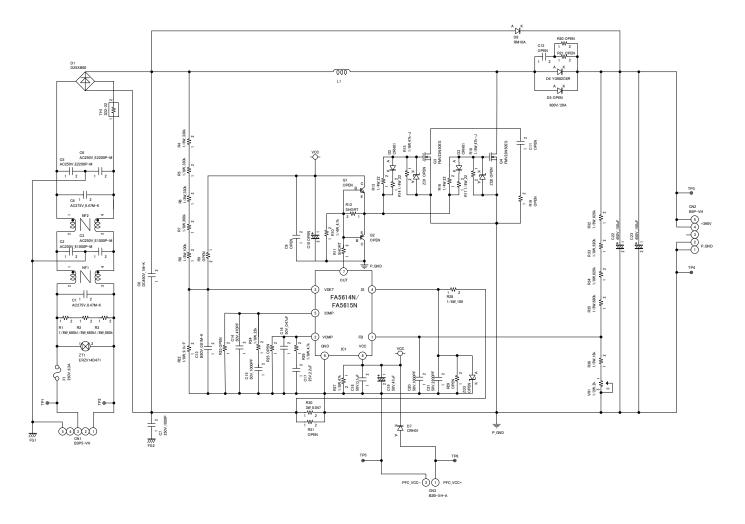

#### 4. Application circuit example

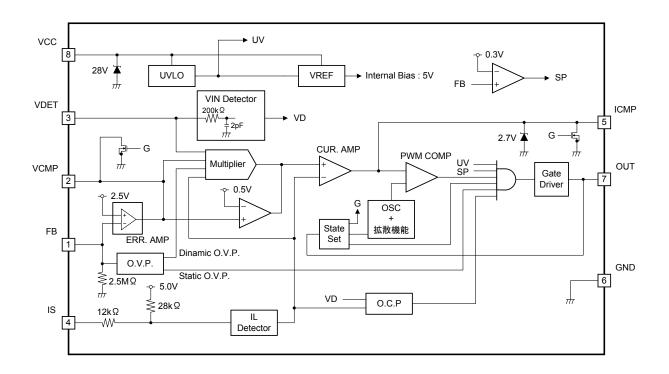

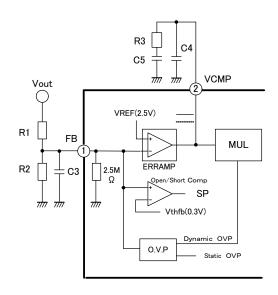

# 5. Block diagram

#### FA5614N / FA5615N

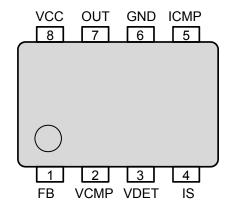

# 6. Functional description of pins

| Pin<br>No. | Pin name | Pin Function                 |

|------------|----------|------------------------------|

| 1          | FB       | Voltage Feedback Input *1    |

| 2          | VCMP     | Voltage Loop Compensation *2 |

| 3          | VDET     | AC Voltage Input *1          |

| 4          | IS       | Current Sense Input          |

| 5          | ICMP     | Current Loop Compensation *2 |

| 6          | GND      | Ground                       |

| 7          | OUT      | Output                       |

| 8          | VCC      | Power Supply *1              |

#### Notes)

<sup>\*1</sup> connect the capacitor.

<sup>\*2</sup> connect capacitor and the resistor.

#### 7. Rating & characteristics

Stress exceeding absolute maximum ratings may malfunction or damage the device.

"-" shows source and "+" shows sink in current descriptions.

#### (1) Absolute maximum ratings

| Item                             |                  | Symbol  | Value              | Unit |

|----------------------------------|------------------|---------|--------------------|------|

| FB pin voltage                   |                  | Vfb     | -0.3~5.0           | V    |

| FB pin current *3                |                  | Ifb     | -100~100           | μΑ   |

| VCMP pin voltage                 |                  | Vvcmp   | -0.3~5.0           | V    |

| VCMP pin current *:              | 3                | lvcmp   | -0.5~30            | mA   |

| VDET pin voltage                 |                  | Vvdet   | -0.3~5.0           | V    |

| VDET pin current *3              | 3                | lvdet   | -100~100           | μΑ   |

| IS pin voltage                   |                  | Vis     | -5.0~1.0           | V    |

| IS pin current *3                |                  | lis     | -300~100           | μΑ   |

| ICMP pin voltage                 | ICMP pin voltage |         | -0.3~5.0           | V    |

| ICMP pin current *3              | 1                | licmp   | -0.2~30            | mA   |

| OUT pin voltage *4               |                  | Vout    | -0.3~VCC+0.3       | V    |

| OUT pin current *1               |                  | lout    | -1500~1500         | mA   |

| OUT pin peak current             | *2               | lout_pk | Self Limiting      | mA   |

| VCC pin voltage *1               | Icc > 4.8mA      | Vcc1    | -0.3~28            | V    |

|                                  | Icc < 4.8mA      | Vcc2    | -0.3∼Self Limiting | V    |

| VCC pin current and z current *1 | ener diode       | lcc+lz  | 15                 | mA   |

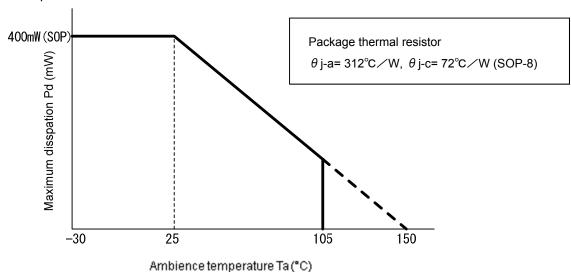

| Power dissipation (Ta=25°C)      | SOP-8            | Pd      | 400                | mW   |

| Operating junction ten           | nperature        | Tj      | - 30∼ + 150        | °C   |

| Storage temperature              |                  | Tstg    | - 40∼ + 150        | °C   |

<sup>\*1</sup> Never exceed power dissipation Pd.

# \*Maximum dissipation curve

<sup>\*2</sup> The period that exceeds 1500mA must be 100ns or less.

<sup>\*3</sup> When the pin current flows continuously for 100ns or more

<sup>\*4</sup> The period of 100ns (dead time period) when the voltage of the terminal OUT changes Low

<sup>⇒</sup> High is out of the question.

# (2) Recommended operating conditions

| Item                                      | Symbol | Min.  | Тур. | Max. | Unit |

|-------------------------------------------|--------|-------|------|------|------|

| Supply Voltage                            | Vcc    | 10    | 18   | 26   | V    |

| VDET pin input voltage                    | Vvdet  | 0     | _    | 2.4  | V    |

| VDET pin peak input voltage               | Vpvdet | 0.54  | _    | 2.4  | V    |

| IS pin voltage                            | Vis    | - 1.0 | _    | 0.5  | V    |

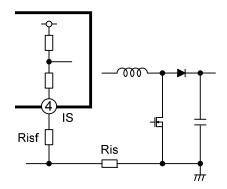

| IS pin connection noise filter resistance | Risf   | 0     | _    | 100  | Ω    |

| Ambiance temperature in operation         | Та     | - 30  | _    | 105  | °C   |

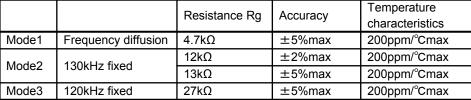

| Item              |              | Symbol | Resistance | Accuracy | Temperature     |

|-------------------|--------------|--------|------------|----------|-----------------|

|                   |              |        |            |          | characteristics |

| Frequency setting | Frequency    | Rg1    | 4.7kΩ      | ±5%      | 200ppm/°C       |

| resistance *1     | diffusion    |        |            |          |                 |

|                   | 130kHz fixed | Rg2    | 12kΩ       | ±2%      | 200ppm/°C       |

|                   |              |        | 13kΩ       | ±5%      | 200ppm/°C       |

|                   | 120kHz fixed | Rg3    | 27kΩ       | ±5%      | 200ppm/°C       |

<sup>\*1)</sup> For connection in Fig.7-2, Ro range: 0 to  $100\Omega$

Fig.7-1 IS pin-connected filter resistance

Fig.7-2 Frequency setting resistance

#### (3) DC electrical characteristics

(Unless otherwise specified, Vfb=2.5V, Vvcmp=2.5V, Vvdet=0V, Vis=0V, Vicmp=2.0V, Vcc=18V, Rg=4.7k $\Omega$ , Tj=25°C) No guaranteed value exists for the column of "— ".

"+" shows sink and "-" shows source in current prescription.

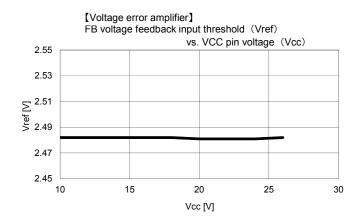

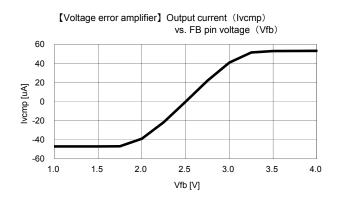

# Voltage amplifier (FB, VCMP pin)

| Item                                      | Symbol  | Condition                           | Min.            | Тур.            | Max.            | Unit   |

|-------------------------------------------|---------|-------------------------------------|-----------------|-----------------|-----------------|--------|

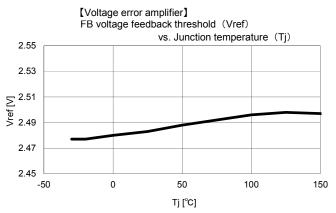

| Voltage feedback input threshold          | Vref    | Ivcmp = 0uA                         | 2.450           | 2.500           | 2.550           | V      |

| Line regulation                           | Regline | Vfb = Vref,<br>Vcc = 10V to 26V     | - 12.5          | _               | 12.5            | mV     |

| Temperature stability                     | VrefdT  | Vfb = vref,<br>Tj = - 30°C to 125°C | - 0.5           | _               | 0.5             | mV /°C |

| Transconductance                          | Gmv     | Vfb = Vref ± 0.3V                   | 70              | 90              | 120             | μmho   |

| VCMD output ourset                        | lvsrc   | Source :<br>Vfb = 1.5V              | - 70            | - 50            | -30             | μA     |

| VCMP output current                       | Ivsnk   | Sink:<br>Vfb = 3.5V                 | 30              | 50              | 70              | μA     |

| VCMP output H voltage                     | Vvcmph  | Vfb = 1.5V                          | 4.0             | _               | 5.5             | V      |

| VCMP transient response output current    | Iresp   | Source :<br>Vfb = 1.5V              | - 170           | - 140           | - 110           | μA     |

| VCMP transient response detection voltage | Vresp   |                                     | 0.902<br>x Vref | 0.940<br>x Vref | 0.978<br>x Vref | V      |

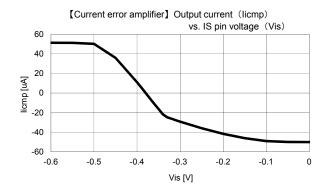

# **Current amplifier (ICMP pin)**

| Item               | Symbol | Condition                          | Min. | Тур. | Max. | Unit |

|--------------------|--------|------------------------------------|------|------|------|------|

| Transconductance   | Gmc    | Vvdet *1,<br>Vis= -0.2V to -0.4V   | 40   | 60   | 80   | μmho |

| Output current     | Icsrc  | Source :<br>Vvdet = 3.5V           | - 70 | - 50 | - 30 | μΑ   |

|                    | Icsnk  | Sink :<br>Vis = -2.0V              | 30   | 50   | 70   | μA   |

| ICMP clamp voltage | Vclamp | Vicmp = 3.0V,<br>licmp max = 320µA | 2.6  | 2.7  | 2.9  | V    |

<sup>\*1</sup> Vvdet is for when Vis = -0.3V, licmp = 0µA

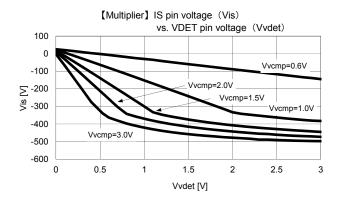

# Multiplier(VDET, VCMP pin)

| Item                       | Symbol  | Condition                                                               | Min. | Тур. | Max. | Unit |

|----------------------------|---------|-------------------------------------------------------------------------|------|------|------|------|

| VDET input bias current    | Ivdet   | Vvdet = 0V                                                              | -1.5 | -0.5 | 0.5  | μA   |

| VCMP threshold voltage     | Vthvcmp | Vvdet = 2.4V                                                            | 0.3  | 0.5  | 0.7  | ٧    |

| Output voltage coefficient | К       | Vvcmp = 1V,<br>licmp = 0µA<br>Vvdet = 0.3V, 1.3V<br>Vis = 0.1V to -0.2V | 0.5  | 0.7  | 0.95 | ı    |

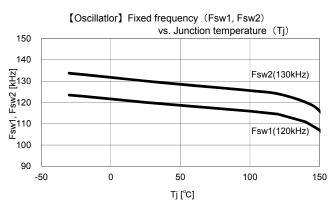

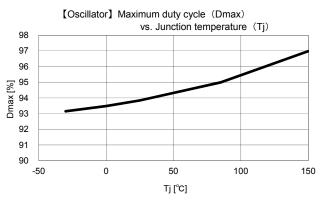

# Oscillator (OUT pin)

| Item                                      | Symbol   | Condition                                                                            | Min.  | Тур. | Max. | Unit       |

|-------------------------------------------|----------|--------------------------------------------------------------------------------------|-------|------|------|------------|

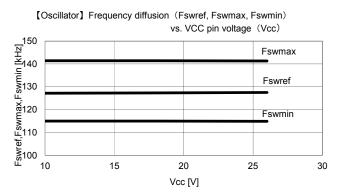

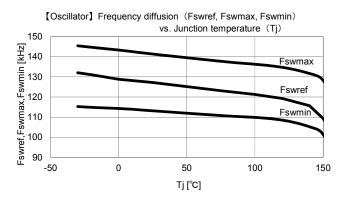

| Frequency diffusion (reference frequency) | Fswref   | Vvcmp *1,<br>Vvdet = 0.88V,<br>Vis = -0.18V,<br>Iicmp = 0µA                          | 112   | 127  | 142  | kHz        |

| Frequency<br>temperature stability        | FswrefdT | Vvcmp *1,<br>Vvdet = 0.88V,<br>Vis = -0.18V,<br>licmp = 0μA,<br>Tj = - 30°C to 125°C | -0.13 | _    | 0.13 | kHz<br>/°C |

| Frequency diffusion (maximum frequency)   | Fswmax   | Vcmp = 0V,<br>Vvdet = 2.4V                                                           | 132   | 140  | 148  | kHz        |

| Frequency diffusion, (minimum frequency)  | Fswmin   | Vcmp = 0V,<br>Vvdet = 0V                                                             | 106   | 114  | 122  | kHz        |

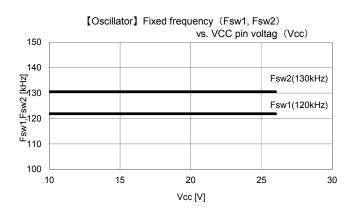

| Fixed frequency 1                         | Fsw1     | Vout2 ≦ Vout                                                                         | 105   | 120  | 135  | kHz        |

| Fixed frequency 2                         | Fsw2     | Vout1≦Vout≦Voiut2                                                                    | 115   | 130  | 145  | kHz        |

| Maximum duty cycle                        | DMAX     | Vvdet = 2.4V,<br>ICMP no connect                                                     | 91    | 94   | 97   | %          |

<sup>\*1</sup> Vvcmp is for when Vvdet = 0.88V, Vis = -0.18V, licmp = 0µA

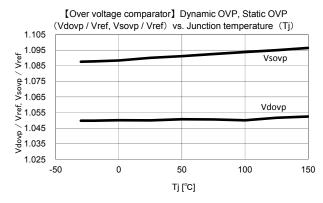

# Overvoltage protection comparator (FB pin)

| Item                             | Symbol   | Condition                                                            | Min.              | Тур.            | Max.             | Unit   |

|----------------------------------|----------|----------------------------------------------------------------------|-------------------|-----------------|------------------|--------|

| Static OVP threshold voltage     | Vsovp    | Vfb = 2.5V→2.9V,<br>Vvcmp = 0V,<br>Vvdet = 0V                        | 1.070 x<br>Vref   | 1.090 x<br>Vref | 1.105 x<br>Vref  | V      |

| Hysteresis                       | Vsovphys | Vfb = $2.9V \rightarrow 2.5V$ ,<br>Vvcmp = $0V$ ,<br>Vvdet = $0V$    | 0.005 x<br>Vref   | 0.020 x<br>Vref | 0.040 x<br>Vref  | V      |

| Static OVP temperature stability | VsovpdT  | Vfb = 2.5V→2.9V,<br>Vvcmp = 0V<br>Vvdet = 0V,<br>Tj= - 30°C to 125°C | -0.0001<br>x Vref | _               | 0.0001<br>x Vref | V / °C |

| Dynamic OVP threshold voltage    | Vdovp    | Vfb = 2.5V → 2.8V,<br>Vvcmp = 1V,<br>Vvdet = 2V                      | 1.025 x<br>Vref   | 1.050 x<br>Vref | 1.075 x<br>Vref  | V      |

| ⊿OVP                             | ⊿Vovp    | Vsovp - Vdovp                                                        | 50                | 95              | 140              | mV     |

# FB short detection comparator (FB pin)

| Item                    | Symbol | Condition                  | Min. | Тур. | Max. | Unit |

|-------------------------|--------|----------------------------|------|------|------|------|

| Input threshold voltage | Vthfb  | Vfb = 0V→1V,<br>Vvcmp = 0V | 0.1  | 0.3  | 0.5  | V    |

| Pull-down resistance    | Rfb    | Vfb = 2.5V                 | 2.0  | 2.5  | 3.0  | МΩ   |

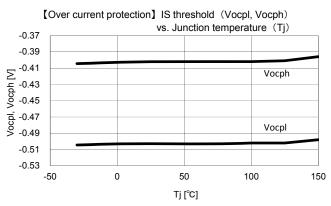

# Overcurrent detection comparator (IS pin)

| Item                                             | Symbol  | Condition                                                                                                                     | Min.    | Тур.   | Max.    | Unit      |

|--------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------|---------|--------|---------|-----------|

| IS offset voltage                                | Visof   | Vvdet = - 0.25V,<br>Vvcmp = 0.6V                                                                                              | 0       | 30     | 60      | mV        |

| IS pin voltage                                   | Vis_054 | Vvdet = 0.54V,<br>Vvcmp = 5.0V                                                                                                | -0.43   | -0.38  | - 0.33  | ٧         |

| IS threshold voltage                             | Vocpl   | Vvdet max = 1.2V,<br>Vvdet min = 0V,<br>Fvdet = 50kHz,<br>Dvdet = 50%                                                         | - 0.525 | - 0.50 | - 0.475 | ٧         |

| To all conditions to large                       | Vocph   | Vvdet max = 1.8V,<br>Vvdet min = 0V,<br>Fvdet = 50kHz,<br>Dvdet=50%                                                           | - 0.432 | - 0.40 | - 0.368 | ٧         |

| IS threshold voltage temperature characteristics | VocpldT | Vvdet max = 1.2V,<br>Vvdet min = 0V,<br>Fvdet = 50kHz<br>Dvdet = 50%,<br>Vis = - 0.4V to - 0.6V<br>Tj = - 30°C to 125°C       | -0.1    | _      | 0.1     | mV/<br>°C |

|                                                  | Vvdeth  | Vvdet max = $1.2V \rightarrow 1.8V$ ,<br>Vvdet min = 0V,<br>Fvdet = 50kHz<br>Dvdet = 50%,<br>Vis = - Vocpl + 0.05V            | 1.54    | 1.60   | 1.66    | V         |

| VDET threshold voltage                           | Vvdetl  | Vvdet max = $1.8V \rightarrow 1.0V$ ,<br>Vvdet min = $0V$ ,<br>Fvdet = $50kHz$<br>Dvdet = $50\%$ ,<br>Vis = - Vocpl + $0.05V$ | 1.30    | 1.35   | 1.40    | >         |

| IS threshold change voltage                      | Vvdets  | Vvdet max = 1.8V,<br>Vvdet min = 0V,<br>Fvdet = 50kHz<br>Dvdet = 50%,<br>Vis = - Vocpl + 0.05V                                | 0.25    | 0.30   | 0.35    | V         |

| Blanking time *1                                 | Tblk    | Vis= -0.6V                                                                                                                    | 300     | 450    | 600     | ns        |

| Delay time                                       | Tdly    | Vis =<br>Vocpl + 30mV → -1.0V<br>Pulse signal                                                                                 | 200     | 350    | 500     | ns        |

| Input bias current                               | lis     | Vvcmp = 0V,<br>Vis = 0V                                                                                                       | - 170   | - 120  | - 70    | μA        |

<sup>\*1</sup> Includes delay time

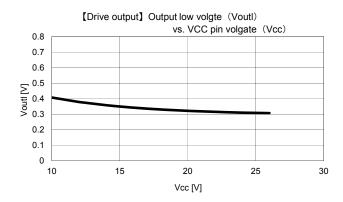

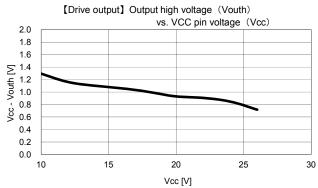

# Output (OUT pin)

| Item               | Symbol | Condition                                                              | Min. | Тур. | Max. | Unit |

|--------------------|--------|------------------------------------------------------------------------|------|------|------|------|

| Output voltage (L) | Voutl  | Vfb = 0V,<br>Vvcmp = 0.3V,<br>Vicmp = 3V to 2V,<br>Sink : lout = 100mA | Ι    | 0.5  | 1.0  | V    |

| Output voltage (H) | Vouth  | Vvcmp = 0.3V,<br>Vicmp = 3V to 2V,<br>Source : lout = - 100mA          | 15.5 | 16.5 | ı    | V    |

| Output rise time   | Tr     | C <sub>L</sub> = 1nF                                                   | _    | 50   | _    | ns   |

| Output fall time   | Tf     | C <sub>L</sub> = 1nF                                                   | _    | 50   | _    | ns   |

# Frequency setting (OUT pin)

| Item                      | Symbol | Condition                              | Min. | Тур. | Max. | Unit |

|---------------------------|--------|----------------------------------------|------|------|------|------|

| Detection current         | Istate | Tj = -30°C to 125°C                    | 34   | 40   | 46   | μA   |

| Frequency setting time *1 | Tset   | Vvcmp = 0V,<br>Vicmp = 0V,<br>Vfb = 2V | 4.1  | 5.9  | 7.7  | ms   |

| Detection time *2         | Tdet   | Vvcmp = 0V,<br>Vicmp = 0V<br>VFfb= 2V  | 420  | 530  | 640  | μs   |

| OUT threshold voltage *3  | Vout1  | Tj = -30°C to 125°C                    | 260  | 310  | 390  | mV   |

| Out threshold voltage 3   | Vout2  | Tj = -30°C to 125°C                    | 700  | 760  | 830  | mV   |

<sup>\*1</sup> Time until OUT pin to output of Istate from UVLO release

# Low voltage protection (VCC pin)

| Item                  | Symbol | Condition             | Min. | Тур. | Max. | Unit |

|-----------------------|--------|-----------------------|------|------|------|------|

| ON threshold voltage  | Vccon  | FA5614 : Vcc= 8V→11V  | 8.6  | 9.6  | 10.6 | ٧    |

| ON threshold voltage  | VCCOII | FA5615 : Vcc= 11V→15V | 11.5 | 13   | 14.5 | ٧    |

| OFF threshold voltage | Vccoff | Vcc= 11V→7V           | 8.0  | 9.0  | 10.0 | V    |

| Hysteresis            | Voobvo | FA5614 0.4            |      | 0.6  | 0.8  | V    |

| Hysteresis            | Vcchys | FA5615                | 3.5  | 4.0  | 4.5  | V    |

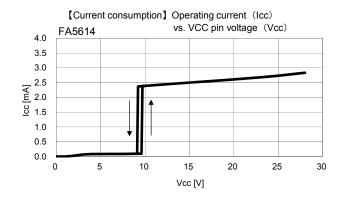

# All devices (VCC pin)

| Item              | Symbol | Condition                                        | Min. | Тур. | Max. | Unit |

|-------------------|--------|--------------------------------------------------|------|------|------|------|

| Start-up current  | Istart | Vcc = 8V,<br>Vvcmp = 0V<br>Vicmp =0V             | 70   | 90   | 110  | μΑ   |

| Operating current | Icc    | OUT pin no load                                  | _    | 2.0  | 4.0  | mA   |

| OFF time current  | Iccoff | OUT pin no load,<br>Vvcmp=0V                     | _    | 1.8  | 3.8  | mA   |

| Standby current   | lstb   | Vcc = 18V,<br>Vfb = 0V<br>Vvcmp=0V,<br>Vicmp =0V | 80   | 110  | 180  | μΑ   |

<sup>\*2</sup> Time to output Istate from OUT pin

<sup>\*3</sup> Voltage of OUT pin in Tdet

#### 8. Characteristic curve

(Unless otherwise specified, Vfb=2.5V, Vvcmp=2.5V, Vvdet=0V, Vis=0V, Vicmp=2.0V, Vcc=18V, Rg=4.7kΩ, Tj=25°C) "+" shows sink and "-" shows source in current prescription.

The data listed here show the typical characteristics of an IC, and does not guarantee the characteristic.

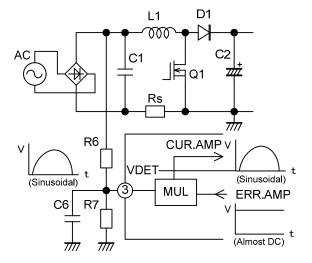

#### 9. Outline of circuit operation

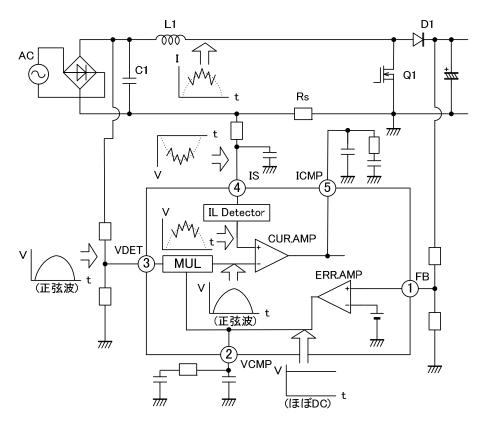

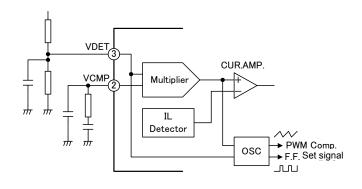

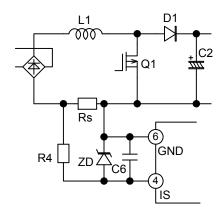

FA5614/FA5615 are controllers for power factor correction converter using boost topology. These IC are designed for the CCM mode operation with the average current control.

The operations, (1) Switching and (2) Power factor collection, are explained as below with the simplified circuit diagram

shown in Fig.1.

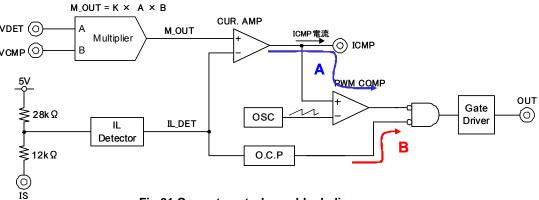

Fig.1 Block diagram of operating circuit

### (1) Switching operation

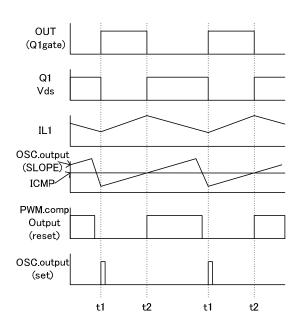

Fig. 2 outlines the waveform of each part of switching operation at a steady state. The operation is as follows.

- I. Set signal of switching frequency outputted from the oscillator sets RS. F/F, whereby OUT pin voltage goes high, thus turning on Q1. ... (t1)

- II. Q1 turned on raises the current of L1. The current of L1 is converted by Rs connected on GND side into a voltage and is inputted to IS pin (VIS). VIS is compared by current amplifier (CUR. AMP) with reference voltage that is obtained via arithmetic output by multiplier (MUL) from input voltage monitoring VDET and VCMP that is obtained by feedback from output and amplification.Current amplifier output (ICMP) compared by PWM comparator (PWM. COMP) with slope waveform outputted from oscillator and, as soon as it attains the reference value, reset signal enters RS. F/F, thereby turning off Q1. ... (t2)

- III. Q1 turned off inverts the voltage of L1. While a current is being fed to the output via D1, the current of L1 reduces. Set signal outputted from internal oscillator transfers the circuit to the next switching cycle. ... (t1)

Fig.2 Waveforms of switching operation (outline)

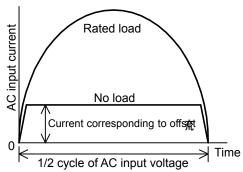

#### (2) Power factor correcting operation

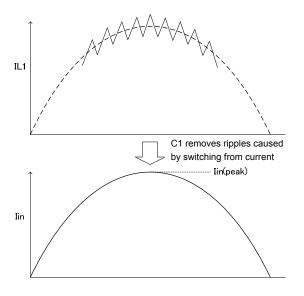

The voltage at VCMP pin that constitutes output of error amplifier (ERR.AMP) is almost DC voltage at a steady state, because of connected phase compensation capacitance. This voltage is inputted to multiplier. Another input to multiplier is a waveform obtained by rectifying AC input voltage. A multiplier multiplies these two of input and outputs a sinusoidal wave proportional to AC input voltage. This outputted sinusoidal voltage waveform is applied as a reference inductor current to current amplifier (CUR.AMP). Therefore, the inductor current's mean value forms a sinusoidal waveform. The current of inductor L1 is deprived of switching ripples by C1 and is turned into a average current. Thus, the current from AC input voltage becomes practically sinusoidal, thus improving the power factor.

Fig.4 Power factor corrected waveform

Fig.3 Aspects of waveforms at different parts

#### 10. Description of each circuit block

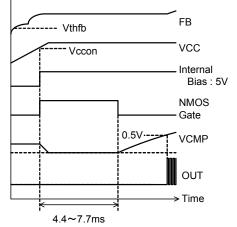

#### (1). Frequency setting circuit

The switching frequency is selectable out of 3 modes by resistance Rg connected between OUT and GND pins.

Mode 1: Frequency diffusion

106 kHz to 148 kHz

Mode 2: Fixed frequency 1

Mode 3: Fixed frequency 2

130 kHz

120 kHz

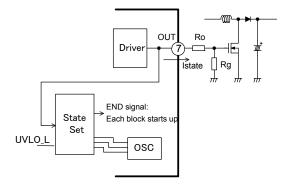

The status setting is completed after FB short detection or UVLO are canceled. The switching operation will start after this completion. Therefore, the mode will not change while operating.

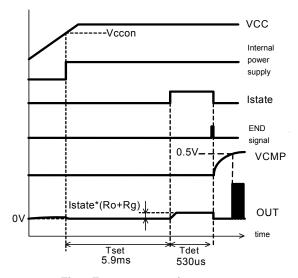

As an example, the operation of frequency setting which is in case of a cancellation of UVLO is shown in Fig. 6.

IC starts to operate after Vcc exceeds Vccon. Then after 5.9ms, the OUT pin outputs current Istate (40mA (typ.)) during 530us.

The current generates a voltage at OUT pin because external resistors (Ro and Rg) are connected to OUT pin. The frequency setting is done with based on this OUT pin voltage.

The internal circuits start switching operation after frequency setting.

Likewise, in case of cancellation of FB short detection, 5.9ms after the cancellation, a current is outputted from OUT pin for 530us, and then switching starts.

OUT pin has in its inside reference voltages of 2 levels, or Vout1 (310mV (typ.)) and Vout2 (760mV (typ.)) To select a frequency, a reference voltage is compared with OUT pin voltage while current Istate is flowing. The relationship is as follows.

Fig.5 Frequency setting circuit

Fig.6 Frequency setting sequence

| OUT pin voltage | OUT pin < Vout1     | Vout1 < OUT pin < Vout2 | Vout2 < OUT pin        |

|-----------------|---------------------|-------------------------|------------------------|

| Mode            | Mode1               | Mode2                   | Mode3                  |

| Frequency       | Frequency diffusion | Fixed frequency 130kHz  | Fixed frequency 120kHz |

#### (2) Oscillator

Oscillator outputs two signals. One is a set signal to flip-flop for setting the OUT pin to Vcc level. Another is a sawtooth signal for PWM comparison.

The oscillation frequency is set by frequency setting circuit to either the frequency diffusion mode or 2 kinds of the fixed frequency mode.

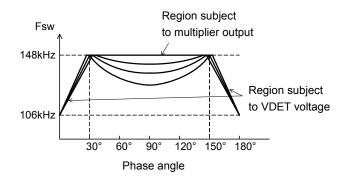

#### (2-1) Frequency diffusion

When the frequency diffusion mode is selected, the frequency changes between 106 and 148 kHz according to the input/output status of PFC power supply. The optimized frequency diffusion based on input/output status realizes a low noise operation with a wide operation range. OSC block determines the frequency based on VDET pin input voltage and multiplier block output voltage. When the phase angle is range of 0° to 30° or 150° to 180° approximately, the frequency rises in proportion to VDET pin voltage. When it is range of 30° to 150° approximately, the frequency is reversely proportional to the multiplier output. (Fig.8)

When the multiplier output is high like when PFC output current is large, the frequency drop is bigger. And it is small in case of reverse situation.

Fig.7 Block diagram for oscillator area

# (2-2) Maximum and minimum frequencies in frequency diffusion mode

As stated above, the switching frequency in the frequency diffusion mode depends on VDET pin or multiplier output voltage within maximum and minimum frequencies determined. However, maximum or minimum frequency may never appear under some conditions while 1/2 of AC cycle

#### (3) Error amplifier

The error amplifier is a circuit for controlling PFC output to a certain level. This IC adopts a transconductance amplifier.

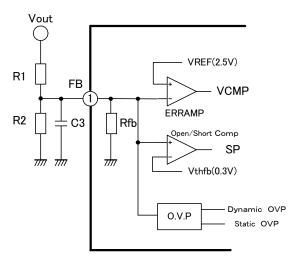

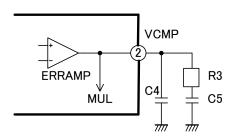

The non-inverting input terminal for the error amplifier is connected to the internal reference voltage of 2.5 V (typ.) The inverting input terminal (FB) receives the output voltage, usually resistively divided, from power factor correction converter. For FB open detecting function, this terminal is connected to a pull-down resistor of  $2.5 \mathrm{M}\Omega$  inside the IC. Error amplifier output (VCMP) is connected to multiplier (MUL) to control the inductor current.

Output voltage Vout of power factor correction converter usually contains a lot of ripples of double the AC line frequency (50 or 60 Hz). When ripples corresponding to double the AC frequency appear excessively on the error amplifier output, power factor correction converter will not operate stably. So, a capacitor and resistor network is connected between pin 2 (VCMP) which is output of the error amplifier and GND for phase compensation.

Increasing the capacitance in the phase compensation network improves the power factor, but the transient responsivity becomes slow.

The error amplifier in FA5614/15 has a function of improving the transient responsivity.

When the load has suddenly become so heavy, the FB pin voltage drops much. If lowered FB pin voltage is below transient response detection voltage (Vresp), the transient response correction circuit increases output current of error amplifier up to the transient response output current (Iresp).

Thus, the VCMP pin voltage rises quickly to increase the output current and suppress the output voltage drop.

#### (4) Overvoltage protection circuit (OVP)

This is a circuit for limiting the voltage when the output voltage of power factor correction converter has exceeded the setting.

When converter is started up or when the load has suddenly changed, the converter output voltage may rise beyond the setting. In such a case, OVP circuit prevents an over voltage and protects the converter.

FA5614/15 has a dynamic OVP function and a static OVP function. The dynamic OVP function restricts the multiplier gain depending on rising of FB pin voltage while FB pin voltage exceeds 2.5 V. The static OVP function makes OUT pulses stop while FB pin voltage exceeds 1.09 time of the reference voltage.

In normal operation, the FB pin voltage is 2.5 V that is almost the same as the reference voltage of error amplifier. When the FB pin voltage exceeds 2.5 V by startup or a sudden change of load, the dynamic OVP function reduces output current by lowering the multiplier gain. Then, if the FB pin voltage still rises and exceeds the reference voltage of a static OVP function, FA5614/15 stops the output pulses.

OUT pulses stopped by the overvoltage protection are resumed as soon as the output voltage lowers back to 1.07 times the reference voltage.

Fig.8 Oscillation frequency vs. phase angle

Fig.9 Error amplifier and overvoltage protection circuit

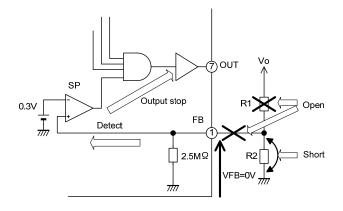

Fig.10 FB open/short detector

# (5) FB short/open detector

On the circuit of Fig. 10, if the FB pin voltage is zero because of R2 short or R1 open, the error amplifier can not control the constant voltage. Therefore, the output voltage rises abnormally. In such a case, the overvoltage protection circuit could not operate because the output voltage detection is faulty.

To avoid such inconvenience, the IC has FB short detector. The circuit consists of reference voltage of 0.3 V (typ.) and comparator (SP).

When the FB pin input voltage has dropped below 0.3 V because of R2 short or R1 open, the output of comparator (SP) is inverted to stop the IC output.

The PFC converter outputs a voltage corresponding to the input voltage even before startup because of the boost topology. That is why, this function never operate as long as the converter is normal.

In case of an open failure of the FB pin FA5614/15 stops the output pulse by this function because a pull-down resistor of 2.5  $M\Omega$  inside the IC is connected to the FB pin. If the FB pin voltage has dropped to almost zero, the IC output will stop. When the FB pin voltage returns normal then, OUT pulses will reappear.

#### (6) Multiplier

Multiplier is the circuit for controlling the input current as the sinusoidal wave forms the same as input voltage.

An input is connected to VDET pin and is inputted the dividing voltage after being rectified from AC input voltage. The other input is connected to error amplifier output (VCMP). Normally, the error amplifier output is almost DC, and multiplier outputs a sinusoidal waveform voltage whose amplitude changes according to the error amplifier output voltage. The multiplier output constitutes a reference for current comparator to control the input current to a sinusoidal waveform (Fig. 11).

It usually makes VDET pin peal voltage set to 0.65 to 2.4 V in the all AC input range.

The voltage obtained by rectifying the AC input voltage contains many noises attributable to switching by Q1. To eliminate the influence by the noise, filtering capacitance C6 is provided usually.

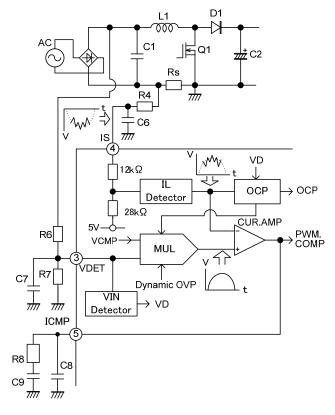

#### (7) Current detector

IL. Detector inverts and amplifies a voltage obtained by voltage-current conversion via current detecting resistance Rs of the inductor current.

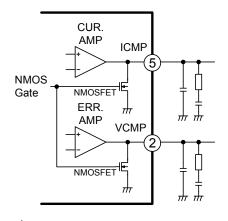

Current amplifier (CUR. AMP) is error amplifier that composes a current loop to make the input current follow a sinusoidal waveform.

Current amplifier receives IL. Detector output and multiplier (MUL) output, subjects them to comparison and error amplification, and outputs the result to PMW comparator (PWM. COMP).

Current amplifier is a transconductance amplifier the same as error amplifier. Capacitance and resistance connected between output terminal (ICMP) and GND for phase compensation eliminate switching ripples of the input current.

The current detector output is clamped to Vclamp: 2.7 V by clamp circuit that constitutes an upper limit of voltage.

Fig.11 Multiplier

Fig.12 Current detector and overcurrent protection circuit

#### (8) Overcurrent protection circuit (OCP)

OCP circuit is the circuit to detect the inductor current, and is to stop the output pulse to protect MOSFET when detected current exceeds certain intensity.

A detected voltage by sense resistor Rs connected to GND is inputted to the IS pin, is converted by the IL\_Detector which is an inverting amplifier, and is compared by overcurrent detection comparator. When IS pin voltage lowers below a threshold value (OCP level), overcurrent protection circuit outputs a signal of an overcurrent status.

The signal of overcurrent status resets a flip-flop for the OUT pulse, and then turns MOSFET off.

When IS voltage gets near a threshold value, overcurrent protection circuit lowers the gain of multiplier (MUL) to suppress the input current, thereby suppressing the audible noise of inductor attributable to an overcurrent.

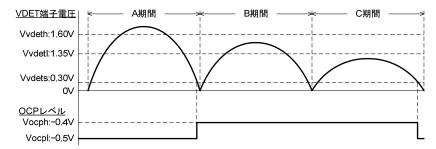

OCP level is changed depending on the peak voltage of VDET pin by VIN\_Detector as follows.

While period A, OCP level is set to Vocph (-0.4 V) because VDET pin voltage exceeds threshold voltage Vvdeth (1.6 V). OCP level is changed only when VDET pin voltage is below Vvdets (0.3V). At this time, the inductor current is low enough, and therefore will not abruptly change. Further, if the load current is very low such VDET will not be below 0.3 V, the OCP level will not change over regardless of VDET.

During period B, VDET will never go below threshold voltage Vvdetl: 1.35 V. Therefore, OCP level will not change either. Some time in period C, VDET will be below threshold voltage Vvdetl: 1.35 V, whereby OCP level is set to Vocpl (-0.5 V). The same as period A, OCP level is changed only when VDET pin voltage is below Vvdets (0.3 V).

Fig.13 Overcurrent protection (OCP) level and VDET voltage

#### (9) Undervoltage lockout circuit (UVLO)

FA5614/15 has the UVLO circuit to avoid unexpected operation when the source voltage has dropped.

The IC starts operation when the source voltage rising from zero has reached 9.6 V (typ.) for FA5614, or 13 V (typ.) for FA5615.

After startup, each of ICs stops operating when the source voltage has dropped to  $9\ V\ (typ.)$

While the IC stops a switching operation by UVLO circuit, the IC keeps OUT pin voltage low and further reduces IC consumption current to below 100  $\mu$ A.

#### (10) Output circuit

The output circuit consists of a push-pull circuit, directly drives MOSFET.

Its maximum peak current is 1.5 A for sink, and 1.5 A for source.

#### (11) Soft start

This IC has a soft-start function as overcurrent does not occur due to the rapid output voltage rise at the time of start-up.

From a state in which the IC output of at FB short detection function or UVOL function is stopped, when the FB short-circuit detection and UVLO has canceled together, pull out the charge of phase compensation capacitor that is connected to the VCMP pin and ICMP pin.

At the start of the switching VCMP pin voltage and ICMP pin voltage has dropped to 0V, gradually increases from ON Duty 0%, soft-start is executed.

Fig. 14 Soft start

The soft-start time can be adjusted by the phase compensation capacitor, but the operation is please be careful so as not to become unstable.

In addition, FB pin voltage is once, if not exceed the FB transient response detection voltage, during the soft-start does not work the transient response improvement function.

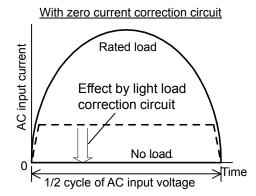

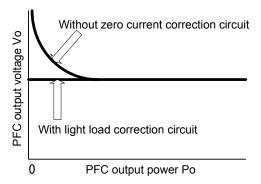

#### (12) Zero current correction circuit

Unless multiplier output or current error amplifier input has offset voltage, the input current to converter will be almost zero when PFC converter has completely no load.

However, if the offset voltage viewed from IS pin is negative, the input current corresponding to offset voltage might flow to converter even when no load or light load. In such a case, the output voltage of power factor correction converter will rise abnormally because the input current will be excessive. Offset voltage in the IS pin (Visof) is 0 mV. However, the offset voltage of the IS pin against sense resistor voltage may be negative because a voltage will be generated by an external filter resistance connected to the IS pin. Therefore, FA5614/15 has this correction circuit to avoid rising the output voltage when light load with such case.

Usual output voltage from error amplifier is 0.5 V or higher. When its output voltage has dropped below 0.5 V, zero current correction circuit operates.

Error amplifier output voltage drops below 0.5 V when an input current flows under no or light load on account of offset in multiplier output or current error amplifier input. Then, zero current correction circuit corrects the offset voltage of multiplier output. This function prevents the output voltage of power factor correction converter from rising excessively, so that the output voltage is kept at a constant level.

The correction amount varies in a linear function of the output of current error amplifier, thereby ensuring a stable run

Fig. 15 shows effects of zero current correction circuit

# Consumption diagram of operations when IS pin offset is negative

#### **Input current**

Without zero current correction circuit

# **Output voltage characteristics**

Fig.15 Effects of zero current correction circuit

#### 11. How to use each pin and advice for designing

#### (1) Pin No.1 (FB pin)

#### **Function**

- (i) Inputs feedback signal of output voltage setting

- (ii) Detects FB pin open/short

- (iii) Detects output overvoltage state

#### How to use

- (i) Feedback signal input

- · Connection method

Connect the node of dividing resistance for output voltage setting

Operation

The PFC output voltage is controlled so that the FB pin voltage will correspond to the internal reference voltage (2.5 V).

For FB pin open circuit, FB pin is connected with pull-down resistance in IC inside. Therefore, take its resistance into account when choosing the resistance of R1 and R2 to set the output voltage (Vout).

Vout =

$$(R2 + Rfb)/(R2 \times Rfb) \times VREF \times R1 + VREF$$

where:

VREF: Reference voltage = 2.5 V (typ.)

Rfb: FB pin pull-down resistance =  $2.5 \text{ M}\Omega$  (typ.)

To avoid an erratic operation by noises, connect capacitance C3 of 100 to 3300 pF between FB pin and GND.

- (ii) FB pin open/short detection

- · Connection method

Same as feedback signal input in (i)

Operation

When, on account of FB pin open circuit or short circuit of R2 in resistive divider, the FB input voltage has dropped below 0.3 V, the output of comparator (SP) is inverted, thereby stopping the IC output.

- (iii) Output overvoltage detection

- · Connection method

Same as feedback signal input in (i)

Operation

In normal operation, FB pin voltage is almost the same as reference voltage of error amplifier (2.5 V). Like when the output voltage has risen for some reason, if the FB pin voltage reaches comparator reference voltage (1.09\*VREF), comparator (OVP) output is inverted to stop OUT pulses. As soon as output voltage returns to a normal level, OUT pulses are recovered.

Fig.16 FB pin circuit

#### (2) Pinl No.2 (VCMP pin)

#### **Function**

- (i) Phase compensation of output of incorporated voltage error amplifier (ERRAMP)

- (ii) Soft start

#### How to use

- (i) Phase compensation of incorporated ERRAMP output

- · Connection method

Connect R and C between COMP and GND as shown in Fig. 17

Operation

COMP pin avoids an appearance of the double frequency ripple of the AC line on the FB pin voltage with connecting R and C.

Reference:

Example of applied circuit: C4 = 0.47 uF

C5 = 2.2 uF

$R3 = 10 k\Omega$

The above is an example. Determine them upon sufficiently verifying your instrument.

Fig.17 VCMP pin circuit

- (ii) Soft start

- Connection method

The same as feedback signal input in (i)

Operation

Besides, Soft start function is realized by slowing a voltage rise of COMP pin with adjustment of capacitance connected between COMP and GND.

When starting, VCMP voltage rises and a switching operation starts at 0.5 V.

At this time, MOSFET ON width increases gradually in proportion to the COMP voltage rise. The soft start time is adjustable with adjustment with changing capacitors C4 and C5.

Increasing C4, C5 capacitance  $\rightarrow$  prolongs soft start time Decreasing C4, C5 capacitance  $\rightarrow$  shortens soft start time

#### (3) Pin No.3 (VDET pin)

#### **Function**

- (i) Input voltage detection (multiplier input)

- (ii) Switching of overcurrent detection level (OCP)

#### How to use

(i) Input voltage setting for VDET pin

Multiplier generates current reference signal. Its VDET pin (pin 3) receives sinusoidal full-waveform rectified waveforms. Considering the dynamic range of multiplier operation, VDET pin peak value would be used within 0.65 to 2.4 V. Therefore, set R6 and R7 in Fig. 17 so that the peak voltage of sinusoidal waveforms at VDET pin will be between 0.65 and 2.4 V with the entire range of AC input voltage.

Recommended dividing ratio: R6:R7 = 160:1

(ii) Switching of overcurrent detection level (OCP)

When the peak of the VDET voltage is the threshold voltage is equal to or greater than Vvdeth:1.6V, OCP level is high (Vocph: -0.4V).

Also, when VDET is the threshold voltage becomes equal to or less than Vvdetl:1.35V, OCP level is low (Vocpl: - 0.5V).

# (4) Pin No.4 (IS pin)

#### Functions

- (i) Inductor current detection

- (ii) Turn off OUT output upon detecting an overcurrent

#### How to use

(i) Inductor current detection

Via IS pin, inductor current signal is applied to current error amplifier (CUR\_AMP) that constitutes a current loop for making the input current follow sinusoidal waveforms. CUR\_AMP that is connected with multiplier output receives current reference signal. IS pin is current input terminal, and receives a potential of 0 to -0.4 V with respect to GND level.

(ii) Turn off OUT output upon detecting an overcurrent When IS pin voltage is lower than IS threshold voltage, comparator output signal is inverted to turn off OUT output.

Fig.18 VDET terminal circuit

Fig.19 IS pin circuit

Fig.20 IS pin circuit (2)

#### Advice for designing

When MOSFET turns on, MOSFET gate drive current and surge current are generated by discharge of stray capacitance, and then those currents flow to current detecting resistance Rs. An excessively large surge current may cause an erratic operation to disturb the input current waveform. Depending on the surge current intensity, timing, etc., pulse shoots may mix with turn-on parts of IC's OUT pulses. So, RC filter shown in Fig. 18 is connected in generally.

Since the level is determined by resistive division as shown in Fig. 18, 100  $\Omega$  or lower is recommended for input resistance R4.

Rated voltage at IS pin for input of inductor current signal is -5 V.

In case of a general boost circuit, a rush current flows for charging the output smoothing capacitance C2 the instant an AC input voltage has been connected. This current may be considerably greater than at a steady operation. As a result, IS pin may receive a voltage that is far higher than usual. Even if such AC voltage is connected, IS pin must not be exposed to a potential higher than -5 V that is an absolute maximum rated voltage.

There may be the case that a voltage higher than the rated is applied to IS pin. In such case, it needs to use a preventive circuit for suppression of a rush current or to add the Zener diode to IS pin as shown in Fig. 19.

#### Notes)

#### Maximum power design

It needs a notice about a setting of the sense resistance to output maximum power at whole input condition because a power limitation may occur by IC functions.

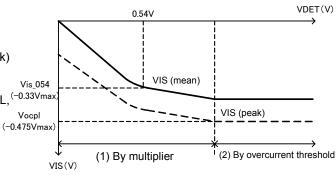

Fig. 20 shows a block diagram concerning the input current control.

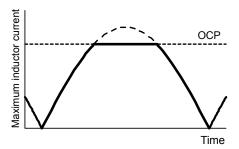

The VDET voltage is relatively high at high RMS input voltage, and the input current is limited by OCP function shown in the path B of Fig. 20 in such case. (Reference figure is shown in Fig. 21.)

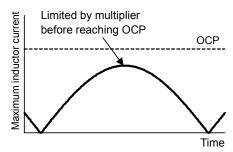

The VDET voltage is relatively low at the low RMS input voltage, and the maximum output voltage of multiplier is low too. So, the input current is limited by the multiplier shown in the path A of Fig. 20 in such case. (Reference figure is shown in Fig. 22.)

This means that the maximum inductor current is limited by an above function unless the reasonable sense resistance is chosen.

Therefore, it needs to choose the sense resistor Rs which satisfies each condition shown in the next page.

Fig.21 Current control area block diagram

Fig.22 Maximum inductor current at high input voltage Fig.23Maximum inductor current at low input voltage

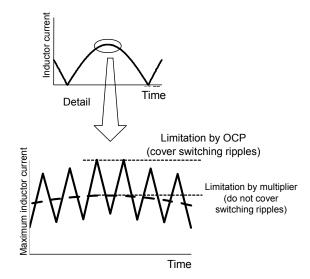

Note that the limitation of maximum inductor current is different as shown in Fig. 24 according to whether by OCP or by multiplier.

- By OCP: Current peaks including switching ripples are subjected to limitation.

- By multiplier: Current excluding switching ripples is subjected to limitation.

Design current detecting resistance Rs so as to meet a maximum power in the input voltage range, and also to clear 2 power limiting conditions below (Fig. 25).

## (1) Power limitation by multiplier

Design current detecting resistance Rs so that VIS voltage (mean) will be -0.33 V or greater that is maximum of item "IS pin voltage (Vis\_054)".

In case of settling as output power Po (W), efficiency  $\eta$ , and minimum input voltage Vacmin (V), maximum inductor current linmax (A) is given by following equation.

$$linmax = \sqrt{2} \cdot \frac{Po}{\eta \times Vacmin}$$

VIS voltage (mean) will be -0.33 V or higher when:

-Rs×linmax > -0.33V

-Rs×

$$\sqrt{2}$$

• Po  $\frac{\text{Po}}{\eta \times \text{Vacmin}}$  > -0.33V

Therefore, design current detecting resistance Rs  $(\Omega)$  so as to meat:

$$Rs < \frac{0.33 \times \eta \times Vacmin}{\sqrt{2} \times Po} (\Omega) \quad \dots (1)$$

## (2) Power limitation by OCP

Design current detecting resistance Rs so that VIS voltage (peak) will be -0.475 V or greater that is maximum of IS threshold voltage (Vocpl).In case of settling as ripple current Iripple (A), Switching frequency fsw, output voltage Vout, boost inductance L, (-0.33Vma: and ON duty D, ON duty D is given by following equation.

$$D = \frac{Vout - \sqrt{2} Vac \, min}{Vout}$$

VIS voltage (peak) will be -0.475 V or higher when:

$$\begin{split} &- \text{Rs} \times (\text{linmax} + \frac{\text{lripple}}{2}) > -0.475 \text{V} \\ &- \text{Rs} \times (\frac{\sqrt{2} \times \text{Po}}{\eta \times \text{Vacmin}} + \frac{\sqrt{2} \times \text{Vacmin} \times \text{D}}{2 \times \text{fsw} \times \text{L}}) > -0.475 \text{V} \end{split}$$

Therefore, design current detecting resistance Rs  $(\Omega)$  so as to meat:

$$\mathsf{Rs} \! < \! \frac{0.475}{\frac{\sqrt{2} \times \mathsf{Po}}{\eta \times \mathsf{Vacmin}} + \frac{\mathsf{Vac\,min} \times \mathsf{D}}{\sqrt{2} \times \mathsf{fsw} \times \mathsf{L}}}$$

In order to output maximum power at a minimum input voltage, therefore, select Rs determined by expression (1) or (2), whichever smaller.

#### Notes)

To define a current limitation by multiplier, select the voltage at VDET pin so as to be 0.54 V or higher even at a minimum input voltage.

Fig.24 Maximum current limitation

Fig.25 Maximum power limitation

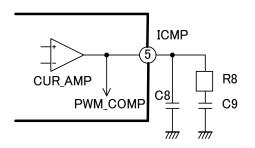

#### (5) Pin No. 5 (ICMP pin)

#### **Functions**

(i) Phase compensation for output of incorporated current error amplifier (CUR AMP)

#### How to use

- (i) Phase compensation for output of incorporated CUR\_AMP

- · Connection method

Connect R and C between ICMP and GND as shown in Fig. 26.

Operation

R and C are connected to ICMP pin to block ripple components of switching frequency that could otherwise appear on IS pin input.

(Reference)

Example of applied circuit: C8 = 470 pF

C9 = 1000 pF

$R8 = 22 \text{ k}\Omega$

The above is an example. Determine them upon sufficiently verifying your instrument.

#### (6) Pin No. 6 (GND pin)

#### **Functions**

Constitutes the reference of each part of IC.

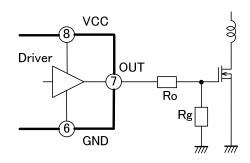

### (7) Pin No. 7 (OUT pin)

#### **Functions**

- (i) Drives MOSFET

- (ii) Sets oscillation frequency

# How to use

- (i) Drive of MOSFET

- · Connection method

- Connected via resistance Ro to gate terminal of MOSFET

- Operation

Goes high when MOSFET is turned on. Nearly VCC voltage is outputted.

Goes low when MOSFET is turned off. Voltage of nearly 0 V is outputted.

Advice for designing

Connect a gate resistance for current limitation at OUT pin, prevention of oscillation of gate terminal voltage, etc.

Rated output currents of IC: Source ... 1.5 A, sink ... 1.5 A.

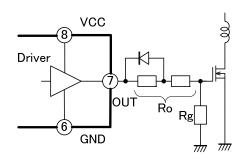

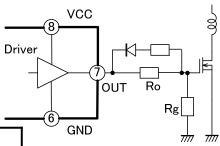

Connection in Fig. 28 or 29 allows to distinctly set the gate drive currents for turning on and off MOSFET.

- (ii) Setting of oscillation frequency

- · Connection method

- (1) Ordinary connection

Connect resistance Rg between MOSFET gate and GND if no buffer is connected on IC output as shown in Fig. 27, 28 and 29. According to resistance Rg, switching frequency can be selected out of 3 different modes given in table below.

\* Ro: 100 Ω max.

#### Notes)

- $\cdot$  Resistance Ro between OUT pin and FET gate must be 100  $\Omega$  or less

- · If mode 3 is selected (27 kΩ used), starting up the frequency setting raises the OUT-GND voltage up to 1.4V

Fig.26 ICMP pin circuit

Fig.27 OUT pin circuit (1)

Fig.28 OUT pin circuit (2)

Fig.29 OUT pin circuit (3)

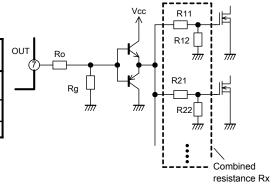

#### (2) If buffer is connected on IC output

If buffer is connected on IC output, select a configuration shown in Fig. 30, and select the frequency setting resistance as given in table below.

|       |                     | Resistance<br>Rg | Accuracy | Temperature characteristics |

|-------|---------------------|------------------|----------|-----------------------------|

| Mode1 | Frequency diffusion | 4.7kΩ            | ±5%max   | 200ppm/°Cmax                |

| Mode2 | 130kHz fixed        | 13kΩ             | ±5%max   | 200ppm/°Cmax                |

| Mode3 | 120kHz fixed        | 30kΩ             | ±5%max   | 200ppm/°Cmax                |

<sup>\*</sup> Ro: 100 Ω max.

If combined resistance connected on buffer output is Rx, set Rx to 3  $k\Omega$  or higher taking into account dispersion and temperature characteristics.

#### Example:

Select R11 = 10  $\Omega$ , and R12 = 10 k $\Omega$ . Suppose their resistance may change by 10% maximum on account of their dispersion and temperature characteristics. If 3 of them each are connected in parallel,

Rx = 10.01 k $\Omega$  × 90%  $\div$  3 = 3.003 k $\Omega$  holds, thereby clearing the requisite.

#### Notes)

- $\cdot$  Resistance Ro between OUT pin and buffer must be 100  $\Omega$  or less

- · If mode 3 is selected (30 kΩ used), starting up the frequency setting raises the OUT-GND voltage up to 1.2 V

- Above conditions presuppose hFE of transistor used in buffer is 50 minimum, and that Vbe is 0.3 V maximum taking

the temperature characteristics into account. Unless characteristics of a particular transistor to use clear the

requisites, set the frequency resorting to a method in "(3) Other circuit configuration."

#### (3) Other circuit configuration

Unless the circuit configuration connected to OUT pin clears the specifications in (1) nor (2), determine the frequency based on the current and voltage defined by specified frequency setting.

(See p. 15 Fig. 5 Frequency setting circuit)

Be sure to take into account the IC characteristics, and dispersion and temperature characteristics of parts connected to OUT pin.

#### General precaution about frequency setting:

In setting the frequency, make sure, in addition to respecting our recommendations in (1) and (2) above, there is no problem of influences by dispersion and temperature characteristics of your resistors, wiring, noise (influence of auxiliary power supply that operates before PFC starts, in particular) and other matters than resistance itself based on the current and voltage regarding the specified frequency setting.

In setting of the frequency, please confirm whether there is no bad influence of following items including our setting recommendation and our setting specification.

- Dispersion of or the temperature characteristic of resistance used, a design of wiring, noise (especially from sub power supply before the PFC start operation), etc.

Fig.30 Buffer

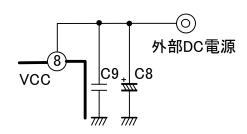

#### (8) Pin No. 8 (VCC pin)

#### Function

(i) Supplies IC with power Application

- (i) Supplies IC with power

- Wiring

Connect a startup resistance between rectified voltage line and VCC pin.

Generally, connect a rectified and smoothed voltage from auxiliary winding provided on transformer.

Or connect an external DC source.

#### Operation

At the time of startup in case VCC voltage is obtained from auxiliary winding, the current via the startup resistance charges the smoothing capacitance and, when the level rises up to UVLO ON threshold voltage, IC starts up. Immediately before startup, a current of at least 110 uA (max.) that is a startup current for IC must be fed. During a steady operation, VCC is supplied from inductor's auxiliary winding (Fig. 31).

As the source voltage rises from zero, the operation starts at 9.6 V (typ.) for FA5614, or at 13 V (typ.) for FA5615.

Any of started-up ICs stops operating when the source voltage drops down to 9 V (typ.)

While IC stops operation by under voltage lockout circuit, OUT pin keeps low level and shuts the output of power supply off.

#### · Advice for designing

Under voltage lockout function avoids an erratic operation of circuit when source voltage has dropped.

Noise applied to VCC pin will cause an erratic operation. To avoid the noise, connect a capacitance near VCC pin whether IC is operated by another source or not. Determine the capacitance so that the noise generated on VCC pin will be within  $\pm 0.6$  V, and make doubly sure no erratic operation occurs by noise (Fig. 32).

Fig.31 VCC pin circuit (1)

Fig.32 VCC pin circuit (2)

#### 12. Advice for design

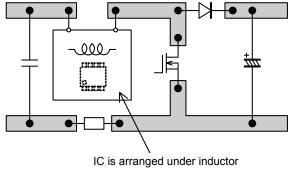

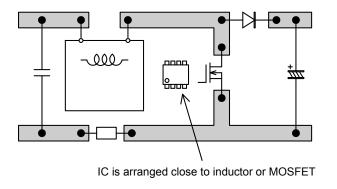

#### (1) Advice in pattern designing

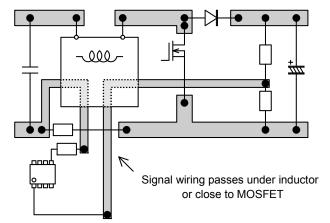

Main circuit MOSFET, inductor, diodes, etc. perform switching under high voltage and large current. If wiring of IC or signals inputted to IC gets too near such main circuit parts, they may operate erratically upon being affected by noise generated there. Attention must be paid particularly in following cases (examples of faulty cases).

- IC is arranged under inductor or other main circuit parts, or immediately behind main circuit parts on double sided circuit board (Fig. 33)

- IC is arranged close to inductor, MOSFET or diode (Fig. 34)

- Signal wiring is placed under inductor or near MOSFET or diode (Fig. 35)

(or on immediately opposite side on circuit board)

Fig.33 Example of inadvisable arrangement (1)

Fig.34 Example of inadvisable arrangement (2)

Fig.35 Example of inadvisable pattern

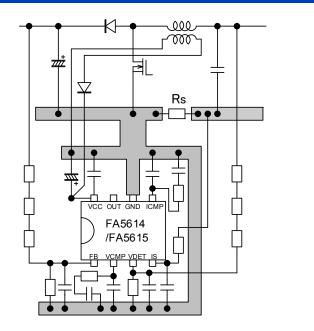

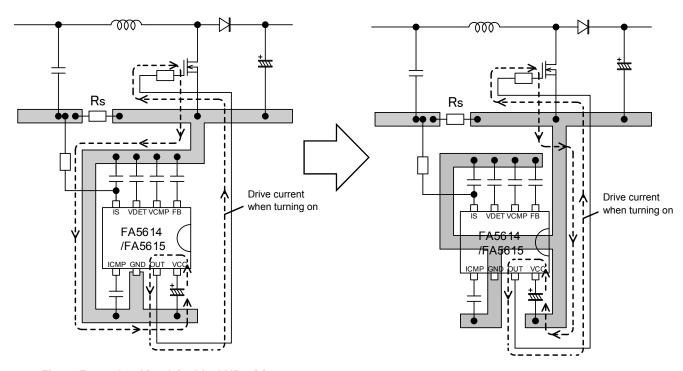

#### (2) Typical GND wiring in IC area

To minimize influences on IC of noises from main circuit, separate GND of IC and signal lines for parts of IC area, and GND of PFC main circuit away from each other, and connect them via one point near current detecting resistance Rs and output capacitance.

IS signal whose voltage level is low is liable to noise. Minimize lengths of IS pin-Rs and Rs-GND wiring. Arrange VCC-GND capacitance close to IC. Otherwise, the effect will be poor.

Arrange the capacitance between IC area input terminal and GND close to IC. It also has a function of noise elimination and, if away from IC, it will be affected by noise.

#### Notes)

Wiring is exemplified for you to understand how to connect the GND line.

Noise and incidental erratic operations differ from one instrument to another. Adopting any wiring exemplified in Fig. 36 will not necessarily guarantee normal operations of your instruments.

Rs

FA5614

/FA5615

ICMP GND OUT VCC

Fig.36 Example of advisable GND wiring

Fig.37 Example of inadvisable GND wiring (GND is common to signal line parts and main circuit)

Fig.38 Example of inadvisable GND wiring (Liable to noise when turning on if GND is common to VCC capacitance and signal line)

Fig.39 Example of GND wiring (GND of VCC capacitance is distinct from signal line GND)

# (3) Cautions in use about pin noise

If noise is applied to any IC pin, an erratic operation may be caused. Proceed to design upon respecting the precautions below.

| ioisc is applicu                                                                         | to an                                         | y ic pin, an erralic operation may be car                                                                                                                              | used. I roceed to design apon res                                                                | pecting the precaution                                                      |  |

|------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| 条件<br>condition                                                                          | 端子<br>Pin                                     | 懸念される不具合<br>malfunction in fear                                                                                                                                        | 入力の規定<br>Input regulations                                                                       | 設計上の注意事項<br>cautions in design                                              |  |

|                                                                                          |                                               | ノイズが過電圧保護レベルを越えると、スイッチングが<br>停止する可能性がある<br>switching may stop when noise is over over voltage<br>protection level                                                      | 入力信号は出力電圧のフィードバック電圧のみ                                                                            | 端子直近にコンデンサを接続                                                               |  |

|                                                                                          | FB                                            | ノイズがショート検出レベルを下回るとICがスタンバイモードになる可能性がある<br>IC may become stanbay mode when noise is under short<br>detection level                                                      | 入が信号は出が電圧のフィードバッグ電圧の終<br>とすること<br>input signal is only for feedback voltage of<br>output voltage | すること<br>connect capacitor near<br>terminal pin                              |  |

|                                                                                          |                                               | 出力電圧にオフセットが発生し、出力電圧が上昇又は低下する可能性がある<br>offset occurs in output voltage and output voltage rises or<br>falls                                                             |                                                                                                  |                                                                             |  |

|                                                                                          |                                               | 乗算器出力が不安定になり、入力電流波形が乱れる可能性がある<br>output of multiplier output becomes unstable, and input<br>current waveform may disturbed                                             |                                                                                                  |                                                                             |  |

|                                                                                          | VCMP                                          | ノイズがスレッシュホールド電圧超えると、スイッチングする可能性がる<br>switching may become when noise is over threshold<br>voltage                                                                      | ノイズが入らないようにすること<br>cancel noise                                                                  | 位相補償の定数は十分確認すること<br>confirm sufficiently phase<br>compensation constant     |  |

|                                                                                          |                                               | ノイズがスレッシュホールド電圧を下回ると、スイッチ<br>ングが停止する可能性がある<br>switching may stop when noise is under threshold voltage                                                                 |                                                                                                  |                                                                             |  |

| ノイズ入力<br>(定格電圧以内)<br>input noise<br>(within absolute<br>maximum ratings)                 | VDET                                          | 乗算器出力が不安定になり、入力電流波形が乱れる可能<br>性がある<br>output of multiplier output becomes unstable, and input<br>current waveform may be disturbed                                      | ノイズが入らないようにすること<br>cancel noise                                                                  | 端子直近にコンデンサを接続<br>すること<br>connect capacitor near pin                         |  |

|                                                                                          | IS                                            | 正確に電流検出しない可能性がある<br>current may be detected incorrectly                                                                                                                | ノイズが入らないようにすること<br>cancel noise                                                                  | 端子直近にコンデンサを接続<br>すること<br>connect capacitor near pin                         |  |

|                                                                                          |                                               | 過電流保護スレッシュレベルを超えると、ターンオフする可能性がある<br>It may turn off when noise is over overcurrent protection<br>level                                                                 | ノイズが入らないようにすること<br>cancel noise                                                                  | 端子直近にコンデンサを接続<br>すること<br>connect capacitor near pin                         |  |

|                                                                                          | ICMP                                          | デューティが変化し、入力電流波形が乱れる可能性がある<br>because a duty changes, input current waveform may be<br>disturbed                                                                       | ノイズが入らないようにすること<br>cancel noise                                                                  | 位相補償の定数は十分確認す<br>ること<br>confirm sufficiently phase<br>compensation constant |  |

|                                                                                          | GND                                           | 基準電位が変動し、ICが正常な動作をしない可能性がある<br>reference voltage changes, IC may not behave normally                                                                                   | ノイズが入らないようにすること<br>cancel noise                                                                  | GND配線は太い配線にすること<br>ground wiring should be a wide<br>wiring                 |  |

|                                                                                          | OUT                                           | 周波数設定中にノイズが入ると、誤って周波数を設定する可能性がある IC may set wrong frequency mode, noise enters OUT pin when IC is setting frequency mode ドライバの能力以上の信号が入力されるとMosを正常に駆動できず、出力が低下する可能性がある | ノイズが入らないようにすること<br>cancel noise                                                                  | _                                                                           |  |

|                                                                                          | VCC                                           | the output may fall not to be able to drive Mos normally when signals more than  UVLOを下回るノイズが入力されるとICが停止する可能性 がある                                                      | 動作時にUVLOを下回るノイズを入力しないこと                                                                          | 端子直近にコンデンサを接続<br>すること                                                       |  |

|                                                                                          |                                               | IC may stop when noise under UVLO is input                                                                                                                             | don't input noise under UVLO when moving                                                         | connect capacitor near pin                                                  |  |

|                                                                                          | FB<br>VCMP<br>VDET<br>ICMP<br>VCC             | 寄生素子が動作し、IC停止等の誤動作が発生する可能性<br>がある<br>a parasitism element works, and the malfunction such as<br>IC stop may occur                                                      |                                                                                                  | _                                                                           |  |

| マイナス電圧入力<br>(絶対最大定格以下)<br>input minus voltage<br>(less than absolute<br>maximum voltage) | IS                                            | ICが破壊する可能性がある<br>IC may be destroyed                                                                                                                                   | 絶対最大定格を下回るマイナス電圧を入力しないこと<br>いこと                                                                  | _                                                                           |  |

|                                                                                          | OUT                                           | ICが破壊する可能性がある<br>IC may be destroyed                                                                                                                                   | don't input minus voltage less than maximum<br>absolute voltage                                  | _                                                                           |  |

|                                                                                          | VCC                                           | 寄生素子が動作し、IC停止等の誤動作が発生する可能性<br>がある<br>a parasitism element works, and the malfunction such as<br>IC stop may occur                                                      |                                                                                                  | -                                                                           |  |

| プラス電圧入力<br>(絶対最大定格以上)                                                                    |                                               | ICが破壊する可能性がある<br>IC may be destroyed                                                                                                                                   | 絶対最大定格を上回るプラス電圧を入力しないこと                                                                          |                                                                             |  |

| (杷对取入定恰以上) input plus voltage (more than absolute maximum voltage)                       | IS GNDレベルが変動する可能性がある gnd level may be changed |                                                                                                                                                                        | don't input minus voltage more than maximum absolute voltage                                     | _                                                                           |  |

|                                                                                          |                                               | ICが破壊する可能性がある<br>IC may be destroyed                                                                                                                                   |                                                                                                  |                                                                             |  |

# 13. Example of application circuit ( 390V / 0.75A output )

Note) This application circuit is a reference material for describing typical usage of this IC, and does not guarantee the operation or characteristics of the IC.

# **Notice**

- 1. The contents of this note (Product Specification, Characteristics, Data, Materials, and Structure etc.) were prepared in July 2016. The contents will subject to change without notice due to product specification change or some other reasons. In case of using the products stated in this document, the latest product specification shall be provided and the data shall be checked.

- 2. The application examples in this note show the typical examples of using Fuji products and this note shall neither assure to enforce the industrial property including some other rights nor grant the license.

- 3. Fuji Electric Co.,Ltd. is always enhancing the product quality and reliability. However, semiconductor products may get out of order in a certain probability. Measures for ensuring safety, such as redundant design, spreading fire protection design, malfunction protection design shall be taken, so that Fuji Electric semiconductor product may not cause physical injury, property damage by fire and social damage as a result.

- 4. Products described in this note are manufactured and intended to be used in the following electronic devices and electric devices in which ordinary reliability is required:

- Computer OA equipment Communication equipment (Pin) Measuring equipment

- Machine tool Audio Visual equipment Home appliance Personal equipment

- Industrial robot etc.

- 5. Customers who are going to use our products in the following high reliable equipments shall contact us surely and obtain our consent in advance. In case when our products are used in the following equipment, suitable measures for keeping safety such as a back-up-system for malfunction of the equipment shall be taken even if Fuji Electric semiconductor products break down:

- Transportation equipment (in-vehicle, in-ship, railways, etc.) Communication equipment for trunk line

- Traffic signal equipment Gas leak detector and gas shutoff equipment

- Disaster prevention/Security equipment Various equipment for the safety.

- 6. Products described in this note shall not be used in the following equipments that require extremely high reliability:

- Space equipment Aircraft equipment Atomic energy control equipment

- Undersea communication equipment Medical equipment.

- 7. When reprinting or copying all or a part of this note, our company's acceptance in writing shall be obtained.

- 8. If obscure parts are found in the contents of this note, contact Fuji Electric Co.,Ltd. or a sales agent before using our products. Fuji Electric Co.,Ltd. and its sales agents shall not be liable for any damage that is caused by a customer who does not follow the instructions in this cautionary statement.

- The contents will subject to change without notice due to product specification change etc.

- Application examples and component in this sheet is for the purpose of assisting in the design.

Therefore, This sheet has not been made in consideration of the margin.

- Before using, Please design in consideration of the parts variation and use condition.