# Inductive Cell Balancer IC with Balancing Current Up to 2A

## DESCRIPTION

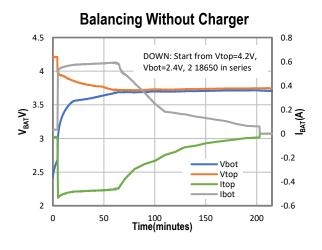

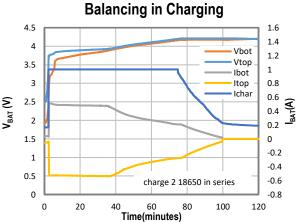

ETA3001 is an inductive cell balancer. Unlike conventional passive balancing technique, ETA3001 utilizes a control scheme with an inductor to shuffle currents between two cells until the cells are balanced. Due to the switching nature, the heat and power dissipation generated in conventional linear balance technique are greatly reduced. The balance time is also significantly reduced due to higher balancing current not being limited by package thermal dissipation.

ETA3001 consumes only 2µA ultra-low current from batteries in standby mode, extending the battery shelf time. The final balanced voltages of both cells are also highly accurate which enhances the performance and lifetime for the batteries connected in series. ETA3001 can also be used in multiple cells stacking with even number of cells. ETA3001 includes protection features similar to precondition in battery charging, that is when one cell's voltage is grossly lower than the other, the balancing current is reduced to a safe level until the lower voltage cell is charged up.

# FEATURES

- Inductive, switching control scheme

- Up to 90% charger transfer efficiency

- Accurate balanced voltages down to 30mV

- Auto detect unbalance and auto balance

- Low sleeping supply current, 2μA

- Programmable balancing current up to 2A

- Precondition balancing current

- Status indications

- Battery over voltage protection

- Support small size inductor

# **APPLICATIONS**

- Multi-cells System

- Battery Pack

- Portable Equipment and Instrumentation

- Battery Backup Systems

- E-Cigarette

ETA3001 is available in DFN2x2-8 package.

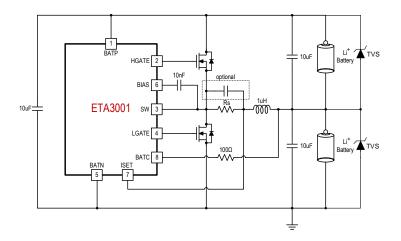

## TYPICAL APPLICATION

Figure 1: Typical Application Circuit

# ORDERING INFORMATION

PART No.

PACKAGE

TOP MARK

Pcs/Reel

ETA3001D2I

DFN2x2-8L

G3<u>YW</u>

3000

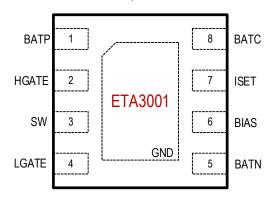

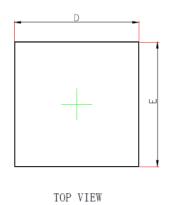

# PIN CONFIGURATION

DFN2x2-8

# ABSOLUTE MAXIMUM RATINGS

(Note: Exceeding these limits may damage the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.)

# **Recommended Operating Conditions**

(Note: The device is not guaranteed to function outside its operating conditions.)

Ambient Temperature Range .....-40°C to 85°C Junction Temperature Range .....-40°C to 125°C

# **ELECTRICAL CHARACTERISTICS**

$(T_A=25\,^{\circ}C, L=1\mu H, C_{BOT}=C_{TOP}=10\mu F \text{ if not specified})$

|                    | PARAMETER                        | TEST CONDITIONS                     | MIN TYP | MAX | UNIT |

|--------------------|----------------------------------|-------------------------------------|---------|-----|------|

| SUPPLY             |                                  |                                     |         |     |      |

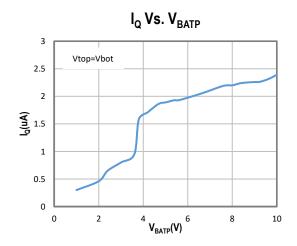

|                    | Quiescent current                | V <sub>BATP</sub> =8V,              | 2       |     |      |

| SUPPLY             | Quiescent current                | VBATP-VBATC=VBATC-VBATN             |         |     | μA   |

| ISUPPLY            | Operating supply current         | V <sub>BATP</sub> =8V, in balancing | 900     |     |      |

|                    | Operating supply current         | mode, No Switching                  | 900     |     | μΑ   |

| V <sub>BATP</sub>  | VBATP operating voltage          |                                     |         | 10  | V    |

| V <sub>BATC</sub>  | VBATC operating voltage          |                                     |         | 5   | V    |

| UVLO               | Under lock-out voltage threshold | V <sub>BATP</sub> Rising            | 3.75    |     | V    |

| UVLO_HYS           | UVLD hysteresis                  |                                     | 200     |     | mV   |

| DETECTION          |                                  |                                     |         |     |      |

| TSLEEP             | Detection interval timer         | Part sleeps during                  | 2       |     | S    |

|                    | Detection interval timel         | TSLEEP                              |         |     | 3    |

| T <sub>ALLOW</sub> | Unbalance detection              | Unbalance status is                 | 3.85    |     | mS   |

|                   | acknowledgment timer                                                                         | accepted after T <sub>ALLOW</sub>                          |            |         |

|-------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|------------|---------|

|                   | _                                                                                            | when enter CHECK                                           |            |         |

|                   |                                                                                              | state.                                                     |            |         |

|                   |                                                                                              | IC get back to                                             |            |         |

| т                 | Maxima una cuale al ance ale action a time                                                   | sleeping mode if don't                                     | 7.60       | C       |

| Тснеск            | Maximum unbalance checking time                                                              | detect unbalance                                           | 7.68       | mS      |

|                   |                                                                                              | after T <sub>CHECK</sub>                                   |            |         |

|                   |                                                                                              | Maximum switching                                          |            |         |

| $T_{DONE}$        | Finishing Timer                                                                              | skip before enter                                          | 62         | mS      |

|                   |                                                                                              | sleep mode                                                 |            |         |

|                   |                                                                                              | Balancing only work if                                     |            |         |

| VKICK             | Unbalance detection threshold                                                                | OVP>VBATP>UVLO                                             | 100        | mV      |

| VINOR             | Chibalance detection threshold                                                               | and V <sub>KICK</sub> Detected                             | 100        | ""      |

|                   |                                                                                              | between 2 cells                                            |            |         |

|                   |                                                                                              | Error voltage between                                      |            |         |

| Verror            | Balancing Accuracy                                                                           | 2 cells after balancing                                    | -70 70     | mV      |

|                   |                                                                                              | finish                                                     |            |         |

| BALANCE CONT      |                                                                                              |                                                            | T          | 1       |

| FREQ              | Switching Frequency                                                                          | PWM Clock                                                  | 1          | MHz     |

| AVERAGE           | Average Inductor current Regulation                                                          |                                                            | 1          | Α       |

| PRECOND           | Precondition current Regulation                                                              | $R_S = 50 \text{m}\Omega$                                  | 100        | mA      |

| BATTERY PROTE     |                                                                                              |                                                            |            | T       |

| TOP_OVP           | Top Cell over voltage protection threshold                                                   | V <sub>(BATP-BATC)</sub> Rising                            | 5          | V       |

| TOP_OVP_HYST      | TOP_OVP hysteresis                                                                           | V <sub>(BATP-BATC)</sub> Falling                           | 350        | mV      |

| BOT_OVP           | Bottom Cell over voltage protection                                                          | V <sub>(BATC-BATN)</sub> Rising                            | 5          | V       |

| BO1_OVF           | threshold                                                                                    | V(BAIC-BAIN) INSING                                        | CTOR       | v       |

| BOT_OVP_HYST      | BATC_OVP hysteresis                                                                          | V <sub>(BATC-BATN)</sub> Falling                           | 350        | mV      |

| TOP_PRECOND       | Top battery precondition threshold                                                           | V <sub>(BATP-BATC)</sub> Rising                            | 2.8        | V       |

| TOP_PREC_HYS T    | TOP_PRECOND hysteresis                                                                       | V <sub>(BATP-BATC)</sub> Falling                           | 150        | mV      |

| BOT_PRECOND       | Bottom battery precondition                                                                  | V <sub>(BATC-BATN)</sub> Rising                            | 2.8        | V       |

| BOT PREC HYS      |                                                                                              |                                                            |            |         |

| BOT_PREC_HYS      | threshold                                                                                    | V F.P                                                      | 450        |         |

| BOT_PREC_HYS<br>T | BOT_PRECOND hysteresis                                                                       | V <sub>(BATC-BATN)</sub> Falling                           | 150        | mV      |

|                   | BOT_PRECOND hysteresis                                                                       | V <sub>(BATC-BATN)</sub> Falling                           | 150        | mV      |

| T BALANCE PROT    | BOT_PRECOND hysteresis ECTION                                                                | V <sub>(BATC-BATN)</sub> Falling  DOWN direction:          |            |         |

| Т                 | BOT_PRECOND hysteresis                                                                       |                                                            | 150<br>4.5 | mV<br>A |

| T  BALANCE PROT   | BOT_PRECOND hysteresis  ECTION  Top cell drive current limit                                 | DOWN direction:                                            | 4.5        | A       |

| T BALANCE PROT    | BOT_PRECOND hysteresis ECTION                                                                | DOWN direction: V(BATP-BATC)> V(BATC-BATN)                 |            |         |

| T  BALANCE PROT   | BOT_PRECOND hysteresis  ECTION  Top cell drive current limit  Lower cell drive current limit | DOWN direction:  V(BATP-BATC)> V(BATC-BATN)  UP direction: | 4.5        | A       |

| TSD HYST | TSD Hysteresis | 30 | °C |

|----------|----------------|----|----|

|          |                |    |    |

# PIN DESCRIPTION

| PIN#        | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                           |  |  |  |  |

|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1           | BATP  | Sense voltage input for top cell. Connect a 10µF capacitor between BATP                                                                                                                                                                                                               |  |  |  |  |

|             |       | and BATC.                                                                                                                                                                                                                                                                             |  |  |  |  |

| 2           | HGATE | Control high side external MOSFET.                                                                                                                                                                                                                                                    |  |  |  |  |

| 3           | SW    | Switching node. Connected to an inductor.                                                                                                                                                                                                                                             |  |  |  |  |

| 4           | LGATE | Control low side external MOSFET.                                                                                                                                                                                                                                                     |  |  |  |  |

| 5           | BATN  | Negative terminal sense voltage input and common Ground pin.                                                                                                                                                                                                                          |  |  |  |  |

| 6           | BIAS  | Bias pin. Connect a 10nF capacitor from BIAS to SW.                                                                                                                                                                                                                                   |  |  |  |  |

| 7           | ISET  | Balancing current setting pin. Connect a resistor from SW to an inductor to program the balancing current. Under an extremely high noise environment, a 1nF capacitor between ISET pin and SW pin can improve the ISET voltage stability, so a capacitor position reservation here is |  |  |  |  |

|             |       | recommended.                                                                                                                                                                                                                                                                          |  |  |  |  |

| 8           | BATC  | Sense voltage input for bottom cell. Connect a 10µF capacitor between                                                                                                                                                                                                                 |  |  |  |  |

| 9           | DATO  | BATC and BATN.                                                                                                                                                                                                                                                                        |  |  |  |  |

| Exposed Pad | EP    | Connect it to GND.                                                                                                                                                                                                                                                                    |  |  |  |  |

#### **FUNCTIONAL BLOCK DIAGRAM BATP** <u>VDD</u> 1uA ВАТС Bandgap & VDD Battery **UVLO** Sense BIAS & BIAS & OVP Timer & TSD Upper Cell HGATE Control Driver Balance ¹∏sw Control Balance Lower Cell **ISET** Current Driver Sense LGATE ETA3001 BATN

Figure 2: Functional Block Diagram

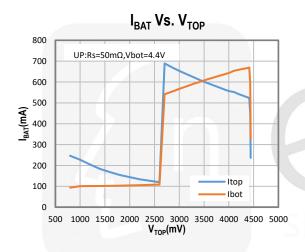

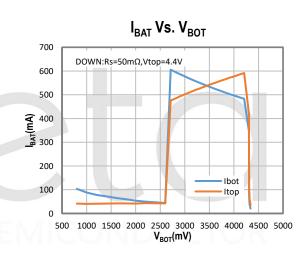

# TYPICAL PERFORMANCE CHARACTERISTICS

(TA=25°C, unless otherwise specified)

300.0% 5.000%/ Trig'd?

# TYPICAL PERFORMANCE CHARACTERISTICS Cont'd

(TA=25°C, unless otherwise specified)

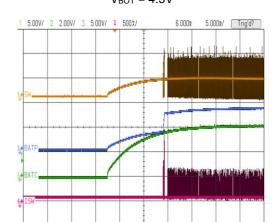

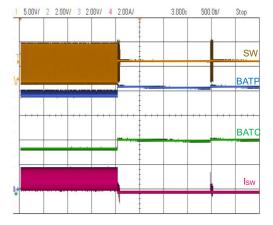

$V_{BOT}$  plug-in Start-Up ,  $V_{TOP}$  = Floating ,  $R_S$  =  $50m\Omega,$  $V_{BOT} = 4.3V$

$V_{BOT}$  plug-in Start-Up ,  $V_{TOP}$  = Shorted ,  $R_S$  =  $50m\Omega$ ,  $V_{BOT} = 4.3V$

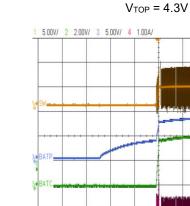

$V_{TOP}$  plug-in Start-Up ,  $V_{BOT}$  = Shorted ,  $R_S$  =  $50m\Omega$ ,  $V_{TOP} = 4.3V$

300.0% 5.000%/

$V_{\text{TOP}}$  plug-in Start-Up ,  $V_{\text{BOT}}$  = Floating ,  $R_{\text{S}}$  =  $50 m \Omega,$

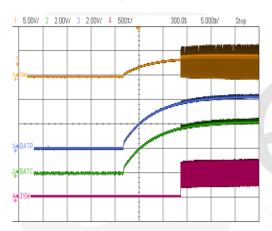

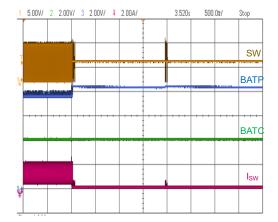

$V_{TOP}$  plug-out, DOWN Condition,  $R_S = 50 \text{m}\Omega$ ,  $V_{TOP}$  = 4.3V,  $V_{BOT}$  = 3.5V

1 5.00V/ 2 2.00V/ 3 2.00V/ 4 1.00A/

$V_{BOT}$  plug-out, DOWN Condition,  $R_S = 50 m\Omega$ ,  $V_{TOP} = 4.3V$ ,  $V_{BOT} = 3.5V$

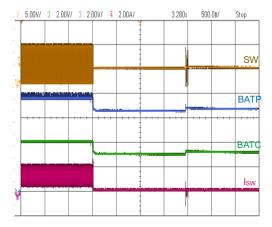

## TYPICAL PERFORMANCE CHARACTERISTICS Cont'd

(TA=25°C, unless otherwise specified)

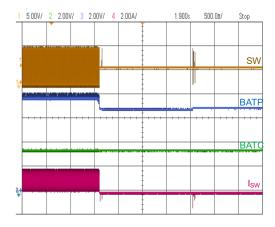

$V_{TOP}$  plug-out, UP Condition,  $R_S = 50m\Omega$ ,  $V_{BOT} = 4.3V$ ,  $V_{TOP} = 3.5V$

$V_{BOT}$  plug-out, UP Condition,  $R_S = 50m\Omega$ ,  $V_{BOT} = 4.3V$ ,  $V_{TOP} = 3.5V$

# FEATURE DESCRIPTION

The ETA3001 is a battery cell balancer with lossless inductive architecture based on ETA's proprietary technology. The technology is developed by ETA Solutions and any copy without ETA's agreement will be forbidden.

During operation, ETA3001 detects the difference between 2 cells then start balancing if the difference exceeds  $V_{\text{KICK}}$ . Once detected  $V_{\text{KICK}}$ , ETA3001 will discharge the higher voltage cell, store that discharging energy in the inductor then charge that energy to the lower voltage cell. ETA3001 keeps balancing until there is no difference between 2 cells.

ETA3001 technology allows balancing in either charge or discharge phases of the battery with minimized loss. Without unbalanced condition, ETA3001 operates in sleep mode with low supply current. This is an advantage to extend battery pack life time.

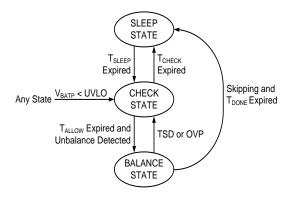

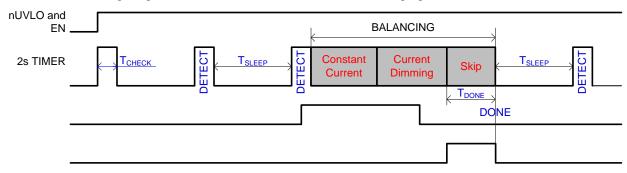

#### STATE MACHINE

The ETA3001 provides a completed state machine that controls whole operation intelligently. With this state machine, ETA3001 is equipped with self-protection from any accident during balancing. It also keeps the part stay asleep as much as possible until unbalance detected.

ETA3001 always starts from CHECK state when battery is plugged in.

Any fault always forces ETA3001 back to SLEEP State where ETA3001 burns only  $2\mu A$  (typically) from BATP.

Figure 3: State Machine Diagram

ETA3001 Rev 1.2

The ETA3001 timing diagram for state machine is shown in following figure.

Figure 4: Timing Profile

## **UNBALANCE DETECTION**

When state is in CHECK State, ETA3001 detects  $V_{\text{KICK}}$  difference between 2 cells to enter BALANCE State. If the top cell voltage is higher, balancing will be "DOWN", meaning discharge the top cell to charge to bottom cell. And if the bottom cell voltage is higher, balancing will be "UP", meaning discharge the bottom cell to charge to top cell.

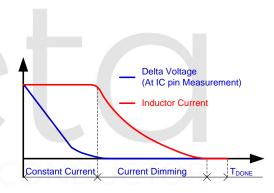

#### **BALANCING PROFILE**

ETA3001 balancing always starts with "Constant Current Regulation" phase since it is always with high voltage difference. Constant current is set by R<sub>ISET</sub>.

When the detected difference at IC pin is almost zero, but due to battery equivalent series resistance, real difference is not zero, then current is not immediately zero but reduced slowly depend on battery capacitance. This condition is called "Current Dimming" phase.

When two cell voltages are equal, balancing current becomes almost zero, when this persist for a time period of  $T_{\text{DONE}}$ , the balancing finishes one cycle, and ETA3001 goes back to SLEEP State.

Figure 5: Balancing Profile

#### **PROTECTION**

ETA3001 provides full protection to batteries that extend the life time of the batteries:

- ➤ Short and Low Voltage Protection: When either of the cell voltage below V<sub>PRECOND</sub>, maximum balancing current will be re-defined to 10% of the level set by ISET pin resistor.

- ➤ Open and Over Voltage Protection: When either of the cell voltage is greater than V<sub>OVP</sub>, ETA3001 will stop balancing, and go back to SLEEPING. Part will wake up after T<sub>SLEEP</sub>.

- ➤ Thermal Shutdown: When part gets hotter than 160°C, ETA3001 will stop balancing, and go back to SLEEPING. Part will wake up after T<sub>SLEEP</sub>.

- Current Limit Protection: Maximum of the peak of inductor current is allowed to 5.5A.

ETA3001 Rev 1.2

# APPLICATION INFORMATION

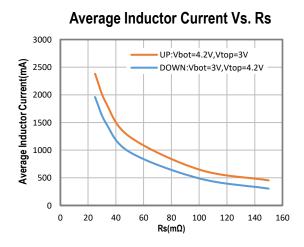

## **BALANCING CURRENT SETTING**

Balancing current is defined as the average inductance current. Average inductance current is regulated following ISET resistor configuration.

| AVERAGE              | RECOMMENDED COMPONENT |                   |          |                      |  |  |  |  |

|----------------------|-----------------------|-------------------|----------|----------------------|--|--|--|--|

| INDUCTION<br>CURRENT | ISET RESSITOR         | ISET<br>CAPACITOR | INDUCTOR | BATTERY<br>CAPACITOR |  |  |  |  |

| 500mA                | 100mΩ                 | 0pF – 10nF        | 0.47-1µH | 4.7μF – 10μF         |  |  |  |  |

| 625mA                | 80mΩ                  | 0pF – 10nF        | 0.68-1µH | 4.7μF – 10μF         |  |  |  |  |

| 800mA                | 62.5mΩ                | 0pF – 10nF        | 0.68-1µH | 4.7μF – 10μF         |  |  |  |  |

| 1000mA               | 50mΩ                  | 0pF – 10nF        | 0.68-1µH | 4.7μF – 10μF         |  |  |  |  |

| 1250mA               | 40mΩ                  | 0pF – 10nF        | 0.68-1µH | 10μF                 |  |  |  |  |

| 1515mA               | 33mΩ                  | 0pF – 10nF        | 0.68-1µH | 10μF                 |  |  |  |  |

| 1667mA               | 30mΩ                  | 0pF – 10nF        | 1μH      | 10μF                 |  |  |  |  |

| 2000mA               | 25mΩ                  | 0pF – 10nF        | 1µH      | 10μF                 |  |  |  |  |

#### RESTRICTED CONDITIONS

ETA3001 does not allow following restricted conditions:

- Reverse battery connection

- Short SW to any of BATN, BATP, BATC

- Exceed the absolute maximum rating of each IC pin

#### **MOSFETs SELECTION**

External N-type MOSFETs must meet the condition of  $V_{DS}>12V$ . The value of Qg should range from 1nC to 3nC, which can make the MOSFETs respond faster.

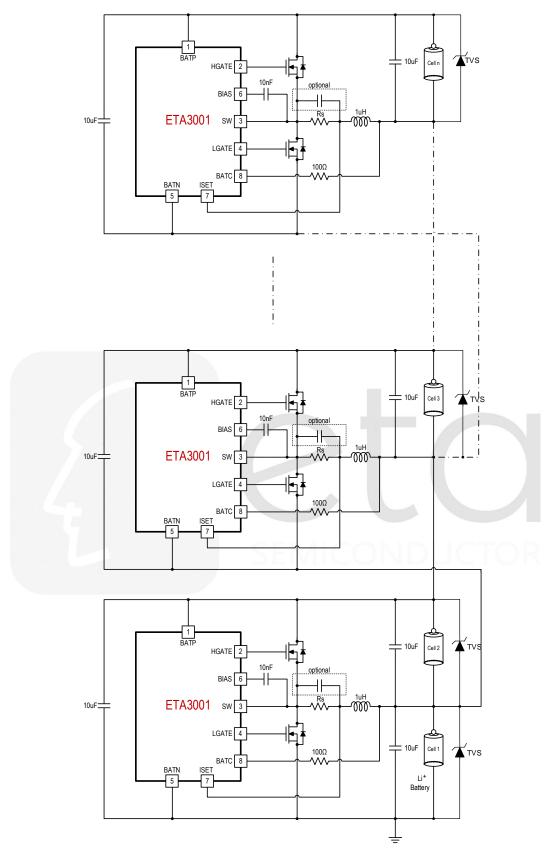

## MULTI-CELLS BALANCING SOLUTION

It is also possible to use several ETA3001 ICs in application to balance multi-cell series battery, such as shown in the Figure 6 (n cells).

For example, Figure 6 shows a typical solution for 4-cell-battery in laptop battery pack.

Each ETA3001 manages balancing of 2 neighbor cells. Each ETA3001 operates independently.

Figure 6: Multi-Cell Balancing Solution

ETA3001 Rev 1.2

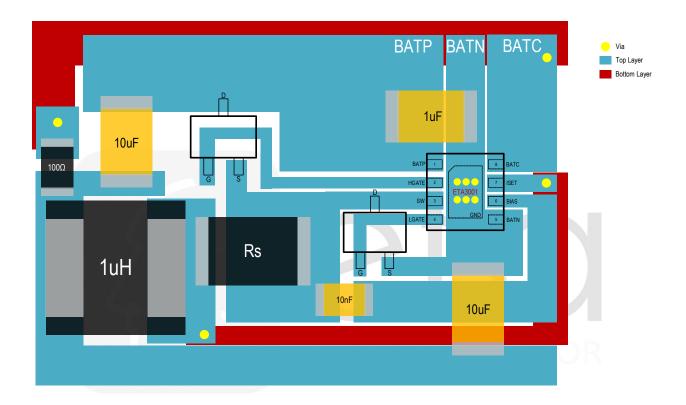

# PCB DESIGN GUIDELINE

In an UP case that bottom cell voltage is greater than top cell voltage, bottom cell becomes input and top cell becomes output of the switching regulation. In a DOWN case that top cell voltage is greater than bottom cell voltage, top cell becomes input and bottom cell becomes output. These mean parallel battery capacitors are always output capacitor or input capacitor for regulator. So please require to locate as close as possible to IC pins to minimize series resistance.

Please try to get the order of battery pins are BATP – BATC – BATN to make an easy battery connection.

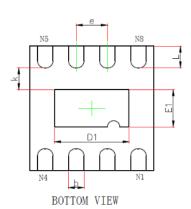

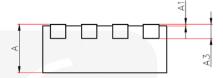

# PACKAGE OUTLINE

Package: DFN2x2-8

SIDE VIEW

| Symbol |             | sions In<br>neters | Dimensions In Inches |       |  |  |

|--------|-------------|--------------------|----------------------|-------|--|--|

|        | Min         | Max                | Min                  | Max   |  |  |

| Α      | 0.700       | 0.800              | 0.028                | 0.031 |  |  |

| A1     | 0.000 0.050 |                    | 0.000                | 0.002 |  |  |

| A3     | 0.203       | REF                | 0.008 REF            |       |  |  |

| D      | 1.924       | 2.076              | 0.076                | 0.082 |  |  |

| Е      | 1.924       | 2.076              | 0.076                | 0.082 |  |  |

| D1     | 1.100       | 1.100 1.300        |                      | 0.051 |  |  |

| E1     | 0.500       | 0.700              | 0.020                | 0.028 |  |  |

| k      | 0.200       | ) MIN              | 0.008 MIN            |       |  |  |

| b      | 0.200       | 0.300              | 0.008                | 0.012 |  |  |

| е      | 0.500 TYP   |                    | 0.020 TYP            |       |  |  |

| L      | 0.274       | 0.426              | 0.011                | 0.017 |  |  |

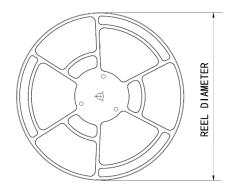

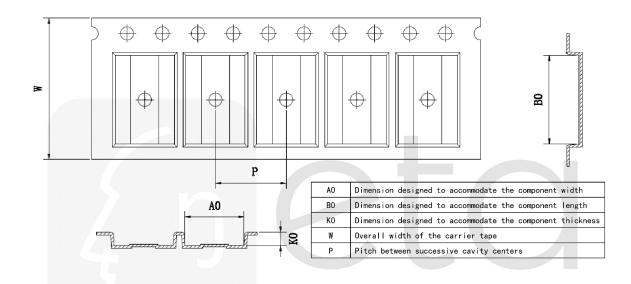

# TAPE AND REEL INFORMATION

| Device     | Package<br>Type | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|-----------------|------|------|--------------------------|--------------------------|------------|------------|------------|-----------|-----------|------------------|

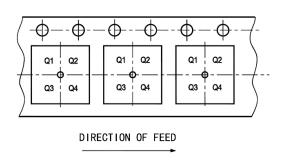

| ETA3001D2I | DFN2x2-8        | 8    | 3000 | 180                      | 9.5                      | 2.3        | 2.3        | 1.1        | 4         | 8         | Q1               |