# 4096 Bit Electrically Alterable Read Only Memory

### **FEATURES**

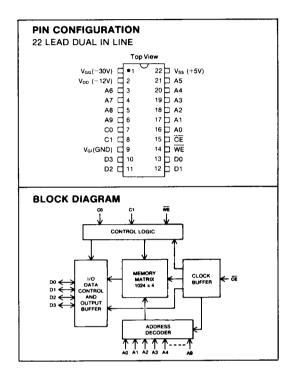

- 1024 word x 4 bit organization

- Latched address and data inputs

- Word or block alterable

- 10 year data storage for ER3400

- 1 year data storage for ER3400IR at +85°C

- and ER3400HR at +95°C

- TTL compatible with pull-up resistors on inputs

- Tri-state outputs

- Read access time: 900ns max.

- Write time: 1ms. Erase time: 10ms

- 10<sup>9</sup> Read cycles/word between refreshes

- 10<sup>7</sup> Read cycles/word for ER3400IR and ER3400HR

- Two extended temperature ranges

### DESCRIPTION

The ER3400 is a 1024 x 4 bit fully decoded Electrically Alterable Read Only Memory fabricated in General Instrument's proven MNOS technology. Address, control and data inputs are latched on board the device thus releasing these lines during Erase and Write operations. Selection of one of the four modes of operation is made by setting the appropriate binary code on control lines C0 and C1.  $C\bar{E}$  is used for chip selection and latching of address and control lines.  $W\bar{E}$  is used to sample and latch input data on D0-D3 during a Write operation.

Power sequencing protection circuitry is provided on the ER3400 to protect against the accidental alteration of data during power Up/Down. However, due to the unpredictable nature of power up and power down sequences in some systems, it is important to apply and remove the programming voltage  $V_{GG}$  only when  $V_{SS}$  and  $V_{DD}$  are within their specified limits.

For applications requiring extended temperature ranges the ER3400I, ER3400IR and ER3400HR are available.

#### **RELATED APPLICATION NOTES**

- 1217 The ER3400: an easy to use 4K EAROM

- 1218 Interfacing the ER3400 to an eight bit microcomputer

- 1220 Generating EAROM programming voltages from a 5 volt supply

- 1210 Data retention testing of the ER3400

#### PIN FUNCTIONS

| Name            | Function                                                                               |

|-----------------|----------------------------------------------------------------------------------------|

| A0-A9           | 10-Bit Word Address                                                                    |

| D0-D3           | Data input and output pins                                                             |

| CE              | Chip Enable. Chip selected when CE is pulsed to logic "0".                             |

| C0, C1          | Mode Control Inputs                                                                    |

|                 | <u>C0</u> <u>C1</u>                                                                    |

|                 | Block Erase Mode: erase operation performed on all words.                              |

|                 | 1 1 Word Erase Mode: stored data is erased at addressed location.                      |

|                 | 0 0 Read Mode: addressed data read after leading edge of $\overline{\text{CE}}$ pulse. |

|                 | 1 0 Write Mode: input data written at addressed location.                              |

| WE              | Write Enable. Input data read when WE is pulsed to logic "0".                          |

| V <sub>SS</sub> | Substrate supply. Normally at +5 volts.                                                |

| V <sub>GI</sub> | Ground Input                                                                           |

| V <sub>DD</sub> | Power Supply Input. Normally at -12 volts.                                             |

| V <sub>GG</sub> | Power Supply Input. Normally at -30 volts.                                             |

## **ELECTRICAL CHARACTERISTICS**

## Maximum Ratings\*

All inputs and outputs except  $V_{GG}$  (with respect to  $V_{SS}$ )...-20V to +0.3V Storage temperature (without data retention) ....-65° C to +150° C Soldering temperature of leads (10 seconds) .....+300° C

# Standard Condition (unless otherwise noted)

$V_{SS} = +5V \text{ to } \pm 5\%$

$V_{DD} = -12V \pm 5\%$

$V_{GG} = -30V \pm 5\%$

V<sub>GI</sub> = GND

Operating Temperature  $(T_A) = 0^{\circ}C$  to  $+70^{\circ}C$  (ER3400)

-40°C to +85°C (ER3400I/IR)

-55°C to +95°C (ER3400HR)

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

|                                            |                 | ER3400               |     |                       | ER3400IR/ER3400HR    |     |                       |       |                                                   |  |

|--------------------------------------------|-----------------|----------------------|-----|-----------------------|----------------------|-----|-----------------------|-------|---------------------------------------------------|--|

| Characteristic                             | Sym             | Min                  | Тур | Max                   | Min                  | Тур | Max                   | Unit  | Conditions                                        |  |

| DC CHARACTERISTICS                         |                 |                      |     |                       |                      |     |                       |       |                                                   |  |

| Input Logic "1"                            | V <sub>IH</sub> | V <sub>ss</sub> -1.5 | _   | V <sub>ss</sub> +0.15 | Vss -1.0             |     | V <sub>ss</sub> +0.15 | l v l |                                                   |  |

| Input Logic "0"                            | VIL             | -10                  | _   | 0.8                   | -10                  | _   | 0.6                   | Ιν̈́Ι |                                                   |  |

| Output Logic "1"                           | VoH             | Vss -1.5             | _   | ı                     | V <sub>SS</sub> -1.5 | _   | _                     | l v   | I <sub>OH</sub> = 2mA                             |  |

| Output Logic "0"                           | Vol             | ] - [                | _   | 0.4                   |                      | l — | 0.5                   | V     | $I_{OL} = 2mA$                                    |  |

| Control Input Leakage                      | ILC             | -                    | _   | 2.0                   | l                    | l — | -2.0                  | μA    | V <sub>on</sub> = V <sub>ss</sub> -15 Volts       |  |

| Data Input Leakage                         | ILD             | _                    | _   | -10.0                 | l — i                | _   | -10.0                 | μA    | $V_{IN} = V_{SS} - 15 \text{ Volts}$              |  |

| Power Supply Current                       |                 |                      |     |                       | 1                    |     |                       | ,     |                                                   |  |

| VDD Supply Current: Chip selected          | IDD             | _                    |     | -25.0                 | _                    |     | -30.0                 | mΑ    | $V_{DD} = V_{SS} - 17 \text{ Volts}$              |  |

| Chip de-selected                           | IDD             | _                    |     | -12.0                 | _ 1                  |     | -15.0                 | mΑ    | $V_{DD} = V_{SS} - 17 \text{ Volts}$              |  |

| V <sub>GG</sub> Supply Current: Write mode | IGG             |                      | _   | -4.0                  |                      | _   | -5.0                  | mΑ    | $V_{GG} = V_{SS} - 35 \text{ Volts}$              |  |

| Vss Supply Current: Chip selected          | Iss             | _                    | _   | -31.0                 | -                    | _   | -37.0                 | mΑ    | $V_{GG} = V_{SS} - 17V$ , $V_{GG} = V_{SS} - 35V$ |  |

| Chip de-selected                           | Iss             | -                    | _   | -14.5                 | _                    | _   | -18.0                 | mΑ    | $V_{GG} = V_{SS} - 17V$ , $V_{GG} = V_{SS} - 35V$ |  |

| AC CHARACTERISTICS                         |                 |                      |     |                       |                      |     |                       |       |                                                   |  |

| Input capacitance—control inputs           | Cı              | _                    | 6   | 8                     | _                    | 6   | 8                     | pf    |                                                   |  |

| Input capacitance—data inputs              | C₀              | -                    | 8   | 10                    | _                    | 8   | 10                    | pf    |                                                   |  |

|                                                         |                 | ER3400          |     | ER3400IR/HR     |      |      |                          |  |

|---------------------------------------------------------|-----------------|-----------------|-----|-----------------|------|------|--------------------------|--|

| Characteristics                                         | Sym             | Min             | Max | Min             | Max  | Unit | Conditions               |  |

| Read Cycle Time                                         | t <sub>CY</sub> | 1700            |     | 1750            | _    | ns   |                          |  |

| Address and Control to ČE                               | t <sub>D1</sub> | 100             | _   | 100             | _    | ns   | 1                        |  |

| Address and Control Hold Time                           | t <sub>D2</sub> | 250             | _   | 350             | i —  | ns   |                          |  |

| CE Rise to Data Tri-state                               | t <sub>D3</sub> | 50              | 300 | 50              | 350  | ns   |                          |  |

| CE High                                                 | t <sub>D4</sub> | 700             | _   | 750             | -    | ns   |                          |  |

| Access Time                                             | t <sub>A</sub>  | <b>–</b>        | 900 |                 | 1000 | ns   | Load = 2K + 100pf to Vss |  |

| E Pulse Width                                           | toE             | 1               | 50  | 1               | 50   | μs   |                          |  |

| CE Rise, Fall Time                                      | $t_r, t_r$      | 10              | 100 | 10              | 100  | ns   |                          |  |

| Number of Read Accesses per<br>Location Between Refresh | N <sub>RA</sub> | 10 <sup>9</sup> |     | 10 <sup>7</sup> | _    | _    |                          |  |

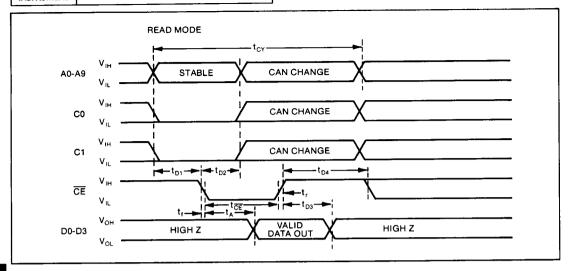

#### **READ OPERATION**

Address and control line inputs are latched on the falling edge of  $\overline{CE}$ . With control lines C0 and C1 both low a read cycle will be initiated. After the access time  $t_A$  the data read will be output on

data lines D0-D3.  $\overline{\text{CE}}$  must be held high for a minimum of 700ns between memory read cycles. To reduce power consumption the ER3400 may be operated with  $V_{GG}$  held at  $V_{SS}$  in the read mode.

|                              |                  | ER3400 |     | ER3400IR/HR |     |      |            |

|------------------------------|------------------|--------|-----|-------------|-----|------|------------|

| Characteristics              | Sym              | Min    | Max | Min         | Max | Unit | Conditions |

| dress and Control to CE      | t <sub>D11</sub> | 100    | _   | 100         | _   | ns   |            |

| ddress and Control Hold Time | t <sub>D12</sub> | 250    | l – | 250         | l _ | ns   |            |

| E Rise to Data Tri-state     | t <sub>D3</sub>  | 50     | 300 | 50          | 350 | ns   |            |

| E High (Dummy Read)          | t <sub>D5</sub>  | 1500   | _   | 1500        | _   | ns   |            |

| E Pulse Width                | t <sub>CE</sub>  | 1      | 50  | 1           | 50  | μs   |            |

| rase Time                    | t <sub>E</sub>   | 10     | 20  | 10          | 20  | ms   |            |

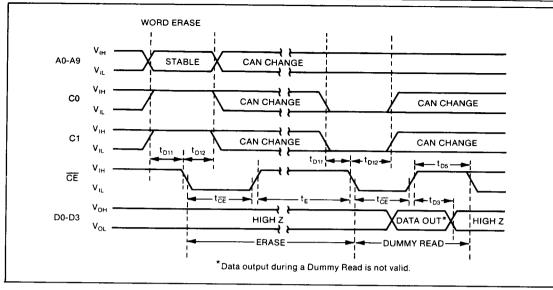

#### WORD ERASE OPERATION

An erase cycle is required prior to a write in order to precondition the memory cells to be written. A word erase operation erases only the four bits of the addressed memory location. The falling edge of CE latches the control inputs and the address of the word to be erased. The rising edge of  $\overline{\text{CE}}$  in the erase mode signals the start of the erase cycle which produces a positive shift in the threshold of the selected MNOS memory transistors. An erase operation must be terminated by a dummy read operation. The dummy read need not occur on the same location as the preceding erase, therefore, the state of the address lines A0-A9 are immaterial during the dummy read cycle. Data output during a dummy read cycle is not valid data.

### **BLOCK ERASE OPERATION**

A block erase operation erases all 4096 bits of memory to the "1" state, in all other respects the operation is identical to the word erase operation described above.

|                                  |                     | ER3400          |      | ER3400IR/HR     |     |      |                        |  |

|----------------------------------|---------------------|-----------------|------|-----------------|-----|------|------------------------|--|

| Characteristics                  | Sym Min Max Min Max |                 | Unit | Conditions      |     |      |                        |  |

| Address and Control to CE        | t <sub>D11</sub>    | 100             | _    | 100             | _   | ns   |                        |  |

| Address and Control Hold Time    | t <sub>D12</sub>    | 250             | –    | 350             | _   | ns   |                        |  |

| CE Fall to WE Fall Delay         | t <sub>D13</sub>    | 0               | –    | 0               | _   | ns   | WE rise may overlap CE |  |

| WE Rise to CE Rise Delay         | t <sub>D14</sub>    | -50             | –    | -100            | _   | ns   | rise by 50ns maximum   |  |

| Data Stable to WE                | t <sub>D15</sub>    | 0               | -    | 0               | -   | ns   |                        |  |

| WE Rise to End of Data Stable    | t <sub>D16</sub>    | 100             | l –  | 100             | –   | ns   |                        |  |

| CE Pulse Width                   | toe                 | 1               | 50   | 1               | 50  | μs   | }                      |  |

| WE Pulse Width                   | t <sub>WF</sub>     | 500             |      | 650             | -   | ns   |                        |  |

| Write Time                       | tw                  | 1               | 2    | 1               | 2   | ms   |                        |  |

| CE Rise to Data Tri-state        | t <sub>D3</sub>     | 50              | 300  | 50              | 350 | ns   |                        |  |

| CE High (Dummy Read)             | t <sub>D5</sub>     | 1500            |      | 1500            | _   | ns   |                        |  |

| Unpowered Data Storage Time      | ts                  | 10              |      | 1               | _   | YRS. | See Note 1             |  |

| Number of Reprogramming Cycles   | Nw                  | 10 <sup>3</sup> | _    | 10 <sup>3</sup> | -   | l –  | See Note 1             |  |

| Number of Read Accesses/Location | 1 "                 |                 |      |                 |     |      |                        |  |

| between Refresh                  | N <sub>RA</sub>     | 10 <sup>9</sup> | _    | 10 <sup>9</sup> | _   | _    |                        |  |

NOTE 1: Does not imply end of useful life. See "Write Operation" for further information.

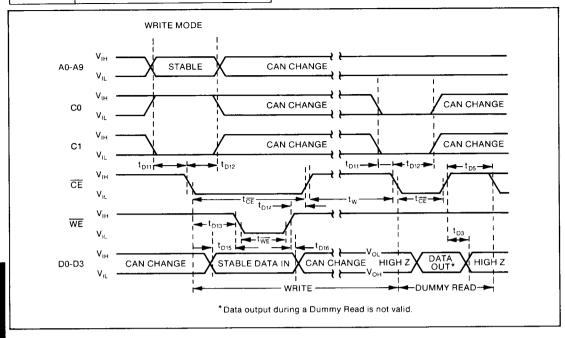

### WRITE OPERATION

Control lines C0 and C1 along with address lines A0-A9 are latched on the falling edge of  $\overline{CE}$ . Input data on D0-D3 is latched on the rising edge of  $\overline{WE}$ . WE may be tied to  $\overline{CE}$  for all operations, however, this separate latching allows the ER3400 to be used in certain systems where address and data busses are multiplexed. The writing of the selected memory transistors is initiated by the rising edge of  $\overline{CE}$ .  $\overline{CE}$  must remain high for the duration of the write time. A write operation can only be terminated by a dummy read. To avoid bus contention, the data lines must be tri-stated prior to initiating the dummy read cycle. The data output by a dummy read cycle is not valid data. The dummy read need not

occur on the same location as the previous write, therefore, address line A0-A9 may be allowed to change during the dummy read cycle.

The specification of 10 years non-volatile data retention after a minimum of  $10^3$  reprogramming cycles is merely one point on the curve of retention versus reprogramming cycles and does not imply a sudden cut-off or end of life. As the number of Erase/Write cycles per address increases, a gradual, logarithmic reduction in data retention capability occurs with 1 year of retention being a typical figure after  $10^4$  cycles.

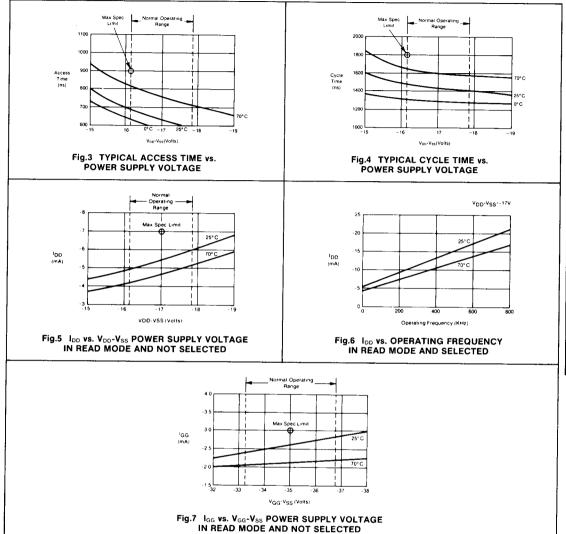

### TYPICAL CHARACTERISTIC CURVES