### **Preliminary Datasheet**

#### **FEATURES:**

- Integrated Gate Driver

- Low Propagation Delay

- Up to 7 MHz Operation

- Operates from 5 V Supply

- Dual 88-mΩ, 150-V eGaN FET

- Low Inductance 2.9 mm x 1.1 mm BGA

EPC2115 devices are supplied only in passivated die form with solder balls

Die Size: 2.9 mm x 1.1 mm

### **APPLICATIONS:**

- Wireless Power (Highly Resonant and Inductive)

- High Frequency DC-DC Conversion

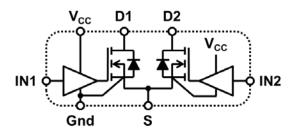

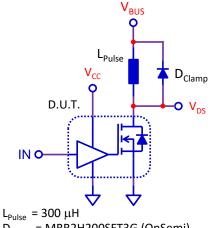

### Schematic Diagram

### **DESCRIPTION**

The EPC2115 enhancement-mode gallium-nitride (eGaN®) monolithic IC contains two monolithic 88-m $\Omega$ , 150-V GaN power transistors, each with an optimized gate driver, in a low inductance 2.9 mm by 1.1 mm BGA package.

The EPC2115 enables designers to improve efficiency, save space, and lower costs compared to silicon-based solutions. The ultra-low capacitance and zero reverse recovery of the eGaN FETs enable efficient operation in many topologies. The integrated drivers are specifically matched to the GaN device to yield optimal performance under various operating conditions that is further enhanced due to the small, low inductance footprint. Monolithic integration eliminates interconnect inductances for higher efficiency at high frequency. This is especially important for high frequency applications such as resonant wireless power.

### **ABSOLUTE MAXIMUM RATINGS**

|                 | Maximum Ratings                                                |            |    |  |  |

|-----------------|----------------------------------------------------------------|------------|----|--|--|

| $V_{DS}$        | Drain-to-Source Voltage (Continuous)                           | 150        | V  |  |  |

| I <sub>D</sub>  | Continuous (T <sub>A</sub> = 25°C, R <sub>0JA</sub> = 32 °C/W) | 5          | А  |  |  |

| ID              | Pulsed (25°C, T <sub>PULSE</sub> 300 μs)                       | 18         | Α  |  |  |

| $V_{IN}$        | Input Signal Voltage                                           | 6          | V  |  |  |

| Tı              | Operating Temperature -40 to 150                               |            | °C |  |  |

| $T_{STG}$       | Storage Temperature                                            | -40 to 150 | C  |  |  |

| V <sub>CC</sub> | Supply Voltage                                                 | 6          | V  |  |  |

### **RECOMMENDED OPERATING CONDITIONS**

|                                                             | Recommended Operating Conditions |      |     |     |      |  |

|-------------------------------------------------------------|----------------------------------|------|-----|-----|------|--|

| PARAMETER Description                                       |                                  | MIN  | TYP | MAX | UNIT |  |

| V <sub>DS</sub> Drain-Source voltage                        |                                  |      | 120 | V   |      |  |

| V <sub>CC</sub> Driver Supply voltage 4.5 5                 |                                  | 5.5  | V   |     |      |  |

| I <sub>CC</sub> External driver supply current <sup>1</sup> |                                  |      |     | 60  | mA   |  |

| V <sub>IN,Off</sub> Input signal for turn-off               |                                  |      |     | 0.5 | V    |  |

| V <sub>IN,On</sub>                                          | Input signal for turn-on         | 4.5  |     |     | V    |  |

| V <sub>IN,slew</sub>                                        | Input signal slew rate           | 0.25 |     |     | V/ns |  |

| Tı                                                          | Operating Temperature            | -40  |     | 150 | °C   |  |

<sup>&</sup>lt;sup>1</sup> For up to maximum operating frequency and to power both FETs

### THERMAL INFORMATION

| Thermal Characteristics |                                                      |     |      |  |

|-------------------------|------------------------------------------------------|-----|------|--|

|                         |                                                      | TYP | Unit |  |

| $R_{\theta JC}$         | Thermal Resistance, Junction to Case                 | 2.1 | °C/W |  |

| $R_{\theta JB}$         | Thermal Resistance, Junction to Board 21 °C          |     | °C/W |  |

| $R_{\theta JA}$         | Thermal Resistance, Junction to Ambient <sup>2</sup> | 66  | °C/W |  |

<sup>&</sup>lt;sup>2</sup> R<sub>0JA</sub> is determined with the device mounted on one square inch of copper pad, single layer 2 oz copper on FR4 board. Thermal models for EPC devices available at <a href="http://epc-co.com/epc/DesignSupport/DeviceModels.aspx">http://epc-co.com/epc/DesignSupport/DeviceModels.aspx</a>

### **ELECTRICAL CHARACTERSITCS**

| PARAMETER                                                                                                                                                         |                                                           | TEST CONDITIONS                                                                           |     | TYP | MAX | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|

| eGaN PO                                                                                                                                                           | WER TRANSISTOR                                            |                                                                                           |     |     |     |      |

| $BV_{DSS}$                                                                                                                                                        | Drain-to-Source Voltage                                   | $V_{CC}$ = 0 V, $V_{IN}$ = 0 V, $I_D$ = 125 $\mu A$                                       | 150 |     |     | V    |

| I <sub>DSS</sub>                                                                                                                                                  | Drain -Source Leakage                                     | V <sub>DS</sub> = 120 V, T <sub>J</sub> = 25 °C                                           |     | 10  | 100 | μΑ   |

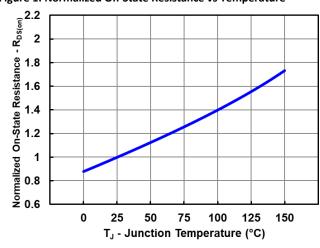

| $R_{\text{DS(ON)}}$                                                                                                                                               | Drain-Source On-Resistance                                | V <sub>CC</sub> = 5 V, T <sub>J</sub> = 25 °C                                             |     | 70  | 88  | mΩ   |

| $V_{\text{SD}}$                                                                                                                                                   | Source-Drain Forward Voltage                              | $V_{CC} = 5 \text{ V}, V_{IN} = 0 \text{ V}, I_{SD} = 0.5 \text{ A}$                      |     | 2   |     | V    |

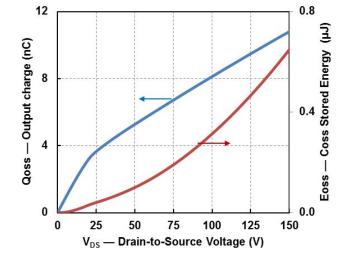

| Coss                                                                                                                                                              | Output Capacitance                                        | $V_{IN} = 0 \text{ V}, V_{CC} = 5 \text{ V}, V_{DS} = 75 \text{ V}, f = 1 \text{ MHz}$    |     | 57  |     |      |

| $C_{OSS(ER)}$                                                                                                                                                     | Energy Output Capacitance,<br>Energy Related <sup>3</sup> | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = 5 V, V <sub>DS</sub> = 0 to 75 V                 |     | 111 |     | рF   |

| $C_{OSS(TR)}$                                                                                                                                                     | Energy Output Capacitance,<br>Energy Related <sup>4</sup> |                                                                                           |     | 108 |     | ·    |

| Qoss                                                                                                                                                              | Output Charge                                             | $V_{IN} = 0 \text{ V}, V_{CC} = 5 \text{ V}, V_{DS} = 75 \text{ V}, V_{GS} = 0 \text{ V}$ |     | 6.7 |     | nC   |

| $Q_{RR}$                                                                                                                                                          | Source-Drain Recovery Charge                              |                                                                                           |     | 0   |     |      |

| C <sub>OSS(ER)</sub> is a fixed capacitance that gives the same stored energy as C <sub>OSS</sub> while V <sub>DS</sub> is rising from 0 to 50% BV <sub>DSS</sub> |                                                           |                                                                                           |     |     |     |      |

$<sup>^4</sup>$ C<sub>OSS(TR)</sub> is a fixed capacitance that gives the same charging time as C<sub>OSS</sub> while V<sub>DS</sub> is rising from 0 to 50% BV<sub>DSS</sub>

### **ELECTRICAL CHARACTERSITCS**

| PARAMETER             |                               | PARAMETER TEST CONDITIONS                                                                  |     | TYP | MAX | Unit |

|-----------------------|-------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>DRIVER S</b>       | UPPLY                         |                                                                                            |     |     |     |      |

| I <sub>VCC, ON</sub>  | Quiescent current (average)   | $V_{IN} = 5 \text{ V}$ , $V_{CC} = 5 \text{ V}$ , $V_{DS} = 0 \text{ V}$ , each FET-driver |     | 4.4 |     |      |

| I <sub>VCC, OFF</sub> | Quiescent current (average)   | $V_{IN} = 0 \text{ V}$ , $V_{CC} = 5 \text{ V}$ , $V_{DS} = 0 \text{ V}$ , each FET-driver |     | 4.4 |     | mA   |

| I <sub>VCC, OP</sub>  | Operating Current             | 50% duty cycle, V <sub>CC</sub> = 5 V, f <sub>SW</sub> = 1 MHz, each<br>FET-driver         |     | 6.5 |     |      |

| V <sub>IH</sub>       | Turn-on Input pin, logic high | V <sub>CC</sub> = 5 V, each FET-driver                                                     | 4.0 |     |     | V    |

| V <sub>IL</sub>       | Turn-off Input pin, logic low | V <sub>CC</sub> = 5 V                                                                      |     |     | 0.7 |      |

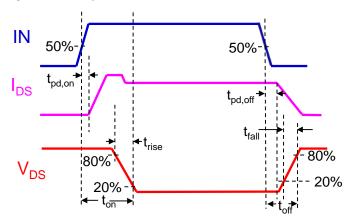

#### **SWITCHING CHARACTERISTICS**

|                     | Switching Characteristics   |                                                                   |     |      |     |      |

|---------------------|-----------------------------|-------------------------------------------------------------------|-----|------|-----|------|

|                     | PARAMETER                   | TEST CONDITIONS                                                   | MIN | TYP  | MAX | UNIT |

| DRIVER <sup>5</sup> |                             |                                                                   |     |      |     |      |

| t <sub>pd,on</sub>  | Propagation delay, turn on  |                                                                   |     | 2.6  |     | ns   |

| t <sub>rise</sub>   | Rise Time                   |                                                                   |     | 2.3  |     | ns   |

| t <sub>on</sub>     | Total turn-on time          | V - F.V. V - 120 V I - 2 A                                        |     | 6.8  |     | ns   |

| t <sub>pd,off</sub> | Propagation delay, turn off | $V_{CC} = 5 \text{ V}, V_{DS} = 120 \text{ V}, I_L = 2 \text{ A}$ |     | 10.1 |     | ns   |

| t <sub>fall</sub>   | Fall Time                   |                                                                   |     | 3.7  |     | ns   |

| t <sub>off</sub>    | Total turn-off time         |                                                                   |     | 16.4 |     | ns   |

| t <sub>MIN</sub>    | Minimum on-time             | $V_{CC} = 5 \text{ V}, V_{BUS} = 120 \text{ V}$                   |     | 9.2  |     | ns   |

| t <sub>MAX</sub>    | Maximum on-time             | $V_{CC} = 5 \text{ V, } I_{DS} = 0.5 \text{ A}$                   |     | 40   |     | ms   |

<sup>&</sup>lt;sup>5</sup>See application circuit, Figure 4 & 5

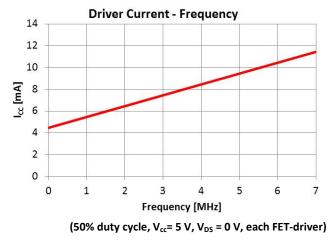

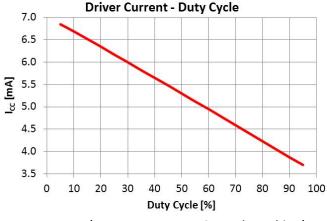

### **TYPICAL CHARACTERSITCS**

Figure 1: Normalized On-State Resistance vs Temperature

Drain-to-Source Voltage (V)

Figure 2: Capacitance (Linear Scale)

Figure 3: Output Charge and Coss Stored Energy

Figure 4: Double pulse Test Definitions

Figure 5: Double pulse Test Circuit

D<sub>Clamp</sub> = MBR2H200SFT3G (OnSemi)

Figure 6: Driver quiescent current as function of frequency

Figure 7: Driver quiescent current as function of duty cycle

(1 MHz,  $V_{CC}$ = 5 V,  $V_{DS}$  = 0 V, each FET-driver)

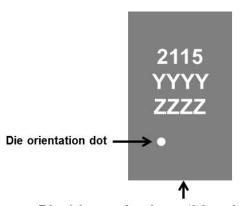

### **DIE MARKINGS**

|              | Laser Marking  |                |                |  |  |

|--------------|----------------|----------------|----------------|--|--|

| Part Number  | Part # Marking | Lot Date Code  | Lot Date Code  |  |  |

|              | Line 1         | Marking Line 2 | Marking Line 3 |  |  |

| EPC2115ENGRT | 2115           | YYYY           | ZZZZ           |  |  |

Pin 1 bump is along this edge of die

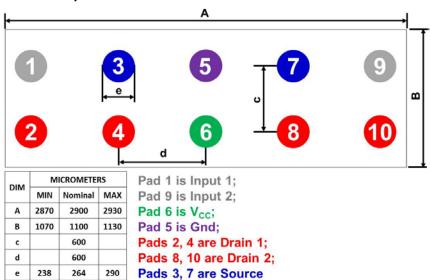

### **DIE OUTLINE**

### **Solder Bump View**

### **Side View**

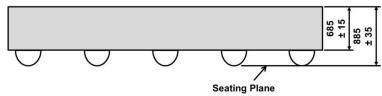

## RECOMMENDED LAND PATTERN

| DIM | MICROMETERS |

|-----|-------------|

| Α   | 2900        |

| В   | 1100        |

| С   | 600         |

| d   | 600         |

| f   | 230         |

The land pattern is solder mask defined. Copper is larger than the solder mask opening.

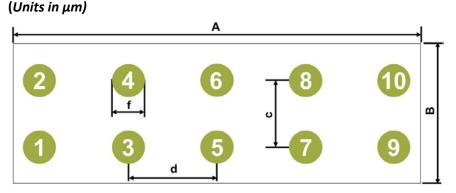

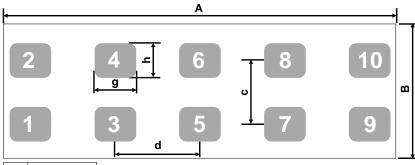

## RECOMMENDED STENCIL DESIGN

(Units in  $\mu$ m)

#### Back Side View (Bump on Bottom)

| DIM | MICROMETERS |  |

|-----|-------------|--|

| Α   | 2900        |  |

| В   | 1100        |  |

| С   | 600         |  |

| d   | 600         |  |

| g   | 300         |  |

| h   | 250         |  |

Intended for use with SAC305 Type 4 solder, reference 88.5% metals content.

Recommended stencil should be 4mil (100µm) thick, laser cut. The corner has a radius of R60.

Additional assembly resources available at http://epc-co.com/epc/DesignSupport/AssemblyBasics.aspx

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein. Preliminary specification sheet contains informaton regarding a product EPC is considering for production release. EPC does not assume any liability arising out of the application or use of any product or circuit described herin; neither does it convey any license under its patent rights, nor the rights of other.

eGaN\* is a registered trademark of Efficient Power Conversion Corporation.

EPC Patents: <a href="http://epc-co.com/epc/AboutEPC/Patents.aspx">http://epc-co.com/epc/AboutEPC/Patents.aspx</a>

March, 2018