# <section-header><section-header><section-header><section-header><section-header><section-header> <section-header><text><text><text>

Digital Media Processor with Multiple A/V Codec Support

#### **Copyright Information**

© 2005 by Sigma Designs Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Sigma Designs Inc. The information in this document is subject to change without notice. Sigma Designs, REALmagic and the REALmagic logo are either registered trademarks or trademarks of Sigma Designs Inc. in the United States and/or other countries. Manufactured under license from Dolby Laboratories and Macrovision. Dolby, Pro Logic, and the double-D symbol are trademarks of Dolby Laboratories. All other trademarks or registered trademarks are the properties of their respective owners.

Sigma Designs products are sold by description only. Sigma Designs reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the datasheet is current before placing orders. Information furnished by Sigma Designs is believed to be accurate and reliable. However, no responsibility is assumed by Sigma Designs or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Sigma Designs or its subsidiaries.

#### Disclaimer

Sigma Designs Inc. makes no warranty, express, statutory, implied or by description regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Sigma Designs Inc. makes no warranty of merchantability or fitness for any purpose.

Sigma Designs Inc. shall not be responsible for any errors that may appear in this document. Sigma Designs Inc. makes no commitment to update or keep current the information contained in this document.

#### Confidentiality

This document contains confidential information, trade secrets or both that are the property of Sigma Designs Inc. It is to be treated as confidential under the Non Disclosure Agreement (NDA), which has been signed by the obtainer. Reproduction or transmission in any manner to others in whole or in part is prohibited without prior written permission from Sigma Designs Inc.

#### **Life Support Policy**

The product(s) described in this document is not intended for use as critical component(s) in life support devices or systems without prior written permission from Sigma Designs Inc.

- Life support devices or systems are devices or systems which, (a) are intended as surgical implant(s) into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to

cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### Trademarks

EM8622L is a trademark of Sigma Designs Inc. All other trademarks belong to their respective companies.

#### Address

Sigma Designs Inc. 1221 California Circle Milpitas CA USA - 95035 Tel: 408.262.9003 Fax: 408.262.9740 www.sigmadesigns.com

Document #: EM8622L-DS-A-03

# **Table of Contents**

|   | Conventions |                                                                | 1           |

|---|-------------|----------------------------------------------------------------|-------------|

|   |             | Acronyms and Abbreviations                                     | 1           |

|   |             | Units of Measurement                                           | . 4         |

|   |             | General Conventions                                            | . 5         |

|   |             | Datasheet Definitions                                          |             |

| 1 | Introductio | n                                                              | 7           |

|   |             | Block Diagram of EM8622L                                       | 7           |

|   |             | Main Features of EM8622L                                       |             |

|   |             | Main Components of EM8622L                                     | 11          |

|   |             | Application Example: Networked DVD Player                      | 16          |

|   |             | Application Example: Digital Media Adapter or IPTV Set-top Box | 17          |

| 2 | Host CPU B  | Block                                                          | .19         |

|   |             | Block Diagram of Host CPU Block                                |             |

|   |             | Introduction                                                   | 20          |

|   |             | Central Processor Unit (CPU)                                   | 21          |

|   |             | Introduction                                                   | 21          |

|   |             | Features                                                       | . Z I<br>21 |

|   |             | Block Diagram                                                  |             |

|   |             | Functional Description                                         |             |

|   |             | Local Memory                                                   | 32          |

|   |             | Introduction                                                   |             |

|   |             | Features                                                       |             |

|   | G           | Functional Description                                         |             |

|   |             | Register Map                                                   |             |

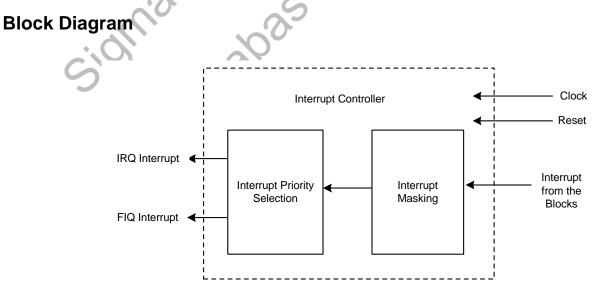

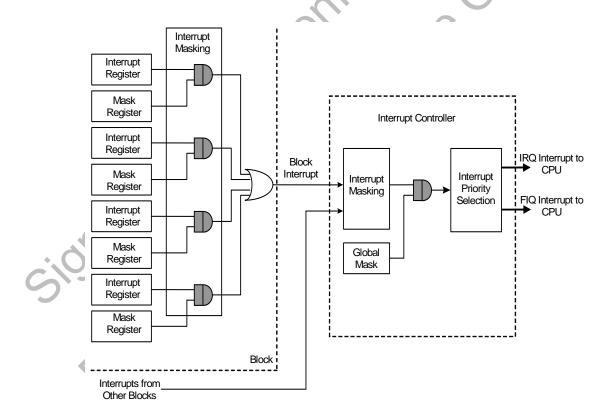

|   |             | Interrupt Controller                                           |             |

|   |             |                                                                |             |

|   |             | Features                                                       |             |

|   |             | Block Diagram                                                  |             |

|   |             | Functional Description                                         |             |

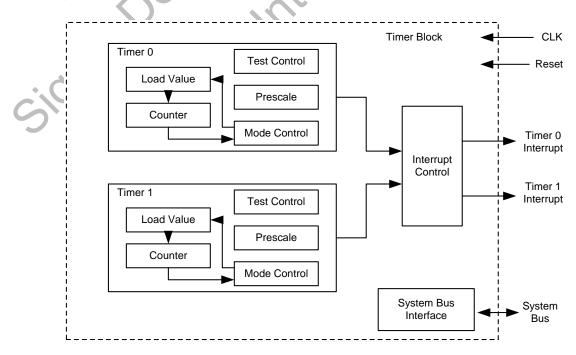

|   |             | Timers                                                         |             |

|   |             |                                                                |             |

|   |             | Features                                                       |             |

|   |             | Block Diagram                                                  |             |

|   |             | Functional Description                                         |             |

|   |             |                                                                |             |

| 3 D | Introduction<br>Features<br>Block Diagram<br>Functional Description<br>Register Map<br>Pin Description<br>Electrical Characteristics<br>Timing Diagrams<br><b>RAM Controller</b><br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description<br>Pin Description | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              |                       |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------|-----------------------|

| 3 D | Block Diagram<br>Functional Description<br>Register Map<br>Pin Description<br>Electrical Characteristics<br>Timing Diagrams<br>RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              |                       |

| 3 D | Functional Description<br>Register Map<br>Pin Description<br>Electrical Characteristics<br>Timing Diagrams<br>RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                        | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              |                       |

| 3 D | Register Map<br>Pin Description<br>Electrical Characteristics<br>Timing Diagrams<br>RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              |                       |

| 3 D | Pin Description<br>Electrical Characteristics<br>Timing Diagrams<br>RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                                  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              |                       |

| 3 D | Electrical Characteristics<br>Timing Diagrams<br>RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                                                     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |              |                       |

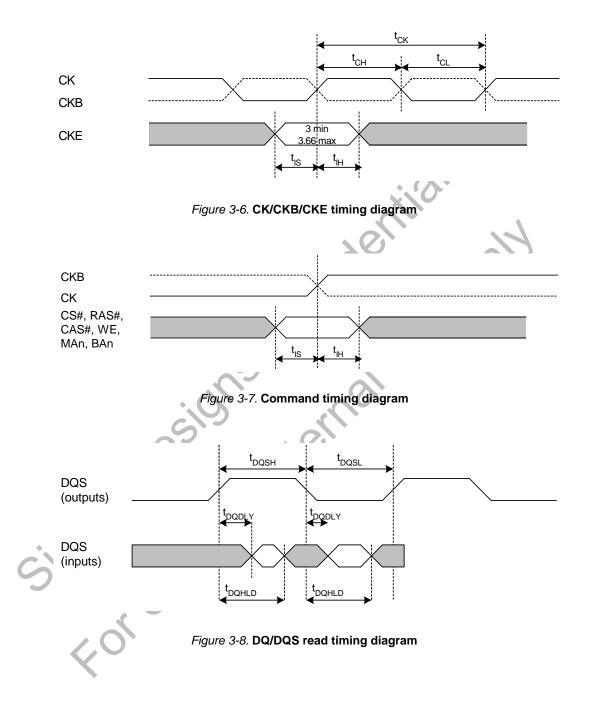

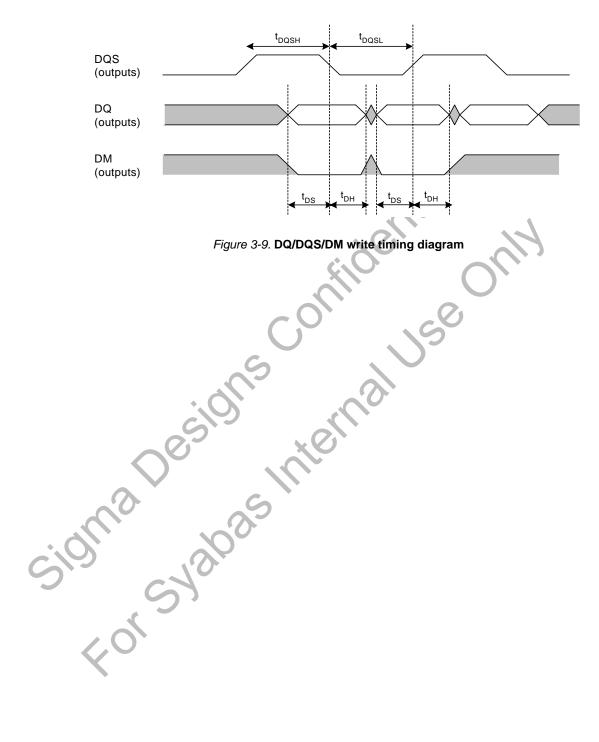

| 3 D | Timing Diagrams<br>RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                                                                                   |                                         | X            | 53<br><b>55</b><br>55 |

| 3 D | RAM Controller<br>Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                                                                                                      | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | <u>io</u>    | <b>55</b>             |

| 3 D | Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                                                                                                                        |                                         | Ň            | 55                    |

|     | Block Diagram of DRAM Controller<br>Introduction<br>Features<br>Functional Description                                                                                                                                                                                                        |                                         | Ň            | 55                    |

|     | Introduction<br>Features<br>Functional Description                                                                                                                                                                                                                                            | X                                       | $\mathbf{O}$ |                       |

|     | Features                                                                                                                                                                                                                                                                                      |                                         |              |                       |

|     | Functional Description                                                                                                                                                                                                                                                                        |                                         |              |                       |

|     | Rin Description                                                                                                                                                                                                                                                                               |                                         |              |                       |

|     |                                                                                                                                                                                                                                                                                               |                                         | $\square$    |                       |

|     | Electrical Characteristics                                                                                                                                                                                                                                                                    |                                         |              | 47                    |

|     | Timing Diagrams                                                                                                                                                                                                                                                                               |                                         | 0,           |                       |

|     | ystem Block                                                                                                                                                                                                                                                                                   |                                         | 5            |                       |

| 4 5 | Block Diagram of System Block                                                                                                                                                                                                                                                                 |                                         |              |                       |

|     | Block Diagram of System Block                                                                                                                                                                                                                                                                 |                                         |              |                       |

|     | Introduction                                                                                                                                                                                                                                                                                  |                                         |              |                       |

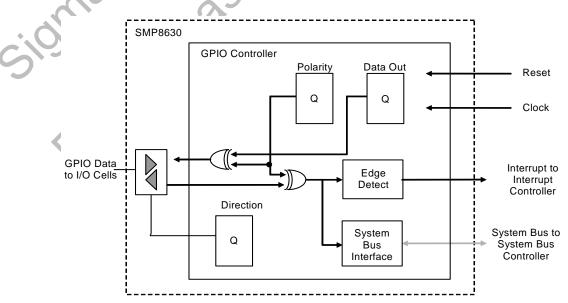

|     | GPIO Block                                                                                                                                                                                                                                                                                    |                                         |              | 73                    |

|     | General Purpose I/O (GPIO)                                                                                                                                                                                                                                                                    |                                         |              |                       |

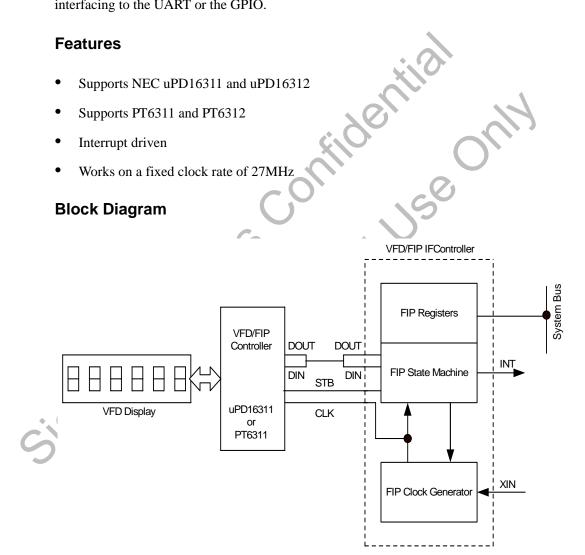

|     | Front Panel Controller Interface (FIP) .                                                                                                                                                                                                                                                      |                                         |              | 78                    |

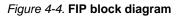

|     | Infrared Decoder                                                                                                                                                                                                                                                                              |                                         |              | 82                    |

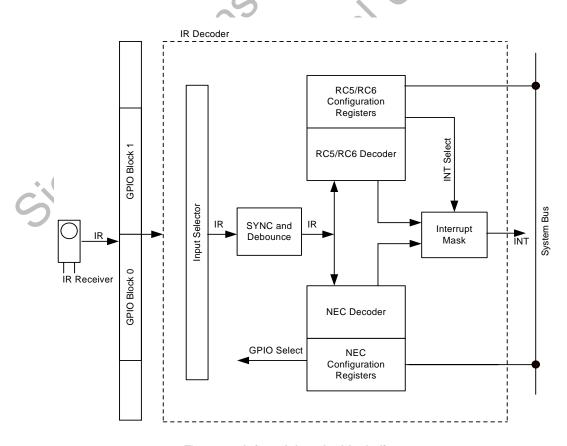

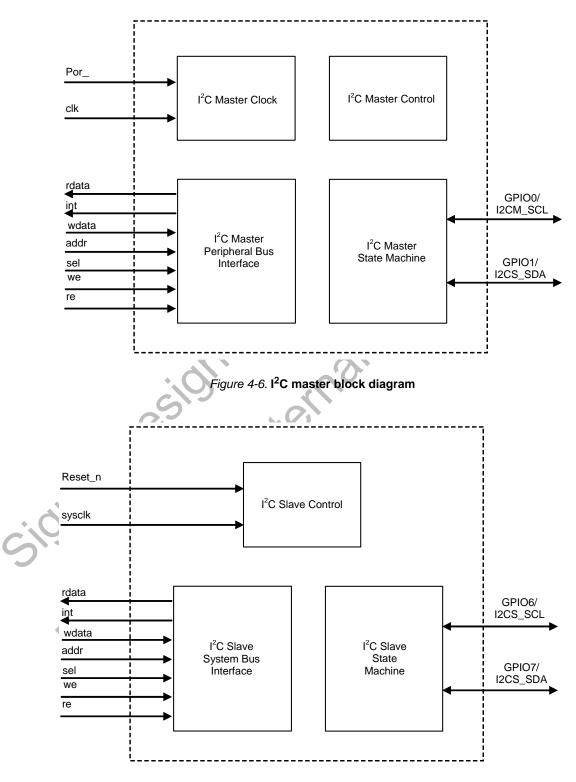

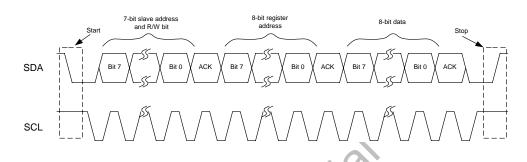

|     | Inter Integrated Circuits (I2C)                                                                                                                                                                                                                                                               |                                         |              |                       |

|     | Introduction                                                                                                                                                                                                                                                                                  |                                         |              |                       |

|     | Features                                                                                                                                                                                                                                                                                      |                                         |              | 88                    |

|     | Block Diagram                                                                                                                                                                                                                                                                                 |                                         |              | 89                    |

|     | Functional Description                                                                                                                                                                                                                                                                        |                                         |              |                       |

|     | Register Maps                                                                                                                                                                                                                                                                                 |                                         |              |                       |

|     | Pin Description                                                                                                                                                                                                                                                                               |                                         |              |                       |

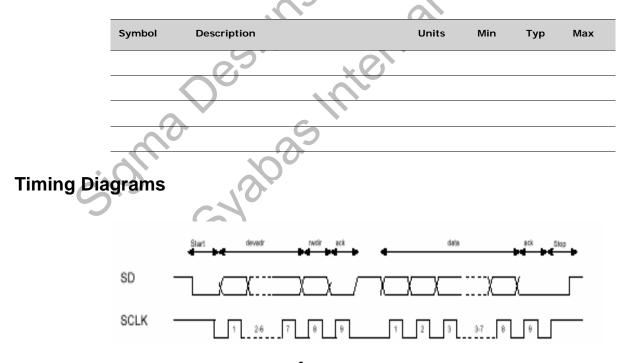

|     | Electrical Characteristics                                                                                                                                                                                                                                                                    |                                         |              | 96                    |

|     | Timing Diagrams                                                                                                                                                                                                                                                                               |                                         |              |                       |

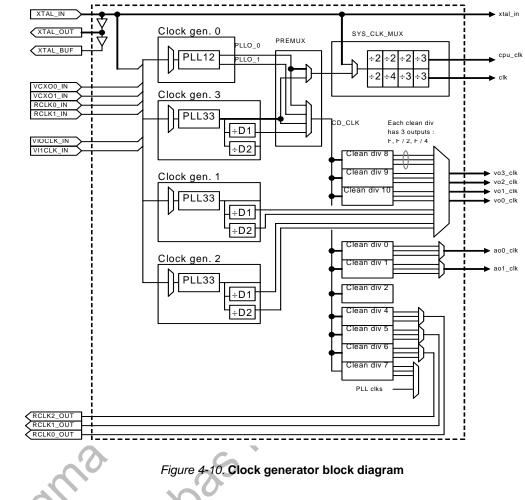

|     | Clock Generator                                                                                                                                                                                                                                                                               |                                         |              | 97                    |

|     | Introduction                                                                                                                                                                                                                                                                                  |                                         |              |                       |

|     | Features                                                                                                                                                                                                                                                                                      |                                         |              |                       |

|     | Block Diagram                                                                                                                                                                                                                                                                                 |                                         |              | 98                    |

|     | Functional Description                                                                                                                                                                                                                                                                        |                                         |              |                       |

|     | Register Map                                                                                                                                                                                                                                                                                  |                                         |              |                       |

|     |                                                                                                                                                                                                                                                                                               |                                         |              |                       |

|     | Pin Description                                                                                                                                                                                                                                                                               |                                         |              | 101                   |

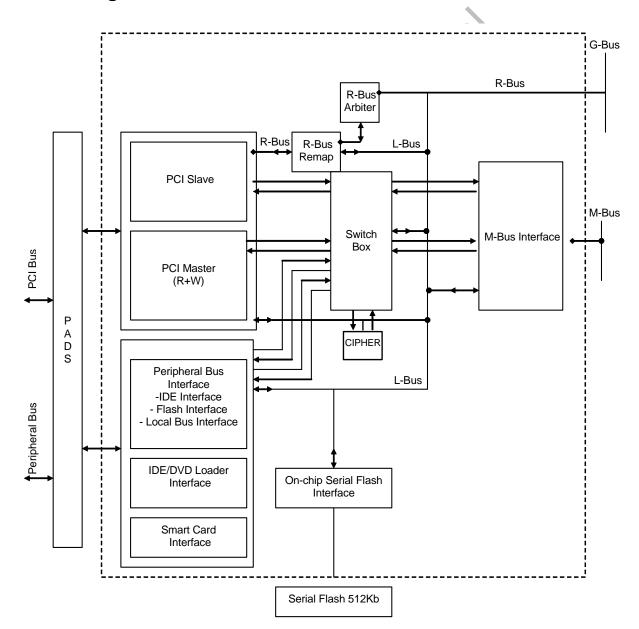

5

| Host Inter | face                                 |   | 103 |

|------------|--------------------------------------|---|-----|

|            | Block Diagram of Host Interface      |   |     |

|            | Introduction                         |   |     |

|            | PCI Master/Slave/Host Interface      |   |     |

|            | Introduction                         |   |     |

|            | Features                             |   |     |

|            | Functional Description               |   |     |

|            | Register Map                         |   |     |

|            | Pin Descriptions                     |   | 115 |

|            | Electrical Characteristics           |   |     |

|            | Timing Diagrams                      |   |     |

|            | Peripheral Bus Interface (PBI)       |   |     |

|            | Introduction                         |   |     |

|            | Features<br>Block Diagram            |   |     |

|            | Block Diagram                        |   |     |

|            | Functional Description               |   |     |

|            | Register Map                         |   |     |

|            | Pin Description                      | ) |     |

|            | Electrical Characteristics           |   | 133 |

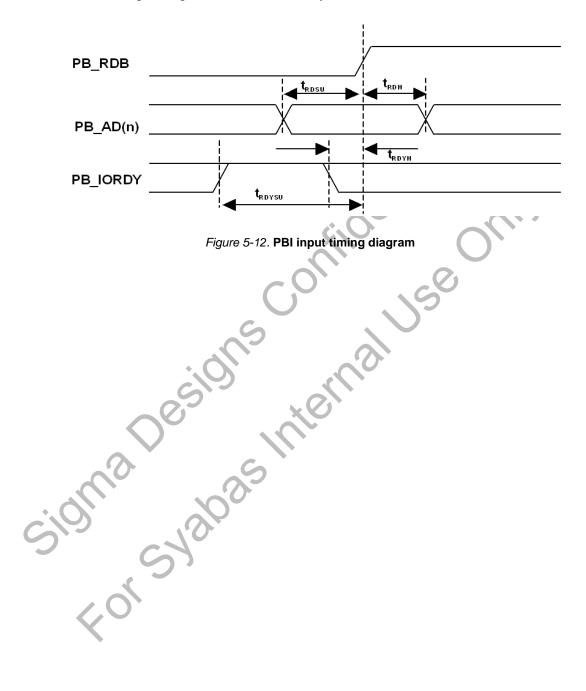

|            | Timing Diagrams                      |   | 133 |

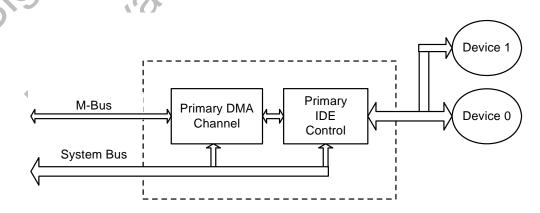

|            | IDE/DVD Loader Interface             |   |     |

|            | Introduction                         |   | 135 |

|            | Features<br>Block Diagram            |   | 135 |

|            | Block Diagram                        |   | 135 |

|            | Functional Description               |   |     |

|            | Register Maps                        |   |     |

|            | Pin Description                      |   |     |

|            | Electrical Characteristics           |   |     |

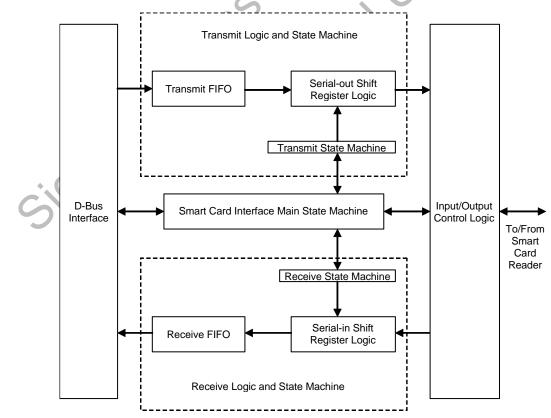

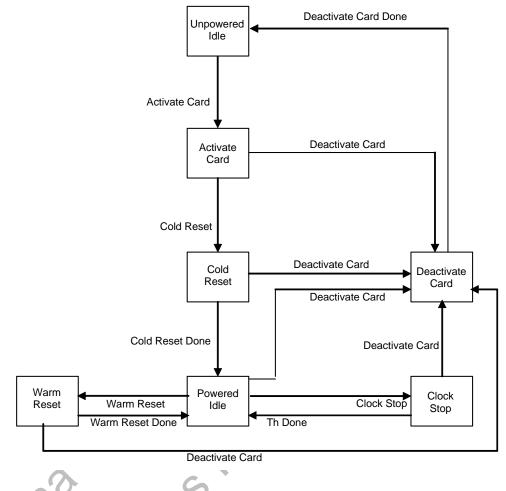

| •.(        | Smart Card Interface                 |   | 142 |

| C          | Introduction                         |   | 142 |

| 9          | Features                             |   |     |

|            | Block Diagram                        |   | 142 |

|            | Functional Description               |   | 143 |

|            | Register Map                         |   |     |

|            | Pin Description                      |   |     |

|            | Host Cipher                          |   |     |

|            | Serial Flash Interface               |   |     |

|            | Pin Description                      |   | 150 |

|            | Electrical Characteristics           |   | 150 |

| Video Dec  | oder Subsystem                       |   |     |

|            | Block Diagram of Video Decoder Subsy |   |     |

|            | Introduction                         |   |     |

|            | Features                             |   |     |

6

| 7  | Video Processing Subsystem                                              | 157   |

|----|-------------------------------------------------------------------------|-------|

|    | Block Diagram of Video Processing Subsystem                             | 157   |

|    | Introduction                                                            | 158   |

|    | Features                                                                | 159   |

|    | Functional Description                                                  | 160   |

|    | Register Maps                                                           | 185   |

|    | Pin Description                                                         | 196   |

|    | Electrical Characteristics                                              | 200   |

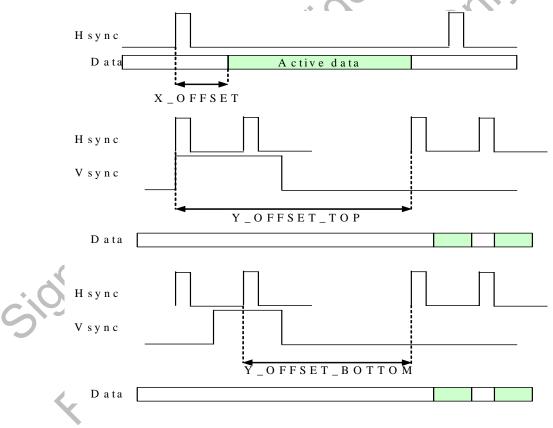

|    | Timing Diagrams                                                         | 201   |

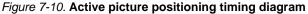

| 8  | Audio Processing Subsystem                                              | 205   |

|    | Block Diagram of Audio Processing Subsystem                             | 205   |

|    | Introduction                                                            | . 206 |

|    | Features                                                                | 206   |

|    | Functional Description                                                  | 207   |

|    | Register Maps                                                           | 217   |

|    | Pin Description                                                         | 219   |

|    | Electrical Characteristics                                              |       |

|    | Timing Diagram                                                          |       |

| 9  | Transport Demultiplexer                                                 | 223   |

|    | Block Diagram of Transport Demultiplexer                                | 223   |

|    | Introduction                                                            | 224   |

|    | Features                                                                | 226   |

|    | Functional Description                                                  | 228   |

|    | Pin Description                                                         | 245   |

|    | Functional Description<br>Pin Description<br>Electrical Characteristics | 246   |

| 10 | Pin Information                                                         |       |

|    | Pin Layout                                                              | 247   |

|    | Pin Listing by Ball Id                                                  | 248   |

|    | Pin Listing by Pin Name                                                 | 254   |

|    | Miscellaneous Pins                                                      | 260   |

| 11 | System Specifications                                                   | 261   |

|    | Electrical Specifications                                               |       |

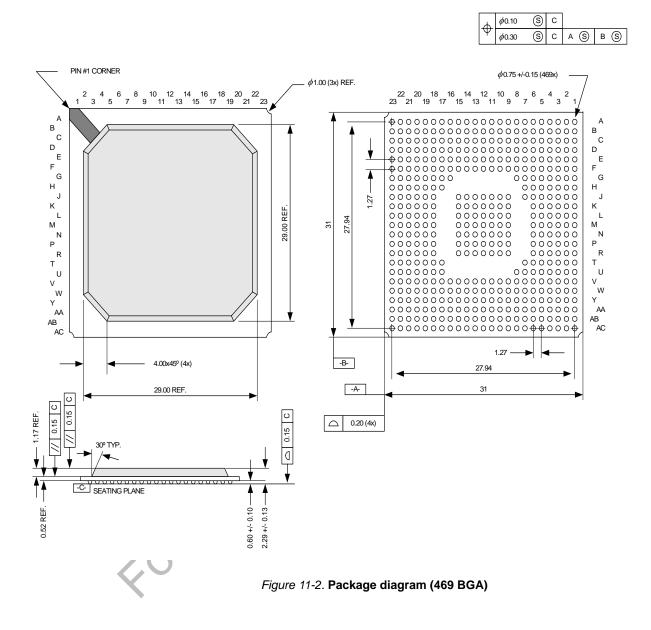

|    | Mechanical Specifications                                               | 269   |

|    | Thermal Specifications                                                  | 270   |

| 12 | Appendix                                                                | 271   |

|    | DDR SDRAM Layout Considerations                                         |       |

| I  | List of Figures                                                         |       |

|    | -                                                                       |       |

| L  | List of Tables                                                          |       |

## Conventions

This section presents the acronyms, abbreviations, units of measurement and other conventions used in this datasheet.

#### **Acronyms and Abbreviations**

The acronyms and abbreviations used in this datasheet are listed alphabetically in the table below:

#### Table 0-1. Acronyms and abbreviations

|   | Acronym/Abbreviation | Definition                                          |

|---|----------------------|-----------------------------------------------------|

|   | 2D/3D                | 2 Dimensional/3 Dimensional                         |

|   | AC                   | Alternating Current                                 |

|   | ADC                  | Analog-to-Digital Converter                         |

|   | ATA                  | AT Attachment                                       |

|   | AV or A/V            | Audio Visual                                        |

|   | BGA                  | Ball Grid Array                                     |

|   | ВРР                  | Bits per Pixel                                      |

| Ċ | CMOS                 | Complementary Metal Oxide Semiconductor             |

| 2 | CODEC                | Coder/Decoder                                       |

|   | CPU                  | Central Processing Unit                             |

|   | CSS                  | Cascading Style Sheets or Content Scrambling System |

| • | D/A                  | Digital-to-Analog                                   |

|   | DAA                  | Data Access Arrangement                             |

|   | DAC                  | Digital-to-analog Converter                         |

|   | DC                   | Direct Current                                      |

|   | DDR SDRAM            | Double Data Rate Synchronous DRAM                   |

|   | DMA                  | Direct Memory Access                                |

|   | DRAM                 | Dynamic Random-access Memory                        |

|   | DSL                  | Digital Subscriber Line                             |

|   |                      |                                                     |

|   | Acronym/Abbreviation | Definition                                     |

|---|----------------------|------------------------------------------------|

|   | DSP                  | Digital Signal Processor                       |

| _ | DVD                  | Digital Versatile Disc or Digital Video Disc   |

| _ | DVI                  | Digital Visual Interface                       |

| _ | EJTAG                | Enhanced Joint Test Action Group               |

| _ | EIA                  | Electronic Industries Alliance                 |

|   | FCS                  | Frame Check Sequence                           |

|   | FIFO                 | First In/First Out                             |

| _ | GPIO                 | General Purpose Input/Output                   |

|   | HDMI                 | High-Definition Multimedia Interface           |

| _ | HDTV                 | High-Definition Television                     |

|   |                      | Input                                          |

|   | 1/0                  | Input/Output                                   |

| _ | I <sup>2</sup> C     | Inter Integrated Circuit                       |

| - | IDE O                | Integrated Drive Electronics                   |

| _ | IEC                  | International Electrotechnical Commission      |

|   | IPTV                 | Internet Protocol TV                           |

|   | IR                   | Infrared                                       |

| _ | IRQ                  | Interrupt Request Line                         |

|   | ISO                  | International Organization for Standardization |

|   | JPEG                 | Joint Photographic Experts Group               |

|   | LCD                  | Liquid Crystal Display                         |

| _ | LSB                  | Least Significant Bit/Byte                     |

|   | MIPS.                | Millions of Instructions per Second            |

|   | ММU                  | Memory Management Unit                         |

| _ | MPEG                 | Moving Picture Experts Group                   |

| _ | MSB                  | Most Significant Bit/Byte                      |

| _ | 0                    | Output                                         |

| _ | OSD                  | On Screen Display                              |

| _ | P/U                  | Pull-up Resistor                               |

| _ | PCB                  | Printed Circuit Board                          |

#### Table 0-1. Acronyms and abbreviations (Continued)

#### Table 0-1. Acronyms and abbreviations (Continued)

|          | Acronym/Abbreviation | Definition                                                                            |

|----------|----------------------|---------------------------------------------------------------------------------------|

|          | PCI                  | Peripheral Component Interconnect                                                     |

|          | PID                  | Program Id                                                                            |

|          | PIP                  | Picture In Picture                                                                    |

|          | PKI                  | Public Key Infrastructure                                                             |

|          | PLL                  | Phase Locked Loop                                                                     |

|          | PVR                  | Personal Video Recorder                                                               |

|          | RAM                  | Random Access Memory                                                                  |

|          | RGB                  | Red Green Blue                                                                        |

|          | RISC                 | Reduced Instruction Set Computer                                                      |

|          | ROM                  | Read Only Memory                                                                      |

|          | RTC                  | Real-time Clock                                                                       |

|          | S/PDIF               | Sony/Philips Digital Interface                                                        |

|          | SDTV                 | Standard Definition Television                                                        |

|          | SPI                  | Synchronous Parallel Interface                                                        |

|          | SRAM                 | Static Random Access Memory                                                           |

|          | SSI                  | Synchronous Serial Interface                                                          |

|          | SSI                  | Server-side Include or Single-system Image                                            |

|          | трмх                 | Transport Demultiplexer                                                               |

| ~        | ТЪВ                  | Translation Look-aside Buffer                                                         |

|          | UART                 | Universal Asynchronous Receiver Transmitter                                           |

| <b>D</b> | USB                  | Universal Serial Bus                                                                  |

|          | VOD                  | Video On Demand                                                                       |

|          | YCbCr                | Y is brightness (luma), Cb is blue minus luma (B-Y) and<br>Cr is red minus luma (R-Y) |

#### **Units of Measurement**

The units of measurement used in this datasheet are listed alphabetically in the table below:

|   | Symbol | Unit of measurement                  |

|---|--------|--------------------------------------|

| - | μΑ     | microampere                          |

| - | μF     | microfarad                           |

| _ | μs     | microsecond (1,000 nanoseconds)      |

| - | °C     | degree Celsius                       |

| - | GB     | gigabyte                             |

| - | bpp    | Bits Per Pixel                       |

| - | Hz     | Hertz (Cycle Per Second)             |

| - | kohm   | kiloohm                              |

| - | Kb     | kilobit                              |

| - | КВ     | kilobyte (1,024 Bytes)               |

| - | Kbps   | kilobit per second                   |

| - | KBps   | kilobyte per second                  |

| - | KHz    | kilohertz                            |

| - | mA     | milliampere                          |

|   | Mbps   | megabit per second                   |

| 5 | MBps   | megabyte (1,048,576 bits) per second |

| - | Mb     | megabit                              |

| - | МВ     | megabyte (1,048,576 bytes)           |

| - | MHz    | megahertz (1,000 kilohertz)          |

| - | ms     | millisecond (1,000 micro seconds)    |

| - | ns     | nanosecond                           |

| - | V      | volt                                 |

| - | W      | watt                                 |

#### Table 0-2. Units of measurement

#### **General Conventions**

#### Numbers and Number Bases

- Binary numbers are enclosed in single quotation marks when in text, e.g., '11' designates a binary number.

- Binary numbers are written with a lower case 'b' suffix. e.g., 16b.

- Binary numbers larger than four digits are written with a space dividing each group of four digits, as in 1011 0101 1010b.

- All other numbers are decimal

#### **Naming Conventions**

- The register acronyms appear in capital letters such as SDIOVH or SDIN\_EGD\_HDG

- Register bits are listed in square brackets MSB-to-LSB separated by a colon mark, e.g., SDHE[3:0].

- TBD indicated that the values are 'to be determined', NA indicates 'not available' and NC indicates that a pin is 'no connect'.

#### **Datasheet Definitions**

The following table gives the general definitions of the status of the datasheet:

Table 0-3. Datasheet status definitions

# Introduction

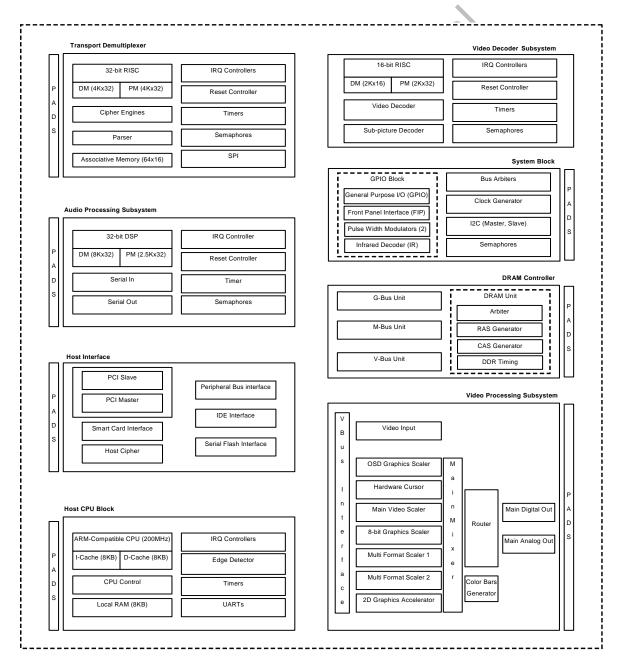

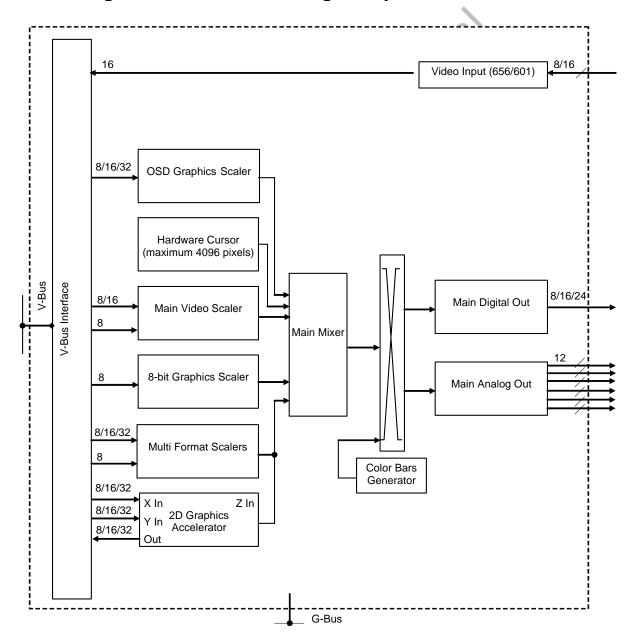

#### Block Diagram of EM8622L

1

Figure 1-1. EM8622L block diagram

#### Main Features of EM8622L

- Host CPU

- Embedded ARM-compatible processor (200MHz) for operating system, middleware and applications designed for use with applications that require ARM (version 4T) instructions

- 16K program and 16K data memory

- IO standards

- 32-bit PCI v2.1 (33 or 66MHz) bus master/slave/host interface with optional AES, 3 DES or DES security

- Flexible peripheral bus supports IDE (ATA/ATAPI-4), CompactFlash, local bus and parallel flash with optional AES, 3 DES or DES security

- IDE (ATA/ATAPI-4) or DVD loader (supports Samsung, Sanyo, Sony and Thomson DVD loaders)

- Front panel controller interface supports NEC uPD16311, NEC uPD16312, PTC PT6311 and PTC PT6312 front panel controllers

- Smart card interface (ISO 7816)

- I<sup>2</sup>C master/slave interfaces

- Single 8-bit parallel SPI transport stream interface, or dual serial transport stream interfaces

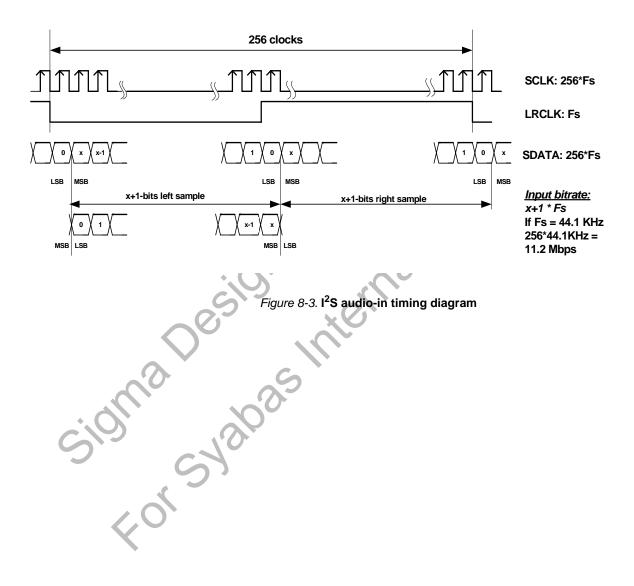

- I<sup>2</sup>S interface up to 20Mbps

- Two UARTs

- Local bus interface supporting Ethernet chipsets, MPEG encoders and other external devices

- Up to 48 general purpose I/O pins

- Video decoding standards

- MPEG-1, MPEG-2 MP@HL up to 1920x1080i30 or 1920x1080p30 resolution

- MPEG-4. 2 ASP@L5. Rectangular shape video decoding up to 1280x720p30 resolution, support for B Pictures, data partitioning and error resiliency.

- WMV9/VC-1 MP@HL up to 1920x1080p30 resolution, progressive sources only

- VC-1 AP@L3 up to 1920x1080p30 resolution

- MPEG-4.10 (H.264) BP@L3 up to 720x480p30 or 720x576p25 resolution, including FMO and ASO

- MPEG-4.10 (H.264) MP@L4.1 and HP@L4.1 up to 1920x1080i30 or 1920x1080p30 resolution

- Baseline JPEG up to 1920x1080 resolution

- DVD-Video and Superbit DVD

- Error concealment, deblocking filter

- Elementary video stream bit rate

- \* MPEG-2 SDTV (HDTV): 15 (30) Mbps maximum

- \* MPEG-4.2 SDTV (HDTV): 15 (30) Mbps maximum

- \* MPEG-4.10 (H.264) SDTV (HDTV): 15 (30) Mbps maximum

- WMV9/VC-1 SDTV (HDTV): 15 (30) Mbps maximum

- Video interfaces

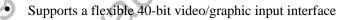

- Flexible video and graphics input interfaces support multiple video sources, DVI and HDMI receivers, 3D graphics chips

- 8-bit video input interface

- 32-bit graphics input interface

- Video outputs

- NTSC/PAL composite analog output with optional Macrovision v7.1.L1 protection (54MHz, 12-bit DAC)

- NTSC/PAL s-video analog output with optional Macrovision v7.1.L1 protection (54MHz, 12-bit DACs)

- \* Analog YPbPr / RGB with optional Macrovision v7.1.L1 and v1.2 protection in 480i, 576i, 480p and 576p YPbPr output modes (12-bit DACs, interlaced or progressive, SDTV or HDTV resolution)

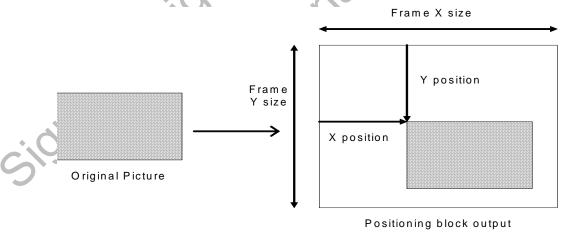

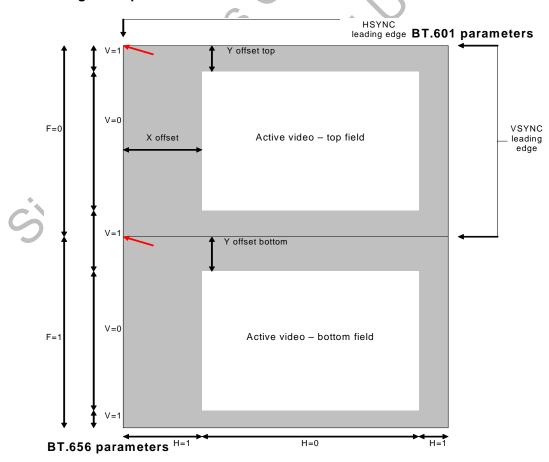

- \* 150MHz YCbCr/RGB digital video output interface; 8-bit 4:2:2 YCbCr data, 16-bit 4:2:2 YCbCr data, 24-bit 4:4:4 YCbCr data, 24-bit RGB data (888), BT.601, BT.656, or VIP 2.0, 'video valid' output signal, master or slave timing

- Video processing

- Brightness, color and contrast controls for each output port

- Hardware cursor (4096 pixels, 4-bpp, up to 255 pixels horizontally and vertically)

- 2D graphics accelerator (up to 100 M samples per second operation for most operations)

- Line, Rectangle, Ellipse and Circle: generate a single-color line, rectangle, ellipse or circle with optional gradient fill

- \* Blend: alpha blend one rectangular region onto another

- \* Move: move a rectangular region to another location

- \* Replace: modified version of Move

- Raster Operations: standard 256 Boolean operations

- \* OpenType font rendering acceleration

- 32-bit OSD with flicker filtering and scaling

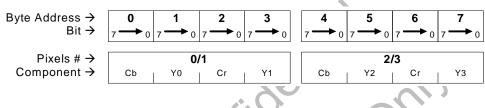

- Optional deinterlacing of interlaced sources

- Arbitrary scaling of video and OSD up to 1920x1080 pixels

- Alpha mixing of video, graphics, cursor and OSD

- On screen display

- \* High resolution, true-color OSD support

- \* 2, 4, 7, and 8-bpp from 24-bit palette

- \* Programmable OSD scaler

- \* Programmable flicker filter for interfaced output modes

- \* Alpha blending over video (8-bit)

0

- Audio interfaces

- Audio DSP supports a wide range of audio codecs

- Audio inputs

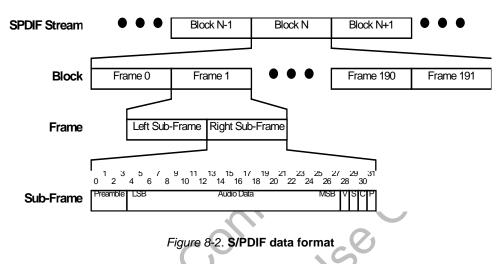

- \* I<sup>2</sup>S or S/PDIF serial digital audio input

- Audio outputs

- \* S/PDIF (IEC 60958) serial digital audio output for 2.0 linear PCM and compressed Dolby Digital, DTS, WMA Pro and MPEG

- \* Three I<sup>2</sup>S serial digital outputs support 5.1-channel audio

- Audio decoding standards

- 16-bit linear PCM with HDCD support

- MPEG-1 and MPEG-2 Layers I, II and III (MP3) 2.

- MPEG-2 and MPEG-4 AAC-LC 2.0

- MPEG-2 and MPEG-4 HE-AAC 2.0

- MPEG-4 BSAC 2.0

- Dolby Digital 5.1

- DTS 5.1

- WMA9@L3 2.0, WMA9 Pro@M2 5.1

- Transport formats

- Transport input interfaces

- \* One 8-bit SPI or two SSI, with polarity control of data valid signal

- \* PCI, IDE, Local Bus

- Transport demux supports 2 dedicated PIDs (audio, video), 16 general PIDs, 64 PIDs from associative memory

- Transport input bit rate: 40Mbps maximum (aggregate)

- Media formats

- DVD-Video, Superbit DVD, SVCD (IEC 62107-2000), VCD 1.x and 2.0

- DVD-R, DVD-RW, DVD+R, DVD+RW (conditional)

- Audio CD (with optional HDCD), CD-R, CD-RW, CompactFlash

- \* WMA, JPEG, MP3 and MPEG-41 AVI files using ISO 9660 or HighMAT<sup>™</sup> format

- Picture CD (JPEG files using ISO 9660 format)

- Navigation software, HighMAT<sup>TM</sup> support

- Streaming formats

- ISMA (Internet Streaming Media Alliance) MPEG-4

- MPEG-2, MPEG-4

- WM9 with DRM

- MPEG-4.10 (H.264) and VC-1 AP over MPEG-2 transport

- Package

- Packaged in 469 ball plastic ball grid array (BGA)

- Advanced 0.13µ low voltage CMOS technology

- Power management

- 1.2V core with 3.3V I/O (5V tolerant)

- Low power and power down modes

#### Main Components of EM8622L

The EM8622L is an advanced, single-chip audio/video decoder that provides highly-integrated solutions for HDTV, IPTV, DVD, MPEG-4.10 (H.264) and WMV9/VC-1 decoding. It incorporates flexible, advanced audio/video processing, enabling cost-effective solutions for consumer appliances, such as digital media players, IPTV set-top boxes, networked DVD players and digital televisions.

The EM8622L includes optimized features for tightly embedded applications such as TV/ PDP integration, streaming video endpoints, and multifunction consumer appliances. The device also includes features that enable designers to easily incorporate advanced capabilities such as A/V streaming, progressive DVD playback, Video-on-Demand (VOD), Personal Video Recording (PVR) and Picture-in-Picture (PIP) into their products.

In addition, the EM8622L supports numerous popular media formats including DVD-Video, Superbit DVD, DVD-Audio, SVCD, VCD1.x, VCD2.0 and CD/CD-R/CD-RW (audio, JPEG, MP3 and MPEG-4 AVI files). It also supports ISMA MPEG-4 streaming format, and MPEG-4 over MPEG-2 transport streaming.

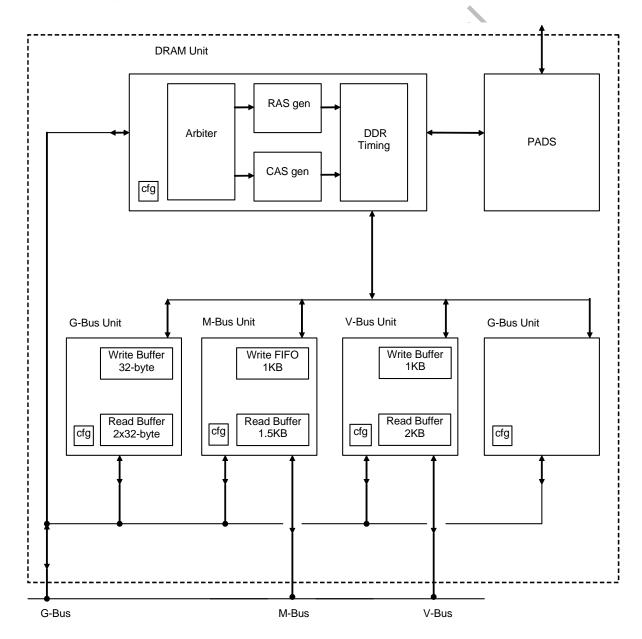

The EM8622L architecture is composed of various hardware functional units – several incorporating custom-designed processor modules – interconnected by multiple high-speed synchronous data buses. Although the details of the on-chip buses are beyond the scope of this document, the primary buses and their functions are described below.

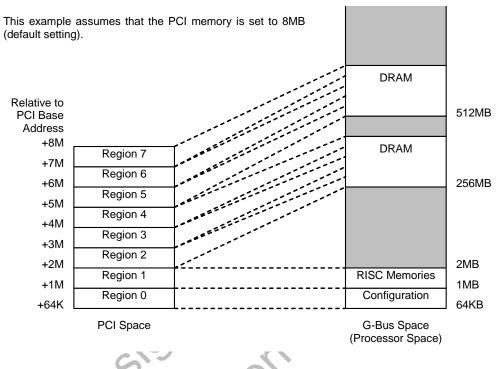

A 32-bit G-Bus connects the integrated ARM-compatible RISC processor with each functional unit. It provides access to the programmable configuration, control and status registers contained within each unit. The state of the device is initialized, controlled, and reconfigured as necessary through this bus. The G-Bus also supports direct access to the memory areas controlled by two memory controllers, PCI, flash memory areas and 32-bits of address and data (4G dwords addressable). It is an arbitrated, multi master bus. The M-Bus provides the data path that allows each functional unit to communicate with the external memory controller. It provides a 64-bit data path resulting in a peak data bandwidth of 1332MB/sec at a system clock frequency of 166MHz. The M-Bus arbitrates access among 17 DMA channels. An arbitration algorithm provides programmable bus bandwidth to be allocated and guaranteed to each DMA channel.

The V-Bus provides a dedicated high-speed data path between the video processing engine and the external memory controller.

In addition to these device-wide buses, the various functional units typically have one or more dedicated local buses within the unit. These buses are not further described in this document.

The main modules of the EM8622L are briefly described below. The modules are discussed in detail under their respective chapters.

#### Host CPU Block

The host CPU block of the EM8622L contains an internal 200MHz ARM-Compatible RISC CPU with its instruction and data caches to support the embedded operating system, middle ware and applications required for the consumer appliances. The CPU is designed for use with applications that require ARM (version 4T) instructions. Typically, the  $\mu$ Clinux embedded OS is used. Alternately, an external host CPU (such as x86, MIPS or ARM) may be used. Since MMU is not included, Linux and WinCE operating systems are not supported.

In addition to the processor itself, the host CPU block contains the following additional resources: 2Kx32 (8KB) local memory, two interrupt controllers, edge detection logic, two programmable timers and two Universal Asynchronous Receiver/Transmitters (UARTs)

#### **DRAM Controller**

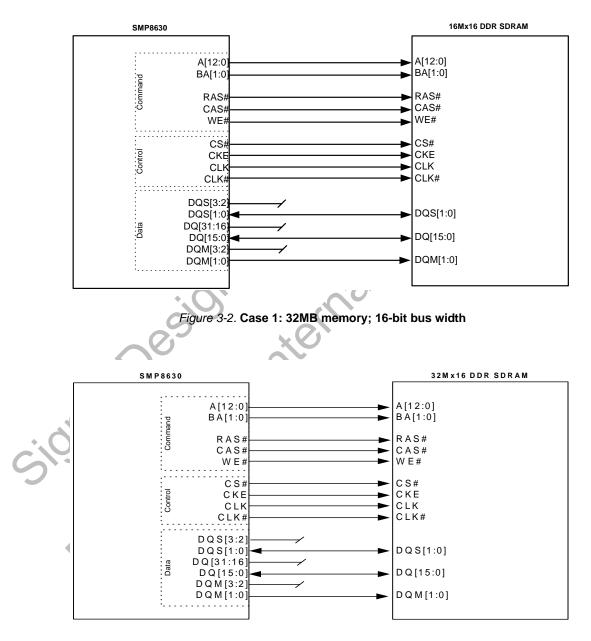

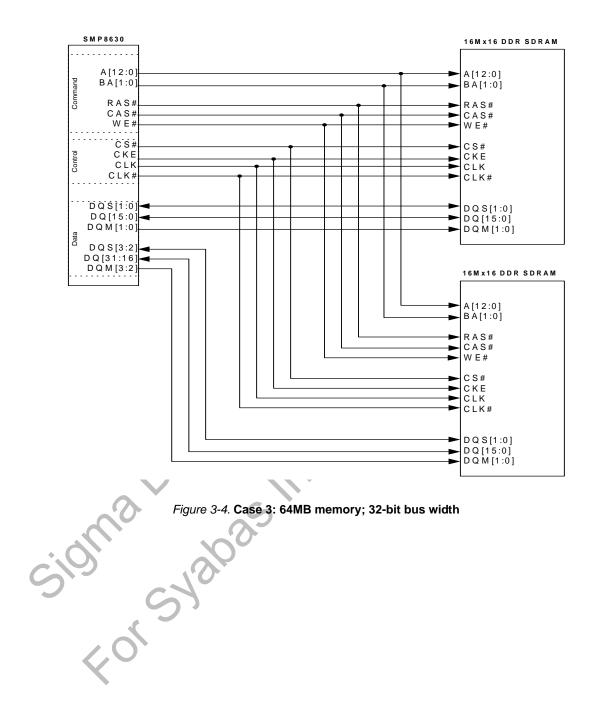

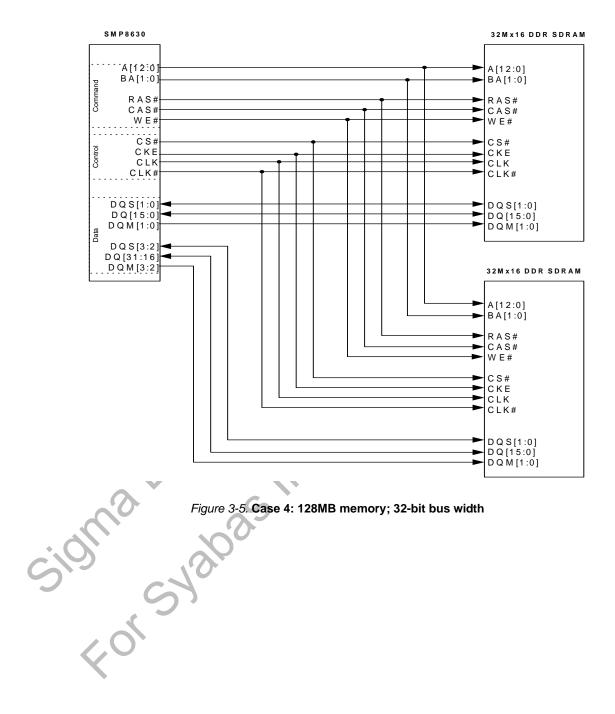

The EM8622L contains double-data rate synchronous DRAM (DDR-SDRAM) controller operating at the memory clock rate. Because the DDR technology transfers data on both edges of the clock, the effective burst data bandwidth of the controller is 1.6GB/sec when using the full 32-bit interface. The DRAM controller can interface up to 128MB of external DDR SDRAM, using a 16 or 32-bit wide data bus.

#### System Block

The EM8622L system block contains the following modules: A GPIO block, I<sup>2</sup>C master and slave and a clock generator. The GPIO block in turn contains General Purpose I/O (GPIO), Front Panel Interface (FIP) controller, Pulse Width Modulator (PWM) and an infrared decoder.

The general purpose I/O controller provides 16 pins of general purpose control signals and logic to help eliminate the glue logic necessary for system integration. Its functions include indicating the system operation and controlling other devices.

The Front Panel Interface (FIP) controller directly supports the NEC uPD16311, NEC uPD16312, PTC PT6311 and PTC PT6312. Other front panel controllers may be used by interfacing to the UART or the GPIO.

The infrared input allows the interfacing to an external IR receiver. The NEC and the Philips RC5/RC6 IR formats, commonly used by consumer equipment are supported.

The I<sup>2</sup>C master and slave interfaces enable the EM8622L to read from and write to external devices. This I<sup>2</sup>C master controller, which supports the synchronous Inter Integrated Circuits (I<sup>2</sup>C) serial protocol, enables the host CPU to access an external I<sup>2</sup>C slave device using a simplified register interface. A separate slave interface allows the EM8622L to be the target of I<sup>2</sup>C transactions initiated by an external master.

The clock generator contains one audio clock, two video clocks, one system clock and one CPU clock. The clock generator creates two high speed (up to 200MHz) clocks from a 27MHz external clock using two programmable PLLs, and creates the main system clock and multiple video and audio clocks by dividing either one of the high speed clocks or the 27MHz reference.

#### Host Interface

The host interface unit provides the interface between the primary internal buses (G-bus and M-bus) and the PCI, the peripheral bus, smart card interface, the serial flash and the IDE interface.

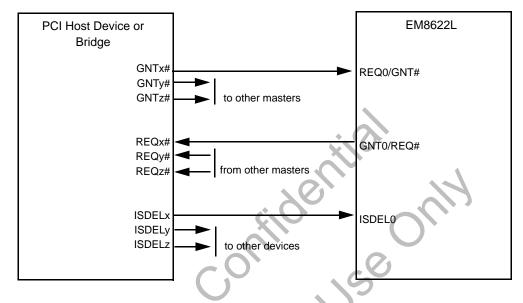

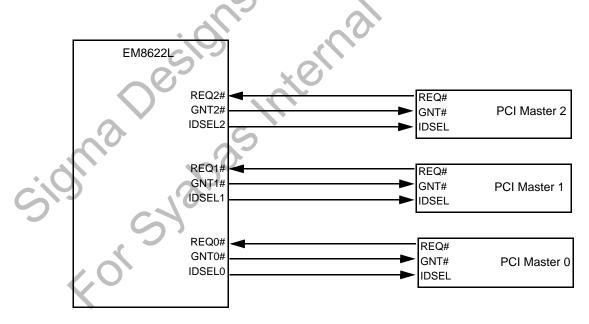

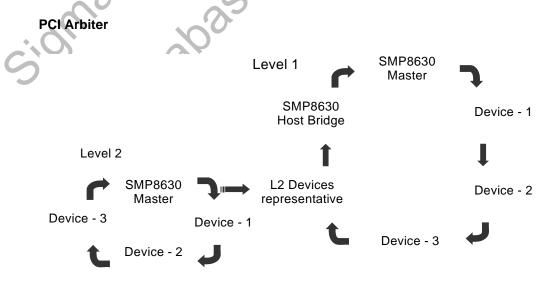

The EM8622L supports both a PCI and a multimode 'peripheral' bus for system-level interconnection. The PCI bus implementation is a version 2.1 compliant, 32-bit wide bus capable of operating at 33 or 66MHz.

The separate Peripheral Bus Interface (PBI) can operate in several modes with programmable cycle timings, which can be varied on a cycle-by-cycle basis. The bus can operate as a general-purpose interface, or an 'ISA-like' bus for connecting external devices, or an IDE bus for attaching storage devices, or a memory bus for directly attaching asynchronous memory such as a parallel flash ROM.

When being used as a general-purpose interface, the PBI can operate in either a separate address and data mode (14 address/16 data) or a multiplexed address/data mode. In the IDE mode, the interface can support ATA device attachments.

The host block also contains an interface to an external serial flash and a smart card interface.

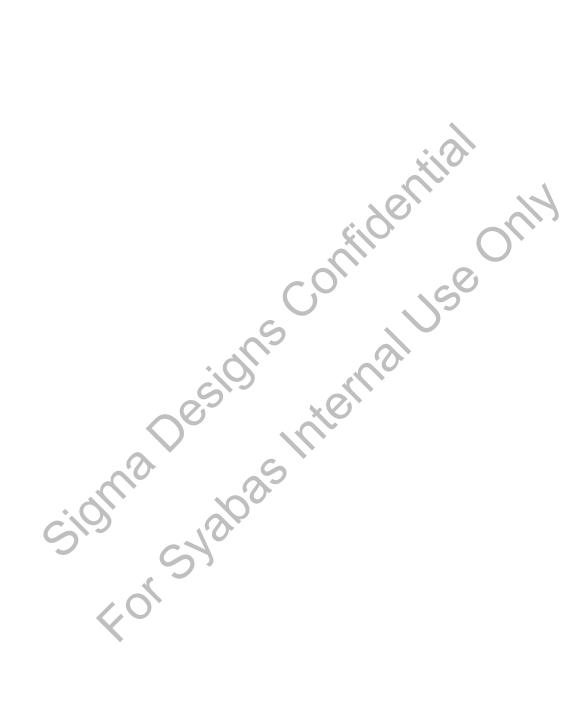

#### Video Decoder Subsystem

The EM8622L video decoder subsystem executes the video decoding algorithms supported by the EM8622L. Its architecture is a hybrid of both processor-based and hard-wired logic approaches.

The video decoder engine consists of a proprietary 16-bit RISC CPU which is augmented by a number of hardware functional units. These functional units perform the most compute-intensive portions of the video decompression algorithms supported by the EM8622L.

#### Video Processing Subsystem

The EM8622L video processing engine provides sophisticated display processing, formatting and output capabilities.

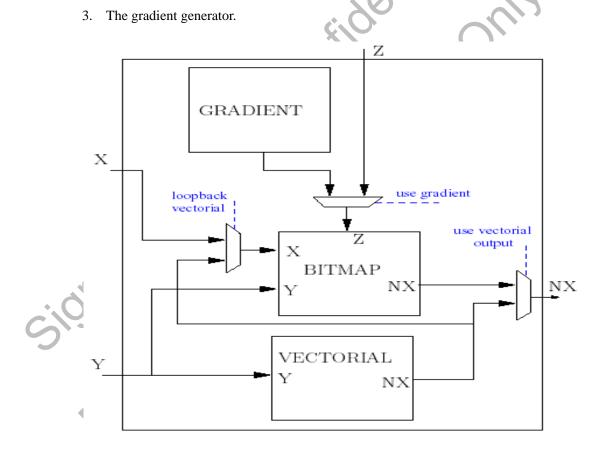

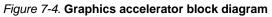

The video processing and display unit (VPD) has extensive capabilities for retrieving graphics and video images from the memory, formatting the images as needed, mixing the images and then presenting the video stream for display in a required format. Other capabilities provided by the VPD include hardware-assisted 2D graphics acceleration, and support for an external video input port.

The 2 available video outputs consist of, digital output and analog output. The digital output supports 8, 16 or 24-bit output, RGB or YPbPr data format and the analog output supports component RGB, YPbPr, S-video and composite video. The digital and analog component outputs can each support output formats up to 1920x1080p.

#### Audio Processing Subsystem

The EM8622L contains an integrated audio subsystem based on a custom-designed 32-bit digital signal processor (DSP). Audio decoding and processing algorithms are implemented on the DSP. This firmware-based approach gives great flexibility for accommodating future audio standards or specialized audio requirements. The audio unit provides three I<sup>2</sup>S output channels, one S/PDIF output channel, and one I<sup>2</sup>S or S/PDIF audio input channel.

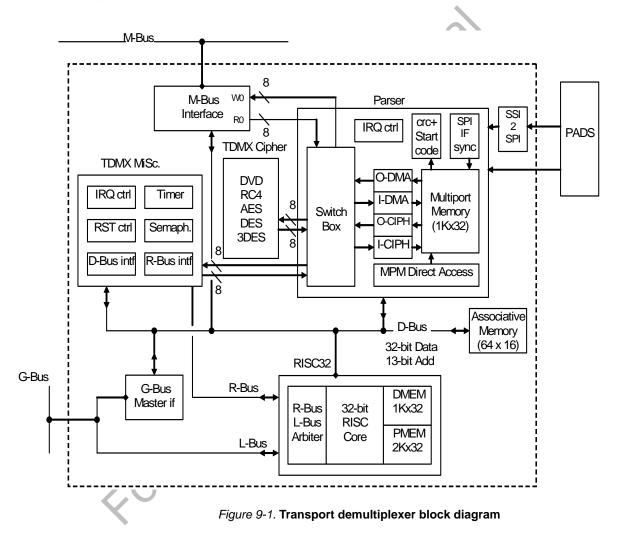

#### **Transport Demultiplexer**

estorma based and the source of the source o The EM8622L includes an on-chip, RISC processor-based transport demultiplexer (TDMX) unit. The transport demultiplexer block is capable of handling up to three multiprogram bitstreams of up to 40Mbps each, with an aggregate total of up to 40Mbps.

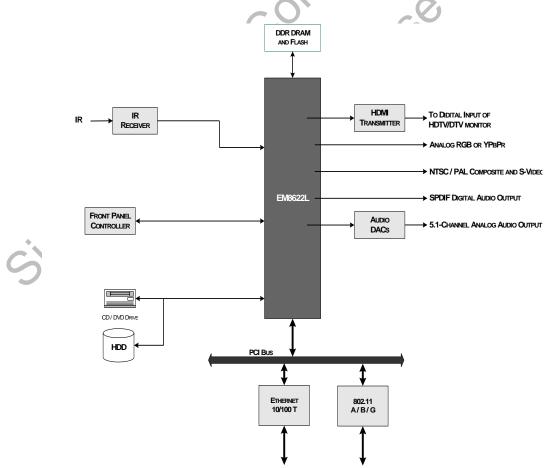

#### **Application Example: Networked DVD Player**

The networked DVD player example below provides the typical functionality required for a networked DVD player. System integration requires very little external logic since the SMP8632 provides most of the features including:

- Progressive DVD-Video, DVD-Audio, MPEG-4.10 (H.264) and WMV9/VC-1 playback

- Interlaced or progressive YPbPr or RGB video outputs

- NTSC/PAL composite and S-video outputs

- 5.1-channel and S/PDIF audio outputs

- I<sup>2</sup>C bus master function for controlling other chips

- · ARM-Compatible CPU for operating system, middleware and applications

Figure 1-2. Application example - networked DVD player

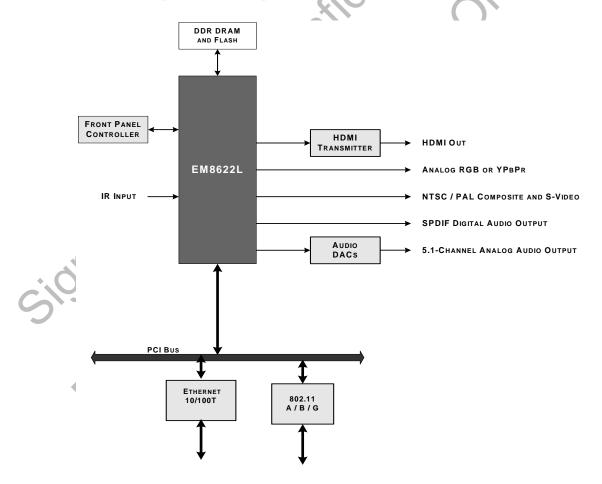

### Application Example: Digital Media Adapter or IPTV Set-top Box

The Digital Media Adapter or IPTV Set-top Box application requires very little external logic since the EM8622L provides most of the features including:

- Decoding of MPEG-1, MPEG-2, MPEG-4. 10 (H.264) and WMV9/VC-1 content

- 2D graphics, OSD and deinterlacing

- Interlaced or progressive YPbPr or RGB video outputs

- NTSC/PAL composite and S-video outputs

- 5.1-channel and S/PDIF audio outputs

- ARM-Compatible CPU for operating system, middleware and applications

Figure 1-3. Application example - digital media adapter or IPTV set-top box

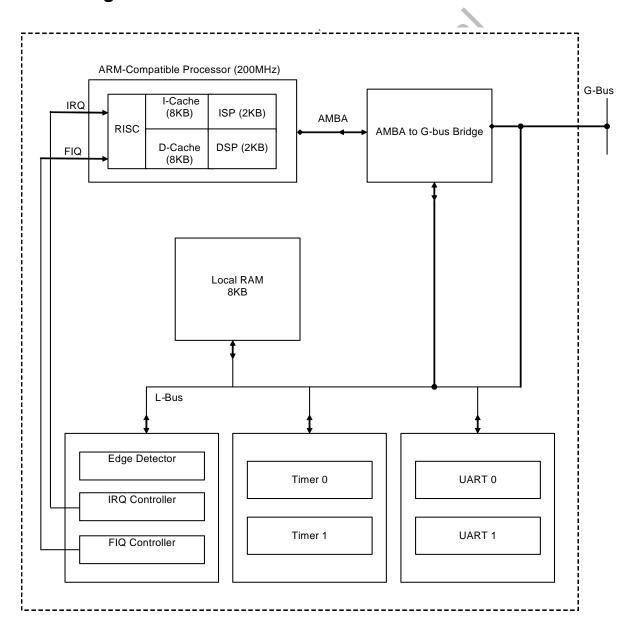

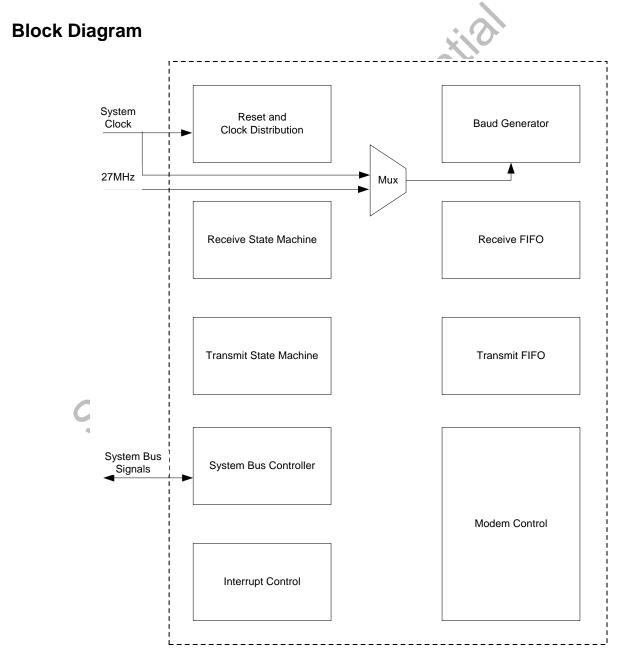

#### **Block Diagram of Host CPU Block**

2

#### Introduction

The host CPU block of the EM8622L contains an internal 200MHz (~260 conforming DMIPS) ARM-compatible processor with its instruction and data caches to support the embedded operating system, middleware and applications required for the consumer products. The CPU is designed for use with applications that require ARM (version 4T) instructions. Typically, the  $\mu$ Clinux embedded OS is used. Alternately, an external host CPU (such as x86, MIPS or ARM) may be used. Since MMU is not included, Linux and WinCE operating systems are not supported.

In addition to the RISC processor itself, the host CPU block contains the following additional resources:

- 2Kx32 (8KB) local memory

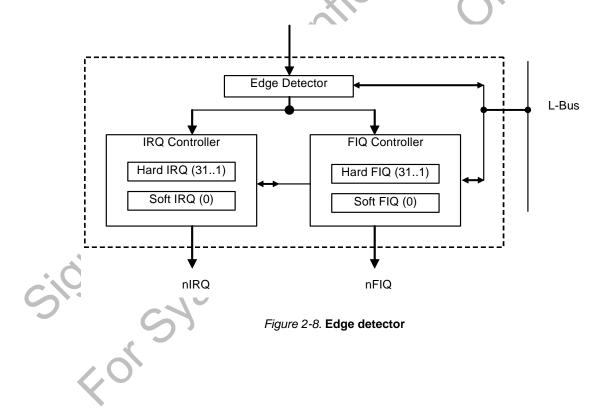

- Two interrupt controllers, IRQ and FIQ

- Edge detection logic

- Two programmable timers

- Two Universal Asynchronous Receiver/Transmitter (UARTs)

The CPU accesses the G-Bus as a master. A bridge allows the CPU to be a G-Bus master, and access all the G-Bus mapped local resources, including the DRAM through the L-Bus. Most of the processor software is executed from the DRAM. For the processor, an AMBA -to-G-Bus bridge is used.

Other components of the host CPU block reside on a local bus and can be accessed by either the RISC or other G-Bus masters. The host CPU block connects to the rest of the chip via the G-Bus.

A local RAM, accessible from the G-Bus can be used to share various types of information between the G-Bus masters. Also, critical processor code, such as reset vectors or interrupt service routines can be stored in the local RAM.

# Central Processor Unit (CPU)

#### Introduction

The EM8622L uses a 200MHz (~260 conforming DMIPS) ARM-compatible processor.

The processor core is a high-performance, low-power, 32-bit RISC processor. It is highly portable across processes. The processor is ideally positioned to support new products for emerging segments of the digital consumer, network, systems and information management markets, enabling new tailored solutions for embedded applications. The EM8622L takes full advantage of all these features.

The EM8622L processor a 32-bit privileged resource architecture that is used with applications that require ARM (version 4T) instructions. It contains direct mapped 16KB instruction and 16KB data caches. Both caches support locking on a per-entry basis. The cache line size is 16-byte, requiring 4 sequential memory transfers on a cache line fill operation.

The processor cache allows support for up to 8 separate memory regions or 'pages'. Each region can contain specific cacheability attributes for the instruction cache, data cache and the write buffer. In addition, multiple levels of access permissions can be attached to each memory region. Memory prefetching is supported on a per-instruction basis.

#### Features

32-bit RISC architecture

5-stage pipeline

$\mathcal{C}$

- Separate, 16KB, direct-mapped instruction and data caches

- Support for up to 8 memory regions, with memory access protection for each region

- Data cache write-back and write-through support on a per-entry basis

- 16-byte fixed line size with cache line locking support on a per-entry basis

- Support for both Supervisor mode and User mode on cache accesses

- 4-deep write buffer for data cache writebacks

- Memory prefetching on a per-instruction basis and Memory prefetch and lock in one operation

- Burst transfers on cache line fill operations

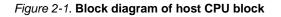

#### **Block Diagram**

#### **Functional Description**

The block diagram of the EM8622L ARM-compatible processor is shown above. The following subsections describe each block in the diagram.

#### Main Blocks of the EM8622L Processor

#### **Instruction Fetch Unit**

The instruction Fetch Unit fetches one instruction per clock cycle and contains a 3-deep FIFO for instruction storage during pipeline stalls. If the pipeline is stalled, then the instruction fetch continues until the FIFO becomes full, at which time the fetching stops.

The program counter (PC) is used to increment the address values used to access the memory. In the 32-bit mode, the counter increments by 4 each time an instruction is fetched. In the 16-bit mode, the counter increments by 2 each time an instruction is fetched. All instruction fetching is performed on the physical address value, eliminating the need for internal virtual to physical address translation.

#### **Primary Instruction Cache**

The processor's primary cache design includes a direct mapped, 16KB instruction cache. It contains a fixed line size of 128-bits and incorporates a 32-bit wide data SRAM and a Tag SRAM.

#### Decoder

The decoder is used to decode the instructions prior to being written to the register file. The 32-bit instructions are decoded and appropriate signals are sent to the core indicating the type of operation to be performed.

#### 32-bit Register File

The 32-bit General Purpose (GP) Register File stores the operands and the results of a computation. The processor accesses the GP register file in one of the 6 operating modes: User, FIQ, IRQ, Supervisor, Abort and Undefined Instruction.

#### Shifter

The shifter performs logical and arithmetic shifting based o the type of instruction being executed. The processor's instruction set incorporates certain shift operations into the instructions and hence does not require a separate shift operation to be performed.

#### Arithmetic Logic Unit (ALU)

The Arithmetic Logic Unit accepts two operands and associated control signals, one from the register file and one from the shifter. The ALU processes all the operations except multiply. These include move, load/store, data processing and coprocessor operations.

#### 32-bit Multiplier

The EM8622L processor contains a 32-bit multiplier that performs signed and unsigned multiply and multiply-accumulate operations. The multiplier requires 2 cycles to perform a multiply-accumulate operation. In the first cycle 3 operands are provided to the multiplier and the actual multiply operation is performed. In the second cycle the 4<sup>th</sup> operand is provided and the accumulate operation is performed. The multiplier requires 2 operands to perform the multiply, and another 2 operands to perform the accumulate.

The processor always generates a 64-bit value on a multiply or multiply-accumulate operation. The lower 32-bits of the result are stored to a GP register whose location is defined in the instruction. The upper 32-bits are stored to the CP15 RdHi register (CP15-11). The CP15-11 is the register 11 in the CP15 control register set. Unlike a multiply long or multiply-accumulate long operation, generating a 64-bit result on multiply and multiply-accumulate operations allows the upper and the lower halves of the 64-bit result to be written to nonsequential registers. For a long multiply or multiplyaccumulate operation, the 64-bit result is stored to 2 sequential GP registers whose locations are defined in the instruction.

The EM8622L processor multiplier executes the following operations:

- Multiply: The multiply instruction (MUL) multiplies 2 signed or unsigned variables to

produce a 64-bit result. The lower 32-bits of the result are stored to a GP register

whose location is defined in the instruction. The upper 32-bits are stored to the CP15

RdHi register (CP15-11) using the MCR instruction. This allows the 64-bit result to

be stored to 2 nonsequential registers. This instruction is executed only if the condition specified in bits 31:28 of the instruction matches the condition code status.

- Multiply-accumulate: The multiply-accumulate instruction (MLA) multiplies 2 signed or unsigned operands to produce a 64-bit result, which is added to a 3<sup>rd</sup> operand and written to the destination register. The lower 32-bits of the result are stored to a GP register whose location is defined in the instruction. The upper 32-bits are stored to the CP15 RdHi register (CP15-11) using the MCR instruction. This allows the higher-precision 64-bit result to be stored to 2 nonsequential registers. This instruction is executed only if the condition specified in bits 31:28 of the instruction matches the condition code status.

- Signed multiply long: The signed multiply long instruction (SMULL) multiplies 2 signed variables to produce a 64-bit result. The result is written to 2 sequential GP registers whose location is defined in the instruction. This instruction is executed only if the condition specified in bits 31:28 of the instruction matches the condition code status.

- Signed multiply-accumulate long: The signed multiply-accumulate long instruction (SMLAL) multiplies 2 signed variables to produce a 64-bit result, which is then added to another 64-bit value stored in 2 sequential destination GP registers. This instruction is executed only if the condition specified in bits 31:28 of the instruction matches the condition code status.

- Unsigned multiply long: The unsigned multiply long instruction (UMULL) multiplies 2 unsigned variables to produce a 64-bit result. The result is written to 2 sequential GP registers whose location is defined in the instruction. This instruction is executed only if the condition specified in bits 31:28 of the instruction matches the condition code status.

- Unsigned multiply-accumulate long: The unsigned multiply-accumulate long instruction (UMLAL) multiplies 2 unsigned variables to produce a 64-bit result, which is then added to another 64-bit value stored in 2 sequential destination GP registers. This instruction is executed only if the condition specified in bits 31:28 of the instruction matches the condition code status.

#### Data Cache

The primary data cache of the EM8622L includes a direct mapped, 16KB data cache. The primary data cache contains a fixed line size of 128-bits and incorporates a 32-bit wide data SRAM, a Tag SRAM, and a 1-bit wide Dirty Bit RAM.

#### Write Buffer

The EM8622L processor provides a 4-entry write buffer to maximize memory bus bandwidth. This buffer is used by the data cache to store modified lines to be written out to memory, and by the core to store non-cacheable data that has access to the write buffer. The entries in the cache that are marked as 'writeback' are written to the write buffer instead of directly to the memory. The writethrough pages are written directly to the memory and do not use the write buffer.

#### Load Store Unit

The EM8622L processor contains a load/store unit that controls the loading and storing of data between the data cache and the write buffer. During a data cache access, the address is generated by the Load/Store Unit of the core and driven to the cache.

The address and the data paths between the load/store unit and the write buffer are also used for non-cacheable stores that have access to the buffer.

#### **Memory Management**

The Memory Management Unit (MMU) provides an interface between the processor core and the caches. The MMU accepts only MCR and MRC instructions from the core. Although the processor executes the CDP, LDC and STC instructions, no coprocessor is implemented to respond to these instructions. Therefore, execution of these 3 instructions result in an Undefined Instruction exception.

The MMU decodes the instruction and manipulates the cache accordingly. This includes updating the contents of the caches, flushing the caches, and locking certain lines within either cache.

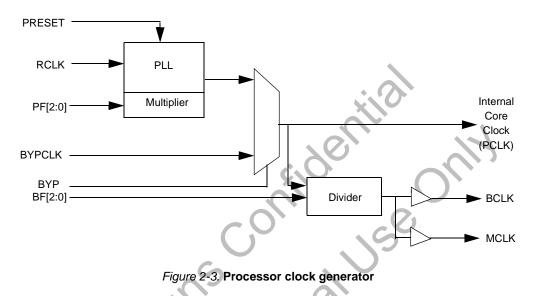

#### **PLL/Clock Multiplier**

The clock multiplier multiplies the input reference clock by a value of 2 to 16. The RCLK input clock to the processor is multiplied within the PLL to derive the CPU clock. The input clock can be multiplied by the following ratios: 2, 4, 6, 8, 10, 12, 14 and 16.

The RCLK input is multiplied by the ratio determined by the PF[2:0] input pins to produce the internal PCLK used by the core. A separate clock divider is used to divide the PCLK signal by the ratio determined by the BF[2:0] pins to produce the clock outputs MCLK and BCLK used to drive the bus.

Because of the skew between the RCLK and the bus clock outputs, all the devices on the system bus must synchronize to either MCLK or BCLK, when the PLL is used as the clock resource.

Alternatively, the BYP input can be asserted to bypass the PLL. In this case, an external clock BYPCLK is used. If the PLL is bypassed, the frequency of the BYPCLK is used to drive the PCLK directly.

#### **Processor Modes of Operation**

The processor contains the following modes of operation: User, FIQ, IRQ, Supervisor, Abort and Undefined Instruction.

| Name                  | Operating Mode | Description                             |

|-----------------------|----------------|-----------------------------------------|

| User                  | User           | Application program                     |

| FIQ                   | Privileged     | Fast interrupt request handler          |

| IRQ                   | Privileged     | Normal interrupt request handler        |

| Supervisor            | Privileged     | Operating system                        |

| Abort                 | Privileged     | Memory manager                          |

| Undefined Instruction | Privileged     | Emulator for instruction set extensions |

There are two basic types of operating modes, user and privileged.

#### **User Mode**

The user mode is where the application program and the other user code such as device drivers reside. The processor operates in this mode during normal operations, and only enters one of the privileged modes when an exception or interrupt occurs. The user mode is selected when the M[4:0] field contains a value of 0b10000 or 0b11111.

#### **Privileged Modes**

There are 5 types of privileged modes: IRQ mode, FIQ mode, Supervisor mode, Abort mode and Undefined Instruction mode.

#### IRQ Mode

The IRQ mode is a privileged mode that is entered when an external interrupt is generated on the IRQ pin. The IRQ contains a dedicated Link register (R14\_IRQ) that contains the return address, and a Save Processor Status Register (SPSR\_IRQ) that contains the processor state at the time the interrupt was taken. Once the interrupt has been serviced, the contents of R14\_IRQ are loaded into the program counter (PC), and the contents of the SPSR\_IRQ are loaded into the CPSR, allowing the program to resume execution in the mode specified in the SPSR\_IRQ.

#### FIQ Mode

The FIQ mode is a privileged mode that allows for faster interrupt processing than the IRQ mode by providing 5 additional dedicated general purpose registers (R8\_FIQ through R12\_FIQ) that the interrupt handler can use for temporary storage. The FIQ mode is entered when an external interrupt is generated on the FIQ pin. Like the IRQ mode, the FIQ mode also contains a dedicated Link Register (R14\_FIQ) that contains the return address, and a Save Processor Status register (SPSR\_FIQ) that contains the processor state at the time the interrupt was taken. Once the interrupt has been serviced, the contents of R14\_FIQ are loaded into the program counter (PC), and the contents of SPSR\_FIQ are loaded into the program to resume execution in the User mode.

#### Supervisor Mode

The supervisor mode is a privileged mode entered through the execution of the software Interrupt (SWI) instruction. Certain memory spaces not available in the User mode can be accessed in the Supervisor mode. In addition, many core maintenance functions are performed in the supervisor mode. The Supervisor mode contains a dedicated Link register (R14\_SVC) that contains the return address, and a Save Processor Status register that contains the processor state at the time the interrupt was taken. Once the interrupt has been serviced, the contents of the Link register are loaded into the program counter (PC), and the contents of the Save Processor Status register are loaded into the CPSR, allowing the program to resume execution in the User mode.

#### Abort Mode

The abort mode is a privileged mode that is entered when the processor must abort an operation. There are 4 types of abort operations:

- External instruction abort

- External data abort

- Internal instruction abort

- Internal data abort

An external data or instruction abort is initiated when an external logic asserts the ABORT pin to the processor. An instruction abort occurs when the processor attempts to fetch instruction from an invalid or restricted address. An instruction operation is indicated by the processor driving the nOPC pin low. A data abort occurs when the processor attempts to store or load instructions to or from am invalid or restricted address. A data operation is indicated by the processor driving the nOPC pin high.

The MMU can also perform an integral instruction or data abort by checking the address generated by the processor against its own access permissions.

Internal and external abort operations are logically OR'd within the processor core to provide a single internal abort signal. The MMU compares the 32-bit address with the access permissions. If there is a match between the access permissions provided by the processor, then the MMU generates an internal abort. The internal abort signal is then logically OR'd with the external ABOT pin. If either of these signals is asserted, then an abort signal is sent to the core.

The abort mode contains a dedicated Link register (R14\_ABORT) that contains the return address, and a Save Processor Status register that contains the processor state at the time the abort was taken. Once the abort request has been serviced, the contents of R14\_ABORT are loaded into the program counter (PC), and the contents of the Save Processor Status register are loaded into the CPSR, allowing the program to resume execution in the User mode.

#### **Undefined Instruction Mode**

The undefined instruction mode is a privileged mode that is entered under either of the following 2 conditions:

- When no coprocessor responds to a coprocessor instruction generated by the processor

- When bits 27:25 of the 32-bit instruction contain a value of 0b011, and bit 3 is 0b1, indicating an access to undefined instruction space.

The undefined instruction mode contains a dedicated Link register (R14\_UND) that contains the return address, and a Save Processor Status register that contains the processor state at the time the interrupt was taken. Once the abort request has been serviced, the contents of R14\_UND are loaded into the program counter (PC), and the contents of the Save Processor Status register are loaded into the CPSR, allowing the program to resume execution in the User mode.

#### **Processor Pipeline**

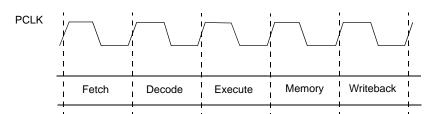

The EM8622L processor core is a high-performance, single-issue RISC architecture that implements a 5-stage pipeline:

- 1. Fetch stage Instruction prefetch.

- 2. Decode stage Instruction decode and read source registers from multiported register file.

- 3. Execute stage: Generate memory read address and perform ALU/MAC operation.

- 4. Memory stage: Read data input bus and ALU/MAC result.

5. Writeback stage: Writeback to register file and load write buffer.

#### Figure 2-4. EM8622L processor pipeline block diagram

#### **Fetch Stage**

During the fetch stage the Instruction Fetch Unit retrieves the instruction from the Instruction Cache and passes it to the decoder.

#### **Decode Stage**

In the decode stage, 32-bit instructions are decoded and the appropriate internal signals are driven to indicate the type of operation to be performed. If the processor is operating in a 16-bit mode, then a 16-bit instruction is translated into a 32-bit instruction that is decoded by the 32-bit decoder during this stage. The result of the operation is written to the register file.

#### Execute Stage

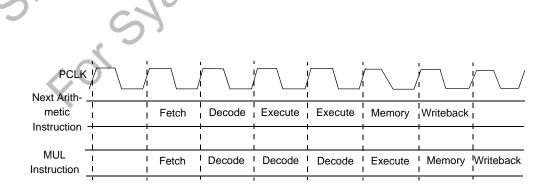

In the execute stage the instruction operands are read from the register file and passed to the ALU or 32-bit multiplier depending on the type of the operation. Most ALU operations require only one PCLK cycle to complete. A multiply instruction occupies the Execute stage for 3 PCLK cycles, which stalls the next instruction. The latency for a multiply is constant, and not data-dependent.

The next instruction stalls in the Decode stage for 2 clocks because the MUL instruction is using the Execute stage. Once the multiplication is complete and the MUL instruction propagates to the Memory stage, the next instruction can move to the Execute stage. This diagram assumes that the next instruction is an arithmetic instruction since only one Execute cycle is required.

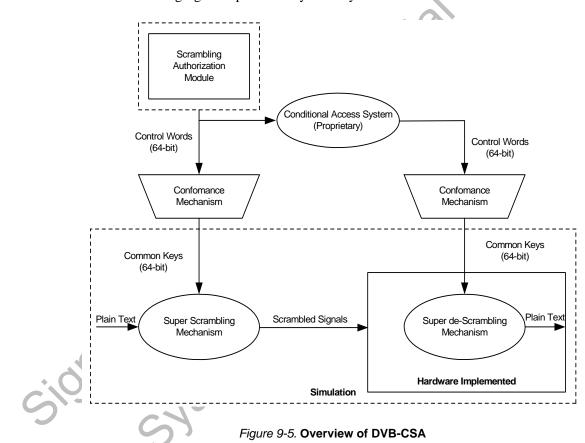

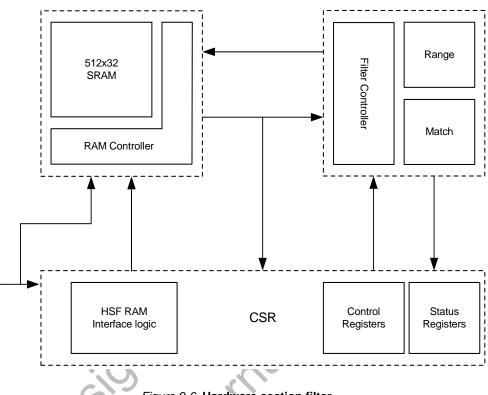

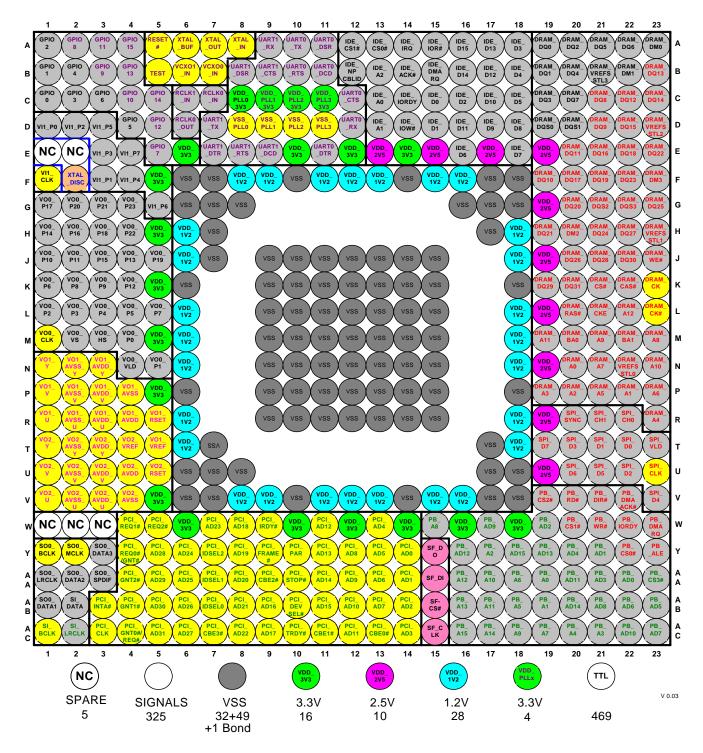

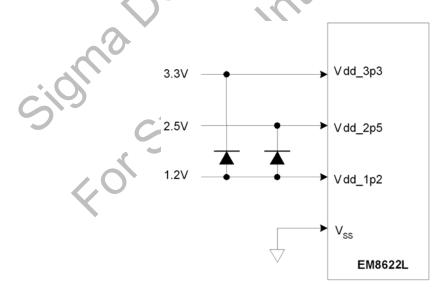

### **Memory Stage**