# 義隆電子股份有限公司

#### ELAN MICROELECTRONICS CORP.

# EM78P803A

8-bit MCU

2005/8/12

Version 1.3.3

ELAN MICROELECTRONICS CORP.

No. 12, Innovation 1<sup>st</sup> RD., Science-Based Industrial Park

Hsin Chu City, Taiwan

TEL: (03) 5639977 FAX: (03) 5780617

# 義隆電子股份有限公司

# ELAN MICROELECTRONICS CORP.

# Version History

| Version |    | Content                                                             | Release Date |

|---------|----|---------------------------------------------------------------------|--------------|

| 1.0     | 1. | Initial version                                                     | 2004/03/29   |

|         | 2. | Original Spec. is oriented from EM78805C v2.0 spec                  |              |

| 1.1     | 1. | Modified the LCD driving waveform of 1/3 bias                       | 2004/05/26   |

|         | 2. | Add internal clock source for R to F Counter                        |              |

|         | 3. | Add option code for supporting 16-bit counter mode                  |              |

| 1.2     | 1. | Modified ERIC mode function                                         | 2004/6/30    |

|         | 2. | Modified pad assignment                                             |              |

| 1.3     | 1. | Modified the configuration of PLL                                   | 2004/11/30   |

|         | 2. | Modified the selection of CNT2 source                               |              |

|         | 3. | Fix up the bug in R to F macro                                      |              |

|         | 4. | Modified the setup of Low Battery Detect                            |              |

| 1.3.1   | 1. | Modified the operating voltage range                                | 2004/12/3    |

| 1.3.3   | 1. | Modified the table of sub frequency divider.                        | 2005/8/12    |

|         | 2. | Modified the definition of R2FHR option code.                       |              |

|         | 3. | Modified the power consumption and reset level on POVD function (in |              |

|         |    | product spec., not in target spec.)                                 |              |

|         | 4. | Modified the definition of P803ON option code                       |              |

|         | 5. | Modified the product no. of 64-pin QFP                              |              |

# CLAN

# 義隆電子股份有限公司

#### ELAN MICROELECTRONICS CORP.

# **User Application Note**

(Before using this chip, take a look at the following description note, it includes important messages.)

- 1. There are some undefined or not existent bits in the registers. For these bits, user need to take more care on them while program use them as data to execute logic or math operations. Because these bits are not relative to chip function, they never test in the factory. We use different symbols to recognize them.

- "0" or "1" → value always equal to 0 or value always equal to 1, (not existent, read only)

- "-" > value unknown, (not existent) undefined bits do not allow to use.

- "x" -> (general purpose) undefined bits do not allow to use as RAM or other data read, write or read/write.

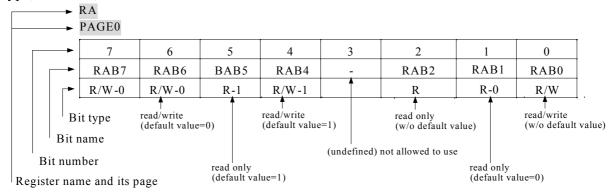

- 2. You will see some names for the register bits definitions. Some name will appear very frequently in the whole spec. The following describes the meaning for the register's definitions such as bit type, bit name, bit number and so on.

#### 3. Family Relation

| Mask     | ROMless  | OTP       |

|----------|----------|-----------|

| EM78805C | EM78R803 | EM78P803A |

#### 4 Main Function Difference

|                   | EM78805C                      | EM78P803A                                  | EM78R803                                   | EM78801                                    |

|-------------------|-------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| Type              | Mask                          | OTP                                        | ROMless                                    | Mask                                       |

| ROM size          | 12k <b>x</b> 13b              | 8k <b>x</b> 13b                            | 16k x 13b                                  | 8k <b>x</b> 13b                            |

| Max. I/O          | 22                            | 28                                         | 28                                         | 24                                         |

| Main<br>Clock     | 3.5826MHz x<br>1/8, 1/2, 1, 2 | 3.5826MHz x<br>1/2, 1, 2, 4<br>& ERIC mode | 3.5826MHz x<br>1/2, 1, 2, 4<br>& ERIC mode | 3.5826MHz x<br>1/2, 1, 2, 4<br>& ERIC mode |

| LCD               | 24 x 8/4                      | 28 x 8/4                                   | 28 x 8/4                                   | 24 x 8/4                                   |

| (Max. Seg.x Com.) | 1/4 Bias                      | 1/3, 1/4 Bias                              | 1/3, 1/4 Bias                              | 1/3, 1/4 Bias                              |

| Tone Generator    | Yes                           | Yes                                        | Yes                                        | No                                         |

| DED               | Yes                           | Yes                                        | Yes                                        | No                                         |

| R to F Counter    | No                            | No                                         | Yes                                        | Yes                                        |

| 16-bit counter    | No                            | No                                         | Yes<br>(Pad Option)                        | Yes                                        |

#### 5. Notice of ERIC Mode:

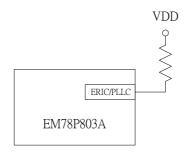

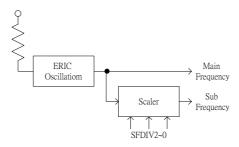

In ERIC mode, the RC oscillation circuit on the chip with an external resister provides the system clock. There is no 32.768kHz clock because no crystal connects to the system. The sub frequency which plays the role as the same as 32.768kHz is divided from system clock. User can setup the scale factor by CODE option when downloading the program. Furthermore, to careful to use the sub frequency clock when system working in ERIC mode. Some frequency didn't suggest might cause unpredictable condition. Please refer Sec.VII.15 for more detail

- 6. Common registers  $0x20 \sim 0x3F$  only have three banks (banks 0,1,2). Notice that there is no bank 3 in these common registers. The bank 3 doesn't exist.

- 7. Care must be taken while programming. When R4 (bit7, bit6) = (1,1), common registers  $0x10 \sim 0x1F$  cannot be read or written otherwise program maybe go to dead lock. ICE cannot reflect this problem. This is incompatible situation between mask and ICE.

II

## I. Main Feature

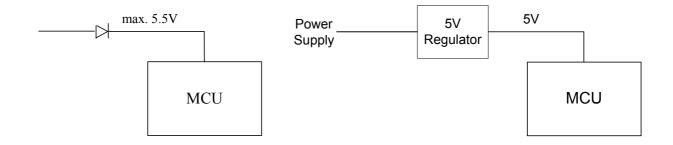

## ■ Single power supply

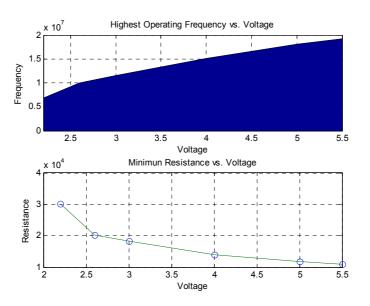

Operating voltage range: 2.8V ~ 5.5V(7.1652MHz)

$4.5V \sim 5.5V(14.331MHz)$

$2.2V \sim 5.5V(3.5826MHz/ERIC mode)$

$2.2V \sim 5.5V(Sleep/Idle/Green mode)$

#### ■ CPU

8-bit RISC kernel

99.9% single instruction cycle commands

#### Clock

32 768KHz clock source

Built-in PLL to generate main clock 3.5826MHz x 0.5, 1, 2 and 4

Optional ERIC mode only with an external R

#### Timer and counter

Watch Dog: Programmable free running on chip watchdog timer

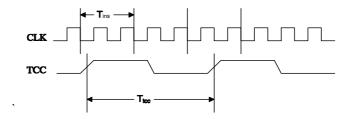

TCC: 8-bit real time clock/counter (TCC) with 8-bit prescaler

COUNTER1: 8-bit counter with 8-bit prescaler can be an interrupt source

COUNTER2: 8-bit counter can be an interrupt source

Both of counters have reload function.

#### ■ Memory

8k x 13bits on chip Electrical One Time Programmable Read Only Memory (OTP-ROM)

0.5k x 8bits on-chip CID RAM

112 x 8bits common registers

#### I/O

Up to 28 bi-directional tri-state I/O ports (18 independent I/O)

IO with internal Pull high, wake-up and interrupt functions

#### ■ Operation mode

Four modes can be selected. (Main clock is generated by internal PLL.)

| Mode        | CPU status | Main clock | 32.768 kHz clock status |

|-------------|------------|------------|-------------------------|

| Sleep mode  | Turn off   | Turn off   | Turn off                |

| Idle mode   | Turn off   | Turn off   | Turn on                 |

| Green mode  | Turn on    | Turn off   | Turn on                 |

| Normal mode | Turn on    | Turn on    | Turn on                 |

#### ■ Interrupt

Selective signal sources and overflow interrupt

STACK: 8 levels stack for subroutine nesting

8 interrupt source, 5 external, 3 internal

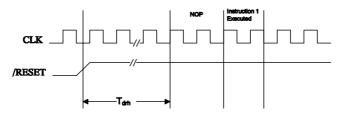

#### Reset

Power on reset, /POVD reset (by PAD option) or external /RESET pin

## ■ Programmable Tone Generators

Programmable Tone1 and Tone2 generators

Independent single tone generation for Tone1 and Tone2

Mixed dual tone generation by Tone1 and Tone2 with 2dB difference

Can be programmed for DTMF tone generation

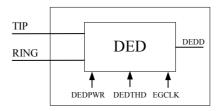

#### ■ DED

Differential-input Energy Detector (DED) for line energy detection

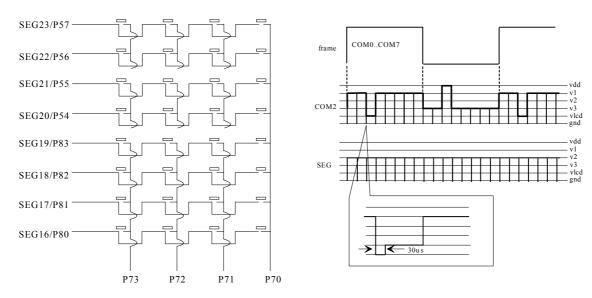

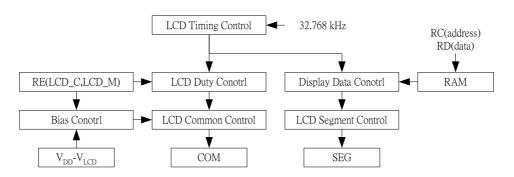

#### LCD

LCD operation voltage chosen by software

Common driver pins: 8/4 Segment driver pins: 28

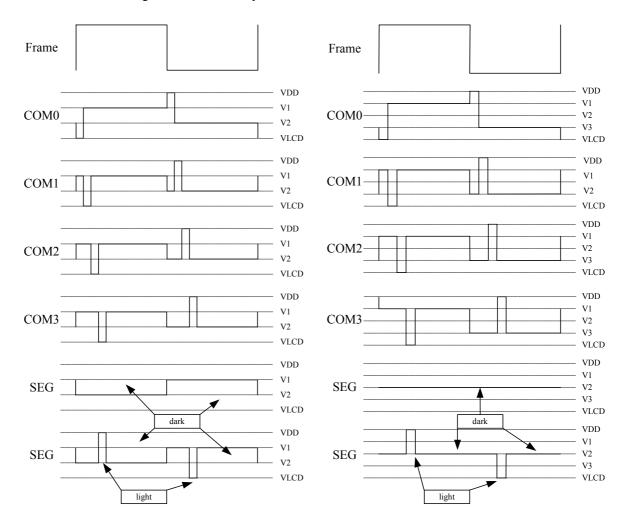

1/3 bias or 1/4 bias with output buffer

<sup>\*</sup> This specification are subject to be changed without notice.

1/4 duty or 1/8 duty

#### ■ PACKAGE

64-pad die (EM78P803AH) 100-pin QFP (EM78P803AQ) 64-pin QFP:

| Name         | /POVD       | ERICen      |

|--------------|-------------|-------------|

| EM78P803AAAQ | Disable (H) | Disable (L) |

| EM78P803AABQ | Disable (H) | Enable (H)  |

| EM78P803ABAQ | Enable (L)  | Disable (L) |

| EM78P803ABBQ | Enable (L)  | Enable (H)  |

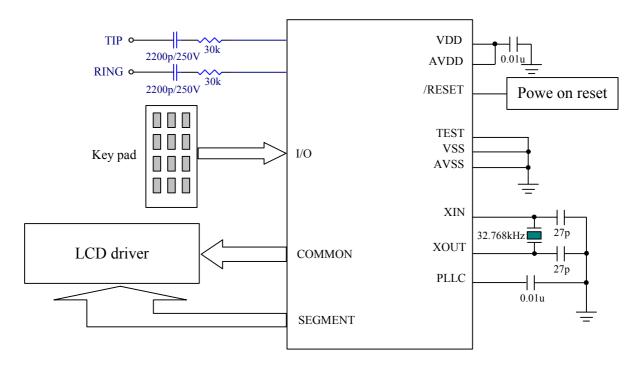

# II. General Description

This is an 8-bit CID (Call Identification) RISC type microprocessor with low power, high speed CMOS technology. Integrated onto a single chip are on-chip watchdog (WDT), RAM, OTP-ROM, programmable real time clock /counter, internal interrupt, power down mode, LCD driver, Energy Detector (DED) or Low Batter Comparator and tri-state I/O. It provides a single chip solution for versatile and general-purpose application use.

# III. Application

Caller ID adjunct box or phone units for FSK/DTMF CID dual system development and general-purpose application.

<sup>\*</sup> This specification are subject to be changed without notice.

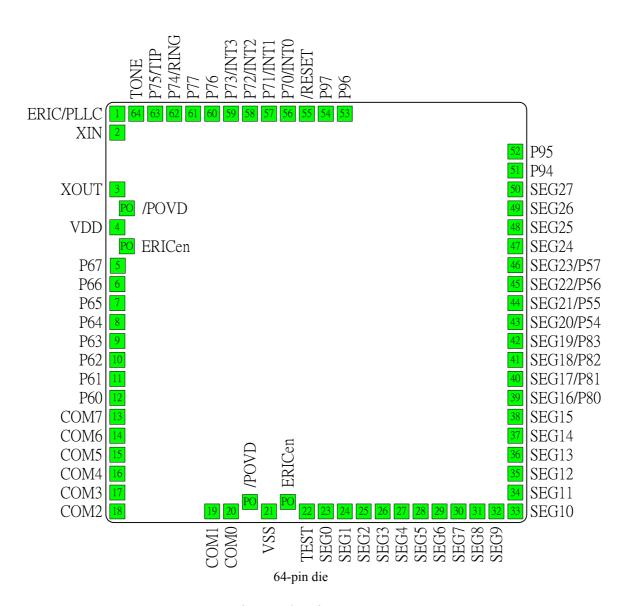

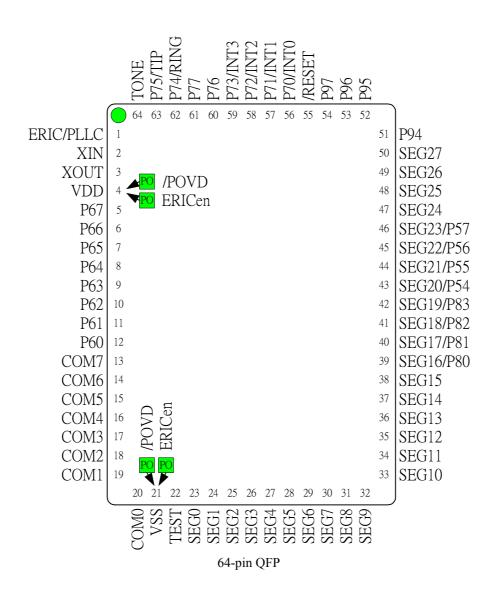

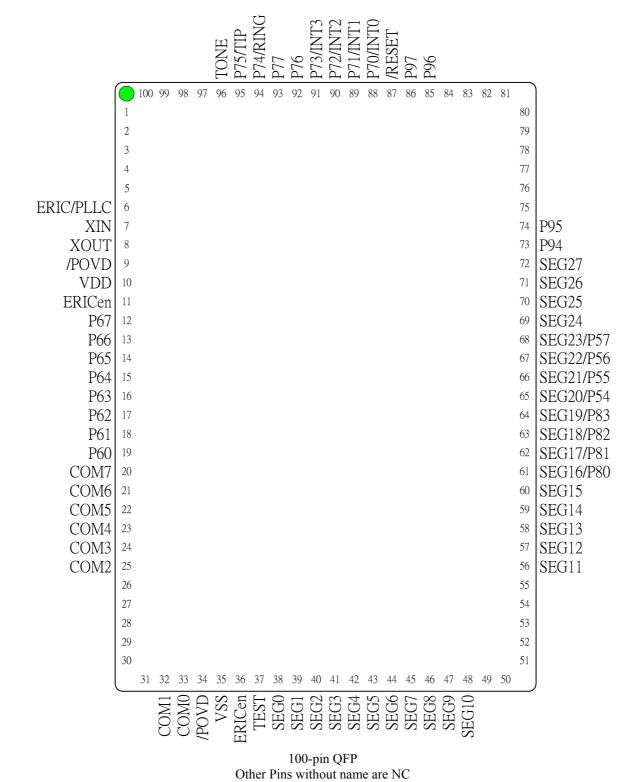

# IV. Pin Configuration

Fig.1 Pad assignment

Fig.1 Pad assignment (Continued)

<sup>\*</sup> This specification are subject to be changed without notice.

Fig.1 Pad assignment (Continued)

<sup>\*</sup> This specification are subject to be changed without notice.

# V. Functional Block Diagram

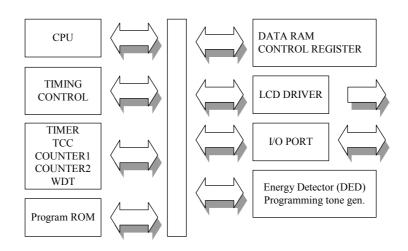

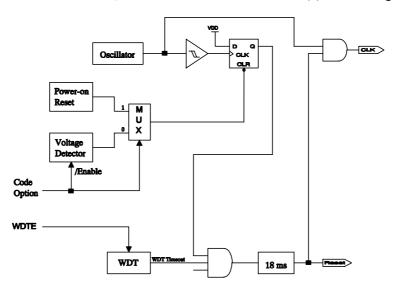

Fig.2 Block diagram1

Fig.3 Block diagram2

<sup>\*</sup> This specification are subject to be changed without notice.

# VI. Pin Descriptions

| Pin           | I/O        | Description                                                                             | Num     |

|---------------|------------|-----------------------------------------------------------------------------------------|---------|

|               | 1/0        | Description                                                                             | 1 (uiii |

| Power<br>VDD  | POWER      | Chia navva VDD                                                                          | 1       |

|               |            | Chip power VDD                                                                          | 1       |

| VSS           | GROUND     | Chip ground GND                                                                         | 1       |

| Clock for MCU | T T        | 1                                                                                       | 1       |

| XIN           | I          | Input pin for 32.768kHz crystal                                                         | 1       |

| XOUT          | 0          | Output pin for 32.768kHz crystal                                                        | 1       |

| PLLC          | I          | Phase locked loop capacitor, connect a capacitor 0.01u to 0.047u to the ground.         | 1       |

| ERIC          | I          | Connect to VDD with a resister serially when in ERIC mode. This pin is shared with PLLC | 1       |

| LCD driver    |            |                                                                                         |         |

| COM0COM7      | O          | Common driver pins of LCD drivers                                                       | 8       |

| SEG0SEG15     | 0          | Segment driver pins of LCD drivers                                                      | 20      |

| SEG24SEG27    |            |                                                                                         |         |

| SEG16SEG19    | O (PORT8)  | Segment driver pins of LCD drivers                                                      | 4       |

|               | ,          | Shared with P80 ~ P83                                                                   |         |

| SEG20SEG23    | O (PORT5)  | Segment driver pins of LCD drivers                                                      | 4       |

|               |            | Shared with P54 ~ P57                                                                   |         |

| DTMF          | T          |                                                                                         | ,       |

| TONE          | О          | Programming tone generator output                                                       | 1       |

| DED           |            |                                                                                         |         |

| TIP           | I (PORT75) | Differential-input Energy Detector input pin. It is non-polarity pin Shared with P75.   | 1       |

|               |            | It can be used as positive input of low battery comparator.                             |         |

| RING          | I (POTT74) | Differential-input Energy Detector input pin. It is non-polarity pin Shared with P74    | 1       |

|               |            | It can be used as negative input of low battery comparator.                             |         |

| Test          |            | <u> </u>                                                                                | l.      |

| TEST          | I          | Test pin into test mode, normal low                                                     | 1       |

| Reset         |            | F                                                                                       | 1       |

| /RESET        | I          | Reset input. Low enable                                                                 | 1       |

| I/O           |            | Trebes in pass 2011 enable                                                              |         |

| P54 ~P57      | I/O PORT5  | PORT5 can be INPUT or OUTPUT port each bit                                              | 4       |

|               |            | And P54 ~ P57 are shared with segment signal                                            | 1       |

| P60 ~P67      | I/O PORT6  | PORT6 can be INPUT or OUTPUT port each bit                                              | 8       |

| ,             |            | P66, P67 and P65 have open drain function                                               | -       |

| P70 ~P77      | I/O PORT7  | PORT7 can be INPUT or OUTPUT port each bit                                              | 8       |

| 1,0 1,,       | 1,010111   | PORT7 have internal pull high function                                                  |         |

|               |            | P70/INT0 ~ P73/INT3 can be interrupt signals                                            |         |

|               |            | P75, P74 is shared with TIP and RING                                                    | 1       |

| P80 ~ P83     | I/O PORT8  | PORT 8 can be INPUT or OUTPUT port each bit                                             | 4       |

|               |            | And P80 ~ P83 are shared with segment signal.                                           | 1       |

| P94 ~ P97     | I/O PORT9  | PORT 9 can be INPUT or OUTPUT port each bit                                             | 4       |

| / ,           |            | P96, P97 have wake-up function.                                                         | 1       |

| PAD Option    |            | 1                                                                                       |         |

| /POVD         | I          | Power on voltage detector reset                                                         | 2       |

| ERICen        | I          | ERIC mode enable                                                                        | 2       |

|               | l •        | Little mode endore                                                                      |         |

<sup>\*</sup> This specification are subject to be changed without notice. 7

When /RESET pulls to 12V, the system will be in programming mode. Then writer can program the code ROM inside the system.

| No. | System Pin Name | OTP writer Pin Name | Description                                      |

|-----|-----------------|---------------------|--------------------------------------------------|

| 4   | VDD             | VDD                 | VDD power                                        |

| 55  | /RESET          | VPP                 | High voltage activation pin                      |

| 61  | P7[7]           | DINCK               | Internal ssyetm clock                            |

| 60  | P7[6]           | ACLK                | External system clock                            |

| 63  | P7[5]           | PGMB                | When PGMB=0, writing action of OTP ROM activates |

| 62  | P7[4]           | OEB                 | When OE=0, reading action of OTP ROM activates.  |

| 59  | P7[3]           | DATA                | Serial data I/O                                  |

| 21  | VSS             | GND                 | Ground power                                     |

# VII. Functional Descriptions

# VII.1 Operational Registers

Register configuration 1:

| A 11          | D DA CE                                                | IOC I                                                      | PAGE                                                                    |

|---------------|--------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------|

| Addr          | R PAGE registers                                       | IOC PAGE0                                                  | IOC PAGE1                                                               |

| 00            | INDA<br>Indirect addressing                            |                                                            |                                                                         |

| 01            | TCCD<br>TCC data                                       |                                                            |                                                                         |

| 02            | PC<br>Program counter                                  |                                                            |                                                                         |

| 03            | STA IOC Page, Tone 1, 2 power control, Status          |                                                            |                                                                         |

| 04            | RBSR<br>Register bank, RSR                             |                                                            |                                                                         |

| 05            | PSIOD<br>PORT5 I/O data, Program ROM page              | PSIOC<br>PORT5 I/O control,                                |                                                                         |

| 06            | P6IOD<br>PORT6 I/O data                                | PORT6 I/O control                                          |                                                                         |

| 07            | P7IOD<br>PORT7 I/O data                                | P7IOC<br>PORT7 I/O control                                 |                                                                         |

| 08            | P8IOD<br>PORT8 I/O date                                | PSIOC PORT8 I/O control                                    |                                                                         |

| 09            | PORT9 I/O data                                         | PORT9 I/O control                                          |                                                                         |

| 0A            | MCUC<br>CPU power saving, PLL, Main clock<br>selection | PSW (P8 low nibble, P5) switch, LCD bias, Key scan control | <b>DEDC</b> LCD power saving, Low battery detect, DED control           |

| 0B            | <b>DEDO</b> Green tone, DED output, CID RAM bank       | LCDA<br>LCD RAM address                                    | CN1D<br>Counter 1 data                                                  |

| 0C            | RAMA<br>CID RAM address                                | LCDD<br>LCD RAM data                                       | CN2D<br>Counter 2 data                                                  |

| 0D            | RAMD<br>CID RAM data                                   | TONE1C TONE1 control                                       | P7PHC<br>PORT7 pull high                                                |

| 0E            | WUPC<br>Wake-up control, LCD control                   | TONE2 control                                              | CNPSC Open Drain Control, CNT1,2 CLK source, CNT1,2 prescaler, LCD mode |

| 0F            | INTF<br>Interrupt flag                                 | INTM<br>Interrupt mask                                     |                                                                         |

| 10<br>:<br>1F | 16 bytes<br>Common registers                           |                                                            |                                                                         |

| 20<br>:<br>3F | Bank0~Bank2² Common registers (32x8 for each bank)     |                                                            |                                                                         |

Ps. 1. Register 20~3F has bank0~bank2 only. The bank3 doesn't exist and cannot access it.

<sup>\*</sup> This specification are subject to be changed without notice.

#### Register Configuration 2:

| Addr. | R      | IOC  | Register                 |              |       |         | Register | hit name  |        |        |        | Power on             |

|-------|--------|------|--------------------------|--------------|-------|---------|----------|-----------|--------|--------|--------|----------------------|

| Addi. |        | 1    | Name                     | Bit 7        | Bit 6 | Bit 5   | Bit 4    | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Reset val.           |

| 00    | page   | page | INDA                     | (Indirect ac |       |         | DIL 4    | DII 3     | DIL Z  | DILI   | Dit 0  | Reset vai.           |

| 01    | X      |      | TCCD                     | (TCC data    |       | ter)    |          |           |        |        |        |                      |

| 02    | X      |      | PC PC                    | (Program c   |       |         |          |           |        |        |        |                      |

| 03    | X      |      | STA                      |              |       | P TONE1 | т        | Р         | Z      | DC     | С      | 000xxxxx             |

| 03    | X<br>X |      | RBSR                     | RB1          | RB0   | RSR5    | RSR4     | RSR3      | RSR2   | RSR1   | RSR0   | 000xxxxx<br>00xxxxxx |

| 05    |        |      | P5IOD                    | P57          | P56   | P55     | P54      | PS3       | PS2    | PS1    | PS0    | xxxx0000             |

| 03    | X      | 0    | P5IOC                    | IOC57        | IOC56 | IOC55   | IOC54    | 0         | 0      | 0      | 0      | 11110000             |

|       |        | 1    |                          | 0            | 0     | 0       | 0        | 0         | 0      | 0      | 0      | 00000000             |

| 06    | Х      | 1    | (non-existence)<br>P6IOD | P67          | P66   | P65     | P64      | P63       | P62    | P61    | P60    |                      |

| 00    | Х      | 0    | P6IOC                    | IOC67        | IOC66 | IOC65   | IOC64    | IOC63     | IOC63  | IOC61  | IOC60  | 11111111             |

|       |        | 1    |                          | 0            | 0     | 0       | 0        | 0         | 0      | 0      | 0      | 00000000             |

| 07    |        | 1    | (non-existence)<br>P7IOD | P77          | P76   | P75     | P74      | P73       | P72    | P71    | P70    |                      |

| 07    | X      | 0    | P7IOD<br>P7IOC           | IOC77        | IOC76 | IOC75   | IOC74    | IOC73     | IOC73  | IOC71  | IOC70  | 11111111             |

|       |        | 1    |                          | 0            | 0     | 0       | 0        | 0         | 0      | 0      | 0      | 00000000             |

| 08    |        | 1    | (non-existence)<br>P8IOD | 0            | 0     | 0       | 0        | P83       | P82    | P81    | P80    | 00000000<br>0000xxxx |

| 08    | X      | 0    | P8IOC                    | 0            | 0     | 0       | 0        | IOC83     | IOC83  | IOC81  | IOC80  | 0000XXXX             |

|       |        | 1    |                          | 0            | 0     | 0       | 0        | 0         | 0      | 0      | 0      | 000001111            |

| 09    |        | 1    | (non-existence)<br>P9IOD | P97          | P96   | P95     | P94      | 0         | 0      | 0      | 0      | xxxx0000             |

| 09    | X      | 0    | P9IOC                    | IOC97        | IOC96 | IOC95   | IOC94    | 0         | 0      | 0      | 0      | 11110000             |

|       |        | 1    |                          | 0            | 0     | 0       | 0        | 0         | 0      | 0      | 0      | 00000000             |

| 0A    |        | 1    | MCUC                     | IDLE         | ENPLL | CLK2    | CLK1     | 0         | 0      | 0      | 0      | 00000000             |

| UA    | X      | 0    | PSW                      | BIASS        | 0     | P8SL    | P5S      | BIAS3     | BIAS2  | BIAS1  | SC     | 00000000             |

|       |        | 1    | DEDC .                   | 0            | 4CDR  | 8CR     | Low BAT  | /LPD      | EGCLK  | DEDPWR | DEDTHD | 000x0000             |

| 0B    | х      | 1    | DEDO<br>DEDO             | EDGE         | GTONE | 0       | 0        | DEDD      | 0      | 0<br>0 | CALL 1 | 000x0000             |

| UB    | X      | 0    | LCDA                     | 0            | 0     | LCDA5   | LCDA4    | LCDA3     | LCDA2  | LCDA1  | LCDA0  | 00000000             |

|       |        | 1    | CN1D                     | CN17         | CN16  | CN15    | CN14     | CN13      | CN12   | CN11   | CN10   | 00000000             |

| 0C    | Х      | 1    | RAMA                     | CIDA7        | CIDA6 | CIDA5   | CIDA4    | CIDA3     | CIDA2  | CIDA1  | CIDA0  | 00000000             |

| UC    | A      | 0    | LCDD                     | LCDD7        | LCDD6 | LCDD5   | LCDD4    | LCDD3     | LCDD2  | LCDD1  | LCDD0  |                      |

|       |        | 1    | CN2D                     | CN27         | CN26  | CN25    | CN24     | CN23      | CN22   | CN21   | CN20   | 00000000             |

| 0D    | х      | 1    | RAMD                     | CIDD7        | CIDD6 | CIDD5   | CIDD4    | CIDD3     | CIDD2  | CIDD1  | CIDD0  | XXXXXXXX             |

| UD    | Λ      | 0    | TONE1C                   | T17          | T16   | T15     | T14      | T13       | T12    | T11    | T10    | 00000000             |

|       |        | 1    | P7PHC                    | PH7          | PH6   | PH5     | PH4      | PH3       | PH2    | PH1    | PH0    | 00000000             |

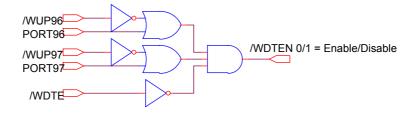

| 0E    | Х      | 1    | WUPC                     | 0            | /WDTE | /WUP97  | /WUP96   | 0         | LCD C2 | LCD C1 | /WUEDD | 00000000             |

| UE    | A      | 0    | TONE2C                   | T27          | T26   | T25     | T24      | T23       | T22    | T21    | T20    | 00000000             |

|       |        | 1    | CNPSC                    | OP77         | OP76  | C2S     | C1S      | PSC2      | PSC1   | PSC0   | LCDM   | 00000000             |

| 0F    | Х      | 1    | INTF                     | EDD          | 0     | CNT2    | CNT1     | INT2/INT3 | INT1   | INT0   | TCIF   | 00000000             |

| OI.   | Λ      | 0    | INTM                     | EDD          | 0     | CNT2    | CNT1     | INT2/INT3 | INT1   | INTO   | TCIF   | 00000000             |

|       |        | 1    |                          | 0            | 0     | 0       | 0        | 0         | 0      | 0      | 0      | 00000000             |

|       |        | 1    | (non-existence)          | U            | U     | U       | U        | U         | U      | U      | U      | 00000000             |

# VII.2 Operational Register Detail Description

#### R0 (INDA: Indirect addressing register)

R0 is not a physically implemented register. It is useful as indirect addressing pointer. Any instruction using R0 as register actually accesses data pointed by the RAM Select Register (R4).

## R1 (TCCD: TCC data buffer)

Increased by an external signal edge applied to TCC, or by the instruction cycle clock. Written and read by the program as any other register. TCC has no reload function.

#### R2 (PC: Program counter)

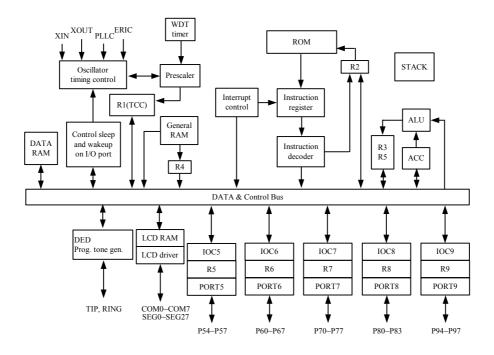

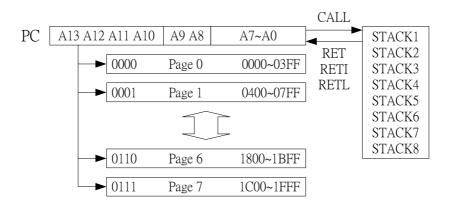

The structure is depicted in Fig.4

Generates  $8k \times 13bit$  internal ROM addresses to the relative programming instruction codes.

"JMP" instruction allows the direct loading of the low 10 program counter bits.

"CALL" instruction loads the low 10 bits of the PC, PC+1, and then pushes into the stack.

"RET" ("RETL k", "RETI") instruction loads the program counter with the contents at the top of stack.

"MOV R2,A" allows the loading of an address from the A register to the PC, and the ninth and tenth bits are cleared to "0".

<sup>\*</sup> This specification are subject to be changed without notice.

"ADD R2,A" allows a relative address be added to the current PC, and contents of the ninth and tenth bits are cleared to "0".

"TBL" allows a relative address be added to the current PC, and contents of the ninth and tenth bits don't change. The most significant bit (A10~A13) will be loaded with the content of bit PS0~PS3 in the status register (R5) upon the execution of a "JMP", "CALL", "ADD R2,A", or "MOV R2,A" instruction.

Fig.4 Program counter organization

## R3 (STA: IOC Page, Tone1, 2 power control, Status register)

| ĺ | 7     | 6       | 5       | 4   | 3   | 2     | 1     | 0     |

|---|-------|---------|---------|-----|-----|-------|-------|-------|

| Ī | PAGE  | P_TONE2 | P_TONE1 | T   | P   | Z     | DC    | С     |

| Ī | R/W-0 | R/W-0   | R/W-0   | R-x | R-x | R/W-x | R/W-x | R/W-x |

Bit 0 (C): Carry flag

Bit 1 (DC): Auxiliary carry flag

Bit 2 (Z): Zero flag

Bit 3 (P): Power down bit.

Set to 1 during power on or by a "WDTC" command and reset to 0 by a "SLEP" command.

Bit 4 (T): Time-out bit

Set to 1 by the "SLEP" and "WDTC" command, or during power up and reset to 0 by WDT timeout.

| Event                         | T | P | Remark         |

|-------------------------------|---|---|----------------|

| WDT wake up from sleep mode   | 0 | 0 |                |

| WDT time out (not sleep mode) | 0 | 1 |                |

| /RESET wake up from sleep     | 1 | 0 |                |

| Power up                      | 1 | 1 |                |

| Low pulse on /RESET           | X | X | x : don't care |

Bit 5 (P TONE1): Power control bit of Tone generator 1

User can use this bit to power on the tone generator 1

Bit 6 (P TONE2): Power control bit of Tone generator 2

User can use this bit to power on the tone generator 2

Ps. Tone frequency is controlled by IOCD and IOCE.

| R3(6,5) | Tone Generator 2 | Tone Generator 1 |

|---------|------------------|------------------|

| 00      | Power off        | Power off        |

| 01      | Power off        | Power on         |

| 10      | Power on         | Power off        |

| 11      | Power on         | Power on         |

Bit 7 (PAGE): change IOCB ~ IOCE to another Page

0/1 → PAGE0/PAGE1

<sup>\*</sup> This specification are subject to be changed without notice.

## R4 (RBSR: RAM bank, RAM selection for common registers $R20 \sim R3F$ )

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RB1   | RB0   | RSR5  | RSR4  | RSR3  | RSR2  | RSR1  | RSR0  |

| R/W-0 | R/W-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

Bit 0 ~ Bit 5 (RSR0 ~ RSR5): Indirect addressing for common registers R20 ~ R3F

RSR bits are used to select up to 32 registers (R20 to R3F) in the indirect addressing mode.

Bit 6 ~ Bit 7 (RB0 ~ RB1): Bank selection bits for common registers R20 ~ R3F

These selection bits are used to determine which bank is activated among the 3 banks for 32 registers (R20 to R3F). *The bank 3 doesn't exist and cannot access.*

| (RB1,RB0) | Bank # for R20 ~ R3F |

|-----------|----------------------|

| 00        | Bank 0               |

| 01        | Bank 1               |

| 10        | Bank 2               |

| 11        | N/A                  |

## R5 (P5IOD: PORT5 I/O data, Program ROM page selection)

| 7   | 6   | 5   | 4   | 3   | 2     | 1     | 0     |

|-----|-----|-----|-----|-----|-------|-------|-------|

| P57 | P56 | P55 | P54 | PS3 | PS2   | PS1   | PS0   |

| R/W | R/W | R/W | R/W | R-0 | R/W-0 | R/W-0 | R/W-0 |

Bit  $0 \sim 3$  (PS0  $\sim$  PS3) : Page selection bits

They should be set before JMP or CALL instruction.

Page select bits

| PS3 | PS2 | PS1 | PS0 | Program memory page (Address) |

|-----|-----|-----|-----|-------------------------------|

| 0   | 0   | 0   | 0   | Page 0                        |

| 0   | 0   | 0   | 1   | Page 1                        |

| 0   | 0   | 1   | 0   | Page 2                        |

| 0   | 0   | 1   | 1   | Page 3                        |

| :   | :   | •   | :   | :                             |

| :   | :   | :   | :   | :                             |

| 0   | 1   | 1   | 0   | Page 6                        |

| 0   | 1   | 1   | 1   | Page 7                        |

User can use PAGE instruction to change page and maintain program page by user. Otherwise, user can use far jump (FJMP) or far call (FCALL) instructions to program user's code. EMC's complier maintains the program page. It will change user's program by inserting instructions within program.

Bit 3 is always 0 and can't be set.

Bit  $5 \sim 7 \text{ (P54} \sim \text{P57)}$ : 4-bit PORT5(4  $\sim 7$ ) I/O data register

#### R6 (P6IOD: PORT6 I/O data)

|   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|-----|

|   | P67 | P66 | P65 | P64 | P63 | P62 | P61 | P60 |

| ſ | R/W |

Bit  $0 \sim \text{Bit } 7 \text{ (P60} \sim \text{P67)}$ : 8-bit PORT6(0 $\sim$ 7) I/O data register User can use IOC register to define input or output each bit.

#### R7 (P7IOD: PORT7 I/O data)

|   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|-----|

|   | P77 | P76 | P75 | P74 | P73 | P72 | P71 | P70 |

| Γ | R/W |

Bit  $0 \sim \text{Bit } 7 \text{ (P70} \sim \text{P77)}$ : 8-bit PORT7 $(0 \sim 7)$  I/O data register

<sup>\*</sup> This specification are subject to be changed without notice.

User can use IOC register to define input or output each bit.

P74~P75 are shared with TIP and RING. When the bit DEDPWR is set, P74~P75 must be set as input port. Otherwise, P74~P75 and DED function will collide and not work as normal.

#### R8 (P8IOD: PORT8 I/O data)

| 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|-----|-----|-----|-----|-------|-------|-------|-------|

| 0   | 0   | 0   | 0   | P83   | P82   | P81   | P80   |

| R-0 | R-0 | R-0 | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

Bit  $0 \sim \text{Bit } 3 \text{ (P80} \sim \text{P83)}$ : 4-bit PORT8(0~3) I/O data register

Bit  $4 \sim Bit 7$ : unused

User can use IOC register to define input or output each bit.

#### R9 (P9IOD: PORT9 I/O data)

| 7     | 6     | 5     | 4     | 3   | 2   | 1   | 0   |

|-------|-------|-------|-------|-----|-----|-----|-----|

| P97   | P96   | P95   | P94   | 0   | 0   | 0   | 0   |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 |

Bit  $0 \sim Bit 3$ : unused

Bit  $4 \sim$  Bit 7 (P94  $\sim$  P97) : 4-bit PORT9(4 $\sim$ 7) I/O data register

User can use IOC register to define input or output each bit.

# RA (MCUC: CPU power saving, PLL, Main clock selection)

| 7     | 6     | 5     | 4     | 3   | 2   | 1   | 0   |

|-------|-------|-------|-------|-----|-----|-----|-----|

| IDLE  | ENPLL | CLK2  | CLK1  | 0   | 0   | 0   | 0   |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 |

Bit  $0 \sim Bit 3$ : unused

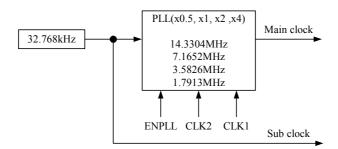

Bit  $4 \sim 5$  (CLK1  $\sim$  CLK2): Main clock selection bits.

User can choose the main clock by setting CLK1 and CLK2. All the clock selections are list below. Please notice that the configuration of main clock is different in P803 mode and 805C mode. When changing the main clock, insert some NOP instruction for system stability.

| ENPLL   | CPU'      | s clock     | (CLK2,CLK1) | MAII      | N clock     |

|---------|-----------|-------------|-------------|-----------|-------------|

| LIVI EE | P803A     | 805C        | (CLK2,CLK1) | P803A     | 805C        |

| 0       | 32.768kHZ | 32.768kHZ   | (x,x)       | X         | X           |

| 1       | 1.7913MHz | 447.8293kHz | (0,0)       | 1.7913MHz | 447.8293kHz |

| 1       | 14.331MHz | 895.6587kHz | (0,1)       | 14.331MHz | 895.6587kHz |

| 1       | 7.1652MHz | 7.1653MHz   | (1,0)       | 7.1652MHz | 7.1653MHz   |

| 1       | 3.5826MHz | 3.5826MHz   | (1,1)       | 3.5826MHz | 3.5826MHz   |

When in ERIC mode, CLK1~2 will be masked. The main clock is generated by the frequency of ERIC oscillation.

Bit 6 (ENPLL): (read/write) PLL enable/disable control

1/0 → enable/disable

The relation between 32.768kHz and main clock can see Fig.5

When in ERIC mode, ENPLL will enforce to 0. The main clock is generated by the frequency of ERIC oscillation. The sub clock is divided from the main clock and can be scale by different factor.

Bit 7 (IDLE): Idle mode/sleep mode selection bit

1/0 → Idle mode/sleep mode.

This bit will decide SLEP instruction which mode to go.

These two modes can be waked up by TCC clock, Watch Dog timer (WDT), PORT96~97, Energy Detector output, PORT70~73 and run from "SLEP" next instruction.

$P70 \sim P73$  's wakeup function is controlled by IOCF P0(1,2,3) and ENI instruction.

P70 's wakeup signal is a rising edge or falling edge defined by CONT REGISTER bit7.

Port96, Port97, Port71, Port72 and Port73 's wake-up pattern is a falling edge-triggering signal.

<sup>\*</sup> This specification are subject to be changed without notice.

| Energy Detector wakeu | p and interrupt signal | can be controlled b | v RB bit 7 ( | EDGE). |

|-----------------------|------------------------|---------------------|--------------|--------|

|                       |                        |                     |              |        |

|               | SLEEP mode    | IDLE mode          | GREEN mode    | NORMAL mode   |  |

|---------------|---------------|--------------------|---------------|---------------|--|

| Wakeup signal | RA(7,6)=(0,0) | RA(7,6)=(1,0)      | RA(7,6)=(x,0) | RA(7,6)=(x,1) |  |

|               | +SLEP         | + SLEP             | No SLEP       | No SLEP       |  |

| TCC time out, |               | Wake-up            |               |               |  |

| EDD           | X             | + Interrupt        | Interrupt     | Interrupt     |  |

| EDD           |               | + Next instruction |               |               |  |

| WDT time out  | RESET         | Wake-up            | RESET         | RESET         |  |

| WD1 tille out | KESEI         | + Next instruction | KESE I        |               |  |

| Port96, 97    | RESET         | Wake-up            | ••            |               |  |

| F01190, 97    | KESEI         | + Next instruction | X             | X             |  |

|               |               | Wake-up            |               |               |  |

| PORT70~73     | RESET         | + Interrupt        | Interrupt     | Interrupt     |  |

|               |               | + Next instruction |               |               |  |

Fig.5 The relation between 32.768kHz and Main clock

#### RB (DEDO: Green tone, DED output, CID RAM banks)

| 7     | 6     | 5   | 4   | 3    | 2   | 1   | 0      |

|-------|-------|-----|-----|------|-----|-----|--------|

| EDGE  | GTONE | 0   | 0   | DEDD | 0   | 0   | CALL_1 |

| R/W-0 | R/W-0 | R-0 | R-0 | R-x  | R-0 | R-0 | R/W-0  |

Bit 0 (CALL\_1): 2 blocks of CALLER ID RAM area

User can use 0.5K CID RAM with RC RAM address.

Bit  $1 \sim 2 = 0$ : unused

Bit 3 (DEDD): Output data of Energy Detector (DED)

If input signal from TIP pin and RING pin to Energy Detector is over the threshold level setting at IOCA PAGE1 bit 0(DEDTHD), the DED will extract the zero-crossing pulse waveform corresponding to input signal.

Bit  $4 \sim Bit 5$ : unused

Bit 6 (GTONE): Green tone for programming tone generator

0/1 → disable/enable green tone function

When this function is enabled, either R3 bit5(P\_TONE1) or R3 bit6(P\_TONE2) is set then PLL is auto-on. At this time, TONE1 or TONE2 can be used no matter what MCU works on 32.768kHz or normal mode. When this function is disabled, TONE1 or TONE2 can only work on normal mode.

Bit 7 (EDGE): Wake-up and interrupt trigging edge control of Energy Detector output

0/1 → Falling edge trig. / Rising edge & Falling edge trig.

#### RC (RAMA: CID RAM address)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CIDA7 | CIDA6 | CIDA5 | CIDA4 | CIDA3 | CIDA2 | CIDA1 | CIDA0 |

| R/W-0 |

Bit 0 ~ Bit 7 (CIDA0 ~ CIDA7): CID RAM address

User can select Caller ID RAM address from 0 to 255.

<sup>\*</sup> This specification are subject to be changed without notice.

#### RD (RAMD: CID RAM data buffer)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CIDD7 | CIDD6 | CIDD5 | CIDD4 | CIDD3 | CIDD2 | CIDD1 | CIDD0 |

| R/W   |

Bit  $0 \sim \text{Bit } 7 \text{ (CIDD0} \sim \text{CIDD7})$ : CID RAM data register.

#### RE (WUPC: Wake-up control, LCD control)

| 7   | 6     | 5      | 4      | 3   | 2      | 1      | 0      |

|-----|-------|--------|--------|-----|--------|--------|--------|

| 0   | /WDTE | /WUP97 | /WUP96 | 0   | LCD_C2 | LCD_C1 | /WUEDD |

| R-0 | R/W-0 | R/W-0  | R/W-0  | R-0 | R/W-0  | R/W-0  | R/W-0  |

Bit 0 (/WUEDD): Wake-up control of Energy Detector (DED) output data

1/0 → enable/disable

Bit 1 ~ Bit 2 (LCD\_C1 ~ LCD\_C2) : LCD display enable or blanking. The display duty change must set the (LCD\_C2,LCD\_C1) to (0,0).

| (LCD_C2,LCD_C1) | .CD_C2,LCD_C1) LCD Display Control |              |            |  |

|-----------------|------------------------------------|--------------|------------|--|

| (0,0)           | Disable (turn off LCD)             | (*1)<br>(*1) | 1/4<br>1/4 |  |

| (0,1)           | Blanking                           | •            |            |  |

| (1,1)           | LCD display enable                 | :            |            |  |

\*1. 1/8 or 1/4 duty depends on IOCE PAGE1 bit0 (LCDM)

Bit 3: unused

Bit 4 (/WUP96): PORT9 bit6 wake-up control, 1/0 → enable/disable Bit 5 (/WUP97): PORT9 bit7 wake-up control, 1/0 → enable/disable Bit 6 (/WDTE): Watchdog timer enable control, 1/0 → enable/disable

Fig.6 Wake up function and control signal

Bit 7: unused

#### RF (INTF: Interrupt status register)

| 7     | 6   | 5     | 4     | 3         | 2     | 1     | 0     |

|-------|-----|-------|-------|-----------|-------|-------|-------|

| EDD   | 0   | CNT2  | CNT1  | INT2/INT3 | INT1  | INT0  | TCIF  |

| R/W-0 | R-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

Bit 0 (TCIF): TCC timer overflow interrupt flag

It will be set when TCC timer is overflow.

Bit 1 (INT0): External INT0 pin interrupt flag

It can be used when PORT70 is set to input port.

Bit 2 (INT1): External INT1 pin interrupt flag

It can be used when PORT71 is set to input port.

Bit 3 (INT2/INT3): external INT2 and INT3 pin interrupt flag It can be used when PORT72 or PORT73 is set to input port.

Bit 4 (CNT1): 8 bit Counter1 overflow interrupt flag.

It will be set when Counter1 is overflow.

<sup>\*</sup> This specification are subject to be changed without notice.

Bit 5 (CNT2): 8 bit Counter2 overflow interrupt flag.

It will be set when Counter2 is overflow.

Bit 6: unused

Bit 7 (EDD): Interrupt flag of Energy Detector (DED) output data

"1" means interrupt request and "0" means non-interrupt. INT0~INT3 interrupts are edge triggering (falling edge or rising edge) which can be set by CONT bit 7 (INT\_EDGE). Interrupt edge control of DED output data is set by RB bit 7(EDGE). Also see corresponding interrupt mask in IOCF register. User can read and clear.

#### R10~R3F (General Purpose Register)

R10~R1F: common registers

Care must be taken while programming. When R4 (bit7,bit6) = (1,1), common registers  $0x10 \sim 0x1F$  cannot be read or written otherwise program maybe go to dead lock. ICE cannot reflect this problem. This is incompatible situation between mask and ICE.

R20~R3F (Banks 0~2): common registers

These common are bank-controlled registers with bank 0,1,2. The bank 3 doesn't exist and cannot access.

# VII.3 Special Purpose Registers

#### A (Accumulator)

Internal data transfer, or instruction operand holding It's not an addressable register.

#### CONT (Control Register)

| 7        | 6     | 5     | 4   | 3     | 2     | 1     | 0     |

|----------|-------|-------|-----|-------|-------|-------|-------|

| INT_EDGE | INT   | TS    | 0   | PAB   | PSR2  | PSR1  | PSR0  |

| R/W-1    | R/W-0 | R/W-1 | R-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

Bit 0 ~ Bit 2 (PSR0 ~ PSR2): TCC/WDT prescaler bits

| PSR2 | PSR1 | PSR0 | TCC rate | WDT rate |

|------|------|------|----------|----------|

| 0    | 0    | 0    | 1:2      | 1:1      |

| 0    | 0    | 1    | 1:4      | 1:2      |

| 0    | 1    | 0    | 1:8      | 1:4      |

| 0    | 1    | 1    | 1:16     | 1:8      |

| 1    | 0    | 0    | 1:32     | 1:16     |

| 1    | 0    | 1    | 1:64     | 1:32     |

| 1    | 1    | 0    | 1:128    | 1:64     |

| 1    | 1    | 1    | 1:256    | 1:128    |

Bit 3(PAB): Prescaler assignment bit

0/1 **→** TCC/WDT

Bit 4: unused

Bit 5(TS): TCC signal source

- 0 → Instruction clock

- 1 → 16.384kHz

Instruction clock = MCU clock/2, Refer to RA Bit  $4 \sim$  Bit 6 for PLL and Main clock selection. See Fig.5. In ERIC mode, the instruction clock is the half of frequency of ERIC oscillation. When TS bit sets 1, the clock is the half of sub frequency divided from the frequency of ERIC oscillation.

Bit 6 (INT): INT enable flag

- 0 → Interrupt masked by DISI or hardware interrupt

- 1 → Interrupt enabled by ENI/RETI instructions

Bit 7(INT\_EDGE): interrupt edge type of P70

- 0 > P70 's interruption source is a rising edge signal and falling edge signal.

- 1 → P70 's interruption source is a falling edge signal.

<sup>\*</sup> This specification are subject to be changed without notice.

CONT register is readable (CONTR) and writable (CONTW).

## IOC5 (P5IOC: PORT5 I/O control)

|   | 7     | 6     | 5     | 4     | 3   | 2   | 1   | 0   |

|---|-------|-------|-------|-------|-----|-----|-----|-----|

|   | IOC57 | IOC56 | IOC55 | IOC54 | 0   | 0   | 0   | 0   |

| Ī | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R-0 | R-0 | R-0 | R-0 |

Bit 0 ~ Bit 3: unused

Bit 4 ~ 7 (IOC54 ~ IOC57): PORT5(4~7) I/O direction control register

0 → put the relative I/O pin as output

1 → put the relative I/O pin into high impedance

#### IOC6 (P6IOC: PORT6 I/O control)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC67 | IOC66 | IOC65 | IOC64 | IOC63 | IOC62 | IOC61 | IOC60 |

| R/W-1 |

Bit  $0 \sim \text{Bit } 7 \text{ (IOC60} \sim \text{IOC67)}$ : PORT6(0~7) I/O direction control register

0 → put the relative I/O pin as output

1 → put the relative I/O pin into high impedance

#### IOC7 (P7IOC: PORT7 I/O control)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IOC77 | IOC76 | IOC75 | IOC74 | IOC73 | IOC72 | IOC71 | IOC70 |

| R/W-1 |

Bit  $0 \sim \text{Bit } 7 \text{ (IOC70} \sim \text{IOC77)}$ : PORT7 $(0 \sim 7)$  I/O direction control register

0 → put the relative I/O pin as output

1 > put the relative I/O pin into high impedance

P74~P75 are shared with TIP and RING. When the bit DEDPWR is set, P74~P75 must be set as input port. Otherwise, P74~P75 and DED function will collide and not work as normal.

## IOC8 (P8IOC: PORT8 I/O control)

| 7   | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|-----|-----|-----|-----|-------|-------|-------|-------|

| 0   | 0   | 0   | 0   | IOC83 | IOC82 | IOC81 | IOC80 |

| R-0 | R-0 | R-0 | R-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

Bit 0 ~ Bit 3 (IOC80 ~ IOC83): PORT8(0~3) I/O direction control register

0 → put the relative I/O pin as output

1 > put the relative I/O pin into high impedance

Bit  $4 \sim \text{Bit } 7$ : unused

## IOC9 (P9IOC: PORT9 I/O control)

|   | 7     | 6     | 5     | 4     | 3   | 2   | 1   | 0   |

|---|-------|-------|-------|-------|-----|-----|-----|-----|

| I | OC97  | IOC96 | IOC95 | IOC94 | 0   | 0   | 0   | 0   |

| F | R/W-1 | R/W-1 | R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 |

Bit 0 ~ Bit 3: unused

Bit 4 ~ Bit 7 (IOC94 ~ IOC97): PORT9(4~7) I/O direction control register

0 → put the relative I/O pin as output

1 > put the relative I/O pin into high impedance

<sup>\*</sup> This specification are subject to be changed without notice.

#### IOCA (PSW, DEDC)

#### PAGE0 (PSW: PORT8,5 switch, LCD bias, key scan)

| 7     | 6   | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-----|-------|-------|-------|-------|-------|-------|

| BIASS | 0   | P8SL  | P5S   | BIAS3 | BIAS2 | BIAS1 | SC    |

| R/W-0 | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

Bit 0 (SC): key scan function control

#### 0/1 → disable/enable

Once you enable this bit, all of the LCD signal will have a low pulse during a common period. This pulse has 30us width. Please use the following procedure to implement the key scan function:

- 1. Set PORT7 as input port

- 2. Set IOCD PAGE1 to enable PORT7 pull high function

- 3. Enable key scan function

- 4. Once push a key. Set RA bit 6 to enable PLL (CPU will run in the normal mode)

- 5. LCD and disable key scan function

- 6. Set P5S =0 or/and P8SL=0. PORT5 or/and PORT8 sent probe signal to PORT7 and read PORT7. Get the key.

- 7. Note!! A probe signal should be delay an instruction at least to another probe signal.

- 8. Set P5S =1 or/and P8SL=1. PORT5 or/and PORT8 as LCD signal

Fig.7. Key scan circuit

Bit  $1 \sim 3$  (BIAS1  $\sim$  BIAS3): LCD bias control used to choose LCD operation voltage.

| (BIAS3,BIAS2,BIAS1) | Vop     | VDD=5V |

|---------------------|---------|--------|

| (0,0,0)             | 0.60VDD | 3V     |

| (0,0,1)             | 0.66VDD | 3.3V   |

| (0,1,0)             | 0.74VDD | 3.7V   |

| (0,1,1)             | 0.82VDD | 4.1V   |

| (1,0,0)             | 0.87VDD | 4.35V  |

| (1,0,1)             | 0.93VDD | 4.65V  |

| (1,1,0)             | 0.96VDD | 4.8V   |

| (1,1,1)             | 1.00VDD | 5V     |

Bit 4 (P5S): PORT5 nibble switch

0/1 → normal I/O port/SEGMENT output

Bit 5 (P8SL): port8 low nibble switch

<sup>\*</sup> This specification are subject to be changed without notice.

0/1 → normal I/O port P80~P83/SEGMENT output SEG16~SEG19

Bit 6: unused

Bit 7 (BIASS) : Bias Select,  $0/1 \rightarrow 1/4$  bias / 1/3 bias

#### PAGE1 (DEDC: LCD power saving, Low battery detect, DED control)

| 7   | 6   | 5     | 4   | 3     | 2     | 1      | 0      |

|-----|-----|-------|-----|-------|-------|--------|--------|

| 0   | 0   | CR    | 0   | (RES) | EGCLK | DEDPWR | DEDTHD |

| R-0 | R-0 | R/W-0 | R-x | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

Bit 0 (DEDTHD): The minimum detection threshold of Dual Input Energy Detector (DED)

0/1 **→** -45dBm/-30dBm

Bit 1 (DEDPWR): Power control of Energy Detector (DED)

$0/1 \rightarrow Power off/Power on$

Bit 2 (EGCLK): Operating clock for Energy Detector (DED)

0/1 **→** 32.768kHz/3.5826MHz

This bit is used to select operating clock for Energy Detector (DED). When this bit is set to "1", the PLL is also enabled regardless of RA bit 6 (ENPLL) value. At this time, the Energy detector works at high frequency mode. When this bit is set to "0", the Energy Detector works at sub frequency mode. The difference between high frequency mode and sub frequency is as follows.

| ENPLL | EGCLK | Energy Detector status    | PLL status      |  |

|-------|-------|---------------------------|-----------------|--|

|       | 0     | 32.768kHz operating clock | PLL is disabled |  |

| 0     | 1     | Normal detection          | PLL is enabled  |  |

|       | 1     | Small current consumption | PLL is enabled  |  |

|       |       | 3.5826MHz operating clock |                 |  |

| 1     | X     | Accurate detection        | PLL is enabled  |  |

|       |       | More current consumption  |                 |  |

Ps. "x" means don't care

In ERIC mode, the PLL will be off. When EGCLK is 1, the operating clock of Energy Detector is the frequency of ERIC oscillation, otherwise, the operating clock is sub frequency divided from ERIC oscillation.

Bit 3 (RES): Reserved bit for factory test only. It has to be clear to zero or remain default value.

Bit 4: unused

Bit 5 (CR): LCD DC current saving

0/1 → normal DC current drive/half DC current drive

When this bit is set to 1, the LCD driving ability will be reducing to the half than normal current drive but it can save power.

Bit 6~7: unused

#### IOCB (LCDA, CN1D)

#### PAGE0 (LCDA: LCD RAM address)

| 7   | 6   | 5   | 4     | 3     | 2     | 1     | 0     |

|-----|-----|-----|-------|-------|-------|-------|-------|

| 0   | 0   | 0   | LCDA4 | LCDA3 | LCDA2 | LCDA1 | LCDA0 |

| R-0 | R-0 | R-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

Bit 0 ~ Bit 4 (LCDA0 ~ LCDA4): LCD RAM address

The LCD display data is stored in the data RAM. The relation of data area and COM/SEG pin is as below:

| COM7 ~ COM0       | Segment |

|-------------------|---------|

| 00H (Bit7 ~ Bit0) | SEG0    |

| 01H               | SEG1    |

| :                 | :       |

| 1AH               | SEG26   |

| 1BH               | SEG27   |

<sup>\*</sup> This specification are subject to be changed without notice.

| COM7 ~ COM0 | Segment |

|-------------|---------|

| 1CH         | (empty) |

| :           | :       |

| 1FH         | (empty) |

Bit  $5 \sim \text{Bit } 7 = 0$ : unused

#### PAGE1 (CN1D: Counter 1 preset)

| Ī | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

| ſ | CN17  | CN16  | CN15  | CN14  | CN13  | CN12  | CN11  | CN10  |

| Ī | R/W-0 |

8-bit up counter (COUNTER1) preset and read out register. (write = preset)

In P803 mode, COUNTER1 has reload function. But in 805C mode, it has no reload function. And after an interrupt, it will count from "00".

#### IOCC (LCDD, CN2D)

#### PAGE0 (LCDD: LCD RAM data buffer)

|   | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | LCDD7 | LCDD6 | LCDD5 | LCDD4 | LCDD3 | LCDD2 | LCDD1 | LCDD0 |

| ſ | R/W   |

Bit 0 ~ Bit 7: LCD RAM data

For 8-COM mode, bit0 ~ bit7 are used. For 4-COM mode, only bit0 ~ bit3 are used.

#### PAGE1 (CN2D: Counter 2 preset)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CN27  | CN26  | CN25  | CN24  | CN23  | CN22  | CN21  | CN20  |

| R/W-0 |

8-bit up-counter (COUNTER2) preset and read out register. (write = preset)

In P803 mode, COUNTER2 has reload function. But in 805C mode, it has no reload function. And after an interrupt, it will count from "00".

#### IOCD (TONE1C, P7PHC)

## PAGE0 (TONE1C: TONE1 frequency control)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| T17   | T16   | T15   | T14   | T13   | T12   | T11   | T10   |

| R/W-0 |

Bit 0  $\sim$  Bit 7 (T10  $\sim$  T17) : TONE1 frequency control bits

Clock source = 111957Hz and Freq. = 111957Hz / N, where N =  $0 \sim 255$  is divider value for T17  $\sim$  T10 Tone generator 1's frequency divider. Please run in normal mode.

T17~T10 = '111111111' **>** Tone generator 1 will has 439Hz SIN wave output

T17~T10 = '00000010'  $\rightarrow$  Tone generator 1 will has 55978Hz SIN wave output

$T17 \sim T10 = '00000001' \rightarrow Tone generator 1 will has 111957Hz$

$T17 \sim T10 = '000000000' \rightarrow \text{no used}$

#### PAGE1 (P7PHC: PORT7 pull high control)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PH7   | PH6   | PH5   | PH4   | PH3   | PH2   | PH1   | PH0   |

| R/W-0 |

Bit  $0 \sim 7$  (PH0  $\sim$  PH7) : PORT7(0 $\sim$ 7) pull high control bits

<sup>\*</sup> This specification are subject to be changed without notice.

0/1 → Disable internal pull-high/enable internal pull-high

These control bits are used to enable the pull-high of PORT7(0  $\sim$  7) pins.

## IOCE (TONE2C, CNPSC)

PAGE0 (TONE2C: TONE2 frequency control)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| T27   | T26   | T25   | T24   | T23   | T22   | T21   | T20   |

| R/W-0 |

Bit  $0 \sim \text{Bit } 7 \text{ (T20} \sim \text{T27)}$ : TONE2 frequency control bits

Clock source = 111957Hz and Freq. = 111957Hz / N, where N =  $0 \sim 255$  is divider value for T27  $\sim$  T20 Tone generator 2's frequency divider. Please run in normal mode.

$T27 \sim T20 = '111111111' \rightarrow Tone generator 2 will has 439Hz SIN wave output.$

$T27 \sim T20 = '00000010' \rightarrow Tone generator 2 will has 55978Hz SIN wave output.$

$T27 \sim T20 = '00000001' \rightarrow Tone generator 2 will has 111957Hz SIN wave output.$

$T27 \sim T20 = '000000000' \rightarrow \text{no used}$

|                 |                | TO            | ONE2 (IOCE)  | High group free | ].           |

|-----------------|----------------|---------------|--------------|-----------------|--------------|

|                 |                | 1203.8 (0X5D) | 1332.8(0X54) | 1473.1(0X4C)    | 1646.4(0X44) |

| TONE1(IOCD,     | 699.7Hz(0x0A0) | 1             | 2            | 3               | A            |

| IOCA PAGE1)     | 772.1Hz(0x091) | 4             | 5            | 6               | В            |

| Low group frog  | 854.6Hz(0x083) | 7             | 8            | 9               | С            |

| Low group freq. | 940.8Hz(0x077) | *             | 0            | #               | D            |

#### PAGE1 (CNPSC: Open-drain control, Counter 1,2 clock source and prescaler, LCD mode)

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| OP77  | OP76  | C2S   | C1S   | PSC2  | PSC1  | PSC0  | LCDM  |

| R/W-0 |

Bit 0 (LCDM): LCD mode control for 8-COM, 1/8 duty or 4-COM, 1/4 duty selection

0 → 8-COM mode selection and COM0 ~ COM7 are enabled

1 → 4-COM mode selection and COM0 ~ COM3 are enabled

Bit  $1 \sim 3$  (PSC0 $\sim$ PSC2): Counter1 prescaler setting

reset = (0.0.0)

| (PSC2,PSC1,PSC0) | Scaler ratio |

|------------------|--------------|

| (0,0,0)          | 1:1          |

| (0,0,1)          | 1:2          |

| (0,1,0)          | 1:4          |

| (0,1,1)          | 1:8          |

| (1,0,0)          | 1:16         |

| (1,0,1)          | 1:32         |

| (1,1,0)          | 1:64         |

| (1,1,1)          | 1:128        |

Bit 4 (C1S): Counter1 source

0/1 → 32.768kHz/MAIN clock if enable

In ERIC mode, the clock source will be replaced by sub frequency (0) and the frequency of ERIC oscillation (1).

Bit 5 (C2S): Counter2 source

In the normal mode:

0/1 → 32.768kHz/Main clock if enable, scale=1:1

In ERIC mode, the clock source will be replaced by sub frequency (0) and the frequency of ERIC oscillation

Bit 6 (OP76): P76 open-drain control

21

<sup>\*</sup> This specification are subject to be changed without notice.

0/1 → disable/enable

Bit 7 (OP77): P77 open-drain control

0/1 → disable/enable

#### IOCF (INTM)

#### PAGE0 (INTM: Interrupt Mask Register)

| 7     | 6   | 5     | 4     | 3         | 2     | 1     | 0     |

|-------|-----|-------|-------|-----------|-------|-------|-------|

| EDD   | 0   | CNT2  | CNT1  | INT2/INT3 | INT1  | INT0  | TCIF  |

| R/W-0 | R-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 | R/W-0 |

Bit  $0 \sim 5.7$ : interrupt enable bit

1/0 → enable/disable interrupt

Bit 6: unused

IOCF Register is readable and writable. They work with RF registers.

#### PAGE1

Non-existence. Always keep this bit to "0". Don't set it to "1" to prevent causing problem

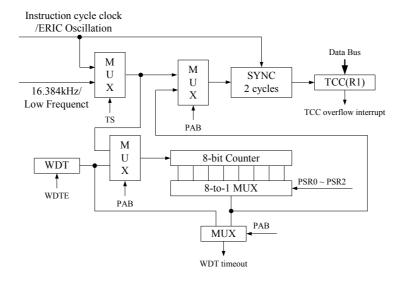

## VII.4 TCC/WDT Prescaler

There is an 8-bit counter available as prescaler for the TCC or WDT. The prescaler is available for the TCC only or WDT only at the same time.

- An 8-bit counter is available for TCC or WDT determined by the status of the bit 3 (PAB) of the CONT register.

- See the prescaler ratio in CONT register.

- Fig. 8 depicts the circuit diagram of TCC/WDT.

- Both TCC and prescaler will be cleared by instructions which write to TCC each time.

- The prescaler will be cleared by the WDTC and SLEP instructions, when assigned to WDT mode.

- The prescaler will not be cleared by SLEP instructions, when assigned to TCC mode.

In ERIC mode, the instruction clock is the half of frequency of ERIC oscillation. When TS bit sets 1, the clock is the half of sub frequency divided from the frequency of ERIC oscillation.

Fig.8 Block diagram of TCC WDT

<sup>\*</sup> This specification are subject to be changed without notice.

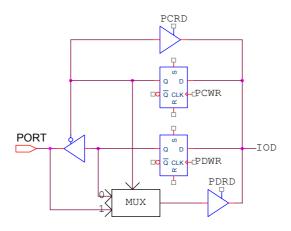

# VII.5 I/O Ports

The I/O registers, Port 9, are bi-directional tri-state I/O ports. Port 9 can be pulled-high internally by software control. The I/O ports can be defined as "input" or "output" pins by the I/O control registers (IOC6  $\sim$  IOC9) under program control. The I/O registers and I/O control registers are both readable and writable. The I/O interface circuit is shown in Fig.9.

Fig.9 Circuit of I/O port and I/O control register

# VII.6 RESET and Wake-up

The RESET can be caused by

- (1) External /RESET pin

- (2) Power on reset or Power on voltage detector reset (/POVD reset)

- (3) WDT timeout. (if enabled and in GREEN or NORMAL mode)

Note that only Power on reset, or only Power on voltage detector reset in Case(2) is enabled in the system by CODE Option bit. If /POVDs disabled, Power on reset is selected in Case (2). Refer to Fig.10.

Fig. 10 Block diagram of Reset of controller

Once the RESET occurs, the following functions are performed.

- The oscillator is running, or will be started.

- The Program Counter (R2) is set to all "0".

<sup>\*</sup> This specification are subject to be changed without notice.

- When power on, the upper 3 bits of R3 and the upper 2 bits of R4 are cleared.

- The Watchdog timer and prescaler are cleared.

- The Watchdog timer is disabled.

- The CONT register is set to all "1"

- The other register (bit7..bit0)

| R5 = "xxxx0000"  | IOC5 = "1111xxxx"       |                         |

|------------------|-------------------------|-------------------------|

| R6 = PORT        | IOC6 = "11111111"       |                         |

| R7 = PORT        | IOC7 = "11111111"       |                         |

| R8 = PORT        | IOC8 = "11111111"       |                         |

| R9 = PORT        | IOC9 = "11111111"       |                         |

| RA = "00110000"  | Page0 IOCA = "00000000" | Page1 IOCA = "00000000" |

| RB = "0000x000"  | Page0 IOCB = "00000000" | Page1 IOCB = "00000000" |

| RC = "00000000"  | Page0 IOCC = "xxxxxxxx" | Page1 IOCC = "00000000" |

| RD = "xxxxxxxxx" | Page0 IOCD = "00000000" | Page1 IOCD = "00000000" |

| RE = "x00000000" | Page0 IOCE = "00000000" | Page1 IOCE = "00000000" |

| RF = "00000000"  | IOCF = "00000000"       |                         |

The controller can be awakened from SLEEP mode or IDLE mode (execution of "SLEP" instruction, named as SLEEP mode or IDLE mode) by (1) TCC time out (IDLE mode only) (2) WDT time-out (if enabled) (3) external input at PORT9 (4) Energy detector (DED) output data. The three cases will cause the controller to be wake-up and run from next instruction in IDLE mode, reset in SLEEP mode. After CPU is wake-up, user should control Watchdog in case of reset in GREEN mode or NORMAL mode. The last three should be open RE register before into SLEEP mode or IDLE mode. The first one case will set a flag in RF bit 0. And it will go to address 0x08 when TCC generates an interrupt.

# VII.7 Interrupt

The Caller ID IC has internal interrupts which are falling edge triggered, as follows: TCC timer overflow interrupt (internal), two 8-bit counters overflow interrupt.

If these interrupt sources change signal from high to low, then RF register will generate '1' flag to corresponding register if you enable IOCF register.

RF is the interrupt status register which records the interrupt request in flag bit. IOCF is the interrupt mask register. Global interrupt is enabled by ENI instruction and is disabled by DISI instruction. When one of the interrupts (when enabled) generated, will cause the next instruction to be fetched from address 008H. Once in the interrupt service routine the source of the interrupt can be determined by polling the flag bits in the RF register. The interrupt flag bit must be cleared in software before leaving the interrupt service routine and enabling interrupts to avoid recursive interrupts.

There are four external interrupt pins including INT0, INT1, INT2 and INT3. And four internal counters interrupt available.

External interrupt INT0, INT1, INT2, INT3 signals are from PORT7 bit0 to bit3. If IOCF is enable then these signal will cause interrupt, or these signals will be treated as general input data.

After reset, the next instruction will be fetched from address 000H and the instruction interrupt is 001H and the hardware interrupt is 008H.

TCC will go to address 0x08 in GREEN mode or NORMAL mode after time out. And it will run next instruction from "SLEP" instruction and then go to address 0x08 in IDLE mode. These two cases will set a RF flag.

## VII.8 Instruction Set

Instruction set has the following features:

- (1) Every bit of any register can be set, cleared, or tested directly.

- (2) The I/O register can be regarded as general register. That is, the same instruction can operate on I/O register.

<sup>\*</sup> This specification are subject to be changed without notice.

The symbol "R" represents a register designator which specifies which one of the 64 registers (including operational registers and general purpose registers) is to be utilized by the instruction. Bits 6 and 7 in R4 determine the selected register bank. "b" represents a bit field designator which selects the number of the bit, located in the register "R", affected by the operation. "k" represents an 8 or 10-bit constant or literal value.

|   | Instruc | tion bin | ary  | Hex  | Mnemonic | Operation                                                          | Status Affected |

|---|---------|----------|------|------|----------|--------------------------------------------------------------------|-----------------|

| 0 | 0000    | 0000     | 0000 | 0000 | NOP      | No Operation                                                       | None            |

| 0 | 0000    | 0000     | 0001 | 0001 | DAA      | Decimal Adjust A                                                   | С               |

| 0 | 0000    | 0000     | 0010 | 0002 | CONTW    | $A \rightarrow CONT$                                               | None            |

| 0 | 0000    | 0000     | 0011 | 0003 | SLEP     | $0 \rightarrow WDT$ , Stop oscillator                              | T,P             |

| 0 | 0000    | 0000     | 0100 | 0004 | WDTC     | $0 \to WDT$                                                        | T,P             |

| 0 | 0000    | 0000     | rrrr | 000r | IOW R    | $A \rightarrow IOCR$                                               | None            |

| 0 | 0000    | 0001     | 0000 | 0010 | ENI      | Enable Interrupt                                                   | None            |

| 0 | 0000    | 0001     | 0001 | 0011 | DISI     | Disable Interrupt                                                  | None            |

| 0 | 0000    | 0001     | 0010 | 0012 | RET      | $[Top of Stack] \rightarrow PC$                                    | None            |

| 0 | 0000    | 0001     | 0011 | 0013 | RETI     | $[Top of Stack] \rightarrow PC$ Enable Interrupt                   | None            |

| 0 | 0000    | 0001     | 0100 | 0014 | CONTR    | $CONT \rightarrow A$                                               | None            |

| 0 | 0000    | 0001     | rrrr | 001r | IOR R    | $IOCR \rightarrow A$                                               | None            |

| 0 | 0000    | 0010     | 0000 | 0020 | TBL      | $R2+A \rightarrow R2$ bits 9,10 do not clear                       | Z, C, DC        |

| 0 | 0000    | 01rr     | rrrr | 00rr | MOV R,A  | $A \rightarrow R$                                                  | None            |

| 0 | 0000    | 1000     | 0000 | 0080 | CLRA     | $0 \rightarrow A$                                                  | Z               |

| 0 | 0000    | 11rr     | rrrr | 00rr | CLR R    | $0 \rightarrow R$                                                  | Z               |

| 0 | 0001    | 00rr     | rrrr | 01rr | SUB A,R  | $R-A \rightarrow A$                                                | Z, C, DC        |

| 0 | 0001    | 01rr     | rrrr | 01rr | SUB R,A  | $R-A \rightarrow R$                                                | Z, C, DC        |

| 0 | 0001    | 10rr     | rrrr | 01rr | DECA R   | $R-1 \rightarrow A$                                                | Z               |

| 0 | 0001    | 11rr     | rrrr | 01rr | DEC R    | $R-1 \rightarrow R$                                                | Z               |

| 0 | 0010    | 00rr     | rrrr | 02rr | OR A,R   | $A \vee VR \rightarrow A$                                          | Z               |

| 0 | 0010    | 01rr     | rrrr | 02rr | OR R,A   | $A \vee VR \rightarrow R$                                          | Z               |

| 0 | 0010    | 10rr     | rrrr | 02rr | AND A,R  | $A & R \rightarrow A$                                              | Z               |

| 0 | 0010    | 11rr     | rrrr | 02rr | AND R,A  | $A & R \rightarrow R$                                              | Z               |

| 0 | 0011    | 00rr     | rrrr | 03rr | XOR A,R  | $A \oplus R \rightarrow A$                                         | Z               |

| 0 | 0011    | 01rr     | rrrr | 03rr | XOR R,A  | $A \oplus R \rightarrow R$                                         | Z               |

| 0 | 0011    | 10rr     | rrrr | 03rr | ADD A,R  | $A + R \rightarrow A$                                              | Z, C, DC        |

| 0 | 0011    | 11rr     | rrrr | 03rr | ADD R,A  | $A + R \rightarrow R$                                              | Z, C, DC        |

| 0 | 0100    | 00rr     | rrrr | 04rr | MOV A,R  | $R \rightarrow A$                                                  | Z               |

| 0 | 0100    | 01rr     | rrrr | 04rr | MOV R,R  | $R \rightarrow R$                                                  | Z               |

| 0 | 0100    | 10rr     | rrrr | 04rr | COMA R   | $/R \rightarrow A$                                                 | Z               |

| 0 | 0100    | 11rr     | rrrr | 04rr | COM R    | $/R \rightarrow R$                                                 | Z               |

| 0 | 0101    | 00rr     | rrrr | 05rr | INCA R   | $R+1 \rightarrow A$                                                | Z               |

| 0 | 0101    | 01rr     | rrrr | 05rr | INC R    | $R+1 \rightarrow R$                                                | Z               |

| 0 | 0101    | 10rr     | rrrr | 05rr | DJZA R   | $R-1 \rightarrow A$ , skip if zero                                 | None            |

| 0 | 0101    | 11rr     | rrrr | 05rr | DJZ R    | $R-1 \rightarrow R$ , skip if zero                                 | None            |

| 0 | 0110    | 00rr     | rrrr | 06rr | RRCA R   | $R(n) \to A(n-1)$<br>$R(0) \to C, C \to A(7)$                      | С               |

| 0 | 0110    | 01rr     | rrrr | 06rr | RRC R    | $R(n) \to R(n-1)$ $R(0) \to C, C \to R(7)$                         | С               |

| 0 | 0110    | 10rr     | rrrr | 06rr | RLCA R   | $R(n) \rightarrow A(n+1)$ $R(7) \rightarrow C, C \rightarrow A(0)$ | С               |

| 0 | 0110    | 11rr     | rrrr | 06rr | RLC R    | $R(n) \rightarrow R(n+1)$ $R(7) \rightarrow C, C \rightarrow R(0)$ | С               |

<sup>\*</sup> This specification are subject to be changed without notice.

| 0 | 0111 | 00rr | rrrr | 07rr | SWAPA R   | $R(0-3) \to A(4-7)$                                 | None     |

|---|------|------|------|------|-----------|-----------------------------------------------------|----------|

|   | 0111 | 0011 | **** | 0711 | 5 1111111 | $R(4-7) \to A(0-3)$                                 | 1,0116   |

| 0 | 0111 | 01rr | rrrr | 07rr | SWAP R    | $R(0-3) \leftrightarrow R(4-7)$                     | None     |

| 0 | 0111 | 10rr | rrrr | 07rr | JZA R     | $R+1 \rightarrow A$ , skip if zero                  | None     |

| 0 | 0111 | 11rr | rrrr | 07rr | JZ R      | $R+1 \rightarrow R$ , skip if zero                  | None     |

| 0 | 100b | bbrr | rrrr | 0xxx | BC R,b    | $0 \rightarrow R(b)$                                | None     |

| 0 | 101b | bbrr | rrrr | 0xxx | BS R,b    | $1 \rightarrow R(b)$                                | None     |

| 0 | 110b | bbrr | rrrr | 0xxx | JBC R,b   | if R(b)=0, skip                                     | None     |