# EM78871

# 8-Bit Microcontroller

# Product Specification

Doc. Version 1.5

ELAN MICROELECTRONICS CORP.

May 2006

#### **Trademark Acknowledgments:**

IBM is a registered trademark and PS/2 is a trademark of IBM. Windows is a trademark of Microsoft Corporation.

ELAN and ELAN logo are trademarks of ELAN Microelectronics Corporation.

#### Copyright © 2006 by ELAN Microelectronics Corporation **All Rights Reserved** Printed in Taiwan

The contents of this specification are subject to change without further notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

In no event shall ELAN Microelectronics be made responsible for any claims attributed to errors, omissions, or other inaccuracies in the information or material contained in this specification. ELAN Microelectronics shall not be liable for direct, indirect, special incidental, or consequential damages arising from the use of such information or material.

The software (if any) described in this specification is furnished under a license or nondisclosure agreement, and may be used or copied only in accordance with the terms of such agreement.

ELAN Microelectronics products are not intended for use in life support appliances, devices, or systems. Use of ELAN Microelectronics product in such applications is not supported and is prohibited. NO PART OF THIS SPECIFICATION MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS WITHOUT THE EXPRESSED WRITTEN PERMISSION OF ELAN MICROELECTRONICS.

#### **ELAN MICROELECTRONICS CORPORATION**

#### **Headquarters:**

No. 12, Innovation Road 1 Hsinchu Science Park Hsinchu, Taiwan 30077 Tel: +886 3 563-9977 Fax:+886 3 563-9966 http://www.emc.com.tw

## Hong Kong:

Elan (HK) Microelectronics Corporation, Ltd. Rm. 1005B, 10/F Empire Centre

68 Mody Road, Tsimshatsui Kowloon, HONG KONG Tel: +852 2723-3376 Fax: +852 2723-7780

elanhk@emc.com.hk

#### USA:

**Elan Information Technology Group (U.S.A.)**

1821 Saratoga Ave., Suite 250 Saratoga, CA 95070

USA

Tel: +1 408 366-8225 Fax: +1 408 366-8220

#### Europe:

Elan Microelectronics Corp. (Europe)

Siewerdtstrasse 105 8050 Zurich, SWITZERLAND Tel: +41 43 299-4060 Fax: +41 43 299-4079 http://www.elan-europe.com

#### Shenzhen:

**Elan Microelectronics** Shenzhen, Ltd.

Shenzhen Hi-Tech Industrial Park Shenzhen, Guandong, CHINA Tel: +86 755 2601-0565 Fax: +86 755 2601-0500

#### Shanghai:

**Elan Microelectronics** Shanghai, Ltd.

SSMEC Bldg., 3F, Gaoxin S. Ave. 23/Bldg. #115 Lane 572, Bibo Road Zhangjiang Hi-Tech Park Shanghai, CHINA Tel: +86 21 5080-3866 Fax: +86 21 5080-4600

# Contents

| 1 | General Description |        |                                                        |    |  |  |  |  |

|---|---------------------|--------|--------------------------------------------------------|----|--|--|--|--|

| 2 | Feat                | tures  |                                                        | 1  |  |  |  |  |

|   | 2.1                 | CPU    |                                                        | 1  |  |  |  |  |

|   | 2.2                 | Curren | nt D/A                                                 | 2  |  |  |  |  |

|   | 2.3                 | Progra | ımmable Tone Generators                                | 2  |  |  |  |  |

|   | 2.4                 | CID    |                                                        | 2  |  |  |  |  |

|   | 2.5                 | Call W | aiting                                                 | 3  |  |  |  |  |

|   | 2.6                 |        | 3x80, 9x80, 16x80, 24x72)                              |    |  |  |  |  |

|   | 2.7                 |        | pe                                                     |    |  |  |  |  |

| 3 |                     |        |                                                        |    |  |  |  |  |

| 4 |                     |        | ment                                                   |    |  |  |  |  |

| 5 |                     | _      | ram                                                    |    |  |  |  |  |

| 6 |                     | _      | otion                                                  |    |  |  |  |  |

| 7 |                     | -      | Description                                            |    |  |  |  |  |

|   | 7.1                 |        | tional Registers                                       |    |  |  |  |  |

|   | 7.2                 | Operat | tional Register Detailed Description                   | 10 |  |  |  |  |

|   |                     | 7.2.1  | R0 (Indirect Addressing Register)                      |    |  |  |  |  |

|   |                     | 7.2.2  | R1 (TCC)                                               | 11 |  |  |  |  |

|   |                     | 7.2.3  | R2 (Program Counter)                                   | 11 |  |  |  |  |

|   |                     | 7.2.4  | R3 (Status Register)                                   |    |  |  |  |  |

|   |                     | 7.2.5  | R4 (RAM Selection for Common Registers R20 ~ R3F, SPI) |    |  |  |  |  |

|   |                     | 7.2.6  | R5 (Port 5 I/O data, Program page selection, SPI data) |    |  |  |  |  |

|   |                     | 7.2.7  | R6 (Port 6 I/O data)                                   |    |  |  |  |  |

|   |                     | 7.2.8  | R7 (Port 7 I/O data)                                   |    |  |  |  |  |

|   |                     | 7.2.9  | R8 (Port 8 I/O data)                                   |    |  |  |  |  |

|   |                     | 7.2.10 | ·                                                      | 10 |  |  |  |  |

|   |                     |        | FSK, Watchdog Timer, LCD Address)                      | 19 |  |  |  |  |

|   |                     | 7.2.12 | RB (Port B I/O Data, LCD Data)                         | 23 |  |  |  |  |

|   |                     |        | RC (Port C I/O Data, Data RAM Data)                    |    |  |  |  |  |

|   |                     |        | RD (Comparator Control, Data RAM Address)              |    |  |  |  |  |

|   |                     |        | RE (CAS, Key Scan, LCD Control, Data RAM Address)      |    |  |  |  |  |

|   |                     |        | RF (Interrupt Flags)                                   |    |  |  |  |  |

|   |                     | 7.2.17 | R10~R3F (General Purpose Register)                     | 32 |  |  |  |  |

|    | 7.3  | Specia   | I Function Registers                                               | 32 |

|----|------|----------|--------------------------------------------------------------------|----|

|    |      | 7.3.1    | A (Accumulator)                                                    | 32 |

|    |      | 7.3.2    | CONT (Control Register)                                            | 32 |

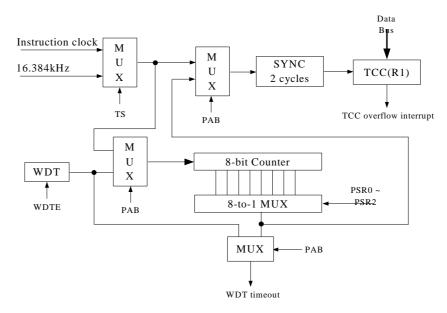

|    |      | 7.3.3    | TCC and WDT                                                        | 33 |

|    |      | 7.3.4    | IOC5 (Port 5 I/O control, Port Switch, Keytone, CDAS, LCD bias)    | 33 |

|    |      | 7.3.5    | IOC6 (Port 6 I/O Control, CDA, Port Switch, LCD driving control)   | 37 |

|    |      | 7.3.6    | IOC7 (Port 7 I/O Control, Key Strobe)                              |    |

|    |      | 7.3.7    | IOC8 (Port 8 I/O Control, , Key strobe)                            |    |

|    |      | 7.3.8    | IOC9 (Port 9 I/O Control, DTMF Receiver)                           |    |

|    |      | 7.3.9    | IOCA (CN1's and CN2's Clock and Scaling, Port 7 Pull-high Control) |    |

|    |      |          | IOCB (Port B I/O Control, Port 6 Pull-high Control)                |    |

|    |      |          | IOCC (Port C I/O Control, Tone 1 Control)                          |    |

|    |      |          | IOCD (Counter1 Data, Tone 2 Control)                               |    |

|    |      |          | IOCE (Counter 2 Data, Comparator and OP Control, Energy Detector ) |    |

|    |      |          | IOCF (Interrupt Mask Register)                                     |    |

|    | 7.4  | I/O Po   | rt                                                                 | 48 |

|    | 7.5  | Reset.   |                                                                    | 48 |

|    | 7.6  | Wake-    | up                                                                 | 49 |

|    | 7.7  | Interru  | pt                                                                 | 50 |

|    | 7.8  | Instruc  | tion Set                                                           | 50 |

|    | 7.9  | Code (   | Option Register                                                    | 53 |

|    |      | 7.9.1    | CODE Option Register1 ( Program ROM)                               | 52 |

|    | 7.10 | Call W   | aiting Function Description                                        | 53 |

| 8  | Abso | olute O  | peration Maximum Ratings                                           | 54 |

| 9  | DC E | Electric | al Characteristic                                                  | 54 |

| 10 | AC E | Electric | al Characteristic                                                  | 56 |

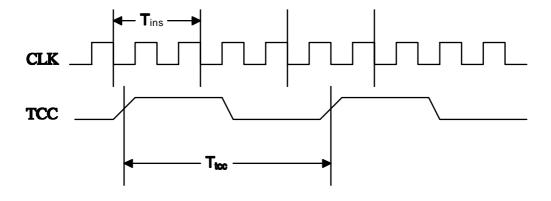

|    | 10.1 | CPU Ir   | nstruction Timing                                                  | 56 |

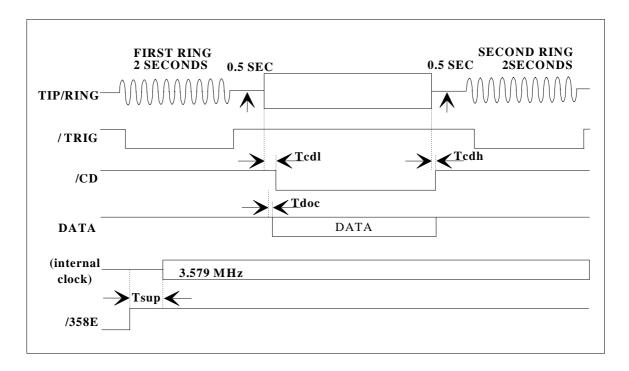

|    | 10.2 | FSK A    | C Characteristic                                                   | 56 |

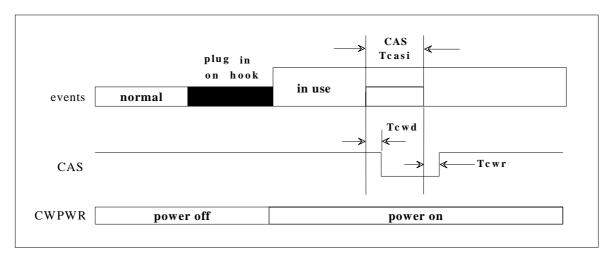

|    | 10.3 | CW AC    | C Characteristic                                                   | 56 |

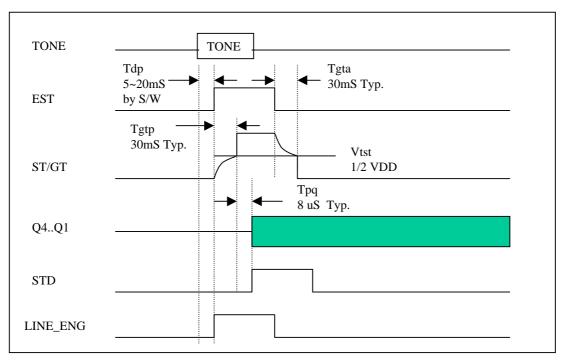

|    | 10.4 | DTMF     | r (DTMF Receiver) AC Characteristic                                | 57 |

|    | 10.5 | Tone G   | Generators for AC Characteristic                                   | 57 |

|    | 10.6 | Timing   | g Characteristic                                                   | 57 |

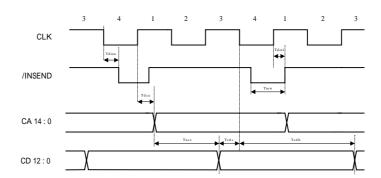

| 11 | Timi | ng Diag  | grams                                                              | 59 |

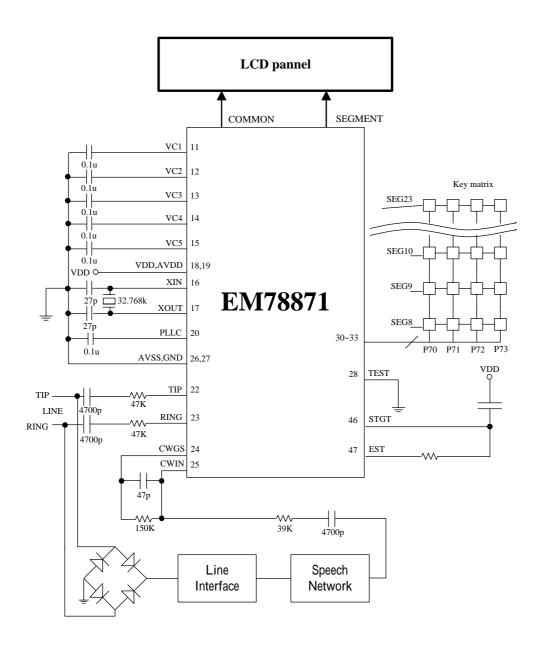

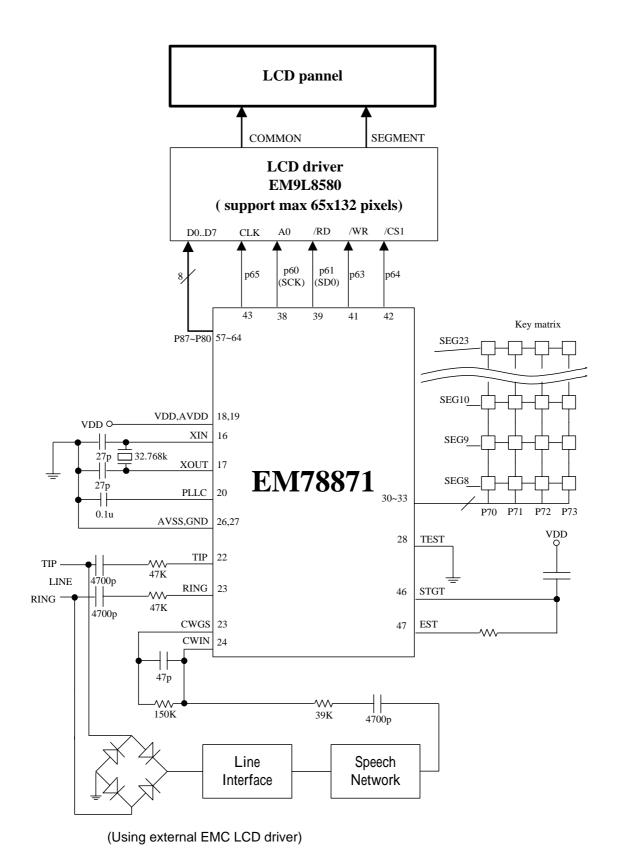

| 12 |      | •        | Circuit                                                            |    |

|    |      |          |                                                                    |    |

#### **APPENDIX**

| Α | User Application Note                                     | 64 |

|---|-----------------------------------------------------------|----|

| В | •                                                         |    |

|   | B.1 Feature                                               |    |

|   | B.1.1 CPU                                                 |    |

|   | B.2 Pin Configuration                                     | 66 |

| С |                                                           |    |

| D | Operational Registers                                     |    |

|   | D.1 R9                                                    | 70 |

|   | D.1.1 Page 1 (LCD Address MSB Bit, Data ROM Address Bits) | 70 |

|   | D.2 IOC5                                                  |    |

|   | D.2.1 Page 2 ( Stack Pointer )                            | 70 |

| Е | AC Electrical Characteristic                              | 71 |

## **Specification Revision History**

| Doc. Version | Revision Description           | Date       |

|--------------|--------------------------------|------------|

| 1.5          | Removed the Idle Mode Function | 2006/05/25 |

# 1 General Description

The EM78871 is an 8-bit CID (Caller Identification) RISC architecture microprocessor with low-power and high-speed CMOS technology. Integrated onto a single IC are on-chip watchdog timer (WDT), RAM, program ROM, programmable real-time clock/counter, external/internal interrupt, power-down mode, LCD driver, FSK decoder, Call-waiting decoder, DTMF receiver, Programming Tone generator, built-in Keytone clock generation, Comparator and tri-state I/O. The EM78871 provides a single-chip solution to design a CID for call message display.

### 2 Features

#### 2.1 CPU

- Operating voltage range : 2.2V~5.5V (Normal mode), 2.0V~5.5V (Green mode)

- 32K×13 on-chip Program ROM

- 4K×8 on-chip data RAM

- 144-byte working register

- 51 bi-directional tri-state I/O ports (32 shared with LCD Segment pins)

- I/O with internal Pull high, wake-up and interrupt functions

- Stack: 32 stack levels for subroutine nesting

- TCC: 8-bit real time clock/counter (TCC) with 8-bit prescaler

- Counter 1: 8-bit counter with 8-bit prescaler which can also be an interrupt source

- Counter 2: 8-bit counter with 8-bit prescaler which can also be an interrupt source

- On-chip Watchdog Timer

- CPU modes:

| Mode        | CPU Status | Main Clock | 32.768kHz Clock Status |

|-------------|------------|------------|------------------------|

| Sleep mode  | Off        | Off        | Off                    |

| Green mode  | On         | Off        | On                     |

| Normal mode | On         | On         | On                     |

- Thirteen interrupt sources (8 external, 5 internal)

- Key Scan: Port key scan function scans up to 64 (16x4) keys

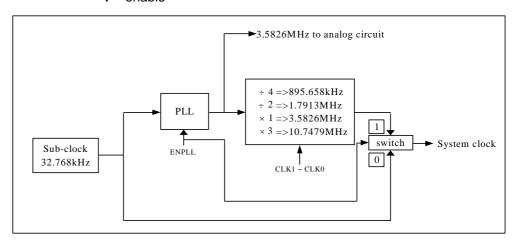

- Sub-clock: 32.768kHz crystal

- Main-clock: 3.5862MHz multiplied by 0.25, 0.5, 1 or 3 generated by the internal PLL

- Keytone output: 4kHz, 2kHz and1kHz (shared with I/O)

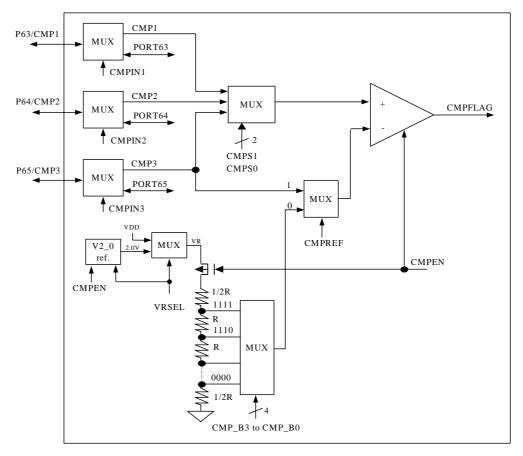

- Comparator: 3-channel comparators: internal (16 level) or external reference voltage (shared with I/O)

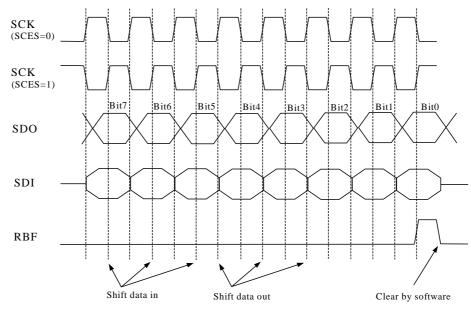

- Serial Peripheral Interface (SPI): Interrupt flag (when the read buffer is full), programmable baud rates and three-wire synchronous communication (shared with I/O)

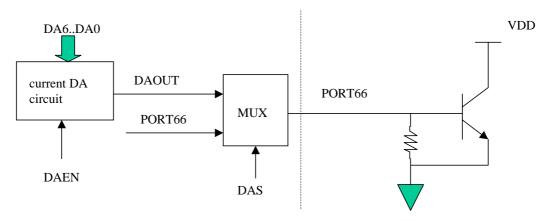

#### 2.2 Current D/A

- Operating voltage range: 2.5V~5.5V

- 7-bit resolution and 3-bit output level control

- Current DA output controls the speaker using a transistor for sound playing (shared with I/O)

#### 2.3 Programmable Tone Generators

- Operating voltage: 2.2V~5.5V

- Two programmable generators: Tone 1 and Tone 2

- Independent single tone generation for Tone 1 and Tone 2

- Mixed dual tone generation by Tone 1 and Tone 2 differs by 2dB

- Programmable DTMF tone generation

- Programmable FSK signal (Bell202 or V.23) generation

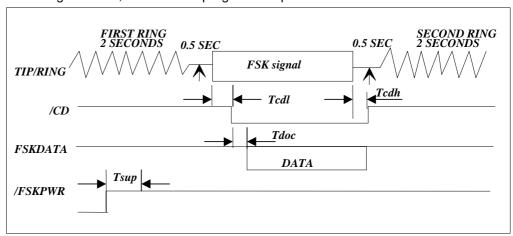

#### 2.4 CID

- Operating voltage: 2.7V~5.5V (FSK)

- Operating voltage: 2.7V~5.5V (DTMF receiver)

- Compatible with Bellcore GR-30-CORE (formerly known as TR-NWT-000030)

- Compatible with British Telecom (BT) SIN227 and SIN242)

- FSK demodulator for Bell 202 and ITU-T V.23 (formerly known as CCITT V.23)

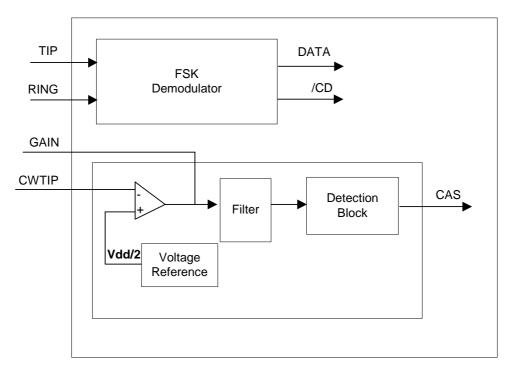

#### 2.5 Call Waiting

- Operating voltage: 2.6V~5.5V

- Compatible with Bellcore special report SR-TSV-002476

- Call-Waiting (2130Hz plus 2750Hz) Alert Signal Detector

- Good talk-down and talk-off performance

- Sensitivity compensated by adjusting input OP gain

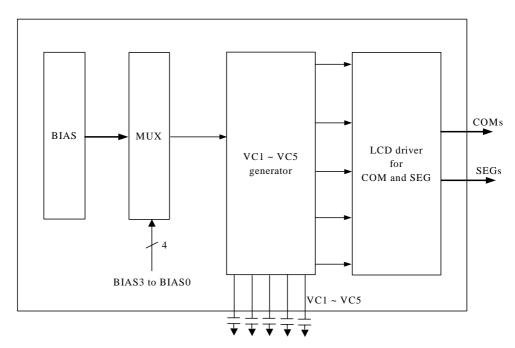

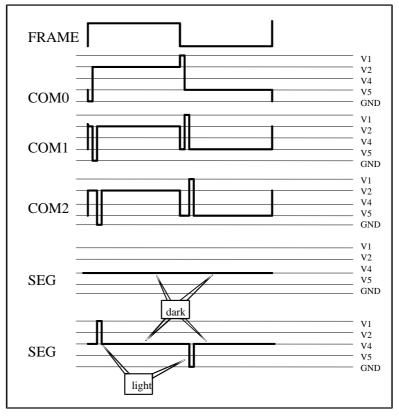

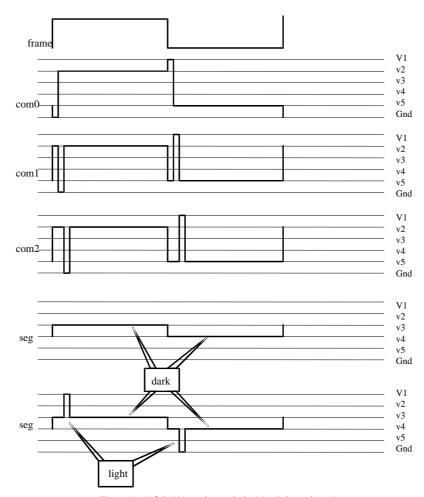

#### 2.6 LCD (8x80, 9x80, 16x80, 24x72)

- Maximum common driver pins: 16/24

- Maximum segment driver pins: 80 (SEG0 ~ SEG79) / 72 (SEG8 ~ SEG79)

- Shared pins: COM16 ~ COM23 pin-shared with SEG0 ~ SEG7

- 1/4 bias for 8, 9 and 16 common modes and 1/5 bias for 24 common mode

- 1/8, 1/9, 1/16, 1/24 duty

- 16 levels of LCD contrast control (software)

- Internal resistor circuit for LCD bias

- Internal voltage follower for better display

#### 2.7 Die Type

- 132-pin die: EM78871H

- 128-pin package: EM78871AQ with POVD disabled

EM78871BQ with POVD enabled

## 3 Application

Adjunct units

Answering machines

Feature phones

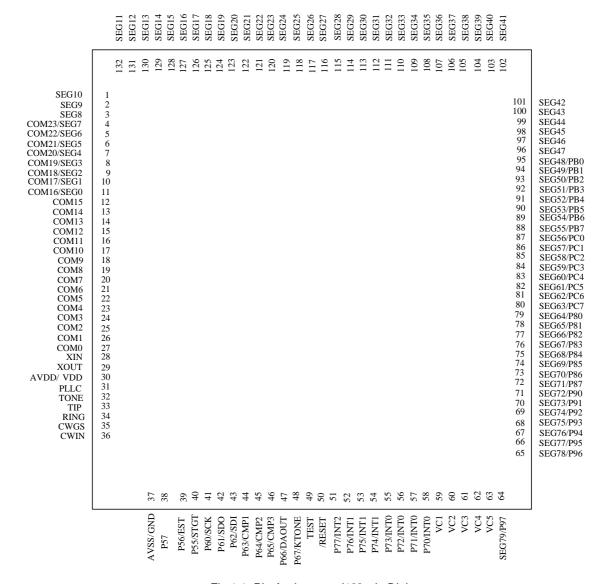

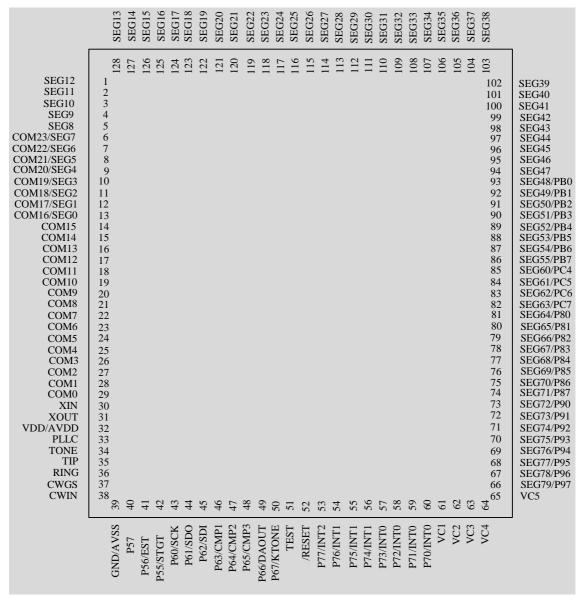

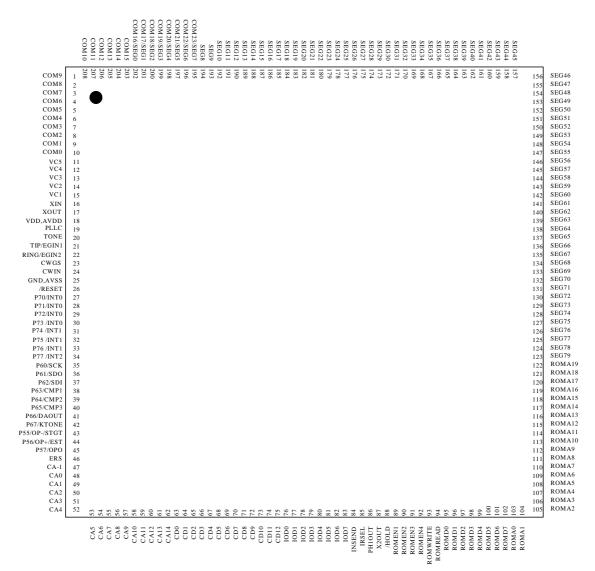

# 4 Pin Assignment

EM78871H

Fig.1.1 Pin Assignment (132-pin Die)

Fig.1.2 Pin Assignment (128-pin QFPA)

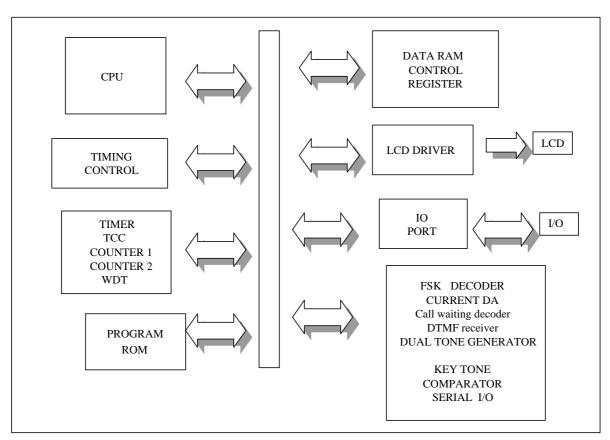

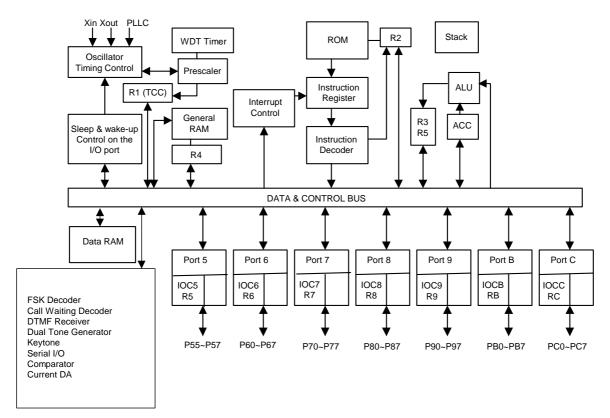

# 5 Block Diagram

Fig. 2 Block Diagram 1

Fig.3 Block Diagram 2

# 6 Pin Description

| Pin                                                                                 | I/O                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power                                                                               | 1/0                                                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                            |

| VDD<br>AVDD                                                                         | -                                                                                                   | Digital power Analog power They are connected together when packaged as 128-pin QFP.                                                                                                                                                                                                                                                                                                                   |

| GND<br>AVSS                                                                         | -                                                                                                   | Digital ground Analog ground They are connected together when packaged as 128-pin QFP.                                                                                                                                                                                                                                                                                                                 |

| Clock                                                                               |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |

| XIN                                                                                 | I                                                                                                   | Input pin for the 32.768 kHz oscillator                                                                                                                                                                                                                                                                                                                                                                |

| XOUT                                                                                | 0                                                                                                   | Output pin for the 32.768 kHz oscillator                                                                                                                                                                                                                                                                                                                                                               |

| PLLC                                                                                | ı                                                                                                   | Phase loop clock capacitor. Connects to a capacitor (between $0.01\mu F$ and $0.1\mu F$ ) to GND.                                                                                                                                                                                                                                                                                                      |

| LCD                                                                                 |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |

| COM0~COM15                                                                          | 0                                                                                                   | Common driver pins of the LCD drivers                                                                                                                                                                                                                                                                                                                                                                  |

| SEG0~SEG7<br>SEG8~SEG47<br>SEG48~SEG55<br>SEG56~SEG63<br>SEG64~SEG71<br>SEG72~SEG79 | O<br>(COM16~COM23)<br>O<br>O (I/O: Port B)<br>O (I/O: Port C)<br>O (I/O: Port 8)<br>O (I/O: Port 9) | Segment driver pins for the LCD drivers<br>SEG0 to SEG7 are pin-shared with COM16 to COM23<br>SEG48 to SEG79 are pin-shared with the I/O port.                                                                                                                                                                                                                                                         |

| VC1~VC5                                                                             | I                                                                                                   | Reference voltage input. Each is connects with a $0.1\mu$ capacitor to GND.                                                                                                                                                                                                                                                                                                                            |

| FSK, TONE, KTO                                                                      | NE                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                        |

| TIP                                                                                 | I                                                                                                   | Should be connected to the TIP side of the twisted pair lines for FSK.                                                                                                                                                                                                                                                                                                                                 |

| RING                                                                                | I                                                                                                   | Should be connected to the RING side of the twisted pair lines for FSK.                                                                                                                                                                                                                                                                                                                                |

| TONE                                                                                | 0                                                                                                   | Dual tone output pin                                                                                                                                                                                                                                                                                                                                                                                   |

| KTONE                                                                               | O (Port 67)                                                                                         | Keytone output, pin-shared with Port 67.                                                                                                                                                                                                                                                                                                                                                               |

| CW                                                                                  |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |

| cwgs                                                                                | 0                                                                                                   | Gain adjustment for the single-ended input OP Amp                                                                                                                                                                                                                                                                                                                                                      |

| CWIN                                                                                | I                                                                                                   | Single-ended input OP Amp for the call waiting decoder                                                                                                                                                                                                                                                                                                                                                 |

| DTMF Receiver                                                                       |                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                        |

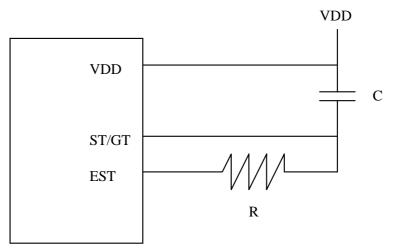

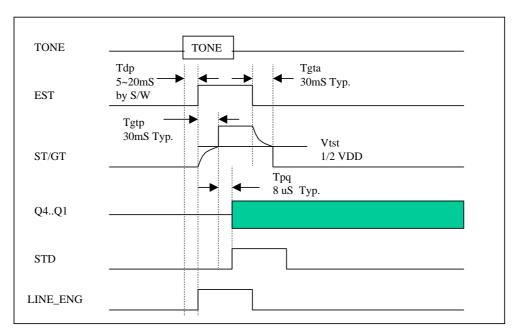

| EST                                                                                 | 0                                                                                                   | Early steering output. Returns HI immediately when the digital algorithm detects a recognizable tone-pair (signal condition). Any momentary loss of signal condition will cause EST to return to LO. This pin is shared with Port 56.                                                                                                                                                                  |

| STGT                                                                                | I/O                                                                                                 | Steering input/guard time output (bi-directional). A voltage greater than Vtst detected at ST causes the device to register the detected tone-pair and update the output latch.  A voltage less than Vtst frees the device to accept a new tone-pair. The GT output resets the external steering time-constant; its state is a function of EST and the voltage on ST. This pin is shared with Port 55. |

| SCK IO (Port 60) Master: output pin, Slave: input pin. This is pin-shared with Port 60.  SDO O (Port 61) Output pin for serial data transferring. This pin is shared with Port 61.  SDI I (Port 62) Input pin for receiving data. This pin is shared with Port 62.  Comparator  CMP1 I (Port 63) Comparator input pins. These are pin-shared with Port 63, Port 64 and Port 65.  CMP2 I (Port 64) I (Port 65) Current DA output pin. Also acts as a control signal for sound generation. Shared with Port 66.  VO  P55 ~P57 I/O Each bit in Port 5 can be an input or output port.  Internal Pull-high function.  P80 ~ P87 I/O Each bit in Port 8 can be an input or output port. These are pin-shared with LCD Segment signal.  P90 ~ P97 I/O Each bit in Port 9 can be an input or output port. These are pin-shared with LCD Segment signal.  P80 ~ P87 I/O Each bit in Port 8 can be an input or output port. These are pin-shared with LCD Segment signal.  P80 ~ P87 I/O Each bit in Port 8 can be an input or output port. These are pin-shared with LCD Segment signal.  P80 ~ P87 I/O Each bit in Port 8 can be an input or output port. These are pin-shared with LCD Segment signal.  P80 ~ P87 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  PR0 ~ P87 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  PR0 ~ P87 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  PR0 ~ P87 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  PR0 ~ P87 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  PR0 ~ P87 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  PR0 ~ P87 I/O Each bit in Port C can be an inp | Serial I/O | Serial I/O   |                                                                                                                                           |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SDI I (Port 62) Input pin for receiving data. This pin is shared with Port 62.  Comparator  CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SCK        | IO (Port 60) | Master: output pin, Slave: input pin. This is pin-shared with Port 60.                                                                    |  |  |  |  |  |

| Comparator  CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SDO        | O (Port 61)  | Output pin for serial data transferring. This pin is shared with Port 61.                                                                 |  |  |  |  |  |

| CMP1 (Port 63) (Port 64) (CMP2 (Port 64) (Port 65) (Port 66) (Port | SDI        | I (Port 62)  | Input pin for receiving data. This pin is shared with Port 62.                                                                            |  |  |  |  |  |

| CMP2 I (Port 64) I (Port 65)  Current DA  DAOUT  O (Port 66)  Current DA output pin. Also acts as a control signal for sound generation. Shared with Port 66.  VO  P55 -P57 I/O Each bit in Port 5 can be an input or output port. Internal pull high.  P70 - P77 I/O Each bit in Port 7 can be an input or output port. Internal pull-high function. Auto key scan function. Interrupt function. Interrupt function.  P80 - P87 I/O Each bit in Port 8 can be an input or output port. Internal pull-high function. Auto key scan function.  P80 - P97 I/O Each bit in Port 9 can be an input or output port. These are pin-shared with LCD Segment signal.  P90 - P97 I/O Each bit in Port 9 can be an input or output port. These are pin-shared with LCD Segment signal.  PB0 - PB7 I/O Each bit in Port B can be an input or output port. These are pin-shared with LCD Segment signal.  PC0 - PC7 I/O Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  INTO Ports 70-73 Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1 Ports 74-76 Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2 Port 77 Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Comparator |              |                                                                                                                                           |  |  |  |  |  |

| DAOUT  O (Port 66)  Current DA output pin. Also acts as a control signal for sound generation. Shared with Port 66.  I/O  Each bit in Port 5 can be an input or output port.  Each bit in Port 6 can be an input or output port.  Internal pull high.  P70 ~ P77  I/O  Each bit in Port 7 can be an input or output port.  Internal Pull-high function.  Auto key scan function.  Interrupt function.  P80 ~ P87  I/O  Each bit in Port 8 can be an input or output port.  These are pin-shared with LCD Segment signal.  P90 ~ P97  I/O  Each bit in Port 9 can be an input or output port.  These are pin-shared with LCD Segment signal.  PB0 ~ PB7  I/O  Each bit in Port B can be an input or output port.  These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port.  These are pin-shared with LCD Segment signal.  INTO  Ports 70-73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74-76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CMP2       | I (Port 64)  |                                                                                                                                           |  |  |  |  |  |

| DAOUT  O (Port 66)  generation. Shared with Port 66.   VO  P55 ~P57  I/O  Each bit in Port 5 can be an input or output port.  P60 ~P67  I/O  Each bit in Port 6 can be an input or output port.  Internal pull high.  P70 ~ P77  I/O  Each bit in Port 7 can be an input or output port.  Internal Pull-high function.  Auto key scan function.  Interrupt function.  P80 ~ P87  I/O  Each bit in Port 8 can be an input or output port.  These are pin-shared with LCD Segment signal.  P90 ~ P97  I/O  Each bit in Port 9 can be an input or output port.  These are pin-shared with LCD Segment signal.  P80 ~ P87  I/O  Each bit in Port B can be an input or output port.  These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port.  These are pin-shared with LCD Segment signal.  INTO  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Current DA |              |                                                                                                                                           |  |  |  |  |  |

| P55 ~P57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DAOUT      | O (Port 66)  | generation.                                                                                                                               |  |  |  |  |  |

| P60 ~P67  I/O  Each bit in Port 6 can be an input or output port. Internal pull high.  Each bit in Port 7 can be an input or output port. Internal Pull-high function. Auto key scan function. Auto key scan function. Interrupt function.  P80 ~ P87  I/O  Each bit in Port 8 can be an input or output port. These are pin-shared with LCD Segment signal.  P90 ~ P97  I/O  Each bit in Port 9 can be an input or output port. These are pin-shared with LCD Segment signal.  P80 ~ P87  I/O  Each bit in Port B can be an input or output port. These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  INTO  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I/O        |              |                                                                                                                                           |  |  |  |  |  |

| Internal pull high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | P55 ~P57   | I/O          | Each bit in Port 5 can be an input or output port.                                                                                        |  |  |  |  |  |

| P70 ~ P77  I/O  Internal Pull-high function. Auto key scan function. Interrupt function.  P80 ~ P87  I/O  Each bit in Port 8 can be an input or output port. These are pin-shared with LCD Segment signal.  P90 ~ P97  I/O  Each bit in Port 9 can be an input or output port. These are pin-shared with LCD Segment signal.  PB0 ~ PB7  I/O  Each bit in Port B can be an input or output port. These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  INT0  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P60 ~P67   | I/O          |                                                                                                                                           |  |  |  |  |  |

| These are pin-shared with LCD Segment signal.  P90 ~ P97  I/O  Each bit in Port 9 can be an input or output port. These are pin-shared with LCD Segment signal.  PB0 ~ PB7  I/O  Each bit in Port B can be an input or output port. These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  INTO  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | P70 ~ P77  | I/O          | Internal Pull-high function. Auto key scan function.                                                                                      |  |  |  |  |  |

| These are pin-shared with LCD Segment signal.  PB0 ~ PB7  I/O  Each bit in Port B can be an input or output port. These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  INTO  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  TEST  I Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | P80 ~ P87  | I/O          |                                                                                                                                           |  |  |  |  |  |

| These are pin-shared with LCD Segment signal.  PC0 ~ PC7  I/O  Each bit in Port C can be an input or output port. These are pin-shared with LCD Segment signal.  INTO  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | P90 ~ P97  | I/O          |                                                                                                                                           |  |  |  |  |  |

| These are pin-shared with LCD Segment signal.  INTO  Ports 70~73  Interrupt sources with the same interrupt flag. A falling-edge signal on any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  TEST  I  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PB0 ~ PB7  | I/O          |                                                                                                                                           |  |  |  |  |  |

| any pin from Port 70 to Port 73 generates an interrupt.  INT1  Ports 74~76  Interrupt sources with the same interrupt flag. An edge signal on any pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  TEST  I Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | PC0 ~ PC7  | I/O          |                                                                                                                                           |  |  |  |  |  |

| pin from Port 74 to Port 76 generates an interrupt.  INT2  Port 77  Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt.  TEST  I Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | INT0       | Ports 70~73  |                                                                                                                                           |  |  |  |  |  |

| TEST I (controlled by the CONT register), it will generate an interrupt.  Sets the device to test mode for testing purposes only. Connect it to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |              |                                                                                                                                           |  |  |  |  |  |

| GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | INT2       | Port 77      | Interrupt source. Once Port 77 has a falling-edge or rising-edge signal (controlled by the CONT register), it will generate an interrupt. |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TEST       | 1            |                                                                                                                                           |  |  |  |  |  |

| /RESET   I   Reset pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | /RESET     | I            | Reset pin.                                                                                                                                |  |  |  |  |  |

# 7 Function Description

#### 7.1 Operational Registers

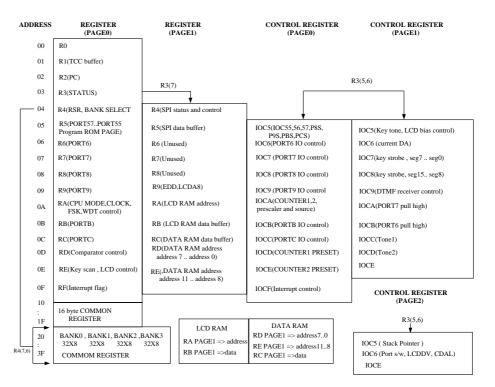

Fig.4 Control Register Configuration

#### 7.2 Operational Register Detailed Description

#### 7.2.1 R0 (Indirect Addressing Register)

R0 is not a physically-implemented register. It is useful as an indirect addressing pointer. Any instruction using R0 accesses data pointed by the RAM Select Register (R4).

#### Example:

```

Mov a,@0x20 ; stores an address at R4 for indirect addressing Mov 0x04,A Mov a,@0xAA ; writes data 0xAA to R20 at Bank 0 through R0 Mov 0x00,A

```

#### 7.2.2 R1 (TCC)

TCC data buffer. Incremented by 16.38kHz or by the instruction clock cycle (controlled by the CONT register).

Written and read by the program as any other register.

#### 7.2.3 R2 (Program Counter)

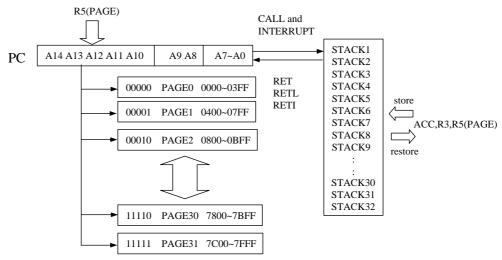

The structure is depicted in Fig. 5.

R2 generates 32K×13 on-chip program ROM addresses to the corresponding instruction codes.

"JMP" directly loads the low 10 program counter bits.

"CALL" loads the low 10 bits of the PC, PC+1, and then pushes the bits into the stack.

"RET" ("RETL k", "RETI") loads the program counter with the contents at the top of the stack.

"MOV R2,A" allows the loading of an address from the A register to the PC, and the ninth and tenth bits are cleared to "0".

"ADD R2,A" allows a relative address to be added to the current PC, and contents of the ninth and tenth bits are cleared to "0".

"TBL" allows a relative address to be added to the current PC, with the contents of the ninth and tenth bits remaining unchanged. The most significant bit (A10~A14) will be loaded with the contents of the bits PS0~PS3 in the status register (R5) upon the execution of a "JMP", "CALL", "ADD R2,A", or "MOV R2,A" instruction.

If an interrupt is triggered, the program ROM jumps to Address 8 at Page 0. The CPU will store ACC, R3 status and R5 PAGE automatically. It will be restored after instruction RETI.

Fig.5 Program Counter Organization

#### 7.2.4 R3 (Status Register)

| Bit 7 | Bit 6  | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

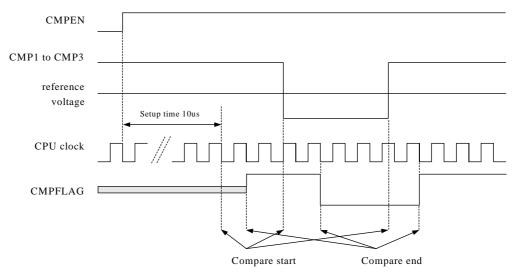

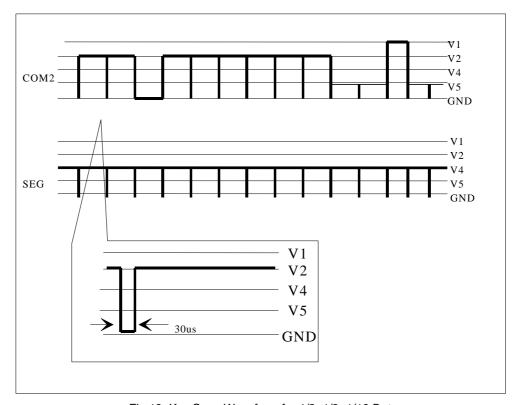

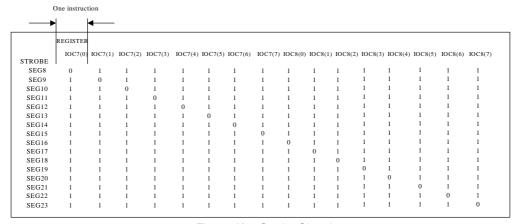

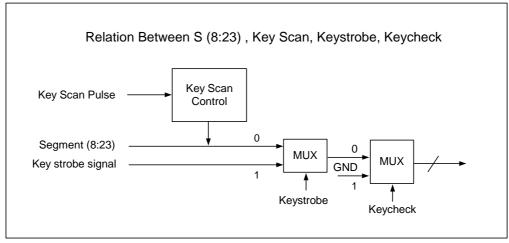

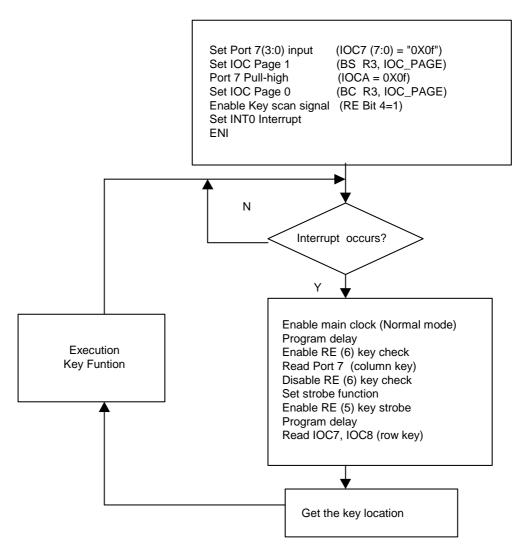

|-------|--------|---------|-------|-------|-------|-------|-------|